# Trade-off and Design optimization of the Notch filter for ultralow power ECG application

# Amit Kumar (EE16MTECH11015)

A Dissertation Submitted to

Indian Institute of Technology Hyderabad

In Partial Fulfillment of the Requirements for

The Degree of Master of Technology

# **Department of Electrical Engineering**

June, 2018

# **Declaration**

I declare that this written submission represents my ideas in my own words, and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources that have thus not been properly cited, or from whom proper permission has not been taken when needed.

(Signature)

Deceb

Amit Kumar EE16MTECH11015

# **Approval Sheet**

This thesis entitled "TRADE-OFF AND DESIGN OPTIMIZATION OF THE NOTCH FILTER FOR ULTRA-LOW POWER ECG APPLICATION" by AMIT KUMAR (EE16MTECH11015)

-Name and affiliationExaminer

Ashiral American Adviser

-Name and affiliation

Examiner

Ashiral American Adviser

-Name and affiliation

Co-Adviser

Chairman

# Acknowledgements

First of all, I would like to thank God Almighty for keeping me in good health and for all the grace.

I express my deepest gratitude to my supervisor Dr. Ashudeb Dutta for his worthwhile guidance, consistent moral support and impetus which helped me in the accomplishment of my thesis.

I would like to thank my parents for giving me this life. I couldn't have achieved anything without their support and I am indebted to them all life. I would like to thank my senior Pravanjan Patra Sir who guided me in my project and making me clear with many concepts. I would also like to thank my best friends Prakash Kumar Lenka, Narendra Nath Ghosh and Pankaj Kumar Jha Sir for being there with me in all times both professionally and personally

I thank IIT Hyderabad for giving me all facilities, Opportunities and resources for completing my Masters and helping for me to grow as Human.

# Dedicated to

My Parents and Pravanjan Patra Sir

# **Abstract**

ECG acquisition, several leads combined with signals from different body parts (i.e., from the right wrist and the left ankle) are utilized to trace the electric activity of the heart. ECG acquisition board translates the body signal to six leads and processes the signal using a low-pass filter (LPF) and SAR ADC. The acquisition board is composed of: an instrumentation amplifier, a high-pass filter, a 60-Hz notch filter, and a common-level adjuster. But miniaturization or need of portable devices for measuring Bio-Potential parameters has led to design of IC's for biomedical application with ultra-low power Because of miniaturization i.e. use of lower technology nodes has led to non-idealities which reduces the attenuation of Common Mode to differential component i.e. not CMRR. Because of this demerit the power line interference signal can't be assumed as a common mode signal. Hence we need to design a power line interference filter to avoid the contamination of the signal.

# **Contents**

|   | Declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | Approval Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3  |

|   | Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4  |

|   | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6  |

| 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9  |

|   | 1.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9  |

| 2 | Characterization of Notch Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11 |

|   | 2.1 Requirement for designing a Notch Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11 |

|   | 2.2 Design of Passive Notch Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11 |

|   | 2.3 Why do we need Active Notch Filter?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12 |

|   | 2.4 Active Notch Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12 |

|   | 2.4.1 Tow-Thomas Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12 |

|   | 2.4.1.1 Notch Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12 |

|   | 2.4.1.2 Notch Depth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13 |

|   | 2.4.1.3 Quality Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13 |

|   | 2.4.2 Modelling of each block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14 |

|   | 2.4.3 Operation of circuit at lower frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18 |

|   | 2.4.4 Operation of circuit at higher frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 |

|   | 2.5 Optimizing R and C Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21 |

| 3 | knowledgements       4         stract       6         oduction       9         Motivation       9         racterization of Notch Filter       11         Requirement for designing a Notch Filter       11         Design of Passive Notch Filter       11         Why do we need Active Notch Filter?       12         Active Notch Filter       12         2.4.1 Tow-Thomas Architecture       12         2.4.1.2 Notch Frequency       12         2.4.1.2 Notch Depth       13         2.4.2 Modelling of each block       14         2.4.3 Operation of circuit at lower frequencies       18         2.4.4 Operation of circuit at higher frequencies       20         Optimizing R and C Values       21         kground of OTAs       24         OTA Terminology       24         Different OTA Configuration       27         Recycling folded cascode OTA       36         Improved Recycling folded cascode OTA       42         Comparison of all the OTA       48 |    |

|   | 3.1 OTA Terminology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24 |

|   | 3.2 Different OTA Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27 |

|   | 3.3 Recycling folded cascode OTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36 |

|   | 3.4 Improved Recycling folded cascode OTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42 |

|   | 3.5 Comparison of all the OTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48 |

|   | 3.6 Application of OTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49 |

| $4~G_m/I_D~M$ | lethodology                                                                                                                                               | 47 |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| 4.1 Int       | <ul> <li>4.1 Introduction</li> <li>4.2 Different regions of operation</li> <li>4.3 Performance Comparison among Different regions of operation</li> </ul> |    |  |  |  |

| 4.2 Dif       |                                                                                                                                                           |    |  |  |  |

| 4.3 Per       |                                                                                                                                                           |    |  |  |  |

| 4.4 Dif       | ferent types of Model                                                                                                                                     | 54 |  |  |  |

| 5 OTA Desi    | gn and Analysis                                                                                                                                           |    |  |  |  |

| 5.1           | The Conventional Folded Cascode Amplifier                                                                                                                 | 57 |  |  |  |

| 5.2           | Recycling Folded Cascode Amplifier                                                                                                                        | 58 |  |  |  |

| 5.3           | Two Stage Recycling Folded Cascode Amplifier                                                                                                              | 60 |  |  |  |

| 5.4           | OTA Design requirements                                                                                                                                   | 61 |  |  |  |

| 5.4.1         | OTA Design Parameter                                                                                                                                      | 61 |  |  |  |

| 5.4.2         | Power Consumption of First Stage OTA                                                                                                                      | 61 |  |  |  |

| 5.4.3         | 2 <sup>nd</sup> Stage OTA                                                                                                                                 | 61 |  |  |  |

| 5.5           | Recycling Folded Cascode                                                                                                                                  | 62 |  |  |  |

| 5.5.1         | Design of RFC                                                                                                                                             | 62 |  |  |  |

|               |                                                                                                                                                           |    |  |  |  |

|               |                                                                                                                                                           |    |  |  |  |

| 6 Simulatio   | on and Results                                                                                                                                            | 65 |  |  |  |

| 7 Reference   |                                                                                                                                                           | 81 |  |  |  |

# **Chapter 1**

# **INTRODUCTION**

#### 1.1 Motivation

In the last Decade, there has been a growing demand for the design of wireless sensing device for biomedical applications. These devices are utilized for monitoring and recording bio-potential signals such as electrocardiogram (ECG), electroencephalography (EEG), and electromyography (EMG), to name a few.

Wearable monitoring systems provide tremendous benefits but they have many design challenges e.g. low power consumption, self-sustainability, light weight, affordability. Most crucial among previously mentioned issues are low power and self-sustainability. A typical biomedical wearable sensor consists of AFE, ADC and power module as shown in fig 1. To make the system self-sustainable an energy harvesting module has to be incorporated. For example, fig presents an ECG acquisition and processing system on chip (SoC) with energy harvesting module to make it self-sustainable. Although the above system fulfils the processing requirement but it suffers from a major drawback of high AFE power consumption  $(4.8\mu W)$  which leads to fast drainage of battery.

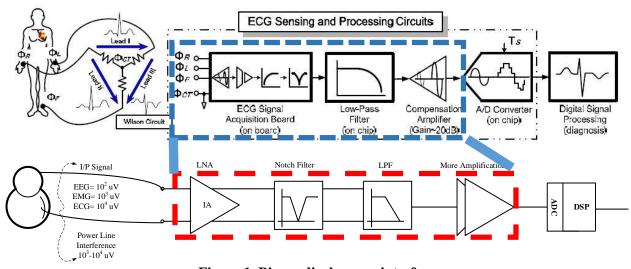

Figure 1. Bio-medical sensor interface

A detailed system level architecture of ECG acquisition unit is shown in fig 1. It consists of AFE which includes Instrumentation amplifier followed by two PGA, a mixed signal AGC and a 10-bit SAR ADC. The system is powered by RF energy harvesting circuit. The AFE combined with ADC consumes a total power of 343nW.

ECG acquisition, several leads combined with signals from different body parts (i.e., from the right wrist and the left ankle) are utilized to trace the electric activity of the heart. ECG acquisition board translates the body signal to six leads and processes the signal using a low-pass filter (LPF) and SAR ADC. The acquisition board is composed of: an instrumentation amplifier, a high-pass filter, a 60-Hz notch filter, and a common-level adjuster.

# Chapter 2

# **Characterization of Notch Filter**

## 2.1 Requirement for designing a notch filter

- ➤ ECG acquisition, several leads combined with signals from different body parts (i.e., from the right wrist and the left ankle) are utilized to trace the electric activity of the heart. ECG acquisition board translates the body signal to six leads and processes the signal using a low-pass filter (LPF) and SAR ADC.

- ➤ The acquisition board is composed of: an instrumentation amplifier, a high-pass filter, a 60-Hz notch filter, and a common-level adjuster.

- The main function of the acquisition board is to pre-amplify the weak ECG signal whose amplitude is between  $100\mu V$  and 4 mV.

- The range of the ECG signal means that this system requires a signal-to-noise and distortion ratio (SNDR) of at least 32 dB (that is, 6 bits) to detect heart activities precisely.

- ➤ The frequency range of the ECG signal is between 0.1 Hz to 250 Hz

- ➤ Therefore, an on-chip low-power LPF behind the acquisition board provides a low cut-off frequency (250 Hz) to decrease the out-of-band high-frequency noise.

- > On the other hand, the noise under 0.1 Hz will be eliminated by a high-pass filter on the acquisition board

# 2.2 Design of Passive Notch filter

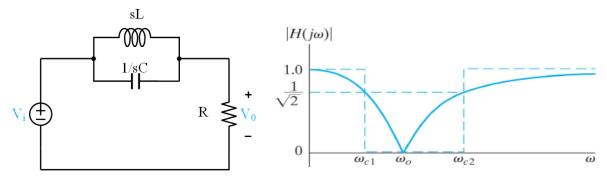

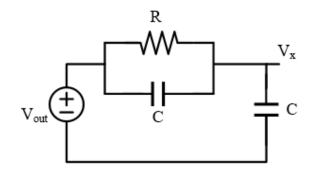

Transfer Function is given as:

$$T(s) = \frac{R}{R + Z_{eq}}, \ Z_{eq} = sL \left\| \frac{1}{sC} \right\|$$

(2.1)

$$T(s) = \frac{V_0}{V_i} = \frac{R}{\left(\frac{L}{C} + R\right)} = \frac{R\left(sL + \frac{1}{sC}\right)}{\left(\frac{L}{C} + R\left(sL + \frac{1}{sC}\right)\right)} = \frac{s^2 + \frac{1}{LC}}{s^2 + \frac{1}{RC}s + \frac{1}{LC}}$$

(2.2)

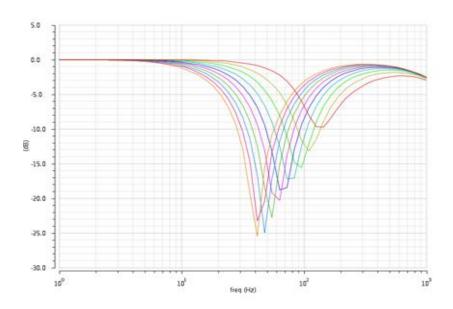

Fig:2.1 Notch Filter Circuit

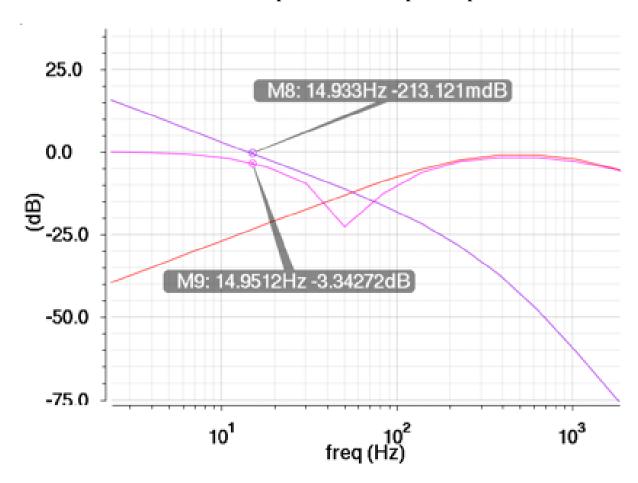

Fig:2.2 Plot Gain Vs frequency

# 2.3 Why do we need Active Notch filter

| PASSIVE                                                                                                                                                                                                                                                                | ACTIVE                                                                                                                                                                       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>inductors large for lower frequencies</li> <li>some inductors (non-toroidal) may require shielding</li> <li>limited standard sizes, often requiring variable inductors and therefore tuning</li> <li>low tolerance inductors (1-2%) very expensive</li> </ul> | <ul> <li>no inductors</li> <li>easier to design</li> <li>high Zin, low Zout for minimal loading</li> <li>can produce high gains</li> <li>generally easier to tune</li> </ul> |  |

| <ul> <li>must be designed with consideration to input and output loading</li> </ul>                                                                                                                                                                                    | small in size and weight                                                                                                                                                     |  |

| <ul><li>Generally not amenable to miniaturization</li><li>no power gain possible</li></ul>                                                                                                                                                                             |                                                                                                                                                                              |  |

| • no voltage gain                                                                                                                                                                                                                                                      |                                                                                                                                                                              |  |

# 2.4 Active Notch filter

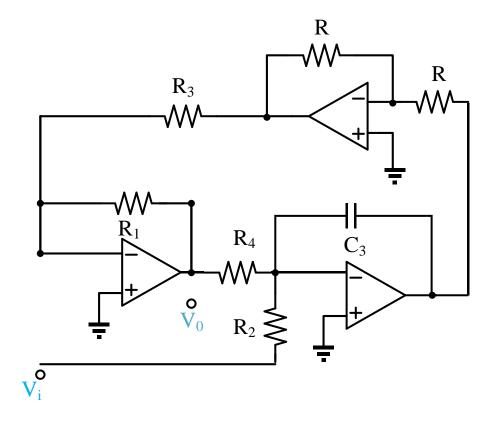

# 2.4.1 Tow-Thomas Architecture

2.4.1.1 Notch Frequency:

$$\omega_0 = \frac{1}{2^n R \sqrt{CC_3}} \tag{2.3}$$

2.4.1.2 Quality Factor:

$$Q = \sqrt{\frac{c}{c_3}}q \tag{2.4}$$

### 2.4.1.3 Notch Depth (p):

$$p = \frac{1}{\left|T_{(non-ideal)}(j\omega_0)\right|}$$

$$= 1 + \frac{C_3}{C} \left(\frac{A}{2q} + 1\right)$$

$$p = 1 + \sqrt{\frac{C_3}{C}} \left(\frac{A}{2Q} + \sqrt{\frac{C_3}{C}}\right)$$

(2.5)

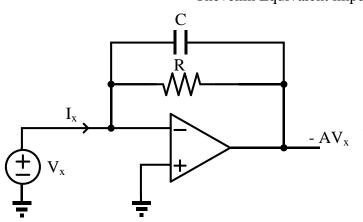

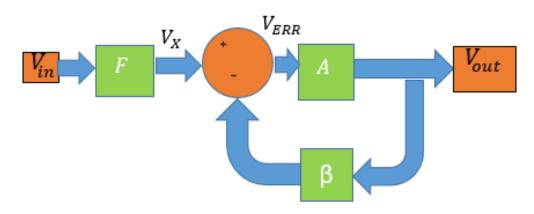

#### 2.4.2 **Modelling of Each block:**

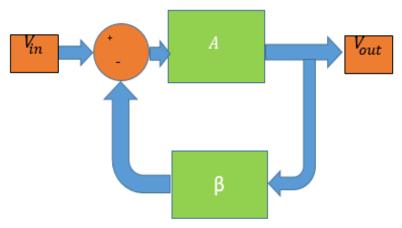

2.4.2.1 Mathematical Modelling of Closed Loop Architecture:

$$V_{out} = \frac{V_{in}*A}{(1+AB)} \tag{2.6}$$

$$Error = \frac{V_{in}}{(1+AB)} \tag{2.7}$$

$$V_{out} = \frac{V_{in}*A}{(1+A\beta)}$$

$$Error = \frac{V_{in}}{(1+A\beta)}$$

$$Feedback Path Voltage = \frac{V_{in}*A\beta}{(1+A\beta)}$$

$$(2.6)$$

Fig: 2.3 Closed Loop block diagram

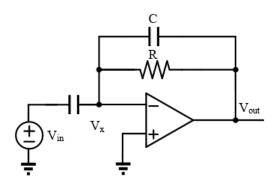

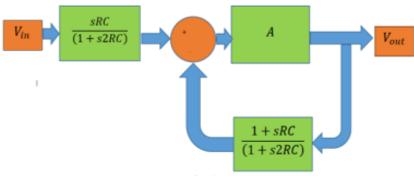

# 2.4.2.2 Mathematical Equivalent of High Pass Filter:

Feedback Path transfer function i.e. β

$$V_{out} = \frac{V_{in}}{\left(\frac{1}{G+sC} + \frac{1}{sC}\right)} \times \frac{1}{sC}$$

$$= \frac{V_{in}}{\left(\frac{sC}{G+sC} + 1\right)}$$

(2.9)

$$\frac{V_0}{V_i} = \frac{1}{\left(\frac{sC}{G+sC}+1\right)} = \frac{1}{\left(\frac{sRC}{1+sRC}+1\right)} = \frac{1+sRC}{1+s2RC}$$

(2.10)

Fig.2.4 High Pass Architecture

Fig.2.5 Feedback Architecture

# 2.4.2.3 Problem in error voltage:

Thevenin Equivalent impedance of the high pass filter

$$I_{x} = V_{x} (1+A)(G+sC)$$

$$\frac{V_x}{I_x} = \frac{1}{(1+A)(G+sC)}$$

$$Z_x = \frac{R}{(1+A)(1+sRC)}$$

$$Z_x = \frac{R}{(1+A)(1+sRC)}$$

$$(V_{in} - V_{err}) * sC = \frac{V_{err} * (1+A)(1+sRC)}{R}$$

$$\frac{V_{err}}{V_{in}} = \frac{sRC}{1 + s2RC + A * (1 + sRC)}$$

$$Error = \frac{V_{in}}{(1 + A\beta)}$$

$$\frac{V_{err}}{V_{in}} = \frac{1 + 2sRC}{1 + s2RC + A * (1 + sRC)}$$

; which is not correct

The below expression is real expression according to the circuit

$$\frac{V_{err}}{V_{in}} = \frac{sRC}{1 + s2RC + A * (1 + sRC)}$$

Note: This Discrepancy is because of input loading which is not taken care.

Fig: 2.6

$$V_{err} = \frac{V_x}{(1+A\beta)}$$

$$\frac{V_{err}}{V_x} = \frac{1+2sRC}{1+s2RC+A*(1+sRC)}$$

$$\frac{V_{err}}{V_{in}} = \frac{sRC}{1 + s2RC + A * (1 + sRC)}$$

$$Since, \quad \frac{V_{err}}{V_{in}} = \frac{V_{err}}{V_x} * \frac{V_x}{V_{in}}$$

$$cansfer Function \quad \frac{V_x}{V_x} = \frac{sRC}{V_x}$$

The Transfer Function,

$$\frac{V_x}{V_{in}} = \frac{sRC}{(1 + s2RC)}$$

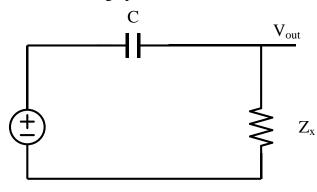

# 2.4.2.4 Complete Model of HPF

Fig: 2.7

### Conclusion-:

- The feedback is unity for lower frequencies.

- > Error voltage is zero as the input is blocked by capacitor.

- Feedback goes to 0.5 for frequencies greater than 1/RC.

- > The input is high passed with a gain of 1 after RC.

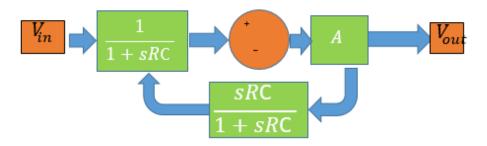

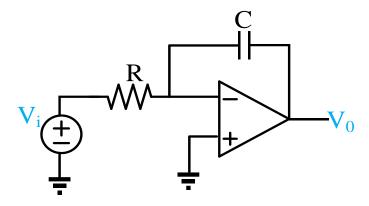

# 2.4.2.5 Mathematical modelling of integrater or LPF

Fig: 2.8

Fig: 2.9

# Conclusion

- $\triangleright$  Here the error voltage is Vin for frequencies <1/RC(1+A).

- ➤ The feedback factor goes to unity at -1/RC.

- $\rightarrow$  The gain is <1 after -1/RC.

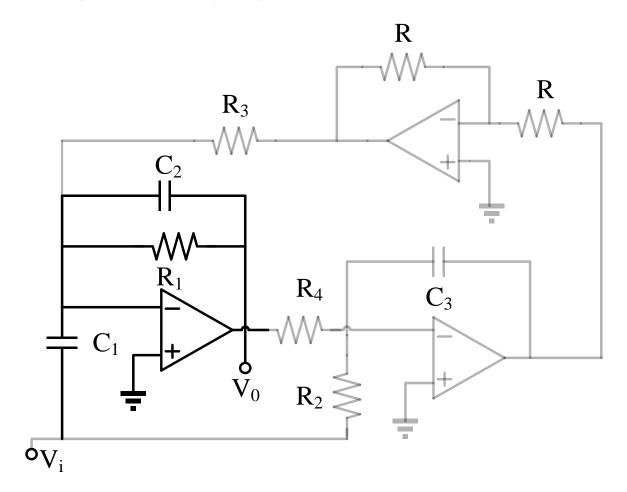

# **2.4.3** Operation of Circuit at Lower frequencies:

Fig:2.10

- For Lower frequencies, as we saw the input is high pass filtered by1st amplifier. The cutoff frequency is 1/R1C. Which is assumed to be lower than 1/R2C3.

- ➤ Hence to have a higher loop gain the R1/R3 ratio has to be improved i.e.>1. As the loop gain increases output voltage exactly follows the input voltage.

- ➤ The UGB of the 2nd amplifier i.e. integrator is -1/R2C3 for the input at lower frequencies.

- > The Loop Gain is shown by red loop. Once the loop gain goes to unity it gives -3dB point of the lower cutoff frequency.

- As R1 is increased the cutoff frequency can be moved but it leads to decrease in peaking as the attenuation decreases.

### 2.4.3.1 Loop Gain at Low Frequencies:

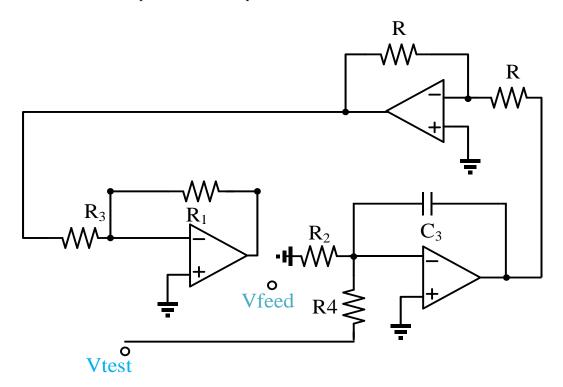

Fig: 2.11

- > Here the loop gain is found by applying a Vtest at the input of R4 and finding feedback at Vfeed.

- For proper negative feedback Vfeed has to be first order. So R1\*C2<R4\*C3.

- For more notch depth R1\*C2 should be around one third of R4\*C3.

- The frequency where  $\frac{V_{feed}}{V_{test}} = 1$ . It gives the lower cutoff frequency of the notch.

# **2.4.4** Operation of Circuit at higher frequencies

Fig: 12

- ➤ At higher frequencies i.e. frequencies greater than -1/R1C2. The part of the active circuit is shown in dark.

- ➤ -1/R1C2 provides the -3dB corner frequency in the upper side.

- ➤ The output is given by C1/C2 ratio which is chosen to be 1 as because of filter.

- The gain continues to be one till the loop gain is greater than one.

- ► Hence for a operation frequency of 250Hz the UGB of the amplifier has to be 500Hz as B=0.5.

- ➤ Hence maximum UGB required is 500Hz.

- As this amplifier should give a gain of 1 for higher frequencies compared to other amplifiers. Hence maximum UGB is given by this amplifier.

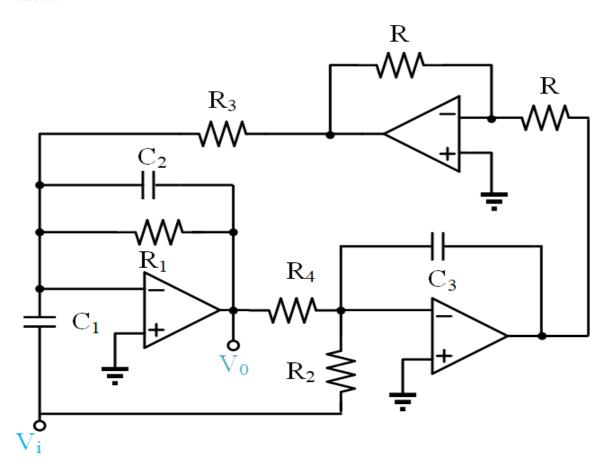

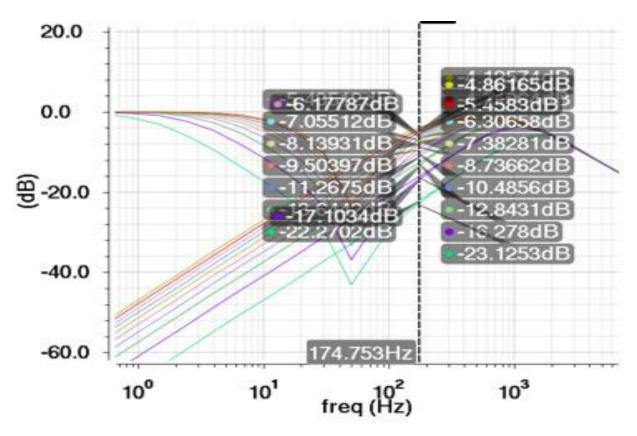

### 2.5 Optimizing the R and C values for Higher Notch depth(p)

- For getting higher notch values the quality factor of zeros has to be increased.

- The other way of optimizing is to increase C3/C ratio. Increasing C3 leads to a lower 3dB cutoff frequency again R4 and R2 has to be optimized. The values of R4 and R2 are kept same.

- The values of R2, R4 and C3 offers the lower cutoff frequency. The values for lower cutoff frequency is chosen to be greater than 10Hz. :  $R_2{}^=R_4=2^nR$  For having higher peaking q has to be less than or equal to 1.  $R_1=qR$

- For A gain of 1 at higher frequencies  $C_1=C_2=C$ For higher peaking and lower quality factor  $C_3>C$

- The design starts with fixing  $\omega_0 = {}^{2*}\pi * 55 \; rad/_{sec}$ Where  $\omega_0$  is given by:  $\omega_0 = \frac{1}{\sqrt{c C_3 2^{2n} R^2}}$

- Here the C is assumed to be 1p, N=15 and C3 is chosen to be 10p. The values are chosen such that it can be implemented within a low power and lower device area. Here n represents the number of R-2R ladders.

Fig: 13

#### 2.5.1 For High Notch Depth

$$p = \frac{1}{\left|T_{(non-ideal)}(j\omega_0)\right|}$$

$$= 1 + \frac{C_3}{C} \left(\frac{A}{2q} + 1\right)$$

$$= 1 + \sqrt{\frac{C_3}{C}} \left(\frac{A}{2Q} + \sqrt{\frac{C_3}{C}}\right)$$

#### **2.5.2** Tabulation of R and C Values:

| Parameters | Values |

|------------|--------|

| C1, C2     | 1pF    |

| C3         | 10pF   |

| N          | 15     |

| q          | 1      |

| R          | 176.5K |

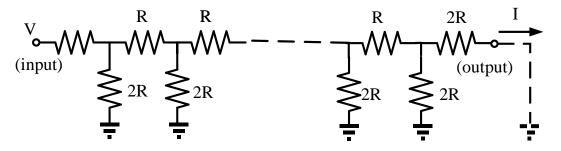

#### **2.5.3** Implementing higher resistance:

> For realizing higher value of resistance a R-2R ladder is implemented as shown in figure.

Fig: 14

- The capacitor values are also chosen to be minimum to reduce power consumption.

- > As capacitor will act as load.

# **Chapter 3**

# **Background of OTAs**

Operational amplifiers are amplifiers (various forms of controlled sources) with a very large forward gain (gain>80dB), the closed loop transfer function is independent of the gain of the amplifier. For CMOS on chip designs we conventionally design an Operational Transconductance Amplifier (OTA) as opposed to the discrete operational amplifier.

# 3.1 OTA Terminology

| OPAMP                                                                                                                                                              | OTA                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| High input impedance and low output impedance                                                                                                                      | High input impedance and output impedance.                                                                                 |

| Modelled as a voltage controlled voltage source because of the above property.                                                                                     | Modelled as a voltage controlled current source.                                                                           |

| Used with external feedback for feedback circuits. Used as an buffer. Contains compensation capacitor in its circuitry between the 2 stages (Miller Compensation). | All nodes are at low impedance except for the input and output nodes.                                                      |

| OpAmp becomes unstable with large load capacitance.                                                                                                                | Better Frequency capabilities than Op-Amp. As load capacitance increases the phase margin increases and the OTA is stable. |

| An OTA with output buffer is an OPAMP.                                                                                                                             | Generally a single state design.                                                                                           |

*Gain*: For any CMOS topology the gain of the circuit is given by the product of its transconductance and the output resistance of the load structure. The gain is strongly dependent on the frequency of

the input signal. At higher frequencies the inherent parasitic capacitances of the circuit reduce the gain. The gain expression can be given as

$$A_v = g_m * R_{out} (3.1)$$

Where  $g_m$  represents the transconductance and  $R_{out}$  represents the output resistance of the circuit. Unity Gain Bandwidth: This specifies the frequency at which the amplifier gain is unity. The maximal capacitance at the output node gives this specification. There is always a trade-off in achieving high gain and high bandwidth as the high gain-bandwidth for any amplifier is constant for a particular design.

$$f_u = \frac{g_m}{2\pi C_l} \tag{3.2}$$

Where  $f_u$  represents the unity gain bandwidth and  $g_m$  represents the transconductance of the circuit and  $C_l$  represents the load capacitance.

*Phase Margin*: The phase margin (PM) will determine the stability of an amplifier. Higher values of PM will allow the output signal to achieve steady state without much ringing. Lower values will cause ringing at the output. In our design we require PM>60<sup>o</sup>.

$$PM = 180 - \arctan\left(\frac{f_u}{f_{dv}}\right) - \arctan\left(\frac{f_u}{f_{ndv}}\right)$$

(3.3)

Where  $f_{dp}$  is the dominant pole and  $f_{ndp}$  are the non-dominant poles in the amplifier transfer function. This equation has ignored the zeros in the amplifier transfer function.

Common Mode Input Range: This is an important parameter at the input of the circuit. The saturation voltage of the bias architecture, the saturation voltage, and  $V_{GS}$  voltage haedroom of the transconductance structure define the CMIR. An approximate expression can be given as

$$CMIR = V_{DD} - V_{GS} - V_{Dsat} (3.4)$$

Similarly Differential mode input range (DMIR) is the  $V_{GS}$  in the circuit. The available supply voltage  $V_{DD}$  defines the type of configuration which can be used for obtaining highest CMIR.

Output Swing: This specification relates to the output of the amplifier. The saturation voltage of the load structure mainly defines the output swing of the amplifier. In general the cascode structures results in a low output swing as more number of transistors as stacked under each other and the  $V_{DSsat}$  subtracted from the  $V_{DD}$  provides the output voltage swing

$$ODR = V_{DD} - \sum V_{DSsat} V_{Ssat}$$

(3.5)

Static Current Consumption: The product of the current in all the amplifier branches and the supply voltage defines this specification. Careful design needs to be done if the power budget allocated is very low. For decreasing the power consumption, the OTAs can be operated in different regions of operation.

*Slew Rate:* The output capacitance and the current flowing in the output branch defines this parameter. High Slew rate designs requires high values of current which may affect other specifications in the amplifier design.

$$SR = \frac{I_{out}}{C_{load}} \tag{3.6}$$

The speed of an amplifier is dependent on the equivalent RC constant at the output node. It also depends on the current sourcing/sinking capability at the output. Thus it is a strong function of the internal capacitances and currents in the amplifier branches.

Common Mode Rejection Ratio (CMRR): The common mode gain is given by the gain of the common mode input to the output. The Common mode rejection ratio is the difference of the differential gain from the common mode gain. The CMRR should be very high such that the cancellation of the signals is proper. The common mode gain is given by

$$A_{CM} = g_m * R_{out} (3.7)$$

$$CMRR = A_{DM} - A_{CM}$$

(3.8)

The  $A_{CM}$  represents the common mode gain,  $g_m$  represents the common mode transconductance and  $R_{out}$  represents the common mode output resistance.  $A_{DM}$  represents the differential mode gain. CMRR is given by the difference of common mode and differential mode gain.

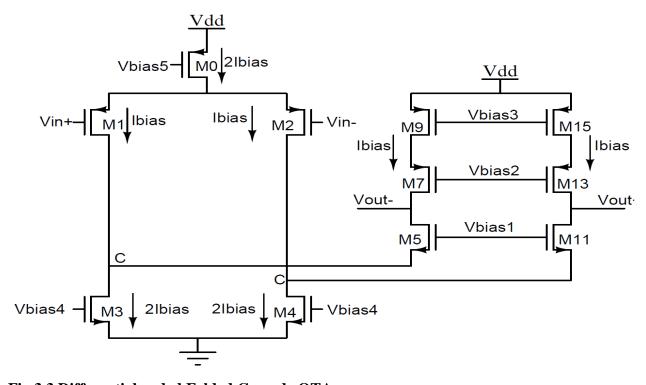

#### 3.2 Different OTA configuration

Cascode circuits are widely used for increasing the gain and output resistance of the OTA. Many positive feedback techniques [1], [2] are used for enhancing the gain by increasing the output resistance. For high UGB and high gain, many architectures has been reported in the literature such as Differential Amplifier, Folded Cascode (FC), Enhanced Fully Differential Folded cascode (EFC), Recycling Folded Cascode (RFC) and Improved Recycling Folded Cascode (IRFC).

### 3.2.1 Telescopic Differential Amplifier

Fig 3.1 Telescopic Differential Amplifier

The NMOS type differential equation is shown in the Fig.2.1. M1 and M2 are the input transistors. M3 and M4 are the Cascode transistors used to increase the resistance of the current source. The half circuit of the differential amplifier is shown in Fig.2.2.

Fig 3.2 Small signal equivalent of Telescopic OTA

DC Gain

The gain is given by

$$A_v = G_m * R_{out} (3.9)$$

where  $G_m$  represents the transconductance and Rout represents the output resistance of the differential amplifier.

The transconductance of the telescopic differential amplifier is given by

$$I_{out} = g_{m1}V_{in} (3.10)$$

$$G_m = g_{m1} (3.11)$$

Where  $g_{m1}$  is the transconductance of the input transistor M1 of the differential amplifier.

The output impedance Rout of the telescopic differential amplifier is given by

$$R_{out} = (g_{m3}r_{o3}r_{o1})||(g_{m5}r_{o5}r_{o7})$$

(3.12)

*Frequency Response:* There are two poles in the telescopic differential amplifier. One is non dominant and other is the dominant pole.

1. Dominant pole-: The dominant pole exists at the output node as the resistance and the capacitance at the output node is very high. The pole frequency is given by

$$\omega_{p1} = \frac{1}{R_{out} * C_{load}} \tag{3.13}$$

$$C_{load} = C_l + C_{DS4} + C_{DS6} + C_{GD4} + C_{GD6}$$

$R_{out}$  is the output impedance and  $C_{load}$  is the output capacitance of the telescopic differential amplifier.

2. Non-dominant Pole-: The non dominant pole exists at the cascode node of the differential amplifier. The non dominant pole frequency is given by

$$\omega_{p2} = \frac{1}{R_C * C_C} \tag{3.14}$$

$$R_c = \frac{1}{g_{m3}}$$

The resistance at the cascode node is given by  $R_C$  and capacitance is given by  $C_c$ . The  $\omega_{p2}$  is at a very high frequency which leads to a very high phase margin.

Common Mode Gain-:

The common mode gain is found by sorting the output nodes and input nodes. The half circuit for calculating the common mode gain is shown in Fig.2.3.

Fig: 3.3 Half circuit for calculation of common mode gain of the Telescopic OTA

In case of differential signal the transistor M9 does not comes into effect as its drain node acts as an virtual ground. But in case of common mode signal M9 acts as a source degeneration transistor for M2. Due to which the input transconductance decreases and the common mode gain decreases.

The common mode gain is given by

$$A_{cm} = -\frac{g_{m2}}{(1 + 2 * g_{m2} * r_{09})} * \left(\frac{g_{m4}r_{04}(r_{02} + r_{09})}{2}\right) || \left(\frac{g_{m6}r_{06}r_{08}}{2}\right)$$

(3.15)

Where  $A_{cm}$  is the common mode gain of the telescopic differential amplifier. The resistance decreases by two because of the two paths are sorted and both are parallel to each other. As the common mode gain decreases the CMRR increases which leads to a better performance.

# Limitations of Telescopic Differential Amplifier

In telescopic differential amplifier the swing at the output node decreases due to a large number of transistors are in series which leads to a consumption of large amount of over drive. To improve the gain of the differential amplifier the cascoding of transistors is done which further leads to decrease in the signal swing at the output. This limitation is solved by using folded cascode OTA.

### 3.2.2 Folded Cascode OTA

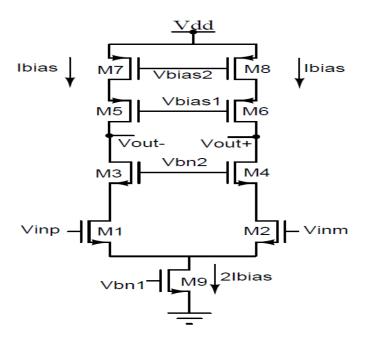

Fig 3.3 Differential ended Folded Cascode OTA

A PMOS type folded cascode OTA is shown in Fig.2.4. In PMOS type folded cascode the input drivers are of P-type M1 and M2. The signal generated by the M1 and M2 are given to the

NMOS cascode transistors M5 and M11. M5 and M11 acts as a common gate stage as no incremental current flows through M3 and M4 as it acts as a folding node denoted by 'C'.

The half circuit of the folded cascode is given in the Fig.2.5 below.

Fig 3.4 Small signal equivalent of Folded cascode OTA

### DC GAIN

The DC gain of the folded cascode is given by

$$A_{vfc} = G_{mfc} * R_{outfc} (3.16)$$

The  $G_{mfc}$  represents the transconductance and  $R_{outfc}$  represents the output impedance of the folded cascode OTA. The transconductance of the folded cascode is given by the input transistor.

$$G_{mfc} = g_{m1a} (3.17)$$

The output resistance of the folded cascode OTA is given by

$$R_{outfc} = g_{m5}r_{o5}(r_{o1a}||r_{o3a})||(g_{m7}r_{o7}r_{o9})$$

(3.18)

Frequency Response

In folded cascode OTA there are two poles. One is dominant pole and other is non dominant pole. The dominant pole is at the output node and the non-dominant pole is at the cascode node of the folded cascode OTA.

### 1. Dominant Pole

The dominant pole frequency  $\omega_{p1}$  at the output node is given by

$$\omega_{p1} = \frac{1}{R_{outfc}C_{outfc}} \tag{3.19}$$

$$C_{outfc} = C_l + C_{DS5} + C_{DS7} + C_{GD5} + C_{GD7}$$

(3.20)

The capacitance at the output node is given by  $C_{outfc}$ .  $C_{l}$  represents the load capacitance of the OTA for which it is designed. The dominant pole frequency is also known as the 3-dB bandwidth of the OTA.

#### 2. Non Dominant Pole

The non dominant pole frequency is given by  $\omega_{p2}$

$$\omega_{p2} = \frac{1}{R_c C_c} \tag{3.21}$$

Where Rc represents the cascode resistance and Cc represents the cascode node capacitance at the folding node. The resistance at the cascode node is given by

$$R_{cfc} = \frac{1}{g_{m5}} \tag{3.22}$$

The capacitance at the cascode node is given by

$$C_{cfc} = C_{GS5} + C_{DS3} + C_{DS1} + C_{GD1} + C_{GD3}$$

As the resistance is very low at the cascode node the non dominant pole is at a very high frequency which leads to a higher phase margin. As the phase margin is very high the stability of the system is maintained.

*Unity Gain Band Width (UGB)*

The UGB is defined as the frequency at which the voltage gain is unity or 0dB. The UGB of the OTA is given by

$$UGB = \frac{g_{m1}}{c_{load}} \tag{3.23}$$

The UGB of the OTA depends upon the input transconductance and the load capacitance. As the load capacitance increases the UGB decreases and the phase margin increases. The UGB increases with the increase in the DC current through the input transistor as the input transconductance increases.

### Common Mode Gain of Folded cascode OTA

The common mode gain of the folded cascode OTA is discussed in this section. The transistor M0 for a common mode signal behaves as a resistance  $r_0$ . The output resistance is half for common mode signal compared to the differential signal. The common mode gain equation is given by

$$A_{cm} = G_{mcmfc} * R_{outcmfc} (3.24)$$

$$G_{mcmfc} = -\frac{g_{m1}}{(1+2*g_{m1}*r_0)}$$

$$R_{out} = \left(g_{m5}r_{05}\left(\frac{r_{03}}{2}\middle|\left(\frac{g_{m1}r_{01}r_{00}}{2}\right)\right)\middle|\left(\frac{g_{m7}r_{07}r_{09}}{2}\right)\right)$$

$$Void \qquad Void \qquad$$

Fig 3.5 Half circuit of Folded Cascode OTA for finding Common Mode gain

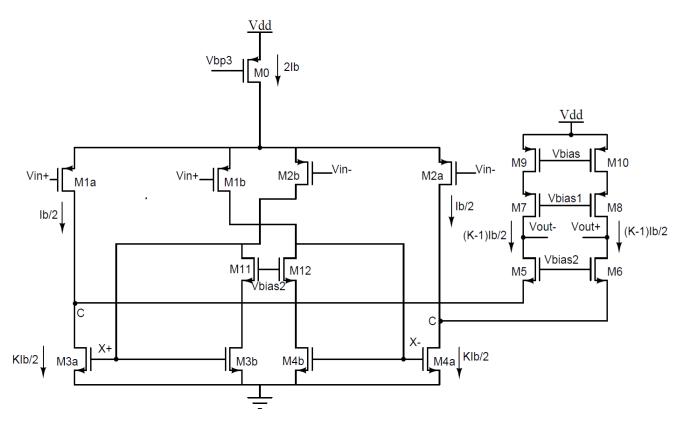

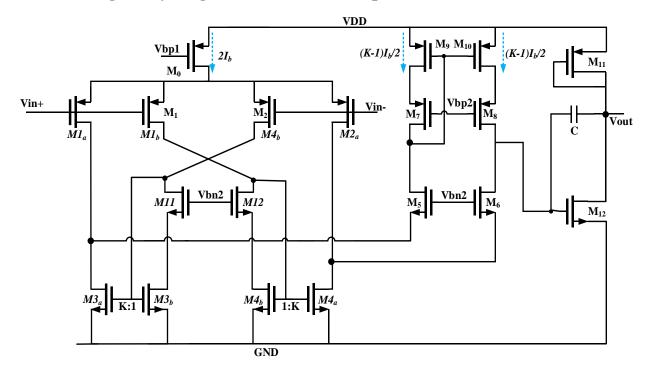

### 3.3 RECYCLIC FOLDED CASCODE OTA

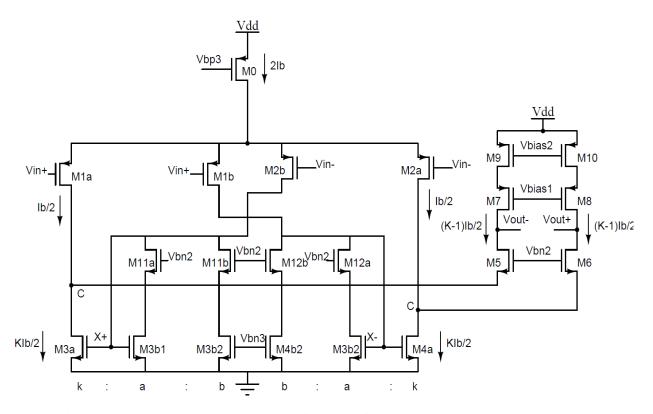

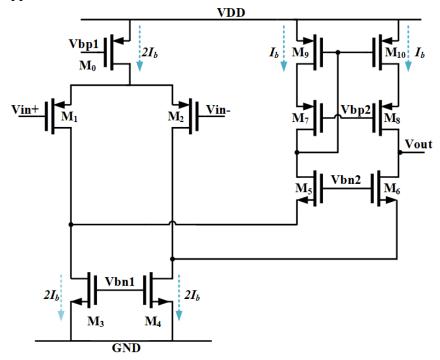

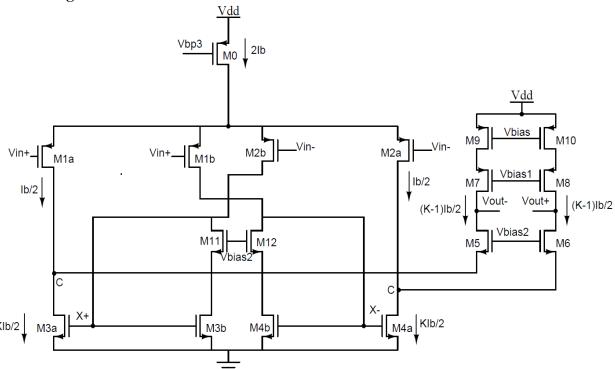

The bias current sources in the conventional FC [3] consume high current, and have large transconductance. However, these current sources don't contribute to the DC gain. In [4], the input transistors of FC are split into two parts (M1a, M1b, M2a, M2b) which conduct fixed and equal currents of  $I_b/2$ . Next the current source transistor in the FC is replaced by current mirrors M3a:M3b and M4a:M4b at a ratio of K: 1. This architecture is called as the RFC OTA and is shown in Fig.2.7.

Fig 3.6 Recycling Folded Cascode OTA

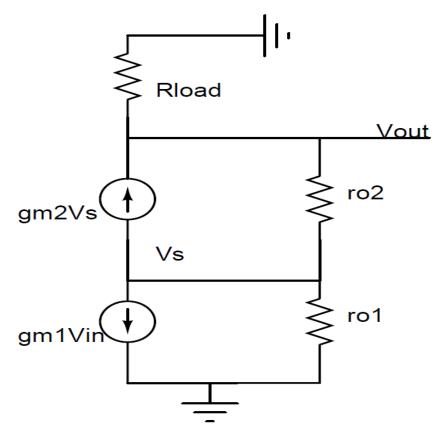

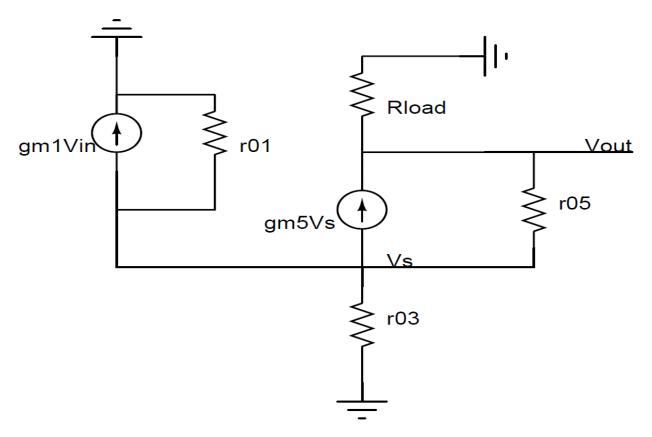

Fig 3.7 Small signal equivalent of Recycling Folded Cascode OTA

DC Gain

The DC gain A<sub>v</sub> of the RFC [4] is given by

$$A_v = G_m * R_{out} (3.25)$$

where  $G_m$  is the transconductance and  $R_{out}$  is the output impedance. The transconductance  $G_m$  is given by

$$G_m = I_{out}/V_{i+} (3.26)$$

where the output current Iout is given by

$$I_{out} \approx g_{m1a} V_{i+} + g_{m3a} V_{x+} \tag{3.27}$$

From Fig.2.7, it can be seen that transistors M2b and the diode connected transistors M11 and M3b act as a common source amplifier with a voltage gain of approximately -1. Since, the input applied to M2b is in opposite direction, the node  $X_+$  (or  $X_-$ ) is in the same phase of  $V_{i+}$  (or  $V_{i-}$ )

where

$$V_{x+} \approx -g_{m2h}R_xV_{i-}$$

and

$$R_x = \frac{1}{g_{m3b}}$$

Hence

$$V_{x+} \approx V_{i+}$$

Substituting  $V_{x+}$  in (2.27)

$$I_{out} = g_{m1a}V_{i+} + g_{m3a}V_{i+} (3.28)$$

Substituting (2.28) in (2.26) gives the small signal transconductance G<sub>m</sub>.

$$G_m = g_{m1a} + g_{m3a} (3.29)$$

where

$$g_{m3a} \approx K. g_{m1a} \tag{3.30}$$

The output impedance Rout of the RFC OTA is given by

$$R_{out} = g_{m5} r_{05}(r_{01a} || r_{03a}) || g_{m7} r_{07} r_{09}$$

(3.31)

Using (2.30) and (2.31) in (2.25),  $A_v$  is given by

$$A_{v} \approx g_{m1a}(K+1).g_{m5}r_{05}(r_{01a}||r_{03a})||g_{m7}r_{07}r_{09}$$

(3.32)

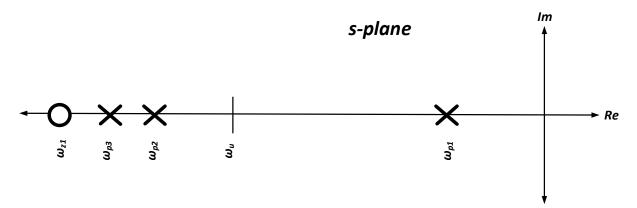

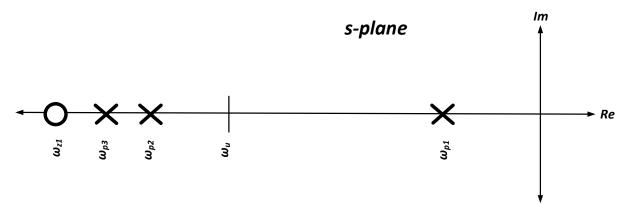

Frequency Response Analysis:

From Fig.2.8, it is observed that there are three poles and one zero. For practical purposes, we need to consider only the poles occurring at the output node and cascode node as the other pole and zero lie far away from origin.

### 1.Dominant Pole:

Because of high impedance ( $R_{out}$ ) and large capacitance ( $C_{out}$ ) at the output node, the dominant pole occurs in this node.

The dominant pole frequency  $\omega_{p1}$  (f-3db) is given by

$$\omega_{p1} = 1/R_{out}C_{out} \tag{3.33}$$

Where

$$R_{out} \approx g_{m5} r_{o5} (r_{01a} || r_{03a}) || g_{m7} r_{07} r_{09}$$

and

$$C_{out} = C_l + C_{DB8} + C_{GD8} + C_{GD6} + C_{DB6}$$

#### 2. Non-Dominant Pole:

It occurs in the cascode node C at a very high frequency compared to the dominant pole. Since the output capacitance bypasses the effect of output impedance, an equivalent impedance  $R_C$  at the cascode node is approximately  $1/g_{m5}$ . Hence, the non-dominant pole frequency  $\omega_{p2}$  is given by

$$\omega_{p2} \approx 1/R_c C_c \tag{3.34}$$

Where

$$C_C \approx C_{GD3a} + C_{GS5} + C_{GD1a} + C_{DB3a} + C_{DB1a} + C_{SB5}$$

The UGB of the OTA is given by

$$UGB = Av *f_{-3db}$$

(3.35)

Using (3.30) & (3.35)

$$UGB \approx g_{m1a}(K+1)/C_{out} \tag{3.36}$$

From (3.30) & (3.35), it is observed that the  $A_V$  and UGB are enhanced by a factor of 2 (for K=3 and  $g_{m1}$  of  $FC=2g_{m1a}$ ), compared to the FC for the same power and area.

#### Common Mode Gain

Fig 3.8 Half Circuit equivalent for finding Common Mode Gain

The common mode operation of RFC is described next. For common mode input, the signal at the gate of M1a and M3a are out of phase. So as the common mode input decreases the current in M1a increases and the current in M3a also increases because of out of phase. So, if the small signal current coming from the M1a is  $\Delta I_d$  then current going through M3a is  $K\Delta I_d$ . Hence  $(K-1)\Delta I_d$  is now coming from the output node to the cascode node. Hence, the transconductance and output resistance may be shown to be given by (3.37) and (3.38).

$$G_m = \frac{I_{out}}{V_{in}} \approx 2g_{m1a}(K - 1) \tag{3.37}$$

$$R_{out} = \left(\frac{g_{m9}r_{09}r_{013}}{2}\right)||g_{m5}r_{o5}(r_{01a}||r_{03a})$$

(3.38)

Hence, the common mode gain is given by (21)

$$A_{cm} = G_m * R_{out}$$

$$A_{cm} = 2g_{m1a}(K-1)\left(\left(\frac{g_{m9}r_{09}r_{013}}{2}\right)||g_{m5}r_{o5}(r_{01a}||r_{03a})\right)$$

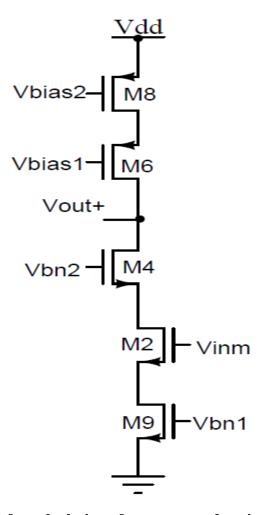

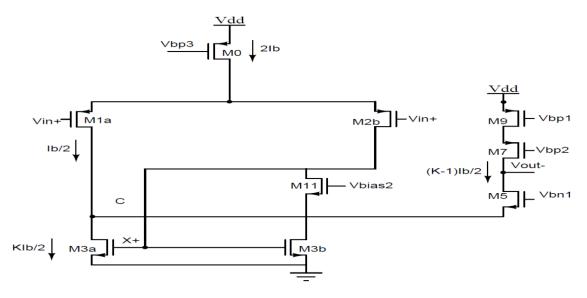

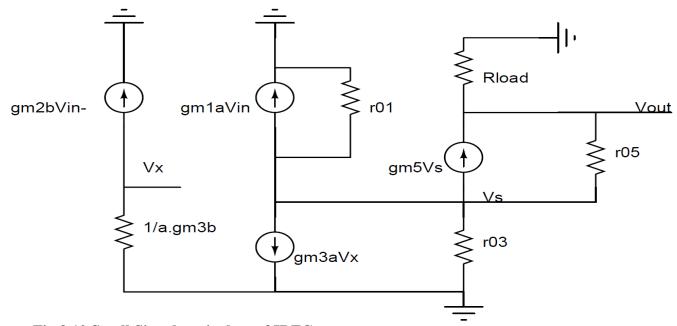

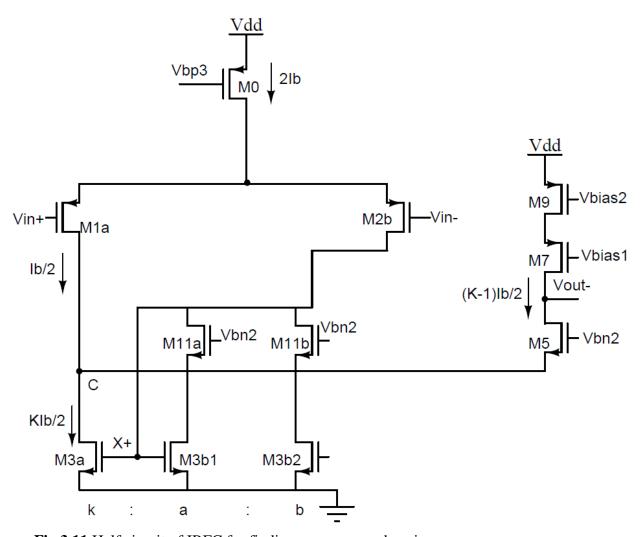

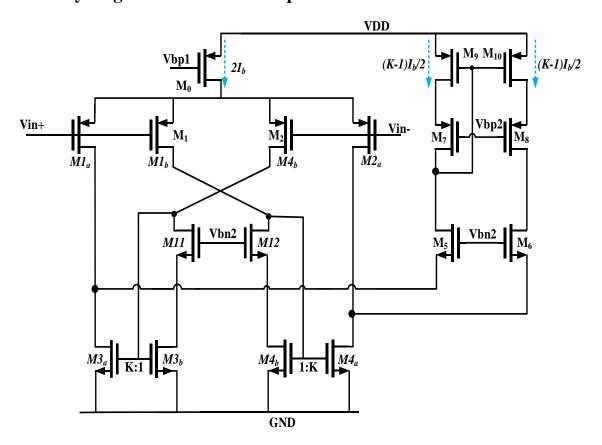

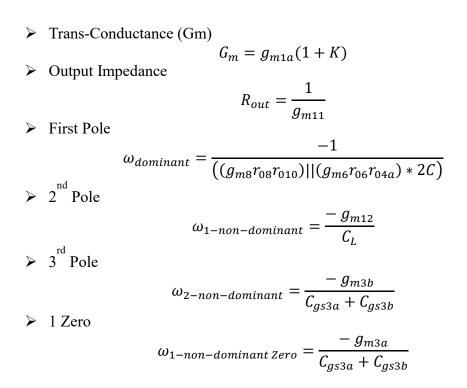

#### 3.4 Improved Recycling Folded Cascode Amplifier

To improve the signal swing at the current mirror node X+ (or X-), the DC and AC path are separated in IRFC proposed in [5] and is shown in Fig.2.10. To achieve this, the transistors M11, M3b and M12, M4b are divided into two parts M11a, M11b, M3b1, M3b2 and M12a, M12b, M4b1, M4b2 respectively. The paths M11b, M3b2 and M12b, M4b2 have high impedance ( $g_{m11b}r_{03b2}$ ). The paths M11a, M3b1 and M12a, M4b1 and have low impedance ( $^{1}/g_{m3b1}$ ). The small signal current flows through the low impedance path. The ratio of DC currents flowing through the high impedance and low impedance paths is a : b and the transconductance of M11a, M3b1 is scaled by 'a' where a < 1. The signal flowing through the current mirror node becomes larger compared to that of the RFC due to the increase in the resistance of the small signal path.

Fig 3.9 Improved Recycling Folded Cascode OTA

DC Gain

Generally the DC gain  $A_v$  of the OTA is given by (2.39)

$$A_{v} = G_{m} * R_{out} \tag{3.39}$$

where  $G_m$  is the transconductance and  $R_{out}$  is the output impedance.

The transconductance of  $G_{mIRFC}$  is given by

$$G_{mIRFC} = I_{out}/V_{in+} (3.40)$$

where the output current  $I_{out}$  is given by

$$I_{out} \approx g_{m1a} V_{in+} + g_{m3a} V_{x+} \tag{3.41}$$

From Fig.3.10, it can be seen that transistors M2b and the diode connected transistors M11a and M3b1 act as a common source amplifier with a voltage gain of approximately  $^{-1}/_a$ . Since, the input applied to M2b is in opposite direction, the voltage at node  $X_+$  (or  $X_-$ ) has the same phase as that of  $V_{in+}$  (or  $V_{in-}$ )

where

$$V_{x+} \approx -g_{m2b} R_x V_{in-}$$

$$R_x = \frac{1}{a.g_{m3b1}}$$

Hence

$$V_{x+} \approx \frac{-V_{\rm in-}}{a}$$

Substituting  $V_{x+}$  in (3.41)

$$I_{out} = g_{m1a}V_{in+} + \frac{1}{a}g_{m3a}V_{in+}$$

(3.42)

Substituting (2.42) in (2.40) gives the small signal transconductance  $G_m$ .

$$G_{mIRFC} = g_{m1a} + \frac{1}{a} g_{m3a}$$

(3.43)

Where

$$g_{m3a} \approx \text{K.} g_{m1a}$$

The output impedance  $R_{out}$  of the IRFC OTA is given by

$$R_{outIRFC} = g_{m5}r_{05}(r_{01a}||r_{03a})||g_{m7}r_{07}r_{09}$$

(3.44)

Substituting (2.43) and (2.44) in (2.39) the voltage gain of IRFC OTA is given by (2.45)

$$A_v = g_{m1a}(\frac{K}{a} + 1) * g_{m5}r_{05}(r_{01a}||r_{03a})||g_{m7}r_{07}r_{09}$$

(3.45)

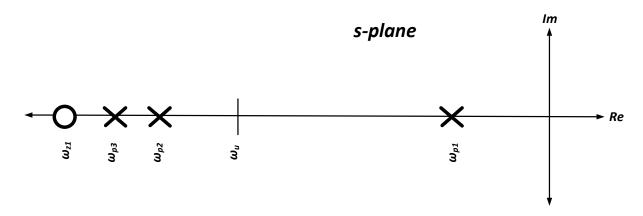

Frequency Response Analysis

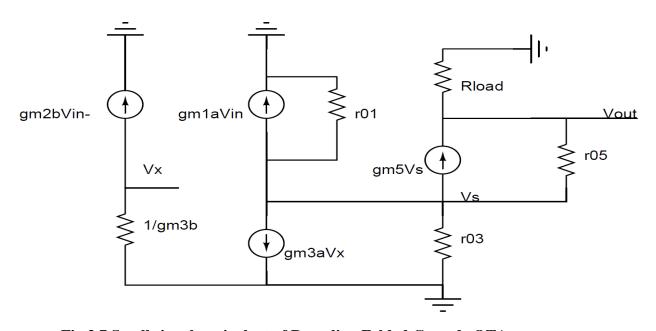

From Fig.3.11, it is observed that there are three poles and one zero. For practical purposes, we need to consider only the poles occurring at the output node and cascode node as the other pole and zero lie far away from origin.

Fig 3.10 Small Signal equivalent of IRFC

#### 1 Dominant Pole:

Because of high impedance ( $R_{outIRFC}$ ) and large capacitance ( $C_L$ ) at the output node, the dominant pole occurs in this node.

The dominant pole frequency  $\omega_{p1}$  (f-3db) is given by

$$\omega_{p1} = 1/R_{outIRFC}C_L \tag{3.46}$$

where

$$R_{outIRFC} \approx g_{m5} r_{o5} (r_{01a} || r_{03a}) || g_{m7} r_{07} r_{09}$$

and

$$C_{out} = C_l + C_{DB8} + C_{GD8} + C_{GD6} + C_{DB6}$$

#### 2. Non-Dominant Pole:

It occurs in the cascode node C at a high frequency compared to the dominant pole. Since the output capacitance bypasses the effect of output impedance, an equivalent impedance  $R_C$  at the cascode node is approximately  $1/g_{m5}$ . Hence, the non-dominant pole frequency  $\omega_{p2}$  is given by

$$\omega_{p2} = 1/RC.CC \tag{3.47}$$

where

$$C_C \approx C_{GD3a} + C_{GS5} + C_{GD1a} + C_{DB3a} + C_{DB1a} + C_{SB5}$$

The UGB of the OTA is given by

$$UGB = Av * f_{3db} (3.48)$$

Substituting

$$UGB \approx g_{m1a}(\frac{K}{a} + 1)/C_L \tag{3.49}$$

From (3.45) & (3.49), it is observed that the  $A_V$  and UGB are enhanced by a factor of 1/a, compared to the RFC [4] for the same power and area.

#### Common mode gain of IRFC

In the IRFC OTA, for common mode input, the signal at the gate of M1a and M3a are out of phase. So, as the common mode input decreases, the current in M1a increases and the current in M3a also increases because of out of phase. So, if the small signal current through the M1a is  $\Delta I_d$ , then current through M3a is  $K/a \Delta I_d$ . Hence, a current of  $\left\{\frac{K}{a}-1\right\} \Delta I_d$  flows from the output node to the cascode node. Hence, the transconductance and output impedance may be shown to be given by (3.50) and (3.51).

Fig 3.11 Half circuit of IRFC for finding common mode gain

$$G_m = \frac{I_{out}}{V_{in}} \approx g_{m1a.} \cdot (K/a - 1)$$

(3.50)

$$R_{out} = \left(\frac{g_{m7}r_{07}r_{09}}{2}\right) ||\frac{g_{m5}r_{o5}(r_{01a}||r_{03a})}{2}$$

(3.51)

Hence, the CM gain of IRFC is given by (3.52)

$$A_{cmIRFC} = g_{m1a} \cdot \left(\frac{K}{a} - 1\right) * \left\{ \left(\frac{g_{m7}r_{07}r_{09}}{2}\right) || \left(\frac{g_{m5}r_{o5}(r_{01a}||r_{03a})}{2}\right) \right\}$$

(3.52)

# 3.5 Comparison of All the OTAs

| Performance<br>Parameters | Telescopic<br>Differential | Folded Cascode OTA                          | Recycling Folded<br>Cascode OTA                                                   | Improved Recycling Folded Cascode OTA                                                           |

|---------------------------|----------------------------|---------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Transconductance          | High                       | Low compared to telescopic differential OTA | High compared to Folded Cascode OTA. Similar to Telescopic OTA for K=3.           | High compared to all the OTAs.                                                                  |

| Output resistance         | High                       | Same as that of the Telescopic OTA          | Same as that of the Telescopic OTA                                                | Same as that of<br>the Telescopic<br>OTA                                                        |

| Phase Margin              | High                       | High                                        | Low compared to folded cascode OTA due to current mirror node in the signal path. | Low compared<br>to RFC due to a<br>high resistance<br>Path formed by<br>M11,M3b and<br>M12,M4b. |

| UGB                       | High                       | Low compared to<br>Telescopic OTA           | High compared to folded cascode OTA. Similar to telescopic for K=3.               | High compared to all the OTAs                                                                   |

| CMRR                      | High                       | High                                        | Low compared to  Folded cascode due to transconductance of M3a.                   | Same as that of the RFC.                                                                        |

| Signal Swing              | Medium                     | High compared to telescopic OTA.            | High compared to telescopic OTA.                                                  | High compared to telescopic OTA.                                                                |

| Slew Rate                 | High                       | Same as that of the telescopic OTA.         | High compared to Folded cascode OTA.                                              | High compared to RFC OTA.                                                                       |

# 3.6 Application of the OTAs

The OTA is the main block of any system design. The power consumption of the system depends on the power consumed by the OTA. So for low power application the OTA power should be reduced.

The different applications Of the OTA are

- 1. Buffer, Integrator, etc.

- 2. Comparators

- 3. High Performance Analog to Digital Converters

- 4. OTA-C Filters

- 5. Switched Capacitor Filters

# **Chapter 4**

#### 4.1 G<sub>m</sub>/I<sub>D</sub> methodology

#### 4.1.1 Introduction

With the advent of advanced fabrication process the transistor dimensions have reduced drastically. Although the trend towards miniaturization has helped digital circuitry with densely packed transistors, the analog counterpart had to pay the price with decreasing supply voltage headroom, reduced dynamic range, lower gain and similar other attributes.

As a consequence the conventional long-channel equations employed in the analog design were no longer producing desired results. The short channel-noise combined with the need for precise and intuitive design procedure called for a complete characterization of the process technology. A methodology is devised where currents are fixed to arrive at the transistor dimensions to satisfy specifications like gain-bandwidth, low power, area, etc. The  $g_m/I_D$  is a ratio obtained by complete characterization of the process for the NMOS and PMOS transistors.

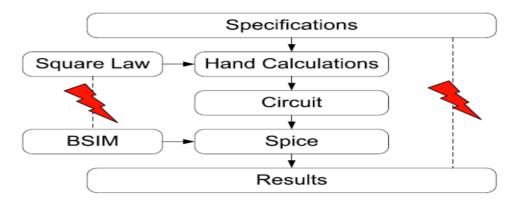

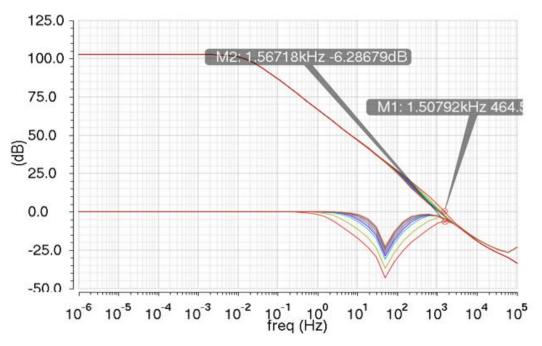

For a given set of design specifications, we may start our design by using MOSFET square law equation. However the modern device models given by BSIM model, or any other models are too complicated for hand analysis. There is a huge discrepancy between modern CMOS models and traditional equations. All these pose a challenge for a modern circuit designer, as shown in Fig.4.1.

Fig. 4.1 The Problem while designing

The lack of good hand analysis models to design circuits forcing many designers to give up hand calculation /analysis, and iterate the design problem in simulators to meet the specifications. So design should be based on systematic design analysis and reasonable considerations, the simulator is just a calculator to check the design meet the specifications or not. From a designers point of view we should understand the optimizations to be done for proper operation of the circuit and not a pile of equations which does not give any design intuition.

#### 4.2.2 Different regions of Operation

The long-channel design has different set of equations which govern each region of operation. The overdrive voltage  $V_{ov}$  is a key parameter which defines the region the device is operating in. The  $g_m/I_D$  characterizes the performance of a transistor in all regions of operation. The following section develops the long-channel equations of the transistor. From these equations we derive the figures of merits for the  $g_m/I_D$  method.

Triode region

$$I_{D} = \mu_{n} C_{ox} \frac{w}{l} \left[ \left( V_{gs} - V_{T} \right) - \frac{V_{DS}}{2} \right] . V_{DS}$$

(4.1)

Saturation region

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{w}{l} \left[ \left( V_{gs} - V_T \right)^2 \right]$$

(4.2)

Transconductance

$$g_m = \frac{\partial I_D}{\partial V_{GS}} = \mu C_{ox} \frac{W}{L} (V_{GS} - V_T) = \mu C_{ox} \frac{W}{L} V_{OV}$$

(4.3)

$$g_m = \sqrt{2I_D \mu_n C_{ox} \frac{W}{L}} = \frac{2I_D}{V_{ov}}$$

$$\tag{4.4}$$

Output conductance with channel length modulation

$$g_{ds} = \frac{\partial I_D}{\partial V_{DS}} = \frac{\partial}{\partial V_{DS}} \left[ \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \right]$$

(4.5)

$$g_{DS} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_T)^2 \lambda = \frac{\lambda I_D}{1 + \lambda V_{DS}} = \lambda I_D$$

(4.6)

The performance of any analog circuit can be broadly divided into its large signal and small signal characteristics. The current  $I_D$  determines the power dissipation; voltage  $V_{DS}$  and available swing (both the ICMR and ODR); the transconductance  $g_m$  signifies speed and voltage gain; the intrinsic impedances  $C_{GS}$ ,  $C_{GD}$ ,  $C_{DB}$  determine the speed and the output impedance;  $r_0$  the voltage gain of the circuit. Summarizing above we have

D.C. Voltage Gain

$$A_{DC} = g_m * r_0 \tag{4.7}$$

Bandwidth

$$f_{transit} = \frac{1}{2\pi R_{in} C_{GG}} \tag{4.8}$$

**Power Dissipation**

$$P = V_{DD} * I_D \tag{4.9}$$

Figure of Merits

Some figure of merits can be defined for the technology characterization in the  $g_m/I_D$  - based method.

Transconductance Efficiency

$$\frac{g_m}{I_D} = \frac{2}{V_{ov}} \tag{4.10}$$

**Transit Frequency**

$$\frac{g_m}{C_{GG}} = \frac{3\mu V_{ov}}{2L^2} \tag{4.11}$$

Intrinsic Gain

$$\frac{g_m}{g_{ds}} = \frac{2}{\lambda V_{ov}} \tag{4.12}$$

The equations in the right hand side are derived from the square law equations. In saturation there are three regions of operation depending upon the effective voltages applied across the gate of the transistor.

Weak Inversion

$$vgs - v_t < -0.72 (4.13)$$

**Moderate Inversion**

$$-0.72 < vgs - v_t < 0.25 \tag{4.14}$$

**Strong Inversion**

$$vgs - v_t > 0.25 \tag{4.15}$$

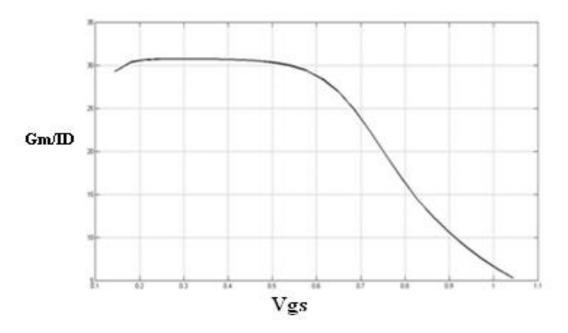

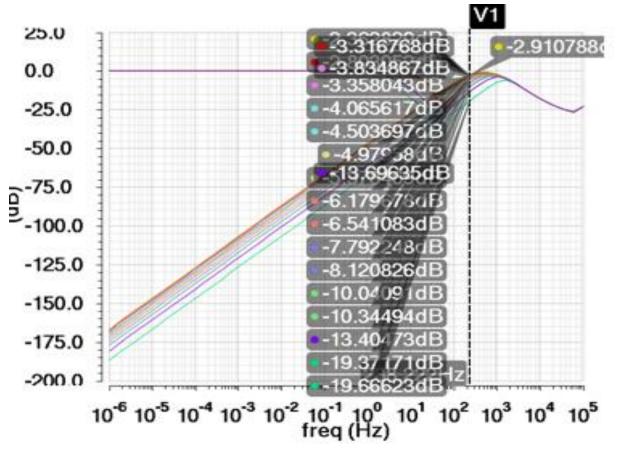

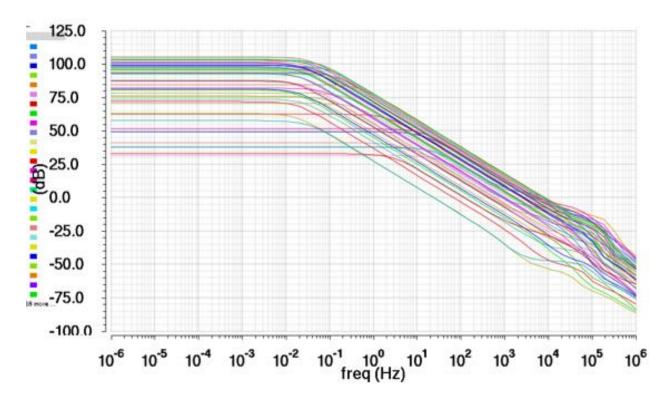

The  $g_m/I_D$  Vs V<sub>gs</sub> curve for NMOS in different regions of operation using 90nm CMOS technology is shown below.

Fig. 4.2 G<sub>m</sub>/I<sub>D</sub> vs Vgs plot

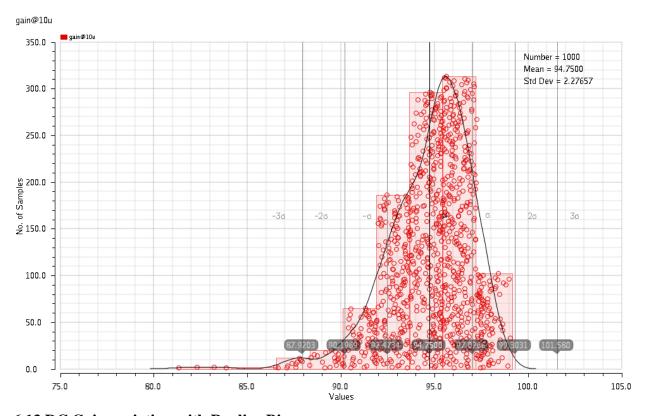

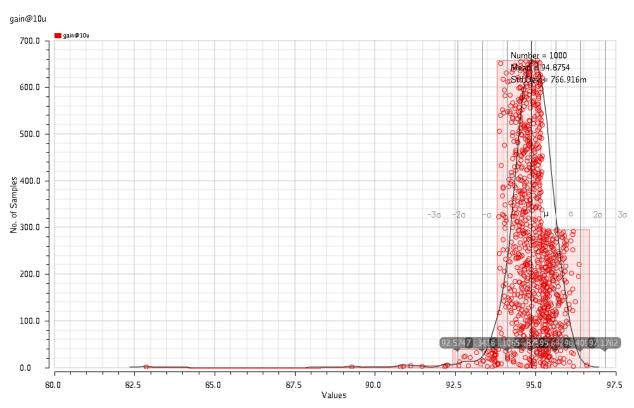

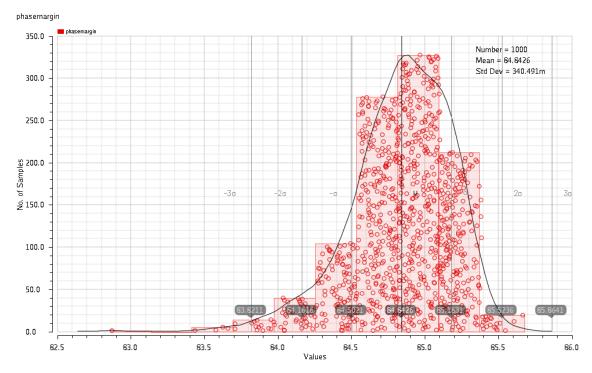

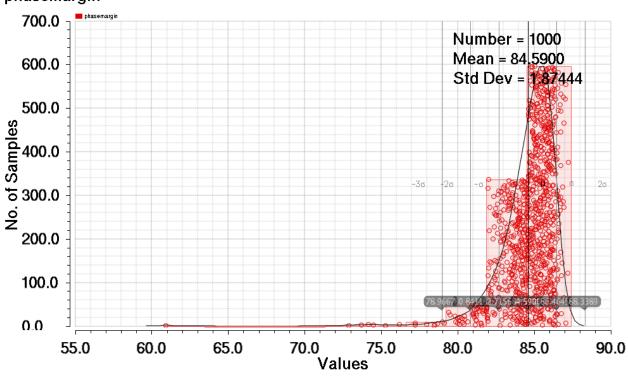

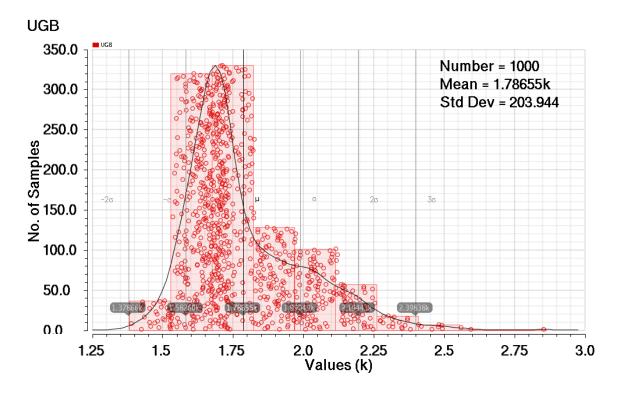

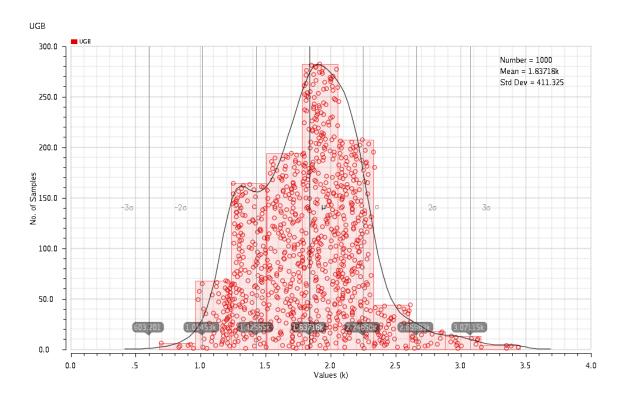

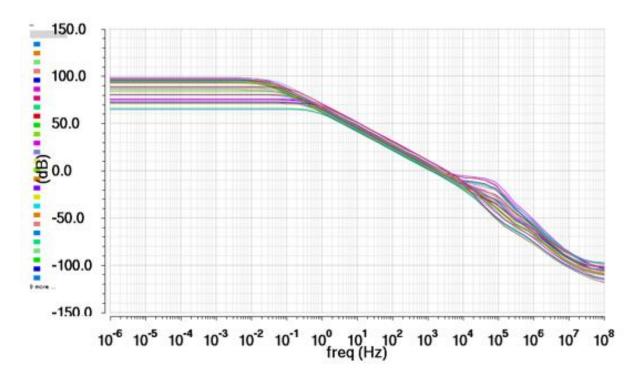

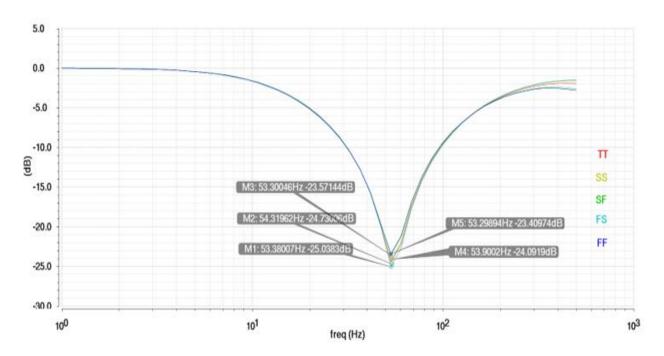

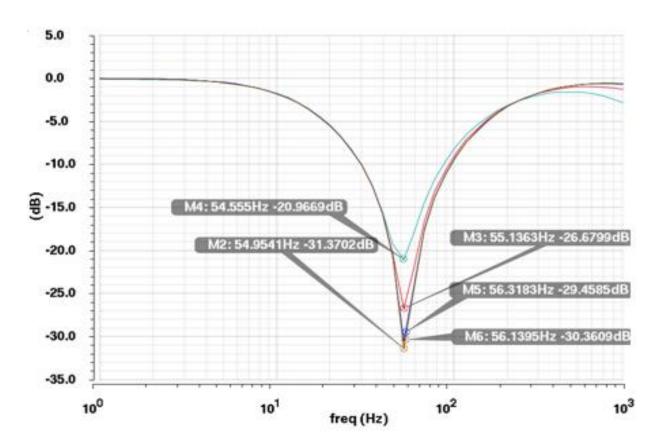

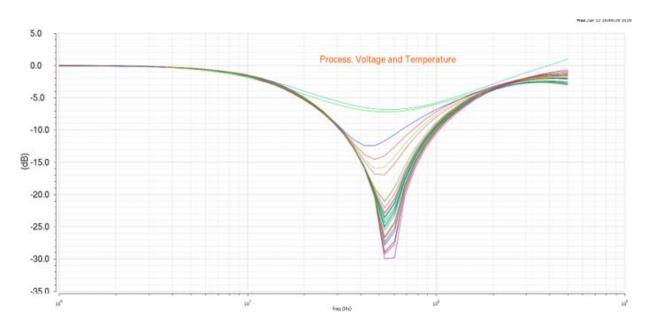

#### 4.2.3 Weak Inversion