Technical University of Denmark

## Reconguration of Computation and Communication Resources in Multi-Core Real-Time Embedded Systems

Pezzarossa, Luca

Publication date: 2018

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Pezzarossa, L. (2018). Reconguration of Computation and Communication Resources in Multi-Core Real-Time Embedded Systems. DTU Compute. (DTU Compute PHD-2018, Vol. 469).

#### DTU Library Technical Information Center of Denmark

**General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Reconfiguration of Computation and Communication Resources in Multi-Core Real-Time Embedded Systems

Luca Pezzarossa

Kongens Lyngby 2018 PhD-2018-469

Technical University of Denmark Department of Applied Mathematics and Computer Science Richard Petersens Plads, Building 324, 2800 Kongens Lyngby, Denmark Phone +45 4525 3351 compute@compute.dtu.dk www.compute.dtu.dk PhD-2018-469

# Abstract (English)

Reconfigurable computing allows application programmers to significantly increase the speed of software algorithms by implementing computationallydemanding tasks in hardware while maintaining a certain degree of flexibility. This can be achieved by using FPGAs to implement hardware accelerators that can be reconfigured when no longer needed, enabling the re-use of the resources of the FPGAs to realise new functionalities. For multi-core platforms, reconfiguration can be extended to the infrastructure supporting inter-core communication and used to dynamically modify the characteristics of the communication channels between the tasks that are affected by the reconfiguration.

This thesis investigates the use of reconfiguration in the context of multi-core realtime systems targeting embedded applications. We address the reconfiguration of both the computation and the communication resources of a multi-core platform. Our approach is to associate reconfiguration with operational mode changes where the system, during normal operation, changes a subset of the executing tasks to adapt its behaviour to new conditions. Reconfiguration is therefore used during a mode change to modify the real-time guaranteed services provided by the hardware platform to fit the requirements of the current mode.

The reconfiguration of the computation resources consists of altering the hardware implementation of selected resources, such as accelerators, and it is achieved by using the dynamic partial reconfiguration feature offered by FPGAs. With regards to this, we also present a lightweight reconfiguration controller, named RT-ICAP, specially developed to support time-predictable dynamic partial reconfiguration. The reconfiguration of the communication resources consists of setting up and tearing down the end-to-end channels offered by the communication fabric between the cores of the platform. To support this, we present a new network-onchip architecture, named Argo 2, that allows instantaneous and time-predictable reconfiguration of the communication channels. Our reconfiguration-capable architecture is prototyped using the existing time-predictable multi-processor platform T-CREST. The thesis also presents low-level reconfiguration time analysis for these architectures.

The evaluation of the proposed approach and the developed architectures is carried out using synthetic benchmarks and hardware accelerators generated by high-level synthesis tools. For the reconfiguration of computation resources, the results show that the use of accelerators in combination with dynamic partial reconfiguration leads to better utilisation of the FPGA resources and tighter worst-case execution time bounds than a pure software solution. Moreover, the results show that using a reconfigurable solution delivers a worst-case performance comparable with that of a non-reconfigurable solution. For the reconfiguration of communication resources, the results show that the worst-case reconfiguration time ranges from hundreds to thousands of clock cycles, making our solution considerably faster than other functionally equivalent networks-on-chips.

In addition to the evaluation based on synthetic benchmarks, we also present a proof-of-concept case study based on a multi-core audio digital signal-processing application that combines reconfiguration of both the computation and communication resources. The case study shows that the presented approaches for reconfiguration can be effectively used in a real-world application and can lead to a reduction of the overall hardware size and better use of the platform resources while maintaining comparable computation performance with respect to a non-reconfigurable approach.

# Resumé (Dansk)

Re-konfigurerbar hardware gør det muligt for applikationsudviklere at øge hastigheden af softwarealgoritmer betydeligt ved at implementere beregningsmæssigt krævende opgaver i hardware, samtidig med at der opretholdes en vis grad af fleksibilitet. Dette kan opnås ved at bruge FPGA'er til at implementere acceleratorer, der kan re-konfigureres når de ikke længere er nødvendige, hvilket gør det muligt at genbruge FPGA'ernes ressourcer til at realisere ny funktionalitet. For multikerne platforme kan re-konfigurationen udvides til den infrastruktur der understøtter kommunikation imellem kernerne, og bruges til dynamisk at ændre karakteristika for kommunikationskanalerne mellem de opgaver der berøres af re-konfigurationen.

Denne afhandling undersøger brugen af re-konfiguration i forbindelse med realtids systemer med flere kerner rettet mod indlejrede applikationer. Vi undersøger rekonfiguration af både beregnings- og kommunikationsressourcer på en multikerne platform. Vores tilgang er at bruge re-konfiguration sammen med ændring af driftstilstanden, hvor systemet under normal drift ændrer en delmængde af de eksekverende processer for at tilpasse sin funktion til nye forhold. Rekonfiguration anvendes derfor i forbindelse med en tilstandsændring for at tilpasse de realtidsgaranterede ydelser der leveres af hardwareplatformen til den aktuelle tilstand.

Re-konfigurationen af beregningsressourcerne består i at ændre hardware implementeringen af udvalgte ressourcer, såsom acceleratorer. Dette opnås ved at bruge den delvise re-konfigurationsfunktion der tilbydes af FPGA'er. Til udførelse af dette præsenterer vi en minimal konfigurationskontroller betegnet RT-ICAP, der er specielt udviklet til at understøtte realtidsforudsigelig delvis re-konfiguration. Re-konfigurationen af kommunikationsressourcerne består i at nedlægge og oprette kanal endepunkterne der tilbydes af kommunikationsnettet mellem platformens kerner. For at understøtte dette præsenterer vi en ny netværk-på-chip arkitektur betegnet Argo 2, som tillader øjeblikkelig og tidsforudsigelig re-konfiguration af kommunikationskanalerne. Vores rekonfigurationsfunktionelle arkitektur er udviklet og testet på den tidsforudsigelige multikerne platform T-CREST. Afhandlingen præsenterer også hardware nær tidsanalyse af re-konfigurationerne for disse arkitekturer.

Evalueringen af den foreslåede tilgang og de udviklede arkitekturer udføres ved hjælp af syntetiske benchmarks og hardware acceleratorer, der genereres af højniveaus synteseværktøjer. For re-konfigurationen af beregningsressourcerne viser resultaterne, at brugen af hardwareacceleratorer i kombination med delvis re-konfigurering fører til bedre udnyttelse af FPGA-ressourcerne og mindre udsving af tidsbegrænsningerne end en software-baseret løsning. Endvidere viser resultaterne, at ved anvendelse af en re-konfigurerbar løsning opnås en worst-case præstation tilsvarende en statisk løsning. For re-konfigurationen af kommunikationsressourcer viser resultaterne, at den værste re-konfigurationstid varierer fra hundrede til tusindvis af klokkecykler, hvilket gør vores løsning betydeligt hurtigere end andre funktionelt tilsvarende netværk-på-chips.

Udover evalueringen baseret på syntetiske benchmarks præsenterer vi også et proof-of-concept casestudy baseret på en multikerne applikation som behandler digitale lydsignaler, der kombinerer re-konfigurering af både beregnings- og kommunikationsressourcerne. Casestudy viser, at de præsenterede strategier til re-konfiguration kan anvendes effektivt i en reel applikation og kan føre til en reduktion af den samlede hardwarestørrelse, samtidig med at man opretholder en beregningsydelse tilsvarende en statisk platform.

### Preface

The work presented in this thesis was conducted at the Department of Applied Mathematics and Computer Science at the Technical University of Denmark (DTU Compute) in fulfilment of the requirements of the PhD program.

The work was supervised by Professor Jens Sparsø and co-supervised by Associate Professor Martin Schoeberl. The thesis explores the use of reconfiguration of computation and communication resources in multi-core real-time embedded systems. The thesis is a monograph and consists of eight chapters.

The thesis does not contain any material that has been accepted for the award of any other degree or diploma in my name, in any university or other institution and, to the best of my knowledge, does not contain any material previously published by another person, except where due reference is made in the thesis.

Kongens Lyngby, 15-March-2018

Luce Jezzarosse

Luca Pezzarossa

vi

## Acknowledgements

At first, I would like to thank my supervisor Professor Jens Sparsø and my co-supervisor Associate Professor Martin Schoeberl for guiding, supporting, and helping me throughout my PhD.

I would also like to thank all the members of the section for Embedded Systems Engineering at the Technical University of Denmark. Especially the PhD colleagues and the MSc and BSc students with whom I collaborated or shared part of the last three years: Evangelia, Rasmus, Wolfgang, Daniel, Andreas, Tórur, Oktay, Eleftherios, and all the others.

Special thanks go to Ioannis, who shared with me times of enthusiasm and discouragement, helped me every time I needed, and proofread this thesis.

Finally, I would like to thank my family, Mauro, Daniela and Marco who, even though they are far away, have always supported me in everything.

viii

### Contents

| A        | bstra | ct (Er  | nglish)                      |   | i            |

|----------|-------|---------|------------------------------|---|--------------|

| R        | esum  | é (Da   | nsk)                         |   | iii          |

| P        | refac | е       |                              |   | $\mathbf{v}$ |

| A        | cknov | wledge  | ements                       |   | vii          |

| Li       | st of | Acror   | ıyms                         | х | iii          |

| Li       | st of | Publi   | cations                      | : | xv           |

| 1        | Intr  | oduct   | ion                          |   | 1            |

|          | 1.1   | Resea   | rch Field and Motivation     |   | 1            |

|          | 1.2   | Thesis  | S Overview                   |   | 4            |

|          | 1.3   | List of | f Contributions              |   | 5            |

|          | 1.4   | Source  | e Access                     |   | 6            |

|          | 1.5   | Thesis  | s Structure and Outline      | • | 6            |

| <b>2</b> | Bac   | kgrou   | nd                           |   | 9            |

|          | 2.1   | Recon   | figurable Computing          |   | 9            |

|          |       | 2.1.1   | Overview                     |   | 10           |

|          |       | 2.1.2   | Evolution and Technology     |   | 10           |

|          |       | 2.1.3   | High-Level Synthesis         |   | 12           |

|          | 2.2   | Dynai   | mic Partial Reconfiguration  |   | 13           |

|          |       | 2.2.1   | Overview                     |   | 13           |

|          |       | 2.2.2   | ICAP Interface               |   | 14           |

|          |       | 2.2.3   | Design Flow and Requirements |   | 17           |

|          | 2.3   | Real-7  | Γime Systems                 |   | 18           |

|          |     | 2.3.1 Overview and Classification                     | 19 |

|----------|-----|-------------------------------------------------------|----|

|          |     | 2.3.2 Timing-Analysis                                 | 20 |

|          | 2.4 | The T-CREST Platform                                  | 22 |

|          |     | 2.4.1 Overview                                        | 22 |

|          |     | 2.4.2 Patmos Processor                                | 22 |

|          |     | 2.4.3 Support Tools                                   | 24 |

|          |     | 2.4.4 Memory Access NoC                               | 25 |

|          | 2.5 | Argo Message-Passing NoC                              | 26 |

|          |     | 2.5.1 Overview                                        | 26 |

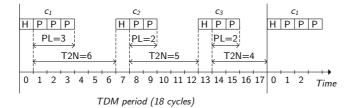

|          |     | 2.5.2 TDM-Schedule                                    | 27 |

|          |     | 2.5.3 NoC Architecture                                | 28 |

| 3        | Rel | ated Work                                             | 33 |

|          | 3.1 | Reconfiguration of Computation Resources              | 33 |

|          |     | 3.1.1 Methods and Tools                               | 34 |

|          |     | 3.1.2 Reconfiguration Controllers                     | 36 |

|          | 3.2 | Reconfiguration of Communication Resources            | 38 |

|          |     | 3.2.1 NoCs Based on Flow Control                      | 39 |

|          |     | 3.2.2 NoCs Based on TDM                               | 40 |

|          | 3.3 | Other Related Topics                                  | 42 |

| <b>4</b> | Ар  | proach to Reconfiguration                             | 45 |

|          | 4.1 | Definition of Communication and Computation Resources | 45 |

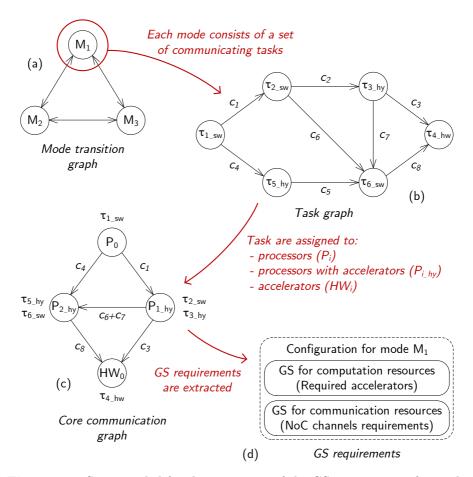

|          | 4.2 | Reconfiguration at Mode Changes                       | 46 |

|          | 4.3 | Extraction of Guaranteed Service Requirements         | 48 |

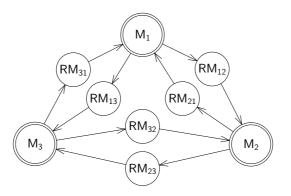

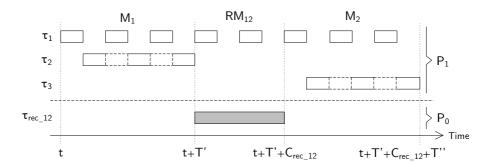

|          | 4.4 | Model of the Reconfiguration Process                  | 50 |

|          | 4.5 | Expected Outcomes and Evaluation Metrics              | 51 |

| <b>5</b> | Rec | configuration of Computation Resources                | 55 |

|          | 5.1 | A Multi-Core Platform Supporting DPR                  | 55 |

|          | 5.2 | RT-ICAP Controller Architecture                       | 57 |

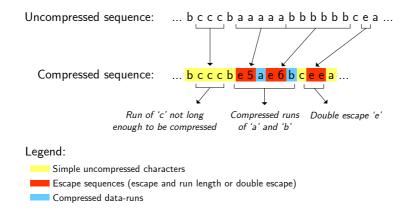

|          | 5.3 | Bit-Stream Compression                                | 61 |

|          | 5.4 | Tool Support                                          | 63 |

|          | 5.5 | Reconfiguration Time Analysis                         | 64 |

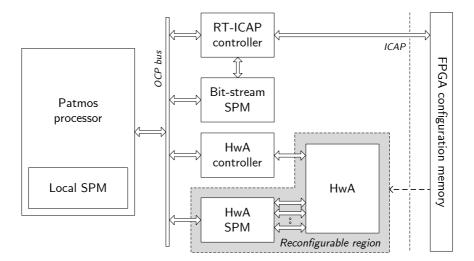

|          | 5.6 | Single-Core Application Example                       | 66 |

| 6        | Rec | configuration of Communication Resources              | 69 |

|          | 6.1 | Overview                                              | 69 |

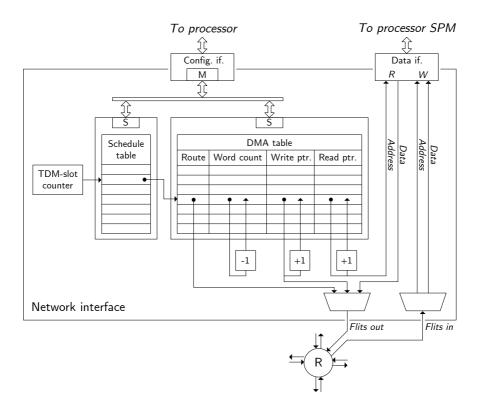

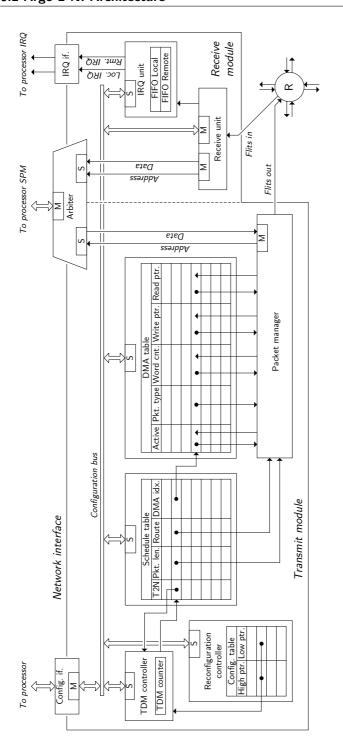

|          | 6.2 | Argo 2 NI Architecture                                | 70 |

|          |     | 6.2.1 Packet Format and Schedule Representation       | 70 |

|          |     | 6.2.2 Transmit Module                                 | 72 |

|          |     | 6.2.3 Receive Module                                  | 74 |

|          |     | 6.2.4 Remote Initialization                           | 75 |

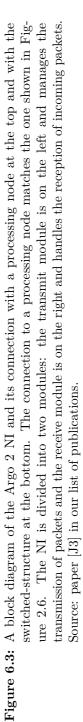

|          | 6.3 | Support for Reconfiguration                           | 76 |

|          |     |                                                       |    |

|    |       | 6.3.1 l  | Key Ideas and Observations                      | 76  |

|----|-------|----------|-------------------------------------------------|-----|

|    |       |          | Reconfiguration Process                         |     |

|    | 6.4   |          | guration Time Analysis                          |     |

| 7  | Eval  | luation  | and Discussion                                  | 81  |

|    | 7.1   | Reconfig | guration of Computation Resources               | 81  |

|    |       | 7.1.1 I  | RT-ICAP Controller Characterization             | 82  |

|    |       | 7.1.2 l  | Bit-Stream Compression and Reconfiguration Time | 84  |

|    |       |          | Synthetic Benchmarks Experiments                |     |

|    | 7.2   |          | guration of Communication Resources             |     |

|    |       |          | Argo 2 Characterization                         |     |

|    |       |          | Synthetic Traffic Experiments                   |     |

|    | 7.3   |          | SP Application                                  |     |

|    |       |          | Overview                                        |     |

|    |       |          | Hardware Platform                               |     |

|    |       |          | Effects and Modes of Operation                  |     |

|    |       |          | Observations and Results                        |     |

| 8  | Con   | clusion  |                                                 | 117 |

|    | 8.1   | Summar   | ry and Final Remarks                            | 117 |

|    | 8.2   |          | Work                                            |     |

| Bi | bliog | raphy    |                                                 | 123 |

## List of Acronyms

| ADC                        | Analog-to-Digital Converter             |

|----------------------------|-----------------------------------------|

| ASIC                       | Application-Specific Integrated Circuit |

| BCET                       | Best Case Execution Time                |

| BRAM                       | Block RAM                               |

| $\mathbf{CC}$              | Clock Cycle                             |

| $\mathbf{CPU}$             | Central Processing Unit                 |

| $\mathbf{D}$ \$            | Data Cache                              |

| DAC                        | Digital-to-Analog Converter             |

| $\mathbf{DMA}$             | Direct Memory Access                    |

| $\mathbf{DPR}$             | Dynamic Partial Reconfiguration         |

| $\mathbf{DSP}$             | Digital Signal Processing               |

| $\mathbf{eFPGA}$           | embedded Field Programmable Gate Array  |

| $\mathbf{FF}$              | Flip-Flop                               |

| FIFO                       | First In First Out                      |

| $\mathbf{FIR}$             | Finite Impulse Response                 |

| FPGA                       | Field Programmable Gate Array           |

| $\mathbf{FSM}$             | Finite-State Machine                    |

| $\mathbf{GS}$              | Guaranteed Service                      |

| HDL                        | Hardware Description Language           |

| HLS                        | High-Level Synthesis                    |

| $\mathbf{HPU}$             | Header Parsing Unit                     |

| $\mathbf{HwA}$             | Hardware Accelerator                    |

| ICAP                       | Internal Configuration Access Port      |

| $I^2C$                     | Inter-Integrated Circuit                |

| $\mathbf{I}^{2}\mathbf{S}$ | Inter-Integrated circuit Sound          |

| I/O                        | Input/Output                            |

|                            |                                         |

| $\mathbf{IRQ}$ | Interrupt (ReQuest)              |

|----------------|----------------------------------|

| $\mathbf{LUT}$ | Look-Up Table                    |

| $\mathbf{M}$   | Method Cache                     |

| NI             | Network Interface                |

| NoC            | Network-on-Chip                  |

| OCP            | Open Core Protocol               |

| $\mathbf{PL}$  | Packet Length                    |

| RAM            | Random-Access Memory             |

| RISC           | Reduced Instruction Set Computer |

| RLE            | Run-Length Encoding              |

| S\$            | Stack Cache                      |

| SDRAM          | Synchronous Dynamic RAM          |

| SoC            | Systems-on-Chip                  |

| SPM            | Scratch-Pad Memory               |

| T2N            | Time-to-Next                     |

| TDM            | Time-Division Multiplexing       |

| TTA            | Time-Triggered Architecture      |

| VC             | Virtual Circuit                  |

| WCET           | Worst-Case Execution Time        |

| XML            | eXtensible Markup Language       |

|                |                                  |

## List of Publications

#### **Journal Publications**

- [J1] L. Pezzarossa, A. T. Kristensen, M. Schoeberl, and J. Sparsø. Using Dynamic Partial Reconfiguration of FPGAs in Real-Time Systems. Accepted for publication in *Microprocessors and Microsystems: Embedded Hardware Design*, Elsevier, 2018.

- [J2] M. Schoeberl, <u>L. Pezzarossa</u>, and J. Sparsø. A Multicore Processor for Time-Critical Applications. In *Journal of Design and Test*, volume PP, number 99, pages 1–1, IEEE, 2017.

- [J3] R. B. Sørensen, <u>L. Pezzarossa</u>, M. Schoeberl, and J. Sparsø. A resourceefficient network interface supporting low latency reconfiguration of virtual circuits in time-division multiplexing networks-on-chip. In *Journal of Systems Architecture*, volume 74, pages 1–13, Elsevier, 2017.

#### **Conference Publications**

- [C1] <u>L. Pezzarossa</u>, A. T. Kristensen, M. Schoeberl, and J. Sparsø. Can Real-Time Systems Benefit from Dynamic Partial Reconfiguration? In *Proceed*ings of the 3<sup>rd</sup> Nordic Circuits and Systems Conference (NorCAS). IEEE, 2017.

- [C2] A. T. Kristensen, <u>L. Pezzarossa</u>, and J. Sparsø. High-Level Synthesis for Reduction of WCET in Real-Time Systems. In *Proceedings of the* 3<sup>rd</sup> Nordic Circuits and Systems Conference (NorCAS). IEEE, 2017.

- [C3] D. S. Ausin, <u>L. Pezzarossa</u>, and M. Schoeberl. Real-time audio processing on the T-CREST multicore platform. In *Proceedings of the 11<sup>th</sup> International Symposium on Embedded Multicore/Many-core Systems-on-Chip* (MCSoC). IEEE, 2017.

- [C4] <u>L. Pezzarossa</u>, M. Schoeberl, and J. Sparsø. A Controller for Dynamic Partial Reconfiguration in FPGA-Based Real-Time Systems. In *Proceedings* of the 20<sup>th</sup> International Symposium on Real-Time Computing (ISORC). IEEE, 2017.

- [C5] R. B. Sørensen, <u>L. Pezzarossa</u>, M. Schoeberl, and J. Sparsø. An Area-Efficient TDM NoC Supporting Reconfiguration for Mode Changes. In *Proceedings of the 10<sup>th</sup> International Symposium on Networks-on-Chip* (NOCS). IEEE/ACM, 2016.

- [C6] <u>L. Pezzarossa</u>, M. Schoeberl, and J. Sparsø. Reconfiguration in FPGA-Based Multi-Core Platforms for Hard Real-Time Applications. In *Proceed*ings of the 11<sup>th</sup> International Symposium on Reconfigurable Communicationcentric Systems-on-Chip (ReCoSoC). IEEE, 2016.

- [C7] <u>L. Pezzarossa</u>, R. B. Sørensen, M. Schoeberl, and J. Sparsø. Interfacing Hardware Accelerators to a Time-Division Multiplexing Network-on-Chip. In *Proceedings of the 1<sup>st</sup> Nordic Circuits and Systems Conference (NOR-CAS)*. IEEE, 2015.

#### **Other Works**

- [O1] <u>L. Pezzarossa</u>. Dynamic Reconfiguration in Multi-Core Hard Real-Time Platforms. Abstract and poster presented at the 12<sup>th</sup> International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES). HiPEAC, 2016.

- [O2] <u>L. Pezzarossa</u>, M. Schoeberl, and J. Sparsø. Towards Utilizing Reconfigurable Shared Resources in Multi-Core Hard Real-Time Systems Nonpublishing article presented at the 9<sup>th</sup> Junior Researcher Workshop on Real-Time Computing (JRWRTC). 2015.

- [O3] <u>L. Pezzarossa</u>. Dynamic Partial Reconfiguration in the T-CREST Multicore Platform. Abstract and poster presented at the 11<sup>th</sup> International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES). HiPEAC, 2015.

### Chapter 1

### Introduction

This thesis explores the challenges and the potential benefits of reconfigurable computing in the context of multi-core real-time systems targeting embedded applications.

This chapter introduces the research work presented in this thesis. At first, we describe the research fields to which this study relates to, and we present the motivation and hypotheses of this work. This is followed by an overview of the thesis content and by the list of contributions. Finally, we provide the information regarding the access to the source code associated with this work and present the structure and outline of the thesis.

#### 1.1 Research Field and Motivation

In recent years, we have observed a transition from single-core towards multi-core architectures, as well as an increased use of specialised hardware accelerators optimised for specific tasks [1]. Moreover, packet switched networks-on-chip (NoCs) are increasingly used in large multi-core chips to support communication between the cores and between cores and shared memory, instead of standard bus architectures [2, 3]. This shift was possible by evolution in chip fabrication

technology and further driven by increasing market demand for high computational capabilities, higher levels of integration, and low power consumption. Examples of commercially-available multi-core platforms targeting embedded systems include LEON4 by Gaislerflex/ESA [4], MPPA-256 by Kalray [5], and Epiphany by Adapteva [6, 7].

Even more recently, advancements in field programmable gate array (FPGA) technology have enabled reconfigurable computing to become viable and be used in end-products. The combination of FPGA technology and reconfigurable computing empowers application developers to design and use their own hardware accelerators to significantly increase the speed of software algorithms by utilising reconfigurable hardware [8]. The major FPGA vendors are beginning to produce hybrid systems-on-chip (SoC) combining a hard processor with a reconfigurable fabric, such as the Xilinx Zyng SoC [9], the Microsemi SmartFusion2 SoC [10], and the Intel Stratix 10, Arria V and 10, and Cyclone V SoC [11]. Other vendors offer FPGA intellectual property cores to embed into an application-specific integrated circuit (ASIC) design in order to increase the flexibility, differentiation, and market lifespan of a chip. These intellectual property cores are known as embedded-FPGA (eFPGA). Commercially-available solutions are provided by Menta-eFPGA [12] and Achronix [13]. In addition, most currently available FPGA devices allow portions of the chip to be reconfigured at run-time, while the rest of the device continues to operate without interruption [14, 15, 16]. This feature, called dynamic partial reconfiguration (DPR), is an active area of research for general-purpose reconfigurable computing.

The use of FPGAs, eFPGAs, and hybrid SoCs to enable a reconfiguration-oriented approach in the design of computing systems can lead to an increase in flexibility, performance, and more efficient utilisation of chip resources compared to a static solution. From an economic point of view, the non-recurring engineering costs of an ASIC implementation makes this technology prohibitively expensive for those applications in which these costs cannot be amortised over a very large production volume. Low volume professional or high-end real-time applications, such as control systems, medical devices, and flight electronics belong in this category. For these applications, reconfigurable computing in the form of FPGAs, eFPGAs, and hybrid SoCs can mitigate the production costs.

This thesis combines the presented research fields and aims to explore the use of reconfigurable computing in multi-core real-time systems. Real-time systems are a class of computing systems characterised by strict constraints on the execution time of tasks [17, 18]. Therefore, the temporal behaviour of a hardware platform supporting real-time applications must be predictable and analysable. Specifically, the possibility to calculate the worst-case execution time (WCET) of tasks is of fundamental importance. Hence, the entire system must be designed taking into account the specifications of time-predictability and time-analysability [19].

The real-time industry is typically rather conservative towards new architectures and approaches since these systems are often used in safety-critical applications where a failure to respond in time may lead to severe consequences. Nevertheless, the use of multi-core architectures and reconfigurable computing in real-time systems are active topics of research [20, 21].

In a multi-core platform which supports real-time applications, the requirement for time-predictable behaviour goes beyond the individual processors. The entire platform must offer guaranteed services in terms of computation resources (e.g., processors and hardware accelerators) and communication resources (e.g., network-on-chip supporting communication among tasks mapped to different cores). The T-CREST platform [21] is an example of an FPGA-based multi-core platform targeting real-time systems. All components are designed with a focus on time-predictability and WCET analysis aiming to reduce the complexity and pessimism of the analysis. The platform consists of a number of processing nodes [22] and two NoCs: a NoC, called Argo [23], that provides message-passing to support inter-processor communication and a NoC that provides shared memory access [24, 25]. T-CREST is used in this research as a prototyping platform for the proposed solutions supporting reconfiguration in multi-core real-time systems.

In general, reconfigurable computing is used to increase the performance of a system by dynamically starting and stopping tasks executed on the dedicated hardware resources implemented on a reconfigurable fabric [8]. However, when taking into account multi-core platforms for real-time applications, the reconfiguration can be extended to the infrastructure supporting inter-processor communication. Reconfiguration may be used to dynamically set up, tear down, and modify the communication channels between the tasks that are reconfigurable As our research targets multi-core real-time systems, we explore reconfigurable computing from both the computation and communication perspectives.

We hypothesise that the use of a hardware platform supporting reconfiguration of both computation and communication resources can provide substantial benefits by allowing run-time changes in the platform. More specifically, a system that uses a reconfigurable approach can be more efficient, flexible, and smaller in terms of hardware size compared to the equivalent static version, while maintaining comparable computational performance. We also hypothesise that the combination of hardware acceleration and reconfiguration can result in both lower and tighter bounds on the WCET since, in general, hardware has a simpler and more time-predictable behaviour than software executing on a processor. These hypotheses are further detailed in the thesis into a set of expected outcomes and evaluation metrics for our reconfiguration approach.

#### 1.2 Thesis Overview

This thesis investigates the use of run-time reconfiguration in the context of multicore real-time embedded systems. Such a run-time reconfiguration relates to both communication resources and computation resources of a multi-core platform. The main idea is to dynamically adapt the hardware platform to the actual needs of the software applications running on it. The reconfiguration of computation resources is achieved using the DPR feature of FPGAs for swapping between a set of hardware accelerators. The reconfiguration of communication resources is achieved by dynamically altering the bandwidth and latency guarantees of the communication channels offered by the inter-processor message-passing NoC. Since this research targets real-time systems, the time-predictability specification must also apply to the reconfiguration techniques.

Our approach is to associate reconfiguration with operational mode changes where the system, during normal operation, changes a subset of the executing software tasks to adapt its behaviour to new environmental conditions. Since different modes of a real-time application can have different requirements for the guaranteed services offered by the platform, run-time reconfiguration is used to modify the platform to meet the requirements of the current mode. This may lead to a reduction of hardware cost compared to a static solution where the hardware platform must meet the overall requirements of all the modes of the application. Moreover, the possibility to move functionality into hardware may increase the performance of the entire system in terms of speed and WCET compared to a pure software solution.

In addition to exploring the reconfiguration from a real-time perspective, we develop a hardware/software infrastructure to support the reconfiguration of the computation and communication resources targeting the existing time-predictable multi-processor platform T-CREST. For the reconfiguration of computation resources in T-CREST, we develop a hardware controller and software tools that enable time-predictable reconfiguration of the hardware accelerators using the DPR feature offered by Xilinx FPGAs. For the reconfiguration of the communication resources, we develop a new version of the T-CREST message passing NoC allowing instantaneous reconfiguration between different sets of virtual circuits without affecting those that persist across the reconfiguration.

The reconfiguration of the communication and computation resources are evaluated and discussed both independently and in conjunction. The independent evaluation of the reconfiguration of the computation resources is carried out using synthetic benchmarks and hardware accelerators implemented using high-level synthesis tools. Synthetic traffic benchmarks are also used for the independent evaluation of the reconfiguration of the communication resources. Finally, a proof-of-concept case study that includes reconfiguration of both the computation and communication resource features is carried out using an audio digital signal processing (DSP) application.

#### **1.3** List of Contributions

The main contributions of this thesis concern the proposed approach to reconfiguration and the hardware/software infrastructure we develop to support it. The following list summarises the features of these contributions.

- We present an approach for using reconfigurable computing in real-time multi-core embedded systems where the reconfiguration of computation and communication resources is associated with operational mode changes. This approach is analysed, especially focusing on the effects on the time predictability of the system. Particular attention is given to the extraction of the requirements for the guaranteed-services provided by the platform and to the role of reconfiguration into ensuring that these requirements are met for a multi-mode application.

- We explore and evaluate how to use the DPR feature of modern FPGAs to support the computation aspects of a mode change by dynamically reconfiguring the computation resources in the platform. More specifically, we present a hardware architecture of a lightweight time-predictable reconfiguration controller, named RT-ICAP, and the associated software tool that supports the controller. A reconfiguration time analysis for the reconfiguration controller is also presented.

- We supplement the message-passing NoC of the T-CREST platform with run-time reconfiguration, thereby supporting the reconfiguration of the communication resources. More specifically, we develop a new NoC architecture, named Argo 2, that supports instantaneous reconfiguration of end-to-end communication channels. An analysis of the reconfiguration effects on the time-predictability of the multi-core platform is also presented.

- We provide an extensive evaluation of the use of reconfiguration in realtime systems using synthetic benchmarks and a multi-core DSP audio application, aiming to confirm the thesis hypotheses.

- We significantly extend the T-CREST project by supplementing the existing time-predictable multi-core platform with reconfiguration capabilities for both hardware resources and the message-passing NoC.

#### **1.4 Source Access**

The entire software and hardware infrastructure developed in relation to the work presented in this thesis and the T-CREST multi-core platform are released under the terms of the simplified BSD open-source license. The full T-CREST platform and the source code related to this thesis are available at https://github.com/t-crest/, which is a collection of git repositories. The hardware source code related to the configuration of computation and communication resources can be found in the reconfig and in the argo repositories, respectively. The software source code can be found in the C folder of the patmos repository. The hardware and software source code related to the audio DSP application case study is available in the branch reconfig-audio of the patmos and aegean repositories. README files describing the file structure and the build instructions are also included in the repositories.

#### 1.5 Thesis Structure and Outline

The thesis begins by presenting general background and a review of related work. Next, we present an overview of our reconfiguration approach followed by the implementation details of the hardware and software infrastructure we developed in relation to the proposed approach. Finally, we provide results and evaluate the proposed approach and architecture. The discussion is integrated with the evaluation. The following list of chapters provides a more detailed outline.

- Chapter 2 introduces the background for the topics related to the thesis, including reconfigurable computing, the DPR feature of FPGAs, real-time systems, the T-CREST multi-core platform, and the Argo message-passing NoC.

- Chapter 3 reviews related work covering two research areas: reconfiguration of computation resources and reconfiguration of communication resources.

- Chapter 4 presents our approach to reconfiguration by introducing a clear definition of computation and communication resources as well as the relationship between operational mode changes, guaranteed service requirements, and reconfiguration.

- Chapter 5 presents the hardware and software infrastructure we developed to support the reconfiguration of computation resources according to the proposed approach. More specifically, it presents the RT-ICAP controller

and the associated software tool we developed to enable time-predictable reconfiguration of the hardware accelerators using DPR.

- Chapter 6 describes the new version of the T-CREST message-passing NoC, called Argo 2, that we developed to support the reconfiguration of communication resources focusing on its reconfigurable features which allows instantaneous reconfiguration between different sets of virtual circuits.

- Chapter 7 evaluates and discusses our proposed reconfiguration approach through reviews of the developed infrastructure supporting DPR and the Argo 2 NoC as well as a proof-of-concept audio DSP application that combines the reconfiguration of both computation and communication resources.

- Finally, Chapter 8 concludes the thesis by summarising the contributions and the results, and by presenting future work.

### Chapter 2

### Background

This chapter provides the background for the main topics related to the thesis, including reconfigurable computing, the DPR feature of FPGAs, real-time systems, the T-CREST multi-core platform, and the Argo message-passing NoC. The background on each of the topics is presented independently to one another and aims to supply the reader with the knowledge needed from the perspective of this work. For additional background information, references to academic literature and technical reports are provided at the beginning of each section.

#### 2.1 Reconfigurable Computing

The main focus of this work is reconfiguration. In this section, we provide background related to reconfigurable computing and overview its evolution and challenges. An extensive review of the state-of-the-art of reconfigurable computing can be found in [8].

#### 2.1.1 Overview

Computing systems are typically implemented using two solutions. The first consists of employing a general-purpose processor to run software that realises the required functionality. This solution is very flexible since the same processor can be reprogrammed to implement multiple functionalities. However, the sequential nature of program execution, combined with the fact that the program must be compiled into a limited set of general-purpose instructions, may limit the efficiency and the performance. The second solution consists of using an ASIC chip that realises the required functionality directly in hardware. This is more efficient and has higher performance than the software-based solution since the hardware can be designed to match the required functionality and to exploit parallelism. However, ASICs lack flexibility, since the implemented functionality cannot be changed. Moreover, the design process of an ASIC is complex and time-consuming, and, thus, very expensive.

Reconfigurable computing is an approach that aims to combine the flexibility of software with the high performance of hardware. This is achieved by using reconfigurable fabrics, such as FPGAs, to implement computationally-demanding tasks in hardware. The hardware can be reconfigured when it is no longer needed allowing the re-use of resources of the reconfigurable fabric to realise new functionalities. The key advantage over a software-based solution is the ability to modify the hardware architecture to offer more complex, high-level instructions, as far as implementing entire tasks in hardware. The main advantages over an ASIC-based solution are the increased flexibility and the easier and less time-demanding design process.

#### 2.1.2 Evolution and Technology

Reconfigurable computing was first presented in 1960 in [26], where the author proposed the concept of an architecture consisting of a fixed unit and a variable unit. The fixed unit would offer a simple interface to a user and manage the hardware implemented on the variable unit. The variable unit could be reconfigured to implement the hardware that better fit the current user application. This concept was not implemented and adopted in the 1960s due to limited technology. The invention of FPGAs in the early 1980s [27] brought new interest in reconfigurable computing from both academia and industry. Several pioneering FPGA-based designs demonstrated the potential of FPGA-based reconfigurable computing. For example, the SPLASH architecture [28] outperformed contemporary supercomputers on a DNA sequence matching problem by using a design based on 16 FPGAs.

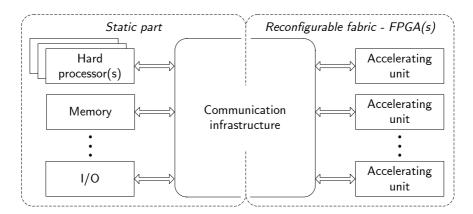

Figure 2.1: A block diagram of a reconfigurable computing system where a static (non-reconfigurable) processors-based architecture is combined with accelerating units implemented in a reconfigurable fabric. An infrastructure that extends in both the static part and the reconfigurable fabric supports the communication between all the system units.

Today, reconfigurable computing is mainly used to increase the speed of software algorithms by using hardware accelerators implemented on FPGAs. As previously mentioned, the common approach is to combine a processor-based computing architecture with reconfigurable accelerators. Figure 2.1 shows a block diagram of a possible computer architecture based on this approach. The system consists of a static (non-reconfigurable) part and a reconfigurable fabric (i.e. one or more FPGAs). The static part includes the processor-based computing system, which may consist of one or more hard processors, memory, inputs/outputs (I/Os), and possibly other peripherals. The reconfigurable fabric is used to implement acceleration units that match the current needs of an application executing on the system. A communication infrastructure supplies the communication channels between the units of the system, and it extends through both the static part and the reconfigurable fabric.

Hybrid SoCs available on the market are based on this architecture. Examples include the Xilinx Zynq SoCs [9], the Microsemi SmartFusion2 SoC [10], and the Intel Stratix 10, Arria V and 10, and Cyclone V SoCs [11]. These devices contain a single- or multi-core ARM processor together with an FPGA. In contrast, architectures incorporating one or more discrete FPGAs with one or more discrete hard processors also exist. For example, Microsoft Azure servers combine Intel FPGAs and processors to create a cloud that can be reconfigured to optimise a diverse set of applications and functions [29, 30]. The reconfiguration capabilities offered by the commercially-available FPGA and hybrid-SoC devices

are further extended by the DPR feature, which enables the reconfiguration of a portion of the FPGA, while the rest of the device continues to operate without interruption [14, 15, 16]. This feature is extensively used in this work to reconfigure computation resources. Thus, a detailed background related to DPR is presented in Section 2.2.

In a reconfigurable system such as the one presented in Figure 2.1, a set of tasks are executed by the hard processors, and another set of tasks are executed on the dedicated hardware resources implemented on the reconfigurable fabric. The communication between these two sets is supported by the communication infrastructure. The idea of reconfiguration, which generally refers to the reconfiguration of the computation resources, can also be applied to the infrastructure that implements the communication among the tasks. In this case, reconfiguration can be used to dynamically modify the characterising parameters (e.g., bandwidth, latency, and transmission policies) of the communication resources. In Section 3.2, we review the related work regarding reconfiguration of NoC-based communication infrastructures.

#### 2.1.3 High-Level Synthesis

To accelerate algorithms on the reconfigurable fabric, application developers must have access to hardware implementations of the desired functionalities. The design of these accelerators can be performed manually or with the help of automated tools, such as high-level synthesis (HLS) tools. HLS is an automated design process that translates a software program into a functionally equivalent hardware architecture expressed in a hardware description language (HDL). Xilinx provides the Vivado HLS [31] tool, which can translate C and SystemC code into a register-transfer level implementation in VHDL or Verilog. An equivalent open-source tool developed in academia is LegUp [32]. A complete survey of available HLS tools is provided in [33].

HLS tools take the source code as input along with a set of constraints and directives provided by the designer defining design specifications for clock frequency, resources utilisation, and performance. First, the source code is analysed and the basic operations to be mapped into the available hardware components are identified. Next, a control flow graph is constructed, and the operations are scheduled, which means assigning the operations to control steps (i.e. to clock cycles). During this process, the operations are assigned to the hardware components aiming to exploit parallelism to the extent allowed by the user constraints on the resource utilisation as well as by data dependencies. A finite-state machine is then generated to orchestrate the execution of the operations according to the identified schedule. In general, HLS-generated accelerators perform worse than manually implemented ones [34]. However, the speed-up over a pure software implementation is still acceptable taking into account the reduction in time and effort for the development process. In our research, we use the Vivado HLS tools to generate hardware accelerators from C benchmarks for evaluation purposes.

#### 2.2 Dynamic Partial Reconfiguration

The reconfiguration approach presented in the thesis uses the DPR feature of FPGAs to reconfigure the hardware resources dedicated to accelerating computational tasks. In this section, we provide the background information regarding DPR for Xilinx FPGAs. Further background can be found in [14, 15].

#### 2.2.1 Overview

DPR is a feature of modern FPGAs that allows for dynamic change of hardware modules of an operating FPGA. After the initial configuration of the FPGA with a full-bit-stream, partial bit-streams can be loaded to reconfigure the hardware design implemented in selected regions without compromising the integrity and the functionality of those parts of the device that are not affected by the reconfiguration.

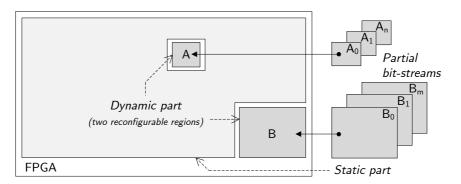

A system using DPR can be conceptually considered as divided into static and dynamic parts. The static part is configured only once at boot-time with a full bit-stream. The dynamic part, which may consist of several independent reconfigurable regions, can be reconfigured multiple times during run-time with different partial bit-files. Figure 2.2 shows an example of an FPGA divided into static and dynamic parts. The dynamic part consists of two reconfigurable regions (A and B). For each region, a partial bit-stream can be loaded from a set to change the hardware implemented in the selected region without interfering with the functionality of the hardware implemented in the static part or in the other reconfigurable regions. For example, in Figure 2.2, the hardware architecture implemented in the reconfigurable region A is modified by loading one of the partial bit-streams  $A_0, A_1, ..., A_n$ .

In reconfigurable computing, DPR can be used to increase the flexibility in the choices of algorithms available to an application. Moreover, it can lead to a reduction of the size of the FPGA with a consequent reduction in cost and power consumption, since it allows the re-use of FPGA resources to implement

Figure 2.2: An example of an FPGA divided into a static part and a dynamic part. The dynamic part consists the two reconfigurable regions A and B. Partial bit-streams can be loaded to reconfigure these regions.

different functionalities. Various approaches may be used when employing DPR in a reconfigurable system. If the entire computing system is implemented on the FPGA, then the static part of the FPGA is used to implement the processing resources that need to run uninterrupted for the entire execution time of an application, such as processors, on-chip communication fabric, and on-chip memory. The dynamic part of the FPGA is shared between hardware accelerators, specialised co-processors, I/O peripherals, etc. that are only needed for a limited period. Alternatively, if the hardware architecture of a computing system is a hybrid SoC or an ASIC equipped with an eFPGA, then the static part of the FPGA is used to implement only the communication fabric between the hard processor (or ASIC logic) and the dynamic part of the system. In this work, we address the class where the entire computing system is implemented on the FPGA.

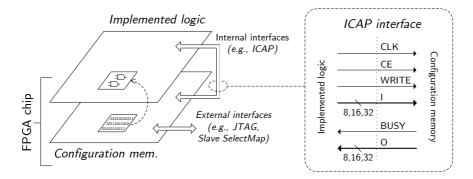

#### 2.2.2 ICAP Interface

From a functional point-of-view, an FPGA can be modelled as a two-layered device, as shown in Figure 2.3. The top layer consists of the configurable logic components and interconnections available to implement the user design. The configuration bit-streams are stored in an SRAM configuration memory in the bottom layer. Depending on the content of the configuration memory, the logic functions implemented by the components and their interconnection are modified to construct the desired digital circuit. In other words, the content of the configuration memory defines the hardware design implemented in the

Figure 2.3: An FPGA chip modelled as two layers: one is the configuration memory, and the other is the configurable logic components and interconnections. The external and internal interfaces allow the access to the configuration memory. The ICAP interface is expanded to show the internal signals.

FPGA. In Figure 2.3, the dashed arrow between the two FPGA layers shows this dependency.

Technically, performing a partial reconfiguration consists of changing the content of selected segments of the configuration memory, which corresponds to the modification of the hardware design implemented in the respective regions of logic. The smallest reconfigurable region is called base region, and it corresponds to the smallest addressable segment, called frame, of the FPGA configuration memory space. The size of a frame depends on the FPGA model. For example, in the Xilinx Virtex-6 FPGA, a frame is equivalent to 320 6-input look-up tables (LUTs) and 640 flip-flops (FFs) (80 slices), or 16 DSP elements, or 8 blocks of RAM (BRAMs).

For Xilinx FPGAs, DPR can be performed by loading a partial bit-stream at run-time through one of the FPGA configuration interfaces [35, 36], which can be either off-chip or on-chip as shown in Figure 2.3. The off-chip interfaces are accessible externally from the FPGA chip through dedicated pins. Commonly available off-chip interfaces are JTAG and Slave SelectMAP. The on-chip interfaces are accessible by the user logic implemented on the FPGA itself. In this work, we use the on-chip internal configuration access port (ICAP) on-chip interface. The ICAP is a hardware primitive that provides read/write access to the FPGA configuration memory.

In Figure 2.3, the ICAP interface is expanded to show the internal signals. The naming of some signals of the ICAP interface changes between FPGA families; however, the functionality remains unchanged (Figure 2.3 uses Virtex-6 naming).

| Reconf.      | Hardware resources |       |     | Bit-stream | Reconf.     |                        |

|--------------|--------------------|-------|-----|------------|-------------|------------------------|

| region       | FF                 | LUT   | DSP | BRAM       | size (Byte) | time                   |

| Base region  | 640                | 320   | 0   | 0          | 5832        | $\sim 16\mu{ m s}$     |

| Patmos proc. | 20480              | 10240 | 64  | 32         | 611712      | $\sim\!1.5\mathrm{ms}$ |

| Large region | 102720             | 51360 | 256 | 140        | 3074112     | $\sim\!7.6\mathrm{ms}$ |

Table 2.1: Bit-stream size and calculated reconfiguration time for three different reconfigurable region sizes for a Xilinx Virtex-6 FPGA.

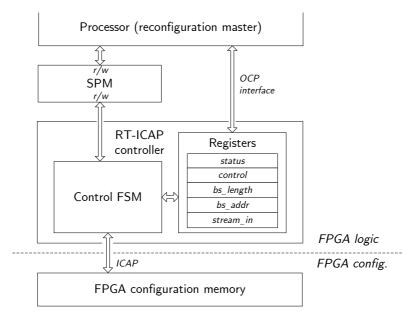

The ICAP is synchronous and has separate read (O) and write (I) buses, which can be configured to support data widths of 8, 16, or 32 bits. The ICAP is a streaming interface and, for DPR purposes, it receives a partial bit-stream as a continuous input stream through the write bus (I). As shown in Figure 2.3, the address of the FPGA configuration memory and the control signals are not directly available on the interface. All the control information needed to manage the reconfiguration, such as commands and frame address, are encoded into the bit-stream together with the data to be written to the configuration memory. In addition, the ICAP provides information about the current state of the ongoing reconfiguration and communicates when a region is successfully reconfigured through the read bus (O). The ICAP interface and the timing diagram for the signals enable (CE), read/write select (WRITE), and busy bit (BUSY) are explained in [36, 35]. A reconfiguration controller is needed to manage the bit-stream transfer through the ICAP. One of the contributions of this work is the design of a time-predictable reconfiguration controller for the ICAP as presented in Section 5.2. A review of some ICAP controllers from industry and academic environments is presented in Section 3.1.

The time to perform a DPR depends on the amount of data to be transferred over the ICAP as well as its speed. The ICAP for Virtex-5, -6, and 7-series FPGAs has a maximum operation frequency of 100 MHz. Assuming the widest possible interface (32 bits) and the fastest possible clock, a bit-stream can be written at a maximum speed of 400 MB/s. To provide an idea of the reconfiguration time for real applications, Table 2.1 reports calculated results for three different sizes of the reconfigurable region assuming the maximum ICAP transfer speed of 400 MB/s. The values shown in Table 2.1 refer to the Xilinx Virtex-6 FPGA. We expect to have similar reconfiguration times for other FPGA families. The first row reports the results for a base region size, and the second row reports the results for a Patmos processor [22], which is a medium-sized processor described in Subsection 2.4.2. The last row reports the results for a large region equivalent to one-third of the entire FPGA.

#### 2.2.3 Design Flow and Requirements

The full bit-stream associated to the static part and the partial bit-streams associated to the dynamic part of the architecture must be generated using the Xilinx tools. For the 7-series FPGAs, the tool used is Xilinx Vivado, while for older FPGAs the tools are Xilinx ISE and Xilinx PlanAhead. This introduces some differences in the design flow between the 7-series FPGAs [14] and older ones [15]. In the following, we provide a summary of the steps of the design flow, which are common for all Xilinx FPGA families.

At first, the HDL description for the static part of the design and each HDL description targeting the reconfigurable regions must be synthesised independently. The HDL descriptions targeting reconfigurable regions are called reconfigurable modules. The synthesis generates a netlist for the static part and a set of netlists for the reconfigurable modules. The synthesis also produces an estimation of the resources needed to implement each reconfigurable module. The next step is to define the number of reconfigurable regions and to assign the netlists of the reconfigurable modules to each region. This is followed by the definition of the size and the location of each region on the FPGA floor-plan. The resources included in each region should be enough to implement the largest module assigned to it. At this point, one reconfigurable module for every region must be promoted to be part of the full bit-stream for the initial configuration (if nothing should be implemented, then a blank reconfigurable module can be used). The static part is then implemented (place and route) together with the promoted reconfigurable region. Then, the rest of the reconfigurable module are implemented respecting the routing of the signals on the border between the previously implemented static part and the reconfigurable regions. Finally, the static bit-stream and the partial bit-streams are generated. If needed, design constraints for the static part and each reconfigurable module can be provided in every step of the design flow. If the differences between two configurations for the same reconfigurable region are minimal, then the Xilinx tools allow the generation of a differential bit-stream that stores only the differences between a previous configuration and the new one. In this work, we do not use differential bit-streams. Possible extensions of this work using differential bit-streams are presented as future work in Section 8.2.

The current FPGA technology and tools introduce some requirements and limitations related to the use of DPR. During the design flow, specific checking procedures are used to verify that the DPR requirements are respected. In the following, we list the most relevant requirements and limitations for the work presented in the thesis.

- During reconfiguration, the interface between the static part and a reconfigurable region may take unknown values. This may affect the functionality of the design implemented in the static part of the FPGA. Therefore, a specially designed border interface is needed between the static and dynamic parts of a design to decouple the affected reconfigurable region from the rest of the design during reconfiguration. The border interface belongs to the static part of the design and may consist of FFs with enable or 2-to-1 multiplexers on all the signals toward the static part.

- A reconfigurable region must contain a super-set of all interface signals used by the possible hardware modules assigned to the region. The unused output signals need to be forced to a constant value by the logic implemented in the reconfigurable region.

- In a design that includes multiple reconfigurable regions in the dynamic part of the system, only one region can be reconfigured at a time. Even if most FPGAs that support DPR offer two ICAP interfaces, it is still not possible to reconfigure more than one region at a time.

- The reconfigurable region must be rectangular-shaped. Moreover, it is recommended that it is a multiple of the base region. This topological constraint, combined with the fact that the base regions containing DSPs and BRAMs are uniformly distributed in the FPGA chip layout, may lead to an over-inclusion of resources into a reconfigurable area.

- From a system point-of-view, particular attention should be given to avoid deadlocks. For example, if some transactions across a reconfigurable region boundary take multiple cycles to complete, then performing DPR after a transaction has started but before it has completed could cause the system to experience deadlocks. The same could apply for some software polling a register that no longer exists.

## 2.3 Real-Time Systems

This study explores reconfiguration in real-time systems. In the following, we provide an overview of this class of systems, as well as background on timinganalysis. Further background on real-time systems can be found in [17, 18]. An extensive overview of the methods and a survey of timing-analysis tools can be found in [19].

### 2.3.1 Overview and Classification

Real-time systems are a class of computing systems characterised by strict constraints on the execution time of tasks in addition to the correctness of the produced result. This definition introduces a set of design specifications on both the software and hardware aspects of a computing system. From a software perspective, this translates to the application of a programming policy that avoids unpredictable or non-analysable behaviours of software tasks (e.g., unbounded loops) and to the use of techniques that guarantee that deadlines are met when multiple tasks share a common resource (e.g., scheduling protocols). From a hardware perspective, the main specification is time predictability of the hardware architecture of a platform targeting real-time applications, which must be developed in a way that allows and simplifies the analysis of the time behaviour of the system.

Real-time systems are commonly used for those applications where a failure to respond in time may lead to undesirable consequences. Depending on the severity of these consequences with respect to the ability to respond in time, real-time systems can be classified into the following three categories:

- Hard real-time: Failure to respond in time is not permitted since it can lead to catastrophic consequences, such as loss of life, severe injury, or significant economic loss. Common hard real-time application examples include flight, train, and automotive control systems, medical devices, and industrial control systems.

- Firm real-time: Failure to respond in time is allowed within certain limits. If a deadline is missed, then the produced result cannot be used but does not cause excessive problems. A firm real-time application example can be found in assembly and production lines where a sporadic production error can be tolerated.

- Soft real-time: Failure to respond in time is allowed within certain limits. If a deadline is missed, then the produced result can still be used. However, this may lead to a degradation of the computing performance of the system. Common soft real-time application examples are audio/video signal processing, quality-of-service management in packet-switched networks, and gaming engines.

In this study, we provide solutions that can satisfy the specification of predictability of hard real-time systems. For this reason, the proposed solutions can also find application in soft and firm real-time systems.

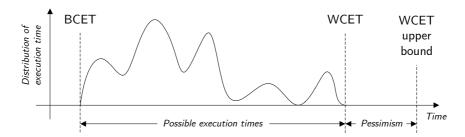

Figure 2.4: Example of a distribution of execution times of a software task. The minimum possible execution time is the BCET, and the maximum is the WCET. The timing-analysis produces an upper bound for the WCET.

#### 2.3.2 Timing-Analysis

In the general case, a real-time application consists of a set of software tasks delivering the required functionality. Typically, the execution time of a task shows a variation that depends on the input data or different operating environments. Figure 2.4 shows an example of a distribution of execution times for a task and defines related terminology. The WCET of a software task is the maximum time interval that a task may take to execute on a specific hardware platform. The minimum interval is called best-case execution time (BCET).

In real-time systems, it is the WCET of the tasks that determines the system performance and its ability to respond in time. For realistic applications, it is impossible to determine the exact WCET of a task, since the space of execution times is too large to be exhaustively explored. Timing-analysis is used to calculate or estimate a safe upper bound of the WCET. The difference between the calculated safe upper bound and the real WCET is called pessimism, as shown in Figure 2.4. The pessimism should be as low as possible and small enough to be acceptable to the system designer.

The WCET of software tasks is dependent on the code structure, data inputs, and targeted hardware architecture. There are two classes of methods used for timing-analysis: measurement-based methods and static methods. In the measurement-based methods, the entire task code or a segment of it is executed on the target hardware or on simulators for a predetermined set of inputs from which the execution time is measured. If the set of inputs coincides with all possible inputs or if the set of inputs that trigger the WCET is known, then this method provides precise WCET results. In real cases, the level of complexity of the tasks to be analysed does not allow for testing all possible inputs, or the set of inputs that trigger the WCET is not known. In these cases, the measurement can be performed using a subset of all possible input. However, this can only produce an estimate of the WCET and not a safe upper bound. This estimate, usually compensated with a safety margin, can still be used for soft and firm real-time applications.

For hard real-time applications, where only a safe upper bound for the WCET is acceptable, static methods or a combination of measurement-based methods and static methods should be used. Static methods do not rely on the execution of code on the target hardware or simulators. Instead, static methods use an abstract model of the hardware architecture and perform an analysis of the entire task code or segments of it to estimate a safe upper bound for the WCET. Static analysis tools work on source code or disassembled binary executables to extract a control flow graph that models the structure of a program. The control flow graph is then combined with annotations provided by the user (e.g., loop iterations bound and input values interval) and with low-level information regarding the hardware architecture on which the task will execute. The resulting control flow graph is therefore analysed aiming to find the longest path, which corresponds to an upper bound on the WCET of a task running on a given hardware platform. A commercial example of a timing-analysis tool is the aiT WCET Analyzer by AbsInt [37, 38]. The tool statically computes tight bounds for the WCET by directly analysing binary executables and taking cache and pipeline behaviour into account.

The extraction of low-level hardware information needed for the static analysis and the determination of tight WCET bounds can be very difficult or even infeasible for general-purpose architectures designed with the goal of improving the average-case performance. These architectures typically include advanced features such as, complex instruction pipelines, out-of-order execution, branch prediction, and caches, which can make timing-analysis very complex and, thus, increase the pessimism. For this reason, special architectures targeting real-time applications have been developed with special focus on time-predictability and reduction of the WCET and timing-analysis complexity. Examples include the CarCore processor in the multi-core platform developed by the MERASA project [20], the family of processors based on the PRET approach [39, 40], and the T-CREST multi-core platform [21]. The latter is used in this work as a prototyping platform and is presented in Section 2.4.

A possible approach to implement dependable real-time systems is to use a timetriggered architecture (TTA) [41]. This approach is based on the assumption that all the component of a system (e.g., the processing cores of a multi-core platform) share a common knowledge of time. Thus, tasks can be executed according to a pre-defined schedule leading to a deterministic and analysable timingbehaviour, especially for multi-core platforms. Using common knowledge of time to synchronise task execution and a static time-division multiplexing (TDM) schedule to share in time resources between multiple users (e.g., a communication channel or a hardware accelerator) can be considered as an application of the time-triggered approach. The work presented in this thesis with regards to the reconfiguration of computation resources relies on the TDM approach to provide guarantees on the communication channels provided by the NoC.

## 2.4 The T-CREST Platform

The T-CREST multi-core platform is used as a target platform for the infrastructure we developed to support reconfiguration. In this section, we provide background on the platform and the associated timing-analysis tools. Further background can be found in [21], and technical background is available in [42].

#### 2.4.1 Overview

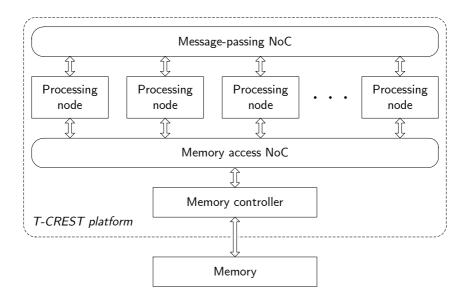

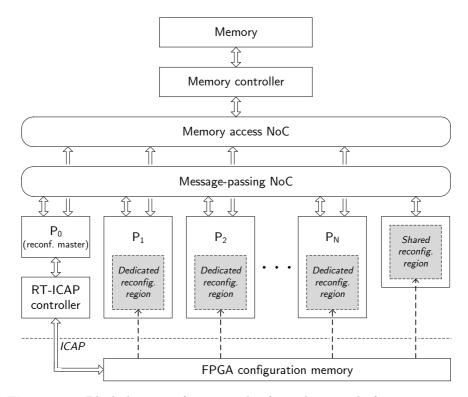

T-CREST is a multi-core platform specially developed to be used in real-time applications [21]. All components of the platform are designed with a focus on time-predictability and reducing the complexity and pessimism of the WCET analysis. Figure 2.5 shows a block diagram of T-CREST consisting of a number of processing nodes and two NoCs: one is used for traffic between cores and the shared external memory, and the other is used for message-passing traffic between the nodes. The message-passing NoC is supplemented with reconfigurable features in this work, and it is described in detail in Section 2.5. T-CREST is supported by a C compiler [43] and WCET analysis tools [37, 44], which are described in the following subsections. In this work, we use T-CREST as a bare-metal platform. Applications are run in the platform without the support of an operating system and, instead, dedicated C libraries are used to interact with low-level primitives offered by the hardware.

#### 2.4.2 Patmos Processor

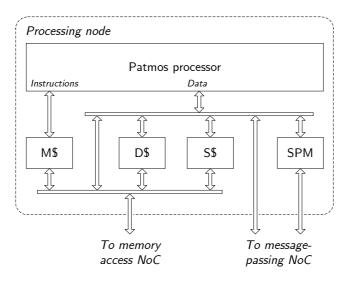

A processing node of T-CREST includes the time-predictable processor Patmos [22]. Patmos is a dual-issue, in-order, reduced instruction set computer (RISC) processor especially optimised for reducing the WCET and simplifying its analysis. For example, the architecture of the pipeline is organised in a way that avoids timing dependencies between instructions. Figure 2.6 shows a

Figure 2.5: Block diagram of the T-CREST multi-core platform.

block diagram of a processing node consisting of the Patmos processor, three different caches, and a local scratch-pad memory (SPM). The communication protocol used by Patmos for memory and I/O devices is a subset of the Open Core Protocol (OCP) [45, 42].

Patmos is equipped with specialised instruction and data caches. The method cache (M\$ in Figure 2.6) acts as an instructions cache, and it is characterised by the property of always storing entire functions (in C) [46]. In this way, it ensures that a cache miss can only happen on a function call or return. The compiler splits large functions into smaller ones to fit within the method cache. The stack cache (S\$ in Figure 2.6) stores the data stack [47]. At function entry and return, the compiler inserts additional instruction to guarantee that the stack is valid. In this way, it ensures there are not stack cache misses during a function execution. Finally, the data cache (D\$ in Figure 2.6) stores the data heap and the statically allocated data.

Patmos is also equipped with a local data SPMs. An SPM is a relatively small private memory coupled to a processor characterised by a single clock cycle access-time. The SPM can be used to store access-time sensitive data structures, and it also acts as data buffer for the message-passing NoC, as is further described in Subsection 2.5.3.

Figure 2.6: Block diagram of a T-CREST processing node and its interfaces to the two NoCs. The node contains the Patmos processor, the method (M\$), data (D\$), and stack (S\$) caches, and the local data SPM.

#### 2.4.3 Support Tools

T-CREST includes an LLVM-based C compiler [43], which supports the instructionset of Patmos and the special features associated with cache management. Moreover, it preserves the information available during the compilation process that can be valuable for an automated and precise timing analysis. This includes the control-flow structure, as well as user-flow fact annotations provided by the user (e.g., loop iterations bound). This information is used as input to the WCET analysis tools. In addition, the compiler can use the results produced by the WCET analysis tools as feedback, to further optimise compilation aiming to reduce the worst-case performance.

T-CREST is supported by the WCET analysis tool aiT [37, 38] from AbsInt and by the Portable LLVM-based Annotation and Timing-Analysis Integration tool or, in short, platin [44]. In this work, we use the platin tool to compute the WCET of a software task running on the Patmos processor. Therefore, in the following, we provide a brief description of the WCET analysis performed by platin. A detailed description can be found in [44].

The platin tool is a comprehensive framework for WCET-aware compilation and WCET analysis. Analogously to the compiler, platin offers dedicated support

for the specific architecture of Patmos (e.g., the method caching) and it allows the derivation of tight WCET bounds using static methods. This means that to estimate the WCET, platin only examines the software structure without code execution on real hardware. The tool works at both the bit-code level, which is the intermediate representation in LLVM, and at the machine code level. It uses the information generated and preserved during the compilation process to determine a control-flow graph annotated with flow facts. The control-flow graph, combined with low-level timing information of the processor architecture, is therefore analysed for the longest paths, which correspond to a safe upper bound of the WCET of the analysed code segment.

#### 2.4.4 Memory Access NoC

For code and larger data structures, external memory is used. All processors are connected by a NoC to a memory controller and then to the shared external main memory. For this NoC and memory controller, two time-predictable solutions exist: the Bluetree [24] memory NoC with the memory controller presented in [48] and the memory NoC presented in [25] with the memory controller presented in [49] supporting synchronous dynamic random-access memory (SDRAM). In this work, we use the latter solution, which is briefly described in the following.

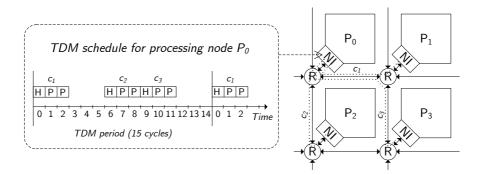

The memory access NoC is a many-to-one NoC with channels toward the memory controller and a return path for read data. Each processing core is connected to a network interface (NI) offering the same interface provided by the memory controller. The arbitration policy of the NoC is TDM-based. The NI of each core executes a common TDM schedule which reserves a time slot for each processing node. When the time slot for the core arrives, and a memory transaction is pending, the NI immediately acknowledges the transaction to the processing node. The transaction freely flows down the network tree reaching the memory controller. For read transactions, the read data is sent back to all the NIs, which filter the data targeting other cores using transaction timing information.

The TDM-based approach, combined with a memory controller that guarantees static latency for a memory transaction, allows for easy computation of the worst-case memory timing for the processing nodes. The worst-case memory timing includes the maximum waiting time for the time slot assigned to a specific node, the static time needed for a memory transaction, the latency needed by the data to travel back to the NI for read transactions, and, if needed, the time needed by the SDRAM periodic refresh. The latter can be modelled as a periodic additional time slot in the TDM-schedule.

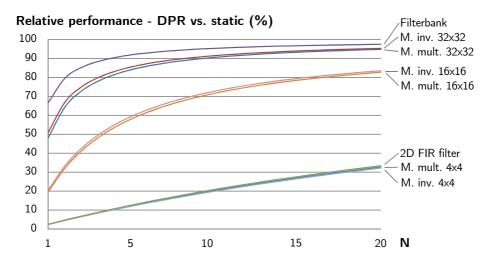

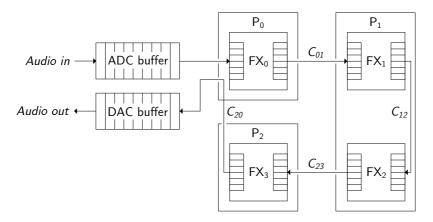

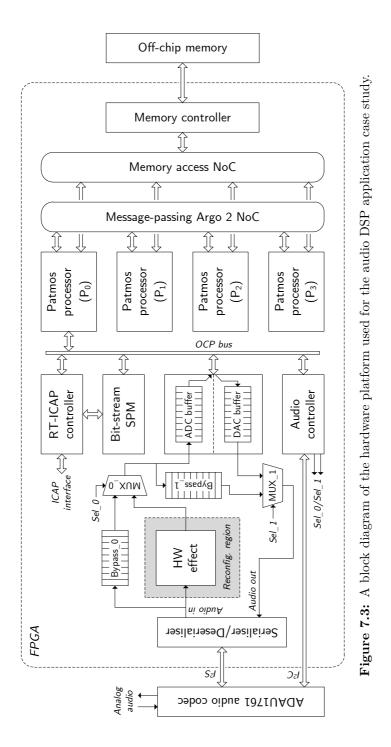

## 2.5 Argo Message-Passing NoC