# Theory, Modelling and Implementation of Graphene Field-Effect Transistor

by

Jing Tian

A thesis submitted in partial fulfilment of the requirements for the degree of

Doctor of Philosophy

School of Electronic Engineering and Computer Science Queen Mary University of London United Kingdom

I, Jing Tian, confirm that the research included within this thesis is my own work or

that where it has been carried out in collaboration with, or supported by others, that

this is duly acknowledged below and my contribution indicated. Previously published

material is also acknowledged below.

I attest that I have exercised reasonable care to ensure that the work is original,

and does not to the best of my knowledge break any UK law, infringe any third partys

copyright or other Intellectual Property Right, or contain any confidential material.

I accept that College has the right to use plagiarism detection software to check the

electronic version of the thesis.

I confirm that this thesis has not been previously submitted for a degree by this or

any other university.

The copy right of this thesis rests with the author and no quotation from it or

information derived from it may be published without the prior written consent of the

author.

Signature:

Date:

i

## Abstract

Two-dimensional materials with atomic thickness have attracted a lot of attention from researchers worldwide due to their excellent electronic and optical properties. As the silicon technology is approaching its limit, graphene with ultrahigh carrier mobility and ultralow resistivity shows the potential as channel material for novel high speed transistor beyond silicon.

This thesis summarises my Ph.D. work including the theory and modelling of graphene field-effect transistors (GFETs) as well as their potential RF applications. The introduction and review of existing graphene transistors are presented. Multiscale modelling approaches for graphene devices are also introduced. A novel analytical GFET model based on the drift-diffusion transport theory is then developed for RF/microwave circuit analysis. Since the electrons and holes have different mobility variations against the channel potential in graphene, the ambipolar GFET cannot be modelled with constant carrier mobility. A new carrier mobility function, which enables the accurate modelling of the ambipolar property of GFET, is hence developed for this purpose. The new model takes into account the carrier mobility variation against the bias voltage as well as the mobility difference between electrons and holes. It is proved to be more accurate for the DC current calculation. The model has been written in Verilog-A language and can be import into commercial software such as Keysight ADS for circuit simulation.

In addition, based on the proposed model two GFET non-Foster circuits (NFCs) are conducted. As a negative impedance element, NFCs find their applications in impedance matching of electrically small antennas and bandwidth improvement of metasurfaces. One of the NFCs studied in this thesis is based on the Linvill's technique in which a pair of identical GFETs is used while the other circuit utilises the negative resistance of a single GFET. The stability analysis of NFCs is also presented. Finally, a high impedance

surface loaded with proposed NFCs is also studied, demonstrating significant bandwidth enhancement.

## Acknowledgments

The research work presented in this thesis was carried out at Antenna & Electromagnetics Research Group, School of Electronic Engineering and Computer Science, Queen Mary University of London. The work was financially supported by Engineering and Physical Sciences Research Council (EPSRC) Grant on 'Graphene Flexible Electronics and Optoelectronics' (EP/K01711X/1), the EU Graphene Flagship (FP7-ICT-604391) and Graphene Core 1 (H2020 696656), which are gratefully acknowledged.

Foremost, I would like to express my gratitude to my supervisor Prof. Yang Hao for providing the great opportunity to work in the field of graphene active devices. His guidance and continuous support through these years have encouraged me to go through the long dissertation path. The discussions we had in the weekly meetings have been invaluable for the achievement of my study.

I would like to thank my second supervisor Dr. Khalid Z. Rajab and independent assessor Prof. Clive Parini for proofreading of my stage reports. I am grateful to Prof. Bian Wu from Xidian University, Shaanxi, China, for the guidance in the first year of my study. I would like to thank Dr. Anestis Katsounaros, Dr. Deepak Singh Nagarkoti, Dr. Luigi La Spada, Dr. Henry Giddens, Mr. Darryl Smith and Mr. Liang Yang, for the research work we did together.

I would like to thank Dr. Oleksandr, Sushko, Dr. Max Munoz Torrico, Dr. Yang Zeng, Dr. Benjamin Vial, Dr. Yangjie Liu, Mr. Shaker Alkaraki, Mr. Peter Lawrence Alizadeh, Mr. Dingliang Wen and Mr. Mingtuan Lin for the 'unbelievable' football games. I also would like to thank the rest of the antenna group for the friendly working atmosphere we created together.

Finally, I would like to thank my parents and family for their continuous support and

inspiration, which have been the main source of motivation during my Ph.D. study. I also would like to thank my daughter, who was born in China during my study. Thank you for reminding me there is always another side of life. Last but not least, I would like to express my special thanks to my wife for her unconditional love.

Jing Tian

London, July 2017

# Table of Contents

| A                 | bstra  | ct      |                                      | ij         |  |  |  |  |  |  |

|-------------------|--------|---------|--------------------------------------|------------|--|--|--|--|--|--|

| f Acknowledgments |        |         |                                      |            |  |  |  |  |  |  |

| Ta                | able ( | of Con  | itents                               | vi         |  |  |  |  |  |  |

| Li                | st of  | Figur   | es                                   | X          |  |  |  |  |  |  |

| ${f Li}$          | st of  | Table   | s xv                                 | 'ii        |  |  |  |  |  |  |

| Li                | st of  | Abbro   | eviations xvi                        | iii        |  |  |  |  |  |  |

| 1                 | Intr   | oduct   | ion                                  | 1          |  |  |  |  |  |  |

|                   | 1.1    | Graph   | nene and Two-dimensional Materials   | 1          |  |  |  |  |  |  |

|                   | 1.2    | Non-F   | Foster Circuit                       | 5          |  |  |  |  |  |  |

|                   |        | 1.2.1   | History of Non-Foster Circuit        | 6          |  |  |  |  |  |  |

|                   | 1.3    | Resea   | rch Objectives                       | 7          |  |  |  |  |  |  |

|                   | 1.4    | Thesis  | s Outline                            | 8          |  |  |  |  |  |  |

|                   | Refe   | erences |                                      | 10         |  |  |  |  |  |  |

| <b>2</b>          | Res    | earch   | on Graphene and Graphene Transistors | L <b>6</b> |  |  |  |  |  |  |

|                   | 2.1    | Prope   | erties of Graphene                   | 17         |  |  |  |  |  |  |

|                   |        | 2.1.1   | Electronic Property                  | 18         |  |  |  |  |  |  |

|                   |        | 2.1.2   | Optical Property                     | 21         |  |  |  |  |  |  |

|   |      | 2.1.3  | Other Properties                              |

|---|------|--------|-----------------------------------------------|

|   | 2.2  | Graph  | ene Preparations                              |

|   |      | 2.2.1  | Top-down Methods                              |

|   |      |        | 2.2.1.1 Mechanical Exfoliation                |

|   |      |        | 2.2.1.2 Graphite Oxide Reduction              |

|   |      |        | 2.2.1.3 Other Top-down Methods                |

|   |      | 2.2.2  | Bottom-up Methods                             |

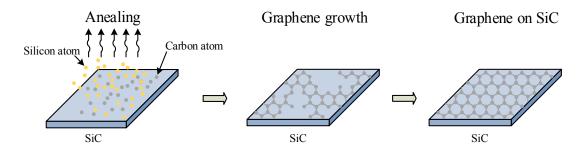

|   |      |        | 2.2.2.1 Epitaxial Growth on SiC               |

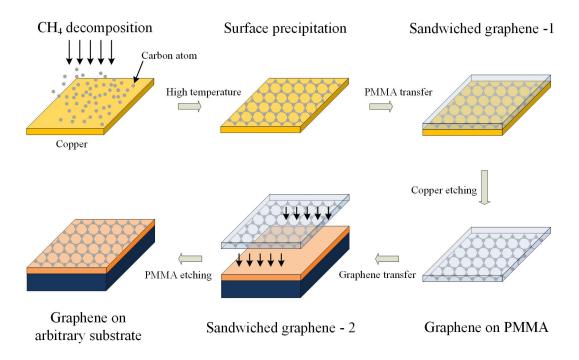

|   |      |        | 2.2.2.2 Chemical Vapour Deposition            |

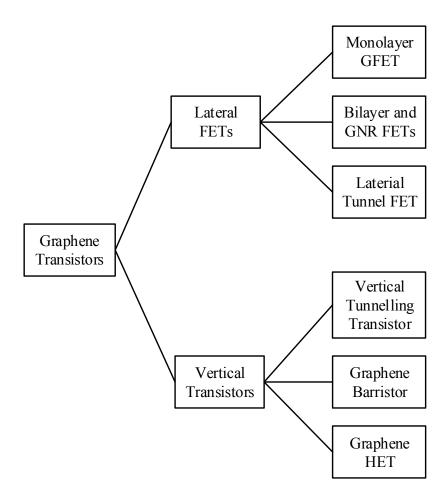

|   | 2.3  | Graph  | ene Transistors                               |

|   |      | 2.3.1  | Transistor Figures of Merit                   |

|   |      | 2.3.2  | Monolayer Graphene Field-Effect Transistor    |

|   |      | 2.3.3  | Bilayer and GNR FET                           |

|   |      | 2.3.4  | Vertical Graphene Transistors                 |

|   |      | 2.3.5  | Hot-Electron Transistor                       |

|   | 2.4  | Conclu | sion                                          |

|   | Refe | rences |                                               |

| 3 | GFI  | ЕТ Мо  | delling 63                                    |

|   | 3.1  |        | cale Modelling of Graphene Transistors        |

|   |      | 3.1.1  | <i>Ab initio</i> Modelling                    |

|   |      | 3.1.2  | Atomistic Modelling                           |

|   |      | 3.1.3  | Semiclassical Device Modelling                |

|   |      | 3.1.4  | Analytical Modelling                          |

|   | 3.2  | Deriva | tion of Analytical Closed-Form GFET Model     |

|   |      | 3.2.1  | Drift-Diffusion Transport Model of GFET       |

|   |      | 3.2.2  | Aspects of GFET Modelling                     |

|   |      |        | 3.2.2.1 Charge Density in Graphene Channel 71 |

|   |      |        | 3.2.2.2 Quantum Capacitance                   |

|   |      |        | 3.2.2.3 Effective Carrier Mobility                                    |

|---|------|--------|-----------------------------------------------------------------------|

|   |      |        | 3.2.2.4 Saturation Velocity                                           |

|   |      | 3.2.3  | Closed-Form Drain Current Expression                                  |

|   |      |        | 3.2.3.1 Electrostatics                                                |

|   |      |        | 3.2.3.2 Drain Current Calculation 89                                  |

|   | 3.3  | Proces | ss of Simulation                                                      |

|   | 3.4  | GFET   | Model Validation                                                      |

|   |      | 3.4.1  | Numerical vs. Analytical Results                                      |

|   |      | 3.4.2  | Model vs. Measurements                                                |

|   | 3.5  | Comp   | arison of GFET Models                                                 |

|   | 3.6  | Conclu | usion                                                                 |

|   | Refe | rences |                                                                       |

| 4 | Gra  | phene  | Non-Foster Circuits 105                                               |

|   | 4.1  | Graph  | nene RF Circuits Review                                               |

|   |      | 4.1.1  | Frequency Doubler and Mixer                                           |

|   |      | 4.1.2  | Amplifier                                                             |

|   |      | 4.1.3  | Oscillator and RF Receiver                                            |

|   |      | 4.1.4  | Conclusion                                                            |

|   | 4.2  | Overv  | iew of Non-Foster Circuit                                             |

|   |      | 4.2.1  | H-model of Non-Foster Circuit                                         |

|   | 4.3  | GFET   | '-based Linvill's Non-Foster Circuit                                  |

|   |      | 4.3.1  | Linvill's Non-Foster Circuit Technique                                |

|   |      | 4.3.2  | GFET Selection                                                        |

|   |      | 4.3.3  | NFC Design                                                            |

|   |      | 4.3.4  | Stability Analysis                                                    |

|   | 4.4  | NFC I  | Realisation Utilizing Negative Differential Resistance of GFET $$ 122 |

|   |      | 4.4.1  | Negative Differential Resistance of GFET                              |

|   |      | 4.4.2  | NFC Design                                                            |

|                  | 4.5  | Concl   | usion                                      | . 129 |

|------------------|------|---------|--------------------------------------------|-------|

|                  | Refe | erences |                                            | . 131 |

| 5                | Hig  | h Imp   | edance Surface Loaded with Graphene NFCs   | 135   |

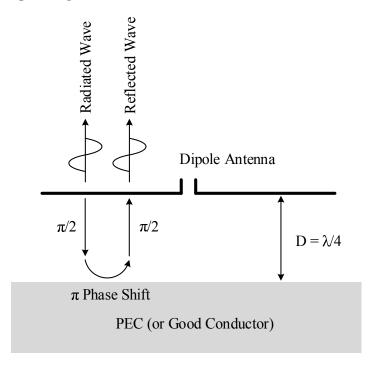

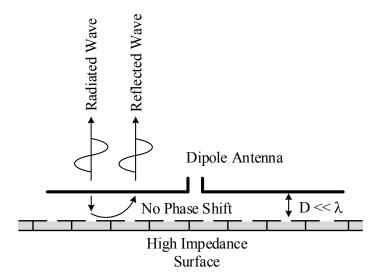

|                  | 5.1  | Conve   | entional Metallic Ground Plane for Antenna | . 135 |

|                  | 5.2  | High 1  | Impedance Surface                          | . 138 |

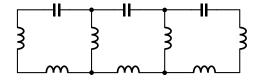

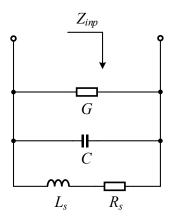

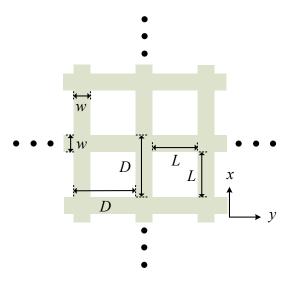

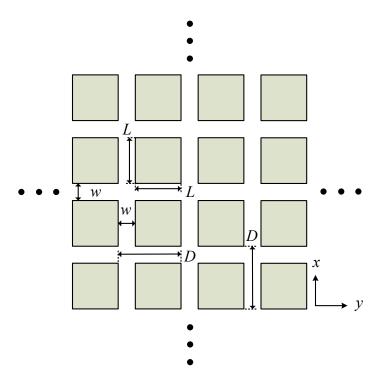

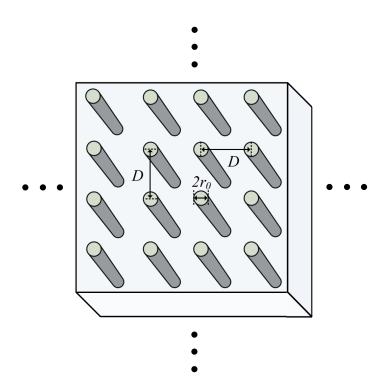

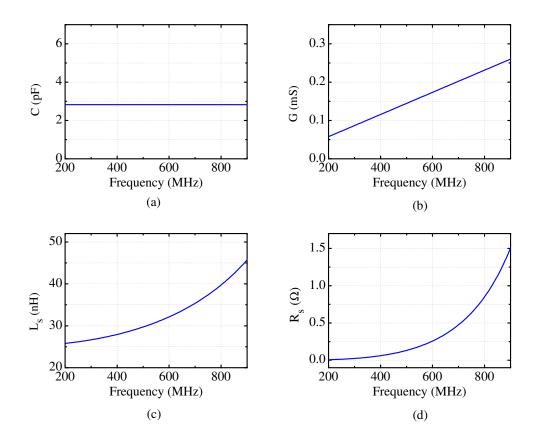

|                  | 5.3  | Effect  | ive Medium Model of HIS                    | . 140 |

|                  |      | 5.3.1   | Grid Impedance                             | . 140 |

|                  |      | 5.3.2   | Surface Impedance                          | . 144 |

|                  |      | 5.3.3   | Reflection Coefficient                     | . 147 |

|                  | 5.4  | High 1  | Impedance Surface Loaded with NFC          | . 148 |

|                  |      | 5.4.1   | Stability Characterization                 | . 151 |

|                  |      | 5.4.2   | Demonstration of Bandwidth Extension       | . 152 |

|                  |      | 5.4.3   | Conclusion                                 | . 153 |

|                  | Refe | erences |                                            | . 155 |

| 6                | Cor  | nclusio | n and Future Work                          | 158   |

|                  | 6.1  | Concl   | usion                                      | . 158 |

|                  | 6.2  | Future  | e Work                                     | . 161 |

| $\mathbf{A}_{]}$ | ppen | dix A   | List of Publications                       | 163   |

| $\mathbf{A}_{]}$ | ppen | dix B   | Analytical Expressions                     | 165   |

| A                | ppen | dix C   | Capacitance Model                          | 169   |

# List of Figures

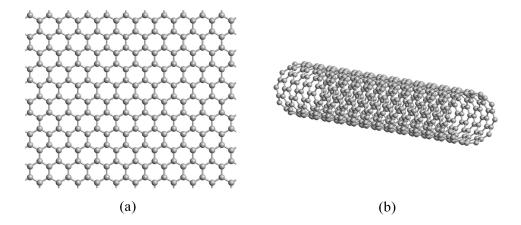

| 1.1  | Atomic structure of (a) graphene (b) single-walled carbon nanotube                     | 2  |

|------|----------------------------------------------------------------------------------------|----|

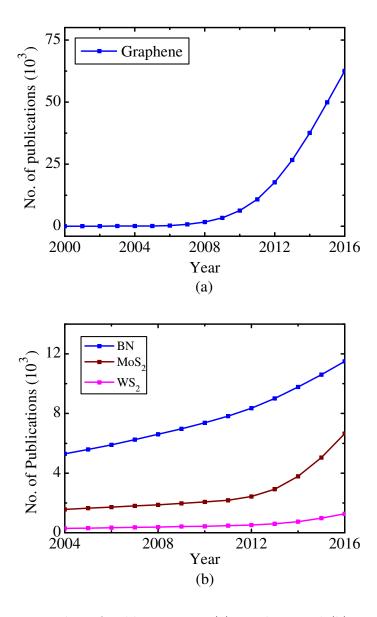

| 1.2  | Number of publications on (a) graphene and (b) BN, $MoS_2$ and $WS_2$ .                |    |

|      | Sourced from Web of Science                                                            | 3  |

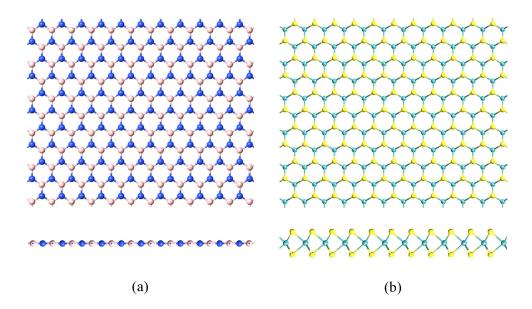

| 1.3  | Atomic structure of (a) h-BN (b) $MoS_2$                                               | 4  |

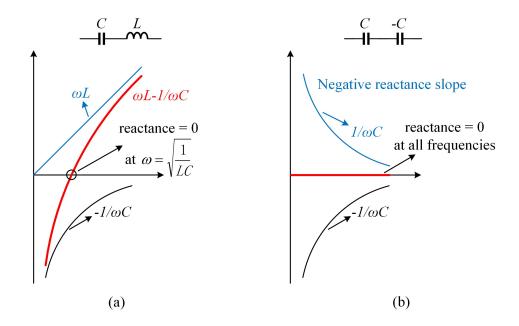

| 1.4  | Impedance matching techniques (a) passive and (b) active. $\ \ldots \ \ldots \ \ldots$ | 6  |

| 2.1  | Bandstructure of graphene calculated with Mathematica                                  | 19 |

| 2.2  | GNR with hydrogenated (a) zigzag and (b) armchair edges                                | 19 |

| 2.3  | Bandstructure of GNR with (a) zigzag and (b) armchair edges. Calculated                |    |

|      | with ATK [11]                                                                          | 20 |

| 2.4  | Bernal-stacked bilayer graphene (a) cross-sectional view and (b) top view.             | 20 |

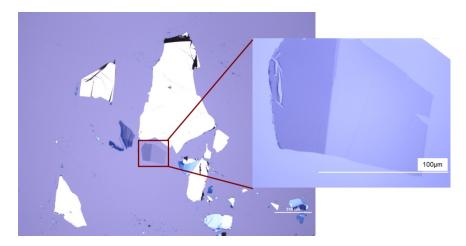

| 2.5  | Exfoliated graphene layers under optical microscope with single layer                  |    |

|      | region enlarged [37]                                                                   | 24 |

| 2.6  | Epitaxial growth of graphene on SiC                                                    | 26 |

| 2.7  | CVD growth of graphene and transferring onto arbitrary substrate                       | 28 |

| 2.8  | Classification schemes for graphene transistors                                        | 30 |

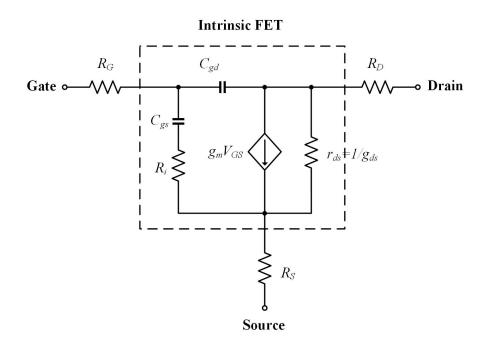

| 2.9  | Typical small signal model of a FET                                                    | 33 |

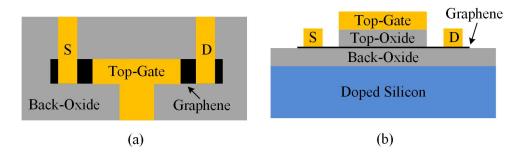

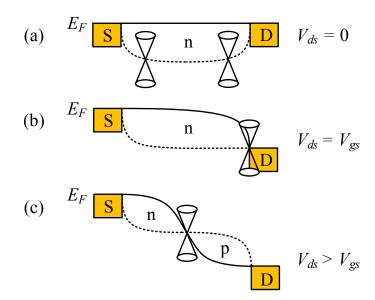

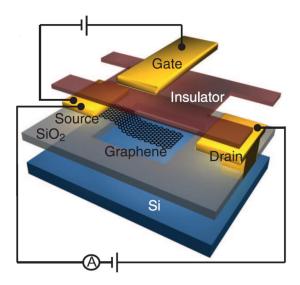

| 2.10 | Conventional GFET schematic (a) top view (b) cross-sectional view                      | 36 |

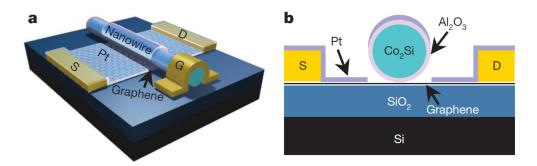

| 2.11 | GFET with self-aligned nanowire gate (a) three-dimensional view (b)                    |    |

|      | cross-sectional view [111]                                                             | 37 |

| 2.12 | Typical output characteristics of a GFET                                               | 38 |

| 2.13 | Qualitative charge distribution in the graphene channel for constant gate-               |    |

|------|------------------------------------------------------------------------------------------|----|

|      | to-source voltage and (a) $V_{ds}=0$ (b) $V_{ds}=V_{gs}$ (c) $V_{ds}>V_{gs}$ . The Dirac |    |

|      | cone represents the charge neutrality point                                              | 39 |

| 2.14 | Graphene field-effect tunnelling transistor and the corresponding band                   |    |

|      | structure                                                                                | 43 |

| 2.15 | Schematic of graphene barristor [149]                                                    | 45 |

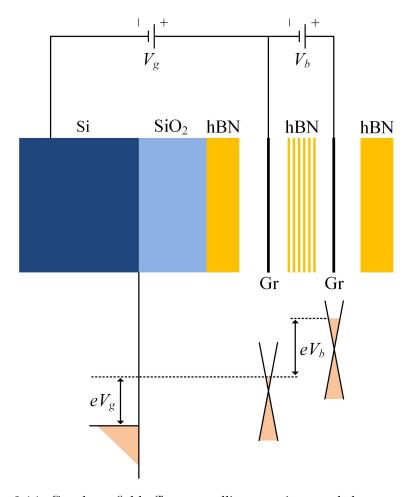

| 3.1  | Bandstructure of bilayer graphene under vertical bias voltage (a) $0V/nm$                |    |

|      | (b) 8 V/nm. Calculated with DFT in ATK [6]                                               | 65 |

| 3.2  | Bandstructure of bilayer graphene under vertical bias voltage (a) $0V/nm$                |    |

|      | (b) 8 V/nm. Calculated with Extended Hückel Model in ATK [6]                             | 66 |

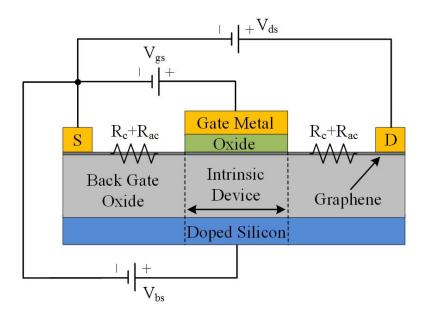

| 3.3  | Cross section of dual-gate GFET modelled in this thesis. The channel                     |    |

|      | material is monolayer graphene. Voltages $V_{gs}$ and $V_{bs}$ are top- and back-        |    |

|      | gate voltages. $V_{ds}$ is the voltage between external drain (D) and source             |    |

|      | (S) electrodes. Contact and access resistances ( $R_c$ and $R_{ac}$ ) are considered     |    |

|      | as one resistance for both source and drain. Intrinsic device is the region              |    |

|      | covered by the top gate                                                                  | 69 |

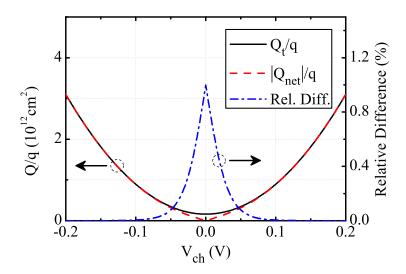

| 3.4  | Charge density as a function of the channel potential $V_{ch}$ (left axis): $Q_{net}$    |    |

|      | and $Q_t$ . The relative difference (right axis) is also shown                           | 74 |

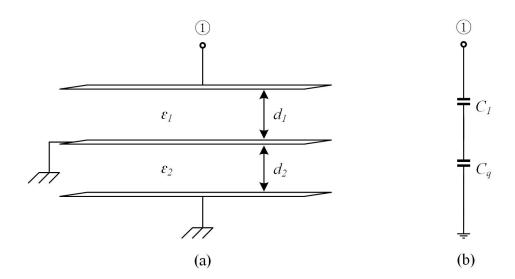

| 3.5  | (a) Schematic of the three-plate capacitor. (b) Equivalent circuit for the               |    |

|      | capacitance seen at node 1 when the middle plate is graphene or 2D elec-                 |    |

|      | tron gas                                                                                 | 76 |

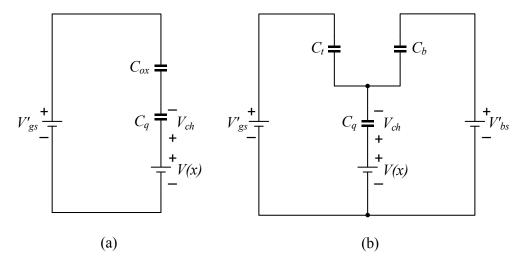

| 3.6  | Equivalent circuit of GFET gate electrostatics describing the relationship               |    |

|      | between gate oxide capacitances $(C_{ox}, C_t \text{ and } C_b)$ and quantum capaci-     |    |

|      | tance $C_q$ (a) single gate (b) dual gate. $V_{gs}'$ and $V_{bs}'$ are the net top- and  |    |

|      | back-gate voltage respectively. $V_{ch}$ represents the channel potential and            |    |

|      | V(x) refers to the voltage drop in the channel                                           | 76 |

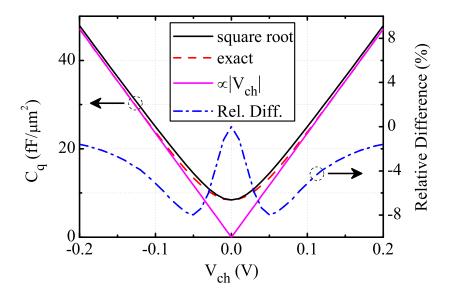

| 3.7  | Quantum capacitance as a function of the channel potential $V_{ch}$ (left axis):                                             |    |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

|      | square-root, exact and $\propto  V_{ch} $ models. The relative difference (right axis)                                       |    |

|      | between the square-root and exact models is also shown                                                                       | 78 |

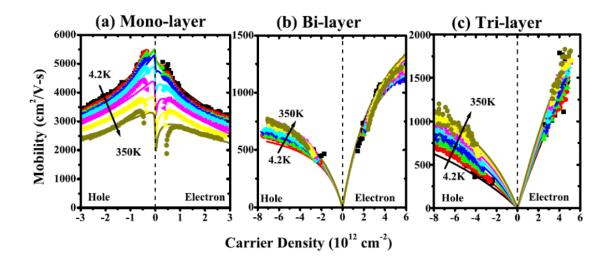

| 3.8  | Measured mobility vs. carrier density at various temperature (a) Mono-                                                       |    |

|      | layer graphene. (b) bilayer graphene. (c) trilayer graphene [26]                                                             | 79 |

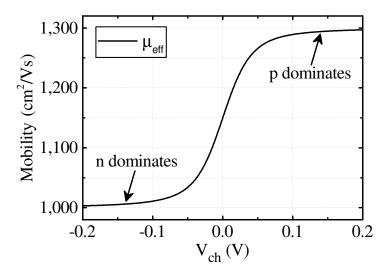

| 3.9  | $\mu_{eff}$ as a function of the channel potential $V_{ch}$ . Parameters used in this                                        |    |

|      | graph: $\mu_n = 1000  \mathrm{cm}^2/\mathrm{Vs}$ , $\mu_p = 1300  \mathrm{cm}^2/\mathrm{Vs}$ and $\Delta = 30  \mathrm{meV}$ | 81 |

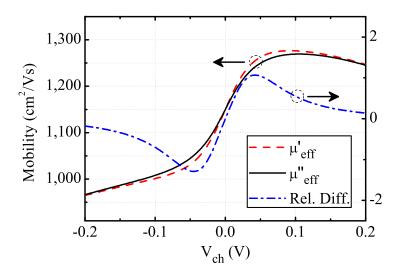

| 3.10 | Effective carrier mobility as a function of the channel potential $V_{ch}$                                                   |    |

|      | (left axis): exact model $\mu'_{eff}$ and approximation $\mu''_{eff}$ . The relative                                         |    |

|      | difference (right axis) is also shown. Parameters used in this graph:                                                        |    |

|      | $\mu_n = 1000 \mathrm{cm^2/Vs},  \mu_p = 1300 \mathrm{cm^2/Vs},  m = 1 V^2,  \Delta = 30 \mathrm{meV}.$                      | 84 |

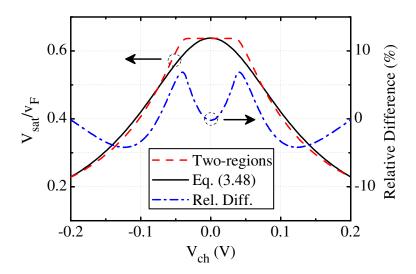

| 3.11 | Ratio of saturation velocity $V_{sat}$ to Fermi velocity $v_F$ in graphene as a                                              |    |

|      | function of the channel potential $V_{ch}$ (left axis): two-region model [16]                                                |    |

|      | and the proposed approximation. The relative difference (right axis) is                                                      |    |

|      | also shown.                                                                                                                  | 85 |

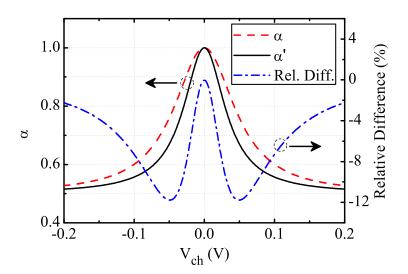

| 3.12 | Capacitance weighting factor as a function of the channel potential $V_{ch}$                                                 |    |

|      | (left axis): exact model $\alpha$ and approximation $\alpha'$ . The relative difference                                      |    |

|      | (right axis) is also shown                                                                                                   | 87 |

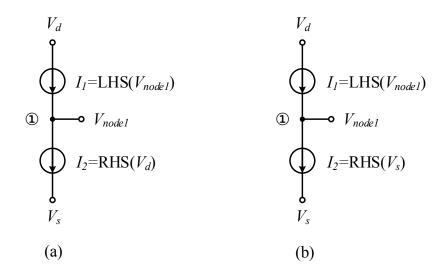

| 3.13 | Equivalent circuits used to extract (a) $V_{cd}$ and (b) $V_{cs}$                                                            | 88 |

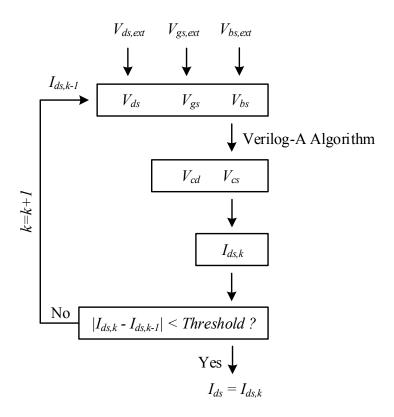

| 3.14 | Simulation steps and the iteration loop in Keysight ADS                                                                      | 91 |

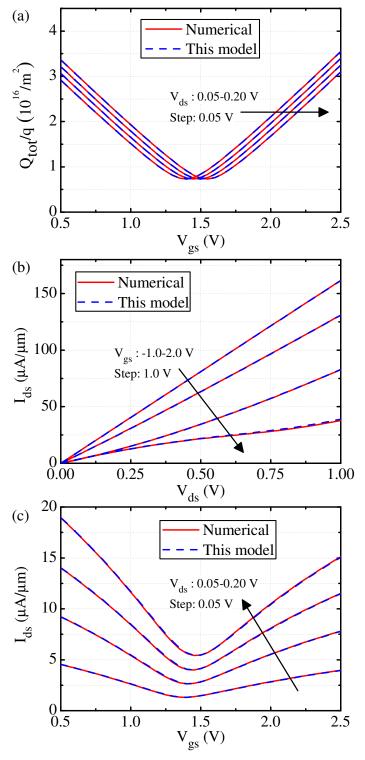

| 3.15 | (a) The charge density on the drain side $(Q_{tot}/q \text{ vs. } V_{gs})$ , (b) Output and                                  |    |

|      | (c) transfer characteristics of a 5- $\mu m$ GFET. The results calculated from                                               |    |

|      | the analytical model proposed in this thesis is compared with the results                                                    |    |

|      | achieved from the numerical calculation. Parameters used in the model:                                                       |    |

|      | $L = 5 \mu\text{m}, \ t_{oxt} = 15 \text{nm}, \ k_t = 8.9, \ t_{oxb} = 300 \text{nm}, \ k_b = 3.9, \ T = 300 \text{K},$      |    |

|      | $V_{gs0}=1.1\mathrm{V},\;V_{bs0}=11\mathrm{V},\;\mu_n=920\mathrm{cm^2/Vs},\;\mu_p=1330\mathrm{cm^2/Vs},\;\Delta=$            |    |

|      | 92 meV, $R_{d/s} = 0 \Omega \cdot \mu \text{m}, m = 0.1 V^2$                                                                 | 93 |

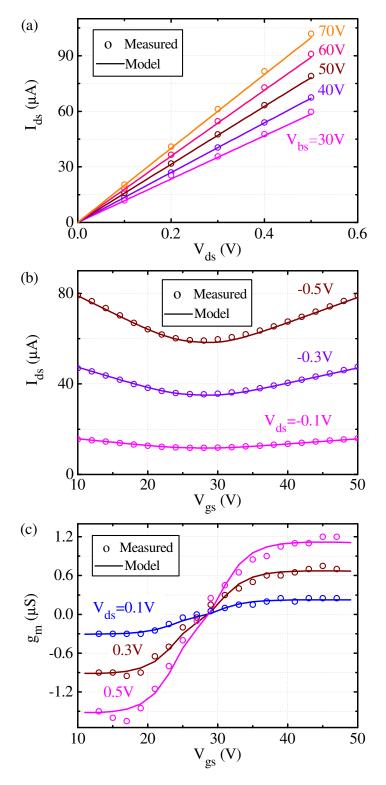

| 3.10 | Modelled output and transfer characteristics of a $20\mu\mathrm{m}\times15\mu\mathrm{m}$ GFE1                                                                          |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | vs. measurement. (a) drain-to-source current $I_{ds}$ against drain-to-source                                                                                          |    |

|      | voltage $V_{ds}$ for various back-gate voltage $V_{gs}$ and (b) drain-to-source cur-                                                                                   |    |

|      | rent $I_{ds}$ against back-gate voltage $V_{gs}$ for various drain-to-source voltages                                                                                  |    |

|      | $V_{ds}$ (c) transconductance $g_m$ against back-gate voltage $V_{gs}$ for various                                                                                     |    |

|      | drain-to-source voltages $V_{ds}$ . Parameters used in the model: $L=20\mu\mathrm{m}$ ,                                                                                |    |

|      | $W = 15 \mu\mathrm{m}, \ t_{oxb} = 500 \mathrm{nm}, \ k_b = 3, \ T = 300 \mathrm{K}, \ V_{bs0} = 27.1 \mathrm{V},$                                                     |    |

|      | $\mu_n = 690  \mathrm{cm}^2/\mathrm{Vs},  \mu_p = 940  \mathrm{cm}^2/\mathrm{Vs},  \Delta = 123  \mathrm{meV},  R_{d/s} = 3.75  \mathrm{k}\Omega \cdot \mu\mathrm{m},$ |    |

|      | $m=1V^2$                                                                                                                                                               | 95 |

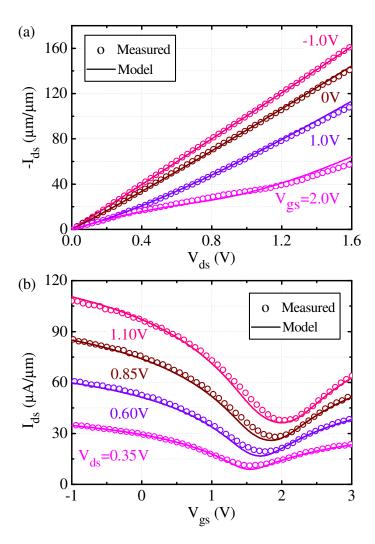

| 3.17 | Modelled transfer characteristics of a 5 $\mu \mathrm{m}$ GFET vs. measurement data                                                                                    |    |

|      | from [47]. Drain-to-source current $I_{ds}$ against top-gate voltages $V_{gs}$ for                                                                                     |    |

|      | various drain-to-source voltage $V_{ds}$ . Parameters used in the model: $L=$                                                                                          |    |

|      | $5 \mu\text{m},  t_{oxt} = 15 \text{nm},  k_t = 8.9,  t_{oxb} = 300 \text{nm},  k_b = 3.9,  T = 300 \text{K},  V_{gs0} = 300 \text{m}$                                 |    |

|      | 1.1 V, $V_{bs0} = 11 \text{ V}$ , $\mu_n = 920 \text{ cm}^2/\text{Vs}$ , $\mu_p = 1330 \text{ cm}^2/\text{Vs}$ , $\Delta = 92 \text{ meV}$ ,                           |    |

|      | $R_{d/s} = 2 \mathrm{k}\Omega \cdot \mu\mathrm{m},  m = 0.1  V^2. \ldots $         | 96 |

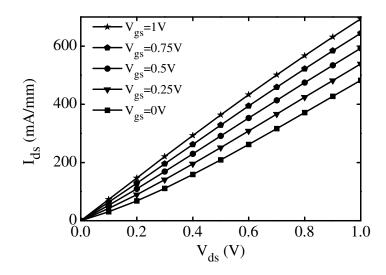

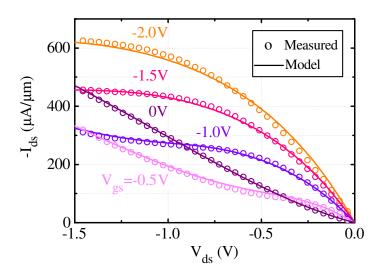

| 3.18 | Modelled output characteristics of a $3\mu\mathrm{m}$ GFET against measurement                                                                                         |    |

|      | data from [48]. Drain-to-source current $I_{ds}$ against drain-to-source voltage                                                                                       |    |

|      | $V_{ds}$ for various gate-to-source voltages $V_{gs}$ . Parameters used in the model:                                                                                  |    |

|      | $L = 3 \mu{\rm m}, \; t_{oxb} = 8.5 {\rm nm}, \; k_b = 3.5, \; T = 300 {\rm K}, \; V_{bs0} = -0.07 {\rm V}, \; \mu_n = 0.07 {\rm V}$                                   |    |

|      | 6500 cm²/Vs, $\mu_p = 7700$ cm²/Vs, $\Delta = 66$ meV, $R_{d/s} = 120\Omega \cdot \mu\text{m}, m =$                                                                    |    |

|      | $0.5 V^2$                                                                                                                                                              | 97 |

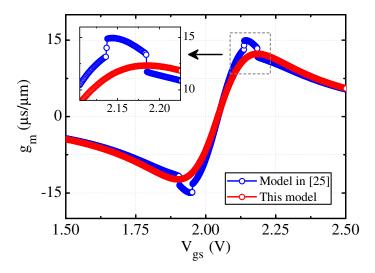

| 3.19 | Comparison of the modelled transconductance $g_m$ vs. top-gate voltage                                                                                                 |    |

|      | $V_{gs}$ ( $V_{ds}$ =1.1 V) of a 5 $\mu$ m GFET [47] in this work and a model with two-                                                                                |    |

|      | region saturation velocity [25]. Parameters used in the model are taken                                                                                                |    |

|      | from [25] except the carrier mobility: $L = 5 \mu\text{m}, t_{oxt} = 15 \text{nm}, k_t = 8.9,$                                                                         |    |

|      | $t_{oxb} = 300  \mathrm{nm}, \; k_b = 3.9, \; T = 300  \mathrm{K}, \; V_{gs0} = 1.24  \mathrm{V}, \; V_{bs0} = 11  \mathrm{V}, \; \Delta = 100  \mathrm{M}$            |    |

|      | $100\mathrm{meV},R_{d/s}=3.5\mathrm{k}\Omega\cdot\mu\mathrm{m}$ (and $m=10V^2$ for this work, $\hbar\Omega=75\mathrm{mV}$                                              |    |

|      | for [25]). $\mu_n = \mu_p = 115,000 \mathrm{cm^2/Vs}$ is used here instead of the original                                                                             |    |

|      | $1150 \mathrm{cm}^2/\mathrm{Vs}$ to magnify the discontinuity of $q_m$                                                                                                 | 97 |

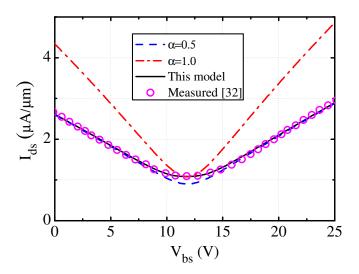

| 3.20 | Comparison of the modelled drain to source current $I_{ds}$ vs. back-gate to                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | source voltage $V_{bs}$ of a 2.8 $\mu \mathrm{m}$ GFET [32] in this work and models using                                                                                                             |

|      | constant $\alpha$ . Parameters used in the models: $L=2.8\mu\mathrm{m},t_{oxb}=285\mathrm{nm},$                                                                                                       |

|      | $k_b = 3.9, T = 300 \mathrm{K}, V_{bs0} = 11.86 \mathrm{V},  \mu_n = 430 \mathrm{cm}^2/\mathrm{Vs},  \mu_p = 410 \mathrm{cm}^2/\mathrm{Vs},$                                                          |

|      | $\Delta = 64 \text{ meV}, R_{d/s} = 100 \Omega \cdot \mu\text{m}, m = 0.5 V^2.$                                                                                                                       |

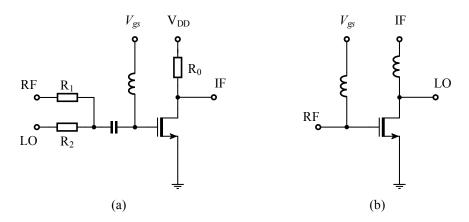

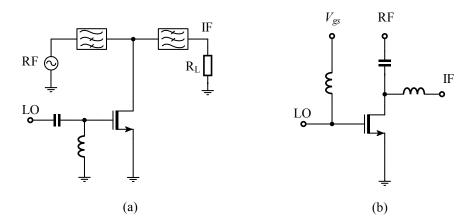

| 4.1  | GFET RF mixers based on (a) ambipolar transfer characteristic (b) gate-                                                                                                                               |

|      | induced electrostatic modulation                                                                                                                                                                      |

| 4.2  | GFET RF mixers (a) subharmonic (b) zero-bias                                                                                                                                                          |

| 4.3  | Block diagram of non-Foster matching topology                                                                                                                                                         |

| 4.4  | Diagram of Floating (a) and single-ended (b) NFC                                                                                                                                                      |

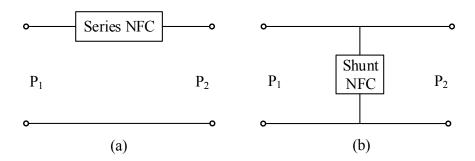

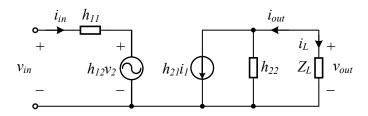

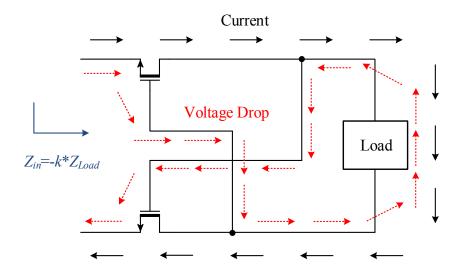

| 4.5  | The h-model of NFC                                                                                                                                                                                    |

| 4.6  | Typical voltage current relationship of Linvill's NFC model having current                                                                                                                            |

|      | flow from lower to higher potential at the load                                                                                                                                                       |

| 4.7  | Schematic of GFET with parasitics [28]. $C_{gs}=280\mathrm{fF},C_{gd}=50\mathrm{fF},C_{ds}=$                                                                                                          |

|      | 150 fF, $C_{pd} = 40$ fF, $C_{pg} = 40$ fF, $L_s = 75$ pH, $L_d = 75$ pH, $L_g = 75$ pH,                                                                                                              |

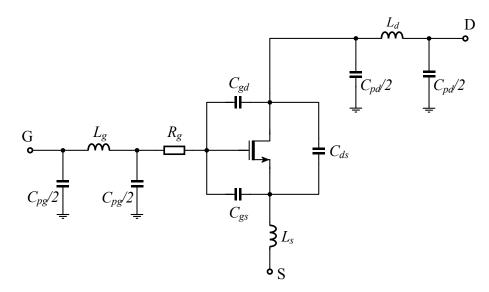

|      | $R_g = 12\Omega.\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$ |

| 4.8  | Schematic of four resistor bias circuit                                                                                                                                                               |

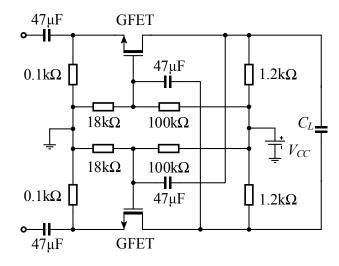

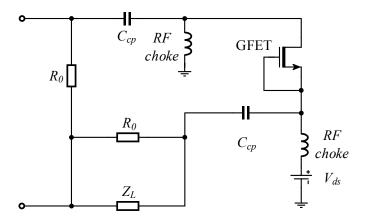

| 4.9  | Schematic of the NFC simulated in this work                                                                                                                                                           |

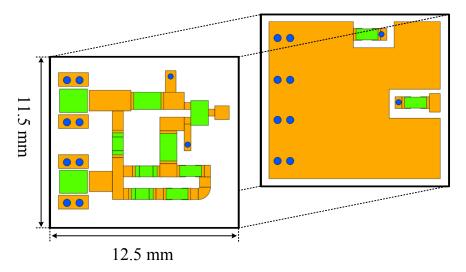

| 4.10 | Layout including footprint of real components (except the GFET foot-                                                                                                                                  |

|      | print) [30]                                                                                                                                                                                           |

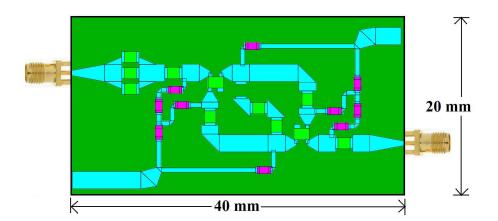

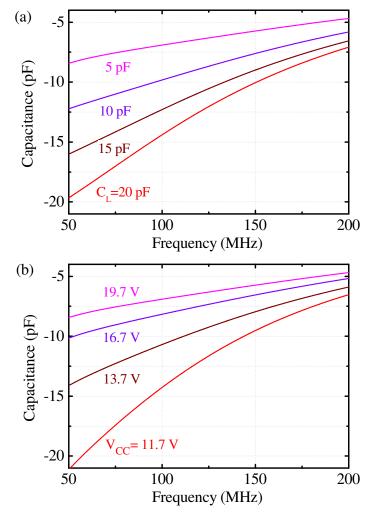

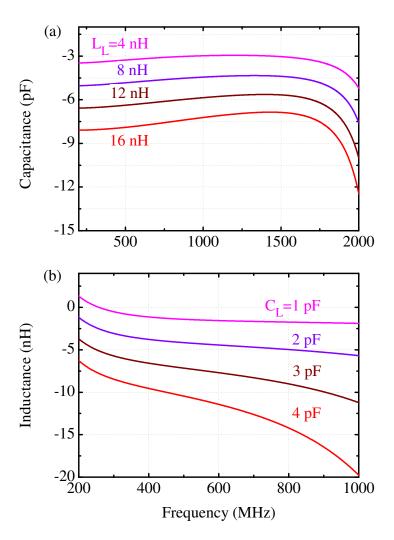

| 4.11 | Simulated capacitance of the proposed NFC: (a) load tuning (b) voltage                                                                                                                                |

|      | tuning                                                                                                                                                                                                |

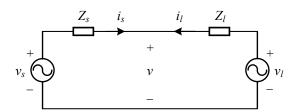

| 4.12 | The venin equivalent source and load converter model                                                                                                                                                  |

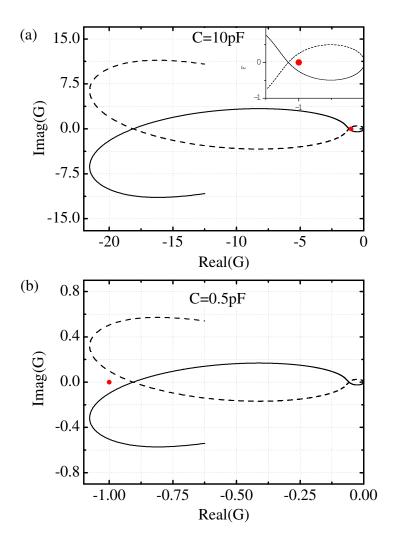

| 4.13 | Complex plot of G(s) (a) for C = 10 pF (b) for C = 0.5 pF $\dots \dots \dots$                         |

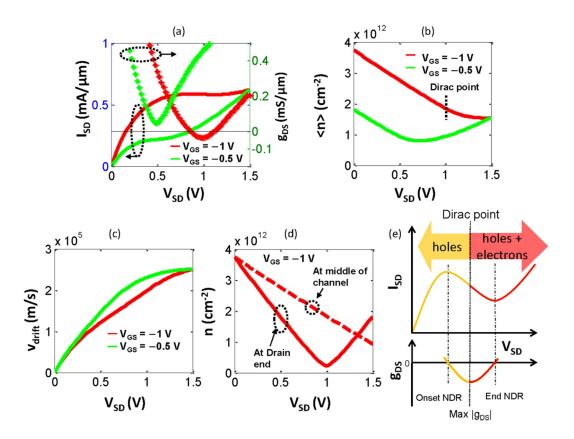

| 4.14 | Simulated results of a L=500 nm GFET (a) source-to-drain current $I_{SD}$                                                |      |

|------|--------------------------------------------------------------------------------------------------------------------------|------|

|      | against source-to-drain voltage for $V_{GS}=-0.5~\mathrm{V}$ and $V_{GS}=-1~\mathrm{V};$ (b)                             |      |

|      | average carrier density $\langle \rho_{sh} \rangle$ as a function of $V_{SD}$ for $V_{GS} = -0.5$ V and                  |      |

|      | $V_{GS} = -1 \text{ V}$ ; (c) drift velocity as a function of $V_{SD}$ for $V_{GS} = -0.5 \text{ V}$ and                 |      |

|      | $V_{GS} = -1 \text{ V}$ ; (d) charge density as a function of $V_{SD}$ for $V_{GS} = -1 \text{ V}$ ; (e)                 |      |

|      | simplified sketch demonstrating the transition from unipolar to bipolar                                                  |      |

|      | channel [38]                                                                                                             | 25   |

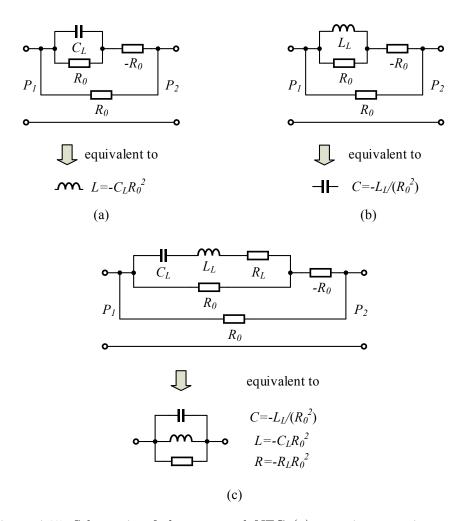

| 4.15 | Schematic of the proposed NFC (a) negative capacitance, (b) negative                                                     |      |

|      | inductance and (c) negative shunt RLC                                                                                    | 27   |

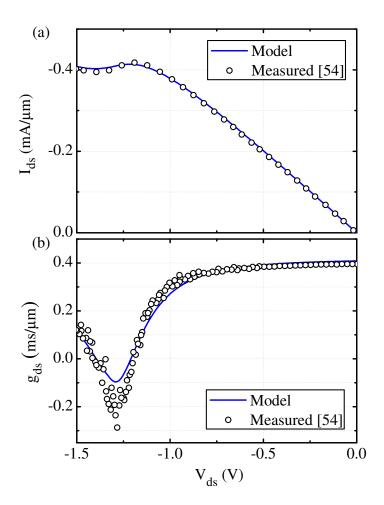

| 4.16 | Measured and modelled results of $L=80\mathrm{nm}$ GFET (a) drain-to-source                                              |      |

|      | current $I_{ds}$ and (b) output conductance $g_{ds}$ against $V_{ds}$ . The measured                                     |      |

|      | data is provided in the supporting information of [37]. Parameters used                                                  |      |

|      | in the model: $L=80$ nm, $t_{oxt}=1.5$ nm, $k_t=3.9,T=300$ K, $\mu_p=$                                                   |      |

|      | $\mu_n = 5000{\rm cm^2/Vs}, V_{gs0} = 0.77{\rm V}, \Delta = 40{\rm meV}, R_{d/s} = 1.55{\rm k}\Omega\cdot\mu{\rm m}$ and |      |

|      | m = 1V <sup>2</sup>                                                                                                      | 28   |

| 4.17 | Schematic of NDR-based graphene NFC                                                                                      | 28   |

| 4.18 | Layout including footprint of real components (neglecting the GFET foot-                                                 |      |

|      | print)                                                                                                                   | 29   |

| 4.19 | Simulations of (a) negative capacitance and (b) inductance for various                                                   |      |

|      | load conditions                                                                                                          | 30   |

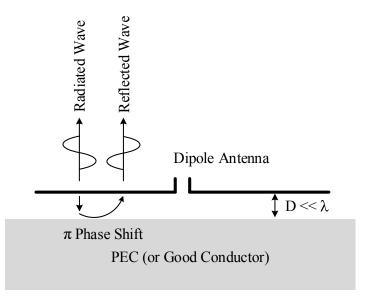

| 5.1  | Out-of-phase reflection when the antenna is placed close to the ground                                                   |      |

| -    | plane                                                                                                                    | 37   |

| 5.2  | In-phase reflection when the antenna is placed at a distance of $\lambda/4$ from                                         | •    |

| J    | ground plane                                                                                                             | 37   |

| 5.3  | Schematic of high impedance surface (a) top view and (b) cross-sectional                                                 | ′'   |

| J.J  | view                                                                                                                     | 39   |

| 5.4  | Ideal equivalent circuit model of high impedance surface                                                                 |      |

| 0.4  | racar equivalent eneunt model of high impedance surface                                                                  | ינינ |

| 5.5  | In-phase reflection when the antenna is placed close to a high impedance      |

|------|-------------------------------------------------------------------------------|

|      | surface                                                                       |

| 5.6  | Non-ideal equivalent circuit model of high impedance surface with grid        |

|      | conductance $G$ and series resistance $R_s$                                   |

| 5.7  | Schematic of the periodic metallic strip array                                |

| 5.8  | Metallic patch array as the complementary structure of the periodic strip     |

|      | array                                                                         |

| 5.9  | Schematic of dielectric surrounded metallic via array                         |

| 5.10 | Plot of (a) grid capacitance (b) grid conductance (c) surface inductance      |

|      | (d) surface resistance as functions of frequency                              |

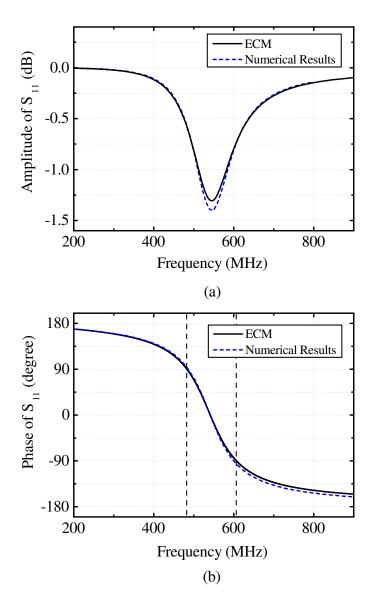

| 5.11 | Plot of $S_{11}$ against frequency (a) magnitude (b) phase                    |

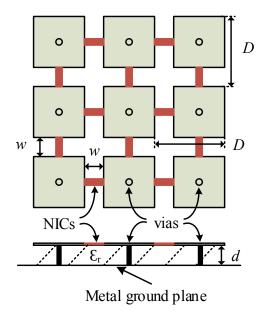

| 5.12 | Schematic of NFCs loaded high impedance surface                               |

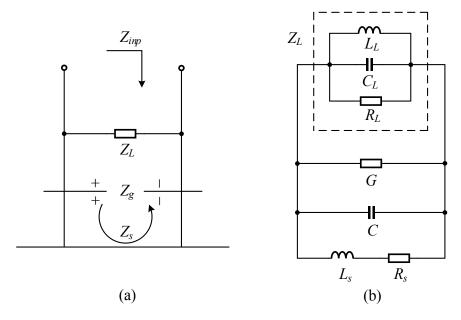

| 5.13 | High impedance surface loaded with NFCs (a) cross-sectional schematic         |

|      | (b) equivalent circuit model                                                  |

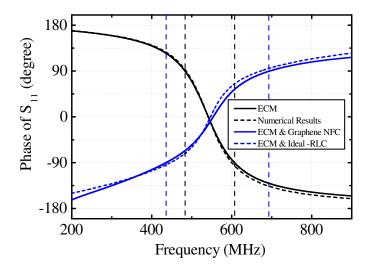

| 5.14 | Phase of $S_{11}$ against frequency. Black lines are for passive HIS and blue |

|      | lines are for actively-loaded HIS                                             |

## List of Tables

| 3-A | Details of | <b>GFET</b> | model | comparison. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 9 | 8 |

|-----|------------|-------------|-------|-------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|---|

|-----|------------|-------------|-------|-------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|---|

## List of Abbreviations

2D Two-Dimensional

h-BN Hexagonal Boron Nitride

TMD Transition Metal Dichalcogenide

BP Black Phosphorous

CVD Chemical Vapour Deposition

FET Field-Effect Transistor

DoS Density of State

GFET Graphene FET

NFC Non-Foster Circuit

BJT Bipolar Junction Transistor

Op-amp Operational Amplifier

RTD Resonant Tunnelling Diode

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

RF Radio-Frequency

GNR Graphene Nanoribbon

GO Graphite Oxide

rGO Reduced Graphene Oxide

GIC Graphite Intercalation Compounds

NMP Nmethylpyrrolidone

UHV Ultra-High Vacuum

C<sub>2</sub>H<sub>4</sub> Ethylene

$C_2H_2$  Acetylene

PMMA Polymethyl Methacrylate

Ge Germanium

FoM Figures of Merit

CS Common-Source

CD Common-Drain

CG Common-Gate

pHEMT Pseudomorphic High-Electron-Mobility Transistors

HEMT High-Electron-Mobility Transistors

mHEMT Metamorphic High-Electron-Mobility Transistors

HET Hot-Electron Transistor

EBI Emitter-Base Insulator

BCI Base-Collector Insulator

NEGF Nonequilibrium Greens Function

2DEG Two-Dimensional Electron Gas

LO Local Oscillator

IF Intermediate Frequency

IIP3 Input Third-order Intercept Point

PSK Phase Shift Keying

FSK Frequency Shift Key

EOT Equivalent Oxide Thickness

ESA Electrically Small Antenna

PCB Printed Circuit Board

OCS Open Circuit Stable

SCS Short Circuit Stable

EM Electromagnetic

RHP Right-Half Plane

LHP Left-Half Plane

W/L Width-to-Length Ratio

${\bf HIS} \quad \ \, {\bf High \ Impedance \ Surface}$

PEC Perfect Electric Conductor

## Chapter 1

## Introduction

The emerging two-dimensional (2D) materials with atomic thickness have been of great interest to scientists and engineers in the last decade. At the moment, the most-explored 2D materials are graphene, hexagonal boron nitride (h-BN), transition metal dichalcogenides (TMDs), black phosphorous (BP), etc. As the first isolated 2D material [1], graphene has been produced through mechanical exfoliation, chemical vapour deposition (CVD) and other approaches like epitaxial growth on SiC substrate. Due to the extraordinary electronic, thermal, optical and mechanical properties, 2D materials have been considered as potential candidates for the development of novel electronic and optoelectronic devices. Their excellent scalability also enables further miniaturisation of electronic components for the future generation of semiconductor technology.

### 1.1 Graphene and Two-dimensional Materials

Graphene, sometimes also considered as unzipped carbon nanotube (Fig. 1.1), is a gapless material with a measured record of carrier mobility exceeding 1,000,000 cm<sup>2</sup>/V·s in suspended form at 4 K [2]. As we know, the carrier mobility ( $\mu$ ) describes how fast electron or hole moves under certain electron field (E):  $v_d = \mu E$ , where  $v_d$  is the drift

Figure 1.1: Atomic structure of (a) graphene (b) single-walled carbon nanotube

velocity that illustrates the average velocity a carrier can reach under E. This ultra high mobility of graphene, beyond any known semiconducting materials, is of particular interest for the development of novel high-speed devices. It is shown in Fig. 1.2 (a) that the number of publications on graphene has been increasing exponentially during the last decade. Graphene has been used to develop field-effect transistors (FETs) [3– 5]. The ambipolar conducting property of graphene allows either electron or hole as the major carriers. By applying a gate voltage perpendicular to the graphene channel, the electrostatic doping of graphene is realized and the channel resistance varies as a function of gate voltage. Unfortunately, due to the nature of zero gap between valence and conduction band of graphene, the on/off current ratio of graphene FET (GFET) is significantly smaller than the requirement of digital circuits [6]. Therefore, the potential application of GFET is focused on analog/RF circuits. It has been predicted in [7] that thanks to the ultrahigh carrier mobility of graphene, the intrinsic cut-off frequency of sub-10 nm GFET is in the range of THz regime, making it attractive for high frequency applications. However, when graphene is deposited onto substrate like SiO<sub>2</sub>, its mobility is significantly degraded compared with the suspended case [1, 8]. This is because of the impurity scattering induced by the charged impurities in the  $SiO_2$  substrate[9]. Meanwhile, the negative differential resistance (NDR) of GFET has also been reported, providing an alternative option for devices in analog/RF applications [10].

Figure 1.2: Number of publications on (a) graphene and (b) BN, MoS<sub>2</sub> and WS<sub>2</sub>. Sourced from Web of Science.

In 2007, a theoretical calculation predicted the generation of a bandgap for graphene on h-BN substrate [11], resulting in a significant increase in the exploration of h-BN. From Fig. 1.2(b) one can see the number of publications on h-BN has been doubled in the last 10 years. h-BN also has hexagonal lattice structure, as shown in Fig. 1.3(a). Although it was revealed later that as a insulator h-BN could not open a bandgap in graphene, it turned out to be a perfect substrate to preserve graphene's ultrahigh carrier mobility [12] due to the reduced charged impurities (compared with grahene-on-SiO<sub>2</sub>)

Figure 1.3: Atomic structure of (a) h-BN (b)  $MoS_2$ .

[12]. However, the mobility of graphene-on-h-BN is still lower than that of suspended graphene.

Soon after the discovery of graphene, other 2D materials like TMDs (e.g. MoS<sub>2</sub>, WS<sub>2</sub>) were also prepared through mechanical exfoliation [13, 14] or CVD method [14, 15]. Among them, MoS<sub>2</sub> is the most well-explored material with the hexagonal lattice structure (trigonal prismatic (2H) phase) shown in Fig. 1.3(b). Intersetingly, the band-structure of TMDs changes while the thickness is reduced from bulk to monolayer. For instance, monolayer MoS<sub>2</sub> has a large direct bandgap of 1.95 eV while bulk MoS<sub>2</sub> exhibits a indirect bandgap of 1.2 eV [16]. Experimental results have shown that the wide bandgap of monolayer MoS<sub>2</sub> can prevent MoS<sub>2</sub> FETs from short-channel effects [17–19]. However, the measured carrier mobility in monolayer MoS<sub>2</sub> on SiO<sub>2</sub> substrate is only up to a few hundred cm<sup>2</sup>/V·s due to the optical photon scattering [20–22], limiting their applications in high frequencies. Meanwhile, FETs based on other TMDs also suffer from the relatively low carrier mobility [23–26].

Black phosphorus (BP) is another emerging 2D material with atomic thickness. Monolayer BP is also known as phosphorene. It is a semiconductor with 0.3 eV indirect bandgap in bulk form and 1.8 eV direct bandgap when the thickness is decreased to the monolayer limit [27, 28]. Thanks to the narrow bandgap of few-layer BP, it is able to absorb light from visible to near-infrared regime efficiently, enabling the development of BP-based photodetectors [29–31]. The room-temperature hole mobility over 5000 cm<sup>2</sup>/V · s has been predicted for BP while the calculated electron mobility of few-layer BP is significantly lower (  $1000 \text{ cm}^2/\text{V} \cdot \text{s}$ ) [32–34]. The measured hole mobility in BP FETs varies from a few hundred to  $1000 \text{ cm}^2/\text{V} \cdot \text{s}$ . The h-BN sandwiched BP has also been reported, demonstrating an improved hole mobility of  $1350 \text{ cm}^2/\text{V} \cdot \text{s}$  [35]. The implementation of h-BN also helps to improve the device stability under ambient condition as BP would easily react with the oxygen in air [36], which can significantly degrade the device performance.

#### 1.2 Non-Foster Circuit

Foster's reactance theorem [37] reveals that the reactance of a two-terminal passive loss-less device (e.g. capacitor and inductor) should increase monotonically with frequency, as show in Fig. 1.4(a). The non-Foster circuit (NFC), in contrast, is an active device whose reactance decreases monotonically with frequency. Compared with the passive matching that only achieves zero reactance at a pre-designed resonant frequency (Fig. 1.4(a)), the realisation of NFCs enables the active impedance matching over a broad frequency range, as shown in Fig. 1.4(b). So far, NFCs have been realised with Linvill's approach utilising a pair of bipolar junction transistors (BJTs) [38]. Other methods using operational amplifier (Op-amp) or resonant tunnelling diode (RTD) have also been reported [39, 40]. The implementations of NFC include active impedance matching of electrically small antenna and bandwidth extension of metasurface structures such as high impedance surface (HIS).

Figure 1.4: Impedance matching techniques (a) passive and (b) active.

#### 1.2.1 History of Non-Foster Circuit

The negative resistance of vacuum tubes was observed by Albert Hull at General Electric in 1918 [41]. About two years later, the concept of NFC, also known as negative impedance converter (NIC), demonstrating negative capacitance or inductance, were proposed by Marius Latour [42]. In 1931, George Crisson et al. at Bell Labs successfully developed a negative resistance as telephone line repeaters with vacuum tubes [43]. Two decades later, the vacuum tube based NFCs were also presented by Merrill [44]. However, it was not until 1953, when the first NFC based on BJTs was demonstrated by Linvill [38], that NFC became of great interest to the engineers. The approach of Linvill's NFC belongs to the voltage-inversion technology. Later in 1957, Larky and Yanagisawa presented their BJT-based current-inversion NFCs individually [45, 46]. Today, the novel BJT NFCs utilizing surface mounted components have successfully demonstrated negative impedance at microwave frequencies. In addition to BJTs, the operational amplifiers (Op-amps) were also used to achieve negative impedance [39, 47, 48]. The Op-amp NFCs have simpler circuit schematic and are easier to stabilise compared with the BJT-based counterparts. This is because it is convenient to define the poles and zeros of the Op-amp

with external components. However, Op-amp NFCs suffer from low operation frequency and small bandwidth due to the fixed gain-bandwidth product of Op-amps and the associated parasitics [49]. Recently, the fully-integrated broadband negative inductances, operating in gigahertz regime have also been developed using CMOS or BICOMS process [50–52]. These circuits are all based on Linvill's model or the modified version. Due to the complexity of Linvill's circuit, the simplified NFCs based on negative resistance of tunnel diode and resonant tunnelling diode (RTD) have been explored in Ref. [53, 54]. The idea of converting negative resistance to negative impedance can be tracked back to the 1920s [55–57]. With only one active device and less biasing components, the dimension of negative-resistance-based NFC has been significantly reduced.

#### 1.3 Research Objectives

The main objectives of this study are presented as below:

- 1. Derive an accurate closed-form analytical model for GFET. The existing GFET models either need to be solved numerically or exhibit poor accuracy in modelling the ambipolar transfer characteristic of GFET. In this thesis, an accurate GFET model will be developed for circuit analysis. The model should have an analytical form and is compatible with Spice or Verilog-A language.

- 2. Explore the implementation of GFET for NFC design. In this case, we focus on the design of Linvill's NFC model with a pair of cross-coupled GFETs. Due to the ultrahigh carrier mobility of graphene, GFETs are predicted to exhibit higher cutoff frequency than other existing transistors. Hence, it would be interesting to investigate the potential of GFET-based NFC for high frequency applications.

- 3. Explore the realization of NFC utilizing the NDR behaviour of GFET.

The NFC based on the NDR of RTD has been demonstrated. The RTD-based NFC has much simpler circuit layout compared with the Linvill's model and can potentially

operate at higher frequency with miniaturized physical dimensions. As GFET also shows NDR effect, it provides us an alternative way to achieve high-performance NFC based on the graphene platform.

4. Demonstrate the implementation of Graphene NFC for bandwidth improvement of HIS. The passive HIS exhibits a narrow bandwidth near its center operation frequency. Due to its inherent limitation of passive resonance, it is impractical to achieve broadband HIS without compromising other performances such as the device thickness, loss and design complexity. Thus, the graphene NFCs are proposed as active loads to cancel the reactance of HIS and extend its operation bandwidth.

#### 1.4 Thesis Outline

This thesis is organised as follows:

Chapter 1 depicts the goals of research as well as the organisation of this thesis. A short introduction of 2D materials and NFC is also included.

Chapter 2 presents a review on electronic and optical properties of graphene. Several approaches used in graphene synthesis are introduced. Graphene transistors as well as classical figures of merit for the analysis of transistor performance are also reviewed.

Chapter 3 is dedicated on the modelling of graphene transistors. The concept of multi-scale modelling for graphene transistors is illustrated and a closed-form analytical model based on the drift-diffusion transport theory is derived. The model is written into Verilog-A language that are suitable for circuit simulation with commercial software such as Keysight ADS. Finally, model validation with measurement results is also presented.

Chapter 4 explores the implementation of GFETs for NFC design. The measurement results of GFET are extracted and reproduced with the proposed model for circuit analysis. Simulation results of a Linvill's NFC utilizing a pair of cross-coupled GFETs and a NFC based on the NDR of GFET are presented.

Chapter 5 examines the bandwidth extension of HIS utilising graphene NFCs. With simulation results presented in Chapter 4, the bandwidth extension of HIS is demonstrated and the stability analysis of actively-loaded HIS is also illustrated.

Chapter 6 concludes the thesis. Some ideas for further research are proposed as well.

#### References

- K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos,

I. V. Grigorieva, and A. A. Firsov, "Electric field effect in atomically thin carbon films," *Science*, vol. 306, no. 5696, pp. 666–669, 2004.

- [2] E. V. Castro, H. Ochoa, M. Katsnelson, R. Gorbachev, D. Elias, K. Novoselov, A. Geim, and F. Guinea, "Limits on charge carrier mobility in suspended graphene due to flexural phonons," *Physical Review Letters*, vol. 105, no. 26, p. 266601, 2010.

- [3] Y.-M. Lin, K. A. Jenkins, A. Valdes-Garcia, J. P. Small, D. B. Farmer, and P. Avouris, "Operation of graphene transistors at gigahertz frequencies." Nano Letters, vol. 9, no. 2, pp. 422–426, 2009.

- [4] L. Liao, J. Bai, Y. Qu, Y.-C. Lin, Y. Li, Y. Huang, and X. Duan, "High-κ oxide nanoribbons as gate dielectrics for high mobility top-gated graphene transistors," Proceedings of the National Academy of Sciences, vol. 107, no. 15, pp. 6711–6715, 2010.

- [5] L. Liao, Y.-C. Lin, M. Bao, R. Cheng, J. Bai, Y. Liu, Y. Qu, K. L. Wang, Y. Huang, and X. Duan, "High-speed graphene transistors with a self-aligned nanowire gate," *Nature*, vol. 467, no. 7313, pp. 305–308, 2010.

- [6] A. V. Klekachev, A. Nourbakhsh, I. Asselberghs, A. L. Stesmans, M. M. Heyns, and S. De Gendt, "Graphene transistors and photodetectors," *The Electrochemical Society Interface*, vol. 22, no. 1, pp. 63–68, 2013.

- [7] J. Zheng, L. Wang, R. Quhe, Q. Liu, H. Li, D. Yu, W.-N. Mei, J. Shi, Z. Gao, and J. Lu, "Sub-10 nm gate length graphene transistors: operating at terahertz frequencies with current saturation," *Scientific Reports*, vol. 3, p. 1314, 2013.

- [8] V. E. Dorgan, M.-H. Bae, and E. Pop, "Mobility and saturation velocity in graphene on SiO<sub>2</sub>," *Applied Physics Letters*, vol. 97, no. 8, p. 082112, 2010.

- [9] J.-H. Chen, C. Jang, S. Xiao, M. Ishigami, and M. S. Fuhrer, "Intrinsic and extrinsic performance limits of graphene devices on SiO<sub>2</sub>," *Nature Nanotechnology*, vol. 3, no. 4, pp. 206–209, 2008.

- [10] Y. Wu, D. B. Farmer, W. Zhu, S.-J. Han, C. D. Dimitrakopoulos, A. A. Bol,

- P. Avouris, and Y.-M. Lin, "Three-terminal graphene negative differential resistance devices," *ACS Nano*, vol. 6, no. 3, pp. 2610–2616, 2012.

- [11] G. Giovannetti, P. A. Khomyakov, G. Brocks, P. J. Kelly, and J. Van Den Brink, "Substrate-induced band gap in graphene on hexagonal boron nitride: Ab initio density functional calculations," *Physical Review B*, vol. 76, no. 7, p. 073103, 2007.

- [12] C. R. Dean, A. F. Young, I. Meric, C. Lee, L. Wang, S. Sorgenfrei, K. Watanabe, T. Taniguchi, P. Kim, K. Shepard et al., "Boron nitride substrates for high-quality graphene electronics," Nature Nanotechnology, vol. 5, no. 10, pp. 722–726, 2010.

- [13] A. Splendiani, L. Sun, Y. Zhang, T. Li, J. Kim, C.-Y. Chim, G. Galli, and F. Wang, "Emerging photoluminescence in monolayer MoS<sub>2</sub>," *Nano Letters*, vol. 10, no. 4, pp. 1271–1275, 2010.

- [14] K. F. Mak, C. Lee, J. Hone, J. Shan, and T. F. Heinz, "Atomically thin MoS<sub>2</sub>: a new direct-gap semiconductor," *Physical Review Letters*, vol. 105, no. 13, p. 136805, 2010.

- [15] H. Liu, M. Si, S. Najmaei, A. Neal, Y. Du, P. Ajayan, J. Lou, and P. Ye, "Dual-gate MOSFETs on monolayer CVD MoS<sub>2</sub> films," in *Device Research Conference (DRC)*. IEEE, 2013, pp. 163–164.

- [16] G. Frey, S. Elani, M. Homyonfer, Y. Feldman, and R. Tenne, "Optical-absorption spectra of inorganic fullerenelike MS<sub>2</sub> (M = Mo, W)," *Physical Review B*, vol. 57, no. 11, p. 6666, 1998.

- [17] H. Liu, A. T. Neal, and P. D. Ye, "Channel length scaling of  $MoS_2$  MOSFETs,"  $ACS\ Nano$ , vol. 6, no. 10, pp. 8563–8569, 2012.

- [18] A. Nourbakhsh, A. Zubair, R. N. Sajjad, A. Tavakkoli KG, W. Chen, S. Fang, X. Ling, J. Kong, M. S. Dresselhaus, E. Kaxiras et al., "MoS<sub>2</sub> field-effect transistor with sub-10 nm channel length," Nano Letters, vol. 16, no. 12, pp. 7798–7806, 2016.

- [19] S. B. Desai, S. R. Madhvapathy, A. B. Sachid, J. P. Llinas, Q. Wang, G. H. Ahn, G. Pitner, M. J. Kim, J. Bokor, C. Hu et al., "MoS<sub>2</sub> transistors with 1-nanometer gate lengths," Science, vol. 354, no. 6308, pp. 99–102, 2016.

- [20] K. Kaasbjerg, K. S. Thygesen, and K. W. Jacobsen, "Phonon-limited mobility in n-type single-layer MoS<sub>2</sub> from first principles," *Physical Review B*, vol. 85, no. 11,

- p. 115317, 2012.

- [21] N. Pradhan, D. Rhodes, Q. Zhang, S. Talapatra, M. Terrones, P. Ajayan, and L. Balicas, "Intrinsic carrier mobility of multi-layered MoS<sub>2</sub> field-effect transistors on SiO<sub>2</sub>," Applied Physics Letters, vol. 102, no. 12, p. 123105, 2013.

- [22] P.-Z. Shao, H.-M. Zhao, H.-W. Cao, X.-F. Wang, Y. Pang, Y.-X. Li, N.-Q. Deng, J. Zhang, G.-Y. Zhang, Y. Yang et al., "Enhancement of carrier mobility in MoS<sub>2</sub> field effect transistors by a SiO<sub>2</sub> protective layer," Applied Physics Letters, vol. 108, no. 20, p. 203105, 2016.

- [23] D. Ovchinnikov, A. Allain, Y.-S. Huang, D. Dumcenco, and A. Kis, "Electrical transport properties of single-layer WS<sub>2</sub>," ACS Nano, vol. 8, no. 8, pp. 8174–8181, 2014.

- [24] W. Zhang, Z. Huang, W. Zhang, and Y. Li, "Two-dimensional semiconductors with possible high room temperature mobility," *Nano Research*, vol. 7, no. 12, pp. 1731– 1737, 2014.

- [25] Y. Cui, R. Xin, Z. Yu, Y. Pan, Z.-Y. Ong, X. Wei, J. Wang, H. Nan, Z. Ni, Y. Wu et al., "High-performance monolayer WS<sub>2</sub> field-effect transistors on high-κ dielectrics," Advanced Materials, vol. 27, no. 35, pp. 5230–5234, 2015.

- [26] M. W. Iqbal, M. Z. Iqbal, M. F. Khan, M. A. Shehzad, Y. Seo, J. H. Park, C. Hwang, and J. Eom, "High-mobility and air-stable single-layer WS<sub>2</sub> field-effect transistors sandwiched between chemical vapor deposition-grown hexagonal BN films," Scientific Reports, vol. 5, p. 10699, 2015.

- [27] Y. Takao, H. Asahina, and A. Morita, "Electronic structure of black phosphorus in tight binding approach," *Journal of the Physical Society of Japan*, vol. 50, no. 10, pp. 3362–3369, 1981.

- [28] V. Tran, R. Soklaski, Y. Liang, and L. Yang, "Layer-controlled band gap and anisotropic excitons in few-layer black phosphorus," *Physical Review B*, vol. 89, no. 23, p. 235319, 2014.

- [29] N. Youngblood, C. Chen, S. J. Koester, and M. Li, "Waveguide-integrated black phosphorus photodetector with high responsivity and low dark current," *Nature Photonics*, 2015.

- [30] M. Huang, M. Wang, C. Chen, Z. Ma, X. Li, J. Han, and Y. Wu, "Broadband black-phosphorus photodetectors with high responsivity," *Advanced Materials*, vol. 28, no. 18, pp. 3481–3485, 2016.

- [31] Q. Guo, A. Pospischil, M. Bhuiyan, H. Jiang, H. Tian, D. Farmer, B. Deng, C. Li, S.-J. Han, H. Wang et al., "Black phosphorus mid-infrared photodetectors with high gain," Nano Letters, vol. 16, no. 7, pp. 4648–4655, 2016.

- [32] J. Qiao, X. Kong, Z.-X. Hu, F. Yang, and W. Ji, "High-mobility transport anisotropy and linear dichroism in few-layer black phosphorus," *Nature Communications*, vol. 5, 2014.

- [33] H. Liu, A. T. Neal, Z. Zhu, X. Xu, D. Tomanek, P. D. Ye, and Z. Luo, "Phosphorene: an unexplored 2D semiconductor with a high hole mobility," *ACS Nano*, 2014.

- [34] X. Liu, K.-W. Ang, W. Yu, J. He, X. Feng, Q. Liu, H. Jiang, D. Tang, J. Wen, Y. Lu et al., "Black phosphorus based field effect transistors with simultaneously achieved near ideal subthreshold swing and high hole mobility at room temperature," Scientific Reports, vol. 6, 2016.

- [35] X. Chen, Y. Wu, Z. Wu, Y. Han, S. Xu, L. Wang, W. Ye, T. Han, Y. He, Y. Cai et al., "High-quality sandwiched black phosphorus heterostructure and its quantum oscillations," *Nature Communications*, vol. 6, 2015.

- [36] Y. Huang, J. Qiao, K. He, S. Bliznakov, E. Sutter, X. Chen, D. Luo, F. Meng, D. Su, J. Decker et al., "Degradation of black phosphorus (BP): the role of oxygen and water," arXiv preprint arXiv:1511.09201, 2015.

- [37] R. M. Foster, "A reactance theorem," *Bell Labs Technical Journal*, vol. 3, no. 2, pp. 259–267, 1924.

- [38] J. Linvill, "Transistor Negative-Impedance Converters," *Proceedings of the IRE*, vol. 41, no. 6, pp. 725–729, Jun. 1953.

- [39] A. Antoniou, "Floating negative-impedance converters," *IEEE transactions on circuit theory*, vol. 19, no. 2, pp. 209–212, 1972.

- [40] D. S. Nagarkoti, Y. Hao, D. P. Steenson, L. Li, E. H. Linfield, and K. Z. Rajab, "Design of broadband non-foster circuits based on resonant tunneling diodes," *IEEE Antennas and Wireless Propagation Letters*, vol. 15, pp. 1398–1401, 2016.

- [41] A. W. Hull, "The dynatron: a vacuum tube possessing negative electric resistance," Proceedings of the Institute of Radio Engineers, vol. 6, no. 1, pp. 5–35, 1918.

- [42] M. Latour, Electrical World. McGraw-Hill, New York, 1920, vol. 76, no. 18.

- [43] G. Crisson, "Negative impedances and the twin 21-type repeater," *Bell System Technical Journal*, vol. 10, no. 3, pp. 485–513, 1931.

- [44] J. Merrill, "Theory of the negative impedance converter," *Bell System Technical Journal*, vol. 30, no. 1, pp. 88–109, 1951.

- [45] A. Larky, "Negative-impedance converters," *IRE Transactions on Circuit Theory*, vol. 4, no. 3, pp. 124–131, 1957.

- [46] T. Yanagisawa, "RC active networks using current inversion type negative impedance converters," *IRE Transactions on Circuit Theory*, vol. 4, no. 3, pp. 140– 144, 1957.

- [47] K. Soundararajan and K. Ramakrishna, "Nonideal negative resistors and capacitors using an operational amplifier," *IEEE Transactions on Circuits and Systems*, vol. 22, no. 9, pp. 760–763, 1975.

- [48] H. Yang, I. Kim, and K. Kim, "Non-Foster matching of a resistively loaded vee dipole antenna using operational amplifiers," *IEEE Transactions on Antennas and Propagation*, vol. 64, no. 4, pp. 1477–1482, 2016.

- [49] J. Long, "Non-Foster circuit loaded periodic structures for broadband fast and slow wave propagation," *Ph.D thesis, University of California, San Diego*, 2015.

- [50] C. R. White, J. W. May, and J. S. Colburn, "A variable negative-inductance integrated circuit at UHF frequencies," *IEEE Microwave and Wireless Components Letters*, vol. 22, no. 1, pp. 35–37, 2012.

- [51] J. M. Covington, K. L. Smith, J. W. Shehan, V. S. Kshatri, T. P. Weldon, and R. S. Adams, "Measurement of a CMOS negative inductor for wideband non-Foster metamaterials," in *Southeastcon*. IEEE, 2014, pp. 1–4.

- [52] S. Saadat, H. Aghasi, E. Afshari, and H. Mosallaei, "Low-power negative inductance integrated circuits for GHz applications," *IEEE Microwave and Wireless Compo*nents Letters, vol. 25, no. 2, pp. 118–120, 2015.

- [53] Q. Tang and H. Xin, "Stability of tunnel diode based negative impedance circuit," in

- Radio Science Meeting (Joint with AP-S Symposium), USNC-URSI. IEEE, 2014, pp. 131–131.

- [54] D. S. Nagarkoti, Y. Hao, D. P. Steenson, L. Li, E. H. Linfield, and K. Z. Rajab, "Design of broadband non-foster circuits based on resonant tunneling diodes," *IEEE Antennas and Wireless Propagation Letters*, vol. 15, pp. 1398–1401, 2016.

- [55] A. Bartlett, "Boucherot's constant-current networks and their relation to electric wave filters," Journal of the Institution of Electrical Engineers, vol. 65, no. 363, pp. 373–376, 1927.

- [56] B. Van der Pol, "A new transformation in alternating-current theory with an application to the theory of audition," *Proceedings of the Institute of Radio Engineers*, vol. 18, no. 2, pp. 220–230, 1930.

- [57] L. C. Verman, "Negative circuit constants," Proceedings of the Institute of Radio Engineers, vol. 19, no. 4, pp. 676–681, 1931.

# Chapter 2

# Research on Graphene and Graphene Transistors

Graphene, the material once believed not existing in an isolated state, has attracted a lot of attention since it was first "peeled off" from graphite by Andre Geim and Kostya Novoselov at the University of Manchester [1]. As a single-atomic-thick 2D thin film, graphene's superior properties such as high carrier mobility, high thermal conductivity and the ambipolar transfer characteristic make it attractive for electronic applications. As predicted in Moore's low, the number of transistors in an digital integrated circuit doubles approximately every two years, leading to an annual 25% reduction in the cost of a transistor on the chip [2]. Behind this great success is the continuous scaling of silicon metal-oxide-semiconductor field-effect transistor (MOSFET). So far, the Si MOSFETs have been successfully mass-produced with sub-10 nm gate length. Further scaling the gate length of Si MOSFET, the parameter fluctuations in the fabrication of identical transistors, short-channel effects and dominating parasitic effects will appear and degrade the device performance. Therefore, engineers and scientists are pursuing new materials as well as innovative device concepts, looking forward to extending the life of Moore's law and ensuring the continuation of semiconductor industry. Meanwhile, in another

subset area of semiconductor electronics: radio-frequency (RF) electronics, new materials with high carrier mobilities are strongly desired for high frequency devices operating at the untapped terahertz gap (0.3-3 THz). Currently, the organic field-effect transistors exhibit low carrier mobility that are not suitable for high-frequency applications. The III-V compound semiconductor based devices have demonstrated carrier mobility exceeding 10,000 cm<sup>2</sup>/V·s and are widely used for high-frequency circuit designs. In addition, the devices made of compound semiconductor like GaAs can also operate at higher temperature and provide lower thermal noise compared with the silicon-based devices. However, the high cost and complicated fabrication process have limited their application in those areas where silicon cannot be used. Hence, graphene, with CMOS-compatible process and remarkable carrier mobilities far beyond that of III-V compound semiconductors, immediately attracts the attention of researchers worldwide. Some of them believe graphene could be used for transistors beyond the scaling limit of silicon devices and hence extend the life of Moore's law.

# 2.1 Properties of Graphene

More than eighty years ago, 2D materials with atomic thickness were considered as thermodynamically unstable due to large thermal fluctuations that force bonded atoms to fall apart [3, 4]. Therefore, for a long time in history, the existence of 2D materials like graphene was theoretically denied. With the discovery of graphene in 2004 this theory was eventually disapproved, bringing a great deal of attention to the emerging 2D materials. Graphene is a single-atom-thick graphite layer with sp<sup>2</sup>-hybridized carbon atoms bonded in hexagonal lattice structure as shown in Fig. 1 (a). Hanns-Peter Boehm named it by combining graphite and the suffix of alkene (i.e. -ene) for the description of monolayer graphite in 1987 [5]. As the thinnest and lightest material known so far, graphene is nearly optical transparent with high thermal conductivity. The electron mobility of graphene at room temperature is significantly higher than carbon nanotube

or monocrystalline silicon, making it a candidate for the development of next generation high speed transistor. Graphene also has the lowest room-temperature resistivity known  $(1.0 \times 10^{-6} \,\Omega \cdot \text{cm})$  [6] and has been used as electrode material in solar cells [7] and touch screens [8]. In this section, the properties of graphene are briefly introduced.

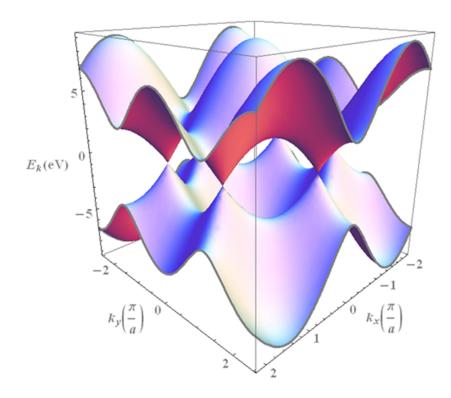

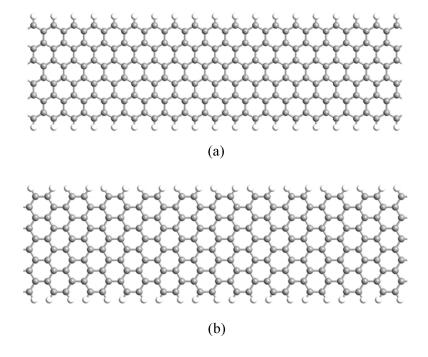

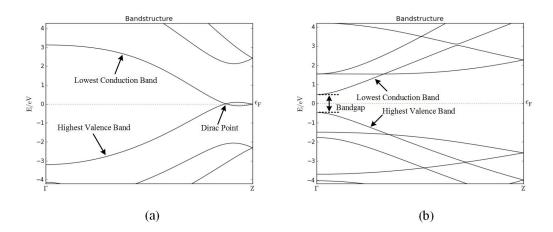

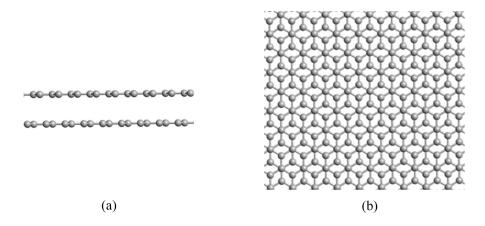

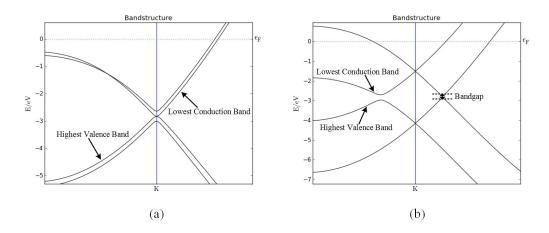

# 2.1.1 Electronic Property

Graphene is a semiconductor with zero bandgap between its valence and conduction band. Thus, it is also known as a semi-metal. The bandstructure of graphene calculated with Mathematica is shown in Fig. 2.1. The conduction and valence bands coincide at the Dirac point, resulting in the zero bandgap. By reducing the width of graphene to nanometer scale, it is possible to introduce a bandgap in graphene nanoribbons (GNRs) due to the quantum confinement effect [9]. Generally, there are two types of GNR named zigzag and armchair GNR as shown in Fig. 2.2(a) and (b), respectively. The zigzag GNR has zero bandgap regardless of the ribbon width while the later one has widthdependent non-zero bandgap, as shown in Fig. 2.3(a) and (b), respectively. In addition, a bandgap can also be achieved by inducing a perpendicular electric field to Bernal-stacked bilayer graphene [10], as shown in Fig. 2.4. The bandgap generation of graphene is very important in the development of graphene-based devices. At room temperature, the carrier mobility of suspended graphene is mainly limited by the acoustic electron-phonon scattering [12, 13]. The intrinsic room-temperature mobility up to 200,000 cm<sup>2</sup>/V · s for the electron density of  $10^{11}$  cm<sup>2</sup> has been predicted in [12], corresponding to a resistivity of  $1.0 \times 10^{-6} \,\Omega \cdot \text{cm}$ . This is lower than that of silver  $(1.59 \times 10^{-6} \,\Omega \cdot \text{cm})$ , which has the lowest room-temperature resistivity before the discovery of graphene. The carrier density of graphene is electrostatically tunable and the electrical conductivity, which describes the ability of graphene for current conduction, reaches a minima on the order of  $4e^2/h$ . Here, e is the elementary charge and h is Plancks constant.

Graphene also exhibits anomalous quantum Hall effect under strong magnetic fields

Figure 2.1: Bandstructure of graphene calculated with Mathematica.

Figure 2.2: GNR with hydrogenated (a) zigzag and (b) armchair edges.

Figure 2.3: Bandstructure of GNR with (a) zigzag and (b) armchair edges. Calculated with ATK [11].

Figure 2.4: Bernal-stacked bilayer graphene (a) cross-sectional view and (b) top view.

even at the room temperature. The quantized Hall conductivity of graphene is given as

$$\sigma_{xy} = \pm 4\left(N + \frac{1}{2}\right) \frac{e^2}{h} \tag{2.1}$$

where N is the Landau level. The coefficient 4 is because of the double valley and double spin degeneracies. It is noted that electrons and holes seem to have nearly identical mobility in suspended graphene, which is different from what has been observed in silicon [14]. When the graphene is transferred onto a  $SiO_2$  substrate, the extrinsic surface phonon scattering introduced by  $SiO_2$  significantly decreases its maximum achievable room-temperature mobility to  $40,000 \text{ cm}^2/\text{V} \cdot \text{s}$  [12]. It has been observed that the

mobility of graphene on  $SiO_2$  substrate decreases with the increase of temperature due to the thermal effects [12, 15, 16]. The theoretical limit of carrier mobility on  $SiO_2$  can be approached by reducing the impurity scattering. Consequently, the mobility can further approach the intrinsic room-temperature limit (i.e.  $200,000 \text{ cm}^2/\text{V} \cdot \text{s}$ ) by the use of alternative substrates such as h-BN [17, 18].

# 2.1.2 Optical Property

In the previous section, it is shown that the valence and conduction band of graphene meet each other at the Dirac point, resulting in the conical bandstructure and zero bandgap. This unique bandstructure of graphene also introduces interesting optical properties to this magic material. It has been reported that suspended graphene absorbs 2.3% optical light in vacuum [19]. As an atomic-thick material, this unexpected opacity is attributed to the unique electronic structure of graphene [20]. In addition, Graphene also exhibits saturable absorption above certain threshold optical intensity from visible to near-infrared region[21]. This saturable absorption of graphene is also observed at microwave and THz bands due to zero-bandgap-induced broadband absorption [21]. The gate-tunable photoresponse of graphene has also been experimentally demonstrated from ultraviolet to visible regime [22], indicating wideband application of graphene-based optical devices.

#### 2.1.3 Other Properties

The bond length between carbon atoms in graphene is approximately 1.42 Å and the interlayer spacing between graphite layers is 3.35 Å [23, 24]. Although graphene is single atom thick, it is harder than diamond and its strength is 200 times that of steel. Actually graphene is the strongest material ever known, demonstrating a Youngs modulus of 1 TPa [25]. Besides, an early work also reveals that suspended graphene exhibits an extraordinary room-temperature thermal conductivity of  $\sim 5300 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$  [26]. This

is significantly higher than that of pyrolytic graphite ( $\sim 2000 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$ ) and carbon nanotube ( $\sim 3500 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$ ). Later, due to the uncertainties in the measurement and differences in the quality of graphene, [27–30] suggest the practical thermal conductivity of suspended graphene should be between  $1500 \sim 2500 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$ . What is worse, when graphene is transferred onto a substrate, the interaction between graphene and substrate drastically reduces the phonon lifetime and suppresses the contribution of flexural phonons to the heat conductivity. As a result, the thermal conductivity is further reduced to  $500 \sim 600 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$  [31, 32].

# 2.2 Graphene Preparations

Typically, there are two types of technology for graphene synthesis namely top-down and bottom-up methods. The first technology is called top-down because it involves obtaining single layer graphene sheets by breaking apart stacked graphene layers (i.e. graphite). The 'scotch tape' approach that Geim and Novoselov used to achieve their early graphene samples belongs to this technology [1]. As we know, graphite consists of staked graphene layers, hence, the peeling of graphene only requires to overcome the weak van der Waals forces between graphene layers [33]. That means preventing possible damage and re-agglomeration of the exfoliated sheets are the main challenges for this approach. Artificial graphite produced under high temperature [34] is not suitable for graphene exfoliation due to the poor graphitisation and non-uniform morphologies. Hence, several bottom-up methods have been developed to achieve graphene samples from other carbon sources. Unlike the top-down approach, bottom-up methods utilise carbon atoms to build the graphene sheet. The carbon atoms can be provided by various sources such as CH<sub>4</sub>, C<sub>2</sub>H<sub>2</sub> and C<sub>2</sub>H<sub>4</sub>. To achieve high levels of graphitisation, in the bottom-up approach, high temperature is usually preferred which guarantees the sample quality. The graphene synthesised with bottom-up method usually contains more defects than that achieved with top-down methods. However, relatively large-area graphene

sheets can be grown with the bottom-up method when proper substrate materials such as copper are used.

## 2.2.1 Top-down Methods

Top-down methods include mechanical exfoliation, graphite intercalation, nanotube slicing, pyrolysis method, etc. In this section, the most commonly used top-down methods are introduced and a discussion of their advantages and drawbacks is also presented.

#### 2.2.1.1 Mechanical Exfoliation