# A study of the sensitivity of switched-current wave analog filters to mismatching and clock-feedthrough errors

Alberto Yúfera<sup>†\*</sup>, Adoración Rueda<sup>\*</sup> and José Luis Huertas<sup>\*</sup> <sup>†</sup> Dpto. de Tecnología Electrónica, Universidad de Sevilla. <sup>\*</sup>Dpto. de Diseño de Circuitos Analógicos, Centro Nacional de Microelectrónica, Edificio CICA, Avda. Reina Mercedes s/n, 41012-Sevilla Tf: (95) 462 38 11 yufera@cnm.us.es

#### ABSTRACT

The influence of the main source of errors in Switched-Current (SI) filters over the performance of Wave Analog Filters (WAF) is evaluated. Models of mismatching and clock-feedthrough (CF) are deduced for basic building blocks, and applied to study the sensitivity of a third-order filter. Monte Carlo simulations performed using a behavior simulator prove that CF are dominant over mismatching effects.

# INTRODUCTION

Two different approaches have been explored for switched-current (SI) low-sensitivity filter realizations; both simulate passive LC ladder structures. One follows the wellknown synthesis methodologies applied for switched-capacitor filters, hence requiring SI integrators as building blocks [1-3]. The other is based on simulating Wave Digital Filter (WDF) structures [4-6].

In addition to excellent passband sensitivity properties, WAFs have two inherent advantages. They are based on the bilinear mapping and involve very regular and simple circuit elements. We have already proved the feasibility of this approach, obtaining SI WAF prototypes [4-6].

An important property of SI WAF is that the range of current gain values in any adaptor does not greatly differ between one filter function and other.

This paper deals with the study of mismatching and CF induced errors, that, will allow us to derive design rules for minimizing their influence in WAF. A statistic model is proposed for the study of random mismatching errors in SI implementations of WAF (systematic mismatching errors are assumed cancelled by an appropriated design of the basic cells), and a statistic sensitivity measure is carried out for a low-pass filter using this model and Monte Carlo simulations. On the other hand, the sensitivity to CF induced error is studied using a simple model for charge injection in the basic memory cell. All is made at a behavioral level oriented to a rapid design validation before going to the physical realization, but with models which are related to this physical realization. The developed models have been introduced in WAVER, an in-house program we use to design SI wave analog filters. The simulation results obtained for a low-pass third-order filter will be presented.

#### **REALIZATION OF SWITCHED-CURRENT WAF**

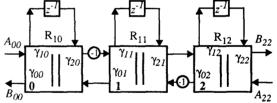

Let us consider the implementation of a third order lowpass filter. The Wave Model shown in Figure 1 is one of the models we can use to realize the filter. The signals  $A_{ij}$  and  $B_{ij}$  represent the incident and reflected wave signals in the j

Figure 1: Third order low-pass wave filter.

adaptor. The coefficients  $\gamma_{ij}$  must be determined taking into account the following relationships

$$\sum_{i=0}^{2} \gamma_{ij} = 2 , \qquad R_{0j} \gamma_{0j} = R_{1j} \gamma_{1j} = R_{2j} \gamma_{2j}$$

(1)

where the port resistance  $R_{20}$  and  $R_{21}$  can have any value and the other resistances are obtained from the LC reference filter and the sampling frequency [4].

Equations for the 3-port parallel adaptor operation are

$$B_j = A_N - A_j$$

,  $A_N = \gamma_0 A_0 + \gamma_1 A_1 + \gamma_2 A_2$  (2)

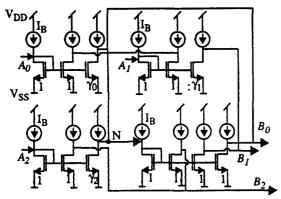

with j=0,1,2. Switched-current implementation of the filter consists of the interconnection of current mode adaptors and unit delay cells. Note that any reflection coefficient  $\gamma_{ij}$  is realized as a current mirror gain. The schematic in Figure 2 is

a simplified version. Using high-swing cascode current mirror (Fig. 3) input-output coupling impedances effects can be reduced.

Figure 2: Simplified schematic for a 3-port parallel adaptor.

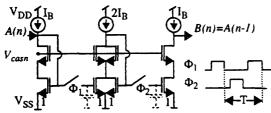

Figure 3: Simplified schematic for a delay cell.

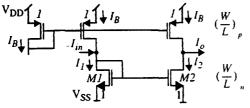

Figure 4: Basic current mirror.

## MODEL FOR MISMATCHING ERRORS

To study transistor mismatch effects in the operation of the proposed adaptors we have used the model given in [7] for the random variations in current mirror gains produced by the variations in the fabrication process. For the simple current mirror in Figure 4, the relative variance in the error between the current  $I_2$  and the input  $I_1$  is calculated. If unit transistor cells are used, systematic error due to  $\Delta W$  and  $\Delta L$ can be reduced, leading to the expression for random mismatching errors

$$\frac{\sigma_n^2(l_2)}{l_2^2} = \frac{K_{ln}}{2W_n L_n} \cdot (\frac{1}{N_1} + \frac{1}{N_2})$$

(3)

where  $N_I$  and  $N_2$  are the number of unit cells in  $M_I$  and  $M_2$ [8]. From the technology parameters in [7], and using (W/ L)<sub>1</sub>=(60µm/10µm) and ( $V_{GSn}$ - $V_{Tn}$ )=0.6V, the error evaluated by (3) is about 0.28%. To obtain the variance in the output currents of any adaptor, we define the relative variance in the unit-gain current mirror as

$$\sigma_{n}^{\prime 2}(1) = \frac{\sigma^{2}(I_{2})}{I_{2}^{2}} = \frac{K_{In}}{W_{n}L_{n}N_{1}}$$

(4)

Regarding the ratio  $I_o/I_{in}$ , mismatching in the NMOS mirrors lead to offset and gain errors, given by

$$\sigma'^{2}_{n, off}(I_{o}) = \sigma'_{n}(1) \cdot I^{2}_{B}$$

(5)

$$\sigma'^{2}_{n \text{ sain}}(I_{\rho}) = \sigma'^{2}_{n}(1) \tag{6}$$

Errors from the PMOS bias transistor generate only offset in  $I_o$ ,

$$\sigma'^{2}_{p, off}(I_{o}) = 2\sigma'^{2}_{p}(1)I^{2}_{B}$$

(7)

where  $\sigma'_{p}(1)$  has been define as (4) for a PMOS current mirror. Taking (W/L)<sub>p</sub>=(100 $\mu$ m/10 $\mu$ m) and ( $V_{GSp}$ - $V_{Tp}$ )=0.5V, the error evaluated by (5) for PMOS transistor is about 0.3%. Global mismatching error contribution can be obtained adding equations (5) to (7).

The variance associated to the actual realization of each filter component (delay cells and adaptors) can be evaluated as follows. First, determine the number of current mirrors and their respective gains in the path from each input to one output. Second, assuming the mismatching error in each mirror modelled as a gaussian distributions which is not correlated with the error in other mirror, add all errors in each input-output path.

Using this procedure, the gain and offset variance in the cascade of two unity-gain current mirrors are given by

$$\sigma_{gain}^{\prime 2}(2) = 2\sigma_{n}^{\prime 2}(1)$$

(8)

$$\sigma_{off}^2(2) = (4\sigma_p^{\prime 2}(1) + 2\sigma_n^{\prime 2}(1)) \cdot I_B^2$$

(9)

which can be used to evaluate the error in unit delay cells,  $\sigma^2(z^{-1}) = \sigma^2(2)$ . For the case above (8) and (9) give a 0.4% gain error and 73nA random offset.

The statistic model corresponding to the 3-port parallel in Fig 2 is obtained in the same way, resulting in a gain variance matrix error with entries given as,

$$\left[\sigma_{ij}^{\prime 2}\right]_{gain} = \frac{\sigma_{n}^{\prime 2}(1)}{2} \cdot \begin{pmatrix} 5+1/\gamma_{i} & if \quad i=j\\ 3+1/\gamma_{j} & if \quad i\neq j \end{pmatrix}$$

(10)

From (10) it can be seen that mismatching errors are more important when  $\gamma$  approaches zero. This effect can be taken into account in the design phase by implementing low-valued coefficients with an arrangement of current mirrors whose total gain is given by  $(1+\gamma)-1$ . Thus, alternative matrix entries of  $(9+1/(1+\gamma))$  or  $(7+1/(1+\gamma))$  appear. This solutions means a penalty area. As illustration, let us consider the matrix variance corresponding to the first adaptor in Figure 1(b), for the particular values  $\gamma_0=0.3 \gamma_1=1.187$  and  $\gamma_2=0.513$ , form (10) we obtain

$$[\sigma'_{ij}^2]_{gain} = \begin{bmatrix} 0.57 & 0.39 & 0.44 \\ 0.50 & 0.48 & 0.44 \\ 0.50 & 0.39 & 0.52 \end{bmatrix}$$

(11)

which means that the maximum standard deviation corresponds to the  $(\gamma_0-1)$  gain, and it is equal to 0.57%. The matrix for output offset errors is given by,

$$[\sigma_{j}^{\prime 2}]_{off} = \frac{4\sigma_{p}^{\prime 2}(1) + 2\sigma_{n}^{\prime 2}(1)}{2}I^{2}{}_{B}\left(7 + \sum_{j=0}^{2}\frac{1}{\gamma_{j}}\right), \forall j \quad (12)$$

As before, for small coefficients realized as  $(1+\gamma)-1$ , the number 7 and  $\gamma$  in (12) must be changed for (7+4) and (1+ $\gamma$ ), respectively. The offset for the example presented is 186nA. The same can be done for all adaptors in the filter.

#### **CLOCK-FEEDTHROUGH INDUCED ERRORS**

Clock-feedthrough in current track-and-hold (T/H) can be modelled by an error voltage on the data holding node. It causes DC offset, gain error and distortion. Although additional circuitry for cancellation of the CF errors is always used, total cancellation is not reached in practice. We have introduced a simple analytical model to study the effects of this error in the global performance of the filter. Assuming a voltage error  $\Delta v_f$  in the holding node, the equation including CF effects will be for the unit delay cells

$$\Delta I_o = \Theta\left(\sqrt{I_B + I_{in}} - \sqrt{(I_B - I_{in}) - \frac{\Theta^2}{4} - \Theta\sqrt{I_B + I_{in}}}(13)\right)$$

where  $\Delta I_o$  represents the output current error evaluated at the *nT* instant,  $I_{in}$  the input current at the (n-1)T instant and  $\Theta = \sqrt{\beta_n \Delta v_f}$ . In order to find a linear model for CF error, (13) can be approximated as

$$I_o = b_0 + b_1 \cdot I_{in} + b_2 \cdot I_{in}^2 + \dots$$

(14)

where only the two first terms in RHS are taking into account for a linear model.

#### SIMULATION RESULTS

Errors can be introduced in numerical simulations performed by WAVER using the computation expressed as  $I_o = I_{in} (\gamma^{o} + \Delta \gamma^{o}) + I_{off}$ , in which the ideal output,  $\gamma^{o}I_{in}$ , is modified by an error gain  $\Delta \gamma^{o}$  and added to an offset term,  $I_{off}$ . We have performed a Monte Carlo analysis of the filter in Figure 1 with the nominal adaptor coefficients given in Table I corresponding to a normalized cutoff-frequency of 0.09577 and a passband ripple of 0.2 dB, using  $I_B = IO\mu A$ and  $IO\mu m/IO\mu m$  unit transistors. Mismatching errors are randomly generated using the standard deviations derived from (8) and (9) for the delay cells, and from (10) and (12) for the parallel adaptors. CF errors are included given a value to  $\Delta v_f$ . For the characterization of the filter, we have measured the parameters defined in Table II.

| Table I: | Three-port | adaptor | coefficients |

|----------|------------|---------|--------------|

|----------|------------|---------|--------------|

| Y00,Y22 | Y10,Y12 | Y20,Y02 | Y01, Y21 | Υ <u>11</u> |

|---------|---------|---------|----------|-------------|

| 0.3     | 1.187   | 0.513   | 0.239    | 1.521       |

Table II: Statistical filter parameters definition. ( $\epsilon$ ) ripple, ( $\omega_0$ ) cutoff-frequency, (H(0)) DC level and (H(0.5)) Niquist level.

| ٤ <sub>mean</sub>       | $\frac{1}{N}\sum_{n=1,\ldots,N} \left(H_{max} - H_{min}\right)_n$                                                                |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| ε <sub>std</sub>        | $\frac{1}{N}\sum_{n=1,\ldots,N} \left(\varepsilon_n^2 - \varepsilon_{mean}^2\right)^{1/2} \times \frac{100}{\varepsilon_{mean}}$ |

| Womcan                  | $\frac{1}{N}\sum_{n=1,\ldots,N}\omega_{o_n}$                                                                                     |

| ω <sub>osid</sub>       | $\frac{1}{N}\sum_{n=1,,N} (\omega_n^2 - \omega_{omean}^2))^{1/2} \times \frac{100}{\omega_{omean}}$                              |

| H(0) <sub>mean</sub>    | $\frac{1}{N}\sum_{n=1,\ldots,N}H(0)_n$                                                                                           |

| 11(0.5) <sub>mean</sub> | $\frac{1}{N}\sum_{n=1,\dots,N}H(0.5)$                                                                                            |

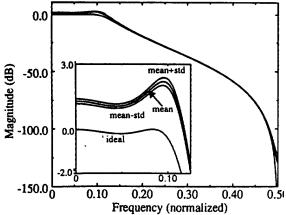

Figure 5 shows the ideal, mean and mean± $\sigma$  frequency responses obtained with N=100 and  $\Delta v_f$ =5mV. The results obtained for  $\Delta v_f$  = 0, 1 and 5mV are summarized in Table III. It can be note that the errors in the ripple and cutoff-frequency mean values due to mismatching ( $\Delta v_f$  = 0) are 12.2% and 0.15%, respectively, while the CF induced errors increase strongly these percentages (66.1% and 4.41% for  $\Delta v_f$  = 1mV, 467.2% and 16.2% for  $\Delta v_f$  = 5mV).

Table III: Three-port adaptor coefficients.

| $\Delta v_f (mV)$      | 0       | 1       | 5        |

|------------------------|---------|---------|----------|

| ε <sub>mean</sub> [dB] | 0.2244  | 0.3322  | 1.1344   |

| ε <sub>sid</sub> [%]   | 11.69   | 16.27   | 8.40     |

| ω <sub>omean</sub>     | 0.09566 | 0.10000 | 0.111291 |

| ω <sub>οsid</sub> [%]  | 1.8443  | 1.5434  | 0.8075   |

| $H(0)_{mean}[dB]$      | 0.0109  | 0.26169 | 1.3061   |

| $H(0.5)_{mean}[dB]$    | -149.9  | -149.7  | -125.2   |

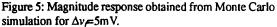

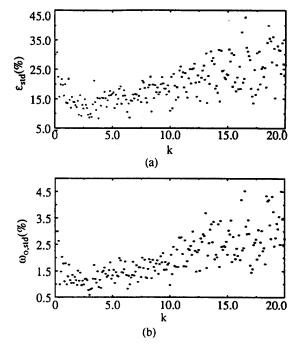

Figure 6(a) shows the effects of positive and negative gate voltage increment in the T/H cells. The corresponding experimental results are shown in Figure 6(b), which were obtained modifying the clock signal level. The displacement in the experimental filter function correspond to be the effects of the CF of opposite sign.

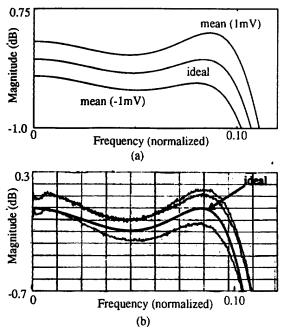

To exploit the freedom in the choice of adaptor coefficients inherent to WAF [6], we have also measured the effects of the ratio  $k = \gamma_{20}/\gamma_{00}$  values on the error in the ripple and the cutoff frequency relative to the nominal ones. The obtained results are illustrated in Figures 7 (a) and (b), Note that there exist values of k which produce low deviations in the filter characteristics.

Figure 6: (a) Pass-Band magnitude response obtained from Monte Carlo simulation with  $\Delta v_f = \pm 1 \text{mV}$ . (b) Experimental results for different clock signal levels.

# CONCLUSIONS

The sensitivity of SI WAF filters to the main sources of errors has been evaluated using operational models and Monte Carlo simulations. The results are close to the experimental measurements and prove that CF effects are dominants. Future work would be focused on including non-linear terms in order to obtain a whole filter characterization.

Figure 7: Evolution of (a) ripple and (b) cutoff frequency errors for different values of  $k=\gamma_{20}/\gamma_{00}$  and  $\Delta v_f=1$ mV.

## REFERENCES

- J. B. Hughes, I. C. Macbeth and D. M. Patullo: "Switched Currents Filters". *Proceedings IEE* VOL. 137, Pt. G, N° 2, pp. 156-162, Apr. 1990.

- [2] T. S. Fiez., D. J. Allstot, "CMOS Switched-Current Ladder Filters", *IEEE JSSC*, VOL SC-25, N°6, pp. 1360-1367, Dec. 1990

- [3] T. S. Fiez., D. J. Allstot: "Switched-Current Circuit Design Issues". *IEEE JSSC*, VOL SC-26, N°3, pp. 192-202, Mar. 1991.

- [4] A. Rueda, A. Yúfera and J.L. Huertas: "Wave Analog Filters Using Switched-Current Techniques". *Electro*nics Letters, VOL-27, N°16, pp.1482-1483, Aug. 1991.

- [5] A. Yúfera, A. Rueda, J. L. Huertas: "Switched-Current Wave Analog Filters". ISCAS'92, pp.859-862. 1992.

- [6] A. Yúfera, A. Rueda, J. L. Huertas, "Programmable Switched-Current Wave Analog Filters", ESS-CIRC'93, pp.174-177. Aug.1993

- [7] M. J. M. Pelgrom, A.J. Duinmaijer, A. P. G. Welbers, "Matching Properties of MOS Transistors", *IEEE JSSC*, VOL. SC-24, N.5, pp. 1433-1444, Oct. 1989.

- [8] J. B. Highes and W. Redman-White: "Switched-Current Limitations and Non-Ideal Behaviour". Chapter 4 in SWITCHED-CURRENTS: an analogue technique for digital technology, Peter Peregrinus Ltd., Eds. C. Toumazou, J. B. Hughes and N. Battersby, 1993.