### UNIVERSITÁ DEGLI STUDI DI UDINE

**Dipartimento di Ingegneria Elettrica, Gestionale e Meccanica** Corso di Dottorato in Ingegneria Industriale e dell'Informazione

Institut de Microelectronique, Electromagnetisme et Photonique Ecole Doctorale Electronique, Electrotechnique, Automatique, Telecomunications, Signal (EEATS)

Tesi di Dottorato di Ricerca

## Impact of the technology boosters on the MOSFET performance

#### **Relatori:**

Prof. Luca Selmi Gerard Ghibaudo

#### **Commission esaminatrice:**

Prof. Roberto Rinaldo Prof. Wim Magnus Prof. Andreas Schenk Dr. Gerard Ghibaudo Prof. Luca Selmi Prof. Pierpaolo Palestri Prof. Raphael Clerc **Dottorando:**

Paolo Toniutti

Anno Accademico 2011-12

#### Abstract

The understanding of the charge transport in nano-scale CMOS device is a very challenging issue that requires a physics-based modeling approach. In this respect, commercial T-CAD simulators have been shown evident limitations in the modeling of ultra-scaled devices, due to the strong off-equilibrium non-local transport that takes place in this kind of devices. On the other hand, full quantum approaches would in principle allow to correctly treat the problem, but their complexity and the difficult inclusion of many important scattering mechanisms limit their use to particular cases, decreasing their effectiveness in being a general tool for the comprehension of all the various aspects of the modeling problem. In this thesis we use a Multi Subband Monte Carlo simulation framework to assess the effects of some of the mostly used techniques to overcome the performances of the conventional ultra-scaled MOSFETs. This approach allows for a better understanding of the charge transport in short channel devices, using a software tool that remains relatively easy to use by the engineering community. The following technology boosters will be addressed: multi-gate structures, high-k dielectrics, strained silicon and germanium channels.

The modeling of screening in non-conventional structures such as double gate SOI and FinFETs is not trivial. In this respect, we analyze different formulations of the screening dielectric function approach in order to establish the correct methodology to properly model this physical mechanism in multi-gate MOSFETs.

Concerning the modeling of the high-k dielectric effects, we assess the effectiveness of various scattering mechanisms in degrading the electron and hole mobility. We also propose original models to explain the mobility degradation found experimentally. Finally, we analyze the influence of the high-k dielectrics on the ON-state current in short channel MOSFETs.

Concerning the alternative high-mobility channel materials, we perform Monte Carlo simulations of germanium and strained germanium channels to compare their performances with respect to silicon and strained silicon materials.

Finally, Monte Carlo simulations are used to analyze, validate and improve an existing technique used to experimentally extract the limiting velocity in short channel MOSFETs, that is useful to assess the real improvement provided by the alternative channel materials.

## Contents

| 1 | Intr | oductio       | n                                                                          | 1  |

|---|------|---------------|----------------------------------------------------------------------------|----|

|   | 1.1  | Scalin        | g of the MOSFET                                                            | 2  |

|   |      | 1.1.1         | The scaling scenario                                                       | 2  |

|   |      | 1.1.2         | Problems related to the fabrication of ultra short MOSFETs                 | 3  |

|   |      | 1.1.3         | Overview of the technology boosters                                        | 3  |

|   |      | 1.1.4         | The state of the art                                                       | 4  |

|   | 1.2  | $\mathcal{C}$ | k dielectrics                                                              | 4  |

|   |      | 1.2.1         | The gate leakage current problem                                           | 5  |

|   |      | 1.2.2         | Benefit of using high- $k$ dielectrics $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 6  |

|   |      | 1.2.3         | Mobility reduction in MOSFETs with high- $k$ in the gate                   |    |

|   |      |               | stack                                                                      | 7  |

|   |      | 1.2.4         | Possible causes of mobility degradation in high- $k$ stacks .              | 9  |

|   | 1.3  |               | gate structures                                                            | 10 |

|   |      | 1.3.1         | Benefits of using multi gate structures                                    | 10 |

|   |      | 1.3.2         | Problems related to the modeling of multi gate structures .                | 11 |

|   | 1.4  |               | ative channel materials                                                    | 12 |

|   |      | 1.4.1         | Benefits of using alternative materials                                    | 12 |

|   |      | 1.4.2         | Strained silicon, germanium and strained germanium mod-                    |    |

|   |      |               | eling                                                                      | 13 |

|   | 1.5  | Evalua        | ation of the effect of technology boosters in real devices                 | 14 |

| 2 | The  | semi-cl       | lassical approach and the Boltzmann transport equation                     | 15 |

|   | 2.1  | The B         | oltzmann transport equation                                                | 16 |

|   |      | 2.1.1         | Validity of the Boltzmann transport equation                               | 16 |

|   | 2.2  | The D         | rift - Diffusion model                                                     | 17 |

|   |      | 2.2.1         | The saturation velocity                                                    | 19 |

|   |      | 2.2.2         | Analytic expressions for the currents                                      | 19 |

|   |      | 2.2.3         | Limits of validity of the Drift - Diffusion model                          | 20 |

|   | 2.3  | The ba        | allistic transport regime                                                  | 21 |

|   |      | 2.3.1         | Basics on the ballistic model                                              | 21 |

|   |      | 2.3.2         | Analytic expressions for the current                                       | 23 |

|   |      | 2.3.3         | Considerations about the ballistic transport model                         | 24 |

|   | 2.4  | The qu        | uasi ballistic transport regime                                            | 24 |

|   |      | 2.4.1   | Basics of the quasi-ballistic model                  | 24 |

|---|------|---------|------------------------------------------------------|----|

|   |      | 2.4.2   | Analytic expressions for the current                 | 25 |

|   |      | 2.4.3   | Models for the back-scattering coefficient           | 26 |

|   | 2.5  | Exact   | solution of the BTE: the Monte Carlo method          | 28 |

|   |      | 2.5.1   | Basics of the Monte Carlo method                     | 28 |

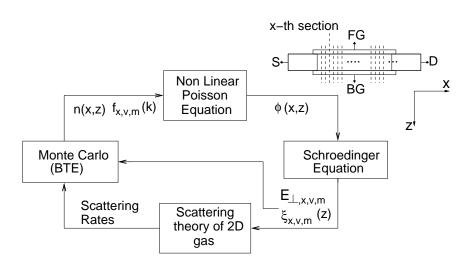

| 3 | The  | Multi S | Subband Monte Carlo simulator                        | 31 |

|   | 3.1  | The ca  | urrier transport framework                           | 32 |

|   |      | 3.1.1   | Flow chart                                           | 32 |

|   |      | 3.1.2   | The quantization effect                              | 33 |

|   |      | 3.1.3   | 2-D multi-subband transport                          | 34 |

|   |      | 3.1.4   | The effective mass approximation for the n-MOSFET    | 35 |

|   |      | 3.1.5   | The semi-analytical model for the p-MOSFET           | 37 |

|   | 3.2  | Scatter | ring mechanisms for conventional MOSFET devices      | 38 |

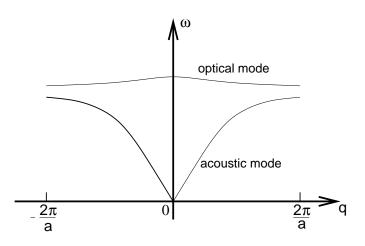

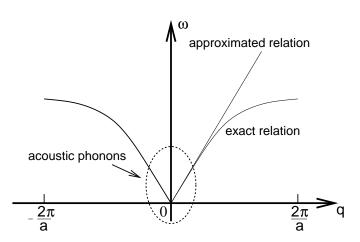

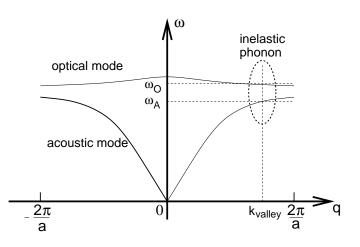

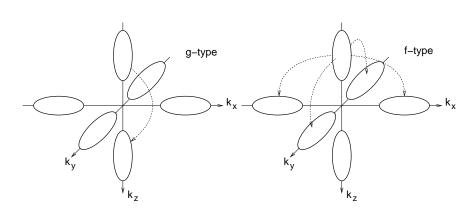

|   |      | 3.2.1   | Phonon scattering                                    | 39 |

|   |      | 3.2.2   | Ionized impurities scattering                        | 42 |

|   |      | 3.2.3   | Surface roughness                                    | 42 |

|   |      | 3.2.4   | The screening effect                                 | 44 |

|   | 3.3  | Calibra | ation of the simulator                               | 45 |

| 4 | Scre | ening i | n multi-gate structures                              | 49 |

|   | 4.1  | Introdu | uction                                               | 50 |

|   | 4.2  | Dielec  | tric function for the screening in MOSFETs           | 52 |

|   |      | 4.2.1   | Tensorial dielectric function approach               | 52 |

|   |      | 4.2.2   | Scalar dielectric function approach                  | 54 |

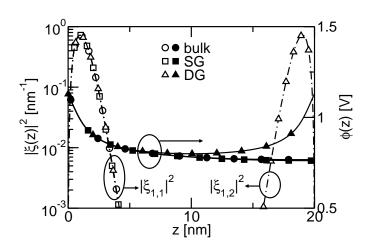

|   | 4.3  | Validit | ty of the SDF model for surface roughness scattering | 55 |

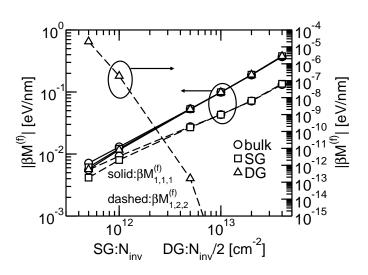

|   |      | 4.3.1   | Unscreened matrix elements                           | 57 |

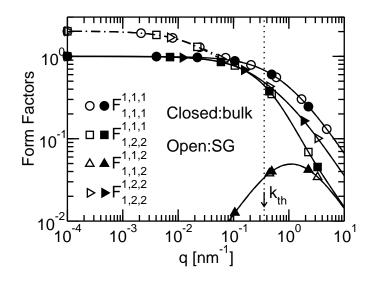

|   |      | 4.3.2   | Screening in bulk and SOI structures                 | 58 |

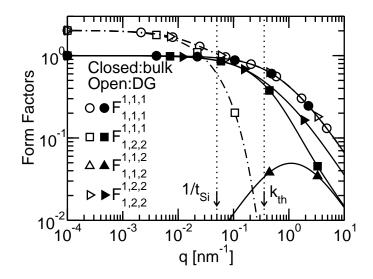

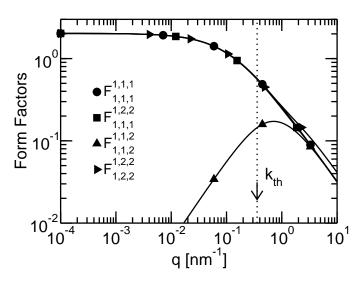

|   |      | 4.3.3   | Form factors                                         | 58 |

|   | 4.4  | Explai  | ning the artifacts in the mobility calculations      | 60 |

|   |      | 4.4.1   | Bulk and SG-SOI devices                              | 61 |

|   |      | 4.4.2   | DG-SOI devices                                       | 61 |

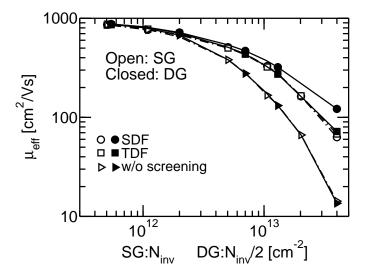

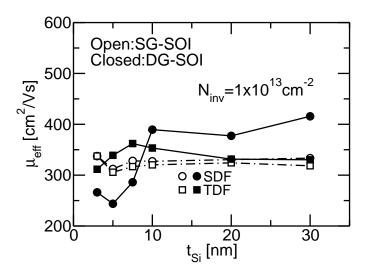

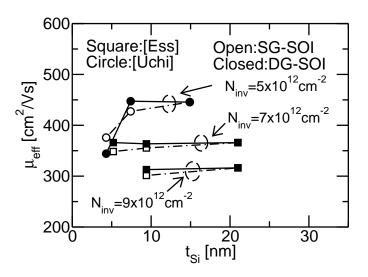

|   | 4.5  | Mobili  | ity simulation results                               | 63 |

|   |      | 4.5.1   | SG-SOI vs. DG-SOI using the TDF approach             | 64 |

|   |      | 4.5.2   | SDF vs. TDF in the SG-SOI structure                  | 64 |

|   |      | 4.5.3   | SDF vs. TDF in the DG-SOI structure                  | 64 |

|   | 4.6  | Conclu  | usions                                               | 67 |

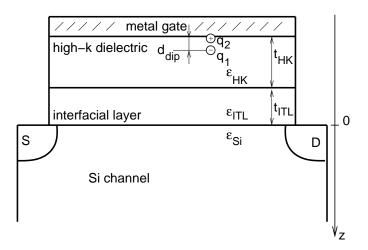

| 5 | МО   | SFETs   | with high- $k$ dielectrics                           | 69 |

|   | 5.1  |         | uction                                               | 70 |

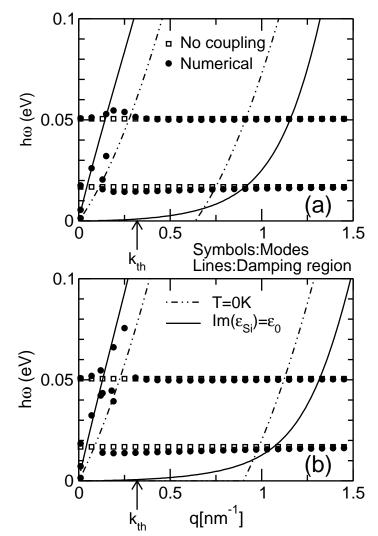

|   | 5.2  |         | ing SO phonons                                       | 71 |

|   |      | 5.2.1   | Models for SO-phonons available in literature        | 71 |

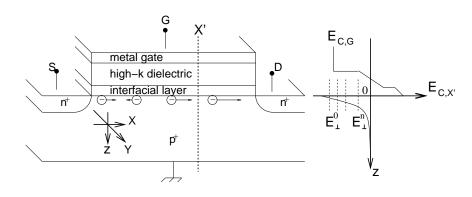

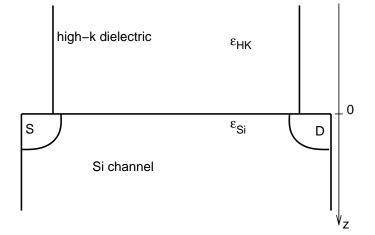

|   |      | 5.2.2   | SOph in structures without interfacial layer         | 72 |

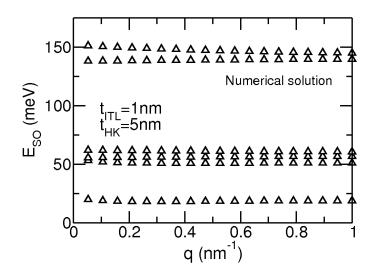

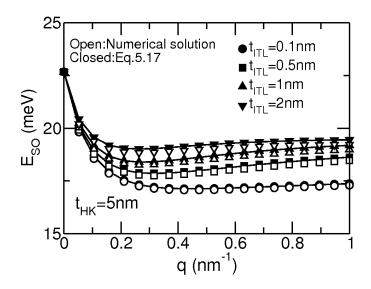

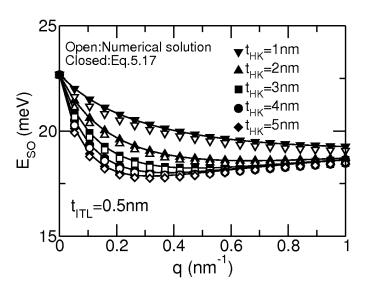

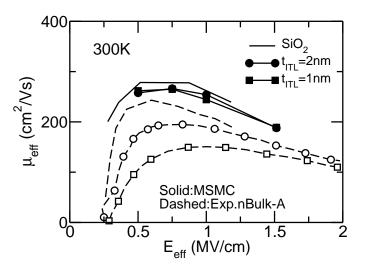

|   |      | 5.2.3   | SOph scattering in MG/HK/ITL structures              | 79 |

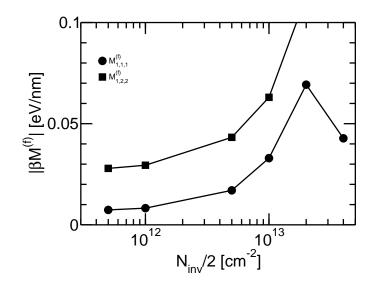

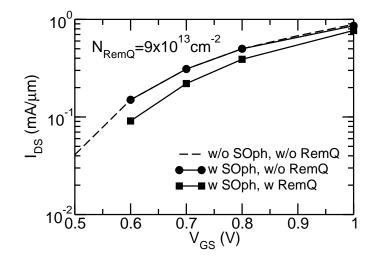

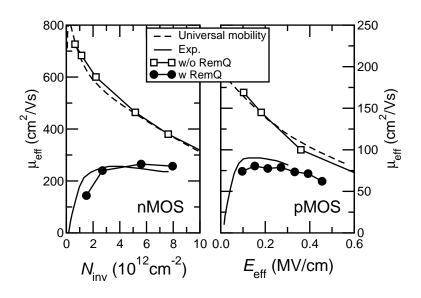

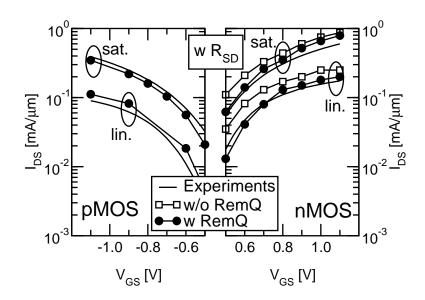

|   | 5.3                                         | Modeling RemQ scattering                                        | 82                |

|---|---------------------------------------------|-----------------------------------------------------------------|-------------------|

|   | 5.4                                         | Modeling DipQ scattering                                        | 86                |

|   | 5.5                                         | Comparison with experimental mobility data                      | 88                |

|   |                                             | 5.5.1 Calibration of the models                                 | 88                |

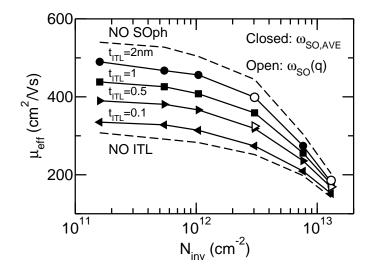

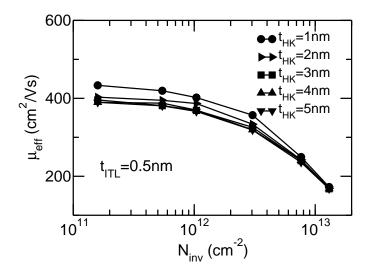

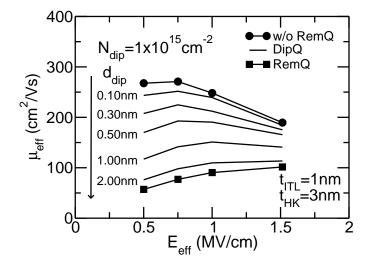

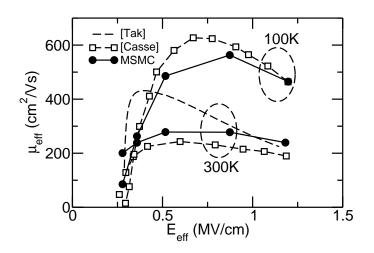

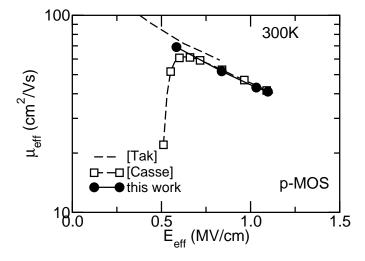

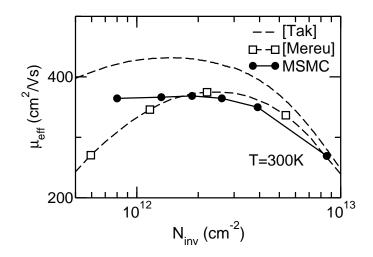

|   |                                             | 5.5.2 Effect of the SOph and RemQ scattering                    | 92                |

|   |                                             | 5.5.3 Effect of the correlation between the charges             | 99                |

|   |                                             | 5.5.4 Effect of the DipQ scattering                             | 102               |

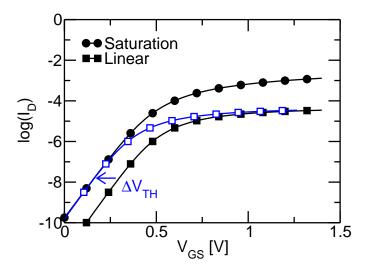

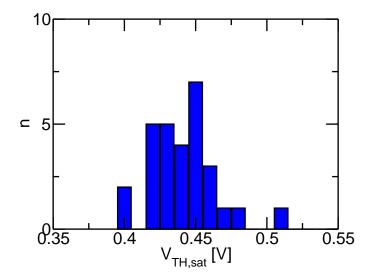

|   | 5.6                                         | Threshold voltage shift                                         | 105               |

|   |                                             | 5.6.1 Threshold voltage associated to charges at the ITL/HK in- |                   |

|   |                                             |                                                                 | 105               |

|   |                                             | I                                                               | 105               |

|   |                                             |                                                                 | 110               |

|   |                                             | 5.6.4 Dipoles at the MG/HK interface                            | 113               |

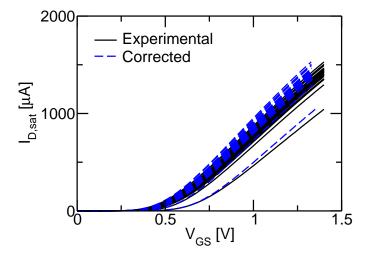

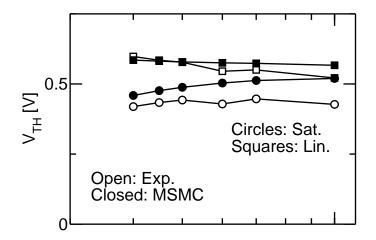

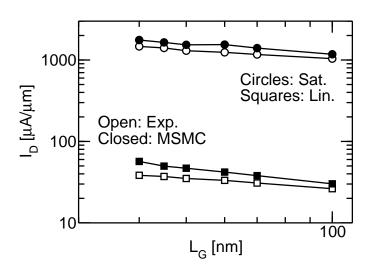

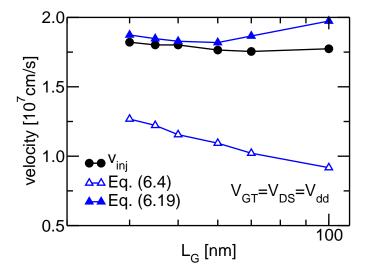

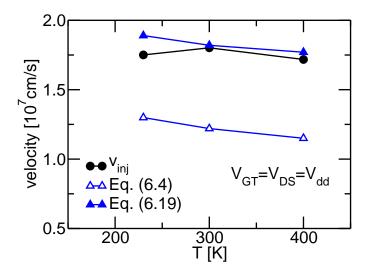

|   | 5.7                                         | 1 0                                                             | 114               |

|   |                                             |                                                                 | 114               |

|   |                                             |                                                                 | 115               |

|   | 5.8                                         | Conclusions                                                     | 117               |

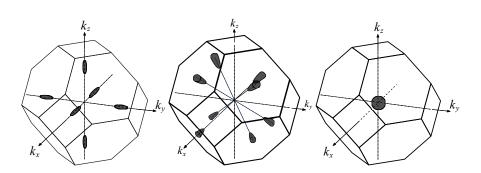

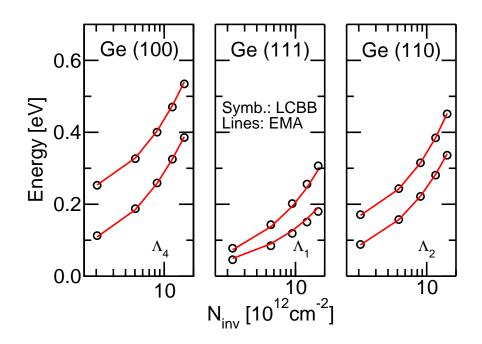

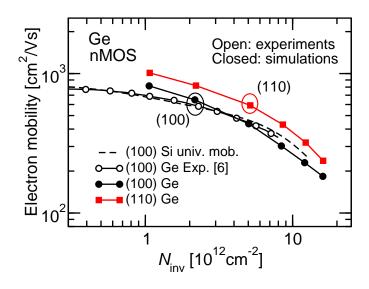

| 6 | 6 Modeling of alternative channel materials |                                                                 |                   |

|   | 6.1                                         | 0                                                               | <b>119</b><br>120 |

|   | 6.2                                         |                                                                 | 120               |

|   |                                             |                                                                 | 120               |

|   | 6.3                                         |                                                                 | 126               |

|   | 6.4                                         | Conclusions                                                     | 130               |

| 7 | Extr                                        | racting and Understanding Carrier Velocity in nano-MOSFETs      | 131               |

| , | 7.1                                         | 8 8 V                                                           | 132               |

|   | 7.2                                         |                                                                 | 132               |

|   | 7.3                                         |                                                                 | 133               |

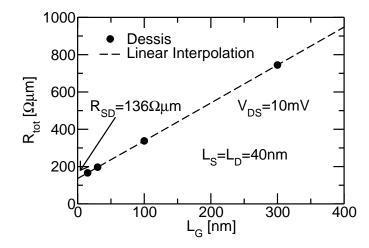

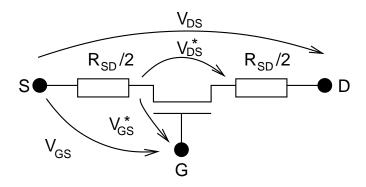

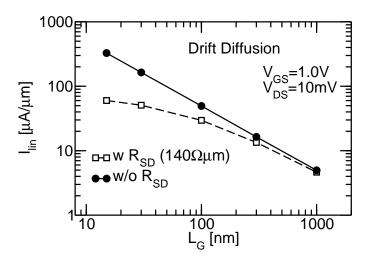

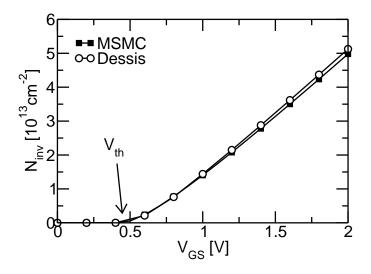

|   | 7.4                                         |                                                                 | 134               |

|   |                                             |                                                                 | 134               |

|   |                                             |                                                                 | 136               |

|   |                                             |                                                                 | 137               |

|   |                                             |                                                                 | 140               |

|   | 7.5                                         | Methodology                                                     | 141               |

|   | 7.6                                         | Analysis and results                                            | 141               |

|   | 7.7                                         |                                                                 | 146               |

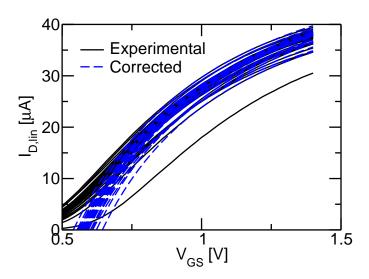

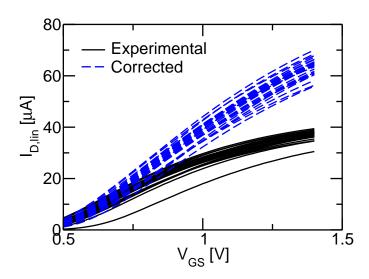

|   | 7.8                                         | Improved method applied to experimental data                    | 150               |

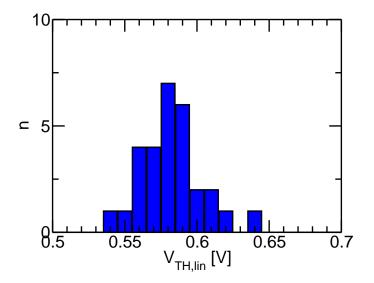

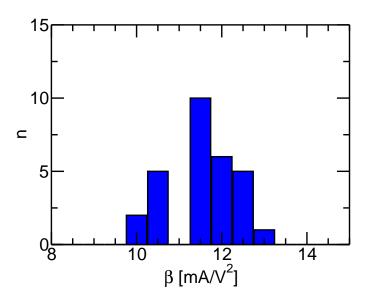

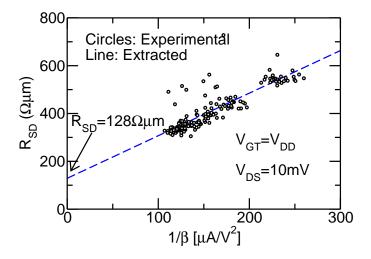

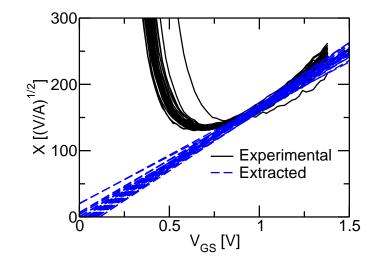

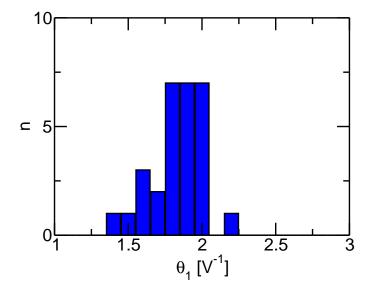

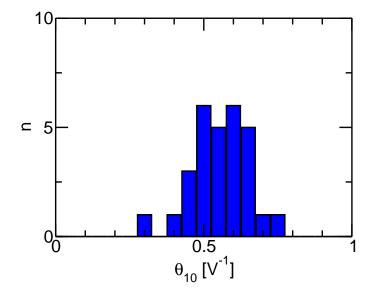

|   |                                             |                                                                 | 150               |

|   |                                             |                                                                 | 156               |

|   |                                             | 7.8.3 Extraction in saturation regime                           | 157               |

|   |                                             | 7.8.4 The extraction of the limiting velocity                   | 160               |

|   | 7.9                                         | Conclusions                                                     | 162               |

| 8  | Con    | clusions                                                           | 163 |

|----|--------|--------------------------------------------------------------------|-----|

| A  | The    | effects of wave function penetration into the high-k dielectric or | 1   |

|    | the s  | surface roughness limited mobility                                 | 165 |

|    | A.1    | Evaluation of mobility when accounting for wave function pene-     |     |

|    |        | tration in high- $k$ stacks                                        | 165 |

| B  | The    | phonon-plasmon coupling                                            | 167 |

| С  | Nun    | nerical algorithm for the determination of the phonon modes in     | 1   |

|    | gene   | ric gate structures                                                | 171 |

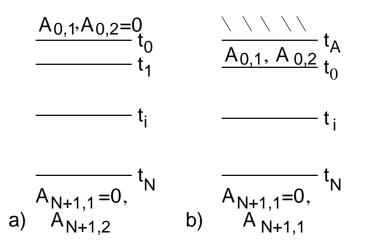

|    | C.1    | General structure approach                                         | 171 |

|    | C.2    | Solution in the case of infinitely thick dielectric                | 172 |

|    | C.3    | Solution in the case of metal gate electrode                       | 172 |

| Bi | bliogı | raphy                                                              | 174 |

## Chapter 1

## Introduction

#### Abstract

In this chapter we introduce various examples of the scaling rules that, in the past decades, have lead the modern devices to dimensions of few nano-meters.

Then, we list some problems that raise in nowadays ultra short MOSFETs, and how they have been solved by means of the introduction of the technology boosters in the fabrication process.

#### 1. Introduction

| Physical parameter       | Constant Field | Generalized           | Gen. Selective                       |

|--------------------------|----------------|-----------------------|--------------------------------------|

| Channel length           | $1/\alpha$     | $1/\alpha$            | $1/\alpha_d$                         |

| Insulator thickness      | $1/\alpha$     | $1/\alpha$            | $1/\alpha_d$                         |

| Channel width            | $1/\alpha$     | $1/\alpha$            | $1/\alpha_w$                         |

| Wiring width             | $1/\alpha$     | $1/\alpha$            | $1/\alpha_w$                         |

| Electric field in device | 1              | $\epsilon$            | $\epsilon$                           |

| Voltage                  | $1/\alpha$     | $\epsilon/lpha$       | $\epsilon/\alpha_d$                  |

| Doping                   | $\alpha$       | $\epsilon lpha$       | $\epsilon lpha_d$                    |

| Area                     | $1/\alpha^2$   | $1/\alpha^2$          | $1/\alpha_w^2$                       |

| Capacitance              | $1/\alpha$     | $1/\alpha$            | $1/\alpha_w$                         |

| Gate delay               | $1/\alpha$     | $1/\alpha$            | $1/\alpha_d$                         |

| Power dissipation        | $1/\alpha^2$   | $\epsilon^2/\alpha^2$ | $\epsilon^2 / \alpha_d^2 \alpha_w^2$ |

| Power density            | 1              | $\epsilon^2$          | $\epsilon^2 \alpha_w / \alpha_d$     |

Table 1.1: Technology scaling rules: constant-electric field scaling, generalized scaling and generalized selective scaling.

#### **1.1 Scaling of the MOSFET**

#### **1.1.1** The scaling scenario

In the past 40 years, most of the electronic fabrication activity has been focused to shrinking the dimensions of the MOSFETs (Metal Oxide Semiconductor Field Effect Transistors). The aim of this scaling is mainly to increase the number of transistors per chip which leads to lower cost per function and larger computing power.

The initial scaling rules proposed in [2] were constructed in order to obtain scaled devices with the same operative conditions as the original ones (i.e. the electric field in the device channel remains constant through the scaling process). This maintains a good reliability of the scaled devices. These rules change various device physical parameters by the same factor  $\alpha > 1$ , as shown in Table 1.1 (second column). In this methodology of scaling, called "constant field scaling", the threshold voltage shift should scale as the other parameters. However, in extremely scaled devices, it is difficult to scale the threshold voltage, since, otherwise, the leakage currents would become excessive.

This fact has lead to a more complex formulation of scaling rules, called "generalized scaling" [3, 4, 5, 6]. In these new methodologies, the supply voltage scales by a factor  $\epsilon$ , with  $1 < \epsilon < \alpha$ . The problem of this scaling approach is that the electric field in the devices increases by a factor  $\epsilon$ , as we can see in the third column of Table 1.1. Thus, new reliability problems can arise.

Recently, a new scaling methodology, called "generalized selective scaling" has been proposed [7, 8, 9]. It consists of scaling the channel length and oxide thickness by a factor  $\alpha_d$ , and the channel width and the wiring width by a factor

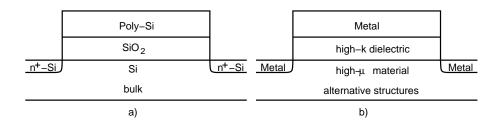

Figure 1.1: Comparison between a conventional MOSFET (a) and a device which features various technology boosters (b).

$\alpha_w$ . Choosing  $\alpha_d > \alpha_w$ , we maintain a good reliability, allowing the gate delay to scale faster than in the previous scaling technologies.

#### 1.1.2 Problems related to the fabrication of ultra short MOSFETs

The scaling rules explained in Sec. 1.1.1 have been applied for entire decades, leading the modern MOSFET devices to dimensions of about 10 nano-meters. Due to the size of nowadays devices, some problems have become much more critical than in the past:

- static power dissipation : the leakage currents (of the gate contact and of the junctions) has augmented considerably;

- short channel effects : the electric potential in the channel of the device is not independent on the drain contact polarization, since the electric field of the channel-drain junction penetrates into the channel;

- limitation of the ON-current : the ON-current does not longer improve as the channel length is shrinked;

- dynamic power dissipation : the areal density of the operating power has increased sensibly.

In order to mitigate these negatives effects, some techniques called "technology boosters" have been introduced in the fabrication process of the modern MOS devices [10].

#### 1.1.3 Overview of the technology boosters

The terminology "technology boosters" stands for all the techniques introduced in the fabrication process of the ultra scaled MOSFETs in order to continue the improvement of the performance of the devices beyond the classical scaling rules explained in Sec. 1.1.1. These techniques have modified all the regions of the MOSFET structure compared to the "conventional" device (see Fig. 1.1):

channel material : the silicon (Si) has been substituted with the strained silicon (s-Si). Moreover, Germanium (Ge) and III-V materials (as for example the gallium arsenide, GaAs) are emerging as promising candidates to substitute the Si based materials in the device channel.

- gate oxide : the SiO<sub>2</sub> has been substituted with materials with a high electric permittivity k, in order to limit the gate leakage current and improve the reliability of the dielectric.

- gate contact : the poly-Si material has been substituted with a metal, for many reasons. The main reason is because of the better integrability with the high-k dielectrics. Moreover a metal gate reduces sensibly the polydepletion region, that is one of the main problems affecting the poly-Si gates, allowing a better control of the channel region.

- source and drain contacts : the doped semiconducting regions will be substituted with metal regions, in order to limit the series resistances of the contacts.

- device architecture : much effort is devoted to substitute the conventional planar structure with Silicon On Insulator (SOI) or multi-gate structures. Mainly, this step will lead to improved capability of the gate contact to control the carriers in the channel, thus allowing to further scale the devices, while avoiding the short channel effects.

#### **1.1.4** The state of the art

The guideline of the technology improvements in MOSFET fabrication is the International Technology Roadmap for Semiconductors (ITRS) [10]. According to the ITRS, devices which enter the mass production in 2012, would be a bulk transistor with a gate length of 22 nm for high-perfomance logic (the channel length is even shorter). The thickness of the SiO<sub>2</sub> dielectric should be around 1.06 nm. The mobility enhancement of the carriers in the inversion layer has to be around a factor 2 for both electrons and holes, with respect to a conventional device with unstrained Si channel. The supply voltage should be 0.9 V, while the threshold voltage is around 0.29 V.

Taking a look on most recent research activities, many publications have been focused on device structures alternative to the bulk ones. For instance, a 20 nm Single Gate Fully Depleted SOI structure has been presented in [11]. Much effort is also given to bulk FinFETS (triple gate structures) [12, 13], SOI FinFETs [14] and 3D vertical integration FinFETs [15]. Although almost all new devices feature the high-k dielectrics, much attention is still paid to the optimization of these type of dielectrics [16, 17, 18]. Concerning the introduction of the alternative channel materials, we can see that s-Si is nowadays employed in almost all Si-technologies. However, interesting publications can be found regarding the possible replacement of Si with Ge [19, 20] and III-V [21, 22, 23] materials.

#### **1.2** High-*k* dielectrics

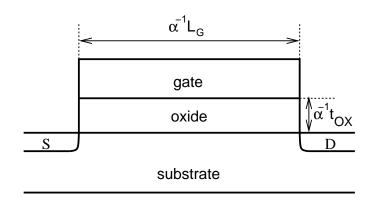

Observing Table 1.1, we can see that in all the mentioned scaling rules the gate oxide thickness must scale by the same factor as the channel length (see Fig. 1.2),

Figure 1.2: Sketch of the MOSFET device. The relation between the scaling of the channel length  $L_{\rm G}$  and the dielectric thickness  $t_{\rm OX}$  is shown.

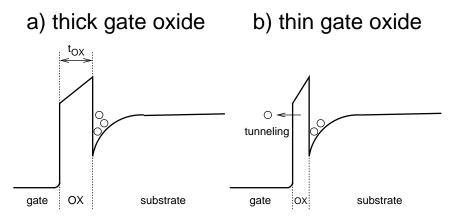

Figure 1.3: Band diagram of structures with a thick (a) and a thin (b) gate oxide. In the thin oxide structure, barrier tunneling is not negligible.

in order to avoid the so called short channel effects and thus allow the gate electrode to have an optimal control of the electrostatics in the channel. However, the oxide thickness shrinking leads to an increased leakage current.

#### 1.2.1 The gate leakage current problem

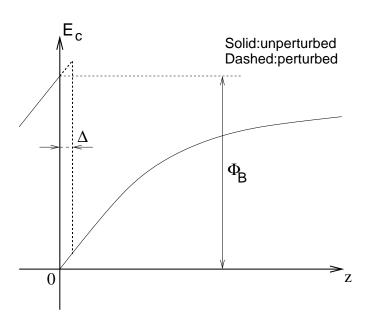

Let's consider the potential barrier between channel and gate. If this barrier is thin in space or low in energy, the probability of barrier tunneling is high (see Fig. 1.3). For this reason, the probability that an electron passes through the dielectric depends on the insulator thickness (thickness of the barrier) and on the insulator material (barrier height, effective mass, ...).

The scaling rules have lead to silicon dioxide  $(SiO_2)$  thicknesses that result in significant tunneling of the carriers from the MOSFET channel to the gate electrode leading to an undesired gate leakage current. This is un undesired effect for mainly two reasons:

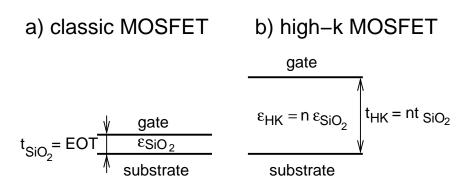

Figure 1.4: Comparison between structures with a SiO<sub>2</sub> (left) and a high-k (right) gate oxide. In the high-k structure, a thicker oxide layer can be used, reducing the gate leakage. n is the ratio between the high-k and SiO<sub>2</sub> electric permittivities.

- the gate current increases the static power dissipation.

- the gate current flows through a dielectric layer, decreasing the reliability of the device.

New solutions have been therefore devised to continue the nano-electronic development.

#### **1.2.2** Benefit of using high-k dielectrics

One possible solution to reduce the gate leakage current is to change the insulator material. The most promising candidates to substitute the  $SiO_2$  are the so called high-k dielectrics.

The introduction of high-k materials allows to increase the dielectric thickness (which should decrease the leakage current) without decreasing the equivalent oxide thickness (EOT). The EOT is the SiO<sub>2</sub> thickness that produces the same gate capacitance  $C_{OX}$  as the one of the high-k stack. The gate capacitance, per unit area, is:

$$C_{\rm OX} = \frac{\epsilon_{\rm OX}}{t_{\rm OX}} \tag{1.1}$$

where  $\epsilon_{OX}$  is the electric permittivity of the gate dielectric and  $t_{OX}$  is the thickness.

Fig. 1.4 shows that if we use a material with a dielectric constant n times larger than the one of SiO<sub>2</sub>, we can have the same  $C_{OX}$  with a thickness n times larger. This allows to decrease the gate leakage current, preserving the scalability of the device apart from two-dimensional effects [24].

However, while the use of the high-k dielectrics allows to increase the physical thickness of the gate oxide, they have a smaller height of the potential barrier. Thus, the carriers in the inversion layer of a MOSFET featuring high-k dielectrics feel a thicker but lower potential barrier than in classical devices. Anyway, despite of the lower potential barrier, high-k dielectric MOSFETs outperform SiO<sub>2</sub> devices [25, 26].

#### **1.2.3** Mobility reduction in MOSFETs with high-k in the gate stack

The carrier mobility  $\mu$  is relates the drift velocity of the carriers with the driving electric field, as:

$$\mu = \frac{v_{\rm drift}}{E_{\rm lateral}} \tag{1.2}$$

when the lateral electric field  $E_{\text{lateral}}$  is not too high (we will explain this aspect in Sec. 2.2.1). In the equation,  $v_{\text{drift}}$  is the drift velocity of the carriers in the inversion layer. Thus, the mobility, whose general definition can be found in [27], expresses the ability of the carriers to gain velocity when they are subjected to a driving electric field.

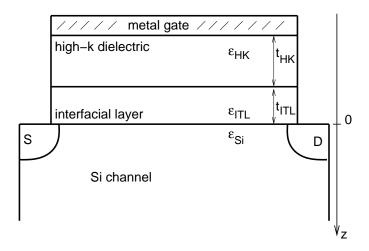

The use of high-k dielectrics leads to a lower value of the carrier mobility than the one obtained with SiO<sub>2</sub>. For this reason two solutions that sensibly improve the mobility have been commonly introduced in the MOSFET fabrication:

- the usage of metal gate electrodes, that improves the quality of the interface between the high-k dielectric and the gate [28];

- a thin SiO<sub>2</sub> layer between the channel and the high-k material (the so called interfacial layer) has been introduced in order to place the high-k dielectric more distant from the free carriers of the inversion layer.

Nevertheless, these solutions do not completely solve the problem of the mobility reduction. Moreover, the interfacial layer introduction poses a trade off between the mobility reduction and the high-k effectiveness allowing for small EOT. However, since these two solutions are almost universally used, all data shown in this section refers to MOSFETs with metal gate and interfacial layer.

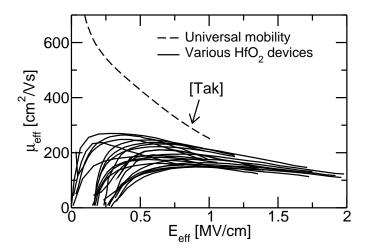

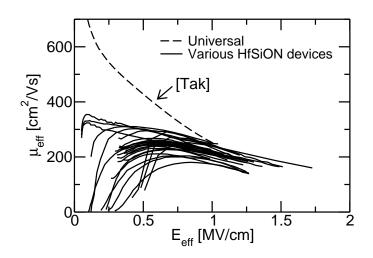

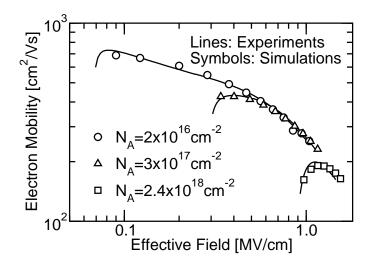

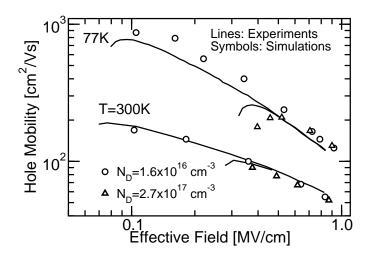

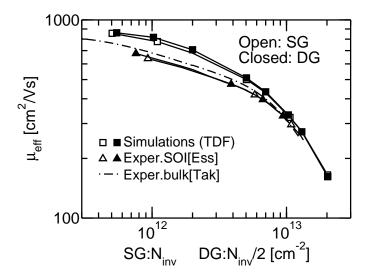

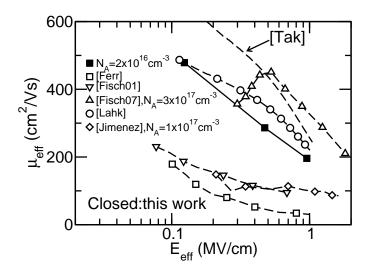

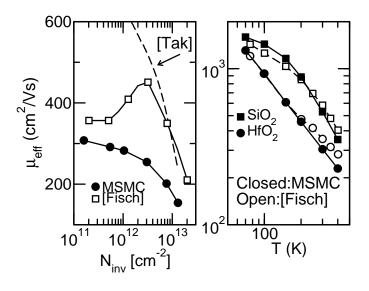

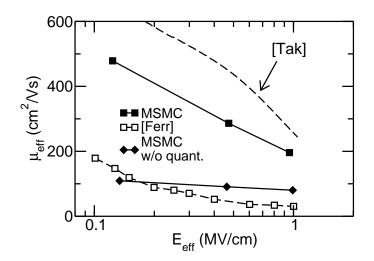

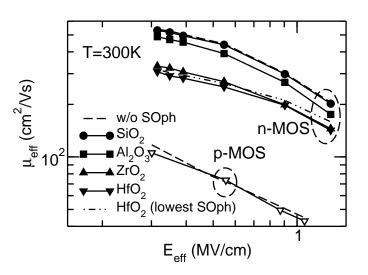

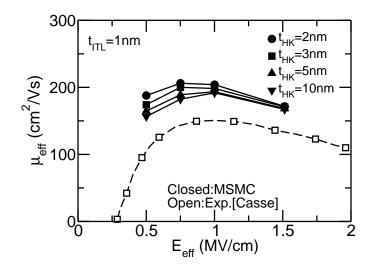

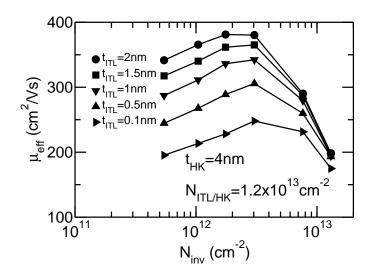

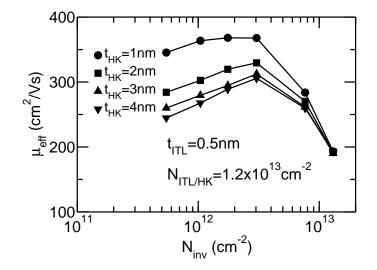

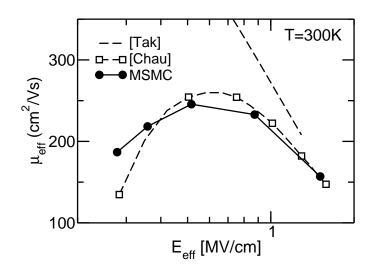

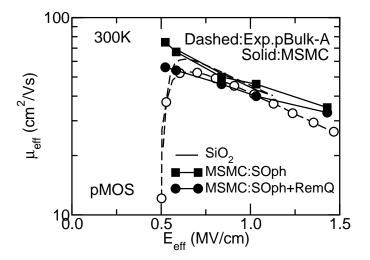

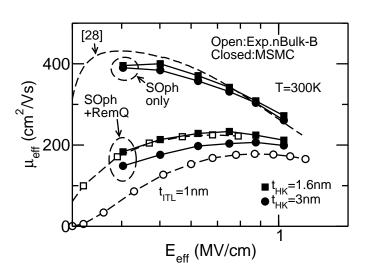

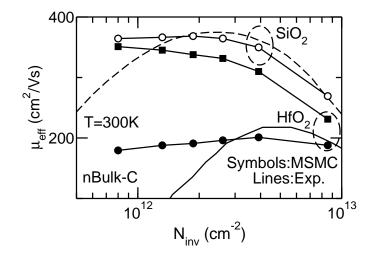

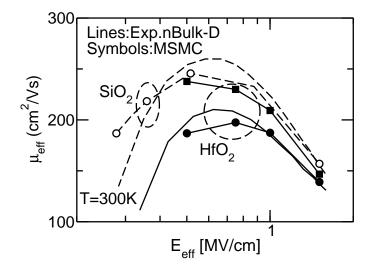

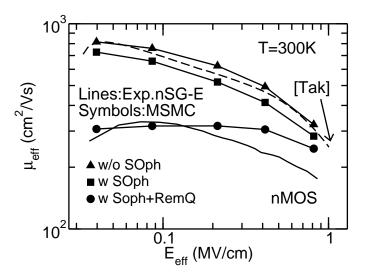

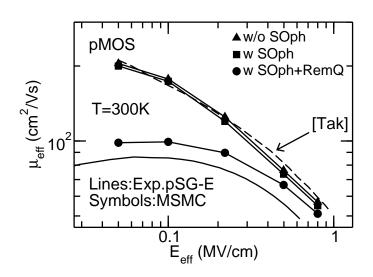

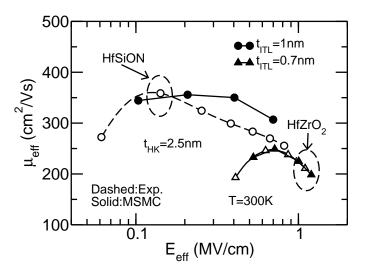

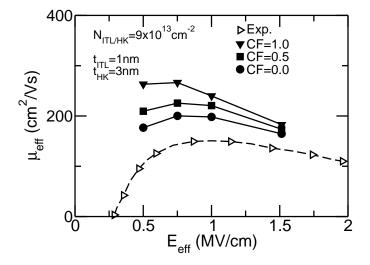

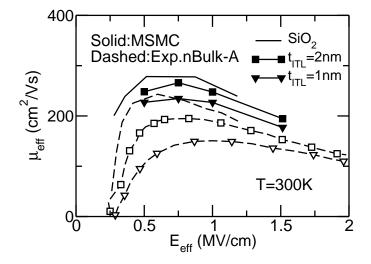

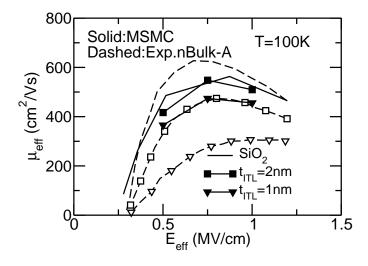

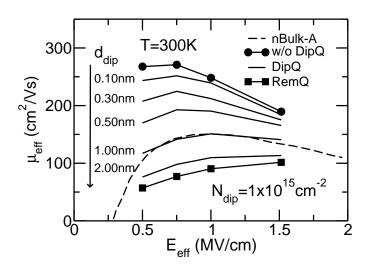

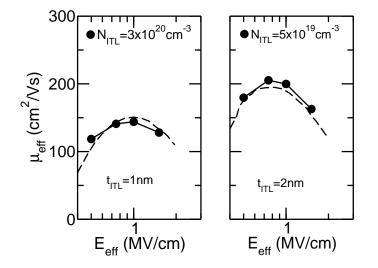

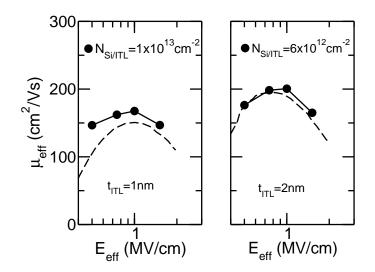

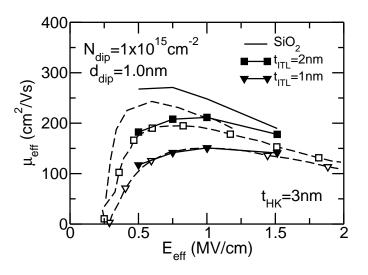

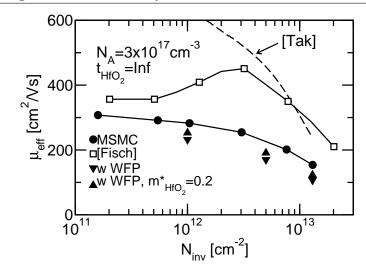

In Figs. 1.5 and 1.6 we show some experimental data that supports the fact that there is a mobility degradation due to the use of high-k insulators. In detail, Fig. 1.5 refers to devices with hafnium dioxide (HfO<sub>2</sub>) and Fig. 1.6 refers to hafnium-silicon oxynitride (HfSiON). These are two of the most used high-k dielectrics. All the curves in the two graphs refer to measurements at 300 K. The HfO<sub>2</sub> data is published in [29, 30, 31, 32, 33, 34, 35, 28, 36, 37]. The HfSiON data is published in [38, 39, 40, 41, 42, 43, 44, 45, 46]

Considering the curves of Fig. 1.5, which refer to measurements at 300 K of  $HfO_2$  devices with metal gate, Ref. [31] is quite useful since it contains a wide set of experimental data that can help us in the analysis of the mobility degradation, as for example the dependencies of the mobility on the interfacial or high-*k* layer thicknesses.

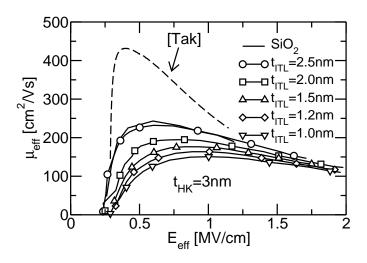

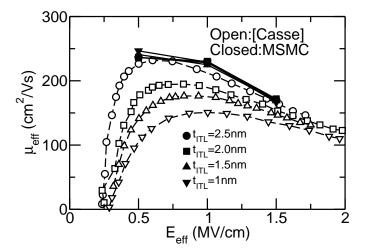

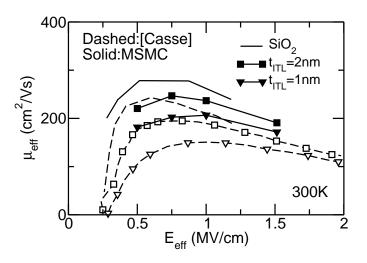

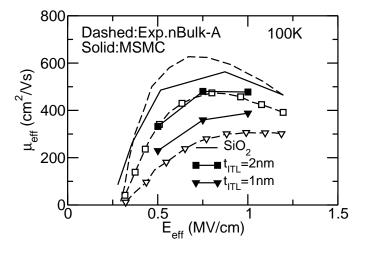

We collect some of these curves in Fig. 1.7. These curves refer to bulk devices with channel doping of  $2 \times 10^{17}$  cm<sup>-3</sup>, with HfO<sub>2</sub> thickness of 3 nm and with various interfacial layer thicknesses ranging from 1.0 to 2.5 nm. In the figure we also show the mobility curve of the reference SiO<sub>2</sub> device with 2.5 nm of SiO<sub>2</sub> and metal gate. All the devices measured in [31] have titanium nitride (TiN) gate electrode. Moreover, Takagi reference curve is shown (which refers to a device with poly-Si gate electrode, but very thick SiO<sub>2</sub> dielectric). We can see that while the device with interfacial layer thickness of 2.5 nm shows no mobility degradation

Figure 1.5: Comparison between the universal mobility curve [47] and various experimental data for  $HfO_2$  devices with metal gate.

Figure 1.6: Same as in Fig. 1.5, but for HfSiON dielectric.

Figure 1.7: Experimental data measured in [31] at 300 K for bulk MOSFETs with doping  $2 \times 10^{17}$  cm<sup>-3</sup>. The measurements refer to devices with 3 nm of HfO<sub>2</sub> and with various SiO<sub>2</sub> thicknesses from 1.0 nm to 2.5 nm. All devices measured have TiN metal gate. The SiO<sub>2</sub> reference device of [31] and the universal mobility curve of [47] are also shown.

with respect to the SiO<sub>2</sub> MOSFET, the device with interfacial layer thickness of 1.0 nm shows a peak mobility reduction of about 38% with respect to the SiO<sub>2</sub> device measured in [31], that is however much lower than the universal mobility curve [47].

#### **1.2.4** Possible causes of mobility degradation in high-k stacks

In the previous section we have seen that the use of high-k dielectrics leads to a non-negligible mobility degradation with respect to conventional SiO<sub>2</sub> devices.

Fig. 1.7 shows that the mobility degradation seems to be strictly related to the interfacial layer thickness (and thus to the distance of the high-k insulator from the free carriers in the channel).

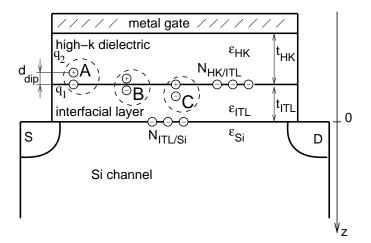

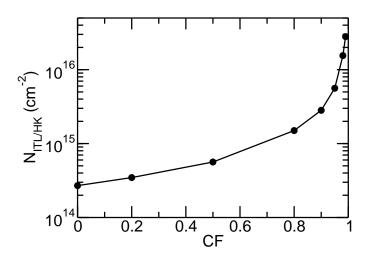

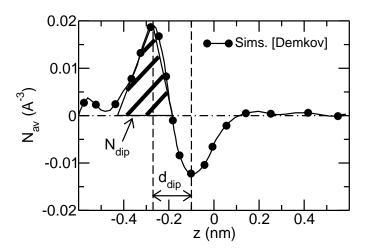

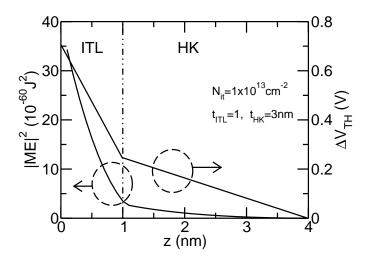

This mobility degradation has been ascribed to the vibration of the polar molecules of high-k dielectrics (the so-called soft optical phonons [48, 49, 50, 51]) or to fixed charges which are located in the gate stack. These charge can reside in the gate stack due to the non-ideality of the MOSFET fabrication process (in the form of single charges [31, 52]) or can be intrinsic and thus features of the interfaces in the gate stack (in the form of dipoles [53, 54, 55]).

In the first part of Chap. 5 we develop models for surface optical phonon scattering, single Coulomb centers and dipoles in gate stacks with interfacial layer, high-k material and metal gate. Moreover, we will compare a wide set of experimental data and Monte Carlo simulations in order to establish which is the main cause of the observed electron and hole mobility degradation. Finally, we will compare simulated and experimental ON-current in short channel devices in order to assess the effect of the high-k dielectrics in modern MOS-FETs.

#### **1.3** Multi gate structures

Due to the short channel effects, in order to maintain a good control of the channel region by the gate contact, the channel length can not be scaled down below a given limit that depends on the depletion region thickness. The thinner is the depletion region, the shorter the channel can be. Indeed, for instance, this is one of the reason that has lead to highly doped channel regions in scaled bulk devices.

In order to avoid this technological limit, one possible solution is to change the structure of the MOSFET. A possible modification of the conventional bulk structure is to substitute the bulk region with a bottom oxide, obtaining the Single Gate SOI (SG-SOI) structure. Doing this, the minimum channel length of a technology is not related to the doping, but to the thickness of the channel region (with the assumption that the device channel is fully depleted) [56, 57].

Unfortunately, the substitution of the bulk doped region with an oxide is a very complex step and maybe not justified, even if the fully depleted SOI has potentially the possibility to overcome the bulk technology limits. However, once the bulk region has been eliminated, we can think to add a gate contact also at the bottom of the device obtaining the so-called Double Gate SOI (DG-SOI).

This further step in the process technology evolution, will expand the scenario of the ultra scaled MOSFETs to the multi-gate structures [58].

#### **1.3.1** Benefits of using multi gate structures

The fabrication of the DG-SOI structure [5, 59] (see Fig. 1.8b) is even more difficult than the SG-SOI one, but it further improves the advantages of the SG-SOI structures over the bulk technologies [6, 60, 61].

It has been shown that the DG-SOI structure has better immunity to short channel effects, with the same Si thickness of the SG-SOI one. Indeed, the constraint of the maximum channel thickness as a function of the channel length is less limiting, leading the DG-SOI to be most promising to overcome the limits of the bulk technology. As an example, in the ITRS [10] a SG-SOI wich features a gate length of 17 nm (planned for 2015), requires a channel thickness of 5.5 nm. A DG-SOI device with the same channel length, needs a channel thickness of 8 nm.

Here we report a brief list of the main advantages of the DG-SOI structure with respect to the bulk technology:

better immunity to short channel effects: for the reason previously explained, these kind of devices are easier to scale.

- larger gate capacitance: the larger is the number of gate contacts and the larger is the gate capacitance. With a large gate capacitance, the density of the carriers in the channel increases, leading to a larger ON-current (see Eq. 1.3).

- sub-threshold slope: the sub threshold slope (i.e. the slope of the logarithm of the  $I_{\rm DS}$ - $V_{\rm GS}$  curve when  $V_{\rm GS}$ < $V_{\rm TH}$  [62]) is increased, getting closer to the theoretical limit of 60 mV/dec. This leads to have smaller OFF-current  $I_{\rm OFF}$ , or equivalently, a lower threshold voltage  $V_{\rm TH}$ , with the same ON-current.

- the channel region can be undoped leading to several advantages:

- better mobility of the carriers

- better immunity to doping variability

- less parasitic capacitances

There is an additional possible improvement of the DG-SOI structure. We can add a third gate contact to the channel in order to further increase the gate capacitance. Such a 3D structure, called FinFET structure [63, 64, 65], if made on a bulk wafer (as in Fig. 1.8c) combines the advantages of the DG-SOI structures with the relative process simplicity of the bulk MOSFET fabrication. To be more precise, if on one hand the process fabrication is difficult since it is 3D for these structures, to the other hand the necessity to having a bottom gate is avoided.

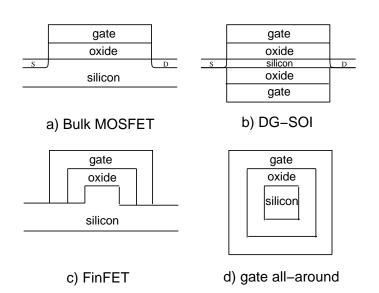

Summarizing, if the total number of gate electrodes is 2, we obtain the DG-SOI. If the device has 3 gate electrodes, we have the triple gate structures (where the most famous architecture is the FinFET). Finally, if the gate electrodes are 4, we have the so called gate all around geometries [66] (see Fig. 1.8d).

#### **1.3.2** Problems related to the modeling of multi gate structures

From the device modeling point of view, two main problems arise:

- the proper modeling of the quantization is more complex because the confinement of the carriers is no longer only due to the squeezing of the carrier at the channel/oxide interface; indeed the confinement is also due to the device geometry. Moreover, in FinFETs and in Gate all-around MOSFETs, the modeling of the quantization is a 2D problem, differently from bulk, SG-SOI and DG-SOI structures, where a 1D solution is required;

- the treatment of the surface roughness scattering mechanism requires a more complex formulation;

- more complex models for screening are required, due to the increased number of inversion layers in the device.

In Chap. 4 we explore the last aspect, by analyzing in detail the methodology to properly take into account the screening effect in multi gate structures.

#### 1. Introduction

Figure 1.8: Comparison between various MOSFET device structures. a) classical bulk MOSFET. b) DG-SOI MOSFET. c) FinFET. d) gate-all-around MOSFET. In the a) and b) case, the device view is parallel to the transport direction. In the c) and b) case, the device view is orthogonal to the transport direction.

#### **1.4** Alternative channel materials

In Sec. 1.1.2 we have seen that nowadays it is becoming extremely difficult to continue the MOSFET scaling. A possible solution is to change the channel material.

#### **1.4.1** Benefits of using alternative materials

The low field mobility (Eq. 1.2) is a property of the channel material. If we choose more favorable materials, i.e. that have a higher low-field mobility than the conventional Si, we have carriers that can move faster through the channel. Thus, we can obtain higher ON-currents, congruently with the basic formula:

$$I_{\rm ON} \simeq Q_{\rm eff} \cdot v_{\rm eff}$$

(1.3)

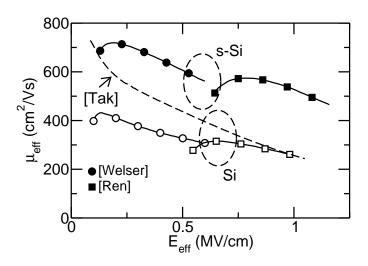

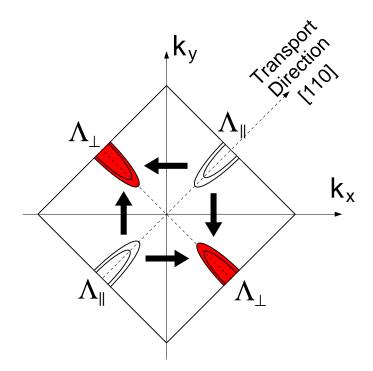

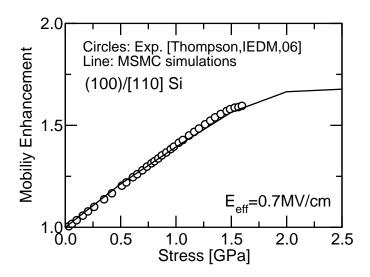

In this regard, the easiest improvement with respect to the conventional Si MOSFET is to use the Strained-Si (s-Si). The s-Si technology have been demonstrated to yield mobility enhancements in CMOS devices and is currently used in the most advanced IC to boost performances beyond the improvements given by device scaling [67, 68, 69]. Fig. 1.9 shows the comparison between the Si and s-Si experimental data of [70, 71]. The device of [70] features a doping of  $1 \times 10^{16}$  cm<sup>-3</sup>, while the data of [71] refers to a device with channel doping of about  $3 \times 10^{17}$  cm<sup>-3</sup>. Both the experimental data refers to bi-axial tensile strain and to very thick SiO<sub>2</sub> oxide devices (13 and 6.7 nm). The mobility enhancement

Figure 1.9: Comparison between the Si and s-Si electron mobility of [70, 71]. The universal mobility curve of [47] is also shown.

is evident and, in particular, it allows to overtake the universal mobility curve of [47].

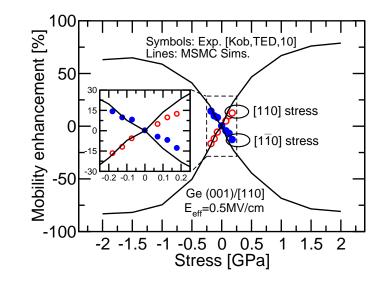

Moreover, it is possible to make less conservative choises. New materials are indeed emerging as possible competitors of the Si and s-Si devices, for instance the Ge, strained germanium (s-Ge) and III-V materials.

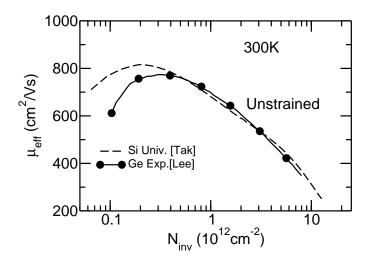

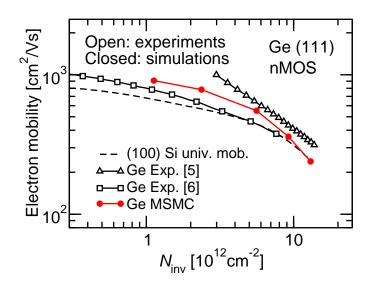

The introduction of these materials is more difficult with respect to the s-Si, but interesting results have already been published for both the unstrained [72, 73] and strained Ge [74] for *n*-MOSFETs. In this regard, Fig. 1.10 shows the electron mobility for a device featuring a high-k dielectric (GeO<sub>2</sub>) on the top of an unstrained Ge bulk. We can see that, despite of the use of a high-k dielectric, the mobility is comparable with the universal one for Si. Thus, Ge and s-Ge are promising candidates for overcome the Si limits.

Finally, much attention has been paid to III-V materials for high-performance devices. The research activity for the integration of these type of materials in these devices is not as advanced as the Ge based materials, but they appear very promising [75].

#### 1.4.2 Strained silicon, germanium and strained germanium modeling

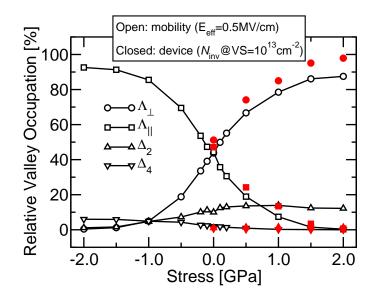

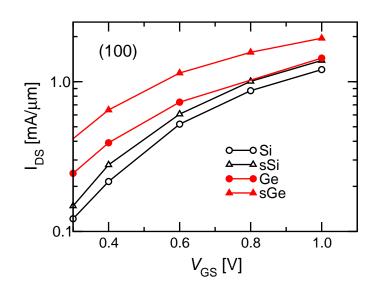

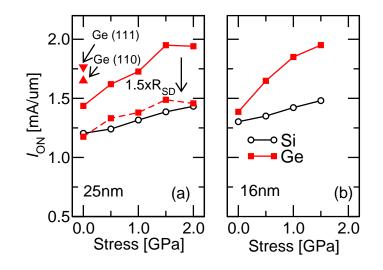

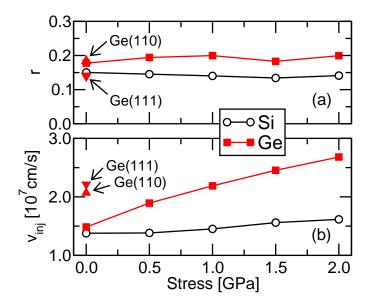

In the first part of Chap 6, we will briefly describe a methodology for the modeling of s-Si, Ge and s-Ge. Then we will compare the performances in ultra scaled n-MOSFETs, in order to assess the competitivity of Ge and s-Ge with respect to Si and s-Si.

Figure 1.10: Comparison betwenn the Universal Si mobility of [47] and the Ge experimental data of [73].

## **1.5** Evaluation of the effect of technology boosters in real devices

High-mobility materials are introduced to boost the ON-current in modern MOSFETs.

We will see in Chap. 7 that the definition of mobility is valid only when the number of the scattering events of the carriers is very large. However, high mobility materials are used in order to reduce the number of scattering events. Moreover, if we consider short channel devices, the number is reduced even more, and the concept of mobility is hard to apply. Thus, the mobility is not a valid metric to describe the behaviour in short channel devices featuring high mobility materials.

Unfortunately, also the drain current, alone, can not give all the information that is needed to correctly characterize a modern MOSFET. Thus, we need other parameters as, for example, the limiting velocity  $v_{\text{lim}}$  of the carriers in the channel of the device. For instance, the  $v_{\text{lim}}$  can be a useful indicator of the regime where the transistor is operating and of the level of strain of the channel material.

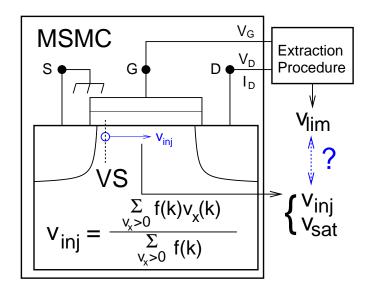

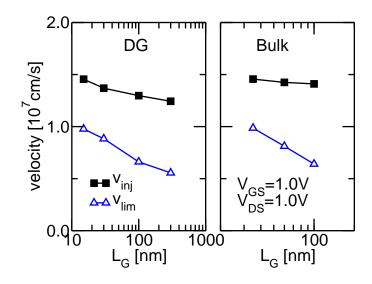

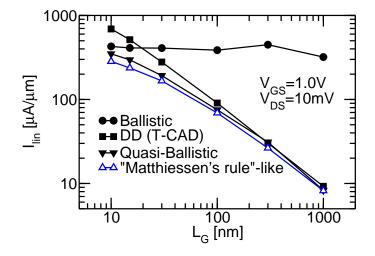

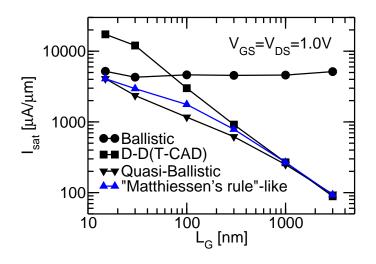

In this regard, in Chap. 7 we use the Multi Subband Monte Carlo simulator in order to validate an existing extraction procedure of the limiting velocity in modern short channel devices [1]. After a detailed analysis of the method, we identify the sources of error of the method. Finally, we propose a new methodology for the extraction of the limiting velocity  $v_{\text{lim}}$  and we extensively validate it.

## **Chapter 2**

# The semi-classical approach and the Boltzmann transport equation

The exact solution of the motion of carriers in a nano structure as a modern MOSFET device is found solving a full quantum problem, where the carriers are described as wave-packets.

However, if the size of the wave-packets representing the carriers are much smaller than their mean free path (the length travelled by an electron between two successive collisions), we can treat the carriers as localized particles with a well defined position and momentum. This kind of approach is called *semi-classical*. In this chapter we present various modeling approaches for MOSFET devices in the semi-classical framework.

Firstly, we present the Boltzmann transport equation, which is the general equation governing the semi-classical transport.

Moreover, we derive the Drift Diffusion model as a simplified solution of the Boltzmann transport equation. We also see the analytic expressions for the drain current which can be derived from the Drift-Diffusion model and identify the main limitations of the Drift-Diffusion model.

Then, we describe the ballistic and quasi-ballistic transport regimes, and we show simplified analytic expressions for the drain currents in those regimes.

Finally, we briefly review the Monte Carlo method which allows to find an exact solution of the Boltzmann transport equation in a statistical way.

#### 2.1 The Boltzmann transport equation

The Boltzmann Transport Equation (BTE) [76] is the basis for the semi-classical description of carrier transport in electron devices. The Boltzmann equation is a continuity equation in the phase space.

We start by defining some quantities that allow to completely describe each carrier in our system:

$$\begin{cases} \mathbf{R} = (x, y, z) \\ \mathbf{p} = (p_x, p_y, p_z) \\ t \end{cases}$$

(2.1)

where  $\mathbf{R}$  is a vector which determines the position of the particle,  $\mathbf{p}$  defines the momentum of the particle, and t is the instant of time considered.

We can describe the entire population of the carriers by considering the distribution function of the carriers  $f(\mathbf{R}, \mathbf{p}, t)$ , which is the probability to find carriers located at the position  $\mathbf{R}$ , with momentum  $\mathbf{p}$  at the istant t [76]. The  $f(\mathbf{R}, \mathbf{p}, t)$  can be obtained by solving the BTE [77, 78]:

$$\frac{\partial f}{\partial t} + \left(\frac{d\mathbf{R}}{dt}\right) \cdot \nabla_r f + \left(\frac{d\mathbf{p}}{dt}\right) \cdot \nabla_p f = \left(\frac{\partial f}{\partial t}\right)_{\mathrm{C}} + U(\mathbf{R}, \mathbf{p}, t)$$

(2.2)

In the left hand side of the equation, we can note that:

$$\left(\frac{d\mathbf{R}}{dt}\right) = \mathbf{v}_{g} \tag{2.3}$$

where  $\mathbf{v}_{g}$  is the group velocity of the carriers, and that:

$$\left(\frac{d\mathbf{p}}{dt}\right) = \pm e\mathbf{E} \tag{2.4}$$

where **E** is the driving field. Eq. 2.4 is a version of the Newton's law. In the right hand side of the equation,  $(\partial f/\partial t)_C$  is the change of the distribution function due to the scattering events of the carriers and  $U(\mathbf{R}, \mathbf{p}, t)$  accounts for the changes of the distribution function due to the generation and recombination mechanisms.

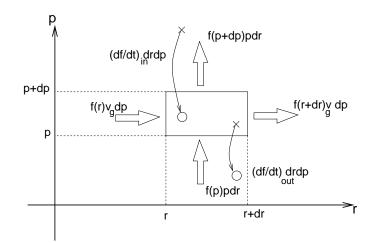

Eq. 2.2 is simply the continuity equation of the carrier fluxes in each portion  $(d\mathbf{R}, d\mathbf{p})$  in the  $(\mathbf{R}, \mathbf{p})$  space, as we can see in Figure 2.1. Indeed, the BTE states that the number of carriers (expressed in terms of probability of occupation of a state) in position  $\mathbf{R}$  with momentum  $\mathbf{p}$  at the time t can change only if some carriers change their position from/to  $\mathbf{R}$ , or change their momentum from/to p (due to acceleration of the particle), or scatter (changing its momentum  $\mathbf{p}$ ).

#### 2.1.1 Validity of the Boltzmann transport equation

It is worth to ask ourselves when it is realistic to apply the BTE to the carrier transport in nano-devices. The limits of validity of the BTE are summarized below:

Figure 2.1: Cell in the phase space at time *t*, with all the possible carrier fluxes that may contribute to modify the carrier population in the cell.

- The BTE uses a classical description of the particle where both the position and the momentum of a particle can be determined. This approximation is reliable when the Heisenberg uncertainty principle of the quantum mechanics can be neglected.

- The semi-classical approach is valid only if the external electric field slowly varies over a distance comparable to the size of the wave packet which would correctly describe the carrier in a quantum approach. For the same reason, the applied potential variations have to be much smoother than the crystal potential variations. Otherwise, the Newton's law (Eq. 2.4) can not be applied to the carriers and a more complicated treatement based on wave equations is required.

#### 2.2 The Drift - Diffusion model

We will see in this Chapter that the exact solution of the BTE (Eq. 2.2) requires computationally demanding methodologies. Thus, it is common to make some assumptions in order to simplify the Boltzmann transport equation.

Firstly, we assume the carriers as point particles with momentum:

$$\mathbf{p} = m^* \cdot \mathbf{v} \tag{2.5}$$

where  $m^*$  (assumed isotropic) is the effective mass of the electron in the semiconductor. We can express the electron density  $n(\mathbf{R}, t)$  by means of the distribution function, as:

$$n(\mathbf{R},t) = \frac{1}{\Omega} \sum_{\mathbf{p}} f(\mathbf{R},\mathbf{p},t)$$

(2.6)

where  $\Omega$  is the normalization volume.

#### 2. The semi-classical approach and the Boltzmann transport equation

By computing the balance equation for the zero-th order moment of the BTE we can find the continuity equations [77, 78]:

$$\begin{cases} \frac{\partial n}{\partial t} - \frac{1}{e} \nabla_r \mathbf{J}_{\mathbf{n}} = U \\ \frac{\partial p}{\partial t} + \frac{1}{e} \nabla_r \mathbf{J}_{\mathbf{p}} = U \end{cases}$$

(2.7)

where  $J_n$  and  $J_p$  are the electron and hole current densities, and can be expressed as:

$$\begin{cases} \mathbf{J}_{n} = -\frac{e}{\Omega} \sum_{\mathbf{p}}^{n \in CB} v(\mathbf{p}) f_{n}(\mathbf{R}, \mathbf{p}, t) \\ \mathbf{J}_{p} = -\frac{e}{\Omega} \sum_{\mathbf{p}}^{n \in VB} v(\mathbf{p}) (1 - f_{n}(\mathbf{R}, \mathbf{p}, t)) \end{cases}$$

(2.8)

where  $\sum_{\mathbf{p}}^{\text{CB}}$  and  $\sum_{\mathbf{p}}^{\text{VB}}$  are sums that are performed in the conduction and valence bands, respectively. Please note that while the probability to find an electron with energy E is expressed by f(E), the probability to find a hole at that energy level is 1-f(E).

Assuming that the semiconductor is not degenerate, the distribution function becomes:  $E_{\rm e}E_{\rm e}$

$$f(E) = e^{-\frac{E-E_{\rm F}}{KT}} \tag{2.9}$$

Eq. 2.9 describes a Maxwell-Boltzmann statistics, which is valid approximately when  $E - E_F > 3KT$ .

Assuming as closing condition of the system Eq. 2.9, from the balance equation for the first order moment of the BTE we can find the expression for the current density [77, 78]:

$$\begin{cases} \mathbf{J}_{n} = -e\mu_{n}n\nabla\phi + eD_{n}\nabla n\\ \mathbf{J}_{p} = -e\mu_{p}p\nabla\phi - eD_{p}\nabla p \end{cases}$$

(2.10)

where  $\mu_n$  and  $\mu_p$  are the mobilities for the electrons and holes (defined in Eq. 1.2), respectively. Moreover,  $\phi$  is the electrostatic potential and  $D_n$  and  $D_p$  are the diffusion coefficients for electrons and holes [27] that can be expressed as a function of  $\mu_n$  and  $\mu_p$  by means of the Einstein relations for non-degenerate gas at thermodynamic equilibrium [77], which are:

$$\begin{cases}

D_n = \frac{K_{\rm B}T}{e}\mu_{\rm n} \\

D_p = \frac{K_{\rm B}T}{e}\mu_{\rm p}

\end{cases}$$

(2.11)

Finally, the electrostatic potential can be found by means of the Poisson equation:

$$\nabla \cdot \epsilon \nabla \phi = -e(p - n + N_{\rm D} - N_{\rm A}) \tag{2.12}$$

where  $N_{\rm D}$  and  $N_{\rm A}$  are the donor and acceptor concentrations of the semiconductor.

Eqs. 2.7, 2.10 and 2.12 form the so-called *drift-diffusion model*, which is used in the TCAD commercial tools. Please note that in this model the unknown values are n, p and  $\phi$ , while the electron and hole mobilities  $\mu_n$  and  $\mu_p$  as well as U are model parameters.

Thus, models for the mobility evaluation are required in the Drift-Diffusion framework.

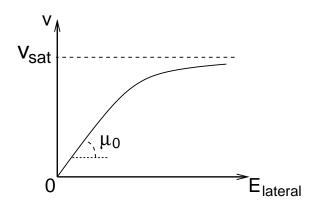

Figure 2.2: Graphical definition of the mobility and the saturation velocity.

#### 2.2.1 The saturation velocity

Eq. 1.2 defines the mobility  $\mu$  as the coefficient of proportionality between the velocity of the carriers and the driving electric field.

However, Eq. 1.2 is valid only when the driving electric field  $E_{\text{lateral}}$  is not too high. Otherwise, the increasing rate of interaction of the carriers with the crystal tends to limit the maximum attainable velocity.

This effect lead to the loss of the proportionality between the carrier velocity and the driving field, for high  $E_{\text{lateral}}$ . Indeed, experimental data [79] and Monte Carlo simulations [80] have shown that the relation between these quantities can be better modeled by [77]:

$$v = \frac{\mu E_{\text{lateral}}}{\left[1 + \left(\frac{\mu E_{\text{lateral}}}{v_{\text{sat}}}\right)^{\beta}\right]^{1/\beta}}$$

(2.13)

where  $v_{\rm sat}$  is the saturation velocity and  $\beta$  is a fitting parameter which for Si is 1.109 and 1.213 for electrons and holes, respectively. The saturation velocity  $v_{\rm sat}$  has the physical meaning of the maximum velocity that carriers can have in a crystal under uniform transport conditions, as shown in Fig. 2.2. For the Si, the saturation velocity  $v_{\rm sat}$  for electrons is  $1.07 \times 10^7$  m/s while for holes has the value of  $8.37 \times 10^6$  m/s.

Since the saturation velocity  $v_{sat}$  is due to a loss of energy of the carriers due to their interactions with the crystal when they are strongly accelerated, this values is strictly related to the inelastic scattering events.

#### 2.2.2 Analytic expressions for the currents

Applying the Drift - Diffusion model to a MOSFET device structure, it is possible to derive some analytic expressions for the currents, in the gradual channel approximation [62], which assumes:

$$\frac{\partial E_{\text{lateral}}(\mathbf{R})}{\partial t} \ll \frac{\partial E_{\text{vertical}}(\mathbf{R})}{\partial t}$$

(2.14)

#### 2. The semi-classical approach and the Boltzmann transport equation

Eq. 2.14 is called Gradual Channel Approximation (GCA) since assumes that the channel potential  $\phi$  slowly varies along the channel over a distance of the order of the oxide thickness. In this way the surface potential  $\phi_S$  at the lateral coordinate x can be found solving a 1D vertical problem. Assuming Eq. 2.14 it is thus possible to find [62]:

$$I_{\rm DD,lin} = \frac{W}{L} \mu C_{\rm G} (V_{\rm GS} - V_{\rm TH}) V_{\rm DS}$$

(2.15)

in the linear regime, i.e.  $V_{\rm DS} < V_{\rm GS} - V_{\rm TH}$ .  $V_{\rm GS}$  and  $V_{\rm DS}$  are the gate-to-source and the drain-to-source voltages, respectively. In Eq. 2.15 W and L are the MOSFET channel width and length,  $\mu$  is the mobility of the carriers,  $C_{\rm G}$  is the effective gate capacitance and  $V_{\rm TH}$  is the threshold voltage [62].

Assuming infinite saturation velocity, the expression for the current in saturation regime is:

$$I_{\rm DD,sat} = \frac{W}{L} \mu C_{\rm G} \frac{(V_{\rm GS} - V_{\rm TH})^2}{2}$$

(2.16)

Accounting for  $v_{sat}$  with  $\beta = 1$  gives [81]:

$$I_{\rm DD,sat} = \frac{W}{L + \mu v_{\rm sat}^{-1} V_{\rm DS,sat}} \mu C_{\rm G} \left[ (V_{\rm GS} - V_{\rm TH}) V_{\rm DS,sat} - \frac{1}{2} V_{\rm DS,sat}^2 \right]$$

(2.17)

where:

$$V_{\rm DS,sat} = \frac{-1 + \sqrt{1 + 2\mu(v_{\rm sat}L)^{-1}(V_{\rm GS} - V_{\rm TH})}}{\mu(v_{\rm sat}L)^{-1}}$$

(2.18)

Eq. 2.17 for  $L \rightarrow 0$  reduces to:

$$I_{\rm DD,sat} = W \mu C_{\rm G} (V_{\rm GS} - V_{\rm TH}) v_{\rm sat}$$

$$(2.19)$$

Eq. 2.19 states that for extremely short channel MOSFETs (usually called *ulti*mate CMOS devices), the scaling rules explained in Sec. 1.1.1 can not be applied since there is no longer any current dependence on the channel length L. Moreover, it states that the saturation current in ultimate CMOS devices is limited by the saturation velocity  $v_{sat}$ . This means, that in this framework, the performances are expected to be strictly related to the inelastic scattering parameters and material/temperature dependence.

However, the validity of Eq. 2.19 is strictly related to the applicability of the Drift-Diffusion model to short channel devices, that is briefly discussed in the following.

#### 2.2.3 Limits of validity of the Drift - Diffusion model

The Drift-Diffusion model has been very successful due to its relative simplicity with respect to more detailed solutions of the BTE. It's still the most used model in many TCAD commercial tools. Anyway, it is based on some assumptions that are questionable under certain conditions. Summarizing, the main assumptions at the basis of the Drift-Diffusion model are:

- the mobility can be defined only when the number of scattering events undergone by a carrier moving from Source to Drain is large;

- in the model presented in Sec. 2.2, the semiconductor is in a non-degenerate condition. Since this assumption is not valid in modern devices, more complicated Drift-Diffusion models have been generalized in the case of a degenerate semiconductor.

These assumptions are fulfilled in classical long-channel MOSFET devices, especially in linear regime.

However, in ultra-scaled MOSFETs, they become questionable. For example, in short channel device in saturation regime, the carriers are quite far from equilibrium conditions. Furthermore, the number of scattering events in the channel of a modern MOSFET is not so large, and the concept of mobility is no longer exploitable. Finally, there is no any evidence that the saturation velocity defined in Sec. 2.2.1 occurs in short channel MOSFET devices.

In the next sections we will see other methods for the solution of the BTE.

#### 2.3 The ballistic transport regime

The DD model relies on the assumption that the device is in a scattering limited regime, namely in a regime where the scattering events thermalize the carriers at equilibrium. This is the condition which allows to define the mobility  $\mu$  of the carriers (Eq. 1.2). In short channel devices it is no longer possible to define the mobility since the channel length of modern devices approaches the mean free path of the carriers (the average path the carriers travel without being scattered). Thus, we need to define new parameters to describe the performances of the nano MOSFET devices.

An approach that overcomes the problem of the impossibility to define the mobility in short channel MOSFETs is the one presented in [82, 83], which is directly derived from the flux theory. This approach is called the quasi-ballistic transport model, that will be described in Sec. 2.4.

For the sake of clarity, we first introduce the ballistic model [84], that is equivalent to the QB model if we assume that the particles do not scatter during their flight from the source contact to the drain one. We will discuss later the validity of this assumption.

#### **2.3.1** Basics on the ballistic model

In the ballistic model, carriers are injected from the source region (in which they are supposed to be at equilibrium) into the channel by crossing a potential barrier whose height is modulated by the gate voltage  $V_{\rm GS}$ . Then, carriers move across the channel and are eventually collected by the drain contact. If scattering is null, all the carriers that are able to cross the potential barrier in the channel will eventually reach the drain contact [84].

Figure 2.3: Graphical definition of the virtual source VS in the ballistic transport model.

Since we are interested in steady-state conditions, the current density in the channel can be considered solenoidal, i.e. constant in each section from the source to the drain. Thus, we can choose the most favorable section for the computation of the current  $I_{\rm DS}$ . We decide to consider the section at the top of the potential barrier, which is called Virtual Source (VS), as shown in Fig. 2.3. The general expression for the current, if calculated at the VS, is [82]:

$$I_{\rm DS} = We(F^+ - F^-) \tag{2.20}$$

where  $F^+$  and  $F^-$  are the charge fluxes at the VS directed to the drain and to the source, respectively, defined as:

$$\begin{cases} F^+ = N^+_{\rm inv,VS} v^+_{\rm VS} \\ F^- = N^-_{\rm inv,VS} v^-_{\rm VS} \end{cases}$$

(2.21)

where  $N_{\text{inv}}^+$  and  $N_{\text{inv}}^-$  are the inversion densities of the carriers moving from source to drain and from drain to source, respectively. Similarly  $v^+$  and  $v^-$  are their average velocities.

Thus Eq. 2.20 becomes:

$$I_{\rm DS,bal} = We(N_{\rm inv,VS}^+ v_{\rm VS}^+ - N_{\rm inv,VS}^- v_{\rm VS}^-)$$

(2.22)

If we focus in the strong saturation regime, we can suppose that there are no carriers in the drain contact able to cross the barrier in the channel (which is larger than  $V_{\text{DS}}$ ). Thus we can assume:

$$N_{\rm inv,VS} = N_{\rm inv,VS}^+ + N_{\rm inv,VS}^-$$

(2.23)

$$\simeq N_{\rm inv,VS}^+$$

(2.24)

where  $N_{\rm inv,VS}$  is the total inversion density of the carriers at the virtual source.

Thus, the total drain current is:

$$I_{\text{bal,sat}} = WeN_{\text{inv,VS}}^+ v_{\text{VS}}^+ \simeq WeN_{\text{inv,VS}} v_{\text{VS}}$$

(2.25)

where  $v_{\rm VS}$  is the average velocity of the carriers at the VS, since all the carriers are crossing the potential barrier in the source-drain direction.

In linear regime, the potential barrier seen by the carriers in the drain is much smaller compared to the one in the saturation regime. As a consequence, we have that, even in a case without scattering, we can not assume that all the carriers at the VS are moving from the source to the drain. Thus, the approximation in Eq. 2.24 is not valid in linear regime, whereas it is reliable to assume that the average velocity of the carriers moving in the source-drain direction is the same as the average velocity moving in the opposite direction [78]:

$$v_{\rm VS}^+ = v_{\rm VS}^-$$

(2.26)

since  $V_{\rm DS}$  is small.

Since the carriers are at equilibrium in the source and drain contacts with Fermi level different by  $eV_{\rm DS}$ , assuming a Maxwell-Boltzmann distribution, we can express the inversion density of the carriers at the virtual source as [78]:

$$N_{\rm inv,VS}^{-} = N_{\rm inv,VS}^{+} e^{-\frac{eV_{\rm DS}}{K_{\rm B}T}}$$

(2.27)

the general expression for the drain current (Eq. 2.22) becomes:

$$I_{\rm bal,lin} = WeN_{\rm inv,VS}v_{\rm VS}^{+} \left(\frac{1 - e^{-\frac{eV_{\rm DS}}{K_{\rm B}T}}}{1 + e^{-\frac{eV_{\rm DS}}{K_{\rm B}T}}}\right)$$

(2.28)

When the device is in linear regime and  $V_{DS}$  is small, we can simplify Eq. 2.28 as:

...

$$I_{\rm bal,lin} = \frac{W}{2} e N_{\rm inv,VS} v_{\rm VS}^+ \frac{e V_{\rm DS}}{K_{\rm B}T}$$

(2.29)

#### 2.3.2 Analytic expressions for the current

From Fig. 2.3 we can see that the electric field driving the carriers at the VS is small (ideally null in the VS-section). Thus at first order we can assume a 1D electrostatics at the VS and write:

$$eN_{\rm inv,VS} = C_{\rm G}(V_{\rm GS} - V_{\rm TH})$$

(2.30)

We can further note that if the semiconductor is not in degenerate conditions, since carriers at the VS are in equilibrium with the source fermi level, their mean velocity becomes the thermal velocity  $v_{\rm T}$ , which takes the form [78]:

$$v_{\rm T} = \sqrt{\frac{2K_{\rm B}T}{\pi m^*}} \tag{2.31}$$

23

where  $m^*$  is the effective mass of the carrier as defined in Eq. 2.5. Using Eqs. 2.30 and 2.31, Eq. 2.25 can be re-written as:

$$I_{\rm bal,sat} \simeq W C_{\rm G} (V_{\rm GS} - V_{\rm TH}) v_{\rm T}$$

(2.32)

Concerning the linear regime, instead, Eq. 2.29 becomes:

$$I_{\rm bal,lin} \simeq \frac{W}{L} \mu_{\rm bal} C_{\rm G} (V_{\rm GS} - V_{\rm TH}) V_{\rm DS}$$

(2.33)

where we have used the so called *ballistic mobility* (usually called *apparent mobil-ity*) which takes the form:

$$\mu_{\rm bal} = \frac{eLv_{\rm T}}{2K_{\rm B}T} \tag{2.34}$$

The dependence of the drain current in Eq. 2.33 on the channel length L is not a real effect, and it appears in the expression due to the definition of the apparent mobility (proportional to L).

#### **2.3.3** Considerations about the ballistic transport model

We can see that Eq. 2.19 and Eq. 2.32 have similar expressions for the drain current in saturation regime, despite of the very different transport models used for their derivation.

Indeed, we saw that in the Drift - Diffusion model the current in ultimate MOS-FETs is limited by the  $v_{sat}$  which is strictly related to the inelastic scattering events and assumes a kind of uniform field profile. Eq. 2.32, instead, has been deduced assuming a transport without scattering events. The thermal velocity  $v_T$  is related to the mass of the carrier in the crystal  $m^*$ . Thus, while  $v_{sat}$  is related to the scattering events,  $v_T$  derives from the properties of the conduction band only.

A further difference between  $v_{sat}$  and  $v_T$  is the following: while  $v_{sat}$  is present where the driving field is the highest (usually the end of the MOS channel),  $v_T$ can be defined only where the driving field is small (the VS), confirming that the Drift-Diffusion and ballistic models, although giving similar expressions for  $L \rightarrow 0$ , are conceptually very different.

#### 2.4 The quasi ballistic transport regime

#### 2.4.1 Basics of the quasi-ballistic model

In Sec. 2.2.3 we have seen that the Drift-Diffusion model (Sec. 2.2) can not be reliably applied to short channel devices, due to its several approximations. However, also the ballistic model (Sec. 2.3) can not be safely applied to nowadays MOSFETs due to the assumption of no-scattering in the channel region (Sec. 2.3) [85, 86]. What it is possible to do is to consider an extension of the ballistic transport model to the case with scattering events. This framework is the so called *quasi ballistic transport regime* and can describe a device in which the number of scattering events occured is not negligible, but it is not large enough to thermalize the carriers as in the Drift-Diffusion model. We will see that this framework is able to cover both the Drift-Diffusion and the ballistic transport regimes as limiting cases.

The validity of the quasi-ballistic model is still debated [83, 87]. However, it has been shown in [88] that this model can be considered valid, but the evaluation of the effects of the scattering events is critical. We will briefly discuss this point in Sec. 2.4.3.

For the sake of simplicity and to be congruent with Sec. 2.3.2 we will adopt the Maxwell-Boltzmann statistics to derive analytical expressions for the currents in Secs. 2.4.2 and 2.4.3. However, similar results can be derived in the case of Fermi-Dirac statistics [89].

#### 2.4.2 Analytic expressions for the current

Firstly, we define the back-scattering coefficient r as [82]:

$$r = \frac{F^+}{F^-}$$

(2.35)

where  $F^+$  and  $F^-$  have been defined in Eq. 2.21. Eq. 2.35 is valid at high  $V_{\rm DS}$  where it has been assumed that there is no flux of the carriers from the drain contact to the source one. The proper modeling of the back-scattering coefficient r is the most critical point of the quasi ballistic model.

Starting from Eq. 2.20, and using Eqs. 2.35 and 2.21, we can write:

$$I_{\rm DS,Q-bal} = eWN_{\rm inv,VS}^+ v_{\rm VS}^+ (1-r)$$

(2.36)

Now we assume that Eq. 2.26 is valid for both the linear and saturation regimes. While this assumption is fulfilled in linear regime, it may become inaccurate in the saturation regime [85]. However, the impact of this assumption is not critical in the cases of pratical interest where r is small.

Using Eqs. 2.26 and 2.23, and remembering the definition of r (Eq. 2.35), we obtain:

$$N_{\rm inv,VS}^{+} = \frac{N_{\rm inv,VS}}{1+r}$$

(2.37)

Eq. 2.37 means that, regarding the saturation regime, since the carriers are backscattered towards the VS-section, the portion  $N^+$  of the inversion charge density at the VS effectively contributing to the  $I_{\rm DS}$  is not equal to the  $N_{\rm inv}$  (as in the ballistic case), but it is decreased by a factor r.

Thus, from Eq. 2.36 and 2.37 we obtain the expression valid in saturation regime [83]:

$$I_{\rm Q-bal,sat} \simeq W N_{\rm inv,VS} v_{\rm VS}^+ \left(\frac{1-r}{1+r}\right)$$

(2.38)

25

#### 2. The semi-classical approach and the Boltzmann transport equation

Finally, using a Maxwell-Boltzmann statistics and using Eq. 2.30, we finally have:

$$I_{\rm Q-bal,sat} \simeq W C_{\rm G} (V_{\rm GS} - V_{\rm TH}) v_{\rm T} \left(\frac{1-r}{1+r}\right)$$

(2.39)

Concerning the linear regime, instead, we can proceed as follows. It can be found that the generalization of Eq. 2.28 in the case with scattering events is [78]:

$$I_{\rm Q-bal,lin} = WeN_{\rm inv,VS}v_{\rm VS}^{+} \left(\frac{(1-r) - (1-r)e^{-\frac{eV_{\rm DS}}{K_{\rm B}T}}}{(1+r) + (1-r)e^{-\frac{eV_{\rm DS}}{K_{\rm B}T}}}\right)$$

(2.40)

Assuming  $V_{\rm DS} \ll K_{\rm B}T/e$  and Eq. 2.34, Eq. 2.40 reduces to:

$$I_{\rm Q-bal,lin} \simeq \frac{W}{L} \mu_{\rm bal} C_{\rm G} (V_{\rm GS} - V_{\rm TH}) V_{\rm DS} (1-r)$$

(2.41)

Comparing Eq. 2.33 with Eq. 2.41, we can see that, differently from the saturation case, the density of the carriers at the VS moving to the drain  $N_{\text{inv,VS}}^+$  is not modified by the introduction of the scattering events in the model.

#### 2.4.3 Models for the back-scattering coefficient

As already said, the evaluation of the r parameter is the most critical point of the quasi-ballistic model. Indeed, it is very difficult to develop analytical solutions of the Boltzmann transport equation valid in the quasi-ballistic transport regime. Thus, to obtain a compact model for the drain current one needs to introduce many simplifications to the problem.

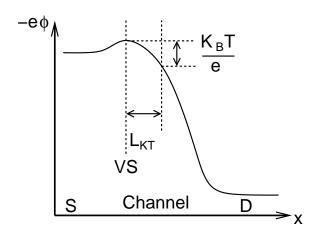

In the saturation regime, the coefficient r is assumed to be [82, 78]:

$$r = \frac{L_{\rm KT}}{L_{\rm KT} + \lambda} \tag{2.42}$$

where  $\lambda$  is the mean free path of the carriers and  $L_{\rm KT}$  is called *KT-layer* and it is defined as the distance over which the potential barrier in the channel falls of  $K_{\rm B}T/e$ , as shown in Fig. 2.4. Since the average energy of the back-scattered carriers is  $K_{\rm B}T/e$  [83], Eq. 2.42 means that only the back-scattered carriers that have to cross a barrier lower than their average energy can go back to the source contact. The validity of Eq. 2.42 has been analyzed in [88] where it has been found that the definitions of  $L_{\rm KT}$  and  $\lambda$  are critical in short channel devices [88].

For long channel devices, an approximated expression for  $L_{\rm KT}$  can be derived [82, 90]:

$$L_{\rm KT} = L \frac{2K_{\rm B}T}{e(V_{\rm GS} - V_{\rm TH})} \tag{2.43}$$

Indeed, under the GCA (Eq. 2.14) [78, 77], we can write:

$$L_{\rm KT} = \frac{K_{\rm B}T/e}{E_{\rm VS^+}} \tag{2.44}$$

Figure 2.4: Graphical definition of the KT-layer in the ballistic transport model.

where  $E_{VS^+}$  is the electric field at the VS, at the side of the drain direction. The value of  $E_{VS^+}$  can be obtained from the expression of the surface potential profile in the channel. Under the same assumptions leading to the analytic expression for  $I_{DS}$  in the Drift-Diffusion model (Sec. 2.2.2), it is possible to express the surface potential as [81]:

$$\phi_{\rm c}(l) = (V_{\rm GS} - V_{\rm TH}) \left(1 - \sqrt{1 - \frac{l}{L}}\right)$$

(2.45)

where l is:

$$l = x - x_{VS} \tag{2.46}$$

From Eq. 2.45 we can obtain:

$$E_{\rm VS^+} = -\frac{d\phi_{\rm c}(l)}{dl}\Big|_{0^+} = \frac{V_{\rm GS} - V_{\rm TH}}{2L}$$

(2.47)

Eqs. 2.44 and 2.47 bring us to Eq. 2.43.

The mean free path  $\lambda$  can be approximated as [90, 91, 78, 77, 92]:

$$\lambda = \frac{2\mu K_{\rm B}T}{ev_{\rm T}} \tag{2.48}$$

where  $\mu$  is the long channel mobility. The advantage of using Eqs. 2.42 and 2.48 is that the quasi ballistic model tends to the Drift - Diffusion when  $L_{\text{KT}} \gg \lambda$ .

In the linear regime, we assume a zero-field condition, i.e. all the device channel contributes to the back-scattering, and we thus write [82, 83, 77, 78]:

$$r = \frac{L}{L + \lambda} \tag{2.49}$$

27

In [88] it has been shown that Eqs. 2.48 and 2.49 well reproduce Monte Carlo simulations at low field. Finally it is worth noting that Eq. 2.33, 2.34, 2.48 and 2.49, we can obtain:

$$I_{\rm Q-bal,lin} = \frac{W}{L+\lambda} \mu C_{\rm G} (V_{\rm GS} - V_{\rm TH}) V_{\rm DS}$$

(2.50)

It is straightforward to see that for a long channel device, since we can assume  $L \gg \lambda$ , Eq. 2.50 reduces to Eq. 2.15. Thus, also in linear regime, the quasi-ballistic framework is consistent with the Drift-Diffusion model for long channel devices.

#### 2.5 Exact solution of the BTE: the Monte Carlo method

Since the effectiveness of the mobility  $\mu$  as performance indicator is hard to judge in short channel devices, we need other performance indicators. In this respect,  $v_{\rm T}$  and r can be used as the main performance indicators of the modern short devices. However, as previously said, the quasi ballistic transport regime is a complex intermediate condition between the Drift-Diffusion and ballistic models where both the crystal structure and the scattering events contribute in determining the current. Thus, an exact solution of the BTE is required to correctly model this transport regime. We now explain the basics of the exact solution of the BTE by means of the Monte Carlo method.

#### 2.5.1 Basics of the Monte Carlo method

The MonteCarlo (MC) is a direct (not approximate) statistical method to solve integral-differential equations, as the BTE [80]. In the case of transport in semiconductors, it consists of simulating the motion of one or many electrons inside the crystal, subject to the action of external forces due to applied electric field and of various scattering mechanisms.

In Sec. 2.4 we have seen that the quasi ballistic transport model can describe both short devices under off-equilibrium transport condition, but the modeling of the back scattering coefficient r (or the average velocity of the carriers  $v_T$ ) is non trivial. The Monte Carlo method can be used to determine these values in modern devices.

Entering the details of the model, the motion of a particle is considered semiclassical. Indeed, it is a sequence of free flights obeying the Newton's law, which is:

$$\frac{d\mathbf{p}}{dt} = -\nabla_{\mathbf{R}} E \tag{2.51}$$

where E is the total energy. During the free flight, the motion of the particle is also governed by:

$$\frac{d\mathbf{R}}{dt} = \mathbf{v}_{\rm g} = \nabla_{\mathbf{p}} E \tag{2.52}$$

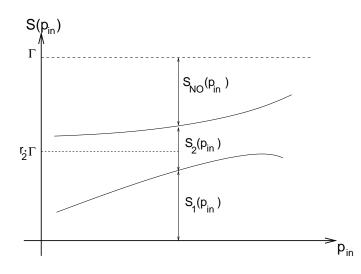

Figure 2.5: Graphic procedure for the determination of the type of the event suffered by a carrier whose state is  $p_{in}$ .

The free flights are interrupted by the scattering events. The scattering events are described by the scattering rates  $S(\mathbf{R}, \mathbf{p}', \mathbf{p})$ .  $S(\mathbf{R}, \mathbf{p}', \mathbf{p})$  is defined as the probability per unit time that a carrier in the position  $\mathbf{p}$  and with momentum  $\mathbf{p}$  scatters to a state with momentum  $\mathbf{p}'$ .

In the self-scattering scheme [93, 78], the free flight duration is:

$$t = -\Gamma^{-1}\ln(r_1) \tag{2.53}$$

where  $r_1$  is a random number whose probability distribution is uniform from 0 to 1.  $\Gamma$  is a number larger than the maximum total scattering rate (self-scattering technique), which is:

$$\Gamma > [S_{\text{TOT}}(\mathbf{p})]_{\text{MAX}} = \left[\sum_{i} \sum_{\mathbf{p}'} S_i(\mathbf{p}', \mathbf{p})\right]_{\text{MAX}}$$

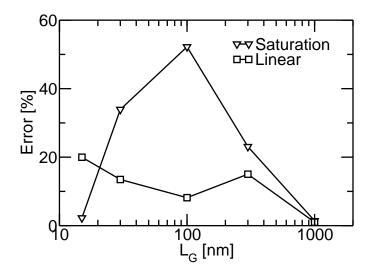

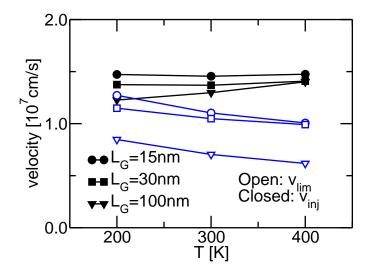

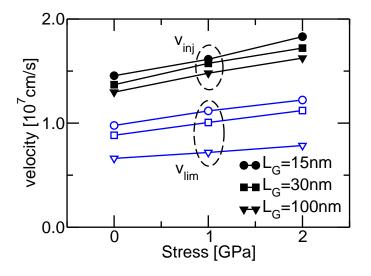

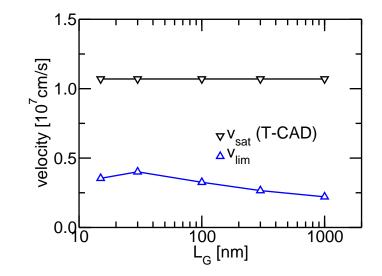

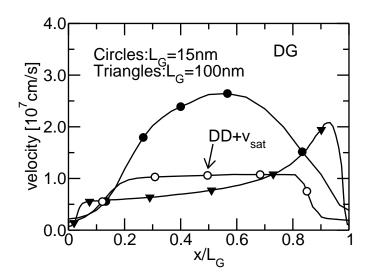

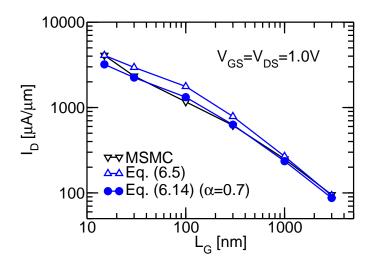

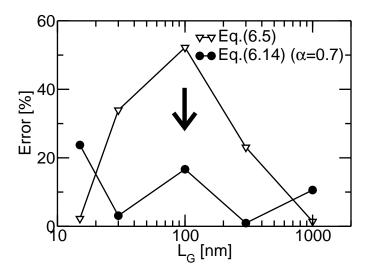

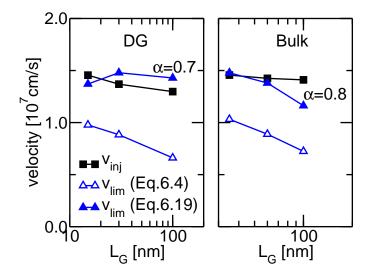

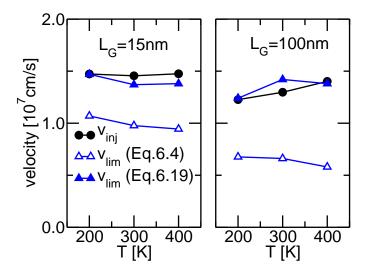

(2.54)