## Particle-Based Modeling of Reliability for Millimeter-Wave GaN Devices

for Power Amplifier Applications

by

Alvaro D. Latorre Rey

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved April 2018 by the Graduate Supervisory Committee:

Marco Saraniti, Chair Jennifer Kitchen Stephen M. Goodnick Trevor Thornton

ARIZONA STATE UNIVERSITY

May 2018

#### ABSTRACT

In this work, an advanced simulation study of reliability in millimeter-wave (mmwave) GaN Devices for power amplifier (PA) applications is performed by means of a particle-based full band Cellular Monte Carlo device simulator (CMC). The goal of the study is to obtain a systematic characterization of the performance of GaN devices operating in DC, small signal AC and large-signal radio-frequency (RF) conditions emphasizing on the microscopic properties that correlate to degradation of device performance such as generation of hot carriers, presence of material defects and self-heating effects. First, a review of concepts concerning GaN technology, devices, reliability mechanisms and PA design is presented in chapter 2. Then, in chapter 3 a study of non-idealities of AlGaN/GaN heterojunction diodes is performed, demonstrating that mole fraction variations and the presence of unintentional Schottky contacts are the main limiting factor for high current drive of the devices under study. Chapter 4 consists in a study of hot electron generation in GaN HEMTs, in terms of the accurate simulation of the electron energy distribution function (EDF) obtained under DC and RF operation, taking into account frequency and temperature variations. The calculated EDFs suggest that Class AB PAs operating at low frequency (10 GHz) are more robust to hot carrier effects than when operating under DC or high frequency RF (up to 40 GHz). Also, operation under Class A yields higher EDFs than Class AB indicating lower reliability. This study is followed in chapter 5 by the proposal of a novel  $\Pi$ -Shaped gate contact for GaN HEMTs which effectively reduces the hot electron generation while preserving device performance. Finally, in chapter 6 the electro-thermal characterization of GaN-on-Si HEMTs is performed by means of an expanded CMC framework, where charge and heat transport are selfconsistently coupled. After the electro-thermal model is validated to experimental data, the assessment of self-heating under lateral scaling is considered.

### ACKNOWLEDGMENTS

The successful completion of a Ph.D. program is, in my experience, a group effort that reflects the contributions and hard work of many people, not only the student leading the research. For this reason, I would like to begin this dissertation by gratefully acknowledging all of those who one way or another have been part of this work.

First, I want to thank my advisor Dr. Marco Saraniti for his robust support, guidance and patience. Doing research for a living guarantees a world of challenges and uncertainty. However, Dr. Saraniti provided me with a solid ground of technical and financial resources, allowing me to pursue my interests and successfully produce measurable contributions. Special thanks are due to Dr. John D. Albrecht, at Michigan State University, East Lansing - MI, for the continuous technical support, discussions and suggestions. I am very thankful for the technical support provided by Dr. Gregg Jessen at the Air Force Research Laboratory (AFRL), in terms of measurements of experimental devices used in this research. Also, I am very grateful for the funding that supported this work, provided by the Air Force Office of Scientific Research (AFOSR) and the AFRL. Finally, I would like to express my gratitude to the members of my committee: Dr. Stephen Goodnick, Dr Jennifer Kitchen and Dr. Trevor Thornton for disposing of their time and technical expertise in evaluating this work.

In a more personal note, I want to express my deepest gratitude to Cyndi, my most valuable finding during the Ph.D., my best friend and soon to be wife, for patiently walking with me through this strenuous path. Her love, kindness and support have been a light in the darkness, from which I have found the strength and encouragement to move forward. I am forever in debt for the unconditional love and support my parents and sister have given me throughout all these years. Without them none of this would have been possible. At last, but not least, I want to thank my friends and colleagues for making these experience a joyful and enjoyable one.

|      |      |        | P                                                    | age |

|------|------|--------|------------------------------------------------------|-----|

| LIST | OF F | IGURI  | ES                                                   | vii |

| CHAI | PTER | t      |                                                      |     |

| 1    | INT  | RODU   | CTION                                                | 1   |

|      | 1.1  | Model  | ling of Semiconductor Devices                        | 7   |

|      | 1.2  | Overv  | iew of this Work                                     | 13  |

| 2    | REV  | /IEW ( | OF GAN TECHNOLOGY AND POWER AMPLIFIERS               | 15  |

|      | 2.1  | Polari | zation Effects in GaN                                | 15  |

|      | 2.2  | AlGal  | N/AlN/GaN Devices                                    | 20  |

|      |      | 2.2.1  | High Electron Mobility Transistors (HEMTs)           | 21  |

|      |      | 2.2.2  | Hot Electron Transistors (HETs)                      | 28  |

|      | 2.3  | Reliab | bility of GaN HEMTs                                  | 30  |

|      |      | 2.3.1  | Hot Electron Effects                                 | 31  |

|      |      | 2.3.2  | Self-heating Current Collapse                        | 36  |

|      |      | 2.3.3  | Threading Dislocations                               | 38  |

|      |      | 2.3.4  | Inverse Piezoelectric effect                         | 40  |

|      |      | 2.3.5  | Electrical-Stress Testing Conditions                 | 42  |

|      | 2.4  | Radio  | Frequency Power Amplifiers                           | 47  |

|      |      | 2.4.1  | Class A Operation                                    | 57  |

|      |      | 2.4.2  | Class AB Operation                                   | 60  |

|      | 2.5  | Concl  | usions                                               | 64  |

| 3    | STU  | DY OF  | F NON-IDEALITIES IN III-N ISOTYPE HETERJUNCTION      |     |

|      | DIO  | DES    |                                                      | 65  |

|      | 3.1  | Introd | luction                                              | 65  |

|      | 3.2  | Chara  | cterization of Experimental Device with Ideal Layout | 68  |

# TABLE OF CONTENTS

# CHAPTER

|   | 3.3 | Mole Fraction Variations in the $Al_xGa_{1-x}N/GaN$ Barrier |  |  |

|---|-----|-------------------------------------------------------------|--|--|

|   | 3.4 | Effect of Emitter and Base Schottky Contacts                |  |  |

|   | 3.5 | Conclusions                                                 |  |  |

| 4 | HO  | T ELECTRON GENERATION UNDER LARGE-SIGNAL RF OP-             |  |  |

|   | ERA | ERATION OF GAN HEMTS 8                                      |  |  |

|   | 4.1 | Introduction                                                |  |  |

|   | 4.2 | GaN HEMT Model Validation 89                                |  |  |

|   | 4.3 | Large Signal RF Characterization                            |  |  |

|   | 4.4 | Hot Electron Generation                                     |  |  |

|   | 4.5 | High Frequency RF Operation    98                           |  |  |

|   | 4.6 | High Temperature Operation101                               |  |  |

|   | 4.7 | Comparison between Class A and Class AB Operation           |  |  |

|   | 4.8 | Conclusions                                                 |  |  |

| 5 | АΠ  | I-SHAPED GATE DESIGN FOR REDUCING HOT ELECTRON              |  |  |

|   | GEI | NERATION IN GAN HEMTS111                                    |  |  |

|   | 5.1 | Introduction                                                |  |  |

|   | 5.2 | Performance of Π-gated HEMTs113                             |  |  |

|   |     | 5.2.1 Principles of Operation                               |  |  |

|   |     | 5.2.2 DC, small-signal AC and large-signal RF Operation115  |  |  |

|   | 5.3 | Reduced Hot Electron Generation119                          |  |  |

|   |     | 5.3.1 Energy Distribution in DC Regime                      |  |  |

|   |     | 5.3.2 Energy Distribution under RF Operation                |  |  |

|   | 5.4 | Conclusions                                                 |  |  |

Page

| 6 ELECTRO-THERMAL CHARACTERIZATION OF $GAN$ HEMT ON |  |  |  |  |

|-----------------------------------------------------|--|--|--|--|

| SI THROUGH SELF-CONSISTENT ENERGY BALANCE-CELLULAR  |  |  |  |  |

| MONTE CARLO DEVICE SIMULATIONS                      |  |  |  |  |

| 6.1 Introduction                                    |  |  |  |  |

| 6.2 Energy Balance Flux Approach                    |  |  |  |  |

| 6.3 Electro-Thermal Device Simulations              |  |  |  |  |

| 6.4 DC Electro-Thermal Characterization             |  |  |  |  |

| 6.5 Impact of Lateral Scaling on Self-Heating142    |  |  |  |  |

| 6.5.1 Gate-to-Drain $L_{GD}$ Scaling                |  |  |  |  |

| 6.5.2 Source-to-Gate $L_{SG}$ Scaling               |  |  |  |  |

| 6.6 Conclusions                                     |  |  |  |  |

| 7 SUMMARY                                           |  |  |  |  |

| REFERENCES                                          |  |  |  |  |

## LIST OF FIGURES

| Figure | P                                                                           | age |

|--------|-----------------------------------------------------------------------------|-----|

| 1.1    | Comparison of semiconductor material properties which enable high           |     |

|        | power and high frequency operation [3]                                      | 2   |

| 1.2    | Diagram of Power-Frequency range of different technologies of semi-         |     |

|        | conductor devices [4]                                                       | 3   |

| 1.3    | Commercially available GaN HEMT products released by Cree Inc,              |     |

|        | showing (a) Discrete 50V GaN HEMT devices for radar and military            |     |

|        | communications and (b) High power MMIC for satellite communications.        | 5   |

| 1.4    | Flowchart of the particle-based Cellular Monte Carlo algorithm (CMC).       | 10  |

| 1.5    | Full electronic-band structure (a) and Phonon dispersion (b) of Wurtzite    |     |

|        | GaN (HCP) used in this work.                                                | 11  |

| 1.6    | GaN scattering rates at $T = 300$ K used in this work                       | 12  |

| 2.1    | Crystal structure of GaN in Wurtzite form showing (a) Highlighted           |     |

|        | Hexagonal Closed Packed (HCP) sublattice for cation Ga, and (b)             |     |

|        | Typical growth planes, indicating the Ga-polar c-plane $\{0001\}$ and the   |     |

|        | semi-polar $\{112\overline{2}\}$ plane                                      | 16  |

| 2.2    | Polarization vectors (Spontaneous $P_{SP}$ and Piezoelectric $P_{PE}$ ) and |     |

|        | equivalent interface charge for Ga-polar $AlGaN/GaN$ heterostructures       |     |

|        | under different growth conditions of the top layer: (a) AlGaN relaxed,      |     |

|        | (b) AlGaN Tensile strain and (c) GaN Compressive strain, while keep-        |     |

|        | ing the bottom layer relaxed                                                | 19  |

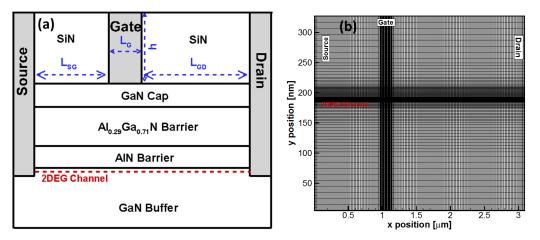

| 2.3    | Basic structure of a Ga-polar $AlGaN/AlN/GaN$ HEMT showing (a)              |     |

|        | device layout and (b) non-uniform grid used for CMC device simulations.     | 22  |

Figure

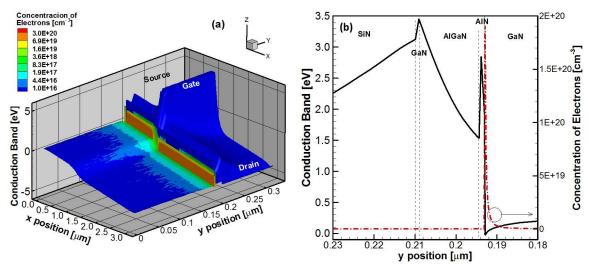

- 2.4 Band diagram of the simulated GaN-HEMT from figure 2.3 at DC bias of  $V_{DS} = 5$  V and  $V_{GS} = -5$  V. Panel (a) shows the 3D conduction band profile with the carrier concentration as contour, while panel (b) shows the vertical profile of the conduction band along with the carrier concentration, taken from a slice on the source-to-gate access region... 26

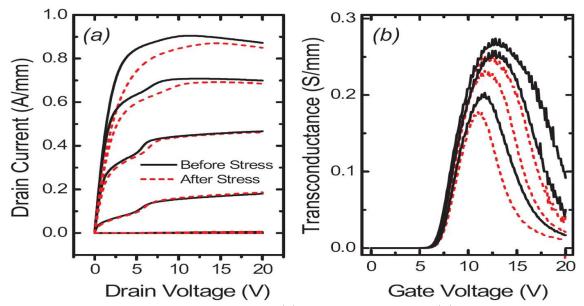

- 2.8 Signature degradation of (a) drain current and (b) transconductance caused by hot-electron effects in the AlGaN barrier of an experimental GaN HEMT. The figure is reproduced from original research presented by Meneghini et al. [26].

35

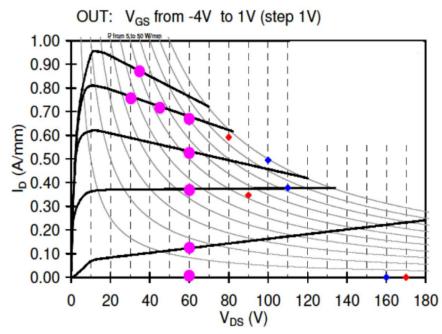

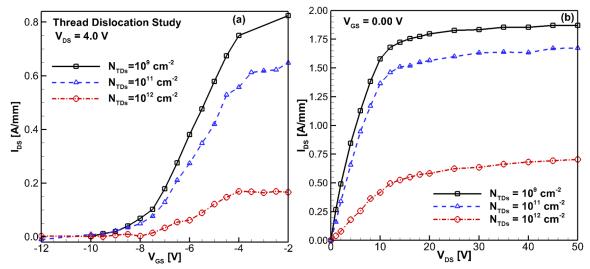

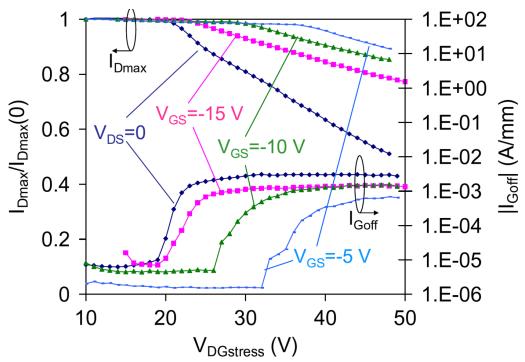

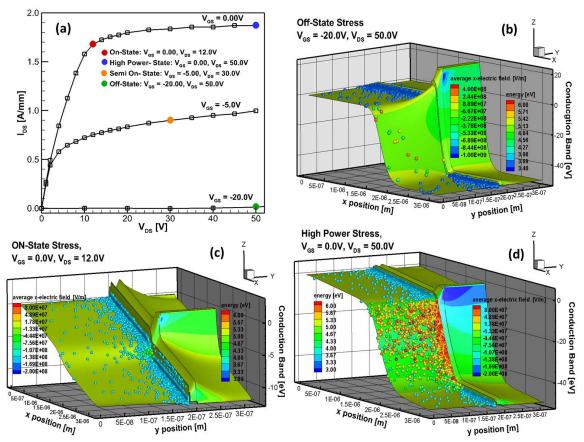

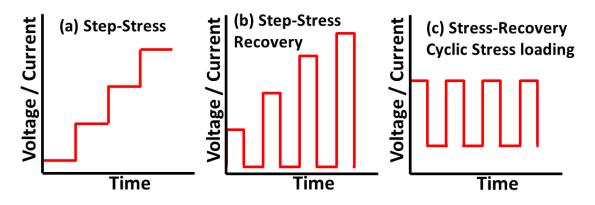

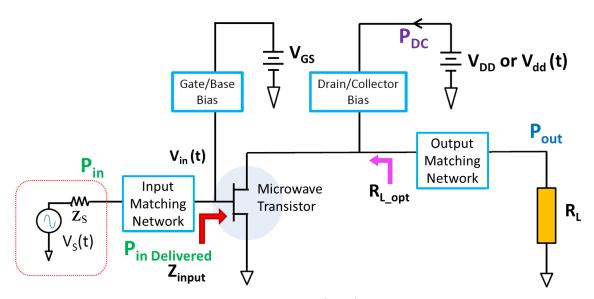

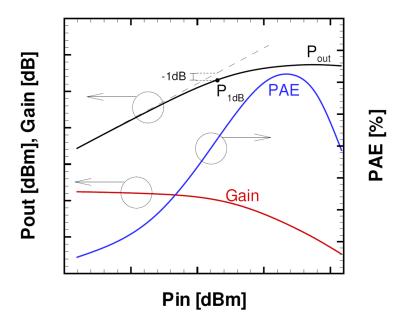

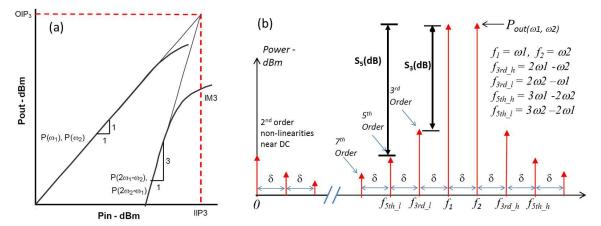

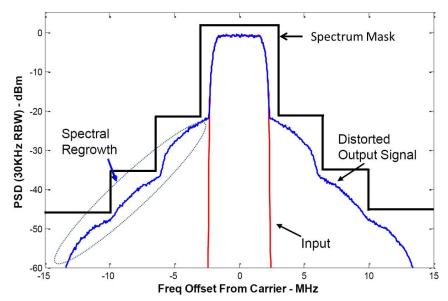

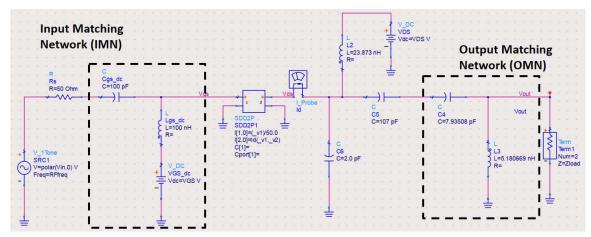

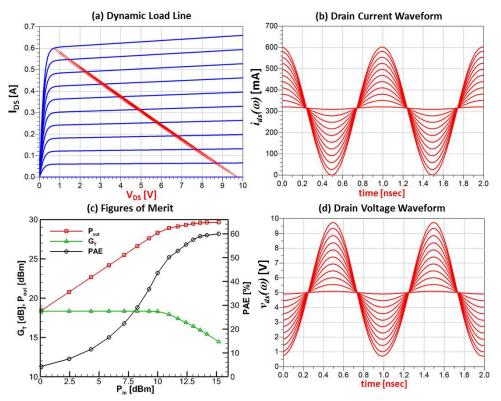

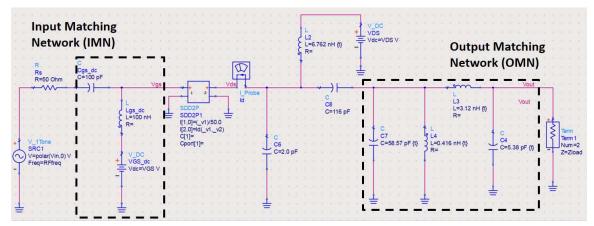

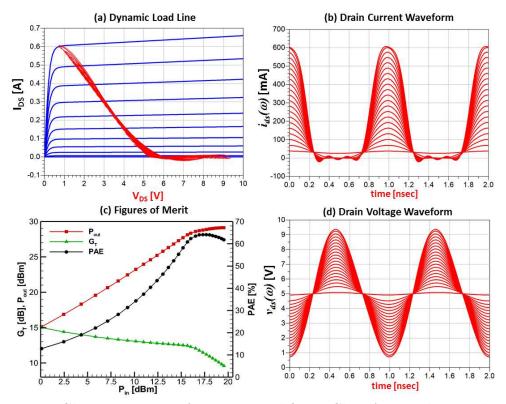

2.10 Effect of thread dislocations (TDs) in the electrical performance of GaN HEMTs, shown with simulations of (a)  $I_{DS}$ - $V_{GS}$  and (b)  $I_{DS}$ - $V_{DS}$ curves at three different TDs density  $N_{TDs}$ ..... 40 2.11 Signature degradation of drain current (left axis) and gate leakage current (right axis) in an experimental GaN HEMT caused by the inverse piezoelectric effect. Figure reproduced from original research presented by del Alamo and Joh [69]..... 41 2.12 Electrical stress characterization of GaN HEMTs, showing (a)  $I_{DS}$ - $V_{DS}$  curves indicating stress bias points. Also, in (b) to (d) the electric field mapping is presented on 3D band diagrams of the device for 3 stress bias points. The spheres represent a snap-shot of real-space distribution of carriers with its corresponding energy as a contour..... 44 2.13 Voltage or Current signal waveforms used in short-term life-time reliability testing, identifying the 3 main protocols (a) Stepped-Stress, (b) Step-Stress Recovery and (c) Stress-Recovery Cyclic Stress loading..... 46 2.14 Schematic of Power Amplifier (PAs) circuits..... 48 2.15 Sketch of figures of Merit for a typical power amplifier for single-tone input, showing output power  $P_{out}$  and transducer gain  $G_T$  on the leftaxis, and power added efficiency PAE in the right-axis as a function of the input power  $P_{in}$ . Also indicated the 1dB compression point  $P_{1dB}$ ... 52 2.16 Sketch of Inter Modulation Distortion (IMD) measurements for a power amplifier (PA) with a two-tone input signal separated by a small frequency  $\delta = f_{\omega 2} - f_{\omega 1}$ . Determining IIP3 and OIP3 can be done from measuring (a) output power delivered to fundamental and harmonic frequencies vs input power sweep, and (b) Output power spectrum of the PA for a given input. 542.17 Example of the output spectrum of a PA with a single carrier WCDMA input signal band limited to 5 MHz, evidencing the spectral regrowth used in Adjacent Channel Power Ratio (ACPR) measurments. A typical spectrum mask is also included. 562.18 Schematic of a Class A power amplifier circuit topology, simulated with commercial software Advanced Design System (ADS) by Keysight. The active device is simulated by using the analytical model by Statz, and the input and output matching networks are identified. ..... 58 2.19 Characterization of a Class A power amplifier, obtained with simulations of the schematic shown in figure 2.18. In the panels is presented (a)  $I_{DS}$ - $V_{DS}$  space along with load-lines, (b) ac current waveform  $i_{ds}(\omega)$ , (d) ac drain voltage waveform  $v_{ds}(\omega)$  and (c) typical figures of merit. . . 59 2.20 Schematic of a Class AB power amplifier circuit topology, simulated with commercial software Advanced Design System (ADS) by Keysight. The active device is simulated by using the analytical model by Statz, and

| 2.21 | Characterization of a power amplifier in Class AB topology with tuned-                     |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | load. The Results correspond to simulations of the schematic from                          |    |

|      | figure 2.20, showing (a) $I_{DS}$ - $V_{DS}$ space along with load-lines, (b) ac           |    |

|      | current waveform $i_{ds}(\omega)$ , (d) ac drain voltage waveform $v_{ds}(\omega)$ and (c) |    |

|      | typical figures of merit                                                                   | 63 |

| 3.1  | Experimental device layout corresponding to the ideal structure of the                     |    |

|      | emitter-base diode. The emitter and base contacts are included                             | 68 |

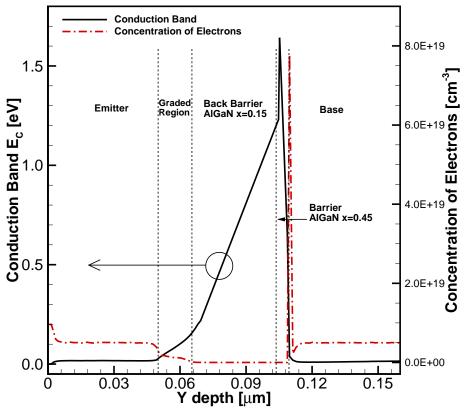

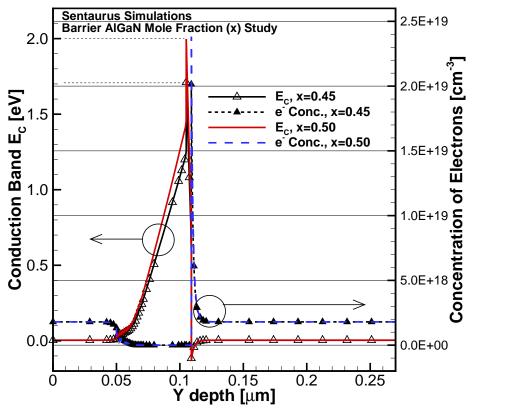

| 3.2  | Profile of the conduction band in thermal equilibrium ( $V_{be}=0.00$ V),                  |    |

|      | along with the concentration of electrons (right-axis) as obtained with                    |    |

|      | CMC simulations                                                                            | 69 |

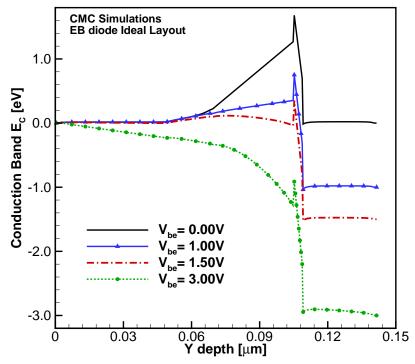

| 3.3  | Evolution with bias of the conduction band profile along the y-direction                   |    |

|      | of the EB diode as obtained with CMC simulations                                           | 70 |

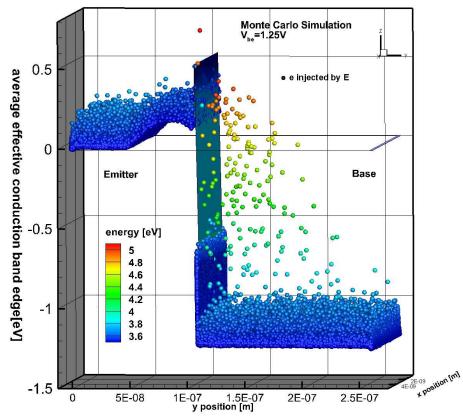

| 3.4  | Conduction Band in 3D and a snap-shot of the electron distribution in                      |    |

|      | real space at $V_{be} = 1.25$ V. The color of each super-particle corresponds              |    |

|      | to its energy.                                                                             | 71 |

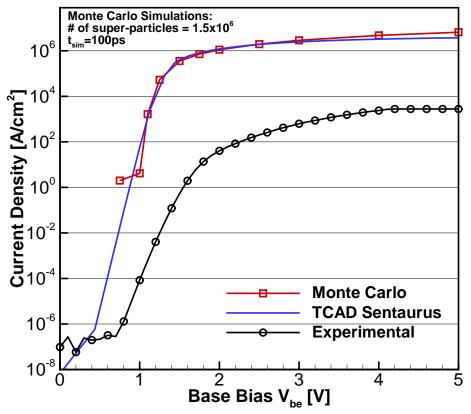

| 3.5  | IV characteristic in semi-log scale of emitter-base diode, showing ex-                     |    |

|      | perimental data along with simulation results obtained by CMC, and                         |    |

|      | TCAD Sentaurus simulations                                                                 | 73 |

| 3.6  | Vertical profile of the conduction band in equilibrium (left-axis) for                     |    |

|      | AlGaN with mole fractions $x = 0.45$ and 0.50. The corresponding                           |    |

|      | concentration of electrons is also shown in the right-axis                                 | 75 |

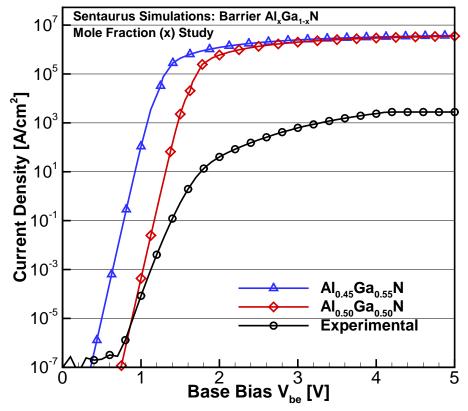

| 3.7  | IV characteristic in semi-log scale, showing experimental data, along                      |    |

|      | with simulation results for mole fraction values $x = 0.45$ and 0.50, at                   |    |

|      | the $Al_xGa_{1-x}N/GaN$ barrier                                                            | 76 |

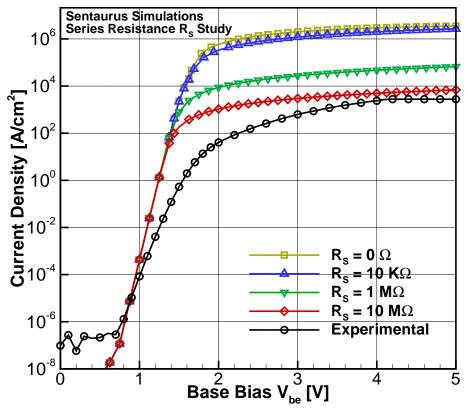

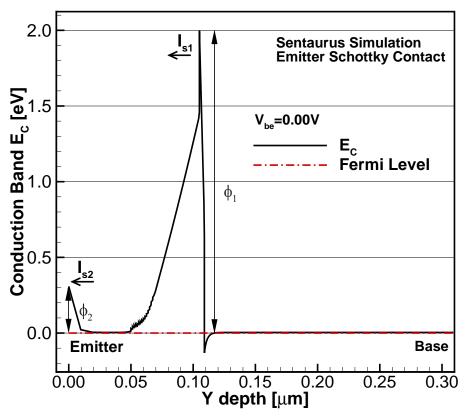

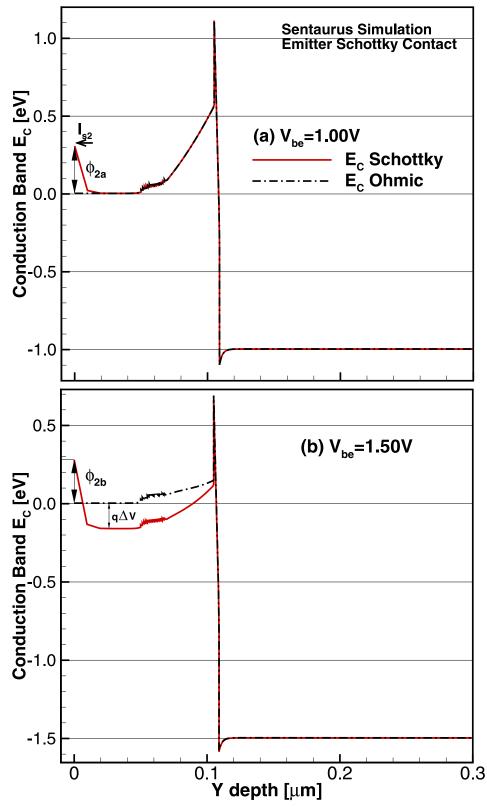

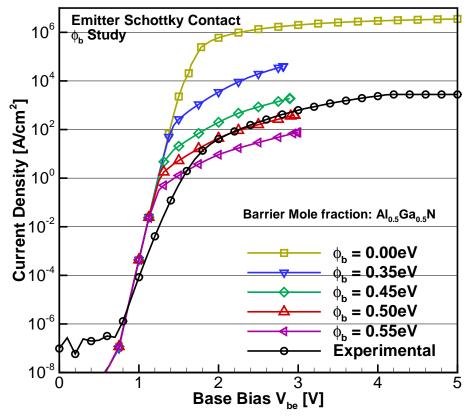

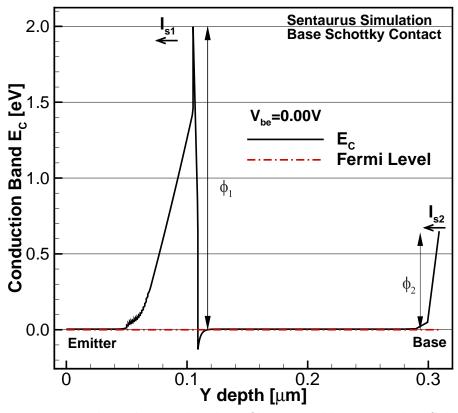

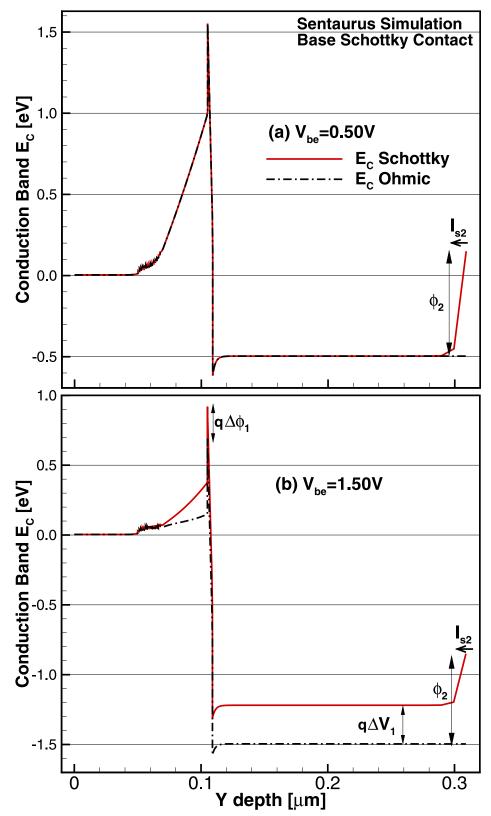

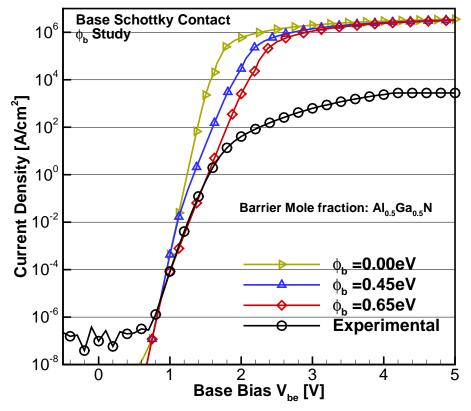

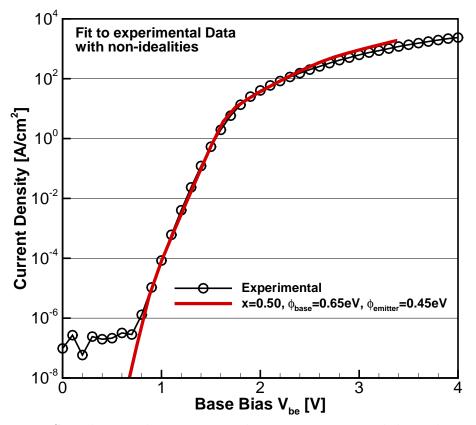

- 3.8IV characteristic in semi-log scale of the EB diode showing experimental data, along with TCAD simulation results for different values of parasitic series resistance  $R_S$  in the contacts..... 77 Vertical conduction band profile at equilibrium, where a Schottky con-3.93.10 Vertical conduction band profile with and without emitter Schottky contact for a)  $V_{be} = 1.0$  V and b)  $V_{be} = 1.5$  V, with Schottky barrier height  $\phi_2 = 0.45 \,\text{eV}$ , while keeping an ohmic base contact. 80 3.11 IV characteristic in semi-log scale, showing experimental data along with simulation results including the effect of a Schottky contact at 3.12 Vertical conduction band profile at equilibrium, with a Schottky contact placed at the base with barrier height  $\phi_2 = 0.65 \,\mathrm{eV}$ , while keeping an ohmic emitter contact. 82 3.13 Vertical conduction band profile with and without base Schottky con-3.14 IV characteristic in semi-log scale showing experimental data, along with simulation results including the effect of a Schottky contact at the base, with different barrier heights. ..... 84 3.15 Semi-log IV characteristic, showing experimental data along with the simulated curve corresponding to a structure with  $Al_{0.50}Ga_{0.50}N, \phi_{base} =$ 85

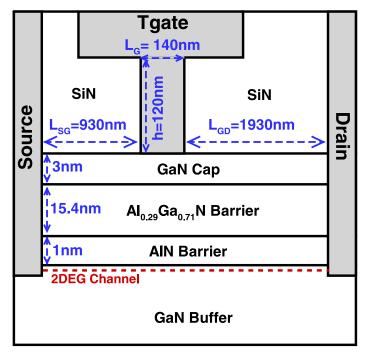

- 4.1 Device layout of the fabricated GaN HEMT used in the CMC model... 90

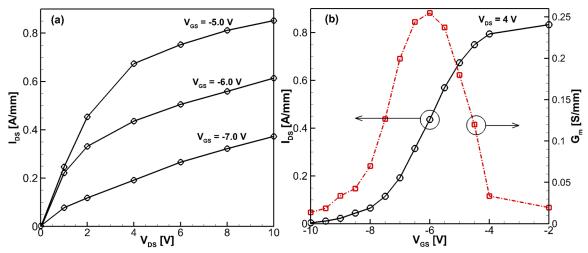

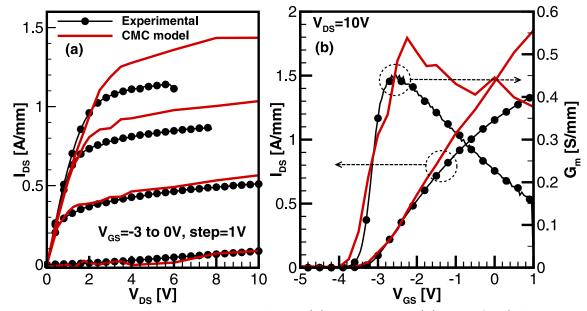

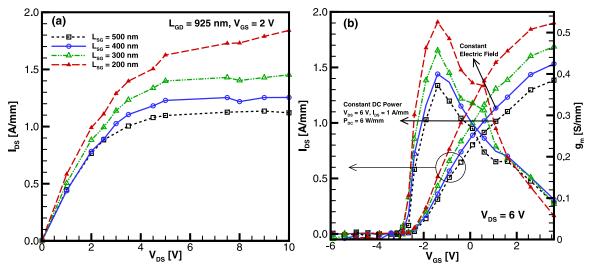

| 4.2 | Experimental and simulated (a) output and (b) transfer (along with                                 |    |

|-----|----------------------------------------------------------------------------------------------------|----|

|     | Transconductance $G_m$ ) characteristics                                                           | 91 |

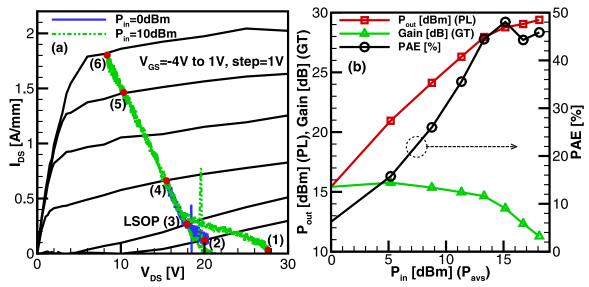

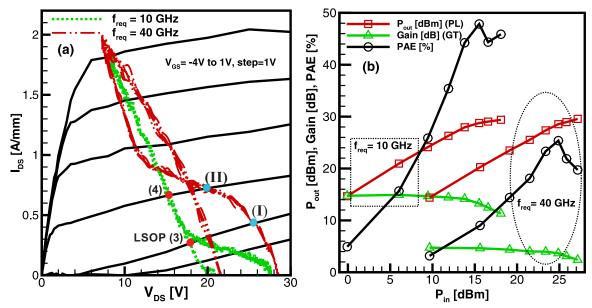

| 4.3 | Power amplifier characterization under Class AB $(RF)$ operation, show-                            |    |

|     | ing (a) dynamic load-lines and (b) FOM, for $f_{req} = 10 \text{ GHz}$ and tuned-                  |    |

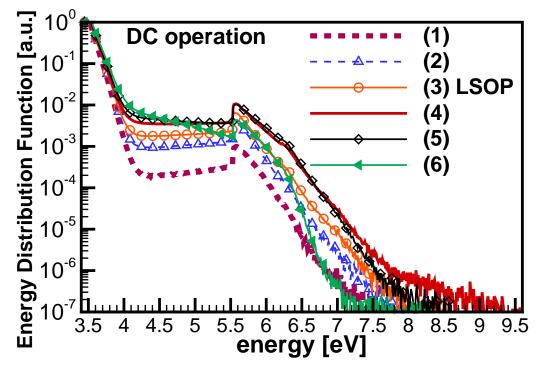

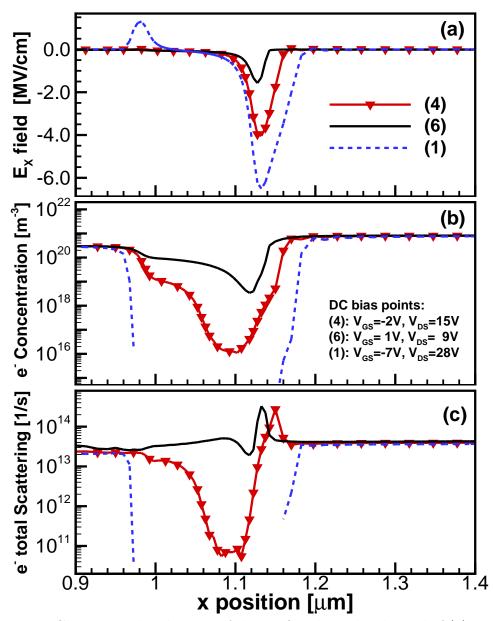

|     | load $Z_{Load} = 100 \Omega$                                                                       | 93 |

| 4.4 | Electron energy distribution function for the DC bias points $(1)$ to $(6)$                        |    |

|     | indicated in figure 4.3 (a) with solid dots. $\dots$                                               | 94 |

| 4.5 | Close up under the gate of the profile along the channel of (a) x-                                 |    |

|     | component of the Electric field $E_x$ , (b) electron concentration and (c)                         |    |

|     | total scattering at DC bias points $(4)$ , $(6)$ and $(1)$ from figure 4.4, which                  |    |

|     | trace the load-line in figure 4.3 (a). $\dots$                                                     | 96 |

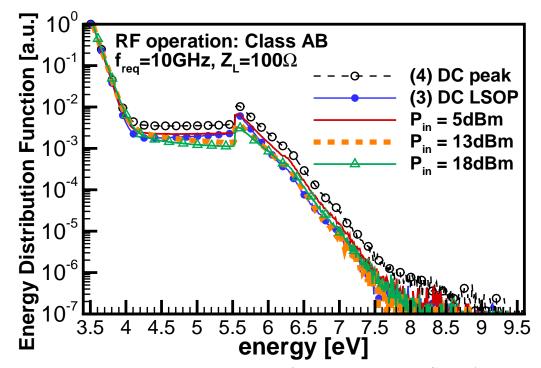

| 4.6 | Electron energy distribution function under RF Class AB operation for                              |    |

|     | different input powers. Curves for DC peak generation $(4)$ and LSOP                               |    |

|     | (3) from figure 4.4 also shown for comparison                                                      | 97 |

| 4.7 | Frequency study of power amplifier characterization under Class AB                                 |    |

|     | (RF) operation, showing (a) dynamic load-lines and (b) FOM, at fre-                                |    |

|     | quencies of $f_{req} = 10 \text{ GHz}$ and $40 \text{ GHz}$ and tuned-load $Z_{Load} = 100 \Omega$ | 99 |

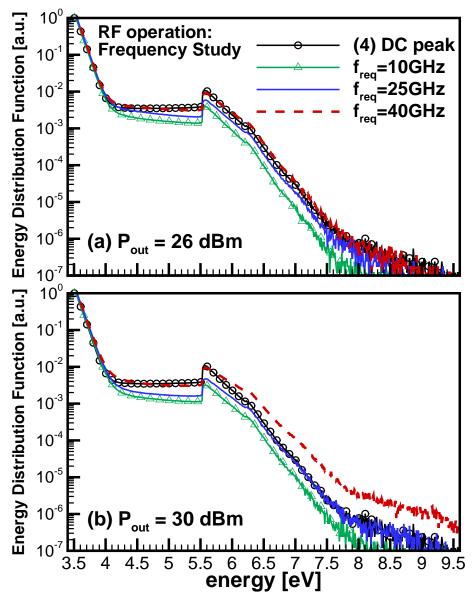

| 4.8 | Frequency study of the energy distribution function for Class AB op-                               |    |

|     | eration at (a) $P_{out} = 26 \text{ dBm}$ and (b) $P_{out} = 30 \text{ dBm}$                       | 00 |

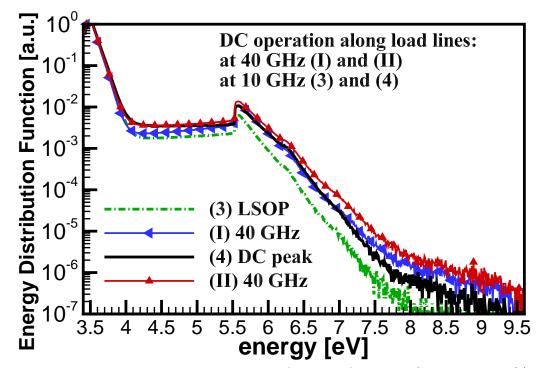

| 4.9 | Electron energy distribution function for the DC bias points (I), (II)                             |    |

|     | and $(3)$ , $(4)$ indicated in figure 4.7 (a) with solid dots, corresponding to                    |    |

|     | DC points along the load-lines at 40 GHz and 10 GHz respectively1                                  | 02 |

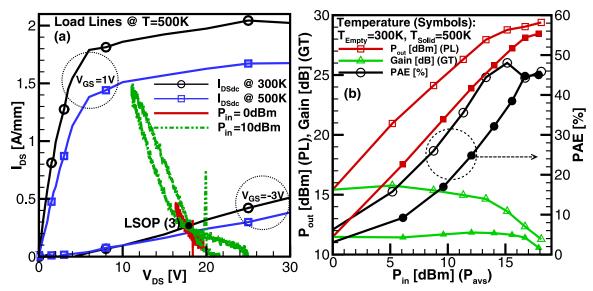

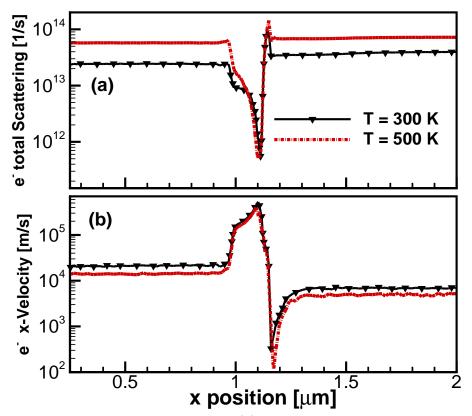

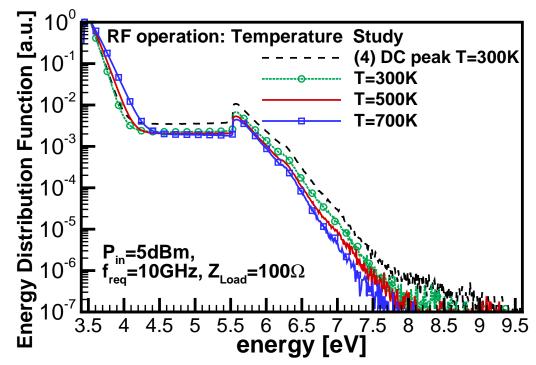

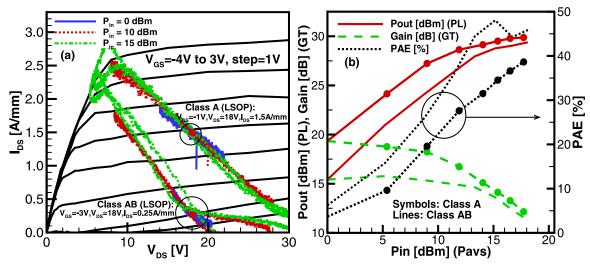

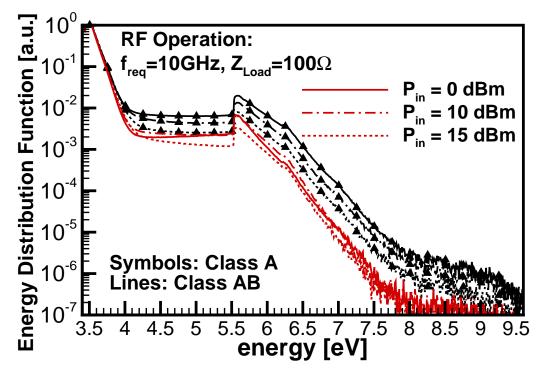

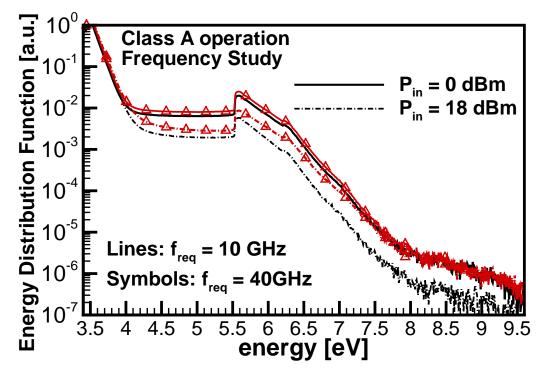

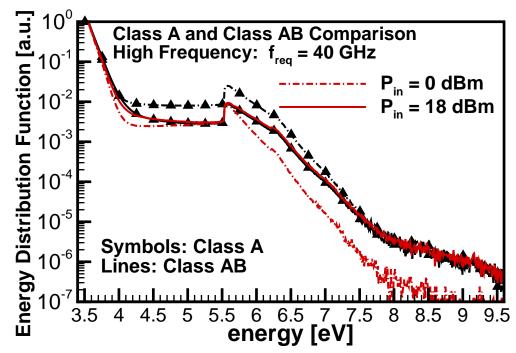

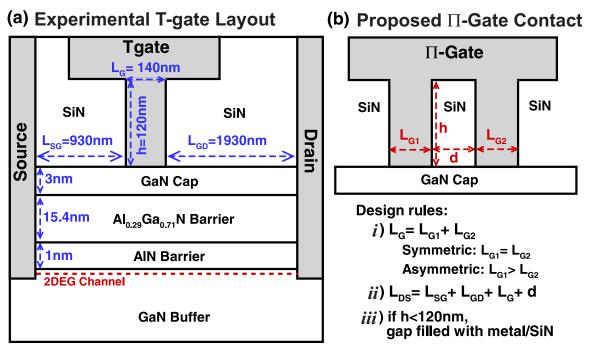

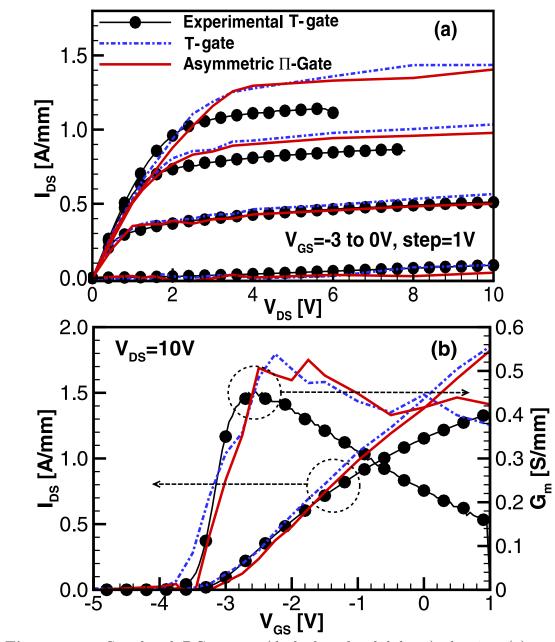

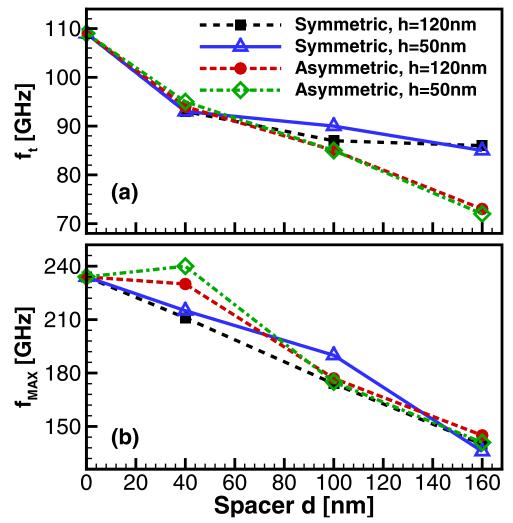

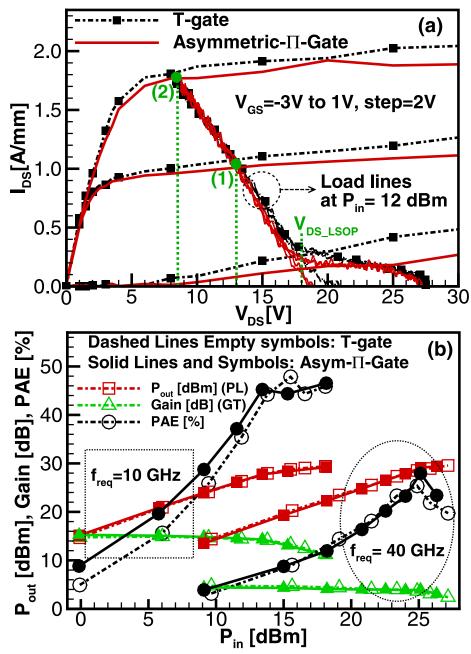

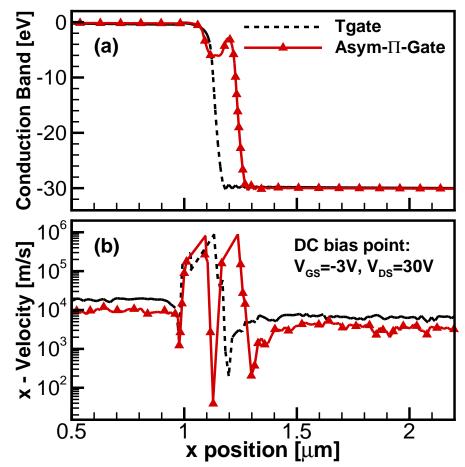

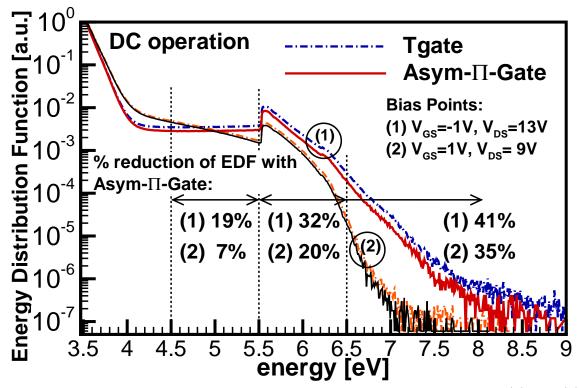

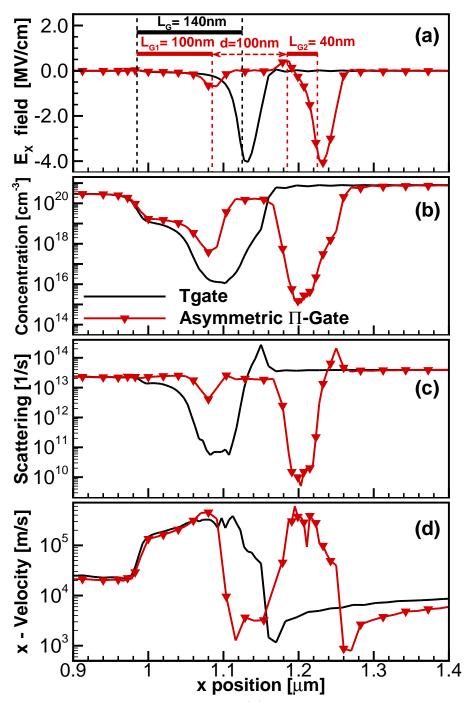

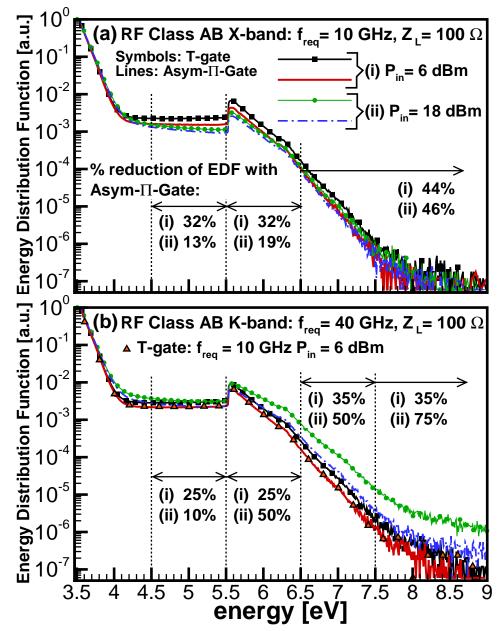

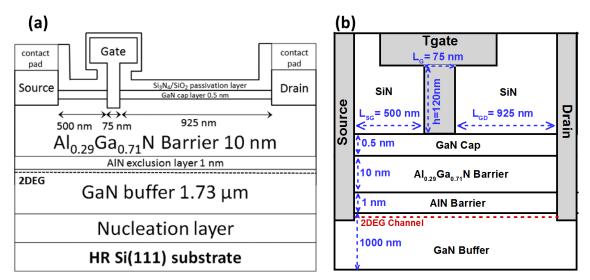

4.10 Effect of temperature in Class AB operation for  $f_{req} = 10 \text{ GHz}$  and  $Z_{Load} = 100 \Omega$  showing (a)  $I_{DS}$ - $V_{DS}$  curves along with load-lines, and 4.11 Effect of temperature on (a) the total scattering rate and (b) the xcomponent of the electron velocity, shown in a region under the gate 4.12 Temperature dependence of the distribution function for Class AB op-4.13 Power amplifier characterization under Class A and Class AB operation for  $f_{req} = 10 \text{ GHz}$  and tuned-load  $Z_{Load} = 100 \Omega$ , showing (a) dynamic load-lines along with  $I_{DS}$ - $V_{DS}$  curves. Also, the typical figures of merit are shown in (b) where lines with and without symbols correspond to Class A and Class AB respectively......106 4.14 Electron energy distribution function under Class A (lines with symbols) and Class AB (lines) PA operation, at 3 input powers  $P_{in} = 0 \, \text{dBm}$ , 4.15 Frequency study of the electron energy distribution function in Class A operation for  $f_{req} = 10 \text{ GHz}$  (lines) and 40 GHz (lines with symbols) 4.16 Comparison of electron energy distribution function at high frequency operation, under Class A (lines with symbols) and Class AB (lines) Device layout showing (a) the experimental T-gate geometry from fab-5.1

ricated devices (b) the proposed  $\Pi$ -gate, including design rules.....114

5.2

5.3

5.4

- 5.6 Electron energy distribution function for the DC bias points (1) and

(2) shown in figure 5.4 (a) for T-gate and asymmetric Π-gate devices. ...122

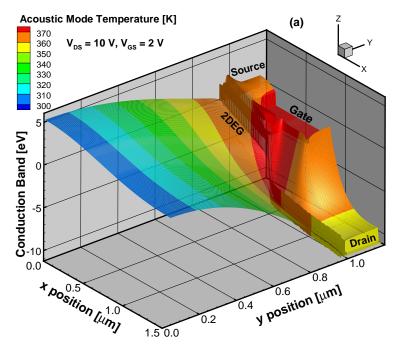

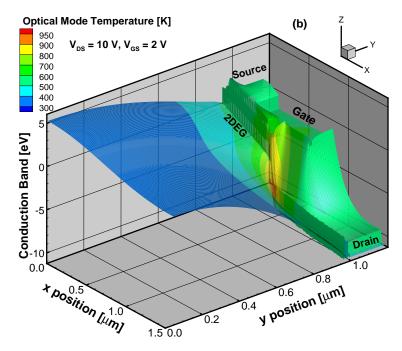

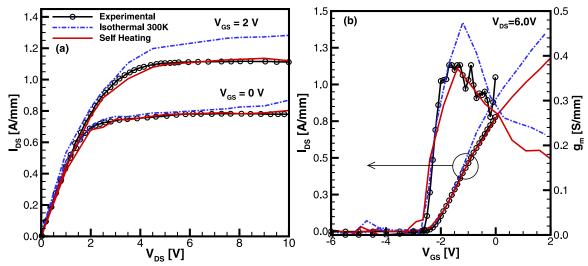

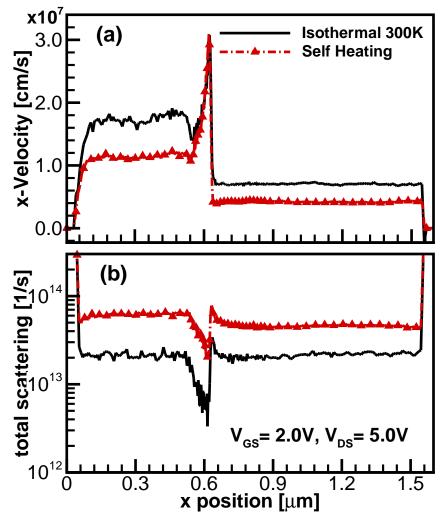

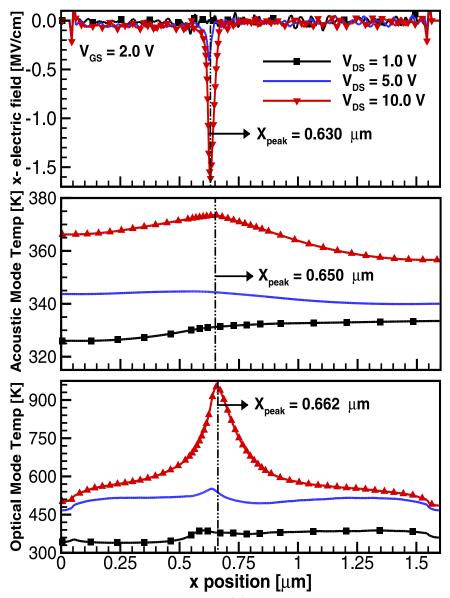

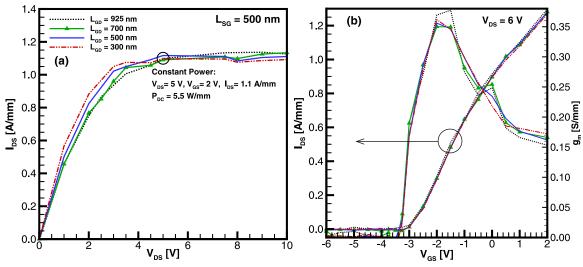

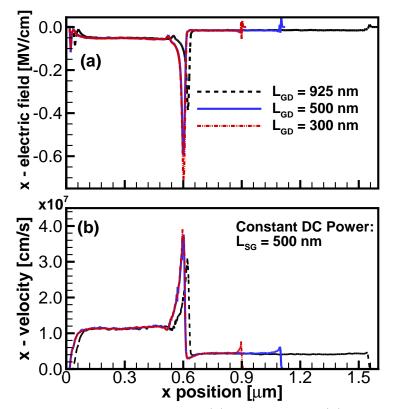

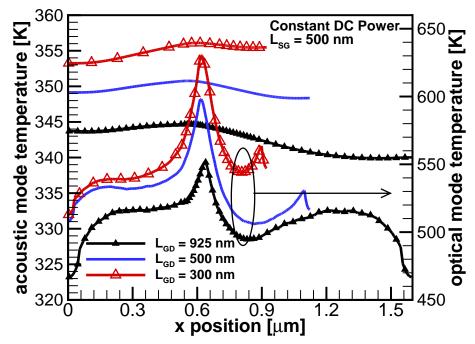

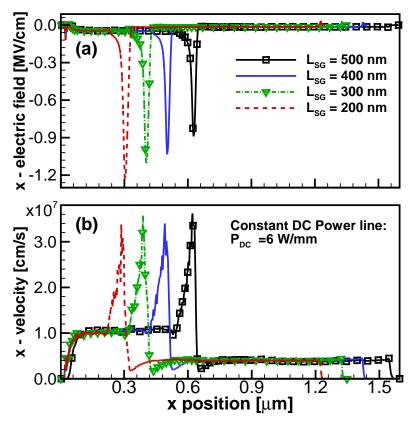

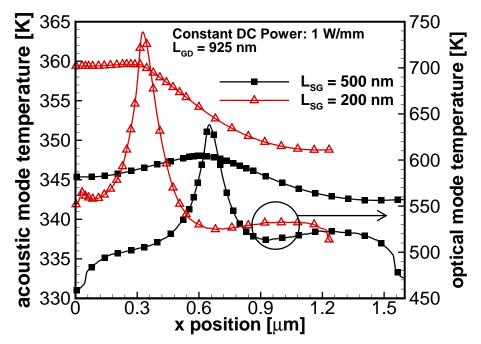

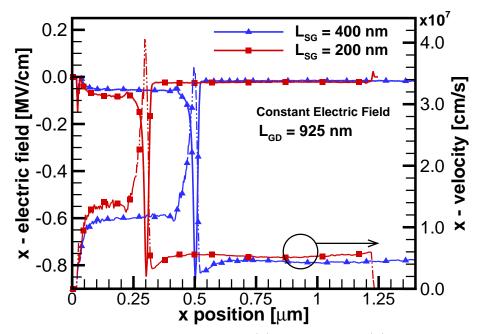

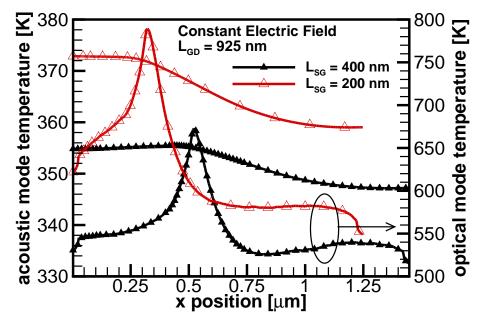

5.8Electron energy distribution function under RF Class AB operation at (a) X-band 10 GHz and (b) K-band 40 GHz, for different input powers. 126 6.1Flowchart of thermal energy transport in semiconductor devices. ..... 131 GaN-on-Si HEMT device layout showing (a) Experimental Layout by 6.26.33D conduction band of the HEMT with temperature profile for Acoustic phonon modes at DC bias of  $V_{GS} = 2 \text{ V}, V_{DS} = 10 \text{ V}. \dots 137$ 3D conduction band of the HEMT with temperature profile for Optical 6.4phonon modes at DC bias of  $V_{GS} = 2 \text{ V}, V_{DS} = 10 \text{ V}. \dots 137$ Validation of the electro-thermal model with experimental curves cor-6.5responding to (a)  $I_D - V_{DS}$  for  $V_{GS} = 0$  V and 2 V, and (b)  $I_D - V_{GS}$  for Profile along the channel of (a) electron x-velocity and (b) total scat-6.6 tering at DC bias point  $V_{GS} = 2 V$ ,  $V_{DS} = 5 V$ , comparing isothermal 6.7Profile along the channel of (a) x- component of the electric field, (b) acoustic mode temperature and (c) optical mode temperature for Effect of gate-to-drain  $L_{GD}$  lateral scaling on the (a)  $I_{DS}$ - $V_{DS}$  for  $V_{GS}$  = 6.82 V and (b)  $I_{DS}$ - $V_{GS}$  for  $V_{DS}=6$  V, also shown the transconductance  $G_m$ in right-axis of (b). Self-heating effects included in all simulations.....145 Profile along the channel of (a) electric field (b) electron velocity for 6.9three different values of  $L_{GD}$ . The DC bias point  $V_{GS} = 2 \text{ V}, V_{DS} = 5 \text{ V}$

corresponds to the point with constant DC power from figure 6.8...... 145

### Chapter 1

## INTRODUCTION

Wireless communications have become a ubiquitous element in modern society, resulting in the upsurge of the telecommunications and radio-frequency (RF) markets with a wide variety of applications and ever-more demanding requirements. In the field of personal mobile technology, internet of things (IoT) and broadband internet connections, one of the main goals is to provide high data transfer rates, such as 1 Gbps in 5G cellular technology [1] and up to 8 Gbps under the IEEE 802.11ad WiGig technology [2]. In addition, since most of these applications are battery-powered there is a strong need for high efficiency and portability. On the other hand, the evolution of airborne, aerospace, satellite and defense applications require not only high data rates, but also high power ratings and in the case of radar technologies high resolution.

The improved product-level performance correlates directly with stringent system level specifications, since high data rates require wider bandwidths, portability translates into smaller and more efficient components and the high power ratings call for higher reliability and efficiency. All these needs have in common that can be delivered in RF systems operating in super high frequencies (SHF) of 3 to 30 GHz and millimeter-wave (mm-wave) frequencies between 30 and 300 GHz. This is why considerable efforts have been directed over the last couple of decades to the development of the technology necessary to implement efficient and reliable high-frequency RF transmitters. In such systems, mm-wave transistors play an essential role as the power amplifier (PA) or the output stage that feeds the antenna [3].

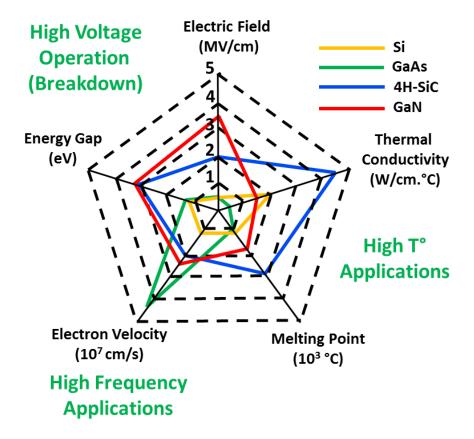

Figure 1.1: Comparison of semiconductor material properties which enable high power and high frequency operation [3].

Even though the semiconductor industry is heavily dominated by Silicon devices, the system requirements of state-of-the-art RF transmitters have driven the development of new microwave and mm-wave transistor technologies based on other materials such as SeGe, GaAs, SiC and GaN, which offer better physical properties to achieve the desired performance. Figure 1.1 shows a diagram comparing the relevant material properties that enable high frequency and high power operation [3].

For the latter, transistors must have high breakdown voltage, which is a process driven by the electric field. In this sense, wide bandgap materials like 4H-SiC and GaN are suitable options because of the high critical electric field required for impactionization. In addition, devices operating under high power conditions must be able to withstand and dissipate high temperatures, which demands for high thermal con-

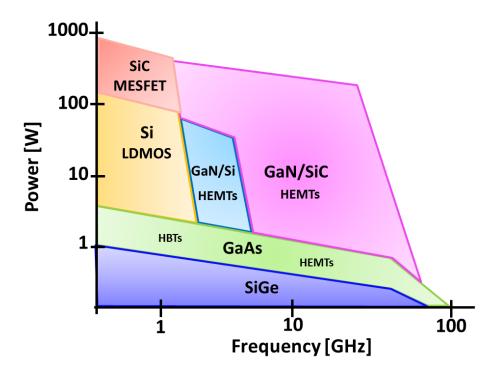

Figure 1.2: Diagram of Power-Frequency range of different technologies of semiconductor devices [4].

ductivity. From this point of view, SiC provides the best option. In terms of high frequency operation, materials with high electron velocities are the most adequate, and GaAs provides the highest, followed by SiC and GaN.

The intrinsic advantages provided by alternative materials have been exploited in devoloping different device technologies suitable for a wide range of power-frequency applications, as it is shown in figure 1.2 [4]. It must be noticed that even though Si is outperformed by all the other materials, advanced devices built with Si such as the laterally diffused MOSFET (LDMOS) transistors allow for improved performance with respect to conventional Si-MOSFETs, enabling its operation in frequencies below 3 GHz and high power between 10 and 100 W typical in power switching applications [5]. However, the properties of 4H-SiC are being exploited in cutting-edge metal-semiconductor field effect transistors or MESFETs providing efficient power switches with low on-resistance and significantly higher power operation [6].

In terms of PAs for hand-sets necessary in personal mobile communications, SiGe p-MOSFETs with low operating voltages of 2 V to 3 V for low power of 1 W to 2 W and high frequency are very attractive because of its integration potential with the dominant analog and digital Si CMOS technology. However, as frequency and linearity requirements have become more demanding, GaAs devices such as the Heterojunction Bipolar Transistor (HBT) and High Electron Mobility Transistor (HEMT) [7], have been adopted as the mainstream technology for applications up to 5 W.

For applications such as cellular base stations, satellite communications and radars for self-driving automotive or defense, typical RF amplifiers require high power above 10 W and frequencies of operation in the mm-wave range. In this case, GaN HEMTs fabricated on both Si and SiC substrates are the most prominent technology [8], enabled by the ability to form heterojunctions in the AlGaN/GaN system. The wide bandgap of this heterostructure results in high breakdown voltage, enabling transistors to be biased at high drain voltages. This not only reduces the need for voltage conversion but also improves the power conversion efficiency critical for PAs [3].

In addition, unlike the AlGaAs/GaAs heterostructure HEMTs that rely on a modulation doping layer to form a channel [9], III-nitrides heterojunctions like  $Al_xGa_{1-x}N/GaN$  show high density of two-dimensional electron gas (2DEG) at the heterointerface due to the presence of a strong polarization effect [10], providing high carrier density and high electron mobility due to a reduced impurity scattering. The combined effects of high carrier density and high mobility result in high current and power densities even at high frequency operation [11; 12]. This in turn allows fabricating devices with small periphery resulting in high output impedance and easier matching with low loss circuits [13]. Furthermore, the high breakdown and high thermal conductivity of substrates such as SiC allow for high temperature operation and better noise performance than SiC MESFETs.

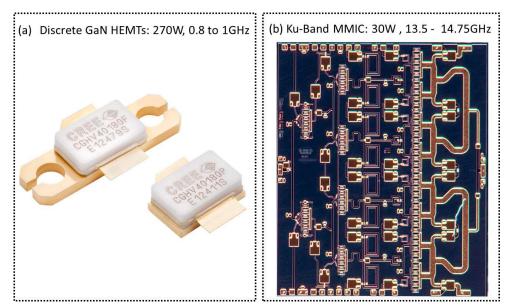

**Figure 1.3:** Commercially available GaN HEMT products released by Cree Inc, showing (a) Discrete 50V GaN HEMT devices for radar and military communications and (b) High power MMIC for satellite communications.

In the last decade, extraordinary progress both at industrial and research level have made *AlGaN/GaN* HEMTs technology commercially available [14; 15], with a market size valued at USD. 974.9 million in 2016 [16], including both GaN on Si HEMTs for power switching and GaN on SiC HEMTs for mm-wave PAs. A couple of commercially available products recently released by Cree are shown in figures 1.3 (a) and (b) corresponding to discrete 50 V GaN HEMT devices for radar and military communications and a high power MMIC (monolithic microwave integrated circuit) for satellite communications [17].

The development of the technology necessary to fabricate these devices is due to major progress in improving the material growth quality and reducing its cost [18]. In addition, process flows for fabrication of devices were developed including passivation techniques that minimize current dispersion [19], along with advanced contact engineering including field plates that increase the RF power density [11]. The leap in GaN processing technology is such that it has enabled the development at a research level of devices for sub-millimeter RF operation, in particular Hot Electron Transistors (HETs) based on vertical AlGaN/GaN heterojunction diodes are being studied as suitable candidates for terahertz operation [20; 21].

In terms of robustness of the technology, remarkable mean-time-to-failure values of 10<sup>7</sup> h and greater have been reported [22], and some HEMT products have been certified matching Si CMOS manufacturing metrics and process control [14]. Despite this significant achievement, reliability concerns are still a roadblock to fully deploy the technology. This issue arises from the fact that niche applications of GaN HEMTs often imply harsh operating conditions such as high temperature and power dissipation, resulting in high electric fields and current densities both under DC and high-frequency operation. In this sense, reliability concerns are still a challenge and the subject of active research [23].

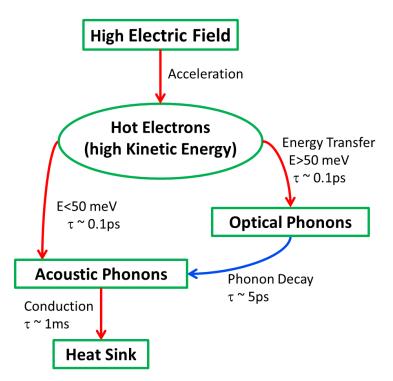

In terms of device failure of intrinsic GaN HEMT devices, two main degradation mechanisms are studied: trap generation induced by hot-electrons and high temperature effects, and electric field-induced current degradation attributed to the inverse piezoelectric effect [24; 25]. Under reverse-bias stress, HEMTs show performance degradation in terms of high gate-leakage current, typically attributed to defect-generation through inverse piezoelectric effect [22]. Under forward bias, current collapse is associated to self-heating effects and defect generation induced by hot-electrons [26]. Even though these phenomena have been widely studied experimentally by means of DC life-time reliability testing, a deeper understanding of the underlying physical mechanisms responsible for device degradation is still necessary, in particular when the electrical stress is induced in RF operation. It is in this context that advanced techniques for simulation of semiconductor devices and materials have made important contributions and have been established as a powerful tool for the study of physical mechanisms of operation and reliability.

### 1.1 Modeling of Semiconductor Devices

Numerical simulations are widely used in industry and research because they allow for a higher level of accuracy than compact models, necessary to capture and predict highly non-linear behavior of devices operating under high fields. In addition, simulations are a traditional surrogate for experiments in the presence of cost, time or even experimental feasibility constrains. Furthermore, computer aided design (CAD) provides an accurate way to advance the development of new technologies. From this point of view, numerical simulations in the context of the broad topic of computational science have been established as the third paradigm of science, adding to theory and experiment [27].

Simulation of semiconductor devices involves several factors. First, it is necessary to obtain the charge and potential distributions self-consistently, which is the realm of electromagnetic theory in the form of Poisson's equation, for which elegant and efficient computational solutions have been developed [28]. Then, the transport of carriers in the semiconductor material, or the way charge moves in the presence of electric fields and potentials through a crystal, requires a physical model to be solved in a self-consistent manner with the electrostatic problem. Finally, for accurate device simulations boundary conditions must be included in order to capture the effect of surfaces and contacts.

Under the semi-classical approach, a complete description of carrier transport can be done in terms of the single-particle distribution function  $f(\vec{r}, \vec{k}, \vec{t})$ , which gives the probability of finding one carrier with crystal momentum  $\vec{k}$ , at position in real space  $\vec{r}$  at time  $\vec{t}$ . This definition can be extended to an ensemble of non-interacting particles [29]. The distribution function describes the average distribution of carriers in phase-space, e.g. in real and momentum space, and can be used to calculate meaningful physical quantities such as carrier concentration, energy, velocity and currents by calculating averages on the ensemble [30]. In order to obtain  $f\left(\vec{r}, \vec{k}, \vec{t}\right)$ , the Boltzmann Transport Equation (BTE) given by 1.1 must be solved [31]:

$$\frac{\partial f}{\partial t} = -\vec{v} \cdot \nabla_{\vec{r}} f - \dot{\vec{k}} \cdot \nabla_{\vec{k}} f + \left(\frac{\partial f}{\partial t}\right)_{coll},\tag{1.1}$$

where  $\vec{v}$  is the carrier velocity, and the last term on the right hand side of 1.1 is the rate of change of f due to collisions. In simple terms, the BTE describes the time evolution of the distribution function in momentum-space, accounting for all possible mechanisms by which it can change, such as driving forces given by applied fields and dissipative scattering forces. However, the BTE is a multi-dimensional, non-linear differential equation and solving it is a cumbersome task [32]. The strategy used to do so, be it analytical or numerical, defines the characteristics of a device simulator.

A widespread technique is the drift-diffusion method [33] based on the first moment of the BTE, where approximations applied to the BTE yield the well known drift-diffusion current equations, which can be self-consistently solved with the electrostatic problem, taking into account analytical carrier statistics [34]. The main advantage of this method is its relative computational efficiency at the expense of relying on significant simplifications that fail under relevant operating conditions of state-of-the-art devices.

The hydrodynamic model is an improved version of the drift-diffusion approach which allows to study non-equilibrium conditions, however it still relies heavily on parameters such as energy relaxation times, mobility and diffusion coefficients among others, whose accuracy determine the validity of the predictions and results obtained under this approach [35]. Nevertheless, this method is widely accepted as the industry standard and several CAD packages such as Sentaurus TCAD tools by Synopsys are commercially available. On the other hand, particle-based simulation based on the stochastic Monte Carlo methods have been established as a highly accurate way to solve the BTE [36], because it mimics the physics of carrier transport, providing an insightful microscopic description of device operation [30]. In this strategy, a population of carriers is represented by an ensemble of particles whose individual trajectories are tracked in both momentum and real space as they move through a device following Newton's laws, under the presence of electric fields and dissipative forces. The latter are the scattering rates, which correspond to the last term on the RHS of 1.1, and are formulated as a probability density function according to a quantum mechanical treatment [29].

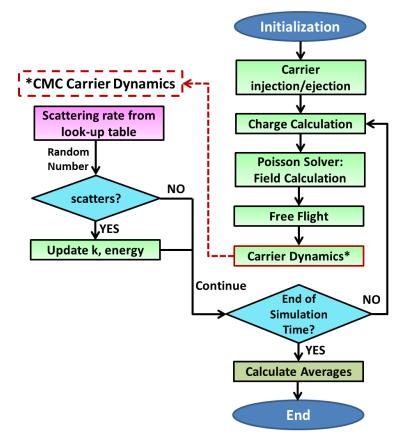

Monte Carlo methods provide an exact statistical solution of the BTE, and from the resulting distribution function physical observables can be derived through averages of the ensemble. Moreover, if the number of particles (or trajectories) considered in the simulation is large enough, the averaged quantities of the ensemble (concentration, energy, velocity and currents) are a good approximation to the average behavior of the carriers in a real device. The flowchart of the particle-based Cellular Monte Carlo framework (CMC) used in this work [37] is presented in figure 1.4.

The algorithm begins with initializing carriers in real and momentum space, within the simulation domain representing the semiconductor device. Then the total charge is calculated by imposing the charge neutrality condition considering mobile carriers, ionized impurities and other fixed charges, which is used to solve Poisson's equation to obtain electric field and potential maps in real space. Then, the field is kept constant over a short time-step called the free-flight and carriers are allowed to move ballistically following Newtown's laws updating the carrier position in both real and momentum space. The following step corresponds to the carrier dynamics portion of the method, where a stochastic Monte Carlo procedure is used to select if the carrier scatters, and if it does then the final momentum state is selected and updated.

Figure 1.4: Flowchart of the particle-based Cellular Monte Carlo algorithm (CMC).

This process is iterated over all particles in the ensemble, which typically requires 4 to 5 free-flight steps before the charge and electric field are re-calculated, implying the use of two different time-steps one for the free-flight and one for the Poisson Solver. Choosing the free-flight time-step most be done so that all scattering processes can be resolved, whereas the Poisson time-step should be chosen so that numerical artifacts such as plasma oscillations are avoided [36]. The whole loop is iterated over a simulation time long enough for the system to evolve into steady-state, where physical observables are obtained by calculating averages over the ensemble during additional simulation time.

Traditional Ensemble Monte Carlo (EMC) simulators have the disadvantage of being inefficient or computationally expensive because the position of carriers in

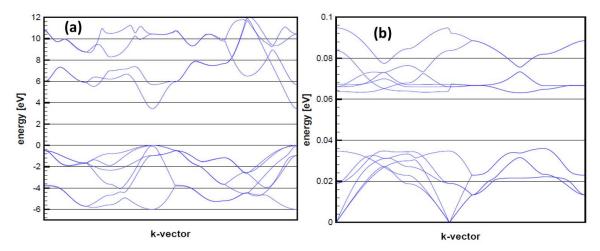

**Figure 1.5:** Full electronic-band structure (a) and Phonon dispersion (b) of Wurtzite GaN (HCP) used in this work.

momentum-space have to be recalculated on the fly during the simulation, for every particle in every scattering step, which requires searching for the final momentum states that conserve energy throughout the entire Brillouin Zone (BZ). Additional inaccuracies are introduced in EMC simulators because with the aim of reducing the computational burden, parabolic band structures are used in the scattering rate calculations. These issues are overcome by the Cellular Monte Carlo method (CMC) [37], where the total scattering probability rates due to all mechanisms, from every initial state to every final state are previously calculated and stored in look-up tables. This approach reduces the selection of the final state to the generation of a single random number, increasing the efficiency in the scattering step of the algorithm reducing the simulation time at the expense of higher memory requirements.

Furthermore, within the CMC framework full electronic-band structures and phonon dispersion are used in the calculation of scattering rates for each material of interest, resulting in high accuracy in the description of highly non-linear, out of equilibrium transport of carriers under high electric fields. The calculation of band structures is done with the empirical nonlocal pseudopotential method [38], whereas the phonon

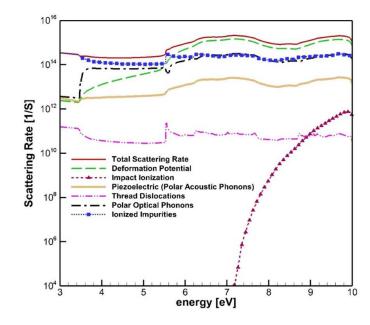

Figure 1.6: GaN scattering rates at T = 300 K used in this work.

dispersion relations are computed with the volume-shell approach [39]. Figures 1.5 (a) and (b) show the calculated band structure and phonon disperssion of GaN-HCP respectively. Concerning the scattering rates, within the CMC simulator scattering processes due to deformation potential phonons, polar optical phonons, piezoelectric (polar acoustic) phonons, ionized impurities, impact ionization and thread dislocations are included in all simulations. The corresponding scattering rates for GaN are shown in figure 1.6. Finally, quantum mechanical effects due to carrier confinement in the 2DEG at the heterojunction interface, are accounted for by including the effective potential approach [40], allowing for effects such as charge setback and energy level quantization [41].

It must be emphasized that under high electric field conditions, carrier transport in semiconductors lead to significant non-linear behavior of devices, which arise from major changes in the shape of the carrier distribution function. The changes in  $f\left(\vec{r}, \vec{k}, \vec{t}\right)$  correspond to far from equilibrium conditions which violate most of the approximations used in methods other than Monte Carlo [29]. Additionally, the accuracy of the description of transport is directly correlated to the material properties considered in simulations. Since GaN HEMTs often operate in high electric field regime, the CMC framework constitutes an appropriate tool for modeling and characterization of these devices.

## 1.2 Overview of this Work

In this work, the assessment of physical mechanisms associated to reliability concerns in mm-wave GaN devices for power amplifier (PA) applications is presented. The study is performed by means of a full band Cellular Monte Carlo particle-based device simulator (CMC) [37], which allows for the systematic characterization of the performance of GaN devices operating in DC, small-signal AC and large-signal radiofrequency (RF) conditions. From the device's response under different operating regimes, the microscopic properties relevant for transport are correlated to effects such as deviations from ideal electrical response, generation of hot carriers, material defects and self-heating associated to degradation of performance.

With the aim of providing the main concepts used throughout this study, Chapter 2 is dedicated to a brief review of the material properties of wurtzite GaN, followed by the discussion of basic operation of GaN devices. In addition, the main reliability concerns associated to this technology is discussed, and the fundamentals of power amplifier operation and design are introduced. Next, chapter 3 is focused on the the study of non-idealities in III-N heterojunction diodes that explain the limited performance of the experimental IV characteristics with respect to those obtained by simulations of the ideal layout, showing that variations of mole fraction in the barrier and the presence of Schottky contacts are the dominant parameters responsible for the deviations from ideal response.

In chapter 4, a hot electron generation study in GaN HEMTs is presented in terms of the electron energy distribution function (EDF), calculated under largesignal RF power amplifier operation. While most studies are done for DC bias only, here simulations are carried out under realistic PA conditions including the effect of frequency and temperature variations. The results suggest that degradation due to hot electrons is higher in DC than in RF Class AB PAs when the frequency is in the X-band (10 GHz) independently of the temperature, but the trend is reverted for mm-wave frequencies (up to 40 GHz). Also, it is shown that Class A operation would lead to lower reliability than Class AB, because of a higher generation of hot carriers.

The methodology presented in chapter 4, is then used in chapter 5 to benchmark a new II-shaped gate contact proposed here for improved reliability of GaN HEMTs which reduces the generation of hot electrons in DC and large-signal RF operation without significantly degrading the device's performance. The results show that in all operating regimes the EDF is lower with a II-gate contact than with a typical T-gated device, which suggests improved robustness to failures from the generation of traps induced by hot carriers. Design rules along with projections of small-signal AC parameters were presented as guidelines for design and fabrication.

Finally, the self-heating effects observed in GaN-HEMTs on Si substrates is studied by means of electro-thermal simulations of the DC characteristics, obtained with an expanded CMC framework. In this new approach, the thermal effects are included through an energy-balance equation for phonons which self-consistently couples the charge and heat transport. After validating the electro-thermal model with experimental data showing excellent agreement, the model is used to assess the impact of lateral scaling of the device in terms of self-heating effects, showing that on scaled devices the improved electrical characteristics are accompanied by stronger self-heating effects which require the development of thermal management strategies.

#### Chapter 2

## REVIEW OF GAN TECHNOLOGY AND POWER AMPLIFIERS

Group III-nitride semiconductors have drawn interest in research and industry in the last decades [42; 43; 18]. The wide band gap of GaN and AlN of  $3.4 \,\mathrm{eV}$  and  $6.2 \,\mathrm{eV}$ respectively, in addition to the ability to form lattice matched heterojunctions in the AlGaN/AlN/GaN system, makes this a very attractive technology for applications in power electronics and mm-wave power amplifiers (PAs). These materials become intrinsic at higher temperatures than narrow band gap semiconductors and they can sustain large current and voltage due to their high breakdown field. In addition, IIInitrides heterojunctions show high density of two-dimensional electron gas (2DEG) at the heterointerface without the need of modulation doping, due to the presence of a strong polarization effect. This translates in higher electron concentration and mobilities which makes the system suitable for high power and high frequency applications [10]. In this chapter, a brief review of the fundamental concepts relevant for GaN technology is presented. First the polarization effects and principles of operation of AlGaN/AlN/GaN devices is discussed, followed by a review of the main aspects of HEMTs reliability. Finally, the principles of operation and design of PAs is introduced.

#### 2.1 Polarization Effects in GaN

In order to understand the material properties that allow high current densities and high frequency operation in AlGaN/GaN devices, making GaN one of the most studied and utilized wide band gap semiconductors, it is necessary to dwell in detail into the characteristics of its crystal structure. While it is possible to grow GaN

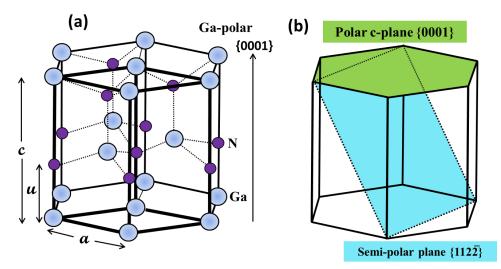

**Figure 2.1:** Crystal structure of GaN in Wurtzite form showing (a) Highlighted Hexagonal Closed Packed (HCP) sublattice for cation Ga, and (b) Typical growth planes, indicating the Ga-polar c-plane  $\{0001\}$  and the semi-polar  $\{112\overline{2}\}$  plane.

in zincblend, the equilibrium crystal under conventional growth conditions is the hexagonal wurtzite structure, as it is shown in figure 2.1 (a). Due in part to the fact that GaN is difficult to grow in bulk form because of its high melting point of  $2500 \,^{\circ}$ C and the high equilibrium pressure of nitrogen, its growth is done on affordable substrates like Si, SiC and sapphire ( $Al_2O_3$ ), which impose the growth direction, typically along the {0001} plane, known as the c-axis, which offers good stability and morphology in diverse growth environments, as well as a strong spontaneous polarization effect [44].

The wurtzite crystallographic structure is composed of two interpenetrating hexagonal closed packed (HCP) sublattices, one made up of anions and the other occupied by cations, these being N and Ga respectively. The sublattice formed by cations is displaced with respect to the anion sublattice by a factor  $u \cdot c$  along the c-axis, where c is the lattice parameter along the {0001} direction and u corresponds to a reduced coordinate. If the HCP structure is not distorted, then the ratio c/a is equal to  $\sqrt{8/3}$ , with a being the length of the hexagonal edge of the HCP cell structure, and u = 3/8. However, in wurtzite crystals the value of u departs from the ideal 3/8. Additionally, since along the c-axis direction planes of cations alternate with planes of anions, the material has a direction of polarity with low symmetry. When crystals have a unique polarity direction, e.g. a direction without symmetry elements relating the two ends, they are pyroelectric and exhibit spontaneous polarization  $P_{SP}$  [18], which is exactly the case for wurtzite GaN grown along the polar c-plane in the {0001} direction, as shown in figure 2.1 (b).

The direction of the  $P_{SP}$  depends on the direction of polarity chosen during growth, which for wurtzite GaN can be either Ga-polar or N-polar obtained along the directions {0001} and {0001} in that order [45]. Concerning the magnitude of the spontaneous polarization, it increases as the parameter u deviates from its ideal value, because it gives rise to a nonzero dipole moment per unit volume, which is independent of external electric fields. Specifically for GaN, AlN, InN and ZnO, the reported  $P_{SP}$  values are -0.029, -0.081, -0.032 and -0.074 C/m<sup>2</sup> respectively [18]. For ternary alloys of the type  $Al_xGa_{1-x}N$ , where x is the Al mole fraction, the spontaneous polarization is proportional to x and it can be found as the linear interpolation between the GaN and AlN values [45]. Even though the polar c-plane is the preferred direction of growth for a variety of applications, in the field of optoelectronics the presence of a polarization vector is deleterious, hence other directions of growth are favored, such as the semi-polar plane {1122} shown in figure 2.1 (b).

In addition to the pyroelectric nature of wurtzite GaN, pseudomorphic AlGaN/GaNheterostructures also exhibit strong piezoelectric polarization effects due to strain in the epitaxial layers induced by the mismatch of the lattice constants and thermal expansion coefficients of AlN and GaN. During crystal growth, if the epitaxial layer grown on top of the buffer is kept under a critical thickness, it undergoes strain along the basal plane leading to a piezoelectric vector  $P_{PE}$  parallel to the direction of growth, i.e. the c-axis in Ga-polar heterostructures. Following the formalism proposed by Ambacher et al. [45], the piezoelectric polarization is given by:

$$P_{PE} = 2\frac{a - a_0}{a_0} \left( e_{31} - e_{33}\frac{c_{13}}{c_{33}} \right), \qquad (2.1)$$

where  $a_0$  is the lenght of the hexagonal edge of the relaxed HCP cell, a is the lattice constants of the strained layer,  $e_{31}$  and  $e_{33}$  are the piezoelectric coefficients, while  $c_{13}$ and  $c_{33}$  are the elastic constants. The positive direction of  $P_{PE}$  is defined from the anion N towards the cation which can be either Ga or Al. Furthermore, since the inequality

$$\left(e_{31} - e_{33}\frac{c_{13}}{c_{33}}\right) < 0, \tag{2.2}$$

is valid for all mole fractions in the AlGaN alloy, then the piezoelectric polarization is negative or parallel to the  $P_{SP}$  vector under tensile strain, and positive or anti-parallel to  $P_{SP}$  under compressive strain. Furthermore, the parameters of equation 2.1 are proportional to the mole fraction x of the alloy and can be found by semi-empirical linear or quadratic interpolation expressions between the GaN and AlN values [45]. Then, the total polarization is given by:

$$P = P_{SP} + P_{PE}, (2.3)$$

which in the case of high polarization discontinuities across heterointerfaces, can be associated to a polarization charge density defined as:

$$\sigma_P = -\nabla P \left[ C/m^2 \right]. \tag{2.4}$$

Considering Ga-polar heterostructures in the system AlGaN/GaN, 3 possible cases of polarization induced charged at the heterojunction can be identified follow-

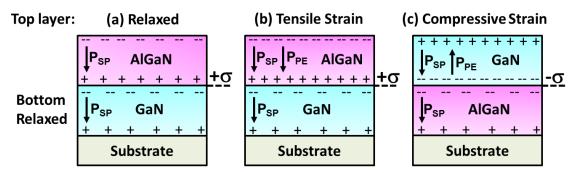

**Figure 2.2:** Polarization vectors (Spontaneous  $P_{SP}$  and Piezoelectric  $P_{PE}$ ) and equivalent interface charge for Ga-polar AlGaN/GaN heterostructures under different growth conditions of the top layer: (a) AlGaN relaxed, (b) AlGaN Tensile strain and (c) GaN Compressive strain, while keeping the bottom layer relaxed.

ing the previous description, and these are shown in figure 2.2. If a thick epitaxial AlGaN layer is grown on top of a relaxed GaN buffer as shown in figure 2.2 (a), then both layers are relaxed, resulting in only  $P_{SP}$  vectors pointing towards the substrate. Since  $P_{SP}|_{AlGaN} > P_{SP}|_{GaN}$  then an equivalent positive polarization charge  $\sigma$  is induced at the heterointerface. On the other hand, if a thin AlGaN layer is grown on top of a relaxed GaN buffer, then the top layer will be under tensile strain resulting in both spontaneous and piezoelectric polarization charge at the interface, as shown in figure 2.2 (b), significantly larger than that of case (a), because of the extra  $P_{PE}$  component. Finally, if a thin epitaxial layer of GaN is grown on top of a relaxed AlGaN buffer, as shown in figure 2.2 (c), then the top GaN layer will be under compressive strain resulting in anti-parallel  $P_{SP}$  and  $P_{PE}$  vectors, which in turn induce a total negative charge density at the heterointerface.

During fabrication of heterojunctions in wurtzite GaN, in particular of the type Ga-polar AlGaN/GaN under tensile stress of figure 2.2 (b), the strong positive polarization charge  $+\sigma$  induced on the AlGaN side at the interface is compensated by free electrons mostly provided by surface donor states [18]. These free electrons

reach high densities, creating a conductive confined layer typically referred to as a 2-Dimensional Electron Gas or 2DEG. The polarization induced 2DEG can reach concentrations higher than  $10^{13}$  cm<sup>-2</sup> without the need of doping, resulting in high electron mobility >1000 cm<sup>2</sup>V<sup>-1</sup>S<sup>-1</sup> due to a reduced impurity scattering [10] which can be exploited in the design of high frequency devices. Herein lies the relevance of the polarization effects observed in wurtzite GaN heterostructures, which provide a strong advantage with respect to the system AlGaAs/GaAs where the 2DEG is formed by carrier injection from the AlGaAs barrier which is heavily doped.

# 2.2 AlGaN/AlN/GaN Devices

The development of technologies such as Metal Organic Chemical Vapor Deposition (MOCVD) and Molecular Beam Epitaxy (MBE), made possible the fabrication of heterojunctions in the 1970s, which was motivated by the early studies of carrier transport parallel to a heterojunction done in the late 1960s [46]. In addition, the first report on mobility enhancement in 2DEGs induced at the interface of heterojunctions was reported for the AlGaAs/GaAs system in 1978 [9], which lead to developing devices based on heterojunctions. In particular, the High Electron Mobility Transistor or HEMT was first proposed in the AlGaAs/GaAs system in 1980 [47], where the 2DEG at the interface is formed by electrons injected from the heavily doped AlGaAsbarrier. Even though research on the growth of GaN had been done since the 1960s, the lack of substrates halted the progress of this field. In fact, the first report on mobility enhancement of carriers in polarization induced 2DEGs in AlGaN/GaNheterojunctions was presented in 1991 [48]. It was not until 1994 that the microwave capabilities of AlGaN/GaN HEMTs was demonstrated for the first time [49]. From this point, the development of devices based on the AlGaN/AlN/GaN system has skyrocketed. In the following subsections the principles of design and operation of GaN HEMTs is discussed, followed by a brief description of the novel Hot Electron Transistors (HETs), which are related to chapter 2 of this study.

# 2.2.1 High Electron Mobility Transistors (HEMTs)

HEMTs based on the AlGaN/GaN heterostructure are the most emblematic devices exploiting the advantages of wide band gap materials and strong polarization effects. Figure 2.3 (a) shows the basic structure of a typical GaN-HEMT, which will be used in this section to explain device performance by means of CMC simulations using the real-space grid of figure 2.3 (b). The epitaxial stack consists of a Ga-polar  $Al_xGa_{1-x}N/AlN/GaN$  heterostructure, where the Al mole fraction of the AlGaN alloy is x = 0.29. A thin AlN interlayer, typically 1 nm to 3 nm thick, is incorporated because it provides a stronger polarization charge inducing higher concentration of carriers in the 2DEG. Furthermore, AlGaN/GaN heterostructures without AlN interlayers suffer from of alloy scattering, which is caused by the perturbation of the periodic potential due to the substituting atom in the alloy crystal structure, affecting electron transport in the channel because of the partial penetration of the wave function of the carriers into the alloy layer. In this sense, adding the AlN layer increases the distance between the channel and the AlGaN barrier resulting in higher mobility by reducing the effect of alloy scattering [50]. The top GaN cap layer is used to provide a high quality surface and also to reduce gate leakage. Traditionally the AlGaN barrier is unintentionally doped, i.e. no impurities are added to increase the 2DEG, however in some new structures the AlGaN layer is doped with Si to increase the 2DEG concentration and therefore the current density [51]. It must be noted that since the 2DEG is intrinsically formed in the heterostructure, Ga-polar HEMTs are depletion devices. This represents no significant concern for mm-wave PAs, but it constitutes a challenge for power-switching applications.

**Figure 2.3:** Basic structure of a Ga-polar *AlGaN/AlN/GaN* HEMT showing (a) device layout and (b) non-uniform grid used for CMC device simulations.

The epitaxial stack is terminated with a SiN layer for passivation of the surface, which is a crucial step in HEMT design and fabrication [51]. As it was explained in section 2.1, the strong polarization charge at the heterojunction interface is compensated by free electrons that are donated from surface state donors during fabrication of the epitaxial stack forming a 2DEG. If the donor surface states are left electrically active, charge trapping /de-trapping can occur during device operation, producing variations of charge at the surface that can accumulate or deplete the 2DEG causing dispersion of the conductivity and therefore the current of the device. In addition, some surface states are acceptor-like which when empty are negatively charged limiting the concentration of the 2DEG. These effects can be eliminated by plasma treatment of the surface and by depositing dielectrics like SiN for passivation [13].

Even though it is not shown in figure 2.3 (a), because all the simulations performed in this work focus on the active region of the device, AlGaN/GaN is grown either by MBE or MOCVD on thick substrates, typically 4H-SiC which provides high thermal conductivity and therefore good thermal dissipation. Also Si substrates are of interest for integration purposes. However, the lattice mismatch between these substrates and GaN require the careful design of nucleation layers in order to grow high quality crystals. This is done by depositing AlN layers on top of the SiC or Si, before growing the wurtzite GaN [13]. The effect of the lattice mismatch is the formation of thread dislocation defects which reduce the mobility of carriers in the channel, as it is explained in the reliability section 2.3.3 of this chapter. An essential technological aspect regarding buffer design, is the compensation of n-type conductivity of the buffer by means of Fe or C doping, which increases the 2DEG confinement and reduces the short-channel effects [52].

Regarding the contacts, HEMTs are fabricated with ohmic source and drain contacts employing Ti/Al/Ni/Au or Ti/Al/Ti/Au layers, that once deposited undergo Rapid Thermal Annealing (RTA). On the other hand, the gate contact is Schottky type made using Ni/Au or Pt/Au layers [13; 51]. Due to the inherently high electric fields present in GaN HEMTs, either under equilibrium because of polarization dipoles or in DC and RF operation, the shape of the gate contact is a crucial design parameter. The state-of-the-art devices are fabricated using a T-shaped gate contact, which consists of a single stem which provides the channel length and a metal top with lateral plates which help reduce the gate resistance. In order to increase the current capability or total output current (not the intrinsic current density), the layout can include multiple gate fingers and interdigitation [51].

Modern structures for high power devices also include field plates that can be connected to the source or the gate which diffuse the peak electric field in the channel, enabling higher breakdown voltages [11]. In addition, shifting the gate placement towards the source contact i.e. making  $L_{SG} < L_{GD}$  also reduces the peak electric field and allows for higher breakdown. In the case of HEMTs fabricated on conductive Si substrates, the source is ohmic-contacted to the substrate while the back-side of the device undergoes metallization to ground the buffer, which is known as sourcevia-grounding or SVG. The use of SVG designs reduces the on-resistance and the source parasitic inductance by eliminating source wire bonding for packaging while also improving thermal dissipation, but more importantly it acts as a backside fieldplate which enhances breakdown voltage capabilities by reducing the peak electric field in the device [53].

Now that a general picture of the complexity associated to the layout of GaN HEMTs has been discussed, it naturally follows the study of DC and small-signal AC characterization of a device. This is done here by means of CMC simulations of the device layout presented in figure 2.3 (a), which despite of following the general structure of an experimental device, it is not the intention of this section to provide a full fit to a particular experimental device but merely a functional model of a HEMT. This is done with the aim of providing a more detailed explanation of the simulation approach of this work as well as the basic operation of the device. If the reader is familiar with both of this aspects, the remaining of this section can be skipped without missing essential contributions of the work.

In all the simulations presented in this work, the main focus is on the active area of the device, meaning that detailed substrate layers are not included. The polarization effect of AlGaN/AlN/GaN heterostructures is included as sheets of charge placed at the corresponding interfaces, with densities calculated following Ambacher's formalism [45] as explained in section 2.1. The effect of passivation of surface states is also included as an additional sheet of charge placed at the SiN/GaN interface, which can be used to calibrate the 2DEG concentration and fit experimental devices. Even though experimental studies to extract the polarization fields and charge values of AlGaN/GaN heterojunctions have shown that Ambacher's theoretical framework lead to an overestimation of about 15% of the polarization charge [54], the accuracy of this simulation approach has been demonstrated by electron holography studies [55]. With respect to the simulation domain in real space, it is discretized with the grid shown in figure 2.3 (b) which is highly inhomogeneous in both the vertical and horizontal directions. This strategy allows to enhance the resolution in critical regions such as the AlGaN/AlN/GaN barrier, the 2DEG region and the channel under the gate, while reducing the computational effort in less relevant areas, i.e. areas with no transport of carriers, such as the SiN passivation layer or deep down the buffer. The dimension of the cells have to be carefully chosen to avoid numerical artifacts such as plasma oscillations, which is done by keeping the maximum length shorter than the Debye length calculated with the local carrier concentration [36]. Also, with the aim of facilitating the convergence of the Poisson solver the variation between two adjacent cells is no larger than 2x the length in any direction [28].

The contacts of the device are modeled as equipotential regions, meaning they serve as boundary conditions for the Poisson solver. In the case of the source and drain contacts, lateral regions are defined across the barrier to directly contact the 2DEG emulating the ohmic behavior, while the doping is used to calibrate the experimental contact resistance when a full fit to experimental data is intended. Even though in the layout of figure 2.3 (a) a simple stem gate contact was used, complex structures such as T-shaped gates can be defined and simulated. In order to capture the buffer related effects such as threading dislocations and conductivity compensation, sheets of charge and doping concentration of the buffer region can be used as parameters for calibration with experiments, in particular of the threshold voltage of the device.

Figure 2.4 presents the band diagram of the simulated GaN HEMT at a DC bias condition of drain voltage  $V_{DS} = 5$  V and gate bias  $V_{GS} = -5$  V. In particular, the left panel identified as (a) shows the 3D conduction band profile with the carrier concentration as a contour, and it can be seen the accurate simulation of the barrier profile and the formation of the 2DEG obtained with the CMC model. Furthermore, in fig-

Figure 2.4: Band diagram of the simulated GaN-HEMT from figure 2.3 at DC bias of  $V_{DS} = 5$  V and  $V_{GS} = -5$  V. Panel (a) shows the 3D conduction band profile with the carrier concentration as contour, while panel (b) shows the vertical profile of the conduction band along with the carrier concentration, taken from a slice on the source-to-gate access region.

ure 2.4 (b) is plotted the vertical profile of the conduction band along with the carrier concentration, corresponding to a slice taken in the source-to-gate access region. In particular, the effect of adding the AlN interlayer in the AlGaN/GaN barrier profile is captured, characterized by a thin barrier with height of 2.8 eV and also a high density 2DEG with a carrier concentration of  $1.9 \times 10^{20}$  cm<sup>-3</sup>, resulting in a density in the order of  $10^{13}$  cm<sup>-2</sup>.

A full DC characterization is presented in figures 2.5 (a) and (b) corresponding to the  $I_{DS}-V_{DS}$  and  $I_{DS}-V_{GS}$  curves respectively, also known as the output and transfer characteristics. The first property that is observed is the depletion mode behavior of the device, which requires  $V_{GS} = -10$  V to turn-off. This value is particularly high because no buffer compensation was used in the simulations as it would be done in an experimental device. Also, it must be noticed the high current densities achieved as well as the high transconductance  $G_m$  shown in the right y-axis of panel (b).

**Figure 2.5:** DC characterization of the simulated GaN-HEMT from figure 2.3 showing (a)  $I_{DS}-V_{DS}$  and (b)  $I_{DS}-V_{GS}$  or output and transfer characteristics respectively.

With respect to the AC simulation method, it consists in calculating the Yparameters of the device over multiple frequencies. This is done by performing two separate simulations where an AC small-signal, meaning small amplitude with respect to the DC bias, is applied to either the gate or the drain of the device while keeping the other contact with only a DC bias, which emulates an AC short-circuit. The type of signal used is a multisinusoid, which consists in a linear combination of sines each centered at a desired frequency while keeping the summation of their amplitudes in the small-signal condition. Then, a fourier decomposition method is used to extract the individual contributions, and calculate the current and power gain [56].

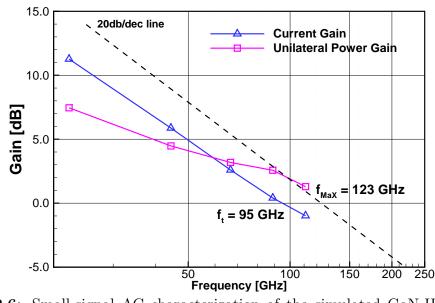

Finally, the small-signal AC characterization of the device is presented in figure 2.6 where the current gain and unilateral power gain are plotted as a function of frequency calculated at a DC bias point corresponding to peak  $G_m$ . From this plot it is possible to extract the cut-off frequency  $f_t = 95$  GHz, defined as the frequency for unity current gain, and the maximum oscillation frequency  $f_{MAX} = 123$  GHz which corresponds to unity power gain. These parameters constitute the most relevant metrics in terms of frequency response, because  $f_t$  measures the maximum frequency at which the

Figure 2.6: Small-signal AC characterization of the simulated GaN-HEMT from figure 2.3 showing short-circuit current gain and unilateral power gain curves as a function of frequency, for extraction of  $f_t$  and  $f_{MAX}$ .

device can be switched, whereas  $f_{MAX}$  represents the maximum frequency at which the device can provide RF power. In both cases, this particular HEMT demonstrates the high frequency capabilities of the GaN-HEMT technology.

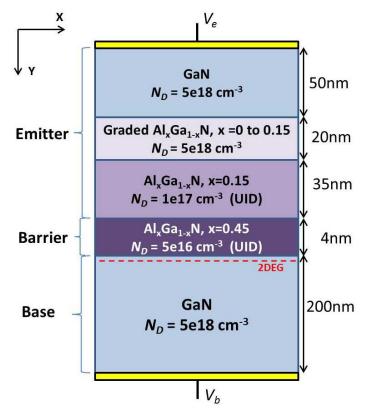

# 2.2.2 Hot Electron Transistors (HETs)

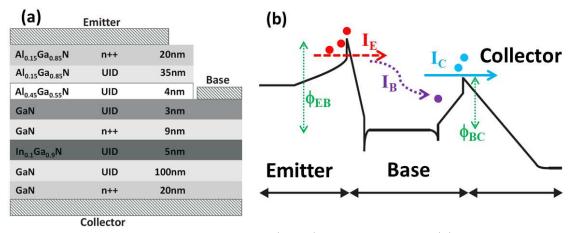

In recent years there has been a resurgent interest in the development, at least at a research level, of vertical GaN devices for ultra-high frequency operation in the range of terahertz. The most prominent device in this field is the Hot Electron Transistor (HETs) based on AlGaN/GaN heterojunctions, and significant progress has been made both in fabrication and transport analysis [20; 21]. The layout of a HET is shown in figure 2.7 (a). It is a 3 terminal device that can be understood as formed by two back-to-back III-N hetorojunction diodes vertically stacked. It helps to think of the HET as an unipolar version of a heterojunction bipolar transistor or HBT. The top diode is formed by an AlGaN/GaN junction and it works as the emitter-base

**Figure 2.7:** Hot Electron Transistor (HET) device showing (a) device layout and (b) 2 dimensional band diagram along the vertical direction. Also indicated in (b) a sketch of some carriers and their trajectories, along with the current components under typical DC operation.

barrier, whereas the bottom diode is made of an InGaN/GaN stack and constitutes the base-collector barrier.

In order to understand the principles of operation of this device, it is convenient to examine the simulated conduction band profile of the stack shown in figure 2.7 (b), where the sketch of a few carriers and their trajectories has been added. When a positive voltage  $V_{BE}$  is applied, the emitter-base barrier  $\phi_{EB}$  is lowered allowing electrons to be injected from the emitter into the base through tunneling and thermionic emission, creating an emitter current  $I_E$ . As the carriers cross the heterojunction interface they gain high kinetic energy becoming hot, hence the name Hot Electron Transistor, which allows them to traverse through the base. Here carriers can experiment scattering, losing energy and getting stuck in the base represented by the purple dot creating the base current  $I_B$ , or they can reach the base-collector barrier with energy higher than  $\phi_{BC}$  as indicated by the blue dots, and cross that second barrier being collected, creating the collector current  $I_C$ . For this last process to happen the base-collector barrier must be biased with a positive  $V_{CB}$  voltage. In practice, biasing HETs is done by forcing a small  $I_B$  and applying a positive  $V_{CE}$  as done in HBTs. In theory, the main advantage of a device as the HET here described rises from the fact that a short base, in the range of 12 nm allows for extremely short transit times enabling terahertz operation. The III-N heterostructure offers fundamental advantages for the implementation with respect to the AlGaAs/GaAs system, because the polarization induced 2DEG at the top AlGaN/GaN emitter-base barrier provides a highly conductive base without doping, reducing the scattering and increasing the collection of electrons in the base-collector barrier. It must be highlighted that in HETs the transport is perpendicular to the 2DEG unlike what is pursued in HEMTs. Also, the wide band gap of AlN and ternary AlGaN alloys, as well as the high energy separation between the  $\Gamma$  and the satellite valleys in GaN, allows for the engineering of  $\phi_{EB}$  barriers which inject high energy electrons into the base without these being transferred to satellite valleys, enhancing the transfer of carriers to the collector.

A comprehensive study of hot electron transistors is out of the scope of this research work. Nevertheless, the non-idealities of fabricated emitter-base diodes affecting HETs performance are indeed studied in detail, and the results are presented in chapter 3. The motivation for this work was the discrepancies observed between CMC simulations and experimental data of the  $I_E - V_{BE}$  curves of emitter-base diodes, which are correlated to the shift observed between CMC simulations and experimental data of the  $I_C - V_{CE}$  curves of HETs. In chapter 3 it is demonstrated that such discrepancies can be explained in terms of mole fraction variations in the AlGaN barrier and including non-ideal Schottky contacts at the emitter and base.

## 2.3 Reliability of GaN HEMTs

Due to the high power and frequency performance of GaN HEMTs, the technology has become a prominent alternative in the field of power amplifiers for satellites, radars and base stations for both civilian and military applications. This applications demand for robust devices capable of operating under harsh conditions and no maintenance, making reliability requirements a crucial aspect. Operation of GaN HEMTs as power amplifiers bring about device failure mechanisms not observed in Si or other compound semiconductors [23], since under typical conditions devices are subjected to high temperature and power dissipation, high electric fields, high current and high-frequency. In addition, GaN technology development relies on heterostructures exhibiting strong polar effects, that are grown in non-native substrates such as Si, SiC or sapphire ( $Al_2O_3$ ), resulting in high density of defects, along with thermal and interfaces mismatches. In this section, the main degradation mechanisms of GaN HEMTs as well as stress testing strategies are discussed.

# 2.3.1 Hot Electron Effects