© 2017 Keith A. Campbell

# ROBUST AND RELIABLE HARDWARE ACCELERATOR DESIGN THROUGH HIGH-LEVEL SYNTHESIS

#### BY

#### KEITH A. CAMPBELL

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2017

Urbana, Illinois

#### Doctoral Committee:

Professor Deming Chen, Chair Professor Wen-Mei W. Hwu Professor Martin D. F. Wong Associate Professor Nam Sung Kim

## ABSTRACT

System-on-chip design is becoming increasingly complex as technology scaling enables more and more functionality on a chip. This scaling-driven complexity has resulted in a variety of reliability and validation challenges including logic bugs, hot spots, wear-out, and soft errors. To make matters worse, as we reach the limits of Dennard scaling, efforts to improve system performance and energy efficiency have resulted in the integration of a wide variety of complex hardware accelerators in SoCs. Thus the challenge is to design complex, custom hardware that is efficient, but also correct and reliable.

High-level synthesis shows promise to address the problem of complex hardware design by providing a bridge from the high-productivity software domain to the hardware design process. Much research has been done on high-level synthesis efficiency optimizations. This dissertation shows that high-level synthesis also has the power to address validation and reliability challenges through three automated solutions targeting three key stages in the hardware design and use cycle: pre-silicon debugging, post-silicon validation, and post-deployment error detection.

Our solution for rapid pre-silicon debugging of accelerator designs is hybrid tracing: comparing a datapath-level trace of hardware execution with a reference software implementation at a fine temporal and spatial granularity to detect logic bugs. An integrated backtrace process delivers source-code meaning to the hardware designer, pinpointing the location of bug activation and providing a strong hint for potential bug fixes. Experimental results show that we are able to detect and aid in localization of logic bugs from both C/C++ specifications as well as the high-level synthesis engine itself.

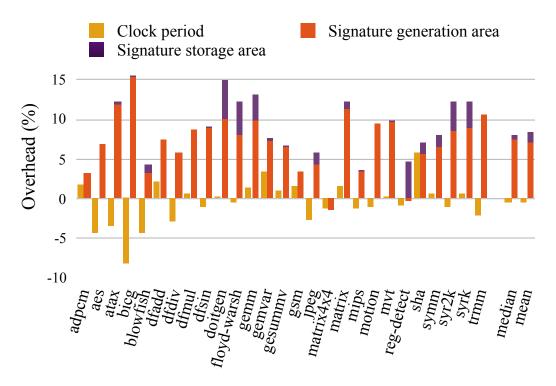

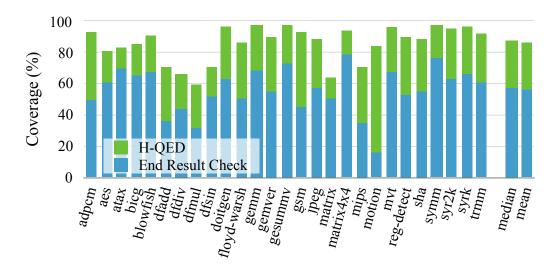

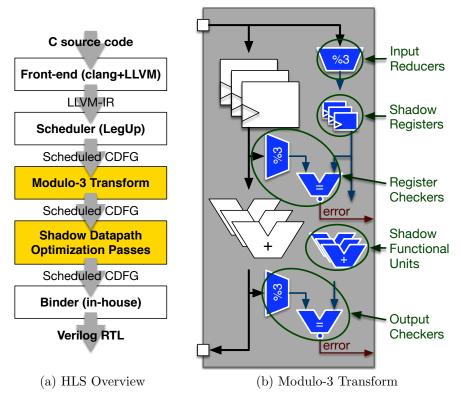

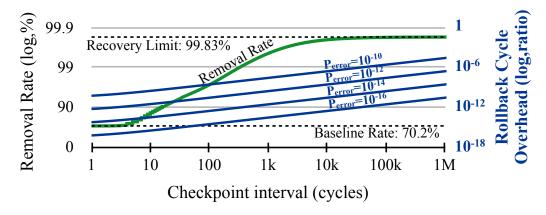

A variation of this solution tailored for rapid post-silicon validation of accelerator designs is *hybrid hashing*: inserting signature generation logic in a hardware design to create a heavily compressed signature stream that captures the internal behavior of the design at a fine temporal and spatial

granularity for comparison with a reference set of signatures generated by high-level simulation to detect bugs. Using hybrid hashing, we demonstrate an improvement in error detection latency (time elapsed from when a bug is activated to when it manifests as an observable failure) of two orders of magnitude and a threefold improvement in bug coverage compared to traditional post-silicon validation techniques. Hybrid hashing also uncovered previously unknown bugs in the CHStone benchmark suite, which is widely used by the HLS community. Hybrid hashing incurs less than 10% area overhead for the accelerator it validates with negligible performance impact, and we also introduce techniques to minimize any possible intrusiveness introduced by hybrid hashing.

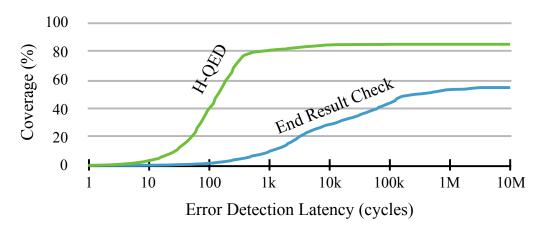

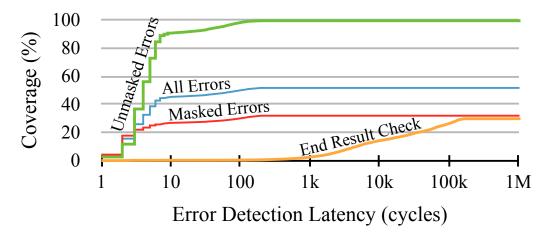

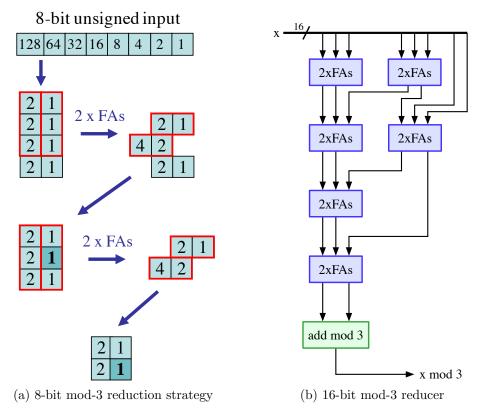

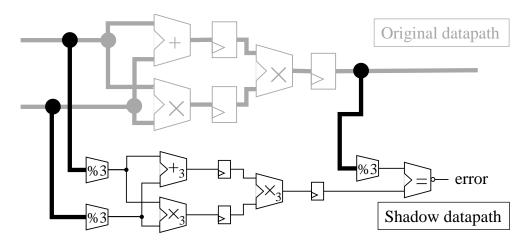

Finally, our solution for post-deployment error detection is modulo-3 shadow datapaths: performing lightweight shadow computations in modulo-3 space for each main computation. We leverage the binding and scheduling flexibility of high-level synthesis to detect control errors through diverse binding and minimize area cost through intelligent checkpoint scheduling and modulo-3 reducer sharing. We introduce logic and dataflow optimizations to further reduce cost. We evaluated our technique with 12 high-level synthesis benchmarks from the arithmetic-oriented PolyBench benchmark suite using FPGA emulated netlist-level error injection. We observe coverages of 99.1% for stuck-at faults, 99.5% for soft errors, and 99.6% for timing errors with a 25.7% area cost and negligible performance impact. Leveraging a mean error detection latency of 12.75 cycles (4150× faster than end result check) for soft errors, we also explore a rollback recovery method with an additional area cost of 28.0%, observing a 175× increase in reliability against soft errors.

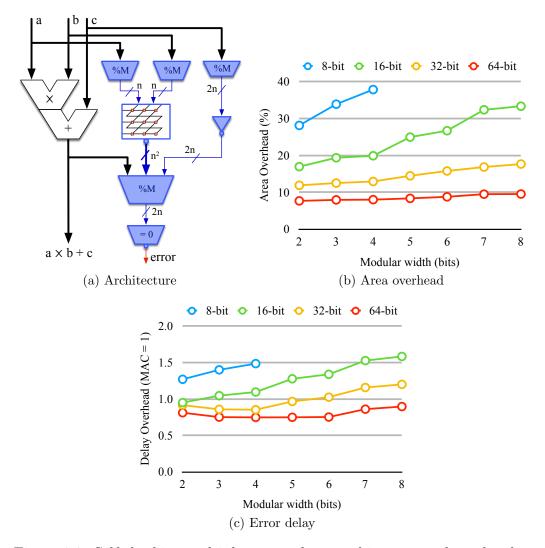

While the area cost of our modulo shadow datapaths is much better than traditional modular redundancy approaches, we want to maximize the applicability of our approach. To this end, we take a dive into gate-level architectural design for modulo arithmetic functional units. We introduce new low-cost gate-level architectures for all four key functional units in a shadow datapath: (1) a modulo reduction algorithm that generates architectures consisting entirely of full-adder standard cells; (2) minimum-area modulo adder and subtractor architectures; (3) an array-based modulo multiplier design; and (4) a modulo equality comparator that handles the residue encoding produced by the above.

We compare our new functional units to the previous state-of-the-art

approach, observing a 12.5% reduction in area and a 47.1% reduction in delay for a 32-bit mod-3 reducer; that our reducer costs, which tend to dominate shadow datapath costs, do not increase with larger modulo bases; and that for modulo-15 and above, all of our modulo functional units have better area and delay then their previous counterparts. We also demonstrate the practicality of our approach by designing a custom shadow datapath for error detection of a multiply accumulate functional unit, which has an area overhead of only 12% for a 32-bit main datapath and 2-bit modulo-3 shadow datapath.

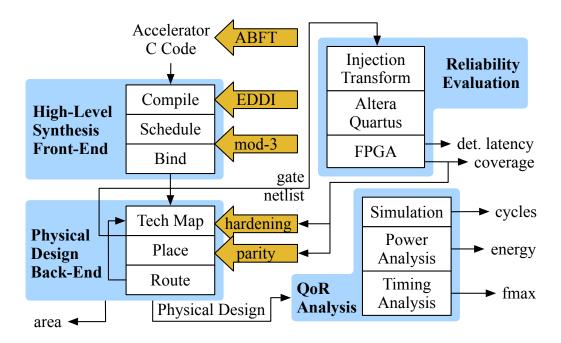

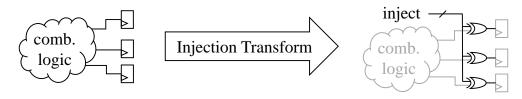

Taking our reliability solution further, we look at the bigger picture of modulo shadow datapaths combined with other solutions at different abstraction layers, looking to answer the following question: Given all of the existing reliability improvement techniques for application-specific hardware accelerators, what techniques or combinations of techniques are the most cost-effective? To answer this question, we consider a soft error fault model and empirically evaluate cross-layer combinations of ABFT, EDDI, and modulo shadow datapaths in the context of high-level synthesis; parity in logic synthesis; and flip-flop hardening techniques at the physical design level. We measure the reliability benefit and area, energy, and performance cost of each technique individually and for interesting technique combinations through FPGA emulated fault-injection and physical place-and-route. Our results show that a combination of parity and flip-flop hardening is the most costeffective in general with an average 1.3% area cost and 5.7% energy cost for a 50× improvement in reliability. The addition of modulo-3 shadow datapaths to this combination provides some additional benefit for some applications, even without considering its combinational logic, stuck-at fault, and timing error protection benefits. We also observe new efficiency challenges for ABFT and EDDI when used for hardware accelerators.

To my parents, for their love and support.

# ACKNOWLEDGMENTS

I would like to thank my advisor Prof. Chen for showing me the meaning of "brute-force" effort and for operating like a true scientist: being convinced once presented with sufficient evidence. I would like to thank my friends in the lab who have kept me company over the years: in particular Yun Heo for giving me insight into the hardware world, Ashutosh Dhar for stepping up to help me maintain our critical lab infrastructure, Yao Chen for complimenting my ideas and treating me like a professional, Wei Zuo for her honest assessments of my work, and Anand Ramachandran for interesting conversations.

# TABLE OF CONTENTS

| LIST O | F ABBREVIATIONS                                   | ix |

|--------|---------------------------------------------------|----|

| CHAPT  | TER 1 INTRODUCTION                                | 1  |

| 1.1    | Root Causes for Hardware Failure                  | 3  |

| 1.2    | Root Cause Effects                                | 8  |

| 1.3    | Error Propagation                                 | 10 |

| CHAPT  | TER 2 BACKGROUND                                  | 12 |

| 2.1    | Execution Signatures                              | 12 |

| 2.2    | Modulo Arithmetic                                 | 14 |

| 2.3    | High-Level Synthesis                              | 17 |

| CHAPT  | TER 3 RELATED WORK                                | 19 |

| 3.1    | Hybrid Quick Error Detection                      | 19 |

| 3.2    | Modulo Shadow Datapaths                           | 21 |

| 3.3    |                                                   | 23 |

| CHAPT  | TER 4 HYBRID QUICK ERROR DETECTION                | 25 |

| 4.1    | Basic Principles                                  | 25 |

| 4.2    |                                                   | 28 |

| 4.3    | Effectiveness and Practicality                    | 29 |

| CHAPT  | ΓER 5 PRE-SILICON DEBUG: HYBRID TRACING           | 31 |

| 5.1    | Comparison to Software Debugging                  | 32 |

| 5.2    |                                                   | 33 |

| 5.3    |                                                   | 42 |

| 5.4    |                                                   | 42 |

| 5.5    |                                                   | 43 |

| CHAPT  | TER 6 POST-SILICON VALIDATION: HYBRID HASHING . : | 52 |

| 6.1    | Hybrid Hashing Framework                          | 54 |

| 6.2    | v e                                               | 60 |

| 6.3    |                                                   | 60 |

| 6.4    |                                                   | 61 |

| 6.5    |                                                   | 62 |

| CHAPTER 7 POST-DEPLOYMENT RESILIENCE: MODULO-3 |     |

|------------------------------------------------|-----|

| SHADOW DATAPATHS                               | 66  |

| 7.1 Framework                                  | 66  |

| 7.2 Results and Analysis                       | 77  |

| CHAPTER 8 CHEAPER MODULO FUNCTIONAL UNITS      | 82  |

| 8.1 Modulo Functional Units Architecture       | 82  |

| 8.2 Quality of Results Comparisons             | 88  |

| CHAPTER 9 CROSS-LAYER RESILIENCE SYNERGIES     | 92  |

| 9.1 Framework                                  | 93  |

| 9.2 Results and Analysis                       | .01 |

| CHAPTER 10 CONCLUSIONS                         | 07  |

| REFERENCES                                     | 10  |

# LIST OF ABBREVIATIONS

ABFT Algorithm Based Fault Tolerance

ACM Association for Computing Machinery

ARM Company that designs CPU cores, initially an acronym for

Acorn RISC Machine

ASIC Application Specific Integrated Circuit

AST Abstract Syntax Tree

BTI Bias Temperature Instability

CDFG Control and DataFlow Graph

CED Concurrent Error Detection

CHStone C-based High-level Synthesis benchmark suite

CLEAR Cross-Layer Exploration for Architecting Resilience

CPU Central Processing Unit

DAC Design Automation Conference

DICE Dual Interlocked Storage Cell

DIVA Dynamic Implementation Verification Architecture, a fault-

tolerant CPU architecture

DMR Double Modular Redundancy

DRAM Dynamic Random Access Memory

ECO Engineering Change Order

EDDI Error Detection by Duplicated Instructions

EDL Error Detection Latency

ERC End Result Check

FA Full Adder

FPGA Field Programmable Gate Array

FSM Finite State Machine

GCC GNU Compiler Collection

GNU GNU is Not Unix

GPU Graphics Processing Unit

HA Half Adder

HH Hybrid Hashing

HLS High-Level Synthesis, also known as behavioral synthesis

HT Hybrid Tracing

HW HardWare

IC Integrated Circuit

ID IDentifier

IEEE Institute of Electrical and Electronics Engineers

IR Intermediate Representation

ISA Instruction Set Architecture

JPEG Joint Photographic Experts Group, develops image compression

standards

JTAG Joint Test Action Group, develops on-chip instrumentation

standards

LEAP Layout design through Error-Aware transistor Positioning

LFSR Linear Feedback Shift Register

LHL Light-Hardened LEAP

LLVM An open-source compiler development framework, initially an

acronym for Low-Level Virtual Machine

LUT LookUp Table

MAC Multiply and ACcumulate

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MSB Most Significant Bit

MUX MUltipleXer

P&R Place and Route

PSV Post-Silicon Validation

QA Quarter Adder

QED Quick Error Detection, detecting errors by fine-grained dupli-

cation

RISC Reduced Instruction Set Computing

RTL Register Transfer Level, referring to the Verilog or VHDL hard-

ware description languages

SDC Silent Data Corruption

SEC Statistical Error Compensation

SEMU Single Event Multiple Upsets

SER Soft Error Rate

SEU Single Event Upset

SoC System on a Chip

SP Service Pack, a minor software update

SP&R Synthesis, Place, and Route

SRAM Static Random Access Memory

SSA Single Static Assignment

TMR Triple Modular Redundancy

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit, a U.S. government program

XOR Exclusive OR, addition in modulo-2 space

## CHAPTER 1

# INTRODUCTION

Designing hardware is hard.<sup>1</sup> A system designer chooses a custom hardware design when a pure software solution is inadequate for power consumption and/or performance reasons. Thus problems that require a hardware solution already come with demanding power and performance constraints. With the end of Dennard scaling, improvements in power consumption and performance for microprocessor-based software platforms have slowed down, pushing more and more system designers to custom hardware solutions.

The result is an explosion in system complexity with increasing effort and chip area dedicated to custom hardware on SoCs. To make matters worse, designers often have additional constraints: limited time to get into a market, complex functionality demanded by that market, and limited chip area budgets due to fabrication costs.

As if this were not enough, the continuation of Moore's law scaling has resulted in new hardware reliability problems. Reliably operating billions of transistors is not easy when power "brown outs" start occurring and thermal hot spots start forming as transistors are packed closer together. Reliably fabricating smaller wires and devices is also not easy, resulting in more permanent defects. Smaller devices are more vulnerable to particle strikes, which manifest as soft errors. Physical effects cause smaller transistors to wear out, resulting in longer gate propagation delays leading to timing errors after prolonged use. All of this does not even consider that designers themselves, without needing any help from circuit physics, are more than capable of creating their own logic bugs to trip over in their complex designs.

Clearly, there is a need for effective methods to manage the complexity of hardware design. High-level synthesis, also known as behavioral synthesis, is one such approach. HLS provides a bridge from the high-productivity software paradigm to the hardware design process, enabling hardware designers to

$<sup>^{1}</sup>$ That is why it is called hardware.

create behavioral specifications of their design in dialects of traditionally software languages. HLS frees hardware designers from the tedious details of hardware resource allocation, scheduling, and binding, allowing them to focus on meeting design requirements and designing effective hardware algorithms. From a research point of view, starting from a behavioral specification provides the synthesis engine with richer information about the behavior and architecture of a design, enabling scheduling and binding optimization potential not possible with RTL design entry, and giving the synthesis engine more freedom to exploit this flexibility to meet multiple optimization goals.

In this thesis, we discuss our research to leverage this power of HLS to address the aforementioned hardware validation and reliability problems through three automated solutions, targeting three key stages of the hardware design and use cycle.

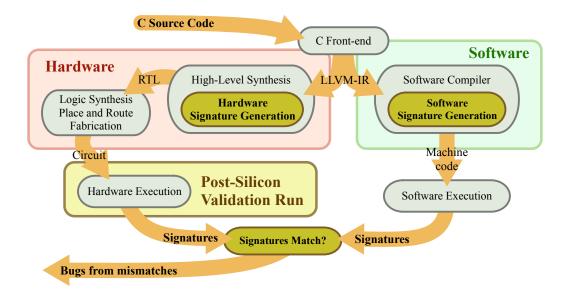

In Chapter 5, we propose the insertion of non-synthesizable instrumentation into an HLS-generated hardware design to capture a trace of internal behavior at a fine spatial and temporal granularity in hardware (RTL) simulation. By comparing this trace with a software version generated to produce the same result, we show that logic bug detection is possible for both bugs in the hardware specification source and in the HLS engine. Furthermore, through the use of debugging metadata, we show that this technique can pinpoint the line where a source-code bug resides. This technique also leverages cosimulation to use high-level language simulation for parts of the design not being directly tested. HLS is critical here because it identifies key RTL variables that have source-code meaning, avoiding the deluge of data from an RTL-level value change dump.

In Chapter 6, we propose the insertion of signature generation logic into a fabricated hardware design to create a heavily compressed signature stream that captures the internal behavior of the design during post-silicon validation at a fine temporal and spatial granularity. By comparing the generated sequence of signatures to a reference set generated by high-level simulation, we can detect both logic and electrical bugs in hardware designs. HLS also plays a critical role here by identifying important variables to capture and enabling the sharing of expensive signature generation logic.

In Chapter 7, we propose creating a redundant, but smaller "shadow" datapath based on modulo arithmetic to detect reliability problems in a design's main datapath. HLS is critical here because it provides a clear

picture of the datapath of the design and enables effective sharing of expensive checksum computing resources.

In Chapter 8, we take a dive into gate-level optimization to further optimize these shadow datapaths, exploring new gate-level algorithms and architectural templates for modulo arithmetic functional units with the goal of automating the generation of these units. We show that the use of these new functional units reduces shadow datapath cost, and enables practical scaling to larger shadow datapath widths for improved error detection effectiveness.

In Chapter 9, we take shadow datapaths further by looking for cross-layer synergies with techniques for improving soft-error reliability ranging from the algorithm to the physical design level. By combining techniques, we can exploit the strength of each technique while compensating for weaknesses. As a side effect, this chapter explores the effectiveness of algorithm and instruction level techniques when applied in the context of high-level synthesis.

Before these main chapters, we will provide some background on the reliability and validation problems hardware designers face in the rest of this chapter, introduce important concepts used in our work in Chapter 2, and discuss related work in Chapter 3. Chapter 4 introduces the concept of hybrid error detection, which creates the foundation for Chapters 5 and 6. We end with concluding remarks in Chapter 10.

This thesis is based on our three publications in the IEEE/ACM Design Automation Conferences of 2015 and 2016: "High-Level Synthesis of Error Detecting Cores through Low-Cost Modulo-3 Shadow Datapaths" [1], "Hybrid Quick Error Detection (H-QED): Accelerator Validation and Debug Using High-Level Synthesis Principles" [2], and "Debugging and Verifying SoC Designs through Effective Cross-Layer Hardware-Software Co-Simulation" [3]. Chapter 9 is based on a publication to appear in TECHCON 2017: "Cost-Effective Cross-Layer Resilience for Hardware Accelerators" [4].

#### 1.1 Root Causes for Hardware Failure

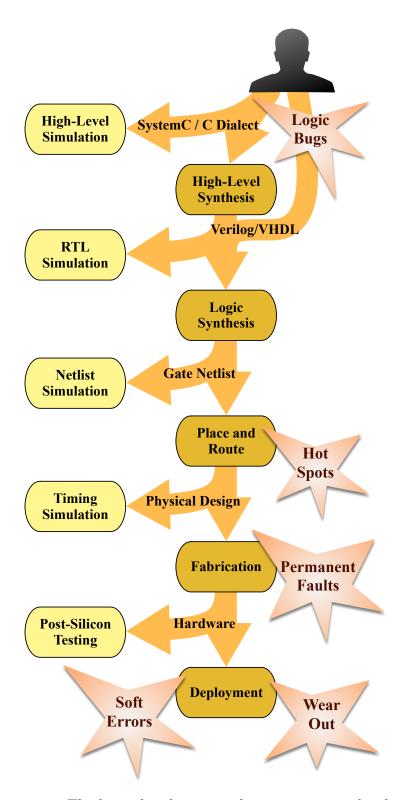

Figure 1.1 provides an overview of the hardware engineering process, which consists of the following steps:

1. The designer writes a Verilog and/or VHDL description of the design.

Figure 1.1: The hazards inherent in designing custom hardware.

For improved productivity, the designer may also elect to specify design blocks at the behavioral level in SystemC or the HLS-tool's proprietary C dialect.

- 2. The designer simulates behavioral design blocks using a software compiler.

- 3. The designer uses a high-level synthesis tool to generate an RTL implementation of behavioral design blocks.

- 4. The test engineer runs the resulting RTL implementations through an RTL simulation tool.

- 5. The designer runs the RTL blocks through logic synthesis to generate a technology mapped gate netlist.

- 6. The test engineer may simulate the netlist with a netlist simulation tool. Simulation at this stage is very slow.

- 7. The designer runs the gate netlist through a placement and routing engine, which produces a physical design.

- 8. The test engineer may simulate the physical design with a chip simulation that takes wire and gate delays into account. This simulation is extremely slow.

- 9. The designer sends the physical design to a foundry, which fabricates the chip.

- 10. Test engineers test the actual hardware to verify that it meets specifications and validate that it implements the correct design.

- 11. Hardware that passes post-silicon testing is sent to end-users who deploy it in their systems.

Figure 1.1 also shows what can go wrong during the hardware engineering process, which we now discuss in the following subsections.

#### 1.1.1 Logic Bugs

Logic bugs are mistakes that the hardware designer makes in writing the C or RTL version of a design that cause it to function in violation of the design specification. Most of these bugs are caught in high-level simulation or RTL simulation. Due to the complexities of system design, it is difficult to design these tests such that they exercise every possible interaction between a design block under test and other design blocks around it. Thus some logic bugs escape high-level and RTL simulation and can make it into the physical design. Some of those bugs evade detection in post-silicon testing and survive all the way to deployment. We define two primary classes of logic bugs:

- Deterministic logic bugs have well-defined behavior that is not compiler or synthesis tool dependent. For input languages with well-defined standards, semantics that are defined in the standard are deterministic for tools that conform to the standard. An example of a deterministic logic bug is a memory copy operation for input data that simultaneously (for faster performance) copies the first half of an input array to both halves of an output array when the programmer intended to copy corresponding halves of the whole input array to the whole output array.

- Non-deterministic logic bugs do not have well-defined behavior; the behavior can depend on the compiler or synthesis tool used, how the tool was configured, what environment the tool was run in or the design was tested in, and even other parts of the design that are seemingly unrelated; the behavior of these bugs can depend on almost anything! For input languages with well-defined standards, non-deterministic semantics may be specified as resulting in "undefined behavior." An example of a non-deterministic logic bug is a read from uninitialized memory.

### 1.1.2 Hot Spots

Hot spots are regions on a chip that exceed local heat dissipation capacity and/or power supply capacity under certain operating conditions. Hot spots happen when a large amount of transistor switching activity is concentrated in a small region of a chip. An excess current demand that lasts long enough causes voltage drops on power supply wires, resulting in longer than expected transistor delays. High power consumption exceeding the thermal dissipation capability of a region of a chip that lasts long enough results in excess heat that causes the transistors in that region, which are not designed to operate at high temperature, to slow down. The net effect is that signal propagation delays increase, leading to timing errors (defined in Section 1.2.1).

#### 1.1.3 Fabrication Defects

Fabrication defects result in gates implementing the wrong logic function (or being permanently bypassed) due to wire or transistor fabrication failures. These permanent defects typically manifest as stuck-at faults: wires that are supposed to be the output of a logic gate are stuck at logic 0 or logic 1 and never change regardless of circuit input.

#### 1.1.4 Soft Errors

Soft errors are caused by a particle striking a transistor with enough energy and the right timing to cause bit-flips in storage elements including flip-flops, SRAM cells, and DRAM cells. The victim transistor can be part of the storage element or an upstream gate that propagates a resulting logic glitch. These particles are typically part of a shower of particles that results when a cosmic ray strikes the Earth's atmosphere. Thus these events are random and unpredictable in nature.

#### 1.1.5 Wear Out

Like mechanical systems, MOSFETs can wear out from prolonged, heavy use. High-energy charge carriers can build up over time in a MOSFET's insulating dielectric, increasing the threshold voltage which causes the transistor to switch more slowly. Bias temperature instability (BTI) is another effect that can charge the insulating dielectric over time, although some of its effects are temporary [5]. Like hot spots, both of these problems can lead to timing

errors (defined in Section 1.2.1). Unlike hot spots, these aging effects can take years to develop.

Worse problems can occur when the dielectric layer breaks down, which can result in a short that causes a permanent failure of a transistor. Another effect called electromigration causes atoms in wires to slowly "flow" downstream, thinning the wire upstream until it becomes a permanent open circuit defect [5].

#### 1.2 Root Cause Effects

The effects of many of the above root causes are predictable enough that they can be modeled. For each effect, there are activation conditions, or conditions required for the effect to occur. More precisely, an activation condition is the condition required for an error, fault, or bug to change the internal behavior of a design. Thus if an error, fault, or bug is not activated, then it is undetectable even with perfect observability of the internal behavior of a design.

### 1.2.1 Timing Errors

Power and thermal hot spots, charge carrier injection, and bias temperature instability all result in transistors switching more slowly than they normally would. The result is that signal propagation delays along chains of gates increase, resulting in a signal taking so long to propagate from a launch flip-flop to a latch flip-flop that it misses the latch window. The result is that the wrong value can be latched at the latch flip-flop; when this occurs it is known as a timing error.

We can model this timing error as a bit flip at the latch flip-flop, given these four activation conditions for a timing error to occur along a given combinational path at a given cycle from a launch flip-flop to a latch flip-flop:

- 1. The sum of the arrival time of the launch flip-flop output and delays of each gate along the path must exceed the required arrival time for the latch flip-flop input.

- 2. The path must be *sensitized*, meaning that all logic values are such that

- a flip in the logic value of the launch flip-flop results in a flip along each segment of the path up to and including the latch flip-flop.

- 3. The launch flip-flop toggles at the given cycle.

- 4. The latch flip-flop latches the wrong value. Favorable glitches may cause the latch flip-flop to latch an intermediate value that happens to be correct even though the final value arrives too late.

#### 1.2.2 Stuck-at Faults

Fabrication defects result in gate outputs being stuck at either a 0 or a 1. The more dramatic wear-out problems that cause permanent defects can also have this effect. Modeling these faults is straightforward: disconnect a net from its original driver and connect it to a constant logic 0 or 1 instead. Stuck-at 0 (1) faults have one activation condition, which is that the input logic values to the gate with the stuck-at fault are such that the output should be 1 (0). The result is an internally detectable deviation in the behavior of a design.

#### 1.2.3 Soft Errors

Soft errors cause random logic values to be injected into storage elements of a design, overwriting the previous value. For this event to be internally observable, the activation condition is that the value injected must differ from the value that would otherwise be latched at the storage element at the time of injection. Thus we model these events as random bit-flips at random cycles in randomly selected storage elements, using the value that would normally be latched as the reference for the flip.

### 1.2.4 Logic Bugs

While logic bug activation conditions and effects are in general more difficult to pin down than the above electrical bug scenarios, they still exist. Logic bugs have activation conditions, which are the conditions under which the internal behavior of a design deviates from what the designer expects, and effects, which are the actual behavior of the bug as compared to a designer's expectations.

# 1.3 Error Propagation

When an error, fault, or bug is activated, it has by definition begun to change the internal behavior of a circuit. This change in behavior is not necessarily externally observable, however. Errors that are activated have multiple possible outcomes:

- The error effects are *masked* before they affect any output of the circuit. This means the error changes the internal behavior of the circuit temporarily, but that eventually, the circuit reverts to behaving as if the error had never activated. Externally (i.e. observing the circuit outputs), there is no way to know a masked error has activated. An example of a masked error is a value that is computed incorrectly, but is then ignored because it is not selected by a multiplexer.

- The error effects change the output of the circuit. In this case, we say that the error is *unmasked*.

- For effects that are not quickly masked or unmasked but instead make it to internal storage elements, there can be a third "limbo" state known as *silent data corruption*. In this state, the error has changed the internal behavior of the circuit, but whether the error will be masked or unmasked depends on the next access to the corrupted storage elements. For example, the corrupted elements may be overwritten, in which case the error becomes masked or the corrupted elements may be read and outputted, in which case the error becomes unmasked. Since data can be stored in memory indefinitely, there is no limit to how long silent data corruption can last.

While unmasked errors are clearly the most problematic, one should be careful about considering masked errors to be benign. In the same way that errors have activation conditions, errors are also sensitive to masking conditions that can turn a masked error into an unmasked one. A particularly insidious case is a masking condition that causes an error to be masked in testing mode,

but unmasked in production mode. Thus for circuit validation, increasing observability to detect masked errors is also important.

# CHAPTER 2

## BACKGROUND

Each of the sections in this chapter provides some useful background information for the convenience of the reader who may be unfamiliar with some of the concepts in the chapters that follow.

### 2.1 Execution Signatures

A software program contains variables that will have dynamic values during the program execution. Similarly, a hardware design has storage elements such as flip-flops that will have dynamic values during hardware execution. An execution signature is a hashed trace of the dynamic value of variables during software or hardware execution. Comparing the trace of hardware to be validated with a reference execution trace is a useful way to catch bugs. As one might imagine, tracing all variables at all times during software or hardware execution is expensive. We can use the following complementary techniques to reduce that cost:

- 1. Select a subset of all variables to trace. This reduces overhead, but also observability.

- 2. Create a diverse tracing schedule (i.e. different variables are traced in different execution states). This allows tracing resources such as buffers and I/O ports to be shared, reducing overhead.

- 3. Hash some of the traced variables. In order for the hash to be reproducible to detect errors, the values of the traced variable must be known (i.e. if there is an unknown or "x" value, then the hash cannot be reproduced and false bug detection positives will occur).

- 4. Compute a running hash to combine variables across cycles. Again all of the values that go into this running hash must be known.

In Chapter 6, we use all four of these techniques, and hash *all* of the traced variables to detect errors, using the high-level synthesis binding solution to identify when register values are known.

#### 2.1.1 Catching Logic Bugs

If a design contains a non-deterministic logic bug and is run in a reference simulation and in hardware, the dynamic trace of the variable values will likely be different. The simulation would involve a different process (e.g. compilation by a high-level C compiler) than the hardware synthesis process, so the undefined behavior would likely manifest itself differently. For example, the values stored in uninitialized memory in hardware could be the device physics dependent power-on state, while uninitialized memory in a reference simulation might contain values from when it was used by another software process.

If a design only contains deterministic logic bugs and the simulation and synthesis tools correctly interpret the input code, the dynamic hardware and reference trace of the variable values will be identical. Thus hybrid comparison techniques will not catch deterministic logic bugs. The good news is that due to their deterministic nature, these bugs are easily reproducible in both hardware and reference executions. Furthermore, for hardware designs written in software input languages, we can leverage traditional software debugging techniques to debug hardware designs.

#### 2.1.2 Hash Functions

In order to minimize hardware cost, we select the following xor-based hash functions:

$$H(x_1, x_2, ..., x_n) = x_1 \oplus x_2 \oplus ... \oplus x_n$$

(2.1)

$$S_n = \begin{cases} H_0 \oplus C & \text{if } n = 0\\ H_n \oplus \text{rotate}(S_{n-1}, r) & \text{if } n > 0 \end{cases}$$

(2.2)

where H is the reduction function that reduces a set of multi-bit variable values (technique 3 above) to a single hash. Similarly,  $S_n$  is the running hash

that combines the values of H across execution cycles (technique 4 above) (H in cycle n is denoted  $H_n$ ). The function rotate(v, r) denotes bit rotation to the left of the bit vector v by r bits. C and r are constants. In Chapter 6, we refer to the hardware that implements these hash functions as an XOR tree and an LFSR, respectively.

Both of these functions have the desirable property that a change in any bit of the input variables will result in a change in at least one bit of the output. Equation (2.2) has the additional desirable property that  $S_n$  depends on the number of cycles that have passed, n, even if all  $H_n = 0$ .

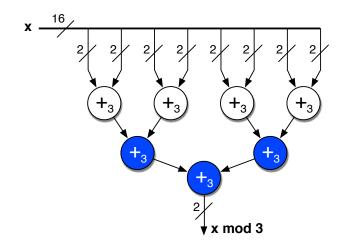

#### 2.2 Modulo Arithmetic

Modulo-b arithmetic is arithmetic defined in a finite field with b possible values, where each possible value corresponds to a remainder when an integer is divided by b (using Euclidean division so that remainders are always positive). Addition, subtraction, and multiplication are defined with "wraparound" arithmetic where the result is immediately divided by b and the remainder taken as the result.

For example, in modulo-3 space the possible values are  $\{0, 1, 2\}$  and 2+2=1 since in integer space (2+2) mod 3=1 where a mod b is the remainder after dividing a by b. Table 2.1 shows the mapping from integer space to modulo-3 space and Table 2.2 provides the modulo-3 addition, subtraction, and multiplication tables.

### 2.2.1 Properties

Since equivalent lightweight computations can be performed in modulo space as in integer space, modulo arithmetic can be used as a way to independently check integer computation. This works because we have defined a homomorphism from integer arithmetic to modulo arithmetic. In other words, given integers  $\{x, y, z\}$  and corresponding modulo variables  $\{x', y', z'\} = \{x, y, z\}$  mod b we observe the following properties:

$$x + y = z \implies x' + y' = z' \pmod{b} \tag{2.3}$$

Table 2.1: Integer to Modulo-3 Space Mapping

| Integer value  | -6 | -5 | -4 | -3 | -2 | -1 | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

|----------------|----|----|----|----|----|----|---|---|---|---|---|---|---|

| Modulo-3 value | 0  | 1  | 2  | 0  | 1  | 2  | 0 | 1 | 2 | 0 | 1 | 2 | 0 |

Table 2.2: Modulo-3 Addition, Subtraction, and Multiplication Tables

| + | 0 | 1 | 2 |

|---|---|---|---|

| 0 | 0 | 1 | 2 |

| 1 | 1 | 2 | 0 |

| 2 | 2 | 0 | 1 |

| _ | 0 | 1 | 2 |

|---|---|---|---|

| 0 | 0 | 2 | 1 |

| 1 | 1 | 0 | 2 |

| 2 | 2 | 1 | 0 |

| × | 0 | 1 | 2 |  |  |

|---|---|---|---|--|--|

| 0 | 0 | 0 | 0 |  |  |

| 1 | 0 | 1 | 2 |  |  |

| 2 | 0 | 2 | 1 |  |  |

$$x - y = z \implies x' - y' = z' \pmod{b} \tag{2.4}$$

$$xy = z \implies x'y' = z' \pmod{b}$$

(2.5)

where  $\pmod{b}$  next to an equation indicates that the arithmetic is performed in modulo-b space. Thus for Equations (2.3), (2.4), (2.5), z' can be independently computed two ways: by mapping z to modulo space or by mapping x' and y' to modulo space and performing the "shadow computation" in each equation.

Note that this "shadow computation" property holds for arbitrarily complex integer arithmetic involving addition, subtraction, and multiplication. For example,  $x^2-4xy+2y^2=z \implies x'^2-x'y'+2y'^2=z' \pmod{b}$ . Exploiting the ability of homomorphisms such as this integer to modulo-b mapping to scale to arbitrarily complex expressions is the key to implementing cost-effective error detection.

### 2.2.2 Aliasing

When using modulo-b arithmetic as an error detection technique, aliasing occurs when the integer result of an erroneous computation corresponds to the same modulo-b checksum as the correct result. For example, for modulo-3 arithmetic, if the correct integer result of a computation is 5, but the value -4 is produced instead since both values map to 2 in modulo-3 space (Table 2.1) the error may not be detected since the correct "checksum" was produced.

One should be particularly wary of the aliasing that can occur when

multiplying by a multiple of b. For example, for modulo-3 arithmetic, if any erroneous integer value is multiplied by 6, then the result will be 0 in modulo-3 space (Tables 2.1 and 2.2). Thus, in our application of modulo-3 arithmetic, we pay special attention to multiplication operations (see Section 7.1.2).

#### 2.2.3 Modular Base

To use modulo-b arithmetic to detect errors effectively in binary logic, we choose b such that  $z'=z \mod b$  is a function of all of the bits in z. For example, b=4 would fail this test because now z' is just the last two bits of z, ignoring the higher-order bits (and any errors in those bits). We also want each bit in z to have the ability to affect any bit in z' to reduce the probability of aliasing. For example, b=6 would fail this test because the last bit of z' would only be affected by the last bit of z. The choice of b will pass both of these tests if b is odd and  $b \ge 3$ . In Chapters 7 and 9, we choose b=3 to minimize the hardware cost, as only two bits are needed to represent the three possible modulo-3 values.

#### 2.2.4 Mersenne Numbers

For positive integers n we define the Mersenne numbers by  $M(n) = 2^n - 1$ . The use of M(n) as a modulo base has the following useful property for  $n \ge 2$ :

$$2^n = 1 \pmod{M(n)} \tag{2.6}$$

### 2.2.5 Binary Representations

Our encodings for modulo residues are based on the standard binary representation for integers, where bits have weights with successive powers of two. In other words the integer value of a particular sequence  $\{b_{n-1}, b_{n-2}, ..., b_0\}$  of bits is defined as:

$$v = \sum_{i=0}^{n-1} 2^i b_i \tag{2.7}$$

A standard Mersenne number residue r with base M(n) will be in the range  $0 \le r \le M(n) - 1 = 2^n - 2$ . Thus n bits are sufficient to encode a residue with base M(n), and the most significant bit (MSB),  $b_{n-1}$ , will have weight  $2^{n-1}$ . If a carry bit is generated from adding two MSB bits, it will have weight  $2^n$  which is equivalent to 1 by application of Equation (2.6).

#### 2.2.6 Normalization

There is one special encoding possible for an M(n) residue encoded with n bits, the value where all bits  $b_i = 1$ . This encoding has the integer value  $2^n - 1 = M(n)$  by Equation (2.7). Since this residue is the same as the modulo base, it is equivalent to zero. We call this special encoding for zero the *denormalized* encoding of zero, write it as -0, and call encodings that allow it *non-normalized* encodings.

### 2.3 High-Level Synthesis

High-level synthesis, also known as behavioral synthesis, is a process that turns a software behavioral specification with an architectural description into hardware that implements that specification. The input to a high-level synthesis tool is typically a C language dialect with language extensions (e.g. pragmas and directives) and libraries to annotate the behavioral description with architectural specifications. The output is a hardware description, typically specified in Verilog or VHDL. A typical synthesis engine will perform the following steps:

- 1. **Compilation**: The synthesis engine parses the input code and converts it to an intermediate representation (IR).

- 2. **Transformation and Optimization**: The synthesis engine runs the IR through a series of optimization passes, similar to software compiler optimizations. The engine also does architectural transformations such as loop unrolling and pipelining.

- 3. **Allocation**: For each hardware resource—memories, ports, registers, and functional units—the synthesis engine determines what kind and

how many of each to use. Larger allocations usually increase performance at the cost of area.

- 4. **Scheduling**: The engine creates a state machine corresponding to the control flow of the software specification. For each state, the engine determines what operations—computations, memory access, and/or I/Os—will occur in that state. The engine may insert extra states to provide sufficient cycles to complete complex chains of operations.

- 5. **Binding**: For each operation, the engine determines which hardware resource(s) will be involved in performing the operation. Operations that can never occur at the same time can share a common hardware resource. The engine inserts multiplexers at this stage to facilitate such sharing.

- 6. **RTL Generation**: The engine generates a complete RTL description of the final state machine and datapath solution.

# CHAPTER 3

## RELATED WORK

### 3.1 Hybrid Quick Error Detection

The inspiration for H-QED is QED [6–9], which is a software technique for the validation of programmable microprocessors. In general, validation techniques that target processors (e.g., [10,11] and others) are inadequate for bugs inside accelerators.

Given a high-level specification and a design produced by HLS (referred to as an implementation), there is a large class of techniques that check if the implementation is equivalent to the high-level specification, often relying on formal techniques [12–14]. The goal is to detect bugs in the implementation that are caused by the HLS tool. However, formal equivalence checking techniques are limited in their capacity to handle HLS transformations and this limitation is further compounded by the large state space of HLS implementations. In contrast, H-QED is a dynamic technique that integrates into the HLS engine to follow instructions through HLS transformations and to generate the corresponding software reference implementation. H-QED can be run in pre-silicon simulation at RTL simulation speeds (with acceptable overhead) or during post-silicon validation at full hardware speed.

### 3.1.1 Hybrid Tracing

Prior works such as [15,16] perform source-level transformations to create external ports for selected signals to improve observability. However, this approach requires manual source code instrumentation. Furthermore, source instrumentation interferes with compiler optimizations, creating intrusiveness. A hardware-software runtime trace comparison technique is proposed in [17,18] to provide automated HW/SW discrepancy detection. Both techniques use a

mapping between software variables and hardware components through LLVM variables to detect discrepancies and assist debug. Again, these techniques are intrusive as they insert additional error detection operations that change the schedule of the hardware design. In contrast, hybrid tracing instrumentation is integrated into HLS to eliminate intrusiveness, creating an RTL design with nonintrusive debugging annotations that can easily be removed before synthesis.

#### 3.1.2 Hybrid Hashing

Although hybrid hashing may appear to be similar to tracing techniques used in PSV (e.g., using trace buffers or system memory [19–22]), there are important differences:

- 1. Hybrid hashing systematically collects signatures, unlike tracing techniques that are often ad-hoc or based on heuristics.

- 2. Hybrid hashing does not require extensive low-level (e.g., RTL) simulation.

- 3. Hybrid hashing does not require designer-crafted assertions.

- 4. Hybrid hashing enables very short error detection latencies and high bug coverage, unlike tracing techniques that become ineffective for difficult bugs with long error detection latencies.

Hybrid hashing is distinct from fault-tolerant computing techniques for processors (e.g., using watchdog processors, DIVA, multi-threading and signature techniques for duplex systems [23–28]). Many of these techniques only check the register values as defined by the Instruction Set Architecture (ISA). In contrast, hybrid hashing is effective for arbitrary hardware accelerators created using HLS and automatically identifies signals to check in the resulting designs. Unlike time redundancy and cycle stealing techniques for enhancing reliability of designs created using HLS [29–31], hybrid hashing utilizes unique aspects of the PSV environment (where the generation of software signatures after a PSV run is acceptable vs. reliability techniques that focus on quick error recovery) to minimize area/performance costs and intrusiveness.

### 3.2 Modulo Shadow Datapaths

#### 3.2.1 Low-Level Fault Resilience

There are many existing approaches to fault resilience. The classical approach is modular redundancy [32,33], duplicating the entire hardware module and comparing the outputs for discrepancies. Such an approach has  $2 \times -3 \times$  area cost, which is prohibitively expensive and negates the benefits of Moore's law scaling.

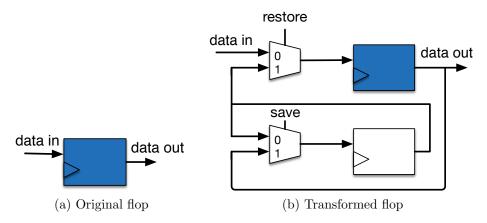

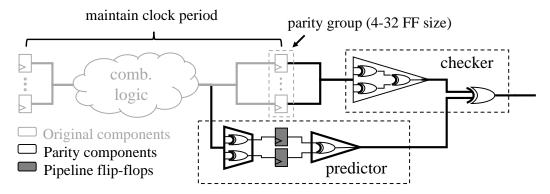

Razor logic [34,35], an approach involving creating a shadow latch for each flip-flop in a design, has been proposed to address timing errors, but also imposes timing constraints on a design. Flip-flop hardening techniques [36,37] have been proposed to address soft errors in flip-flops, but such techniques do not protect combinational logic. Logic parity [38] is another technique for protecting flip-flops by adding a parity flip-flop for flip-flop clusters with parity prediction and checking logic. Such parity techniques are practically limited to protecting only the flip-flops in a design using the aforementioned clustering technique [38] due to the high overheads (e.g., around 30% area overhead for a 32-bit adder [39]) associated with parity prediction across functional units.

While razor logic, flip-flop hardening, and parity are limited to certain kinds of faults and certain parts of a datapath, modulo shadow datapaths have none of these limitations. Modulo shadow datapaths holistically protect the entire datapath from input to output, including all of the combinational logic. Modulo shadow datapaths is a general purpose error detection technique with essentially no assumptions about fault behavior.

### 3.2.2 High-Level Error Resilience

There are also a number of high-level error resilience techniques, which are related to (or may be leveraged in) our high-level synthesis approaches in Chapters 7 and 9. DIVA [23] is a popular technique which uses an extra checker core to verify the correctness of a main core computation and commit only non-faulty results. Concurrent error detection (CED) [40] uses HLS to introduce redundancy at the functional unit level. Although each component is fully duplicated, this technique aims at reducing area and performance

overhead through resource sharing. But this technique can incur at least 75% area cost for simple and small datapaths.

Another approach is time-redundancy, where we re-compute results using the same hardware units to detect errors. In [41], Wu and Karri use a time redundancy-based concurrent error detection scheme with diverse binding solutions in its re-computation stage but has performance overheads even though it incurs low area cost. Argus [42] is a prototype processor with a modulo-3 arithmetic checker that can detect up to 98.0% and 98.8% of unmasked transient and permanent errors respectively. Argus has low area (17%) and performance (4%) costs but it is limited to the Von Neumann processor architecture and, to the best of our knowledge, there is no similar work in high-level synthesis that targets application-specific custom logic and accelerator designs.

In [43], Karri et al. integrated modular redundancy into high-level synthesis and presented techniques to increase reliability with cost and performance constraints and decrease cost given reliability constraints, but not both together. New approaches to modular redundancy such as statistical error compensation (SEC) involving pairing an estimator module with unreliable hardware still come with high (50-100%) area cost [44]. Tosun et al. [45] proposed a technique to recover from soft errors but do not perform any error injection experiments and has a passive approach to masking errors whereas we actively detect and correct errors.

Finally, Algorithm-Based Fault Tolerance (ABFT) [46,47] is an algorithm-level technique for protecting linear vector and matrix computations by predicting and checking the sums of groups of output elements. ABFT can involve expensive extra memory accesses for checksum computation and storage and may require the duplication of vectors for certain computations. In Chapter 9, we empirically show that these costs make cost-effective application of ABFT to reliable accelerator designs difficult.

#### 3.2.3 Modulo Arithmetic Functional Units

For small modulo bases, a lookup table based approach has been used for basic functional units [48] with explicit *don't cares* inserted to provide hints to the logic synthesis engine for inputs combinations that should never occur.

A reducer is built with a tree of such lookup-table based modulo adders [48]. Such an approach is impractical for larger bases due to exponential scaling.

Piestrak et al. propose a design for a modulo-3 reducer consisting of full-adder (FA) cells and interleaved inverters [48, 49] which exploits the fact that for a given bit  $b \in \{0,1\}$ ,  $2b = -b = 3 - b = 2 + (1 - b) \pmod{3}$ . In other words, bits of weight 2 can be inverted and treated as a bit of weight 1 with a constant offset (which can be lumped together at the end) so that all bits have the same weight of 1 and can be passed through stages of FAs. While this design may appear superficially similar to our reducer design in Figure 8.1b on page 83, our design uses a more general strategy inspired by Wallace trees that does not require separate inverters. Furthermore our strategy generalizes to any Mersenne base while their design trick is limited to modulo-3 arithmetic.

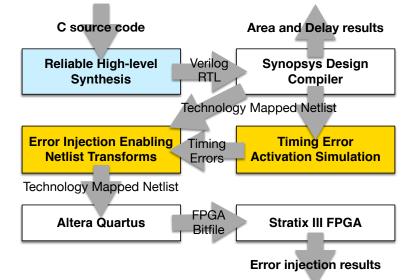

For cryptography applications, there are also a number of hardware accelerator designs for accelerating modulo exponentiation of large (e.g. 256-bit) numbers which is performed with a series of modulo multiplies [50]. These designs use application-specific algorithms (e.g. Montgomery multiplication [51]) that make them very specialized for big-integer modulo exponentiation, and thus unsuitable for reliability applications.

### 3.3 Cross-Layer Reliability

The CLEAR study [38] was a cross-layer approach to finding the most cost-effective way to improve flip-flop soft error reliability in programmable microprocessors, considering both software and hardware transformations and their combinations to improve reliability. But, with Dennard scaling ending, the status quo of using programmable microprocessors for all computation is disrupted by hardware accelerators that proliferate on SoCs and embedded FPGAs due to their performance and energy benefits. Thus, a complete reliability solution for modern complex SoCs must consider both microprocessors and accelerators.

In Chapter 9, we take a cross-layer approach to the reliability problem for application specific hardware accelerators. While existing coding techniques address soft errors in memories and CLEAR [38] addressed soft errors in microprocessor flip-flops; cost-effective error resilience for flip-flops in hardware

accelerators remains a challenging problem.

Compared to the microprocessor reliability problem, the hardware accelerator reliability problem poses some unique opportunities and challenges. As shown in [38], when limiting processor cores to running specific applications, combinations incorporating algorithm-level techniques like algorithm-based fault tolerance (ABFT) correction can further reduce energy overheads. In general-purpose processor cores, imposing such limitations are not always possible; however, the application-specific nature of accelerators allows us to fully explore these opportunities.

Additionally, in application-specific hardware accelerators, most of the software parts of the stack are removed since the algorithm is hard-wired into the hardware logic. Thus, algorithm and instruction overhead (which manifested as execution time overhead on microprocessors) is translated into hardware overhead. On the other hand, this translation into hardware results allows for optimizations of the software techniques at the hardware level by leveraging hardware customization not previously possible in general-purpose processors. Finally, given the interest of implementing application-specific accelerators not only on custom application-specific integrated circuits (ASICs) but also in an agile manner by utilizing reconfigurable field-programmable gate arrays (FPGAs), it is necessary to explore and understand the implications for reliability when changing the underlying hardware assumptions.

## CHAPTER 4

# HYBRID QUICK ERROR DETECTION

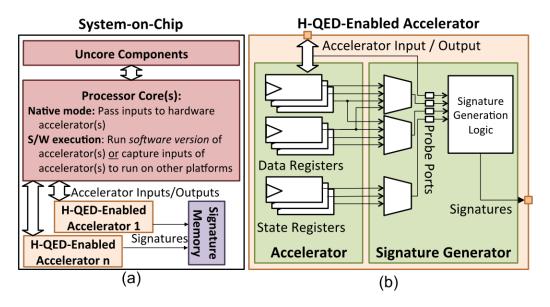

In this chapter, we introduce the basic concepts for the Hybrid Quick Error Detection (H-QED) technique to overcome validation and debugging challenges for non-programmable hardware accelerators on SoCs. Such accelerators implement a pre-defined set of functions and are not programmable using software (unlike processor cores or software-programmable accelerators such as GPUs). H-QED is inspired by the QED technique for PSV [6–9]. Since QED is (mostly) implemented in software, the error detection latencies of bugs inside hardware accelerators can be very long (e.g., bounded by long execution times of hardware accelerators). H-QED builds on advances in high-level synthesis (HLS) [52,53] to overcome this challenge by automatically embedding small hardware structures inside hardware accelerators. H-QED simultaneously improves error detection latencies and coverage of logic and electrical bugs inside hardware accelerators. H-QED is compatible with QED. By combining H-QED with QED, we provide a systematic solution for PSV of SoCs consisting of processor cores, uncore components, software-programmable accelerators, and hardware accelerators. H-QED can be applied to both pre-silicon and post-silicon validation and debugging scenarios and provides effective source-code bug localization.

## 4.1 Basic Principles

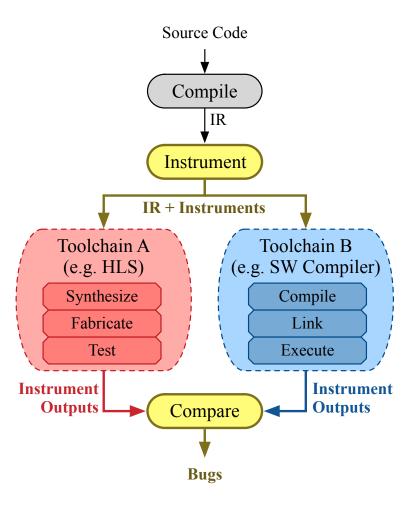

The basic principles of H-QED are illustrated in Figure 4.1, which involves three key components:

- fine-grained debugging instrumentation

- simulation/execution with two diverse toolchains

- comparison of the instrument outputs

Figure 4.1: Basic working principles of H-QED. A toolchain can be any process that executes or simulates the design. IR = Intermediate Representation.

The instrument pass adds debugging logic or instructions that cause the design to generate output which is a function of the design's internal state. This instrumentation can be translated to unsynthesizable code for presilicon validation or signature generation logic for post-silicon validation. The two toolchains are abstract processes that perform transformations on the design leading to some execution or simulation that produces the runtime output of the instruments. When a design contains a non-deterministic bug, it is unlikely that two diverse toolchains will generate models and/or physical designs with identical external and internal behavior. Fine-grained instruments will capture this behavioral discrepancy resulting in two different instrument outputs and the bug will be caught. Because the instruments are fine-grained, the error detection latency will be low and many masked bugs will also be caught. Thus H-QED should quickly detect any bug in the source code that results in non-deterministic behavior. It is also clear from Figure 4.1 that H-QED can detect toolchain bugs as a bug in one toolchain that affects the instrument outputs in that branch will result in a mismatch with the outputs produced by the other toolchain. When one "toolchain" involves a full IC fabrication and testing process, this capability of H-QED is particularly important for detecting electrical bugs.

While different variations of this process are possible (in particular integrating the instrumentation pass into parts of the two toolchains is beneficial as we will see), the key invariant is that the instruments must produce the same output in both toolchains if the design is free of bugs. In order to achieve this, the instruments must generate output that is a function of deterministic variables, e.g. output cannot depend on signals in unknown states. Furthermore, the order of the instrument output must be preserved in both toolchains. Finally, an important constraint from a practical point of view is to insert instruments so as to avoid *intrusiveness*, meaning that the external and internal behavior of a design should not change when instruments are added. Instruments that change the behavior of a design can also change the behavior of bugs in that design, undermining its bug detection and localization benefit.

## 4.2 Hybrid Tracing vs. Hybrid Hashing

Since pre-silicon validation and post-silicon validation have different constraints for inserting instruments into a design, we created different variations of H-QED for each scenario. In this thesis, we present both adaptations of H-QED: a pre-silicon tailored adaptation called *hybrid tracing* which we discuss in Chapter 5 and a post-silicon tailored adaptation called *hybrid hashing* which we discuss in Chapter 6. We now provide a brief comparative overview of each adaptation.

#### 4.2.1 Hybrid Tracing

In pre-silicon validation, simulation time is the primary challenge. As mentioned before, simulation speeds are many orders of magnitude slower than real-time, limiting testing coverage. To address this problem, hybrid tracing leverages HLS to select RTL signals for only CDFG variables, minimizing overhead. Hybrid tracing also leverages co-simulation to use high-level language simulation for parts of the design not being directly tested. As mentioned before, high-level language simulation is  $1000\times$  faster than RTL simulation. Compared to hybrid hashing, hybrid tracing has the following unique advantages:

- 1. Hybrid tracing instrument output produces full variable values with unsynthesizable constructs, making the design state fully visible.

- 2. Hybrid tracing leverages this information to pinpoint the source code location for bug activation.

- 3. Hybrid tracing instruments are easily removed or ignored from the generated RTL when the design passes validation and is ready for synthesis.

## 4.2.2 Hybrid Hashing

In post-silicon validation, minimizing area and instrument output bandwidth costs are the primary challenges. To meet bandwidth constraints, hybrid hashing probes internal CDFG variable values and reduces those values with

a running hash function, reducing output bandwidth to a single bit for each multi-cycle interval. The hash function logic has significant area cost, so it is shared as much as possible with multiplexers by scheduling probes for a "non-temporary" variable subset (variables with long lifetimes and thus also scheduling flexibility). Compared to hybrid tracing, hybrid hashing has the following unique advantages:

- 1. Hybrid hashing instruments are designed to be synthesized as lightweight hardware integrated into an accelerator, enabling bugs to be caught (electrical bugs in particular) that could not be caught in pre-silicon validation due to model limits.

- 2. Hybrid hashing has essentially no performance impact and allows a manufactured IC to run at full speed.

# 4.3 Effectiveness and Practicality

As a preview for our experimental results when applying H-QED, we observe the following, demonstrating the effectiveness and practicality of the technique:

- 1. H-QED enables 2–3 orders of magnitude improvement in error detection latencies for both electrical bugs and logic bugs vs. validation techniques using end-result-checks that compare accelerator outputs against known correct outputs.

- 2. H-QED uncovered two previously unknown logic bugs in the widely used CHStone HLS benchmark suite [54].

- 3. H-QED does not require any failure reproduction or low-level simulation (e.g., RTL or netlist) to detect bugs.

- 4. H-QED allows accelerators to operate in "native" mode (similar to normal system operation) and has a minimal intrusiveness impact. (Incorporation of H-QED continues to detect bugs that are detected by traditional validation techniques.)

- 5. Hybrid tracing detects all non-deterministic logic bugs in CHStone within one cycle.

- 6. Hybrid tracing pinpoints where in the source code the bug activates and provides a strong hint for possible bug fixes.

- 7. Hybrid hashing improves electrical bug (timing error) coverage by up to  $3 \times$  compared to PSV techniques using end-result-checks.

- 8. Hybrid hashing incurs an 8% accelerator area overhead and negligible performance costs.

Chapters 5 and 6 discuss our pre-silicon and post-silicon H-QED implementations in detail. Chapter 5 discusses the hybrid tracing technique and Chapter 6 discusses the hybrid hashing technique.

## CHAPTER 5

# PRE-SILICON DEBUG: HYBRID TRACING

We call our pre-silicon variation of H-QED hybrid tracing since we use uncompressed traces of variable values for the instrument outputs in Figure 4.1 on page 26. Hybrid tracing can be used for both module-level pre-silicon verification of HLS-produced RTL as well as pre-silicon integration testing — verification of multiple RTL modules and software on a CPU into a system. Although module-level testing is important, integration testing invariably detects additional bugs that went undetected due to insufficient module-level test vectors or bugs that relate to integration (e.g. a module that works perfectly with the expected number of input data items, but another module sends the wrong amount of data). In both cases, the goal of hybrid tracing is to detect logic bugs as RTL-level simulation models only logic, not electrical behavior.

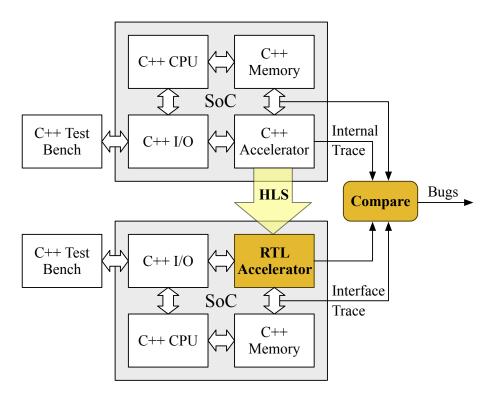

As illustrated in Figure 5.1, hybrid tracing enables hardware designers to isolate logic bugs by swapping between C/C++ reference implementations and RTL implementations with HLS. Thus, designers can validate complex designs piecemeal, selecting one module at a time to integrate with the rest of the system for verification. Note that the designer of a target module only needs high-level C/C++ models of the system it interfaces with, which need not be synthesizable, enabling early stage integration testing for parts that are synthesizable. Our framework compares the series of module output values for discrepancies between the software model and the RTL implementation. When validation reveals a problem due to non-deterministic behavior, our code instrumentation, trace comparison and back-tracing steps (discussed in Section 5.2) provide the hardware designer with C/C++ locations where the discrepancies occur.

Figure 5.1: Using hybrid tracing for early pre-silicon integration testing.

Table 5.1: Methods for Catching Different Kinds of Logic Bugs

|                   | unactivated | masked          | unmasked    |

|-------------------|-------------|-----------------|-------------|

| deterministic     | coverage    | unit testing    | debug tools |

| non-deterministic | analysis    | s hybrid tracii |             |

# 5.1 Comparison to Software Debugging

As mentioned in Chapter 1, logic bugs have many ways to elude detection. Fortunately, hybrid tracing leverages HLS, which brings in a variety of software debugging tools to bear on the problem. Table 5.1 broadly classifies logic bugs by their behavior in three categories: unactivated, masked, and unmasked. Each of these bug classes can be further divided into deterministic and non-deterministic subcategories.

Unactivated bugs are caused by gaps in coverage (e.g. the buggy line of code was never executed or a condition was never met) which are best addressed by software coverage analysis tools. Such tools will point out these gaps, allowing the hardware designer to modify the design or test vectors to eliminate the coverage gaps and activate bugs that may be hiding in those gaps. A deterministic, activated bug is reliably reproducible by definition. Existing

software debugging tools are good at helping a user to isolate a deterministic bug. While software debugging tools can help with deterministic, masked bugs as well by increasing observability, software practices also encourage unit testing to help detect such masked bugs in the first place.

Software debugging techniques are much less useful for non-deterministic, activated bugs. By definition, such bugs are likely to behave differently in a software testing environment when compared to an RTL simulation environment. For example, the bug may cause a failure in RTL simulation, but the high-level simulation produces correct output, rendering software debugging techniques by themselves unhelpful. Without any aid to track this bug down, the hardware designer has little choice but to attempt to find the bug in the RTL waveform by tracing backward in execution from the observed failure to the root cause. After this painstaking process, the designer has another difficult problem to solve: determining the source-code level meaning for the buggy RTL variable he identified. This can be very non-trivial with the complex software and HLS transformations involved in translating a high-level language to RTL. Hybrid tracing is designed to address both of these difficult problems, making isolation for the most difficult bugs automated and fast.

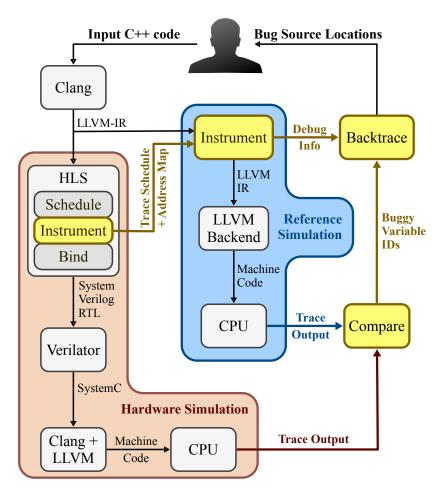

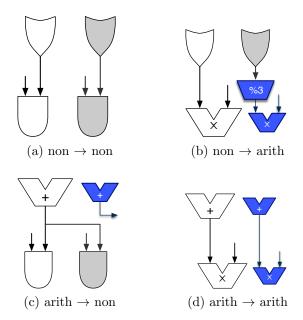

# 5.2 Hybrid Tracing Framework

Our hybrid tracing implementation is illustrated in Figure 5.2. The input to the framework is a C++ module targeted for debugging and written with a synthesizable subset of C++ supported by the HLS tool. Additional non-synthesizable modules (not shown to simplify the illustration) representing the system environment such as those in Figure 5.1 can be integrated into the hardware simulation through co-simulation and into the software simulation environment through linking.

As one would expect from an H-QED variant, there are two branches of the framework, a hardware RTL-level simulation branch and a "reference" software branch. Both branches have integrated instrumentation passes to enable greater observability of internal source-level variables. In the hardware branch, the instrumentation is integrated into the HLS engine after scheduling to minimize intrusiveness. The HLS engine produces SystemVerilog as output, which is then translated to a cycle-accurate SystemC module

Figure 5.2: Our hybrid tracing framework.

using Verilator [55,56]. The software branch performs software compilation using the LLVM framework [57] and contains a custom instrumentation pass designed to reproduce the trace output produced by the hardware simulation given some scheduling and address mapping information from the HLS instrumentation pass. The output of the two branches is variable trace sequences for discrepancy analysis; when mismatches are found, information on which variable(s) caused the discrepancy can be used to identify the C/C++ source code involved with the bug. We now discuss each component of our framework in detail in the following subsections.

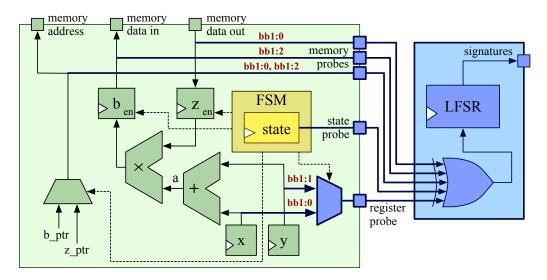

#### 5.2.1 Hardware Simulation

The hardware simulation is a cycle-accurate RTL simulation of the hardware module in a test environment that can include high-level implementations of modules it interfaces with. This process starts with the high-level synthesis of the LLVM Intermediate Representation (LLVM-IR) for the hardware module. We use an in-house high-level synthesis engine that is based on LegUp [58]. We insert our hardware instrumentation pass after scheduling and optimization, but before binding. The pass takes an optimized, scheduled CDFG as input and adds trace annotations on all variables that have a software counterpart.

In our previous prototype implementation in [3], the instrumentation pass was inserted pre-scheduling. The problem with this approach is that the trace calls need to be scheduled and their dependencies considered. This results in some cases in deferred scheduling of trace calls to maintain ordering (i.e. the scheduler would prefer to reorder the trace calls to match the scheduling of the operations traced, but is not allowed to) which can increase register pressure artificially, change the synthesis result, and result in multicycle error detection latencies. Furthermore, trace calls create false dependencies that can potentially block or complicate HLS optimizations. To improve the hybrid tracing implementation in [3], we split the instrumentation pass into complementary hardware and software passes as shown in Figure 5.2 and integrated the hardware instrumentation pass into our HLS engine.

Adding the trace calls pre-binding makes them mere debugging annotations on signals that the HLS engine has decided are "real" signals (i.e. not redundant operations or dead operations) that must be bound to a physical

Listing 5.1: Input C++ Code (foo.cpp)

```

int bar [4];

int foo (int x, int index) {

int y = bar[index];

bar[index] = x + y;

return x * y;

}

```

Listing 5.2: LLVM-IR (Simplified for Clarity)

```

global [4 x i32] bar

i32 foo (i32 x, i32 index) {

i32 * addr = getelementptr(bar[index])

i32 y = load addr

i32 tmp1 = add x, y

store tmp1 → addr

i32 tmp2 = mul x, y

ret tmp2

}

```

resource. The trace annotations simply follow their operations and variables to the physical functional units and registers that they are bound to, producing the appropriate output in the state the variable is generated. During binding, the annotations are handled separately from the binding of "real" hardware. In other words, the addition of these debugging annotations is nonintrusive as they do not affect the synthesizable binding solution generated by the HLS engine. Furthermore, the annotations can easily be removed or ignored for the purpose of synthesis.

We illustrate our hardware instrumentation pass with an example shown

Listing 5.3: Scheduled Operations (Custom IR)

Listing 5.4: Hardware Trace Operations Inserted

```

i32 foo (i32 x, i32 index) {

...

[0] trace(0, x)

[0] trace(1, index)

[0] trace(2, addr)

[1] trace(3, y)

[1] trace(4, tmp1)

[2] trace(5, tmp2)

[2] ret tmp2

}

```

Listing 5.5: Software Trace Operations Inserted

```

i32 foo (i32 x, i32 index) {

...

trace(0, x)

trace(1, index)

trace(2, addr_convert(addr))

trace(3, y)

trace(4, tmp1)

trace(5, tmp2)

ret tmp2

}

```

Table 5.2: Hardware Address Map

| Memory | Address | Depth | Width |  |

|--------|---------|-------|-------|--|

| bar    | 0x1000  | 4     | 32    |  |

Table 5.3: Trace Schedule

| Func. | Block | Traced Variables      |

|-------|-------|-----------------------|

| foo   | entry | x:0, index:1, addr:2, |

|       |       | y:3, tmp1:4, tmp2:5   |

Table 5.4: Debugging Information

| $\operatorname{id}$ | func:var  | file:line:col |

|---------------------|-----------|---------------|

| 0                   | foo:x     | foo.cpp:2:14  |

| 1                   | foo:index | foo.cpp:2:21  |

| 2                   | foo:addr  | foo.cpp:3:16  |

| 3                   | foo:y     | foo.cpp:3:9   |

| 4                   | foo:tmp1  | foo.cpp:4:20  |

| 5                   | foo:tmp2  | foo.cpp:5:14  |

Table 5.5: Address Translation Table

| Variable | SW addr | HW addr |

|----------|---------|---------|

| bar[0]   | 0xa7010 | 0x1000  |

| bar[1]   | 0xa7014 | 0x1001  |

| bar[2]   | 0xa7018 | 0x1002  |

| bar[3]   | 0xa701c | 0x1003  |

in Listings 5.1–5.5 and Tables 5.2–5.5. Listing 5.1 shows an example input C program with a global variable to be mapped to a memory and a function which becomes a hardware module. Listing 5.2 shows the same program lowered to LLVM-IR and Listing 5.3 shows the scheduled, optimized hardware IR (internal scheduled CDFG and memory address space map representation) right before binding. The memory is annotated with its base address on the left, and each instruction is annotated on the left with scheduling information indicating the cycles the instruction is scheduled for execution in. An instruction result becomes available on the final cycle it executes.

Listing 5.4 shows the additional trace instructions inserted by our hardware instrumentation pass as well as their scheduled states. Table 5.2 shows the hardware address map determined by our HLS engine and passed to the software instrumentation pass (Section 5.2.2). Each row of the address map indicates an LLVM variable, its base hardware address and the corresponding memory block depth and width. Table 5.3 is the trace schedule passed from our hardware instrumentation pass to the software instrumentation pass. The trace schedule has a row for each basic block in each function and indicates the LLVM-IR variables traced in that basic block, in the order they are traced, as well as a unique integer identifier for each variable.

The challenge in creating this trace schedule is mapping hardware IR variables to LLVM-IR variables. Not all LLVM-IR variables have a corresponding hardware IR counterpart as some CDFG nodes may be optimized away by HLS transformations (e.g. a global array reference becomes a constant address in hardware IR after the HLS engine defines a static address space mapping which can lead to further constant propagation optimizations). Similarly not all hardware IR variables have an LLVM-IR counterpart. An abstract LLVM-IR operation such as the memory address computing getelementptr operation can involve a number of additions and multiplications, generating multiple hardware IR variables that represent intermediate computations and

do not correspond to the final getelementptr result.

Our solution to this problem is to propagate debugging annotations in our hardware IR. During the initial lowering of LLVM-IR to our hardware IR, we annotate hardware IR CDFG nodes with references to the corresponding LLVM-IR variables they are equivalent to. We then preserve these LLVM-IR variable references across hardware IR transforms such as scheduling and optimization where feasible. Even if a variable is lowered to a constant, we propagate the variable annotation to a constant as this enables the compile-time computation of the constant value to be checked. Our hardware instrumentation pass can then scan the hardware IR to find all nodes with debugging annotations, generate trace instructions for them, and use the annotations to produce the corresponding LLVM-IR instruction in the trace schedule.

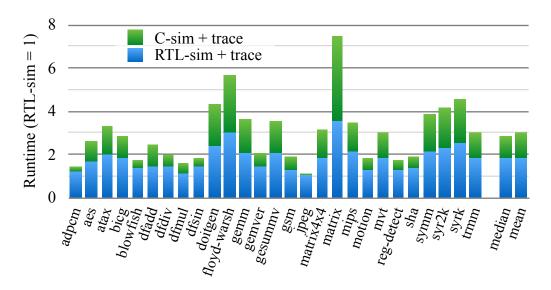

Once the trace annotations are inserted, our HLS engine performs binding and finishes with RTL generation, during which our HLS engine lowers each "trace" instruction instance to a SystemVerilog "sfwrite" call that prints the corresponding variable ID and value to a file.<sup>1</sup> The hardware simulation process then proceeds with the following steps: