© 2017 Li-Wen Chang

#### TOWARD PERFORMANCE PORTABILITY FOR CPUS AND GPUS THROUGH ALGORITHMIC COMPOSITIONS

BY

LI-WEN CHANG

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2017

Urbana, Illinois

Doctoral Committee:

Professor Wen-mei W. Hwu, Chair Professor Deming Chen Associate Professor Nam Sung Kim Associate Professor Steven S. Lumetta

# ABSTRACT

The diversity of microarchitecture designs in heterogeneous computing systems allows programs to achieve high performance and energy efficiency, but results in substantial software redevelopment cost for each type or generation of hardware. To mitigate this cost, a performance portable programming system is required.

This work presents my solution to the performance portability problem. I argue that a new language is required for replacing the current practices of programming systems to achieve practical performance portability. To support my argument, I first demonstrate the limited performance portability of the current practices by showing quantitative and qualitative evidences. I identify the main limiting issues of conventional programming languages. To overcome the issues, I propose a new modular, composition-based programming language that can effectively express an algorithmic design space with functional polymorphism, and a compiler that can effectively explore the design space and facilitate many high-level optimization techniques. This proposed approach achieves no less than 70% of the performance of highly optimized vendor libraries such as Intel MKL and NVIDIA CUBLAS/CUSPARSE on an Intel i7-3820 Sandy Bridge CPU, an NVIDIA C2050 Fermi GPU, and an NVIDIA K20c Kepler GPU.

To my family, for their love and support.

# ACKNOWLEDGMENTS

I would like to thank my advisor, Professor Wen-mei W. Hwu, for his tremendous mentorship, patience and support. He has always motivated my work and been patient with me. His wisdom will keep inspiring me in my professional career and personal life.

I would like to thank all members of the IMPACT research group, past and present, for their help and camaraderie. They are, in no particular order, Chris Rodrigues, Sara Baghsorkhi, Alex Papakonstantinou, John Stratton, I-Jui Sung, Xiao-Long Wu, Nady Obeid, Victor Huang, Deepthi Nandakumar, Hee-Seok Kim, Nasser Anssari, Tim Wentz, Daniel Liu, Izzat El Hajj, Steven Wu, Abdul Dakkak, Simon Garcia de Gonzalo, Wei-Sheng Huang, Carl Pearson, Cheng Li, Sitao Huang, Tom Jablin, John Larson, Chia-Jen Chang, Chih-Sheng Lin, Judit Planas, Jose Cecilia, Juan Gómez Luna, Javier Cabezas, Isaac Gelado, Nacho Navarro, Hiroyuki Takizawa, Xuhao Chen, Omer Anjum, and Mohamed El Hadedy.

Particularly, I would like to thank Izzat El Hajj, Simon Garcia de Gonzalo, Sitao Huang, Chris Rodrigues and Abdul Dakkak for help in design and coding development of this work. Additionally, I want to thank Carl Pearson, Hee-Seok Kim, Juan Gómez Luna and John Stratton for help in performance portability study and survey.

Also, I want to thank Marie-Pierre Lassiva-Moulin, Andrew Schuh, and Xiaolin Liu for their help, and convey my gratitude to a lot of people I met during my time here, including Wooil Kim, Deming Chen, Nam Sung Kim, Steven Lumetta, and those people I forget to mention or do not know the names of, especially the cleaner of my office.

Finally, I would like to thank my parents and my wife for their unconditional love and support. Thank you everyone.

# TABLE OF CONTENTS

| LIST OF TABLES                                                                                                              | i      |

|-----------------------------------------------------------------------------------------------------------------------------|--------|

| LIST OF FIGURES                                                                                                             | i      |

| LIST OF ABBREVIATIONS                                                                                                       | X      |

|                                                                                                                             | 1<br>1 |

|                                                                                                                             | 3      |

| 0 0 0                                                                                                                       | 4      |

| Ū                                                                                                                           | 5      |

| 1.5 Organization of this Dissertation $\ldots \ldots \ldots$ | 6      |

| CHAPTER 2 SURVEY OF PERFORMANCE PORTABILITY 7<br>2.1 Performance Portability Challenges and Conventional Tech-              | 7      |

| · •                                                                                                                         | 7      |

| 2.2 Current Status of Portable Languages                                                                                    | 5      |

| CHAPTER 3 TANGRAM OVERVIEW                                                                                                  | 1      |

| 3.1 Conventional Problem-solving Process                                                                                    | 1      |

| 3.2 Design Space and Performance Portability                                                                                | 3      |

| 3.3 TANGRAM Programming System                                                                                              | 3      |

| CHAPTER 4 TANGRAM LANGUAGE                                                                                                  | )      |

| 4.1 Design Space and Language                                                                                               | )      |

| 4.2 TANGRAM Language Design Objectives                                                                                      |        |

| 4.3 Code Example $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 35$                                 |        |

| 4.4 Recommended Programming Workflow                                                                                        |        |

| 4.5 Comparison of Related Composition-based Languages 37                                                                    | 7      |

| 4.6 Feature Beyond Performance Portability                                                                                  | )      |

| CHAPTER 5 HARDWARE ABSTRACTION AND COMPOSITION 40                                                                           | )      |

| 5.1 Architectural Hierarchy in Hardware Abstraction 40                                                                      | )      |

| 5.2 Composition Rule $\ldots$ 42                                                                                            | 2      |

| 5.3 Composition Specialization $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 45$                                        | 5      |

|                                                                                                                             |        |

| 5.4   | Model Extensibility                                       | 49 |

|-------|-----------------------------------------------------------|----|

| 5.5   | Discussion of Hardware Abstraction                        | 50 |

| CHAPT | FER 6    TANGRAM COMPILER                                 | 51 |

| 6.1   | Compiler, Design Space and Performance Portability        | 51 |

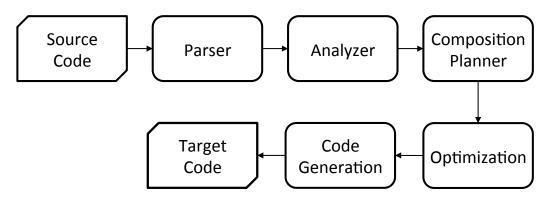

| 6.2   | TANGRAM Compiler Design Overview                          | 54 |

| 6.3   | TANGRAM Compiler Infrastructure                           | 55 |

| 6.4   | Parser                                                    | 58 |

| 6.5   | Analyzer                                                  | 58 |

| 6.6   | Composition Planner                                       | 63 |

| CHAPT | TER 7 OPTIMIZATION AND CODE GENERATION                    | 68 |

| 7.1   | Optimization                                              | 69 |

| 7.2   | Code Generation                                           | 71 |

| CHAPT | ΓER 8 EVALUATION                                          | 75 |

| 8.1   | Setup                                                     | 75 |

| 8.2   | Performance Results                                       | 77 |

| 8.3   | Discussion                                                | 83 |

| 8.4   | Performance Comparison to Existing Composition-based Lan- |    |

|       | guage                                                     | 84 |

| CHAPT | FER 9 CONCLUSION AND FUTURE WORK                          | 86 |

| 9.1   | Conclusion                                                | 86 |

| 9.2   | Future Work                                               | 87 |

| REFER | RENCES                                                    | 90 |

# LIST OF TABLES

|     | Overview of Performance Portability Challenges and Techniques<br>Overview of Languages and Techniques |    |

|-----|-------------------------------------------------------------------------------------------------------|----|

|     | Function and Data Qualifiers                                                                          |    |

| 6.1 | Relationship between Level Capability to Codelet Property                                             | 62 |

| 7.1 | Codegen Preprocessors                                                                                 | 72 |

| 8.1 | Benchmarks                                                                                            | 76 |

# LIST OF FIGURES

| 1.1                                      | OpenCL SGEMM Performance Portability Evaluation                                                                                                                                                                                                                                                               | 2  |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1                                      | Over-decomposition and Coarsening: Performance com-<br>parison of AMD and Intel CPU OpenCL stacks on an i7-<br>3820 CPU. AMD results are used as baselines                                                                                                                                                    | 8  |

| 2.2                                      | Memory Characteristics and Tiling: Performance of SGEMM<br>with different tiling strategies and tuning parameters on<br>different devices. White and black bars are normalized to<br>different references. Performance relative to reference is                                                               |    |

|                                          | compared, not absolute performance                                                                                                                                                                                                                                                                            | 9  |

| 2.3                                      | Atomic Efficiencies and Choices of Algorithms: Stream<br>compaction with shared memory atomics versus Thrust                                                                                                                                                                                                  |    |

|                                          | prefix sum                                                                                                                                                                                                                                                                                                    | 11 |

| 2.4                                      | Reduction with Multiple Levels                                                                                                                                                                                                                                                                                | 12 |

| 3.1                                      | Conventional Problem-Solving Abstraction Hierarchy and<br>Corresponding Tasks: At left are levels of abstraction trans-<br>lating a problem into a computational solution. At right<br>are tasks associated with their level of abstraction where<br>they are typically addressed, and a typical boundary be- |    |

|                                          | tween manual and automatic tasks.                                                                                                                                                                                                                                                                             | 22 |

| $\begin{array}{c} 3.2\\ 3.3 \end{array}$ | Illustration of Relationships among Different Design Points<br>TANGRAM's Problem-Solving Abstraction Hierarchy and<br>Corresponding Tasks: Red, bold-line boxes are different                                                                                                                                 | 25 |

|                                          | parts from the conventional one                                                                                                                                                                                                                                                                               | 26 |

| 3.4                                      | Big Picture of TANGRAM for Various Devices                                                                                                                                                                                                                                                                    | 27 |

| 3.5                                      | TANGRAM's Workflow                                                                                                                                                                                                                                                                                            | 28 |

| 4.1                                      | Example of Linear Combination                                                                                                                                                                                                                                                                                 | 31 |

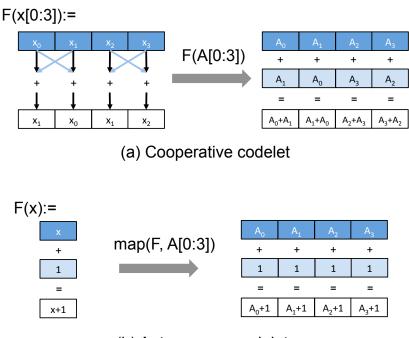

| 4.2                                      | Vectorization for Cooperative and Autonomous Codelets                                                                                                                                                                                                                                                         | 33 |

| 4.3                                      | Codelet Examples for a sum Spectrum                                                                                                                                                                                                                                                                           | 36 |

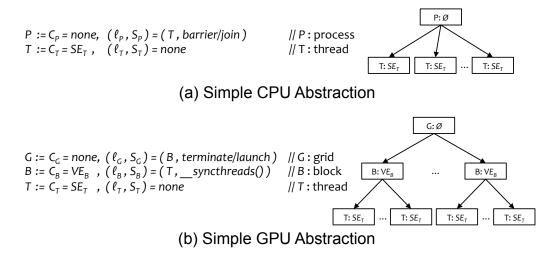

| 5.1                                      | Hardware Abstraction of Architectural Levels                                                                                                                                                                                                                                                                  | 40 |

| 5.2                                      | Examples and Illustrations of Simple CPU and GPU                                                                                                                                                                                                                                                              | 41 |

| 5.3                                      | Abstract Composition Rules                                                                                                                                                                                                                                                                                    | 43 |

| 5.4 | Example of map Rules in OpenMP                               |     | 44 |

|-----|--------------------------------------------------------------|-----|----|

| 5.5 | Program Composition Rules and Example for Deriving Com-      |     |    |

|     | position Rules                                               |     | 45 |

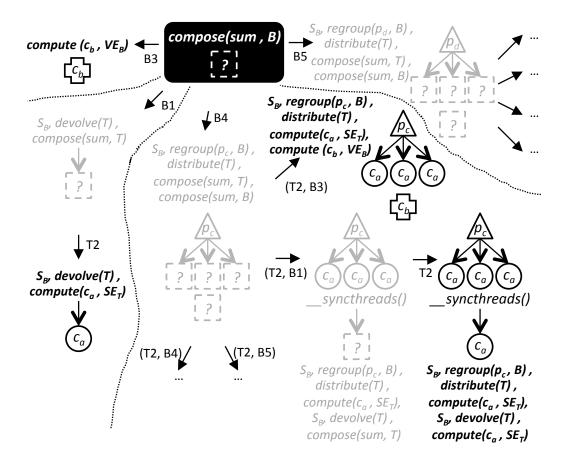

| 5.6 | Rule Specialization and Composition (CPU Example): For       |     |    |

|     | the composition plan diagram on the right side, a triangle   |     |    |

|     | represents distribution of work according to the partition   |     |    |

|     | pattern from the indicated codelet and a circle represents   |     |    |

|     | scalar compute according to the indicated codelet.           | • • | 46 |

| 5.7 | Rule Specialization and Composition (GPU Example): In        |     |    |

|     | addition to the triangles and circles introduced in the pre- |     |    |

|     | vious diagram, a cross represents vector compute according   |     | 10 |

| 5.8 | to the indicated codelet                                     | • • | 48 |

| 5.8 | Four Possible Composition Plans for the Block and Thread     |     |    |

|     | Levels)                                                      |     | 49 |

|     |                                                              | ••• | 10 |

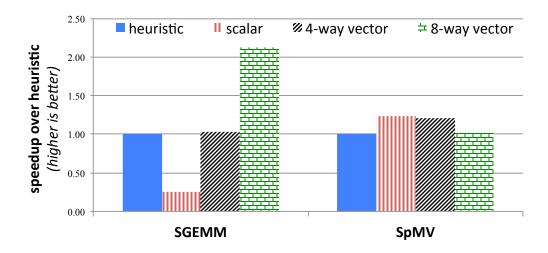

| 6.1 | Performance Impact for Loop Transformations of OpenCL        |     |    |

|     | Compilers on an i7-3820 CPU                                  |     | 53 |

| 6.2 | Performance Impact for Different Vectorization Strategies    |     |    |

|     | of Intel CPU OpenCL                                          |     | 54 |

| 6.3 | TANGRAM Compiler Organization                                |     | 54 |

| 6.4 | Composition Algorithm with Pruning                           |     | 66 |

| 6.5 | Comparing Composition Rules for Pruning                      | • • | 67 |

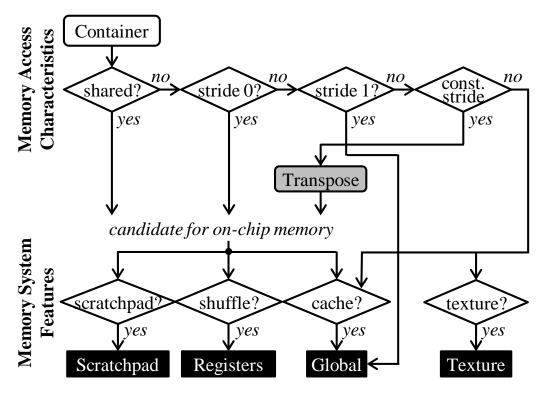

| 7.1 | Heuristic for Data Placement                                 |     | 70 |

| 7.2 | Codegen for CPU Example in Figure 5.6                        |     | 73 |

| 7.3 | Codegen for GPU Example in Figure 5.7                        |     | 74 |

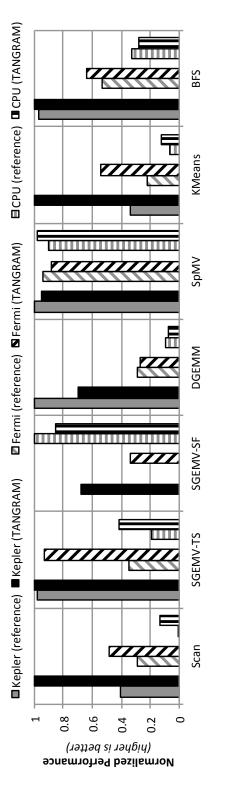

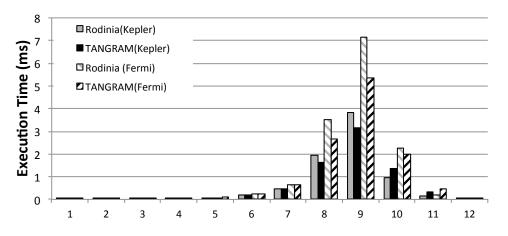

| 8.1 | TANGRAM Performance Results                                  |     | 78 |

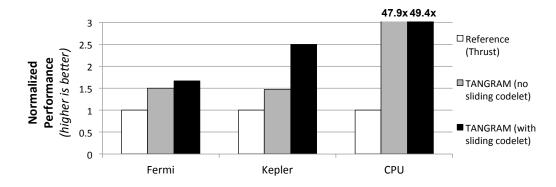

| 8.2 | Scan Results with or without the Sliding Codelet (Normal-    | ••• | 10 |

| 0.1 | ized to the Corresponding Thrust Results)                    |     | 79 |

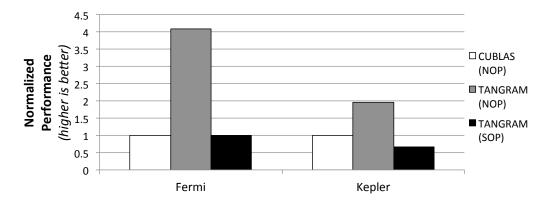

| 8.3 | SOP and NOP SGEMV-SF Results on GPUs (Normalized to          |     |    |

|     | the Corresponding CUBLAS Results)                            |     | 80 |

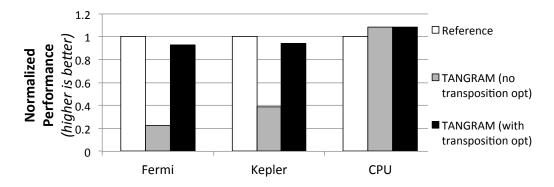

| 8.4 | SpMV Results with and without Transposition Optimization     |     |    |

|     | (Normalized to the Corresponding References)                 |     | 82 |

| 8.5 | BFS GPU Performance Breakdown                                |     | 83 |

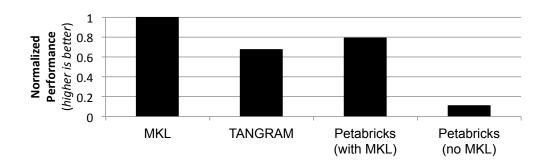

| 8.6 | Comparison between TANGRAM and Petabricks using DGEMM        |     |    |

|     | on CPU                                                       |     | 85 |

# LIST OF ABBREVIATIONS

- AMD Advanced Micro Devices

- AST Abstract Syntax Tree

- AVX Advanced Vector Extension

- BFS Breadth-First Search

- BLAS Basic Linear Algebra Subprograms

- C++AMP C++ Accelerated Massive Parallelism

- CEAN C++ Extension for Array Notation

- CPU Central Processing Unit

- CSR Compressed Sparse Row

- CUBLAS Compute Unified Basic Linear Algebra Subprograms

- CUDA Compute Unified Device Architecture

- CUSPARSE Compute Unified SPARSE Library

- DGEMM Double-precision General Matrix to Matrix Multiplication

- FPGA Field-Programmable Gate Array

- GFLOPS Giga Floating Point Operations Per Second

- GPU Graphics Processing Unit

- I/O Input/Output

- ILP Instruction-Level Parallelism

- IR Intermediate Representation

- JDS Jagged Diagonal Storage

- LL/SC Load-Link/Store-Conditional

- MKL Math Kernel Library

- NESL Nested Data-Parallel Language

- NOI Node of Interest

- NOP Non-Order-Preserving

- OpenACC Open Accelerators

- OpenCL Open Computing Language

- OpenMP Open Multi-Processing

- SF Short-and-Fat

- SGEMM Single-precision General Matrix to Matrix multiplication

- SGEMV Single-precision General Matrix-Vector multiplication

- SIMD Single-Instruction Multiple-Data

- SM Streaming Multiprocessor

- SOP Sequential-Order-Preserving

- SpMV Sparse Matrix-Vector multiplication

- SSE Streaming SIMD Extensions

- STL Standard Template Library

- TS Tall-and-Skinny

# CHAPTER 1 INTRODUCTION

Modern computing systems are transitioning to heterogeneous platforms, integrating many parallel or specialized computing devices, such as multicore CPUs, GPUs, Intel Xeon Phis, DSPs, and FPGA, to meet computational demands and/or energy efficiency requirements of applications. However, to successfully adopt such computing devices, code transformations and optimizations are typically necessary for gaining performance of existing applications. Ideally, programmers should be able to write in a portable language once, and expect the compilers to automatically perform these code transformations and optimizations and deliver high performance. Yet, the current practice entails substantial effort for rewriting entire applications or core algorithms to gain reasonable performance. Furthermore, maintaining multiple source code versions optimized for different devices could be a burden. Therefore, single-source performance portability has become very desirable for the adoption of heterogeneous systems.

## 1.1 Current Practice of Performance Portability

Multiple languages, such as OpenCL [1], C++AMP [2], OpenMP [3], and OpenACC [4], have been proposed as a portable parallel language over multiple variants of computing devices. OpenCL, as the most popular proposal, has received tremendous support from both hardware vendors [5, 6, 7, 8, 9, 10, 11, 12, 13] and software developers [14, 15, 16, 17, 18]. However, as a portable language, OpenCL still delivers limited performance compared to vendor libraries [19].

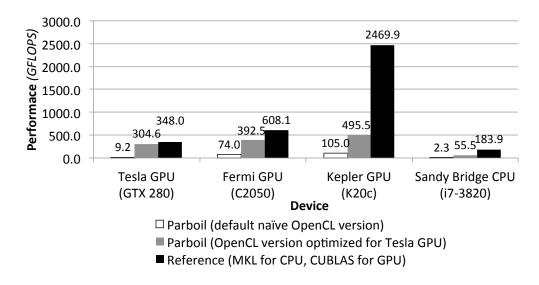

Figure 1.1 shows a quantitative study for performance portability of the current OpenCL stacks by evaluating two versions of Parboil's [20] OpenCL SGEMM benchmark and corresponding vendor libraries on three NVIDIA

Figure 1.1: OpenCL SGEMM Performance Portability Evaluation

GPUs (Tesla, Fermi and Kepler microarchitectures) and an Intel CPU (Sandy Bridge microarchitecture). Three key observations can be made from these results. First and foremost, though the kernel optimized for a Tesla GPU outperforms the naive version not only for a Tesla GPU but also for Fermi and Kepler GPUs and more interestingly the Sandy Bridge CPU, the kernel optimized for a Tesla GPU only achieves 65% and 20% of the CUBLAS library on the Fermi and Kepler GPUs respectively, and 30% of MKL on the Sandy Bridge CPU. This result demonstrates that optimizations of this OpenCL kernel are not always transferable to non-target GPU and CPU, since, compared to highly optimized vendor libraries, the relative performance drops from 87% to 65%, 20% and 30% respectively. Second, the naive version only delivers limited performance, significantly less than the optimized version (for the Tesla GPU) and the corresponding vendor libraries on the tested GPUs and CPU. This result demonstrates optimizations are necessary for gaining performance in OpenCL. Third, the absolute performance of the kernels does indeed benefit from the architectural improvements from Tesla to Fermi, but the achieved percentage of the vendor library performance decreases. This result demonstrates the improved performance from an architectural upgrade is not sufficient evidence for performance portability. Through this evaluation, we demonstrate the limited performance portability of the current OpenCL stacks.

Qualitatively, OpenCL, as a low-level language, requires optimizations ex-

posed by programmers for gaining performance. Without proper optimizations, an OpenCL kernel delivers very limited performance for most devices. This fact can also be observed by comparing the performance between the white and grey bars on the Tesla GPU in Figure 1.1. The fine-grained threadlevel model OpenCL adopts makes performance sensible to target devices, since parallelism becomes the main source of performance scaling. Without carefully crafting work assignment to threads, multi-level tiling, or scheduling of the threads [16, 21, 19], an OpenCL kernel might suffer from huge inefficiency.

On the other hand, optimizations for a specific device are not always transferrable to another device. Also, features specific to the target architecture might not be easily exploited universally. These issues eventually limit performance portability. Ideally, the OpenCL compiler should be able to adapt work assignment to threads, multi-level tiling, or scheduling of the threads for the target device. Unfortunately, techniques for the OpenCL compiler do not yet seem mature enough to deliver reasonable performance portability [19, 22]. Optimizations crafted for the source device are typically coupled together, consequentially obstructing efficient transformation for the target device. A transformed OpenCL kernel typically suffers from huge overhead and inefficiency.

Without architecture-specific customization, performance is limited, while with it, performance portability becomes limited. This dilemma of architectureneutral programing versus architecture-specific customization becomes the major challenge of performance portability in OpenCL.

## 1.2 Challenges of Performance Portable Programming

Performance portability is challenging. In the current practice, even with rewriting, programmers still must understand and exploit a wide set of architectural entities to utilize these devices well, not to mention compilers. Most programs come with certain degrees of device-specific optimizations. That makes the programs hard to be analyzed and/or transformed by compilers and eventually obstructs performance portability.

We further classify the challenges of performance portable programming into two major factors, *compiler* and *programming language*. The compiler factor mainly covers the robustness of optimization in the compiler. For example, most OpenCL compilers [10, 11] focus on loop transformations. The reachability, efficiency and optimality of loop transformations highly impact final performance on a particular device. As mentioned and evaluated in Section 1.1, the OpenCL compilers do not seem robust enough. To the best of our knowledge, even with the most robust OpenCL compiler, there is still a reasonable performance gap between transformed OpenCL code and architecture-specific libraries [19].

On the other hand, the language is mainly about design space. For example, OpenCL forces programmers to express a kernel in a specific, monolithic form. Meanwhile, as a low-level language, it requires most optimizations exposed by programmers for gaining performance. Consequently, the design space of a particular kernel becomes very narrow. In that sense, the optimal design for another device might not be included in the original, narrow space, and that eventually limits performance portability.

In this dissertation, I argue that a new language is required for replacing the current practices of programming systems to achieve practical performance portability. I first demonstrate the limited performance portability of the current practices and argue how conventional optimization techniques get obstructed in these practices. I further identify the main limiting factors of conventional attempts. To overcome this problem, I propose a programming system, called TANGRAM, with a newly-defined high-level language with its corresponding compiler.

### 1.3 Beyond Performance Portability

Although performance portability is crucial in modern applications, there are several other important factors for a programming system.

**Productivity** is a measure of the ease to program an application. Typically, most high-level languages provide abstractions to reduce application complexity to achieve high productivity. Modular programming can deliver high productivity by reusing modules.

**Maintainability** is a measure of the ease to modify code. It typically includes debuggability and incremental improvement. Programs with golden references or test data can have good debuggability. Code reusing for algorithmic improvement and optimizations can deliver incremental improvement.

These factors are not the major foci of this dissertation. Therefore, in the rest of the chapters, we will only briefly discuss these factors, after we introduce the proposed language.

## 1.4 Summary of Contributions

The following list summarizes the contributions of this dissertation.

- I present a thorough discussion of the challenges of performance portability and a comprehensive survey for existing techniques that tackle these challenges and existing languages that attempt to deliver performance portability.

- I demonstrate the limited performance portability of the current practices, and identify the limiting factors.

- I present a programming language that supports specification of architectureneutral computations and composition rules.

- I define a simple hardware abstraction model that can be used to specify different architectures with different hierarchical organizations, and show how this model is used to guide architecture-specific composition rules from the proposed architecture-neutral language.

- I design a generic composition algorithm that can be used to compose architecture-specific kernels based on the abstractions.

- I develop a compiler infrastructure specialized for compositions, and use the infrastructure to implement a holistic kernel synthesis framework that leverages our generic composition algorithm, and couples it with other portability techniques during code generation and optimization, such as data placement and parameterization, to synthesize highly optimized processor-specific kernels.

- I demonstrate that kernels synthesized from the same description achieve 70% performance (in the worst observed case) to multiple times performance compared to vendor hand-tuned data-parallel libraries.

## 1.5 Organization of this Dissertation

The rest of this dissertation is organized as follows. Chapter 2 discusses performance portability challenges and surveys existing corresponding techniques and existing languages. Chapter 3 identifies two major limiting factors (language and compiler) of the current practices and proposes the TAN-GRAM programming system to resolve these factors. Chapter 4 discusses the language factor and details the TANGRAM language. This chapter also compares the existing languages similar to the TANGRAM language. Chapter 5 introduces a hardware abstraction model, and computation rules, and discusses the relationship between them. Chapter 6 discusses the compiler factor, presents a compiler infrastructure, and details the implementation of the TANGRAM compiler. Chapter 7 explains the optimizations and code generation stages in the TANGRAM compiler. Chapter 8 evaluates the proposed programming system against vendor hand-tuned data-parallel libraries. Chapter 9 concludes this dissertation and outlines areas for continued development.

# CHAPTER 2

# SURVEY OF PERFORMANCE PORTABILITY

In this chapter, I first introduce the major challenges of performance portability, and corresponding conventional techniques. Then, I briefly introduce the status of the current portable language.

## 2.1 Performance Portability Challenges and Conventional Techniques

The architectural differences among devices and mismatched optimizations between programs and devices are major sources blocking performance portability. Five major differences, including granularity of hardware thread parallelism, characteristics of the memory subsystem, hierarchical organization of the hardware, size and abundance of resources, and special instructions, are identified. Also, the corresponding conventional techniques and possible obstructions across these differences are discussed in each section.

#### 2.1.1 Granularity of Parallelism

Different devices have different numbers of parallel workers with varying execution resources. For example, multicore CPUs provide a few coarsegrain heavyweight threads, while manycore GPUs provide many fine-grain lightweight threads. Moreover, each CPU thread executes scalar or short vector operations while each GPU thread executes one lane of a long vector operation.

Difference in granularity can be handled portably through over-decomposition and coarsening. Programmers typically describe all the parallelism in applications and leave it for the compiler to decide what to execute in parallel and what to serialize in a single thread (coarsening). OpenCL is one example of a programming interface that enables over-expressing parallelism. OpenCL compilers do varying levels of coarsening depending on the device type. Compilers for most GPUs do minor [23] or no coarsening of work-items. Compilers for CPUs coarsen work-items in each work-group down to a single thread [14, 16, 24, 25, 26, 27]. Higher-level languages [28, 29] also support over-decomposition through mapped functions and perform varying degrees of coarsening depending on the target architecture.

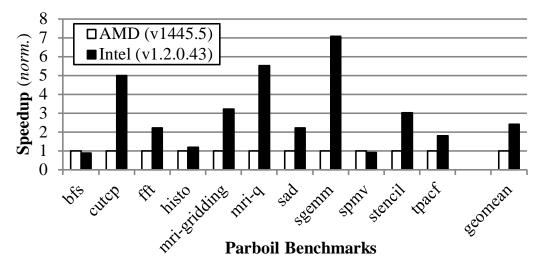

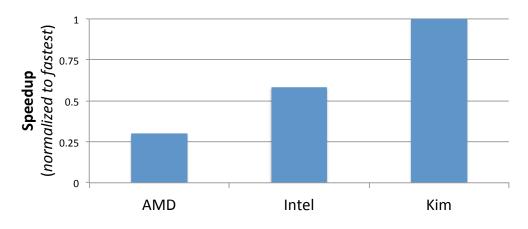

Figure 2.1: Over-decomposition and Coarsening: Performance comparison of AMD and Intel CPU OpenCL stacks on an i7-3820 CPU. AMD results are used as baselines.

There are several design choices of coarsening that might impact its efficiency and overhead. Figure 2.1 compares the performance of AMD's [30] and Intel's [26] CPU OpenCL stacks on an i7-3820 CPU. It is evident that Intel's stack outperforms AMD's. AMD's implementation executes each work-item as a user-level thread, while Intel's coarsens work-items into a single thread. Intel's coarsening enables many optimizations such as collapsing a uniform variable into a single register and vectorizing across multiple work-items. It also reduces thread management overhead and provides more instructions in the same scope for instruction scheduling.

In general, coarsening over-decomposed work can be challenging, because it is not always easy to remove expanded scalars and redundant computations. However, generally automatically coarsening parallel work is still simpler than parallelizing work that is expressed serially [22].

#### 2.1.2 Memory Characteristics

Different types of devices have different memory structures and favor different kinds of locality. For example, CPUs have global memory with private and shared caching, while GPUs - in addition to cached global memory - have scratchpad, read-only, constant, and texture memory. Moreover, CPUs favor intra-thread locality for cache line reuse, whereas GPUs favor inter-thread locality for memory coalescing. Also, in general, CPUs have better temporal locality than GPUs, since the nature of massive multithreading limits lifetime of cache lines on GPUs [31, 32]. Differences in the memory hierarchy also exist across generations of the same device. For example, L1 caches on NVIDIA GPUs were non-existent in the Tesla generation, added in the Fermi generation for caching global memory, and restricted to local memory (register spills, stack data) in the Kepler generation [33].<sup>1</sup>

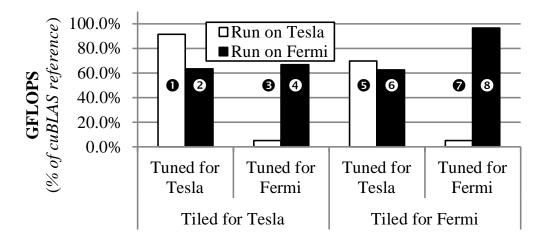

Figure 2.2: Memory Characteristics and Tiling: Performance of SGEMM with different tiling strategies and tuning parameters on different devices. White and black bars are normalized to different references. Performance relative to reference is compared, not absolute performance.

These memory characteristics could highly impact performance of classical optimizations like tiling or other loop transformations. Figure 2.2 shows the performance of SGEMM on different devices using different tiling strategies (e.g., data placement, tile dimensionality, traversal ordering of multidimensional tiles) and tuning parameters (e.g., tile size, work-group size,

<sup>&</sup>lt;sup>1</sup>Some advanced Kepler GPUs allow L1 caching of global memory via a compiler flag, but it is disabled by default.

coarsening factor). The version tiled for Tesla [34] places the first matrix in registers and the second in shared memory, while the version tiled for Fermi [35] places both in shared memory. They also employ different coarsening strategies. While the version tiled and tuned for Tesla and run on Fermi (2) improves when retuned for Fermi (() > 2), it improves much more when the data placement and tiling strategy are also changed (() > 4). The opposite is also true (0 > 4 > 6). This result demonstrates the need for proper tiling strategies and data placement (not just retuning) to achieve good performance. Autotuning is discussed separately in Section 2.1.4..

Many techniques have been developed to achieve portability across different memory subsystems. Different types of memories can be utilized with automatic data placement tools such as PORPLE [36], or with heuristic policies [37]. Satisfying different locality preferences can be done by localityaware scheduling of parallel tasks [16]. Most of these techniques require sophisticated analyses of memory access patterns which could be made easier via built-in data containers [2]. Also, not every memory access is analyzable.

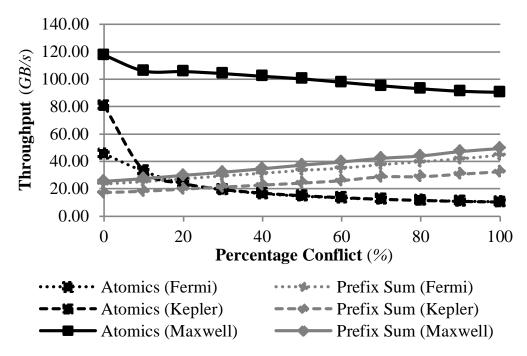

Another example of changes in the memory subsystem is latency of atomics. Scratchpad atomics in Fermi and Kepler GPUs use load-link/storeconditional (LL/SC) instructions, while Maxwell provides faster native instructions for integer scratchpad atomics [38].<sup>2</sup>

These different efficiencies of atomic operations might impact choices of algorithms. Figure 2.3 compares the throughput of stream compaction [39] for two algorithms (with and without atomics) and three different GPU generations. Maxwell's use of native instructions instead of LL/SC significantly improves the algorithm with atomics, causing it to overtake its non-atomics counterpart. Profiling results show that the atomic-based Maxwell version executes significantly fewer instructions than that for Fermi and Kepler. That is because it does not replay instructions until success like LL/SC does. This result further demonstrates the importance of the memory subsystem properties in performance portability. In this case, the difference in atomic latency called for a fundamental change in the optimal algorithm, not just in the placement of data. Algorithm selection is discussed separately in Section 2.1.6.

<sup>&</sup>lt;sup>2</sup>For floating-point scratchpad atomic operations, Maxwell uses ATOMS.CAS.

Figure 2.3: Atomic Efficiencies and Choices of Algorithms: Stream compaction with shared memory atomics versus Thrust prefix sum.

#### 2.1.3 Levels of Hierarchy

Different architectures are laid out with varying levels of hierarchy. A multicore CPU has two levels: the sequential thread and the thread pool where all threads are logically equidistant to each other. A GPU has three levels: the work-items, the work-groups, and the work-group range. Work-items in the same work-group are scheduled closer than work-items in different work-groups, and can share local memory and perform lightweight synchronization.

Programming a hierarchical system requires defining multiple phases of computation for each level of the hierarchy. It might impact algorithmic structures significantly. For example, a CPU reduction typically involves a sequential reduction on each thread followed by a collective operation across threads. On the other hand, a GPU reduction involves a sequential reduction in each work-item from multiple work-groups, a tree-reduction across workitems in the same work-group, and another sequential or tree reduction on the partial sums of each work-group.

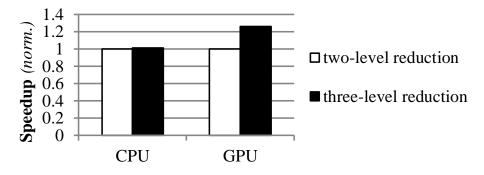

Figure 2.4 compares the performance of two- and three-level reduction implementations on CPU and GPU. The addition of a third level on CPU has little impact on performance because a CPU only has two levels. Thus, adding a third level breaks a sequential loop into two nested sequential loops which has a negligible impact on this benchmark. On the other hand, the GPU benefits significantly from the third level because it is a three-level device. The best two-level version does a tree reduction in the work-groups followed by a reduction of partial sums. The third level adds a sequential reduction in each work-item which improves resource utilization. This result demonstrates the importance of considering the hierarchical division of the device for performance portability.

Figure 2.4: Reduction with Multiple Levels

Adapting a program with more levels of hierarchy to an architecture with fewer levels can be done through collapsing levels and coarsening/serialization. However, the reverse action is extremely challenging. For portability, a programming system should remove from the programmer the burden of managing the hierarchy. An effective solution is to allow the programmer to express all possible nested parallelism [40] through recursive and non-recursive implementations of an algorithm. The system then composes these implementations in different ways depending on the underlying architectural hierarchy. A possible challenge of this technique is that it requires sophisticated analyses, transformations, and more work for programmers in many cases.

Dynamic parallelism [41, 42] is one proposal to achieve nested parallelism for GPUs by relying on programmers expressing nested parallelism through certain interfaces and efficiently computing those parallelism through hardware techniques [43, 44, 45] or compiler transformations [46, 47, 48]. Depending on techniques, performance might vary significantly. Also, the current dynamic parallelism only allows a certain type of nested parallelism, instead of general, native nested parallelism.

#### 2.1.4 Resource Constraints

As technology scales, generations of devices come out with different (often increasing) hardware resource sizes and quantities. The size of a resource impacts the tuning of a program in many ways. For example, the optimal loop-tiling factor is usually dependent on the size of a cache, so a larger cache necessitates re-picking the loop tile size. In a GPU, the maximum occupancy of work-items and work-groups on compute units changes across devices, which impacts the optimal work-group size.

Referring back to the results in Figure 2.2, it is evident that within the same tiling strategy, the tuning parameters have a great impact on performance. For both tiling strategies, different devices have different optimal tuning parameters, thus no size fits all. The Tesla-tuned kernels underutilize the maximum occupancy on Fermi (@ < 4, 6 < 8). On the other hand, the Fermi-tuned kernels perform very badly on Tesla because they demand more resources than actually exist which results in register spilling (3 < 0, 7 < 5).

A common way to deal with variation of resource size is through parameterizing variables that are impacted by the resource size and autotuning those variables at compile time or runtime. Plenty of work has been done on autotuning and search space pruning [49, 50, 51]. However, for a general program, it could be challenging to identify possible variables as parameters, which could be made easier via annotation.

#### 2.1.5 Special Instructions

Some devices provide special instructions to accelerate common computation patterns. These differ across device types and generations. The aforementioned native scratchpad atomics introduced in Maxwell GPUs is an example of such instructions. Other examples include AVX instructions introduced in Sandy Bridge CPUs and shuffle instructions introduced in Kepler GPUs.

One way to handle special instructions is for the compiler to automatically detect common computation patterns and replace them. Some compilers have the ability to detect and replace basic patterns like memory copies, but this approach is not generally applicable due to provability issues. Another approach to handle special instructions is by hiding them behind functions or language constructs that represent common computation patterns. For example, CEAN [52] is a language extension that enables higher-level expression of vector operations and relies on the compiler to generate SSE, AVX, or serial code depending on what is available, feasible, and efficient. Finally, some instructions may enable completely different algorithms, which requires more general approaches discussed in the next subsection.

#### 2.1.6 General Approaches

Each technique listed so far handles a specific category of architectural differences. A more general approach to performance portability is using libraries of basic data structures and algorithms with algorithm and implementation selection. In this approach, the programmer writes the program using basic computational patterns as building blocks. Programming systems [53, 28, 29, 54, 55] then select the implementation of the pattern that best matches the target device. The alternate implementations can be manually or automatically generated and can differ by implementing different algorithms or different combinations of the techniques in this section applied to the same algorithm.

Algorithm selection can vary in power and flexibility. Computation patterns can be built into the compiler, provided by a library, or defined by the user via a special interface. Selecting between algorithms can be done based on static analysis, static profiling, or dynamic profiling. When source code for the implementation is available, it can be inlined and optimized by the compiler.

#### 2.1.7 Summary of Challenges and Techniques

A summary of the concepts in this section can be found in Table 2.1. In the next section, many of these challenges and techniques are discussed in multiple portable languages.

| D:#                        |                           |                           |

|----------------------------|---------------------------|---------------------------|

| Differences                | Specific Techniques       | General Techniques        |

| Granularity of Parallelism | Over-decomposition        |                           |

| Granularity of Faranensin  | and coarsening            |                           |

| Memory Characteristics     | Auto data placement       |                           |

| Memory Characteristics     | Locality-aware scheduling | Basic algorithm libraries |

| Levels of Hierarchy        | Nested parallelism        | Algorithm selection       |

| Resource Constraints       | Autotuning                |                           |

| Special Instructions       | Language abstraction      |                           |

| Special Instructions       | Pattern replacement       |                           |

Table 2.1: Overview of Performance Portability Challenges and Techniques

## 2.2 Current Status of Portable Languages

Multiple languages have been proposed as a portable parallel language over multiple variants of computing devices. Here, only mainstream and generalpurpose languages are discussed in detail, while some noteworthy domainspecific, mobile-platform, or in-progress languages are briefly mentioned in Section 2.2.5.

#### 2.2.1 OpenCL

OpenCL is the most popular portable language. It is a low-level language, and requires most optimizations to be expressed in kernels by programmers for achieving performance on most devices. Although this design might limit performance, there are still several existing techniques incorporated in OpenCL, benefitting performance portability.

OpenCL adopts a fine-grained thread-level programming model, which natively provides the functionality of over-decomposition. Most OpenCL compilers provide some capabilities of coarsening for CPUs, and few or none for GPUs. In terms of techniques for memory, some recent studies [16, 19, 36, 37] incorporated data placement or locality-aware scheduling into OpenCL, while most vendor compilers do not include these techniques. In terms of hierarchy, OpenCL natively provides a fixed three-level hierarchy, which perfectly fits the current GPUs and applies extra coarsening/serialization to adapt CPUs. For programs with more nested parallelism, dynamic parallelism can be applied for GPUs with hardware techniques [43, 44, 45] or compiler transformations [46, 47, 48] to deliver reasonable performance. However, for architectures with more levels of hierarchy, OpenCL might still have limited performance. In terms of techniques for resources, most OpenCL compilers provide no such capability. Recent studies [56, 57] proposed such resource management techniques (in CUDA) for GPUs but required either source code or hardware modification. In terms of special instructions, vendor OpenCL compilers might provide some capabilities for their own SIMD instructions. For common primitives, SyCL [58] introduces group-class primitives to bridge performance gaps across OpenCL devices, but it is still in progress. In algorithm selection, OpenCL adopts monolithic expression for kernels, which might limit such support.

As mentioned, OpenCL, as the most popular portable language, has received tremendous hardware and software support. However, as shown in Figure 1.1, the performance portability OpenCL can deliver is still limited. The key reason is that the fixed three-level hierarchy in OpenCL is too GPUoriented. That might drive entire codebase design biased to GPUs, and eventually limits performance portability to other devices.

#### 2.2.2 C++AMP

C++AMP is a language designed to support data-parallel computation in accelerators, like GPUs, in C++. It relies on concurrency APIs, such as parallel\_for\_each, to label data-parallel code regions, and another keyword restrict to specify a region (or a function) to the device where it executes. Different from OpenCL, C++AMP provides a monolithic interface unifying host and device code. Also, C++AMP provides an implicit interface for memory space.

For a data-parallel region, C++AMP adopts fine-grained thread-level programming model through lambda expressions. Therefore, it natively provides the functionality of over-decomposition. Similar to OpenCL, its compilers typically provide some capabilities of coarsening for CPUs, and few or none for GPUs. In terms of techniques for memory, C++AMP relies built-in containers, such as array\_view and index, and tiling APIs to provide hints for data placement. One exception is texture, which requires an explicit keyword. In terms of hierarchy, C++AMP relies on parallel\_for\_each, which natively implies a two-level hierarchy. The keyword parallel\_for\_each implies independent tasks, which potentially can be scheduled freely in a multilevel hierarchy. Meanwhile, the built-in tiling APIs can further extend its support to three-level devices, such as GPUs. However, since the performance of C++AMP programs seems sensitive to tiling for GPUs, that implies code written for GPUs requires serialization/coarsening for CPUs. It also implies possible performance issues for architectures with more levels of hierarchy. C++AMP compilers do not have its own techniques for resource management. For special instructions, C++AMP might have a limited support, due to no direct support from hardware vendors. Some C++AMP compilers with source-to-source translation could take advantage of backend compilers. Finally, so far, there is no direct support in common primitives or algorithm selection.

In general, C++AMP provides higher-level language features than OpenCL, and can potentially deliver better performance portability. Similar to OpenCL, its main limiting factor is still the support for hierarchy. Different from OpenCL, codebase of C++AMP might not be entirely biased to GPUs. However, code written by programmers still requires explicit optimizations (mainly through tiling) for gaining performance of either CPUs or GPUs. This coding behavior eventually limits performance portability.

#### 2.2.3 OpenMP

OpenMP is a language originally designed for CPU multithreading, and it gets extended for GPUs and other architectures. OpenMP relies on pragmas to annotate code regions for parallelism. Here data parallelism is mainly discussed.

For a data-parallel region, a fine-grained thread-level model is also used. Coarsening can be further controlled through schedule annotation. In terms of techniques for memory, OpenMP relies on sophisticated analyses with help of data-sharing attribute clauses, such as shared. In terms of hierarchy, OpenMP natively supports a two-level of hierarchy, threads and a range of threads. With the newly introduced teams construct, one extra level can be added for GPUs. In terms of resources, OpenMP provides some degree of flexibility for the number of threads (and the size of teams); the runtime or compiler can determine these sizes. For special instructions, OpenMP might have some degree of supports from hardware vendors. Finally, so far, there is no direct support in common primitives or algorithm selection.

Commonly, the performance of an OpenMP program is very sensitive to its annotation. In order to get good performance, different sets of annotations are required for different devices, or a single set of annotations with different conditions. In the end, no true performance portability is achieved in OpenMP.

#### 2.2.4 OpenACC

OpenACC is a language designed for data-parallel computation in accelerators using annotation like OpenMP. It also uses pragmas to annotate code regions for data parallelism. In terms of discussion related to performance portability, OpenACC is very similar to OpenMP. Compared to OpenMP, OpenACC provides more detailed annotation for loops and data placement. Meanwhile, OpenACC typically has better support in (NVIDIA) GPUs. OpenACC also has limitations similar to those of OpenMP, though it provides better performance.

#### 2.2.5 Other Languages

Here, multiple noteworthy domain-specific, mobile-platform, or in-progress languages are briefly covered. Only main techniques and possible limitation are discussed for each language. Composition-based languages, such as NESL [40], Sequoia [59] and Petabricks [55], are discussed in Chapter 4.

Halide [60] is a domain-specific language in C++ for digital image processing. It adopts most existing techniques discussed in Section 2.1, such as coarsening, auto data placement, locality-aware scheduling, autotuning, and pattern replacement. Particularly for levels of hierarchy, most image processing algorithms have huge independent tasks, which can be arbitrarily scheduled and fitted in a multi-level hierarchy. Though Halide does not provide any functionality of common algorithm library or algorithm selection, its huge number of scheduling choices already provide huge design space for performance portability. Finally, Halide heavily relies on autotuning for selecting the best design.

Surge [28, 29] is a language in C++ for tunable bested data parallelism. It

strongly relies on collective primitives. Each primitive has multiple *schedules* for different levels of hierarchy and tunable parameters. Although general algorithm selection is not applicable in Surge, each built-in primitive could support algorithm selection in its own, Surge applies autotuning (through a machine learning strategy) for selecting the best design.

Parallel Standard Template Library (Parallel STL) [61] is an inprogress built-in library in C++17. It provides a set of parallel templates, which are potentially performance portable across devices. Similar to Surge, each template could have multiple implementations for different levels of hierarchy and tunable parameters. Potentially, compilers could fuse these templates properly and autotuners can select the best design.

**RenderScript** [62] is a mobile-platform language for Android systems. Compared to OpenCL, which might support some mobile devices, Render-Script typically provides better performance for mobile platform. Although RenderScript provides single-source portability with better performance than OpenCL, RenderScript does not support device selection for programmers. It is clear RenderScript can deliver reasonable degrees of performance portability, but it is difficult to measure its performance portability.

RenderScript does not provide details of its optimization techniques. Since its script (similar to a kernel in OpenCL) is expressed in a fine-grained threadlevel model, coarsening most likely is applied. In order to utilize mobile GPUs efficiently, some techniques for memory management could exist.

#### 2.2.6 Summary of Languages and Techniques

A summary of the major languages in this section can be found in Table 2.2. In the next few chapters, I discuss how TANGRAM integrates many of these techniques into a single framework, enables them with language extensions, and manages interactions among them.

Table 2.2: Overview of Languages and Techniques

| Types of Techniques        | OpenCL      | C++AMP | OpenMP | OpenACC |

|----------------------------|-------------|--------|--------|---------|

| Granularity of Parallelism | 1           | 1      | 1      | 1       |

| Memory Characteristics     | $\triangle$ | 1      | 1      | 1       |

| Levels of Hierarchy        | †           |        |        |         |

| Resource Constraints       | *           |        | **     | **      |

| Special Instructions       | \$          | \$     | \$     | \$      |

| Basic algorithm libraries  | 1           |        | 2      | 2       |

| Algorithm selection        |             |        |        |         |

✓ Support. <sup>△</sup>Through third-party techniques.

<sup>†</sup>Through coarsening and dynamic parallelism with third-party techniques.

\*Only for work-item sizes. \*\*Only for threads.

$^\circ\mathrm{It}$  depends on the compiler.  $^1\mathrm{Through}$  SyCL.  $^2\mathrm{Only}$  for reduction pragma.

## CHAPTER 3

# TANGRAM OVERVIEW

In the previous chapter, multiple challenges, existing techniques, and status of current portable languages were discussed. In this chapter, impact of the above is discussed, in terms of programmers' problems-solving processes. Further, that process leads to the design of the TANGRAM programming system, and how TANGRAM integrates many existing techniques into a single framework, enabling them with language extensions, and managing interactions among them.

## 3.1 Conventional Problem-solving Process

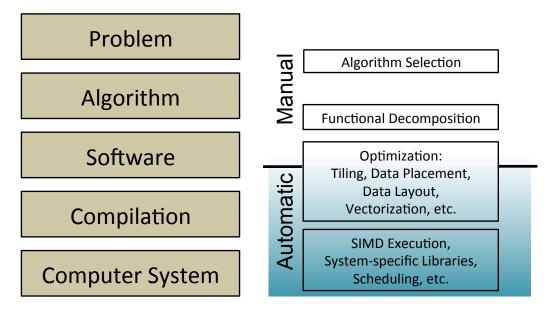

A typical process for solving a real-world problem on a computing system requires multiple steps. Figure 3.1 summarizes such steps and translates them into levels of abstraction and corresponding tasks for solving real-world problems on computing systems [22]. A problem typically can be translated to a set of reasonable algorithms by domain specialists. Given a computer system, the problem can be further mapped into one or a few specific algorithms through particular algorithmic consideration, such as their algorithmic complexity or corresponding efficiencies on the target system. Then, the algorithm can be translated into a piece of software containing one or multiple computing functions or kernels. Each of these functions or kernels in software could involve multiple optimizations, which could be performed manually by programmers or automatically by a compiler. A boundary between manual and automatic tasks typically happens between the software and compilation levels. Depending on the programming language and the compiler, manual or automatic optimizations could vary. After compilation, the software can execute in a particular computer system.

In general, the computer systems might impact the compiler optimizations,

Figure 3.1: Conventional Problem-Solving Abstraction Hierarchy and Corresponding Tasks: At left are levels of abstraction translating a problem into a computational solution. At right are tasks associated with their level of abstraction where they are typically addressed, and a typical boundary between manual and automatic tasks.

the code expression (including manual optimizations) in software, and even the choices of algorithms. The compiler optimizations are highly related to performance portability [22]. Given a precise algorithm, the code expression is also highly related to the language and the compiler, since coding typically requires the interaction between the programmer and the compiler. As discussed in the previous chapter, different portable languages with corresponding compilers might deliver different code expression, leading to various degrees of performance portability. This kind of differences is also a common consideration for programmers' choices of programming languages.

Compared to the former two, the choices of algorithms are typically related to the programmers' understanding of the computer systems, and/or the programmers' consideration for performance portability. For example, given a single-core sequential system, there is no reason for a skilled programmer selecting a parallel algorithm with possibly higher overheads over a sequential algorithm, unless he/she expects this program will be ported to another parallel system. After all, eliminating overheads of a parallel algorithm executing on the single-core sequential system is not trivial.

## 3.2 Design Space and Performance Portability

The problem-solving process in Figure 3.1 can be considered as a narrowing process of a design space. When algorithms are selected by the programmer, the design space is limited to one particular set. When a particular algorithm is coded in a language, its design space gets narrowed down. When manual optimizations are introduced, the design space shrinks further. Compilation and then execution for a computer system eventually reduce the design space into one specific design point.

Given a problem and corresponding written code in a particular language, a design space S is defined as a set of all possible transformed versions. Since code transformations happen in compilers, and different compilers could deliver different code transformations, the design space becomes a function of a compiler. In order to rule out the effect of compilers in this analysis, we can redefine a design space S as a set of all possible transformed versions *among all possible compilers*. We can also define  $S_X$  as the design space for the code written for the computer system X, and  $S_U$  as the universal set of design space for all possible machines. Then, we further define  $P_{X|S}$  as the best version in the design space S with a particular kind of performance measurement M, assuming the higher is the better, on the computer system X:

$$P_{X|S} = \operatorname*{arg\,max}_{p \in S} M_X(p),$$

and  $P_X$  as the optimal point in the  $S_U$ :

$$P_X = P_{X|S_U}$$

By the definition,  $P_X$  can deliver performance better than or equal to  $P_{X|S_X}$ on the system X:

$$M_X(P_X) \ge M_X(P_{X|S_X}) \ge M_X(P'_{X|S_X}),$$

where  $P'_{X|S_X}$  is defined as the final selected version. Since  $S_X$  represents the code written for the system X,  $M_X(P_{X|S_X})$  should be reasonably close to  $M_X(P_X)$ , and  $M_X(P'_{X|S_X})$  should be also very close to  $M_X(P_{X|S_X})$ , if the programmer performs the problem-solving process properly.

When the code with the design space S (regardless it is written for X) is

ported to another system Y,  $P_{Y|S}$  can be considered as the best version the system can achieve:

$$M_Y(P_{Y|S}) \ge M_Y(P_{X|S}).$$

Also,  $P'_{Y|S}$  can be defined as the selected transformed version:

$$M_Y(P_{Y|S}) \ge M_Y(P'_{Y|S}).$$

Typically, if transformations are profitable, we should follow:

$$M_Y(P'_{Y|S}) \ge M_Y(P'_{X|S}).$$

By the definition,  $P_Y$  performs better than  $P_{Y|S}$  on Y:

$$M_Y(P_Y) \ge M_Y(P_{Y|S}).$$

Here, we further define (absolute) performance portability (from X) to Y as follows:

$$Perf_Port_Y(S) = M_Y(P'_{Y|S})/M_Y(P_Y) \le 1.$$

It has an upper bound:

$$Perf_Port_Bound_Y(S) = M_Y(P_{Y|S})/M_Y(P_Y) \le 1$$

In general,  $P_Y$  might not be in S, so performance portability could not get close to 1.

Note X are not involved in the above two equations. Here, the design space S is determined by the written source code, and our definition of performance portability is only based on the design space S, not the machine X. However, since the source code is written for the machine X, its design space S should be highly biased to the machine X. This bias becomes the major limiting source for performance portability

Depending on the difference between  $P'_{Y|S}$  and  $P_{Y|S}$  and whether  $P_Y$  is in the design space S, performance portability could vary. The former implies the code transformation from the compiler, while the latter comes from the design space, which is highly related to either the written code or even the programming language. It is obvious the code defines the design space. On the other hand, the impact of the language is not that straightforward. Given a mainstream portable programming languages, such as OpenCL or OpenMP, the programmers might not easily express all of the algorithmic consideration for all various devices. A classic example is that code written in an older version of OpenMP, which only considers two levels of hierarchy for multicore CPUs, cannot perform well on manycore GPUs, without introducing a new teams features for three levels of hierarchy. Even with the newest OpenMP or OpenCL, a possible device with four levels of hierarchy could fail to exhibit performance portability.

Figure 3.2 summarizes the relationships among these design points and the design space S. Here,  $P_Y$  is the optimal point users desire, while  $P'_{Y|S}$  is really the final transformed version. The performance difference between  $P'_{Y|S}$  and  $P_Y$  reflects performance portability for the system Y. In this illustration,  $P_Y$  is not achievable, since it is out of the design space S. Without expanding the design space, the gap between  $P'_{Y|S}$  and  $P_Y$  cannot be completely removed. On the other hand,  $P_{Y|S}$  represents the best version in the design space S. The difference between  $P'_{Y|S}$  and  $P_{Y|S}$  (and also between  $P'_{X|S}$  and  $P_{X|S}$ ) implies the capability of a compiler for performance optimizations. This gap can be removed by improving the compiler.

Figure 3.2: Illustration of Relationships among Different Design Points

The **coverage** of a design space is defined as the *cardinality* (or size) of the given design space S over that of the universal design space U:

$$Coverage(S) = |S|/|U|.$$

Here the cardinality of design space is defined as the cardinality of trans-

formed versions from a single codebase in the given programming language. Multiple programming systems [53, 28, 29, 54, 55], as discussed in the previous chapter, provide some degree of support for improving the coverage of an algorithmic design space to bridge possible performance gaps. In order to expand the algorithmic design space, most of them rely on either fixed, implicit functional compositions with built-in libraries, primitives, or specific rules in a domain, or flexible, explicit compositions with new language features. These features inspire me to design a programming system, including defining a new programming language, to natively support effective expression of an algorithmic design space.

## 3.3 TANGRAM Programming System

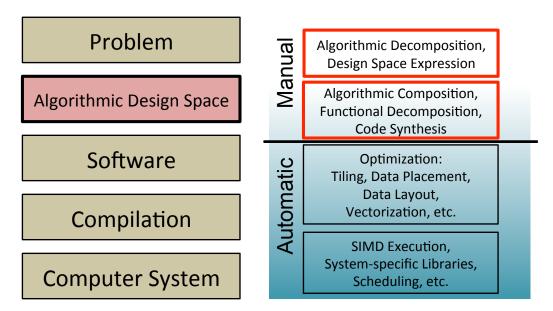

Figure 3.3: TANGRAM's Problem-Solving Abstraction Hierarchy and Corresponding Tasks: Red, bold-line boxes are different parts from the conventional one.

I present TANGRAM, a kernel synthesis framework that generates highly optimized architecture-specific kernels. TANGRAM is designed to achieve performance portability through the following methods:

1. a modular, composition-based programming language that can effectively express a design space with high coverage of implementations 2. a compiler that can effectively explore the design space and facilitate many high-level optimization techniques, described in Section 2.1

In the TANGRAM system, programmers directly express algorithmic design space by writing the proposed high-level language (the TANGRAM language). The language is designed for effective expression of design space through algorithmic decomposition by programmers with the domain knowledge. The TANGRAM compiler then performs design space exploration to select a proper algorithmic structure and implementation, and synthesizes the software with proper high-level optimizations.

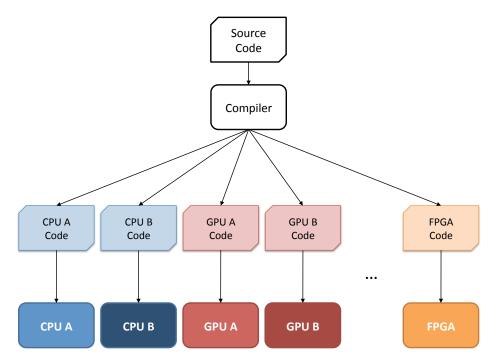

Figure 3.4: Big Picture of TANGRAM for Various Devices

It is not trivial to introduce native support for effective expression of design space. It might change the problem-solving process in Figure 3.1. Figure 3.3 shows the refined version of problem-solving abstraction for TANGRAM. Different from the conventional levels of abstraction, a level of algorithmic design space is introduced to replace conventional level of algorithm. Instead of manually choosing the proper algorithms for a given computer system, programmers express the generic algorithmic design space and rely on the TANGRAM compiler to guide selection for the proper algorithms. Depending on target devices, different output languages/programming models could be used in the level of software, and corresponding backend compilers in the level of compilation are applied for low-level optimizations.

We argue our refined problem-solving abstraction does not increase complexity for solving a problem compared to the conventional abstraction. In the conventional problem-solving abstraction, programmers are still required to consider algorithmic alternatives in their mind and then make a choice before the software stage. The refined abstraction simply requires programmers to encode their consideration in a certain language.

Figure 3.4 illustrates the big picture of TANGRAM's workflow for various devices. A single copy of input source code written in the TANGRAM language defines the design space for a computation pattern in a given application. Given a device, the TANGRAM compiler further explores the design space and synthesizes one or few kernels. Input source code of the TANGRAM system natively presents a design space, instead of a specific code expression for a machine in conventional programming systems. This strategy potentially can deliver better performance portability.

Figure 3.5: TANGRAM's Workflow

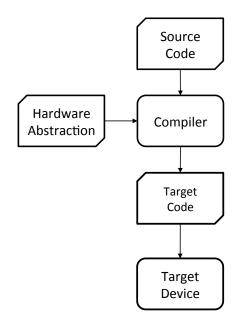

Figure 3.5 zooms in and shows the workflow for each device. In the TAN-GRAM's system, source code is written in TANGRAM language, which will be defined in Chapter 4. Additionally to input source code, *hardware ab-straction* is given to the compiler for "understanding" the device, and further

guiding design space exploration. In TANGRAM, hardware abstraction encodes information of architectural hierarchy. It is based on a key observation that the algorithmic structure of a program is highly sensitive to the architectural hierarchy of a device. Each device typically has its own hardware abstraction. The detailed discussion is given in Chapter 5. Most key mechanisms of the TANGRAM system are discussed in the next two chapters. Finally, the TANGRAM compiler is discussed in Chapters 6 and 7. Different from Chapters 4 and 5, which focus on the design and theory, Chapters 6 and 7 cover the implementation details.

### 3.3.1 Focus of TANGRAM System

The TANGRAM system focuses on language and compiler support for performance portability, and relies on a user-defined design space and hardware abstraction to guide code generation for a highly optimized version. However, in general, given an application and an architecture, the optimal version could depend on runtime information, such as input data distribution, data sizes, resources consumed by co-running applications, or memory which are not accessible statically. Our previous work, DySel [63], is proposed to resolve the above issue by dynamically sampling the performance metrics and then switching versions. Multiple runtime-based approaches [36, 64, 65, 66, 67, 68] also provide the similar functionality to migrate the issue through either performance models or online learning. Although TANGRAM itself does not include runtime, it can work with every existing method, including DySel. Even with a robust runtime that provides lightweight performance monitoring and version switching, a programming system still requires language and compiler support to effectively generate highly optimized versions for switching. TANGRAM is proposed to serve that purpose.

# CHAPTER 4

# TANGRAM LANGUAGE

In the previous chapters, the relationship between a design space and its performance portability was discussed. The discussion also briefly included the possible impact from the existing language. In this chapter, the detailed relationship between design space and language design is discussed. The design of the TANGRAM language is further defined for effective expression of a design space with high coverage to support performance portability.

# 4.1 Design Space and Language

In terms of the design space, there are two important factors, **coverage** and **ease of expression**, for a programming language. As mentioned in Section 3.2, the coverage of a design space is defined as the cardinality of transformed versions from a single codebase in the given programming language. Given a language, code might be written in multiple ways, which might deliver different degrees of coverage. In order to define the coverage factor of a language L, the *limit superior* (or upper bound) is applied. That implies Coverage(L) is defined as the *best Coverage*(S) among all possible single-source code written for a particular application.

On the other hand, the **ease of expression** factor typically implies lines of code for expressing a given design space. In mathematics, a space is defined as a set. Here, a design space can be considered as a countable set, which can be either expressed through listing all of its elements or constructed through rules. A systematic construction is highly important for effective expression for a design space. For example, linear combination is used to effectively construct a linear span (which is a vector space) of vectors in another vector

Parts of this chapter appeared in the International Symposium on Microarchitecture [69]. The material is used with permission.

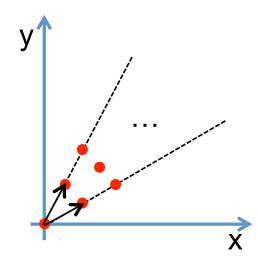

space. Figure 4.1 shows an example of linear combination to construct a set containing positive integer pairs (red dots) in 2D Cartesian coordinate system. The set can be expressed by listing all possible points:

$$S = \{(0,0), (2,1), (1,2), (4,2), (3,3), (2,4), \ldots\}.$$

Alternatively, the set can be also expressed by linear combination:

$$S = \{v | v = a * (2, 1) + b * (1, 2), where a, b \in N_0\}$$

Considering this set contains infinite elements, that makes the second method more effective. Similar to this example, in most situations, a design space may contain infinite design elements, making listing impossible, so it requires a set of compositions to effectively express a space.

Figure 4.1: Example of Linear Combination

#### 4.1.1 Composition-based Language

Similar to linear combination, composition-based languages [40, 59, 55] or libraries [50, 70] are widely applied to effectively express a program through *modules*. Typically, *modules* are defined through *decomposing* a program to patterns and identifying the reusable ones. Functions or kernels within a program can be composed by combining proper modules. Multiple composition-based methods enable *functional polymorphism*, which support different implementations or algorithms in the same module. In functional polymorphism, the invoked version can be determined by the programmer, the compiler, the autotuner, or the runtime. Most automatic methods can deliver effective expression with reasonable coverage for the design space of a given single-source codebase.

Compared to listing all possible design elements, composition-based languages generally require an extra step to combine modules. Depending on the method determining the invoked version, it could increase the complexity of compilation, profiling, or runtime. Also, this step could introduce potential overheads, degrading reachable performance.

TANGRAM adopts composition-based languages, and applies compilerbased methods to determine invoked modules, and further inlines modules to reduce the invocation overhead. Multiple language features are introduced to improve coverage of design space over existing languages and the capability of the compiler to facilitate both compile-time composition and optimizations.

# 4.2 TANGRAM Language Design Objectives