# TOWARD HIGH-EFFICIENCY HIGH POWER DENSITY SINGLE-PHASE DC-AC AND AC-DC POWER CONVERSION — ARCHITECTURE, TOPOLOGY AND CONTROL

#### BY

#### SHIBIN QIN

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2017

#### Urbana, Illinois

#### Doctoral Committee:

Assistant Professor Robert C. N. Pilawa-Podgurski, Chair

Professor Philip T. Krein

Associate Professor Kiruba Sivasubramaniam Haran

Associate Professor Pavan Kumar Hanumolu

## ABSTRACT

Power conversion between the single-phase AC grid and DC sources or loads plays an indispensable role in modern electrical energy system for both generation and consumption. The renewable resources and electrical energy storage are integrated to the grid through inverters. Telecoms, data centers and the rest of the digital world is powered by the grid through rectifiers. Existing and emerging applications all demand the DC-AC and AC-DC systems to be not only more efficient to reduce energy consumption, but also more compact to reduce cost and improve portability. Therefore, new AC-DC and DC-AC converter designs that improve the efficiency and power density of the system is a critical area of research and is the focus of this dissertation.

The recent development of wide band-gap devices stimulates a new round of improvement on efficiency and power density of AC-DC converters. However, despite the new transistors used, the fundamental system architecture and topology remain relatively unchanged, which is becoming the bottleneck for further improvement.

This dissertation explores new architecture, topology and control to overcome this bottleneck, targeting an order-of-magnitude improvement on power density and comparable efficiency to the conventional design. The proposed solutions build on two key innovations: the series-stacked buffer architecture for twice-line-frequency power pulsation decoupling in single-phase AC-DC and DC-AC conversion, and the flying capacitor multilevel topology for power transfer and waveform conversion between AC and DC. This work provides complete solutions for these ideas, including the theoretical development, design procedure, control method, hardware implementation and experimental characterization.

To Mengyao

## ACKNOWLEDGMENTS

It has been five amazing years since I came to Illinois (how time flies). When I reflect back on my time here, what I appreciate the most are the people that I have the privilege of knowing.

I would like to thank my advisor, Professor Robert Pilawa-Podgurski, who brought me to Illinois and helped me thrive here. He is the coolest boss a graduate student could wish for. He is nice and caring to his students, while he has the ability to really encourage and inspire us to work hard and achieve our full potential. Five year ago, I was a complete novice in power electronics; now I feel like a really engineer ready to solve challenging problems. My research work in the past five years is not possible without his vision and support, and I am grateful for all the things he taught me — power electronics and much more.

I would like to thank Professor Philip Krein, Professor Kiruba Haran and Professor Pavan Hanumolu for serving on my doctoral committee, providing insightful suggestions and comments and sharing their knowledge. I would also like to thank other professors from the power group, especially Professor Alejandro Dominguez-Garcia who helped me a lot with my earlier DPP work and Professor George Gross, who, as I just learned days ago, made my admission to Illinois possible in the first place by bringing Professor Pilawa-Podgurski's attention to my application.

I want to thank my fellow members of the "Pilawa-group", past and present, for the camaraderie and all the fun. Thank you to Dr. Yutian Lei, my colleague and good roomie, photographer of my marriage ceremony, witness of my successful and unsuccessful experiments in the lab — he was there for many important moments in my life in the past five years. Heartfelt gratitude to Enver Candan, Chris Barth, Pourya Assem, Joseph Liu, Zichao Ye, Zitao Liao, Andrew Stillwell, Derek Chou, Thomas Foulkes, Yizhe Zhang, Nathan Brooks, Nathan Pallo, Pei Han Ng, Dr. Modeer and many more. Thank you to all my colleagues in the power group. I enjoyed learning, working and laughing with you, and it would not be the same five years without all of you.

I would like to thank my parents, who taught me the most important lessons in my life. They always trust me and support me in all my decisions. They are always there to listen. Living so far away from home has not been easy for either them or me. I wish I could have gone home more often; now I certain will.

Most of all, I want to thank my wife, Mengyao. We just got married this year, which is my biggest accomplishment and happiest moment. Pursuing a PhD is not easy, cheering me on throughout the journey is just as hard. I am always grateful for her love and support, and I cannot wait to begin a new chapter of life with her.

# TABLE OF CONTENTS

| LIST C | OF ABBREVIATIONS                                       | ⁄iii |

|--------|--------------------------------------------------------|------|

| CHAPT  | ΓER 1 INTRODUCTION                                     | 1    |

| 1.1    | Single-phase AC-DC and DC-AC power conversion          | 1    |

| 1.2    | Research scope and goal                                | 3    |

| 1.3    | Research contribution                                  | 5    |

| 1.4    | Organization of this dissertation                      | 6    |

| CHAPT  | ΓER 2 ENERGY BUFFER BACKGROUND                         | 8    |

| 2.1    | Energy storage in single-phase AC-DC converter         | 8    |

| 2.2    | Energy density of storage elements                     | 9    |

| 2.3    |                                                        | 10   |

| 2.4    |                                                        | 12   |

| CHAPT  | ΓER 3 REVIEW OF ACTIVE ENERGY BUFFER                   | 15   |

| 3.1    | Overview                                               | 15   |

| 3.2    | Buffer cell concept                                    | 17   |

| 3.3    | Parallel-connected cell                                | 20   |

| 3.4    | Stacked switched-capacitor cell                        | 32   |

| 3.5    | Series-connected cell                                  | 36   |

| 3.6    |                                                        | 38   |

| CHAPT  | ΓER 4 OPERATION PRINCIPLE OF THE SERIES-STACKED BUFFER |      |

| ARO    | CHITECTURE                                             | 42   |

| 4.1    | Analysis of operation                                  | 42   |

| 4.2    | Numerical example                                      | 47   |

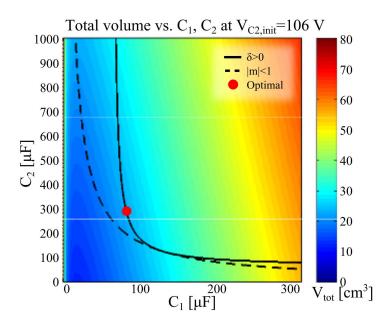

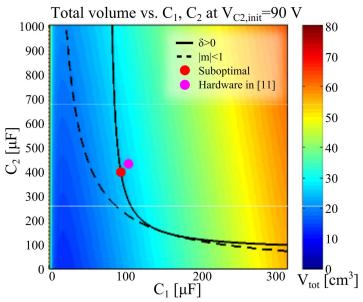

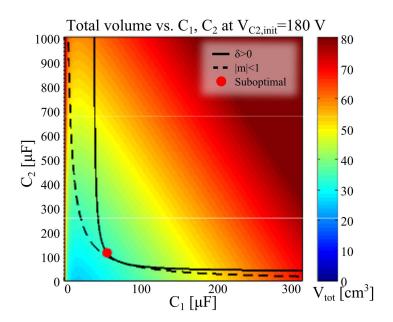

| 4.3    | Design constraints                                     | 48   |

| 4.4    | Optimal sizing                                         | 50   |

| CHAPT  | ΓER 5 CONTROL AND CAPACITOR VOLTAGE BALANCING          | 56   |

| 5.1    | Buffer current control                                 | 56   |

| 5.2    | Capacitor $C_1$ voltage balancing                      | 57   |

| 5.3    | -                                                      | 58   |

| 5.4    | -                                                      | 63   |

| 5.5    |                                                        | 65   |

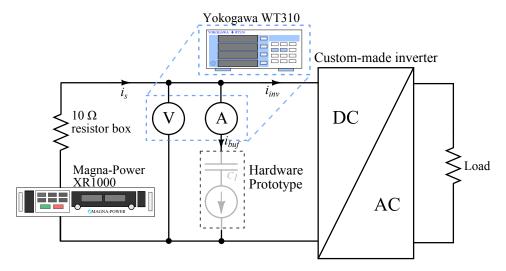

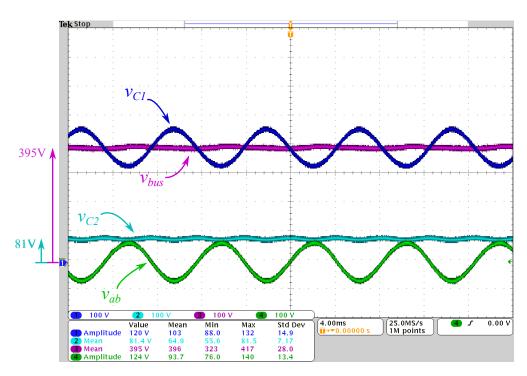

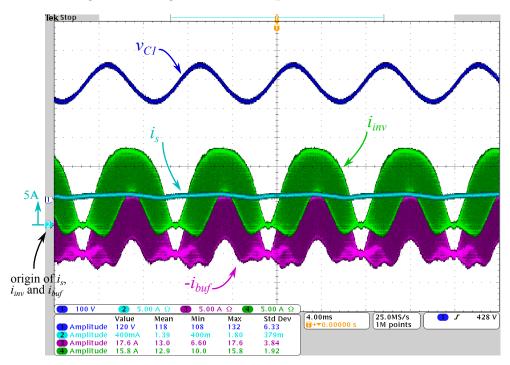

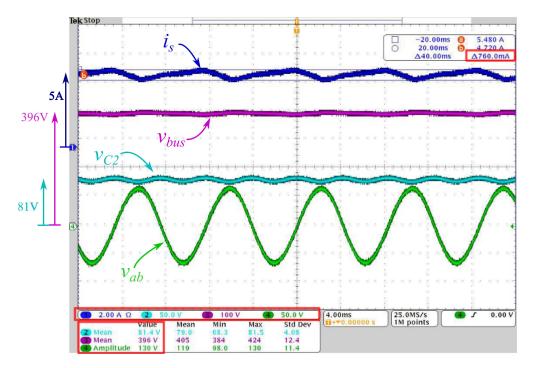

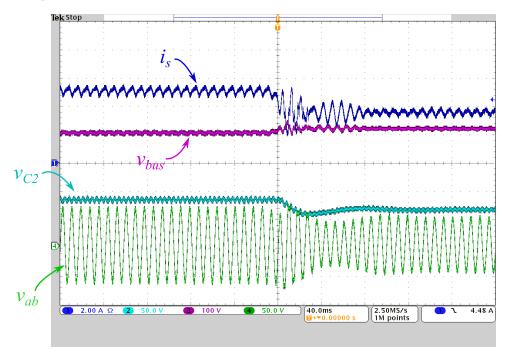

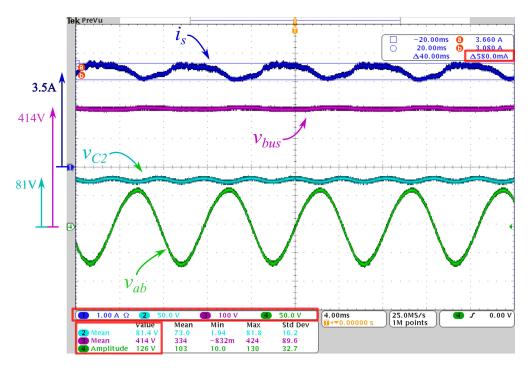

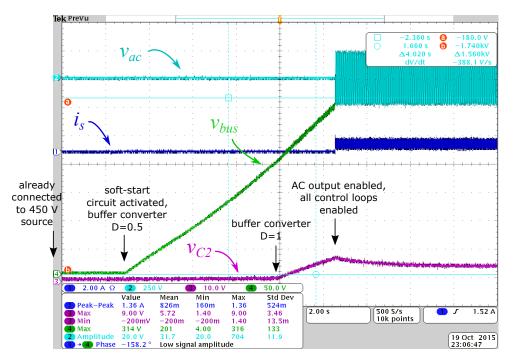

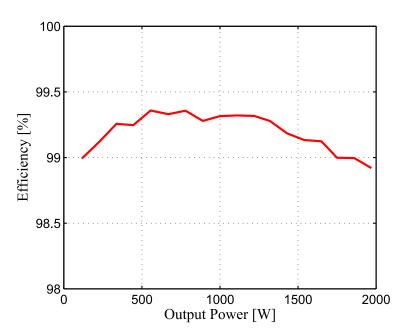

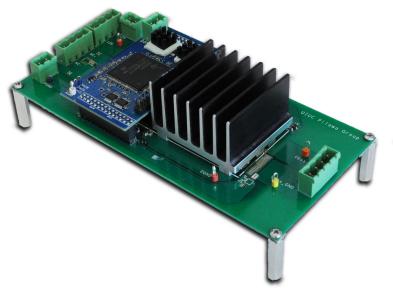

| CHAPTER 6 SERIES-STACKED BUFFER HARDWARE PROTOTYPE AND EXPERIMENTAL RESULTS | . 67<br>. 69<br>. 69                                              |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------|

| 6.5 Comparison to literature                                                |                                                                   |

| CHAPTER 7 REVIEW OF FLYING CAPACITOR MULTILEVEL TOPOLOGY 7.1 Motivation     | . 85<br>. 86                                                      |

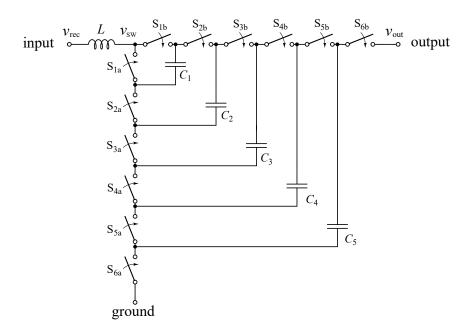

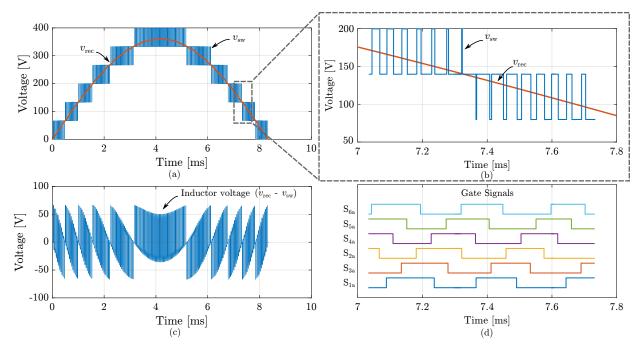

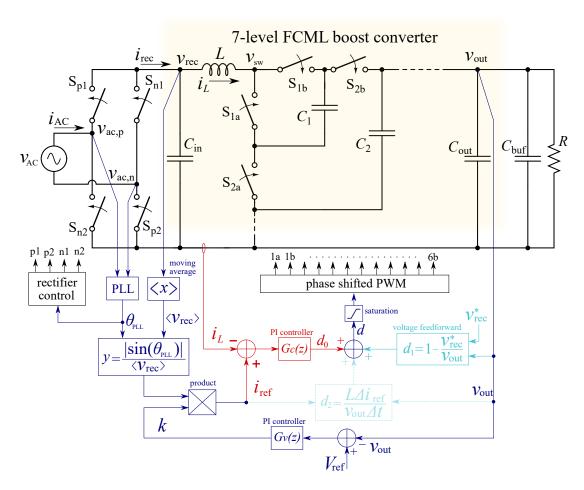

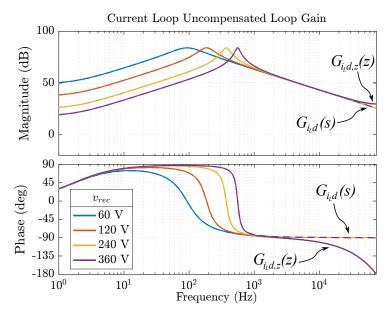

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                        | . 91<br>. 93<br>. 94<br>. 99<br>. 100                             |

| CHAPTER 9 FCML PFC FRONT END HARDWARE PROTOTYPE AND EXPERIMENTAL RESULTS    | . 103<br>. 107                                                    |

| CHAPTER 10 CONCLUSION AND FUTURE WORK  10.1 Summary                         | <ul><li>. 115</li><li>. 116</li><li>. 116</li><li>. 117</li></ul> |

# LIST OF ABBREVIATIONS

EMI ElectroMagnetic Interference

EUR Energy Utilization Ratio

FCML Flying Capacitor MultiLevel

IVI Inductor Volume Index

PFC Power Factor Correction

RVR Ripple Voltage Ratio

THD Total Harmonic Distortion

TSS Total Switch Stress

# CHAPTER 1

## INTRODUCTION

### 1.1 Single-phase AC-DC and DC-AC power conversion

Power conversion between DC and single-phase AC (inversion or rectification) finds a wide range of applications in both energy generation and consumption, spanning some of the most important areas of power electronics research and applications, such as transportation electrification and grid integration of storage and renewable resources. To name a few examples, on the energy generation side, residential or commercial scale PV installations typically have a string inverter or many micro-inverters to feed the DC power from PV modules into the single-phase electric grid; on the energy consumption side, most of the electrical systems power from the grid require rectifiers with power factor correction (PFC) capability; many battery storage systems require an AC-DC converter with bidirectional power transfer capability.

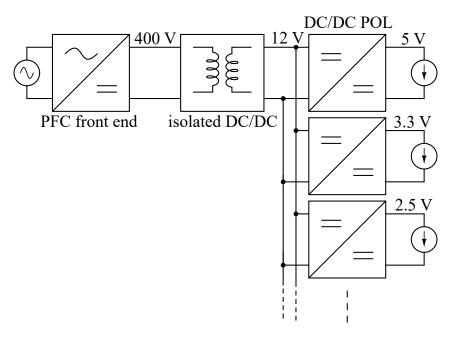

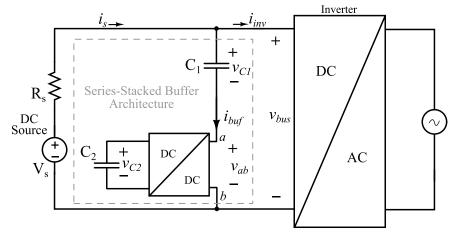

A modern distributed power architecture utilized in many industrial applications including telecoms and data centers is shown in Fig. 1.1 [1,2]. A PFC front end converter, typically non-isolated, interfaces the grid and transfers the power to a high voltage DC bus (e.g., 400 V). Then a front end DC/DC converter (e.g., an LLC converter) provides the isolation and steps down the voltage to an intermediate voltage DC bus (e.g., 48 V), which further distributes the power among downstream point-of-load (POL) regulators. The POL regulators eventually provide well-regulated voltages to the load. Similar architecture with power flowing in reverse can be found in distributed PV generation systems [3–5], etc. While such a distributed power architecture involves a variety of different power converters at different points of the system, the focus of this research is on the AC-DC converters between the AC grid and the high voltage DC bus, i.e., PFC front end rectifiers or grid-connected inverters. Beside the power supply architecture given in Fig. 1.1, such AC-DC converters are also indispensable in a wide range of other applications such as electric vehicle charging, LED drivers, battery storage systems and many more. Therefore, it is an important building block worth in-depth study.

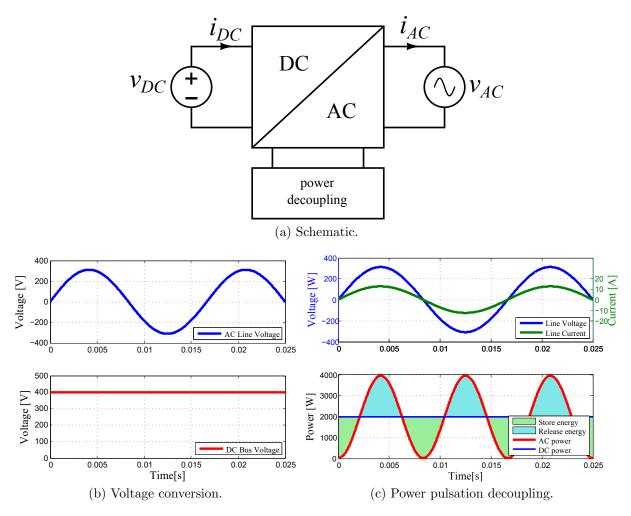

A high-level conceptual schematic of a single-phase AC-DC converter is shown in Fig. 1.2a.

Figure 1.1: A typical distributed power architecture.

The power on the AC side is given as

$$P_{ac} = v_{ac}i_{ac} = V_{AC}sin(\omega t) \times I_{AC}sin(\omega t + \phi)$$

$$= \underbrace{\frac{1}{2}V_{AC}I_{AC}cos\phi}_{\text{constant}} - \underbrace{\frac{1}{2}V_{AC}I_{AC}cos(2\omega t + \phi)}_{\text{pulsation}}, \tag{1.1}$$

where  $\omega$  is the line angular frequency,  $\phi$  is the power factor angle and  $V_{AC}$  and  $I_{AC}$  are the AC output voltage and current amplitude, respectively. Obviously, the AC side power consists of a constant part and a pulsating part at twice line frequency. With a unity power factor,  $\phi = 0$  represents the inverter operation and  $\phi = \pi$  represents the rectifier operation. The power on the DC side is supposed to be constant and equals the constant part of the AC side power, i.e.,

$$P_{dc} = v_{dc}i_{dc} = \frac{1}{2}V_{AC}I_{AC}cos\phi. \tag{1.2}$$

While the constant power should transfer between the AC and DC sides, the pulsation power on the AC side is supposed to be buffered completely by the AC-DC converter. Otherwise, the pulsation power would propagate to the DC side and introduce current and voltage ripples on the DC bus. Such ripples are usually very undesirable and strictly restricted. For example, ripples in a PV system reduce the tracking efficiency of maximum power point tracking operations [6]; ripples in an LED driver cause flicker in the light, which imposes

Figure 1.2: The main functionalities of a DC-AC converter.

potential health concerns [7]. Therefore, the basic task of a single-phase AC-DC converter is twofold: it needs to convert the voltage and current to the right level and transfer the power between input and output, as illustrated in Fig. 1.2a; it also needs to buffer the twice line frequency power pulsation from the AC side to maintain a ripple-free DC side, as illustrated by Fig. 1.2c. The entire research is built around fulfilling these two tasks in the most effective and efficiency way.

#### 1.2 Research scope and goal

When designing a system to fulfill these two tasks, a few performance metrics should be first determined. As the case for most power converters, the conversion efficiency is often the most important metric, as it affects not only the amount of energy consumption but also

Table 1.1: Google/IEEE little box challenge design specifications [8]

| Specifications     | Value                                      |

|--------------------|--------------------------------------------|

| Input              | 450 Vdc with 10 $\Omega$ source resistance |

| Output             | 240 Vac, 60 Hz                             |

| Power Level        | 0 to 2 kVA                                 |

| Power Factor       | 0.7 - 1, leading and lagging               |

| Input Ripple       | current $< 20 \%$ , voltage $< 3\%$        |

| Efficiency         | > 95% (CEC weighted)                       |

| Power Density      | $> 50 \text{ W/inch}^3$                    |

| Thermal Limit      | < 60 °C on all enclosure surface           |

| Output Current THD | < 5% for 25% to 100% load, $< 60$ mA       |

|                    | for below $25\%$ load                      |

| Output Voltage THD | < 5%                                       |

| EMC                | FCC Part 15 B                              |

other factors in the system such as thermal management and component lifetime. Besides efficiency, power density (i.e., the hardware volume to deliver certain power) is often an equally important metric. A large portion of AC-DC converter applications are volume or weight constrained, so a high power density converter is very desirable. Usually high efficiency and high power density are closely related. It is difficult to achieve high power density with poor efficiency since more power loss will likely increase the heatsink volume. However, high efficiency and high power density are also contradicting to each other. It is relatively easy to build a highly efficient converter with unlimited volume, while to build a very efficient converter with as small as possible volume is difficult, but of high interests in both research and applications.

One such example is the Google/IEEE little box challenge [8], an open competition to build the world's most power dense inverter with high efficiency. The competition requires the design and implementation of a 2 kW single-phase inverter with a 240 V RMS AC output; the DC source is 450 V with a 10 Ohm source resistor (presumably to emulate the characteristics of a PV string), implying a DC bus voltage of 400 V at full 2 kW load; the efficiency has to be higher than 95%; the DC side voltage ripple has to be smaller than 3% and the DC side current ripple smaller than 20% of the average. There are also other requirements on the EMI, etc. The main requirements listed in [8] are summarized in Table 1.1. The competition is to achieve the highest power density while meeting all these specifications. In order to establish a common baseline for analysis and comparison, the aforementioned specifications will be used as a design example target throughout Chapter 2 to Chapter 6.

Table 1.2: 1.5 kW PFC front end design specifications

| Specifications        | Value                  |

|-----------------------|------------------------|

| Input voltage         | 90 Vac – 260 Vac (RMS) |

| Output power          | $1500~\mathrm{W}$      |

| Output voltage        | $400 \mathrm{Vdc}$     |

| Output voltage ripple | < 5 V                  |

| Power factor          | > 0.98                 |

| Input current THD     | < 5% above 25% load    |

The Google/IEEE little box challenge design requirements represent most of the important aspects of single-phase AC-DC power conversion, but an important part that is missing is the grid-connected operation. The little box challenge only requires the inverter driving a standalone passive load, while most of the practical applications requires connection with the AC grid. Therefore, this work also study grid-connected operation of single-phase AC-DC converter. This part is studied through a 1.5 kW PFC rectifier design with requirements listed in Table 1.2. This design example is considered throughout Chapter 7 to Chapter 9.

To summarize, the goal of this research is to develop new techniques for AC-DC and DC-AC power conversion achieving high efficiency and high power density simultaneously, while improving other commonly cited performance for grid connected converters such as power factor and total harmonic distortion (THD). With other performance comparable or better than conventional approaches, this research targets power density improvement by an order of magnitude compared to conventional approaches. The fundamental methodology to achieve this goal is to leverage new system architecture, unconventional circuit topology and advanced digital control. Two design examples that embody the new ideas developed are considered throughout this work: the 2 kW inverter per the little box challenge requirement and the 1.5 kW universal input PFC front end.

#### 1.3 Research contribution

The contribution of this work builds upon two major innovations to address the challenge of designing high-efficiency, high power density AC-DC system. The first one is a series-stacked buffer architecture for the task of twice-line-frequency power pulsation decoupling. The second one is the practical realization of a compact, high frequency flying capacitor multilevel (FCML) topology for the task of AC-DC power converter. The theoretical development of the idea as well as its design procedure, control method, hardware implementation and

experimental characterization are presented in this dissertation.

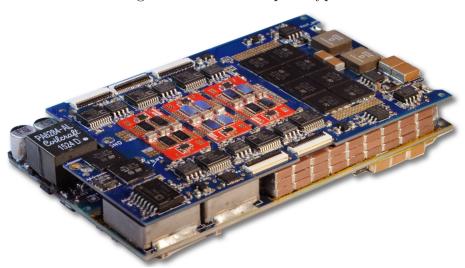

In the Google/IEEE little box challenge, while the originally set power density challenge is 50 W/inch<sup>3</sup>, our team from University of Illinois at Urbana-Champaign developed a 216 W/inch<sup>3</sup> inverter which makes the highest power density entry from academia [9]. The multilevel topology and active power pulsation decoupling techniques to be discussed in this dissertation are the key enablers of such high power density.

#### 1.4 Organization of this dissertation

The rest of this document can be divided into two major parts.

The first part consists of Chapter 2 to Chapter 6. This part prepares the necessary background on circuit element property, topology, control characteristics to derive and analyze active energy buffers, and then presents a new active power pulsation decoupling technique with tenfold power density improvement compared to other solutions in the literature.

Chapter 2 introduces the property of inductors and capacitors as energy storage elements in the circuit, which greatly affect the design considerations throughout this research. The conventional passive decoupling solution is introduced and its shortcomings are discussed, which motivates the use of active power pulsation decoupling techniques.

Chapter 3 reviews previous work on active power pulsation decoupling in the literature. To facilitate comparison, the concept of active buffer cell is established and a few performance metrics are highlighted. The main drawbacks of the existing solutions are the high component voltage stress and severe efficiency penalty of the active decoupling circuit, which motivates the development of the series-stacked buffer that solves these problems.

Chapter 4 explains the operation of the series-stacked buffer architecture and its advantages compared to other solutions reviewed in Chapter 3. The design constraints and optimization procedures are also derived.

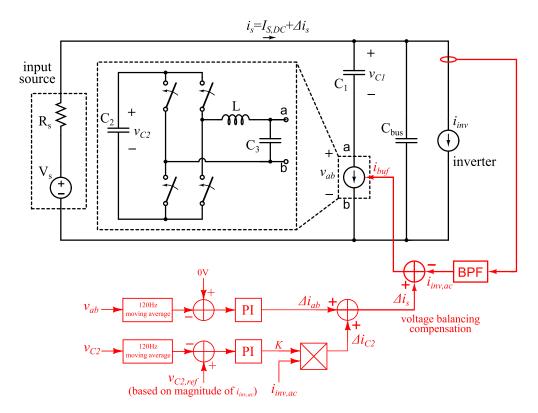

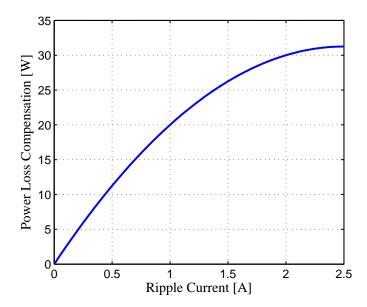

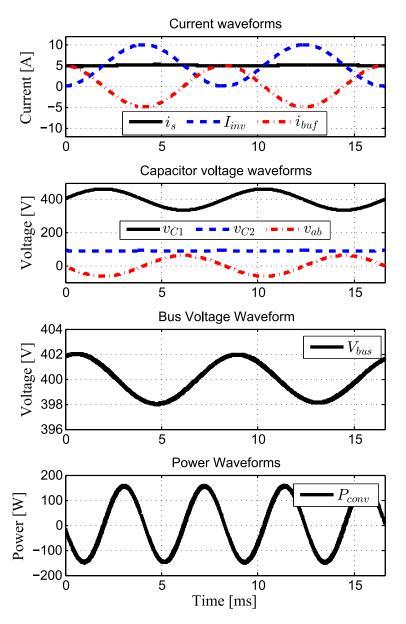

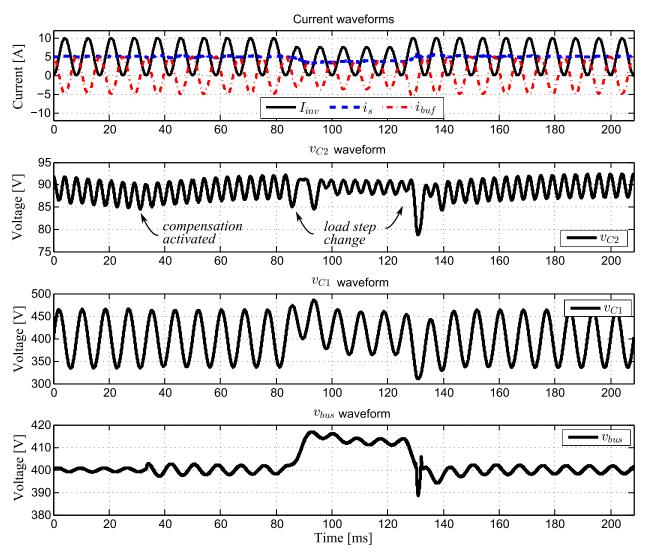

Chapter 5 reveals the control challenges associated with this architecture and presents the solution. Due to the series-connected nature of this architecture, current matching and capacitor voltage balancing are difficult. A compensation scheme utilizing the small ripple on the DC bus is developed to solve this problem.

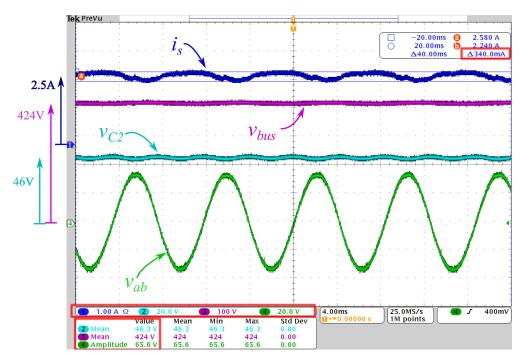

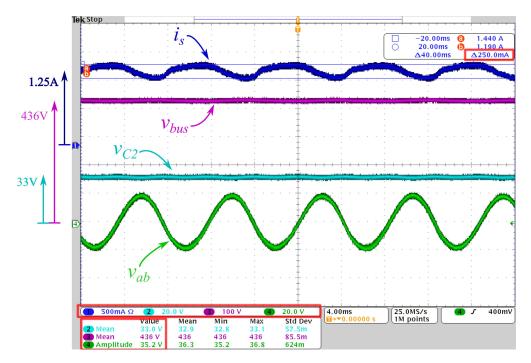

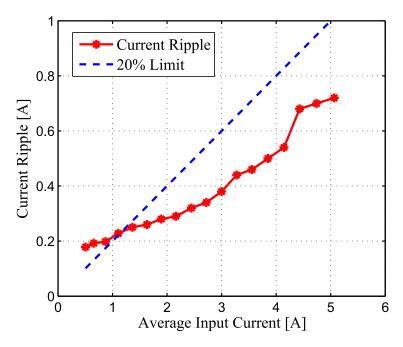

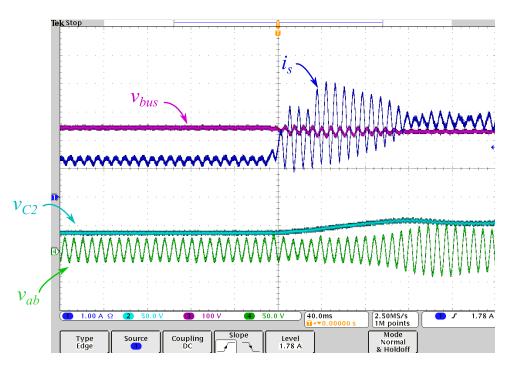

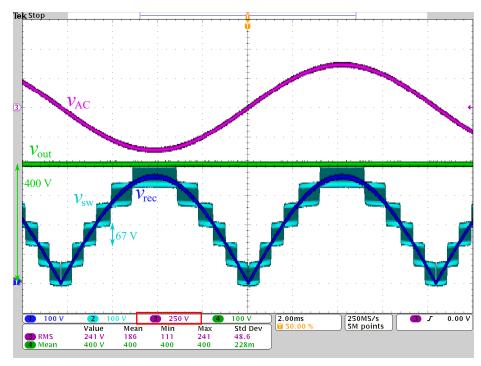

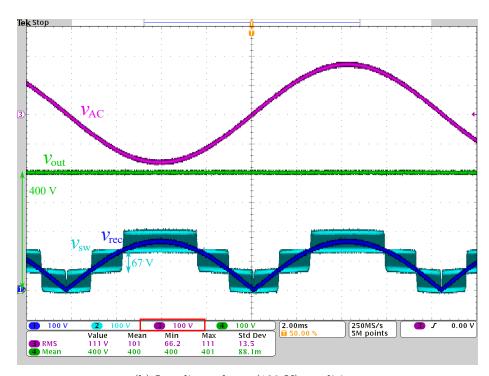

Chapter 6 presents the hardware prototype implemented for this architecture per the little box challenge requirements and the experimental results that verify the performance of the prototype, including power density, efficiency, DC side ripple, transient performance and various other waveforms illustrating of the operation. The experimental performance is also compared with various works in previous literature and other little box challenge entries.

The second part consists of Chapter 7 to Chapter 9. This part introduces the FCML topology and explores its control for grid connected operations.

Chapter 7 reviews the problems of conventional two-level based topologies and introduces the basics of the FCML topology. Its advantages is highlighted to motivate its application in single-phase AC-DC converters.

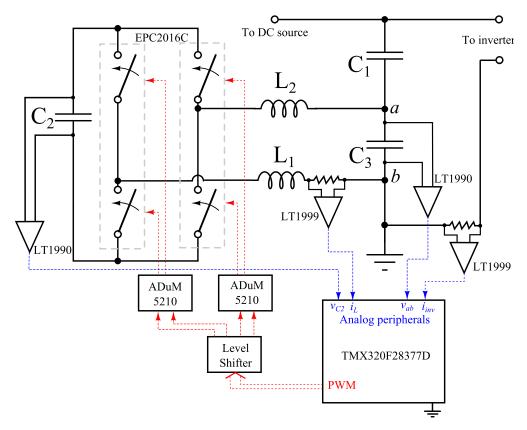

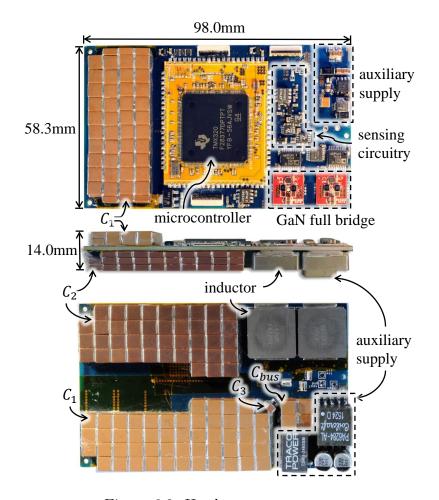

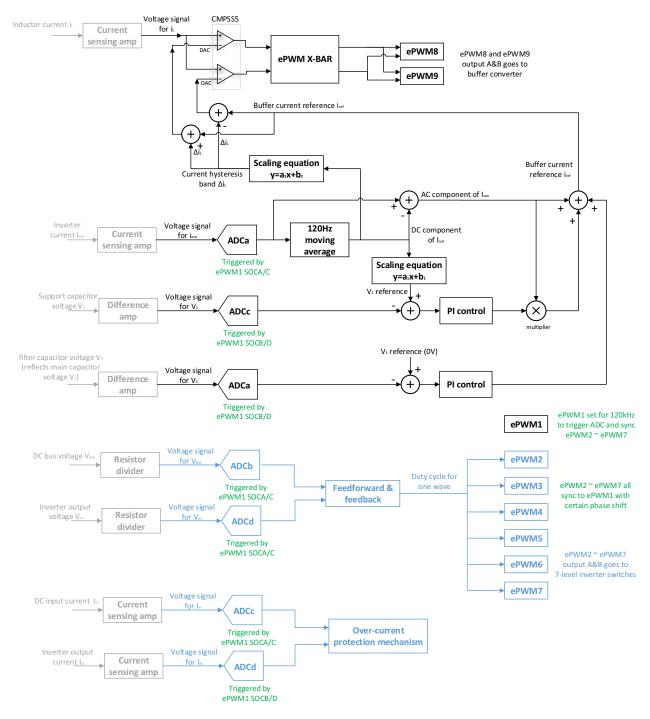

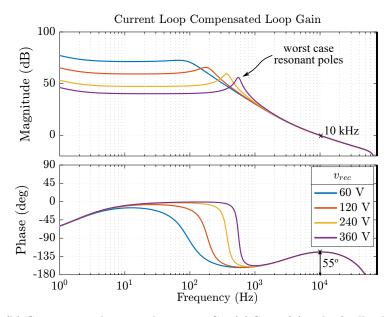

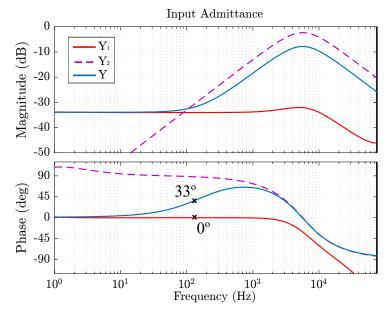

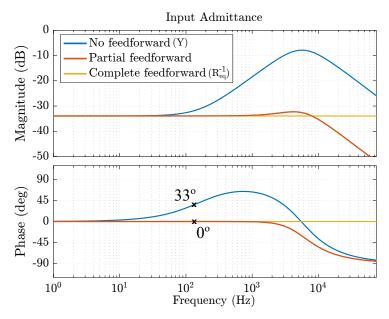

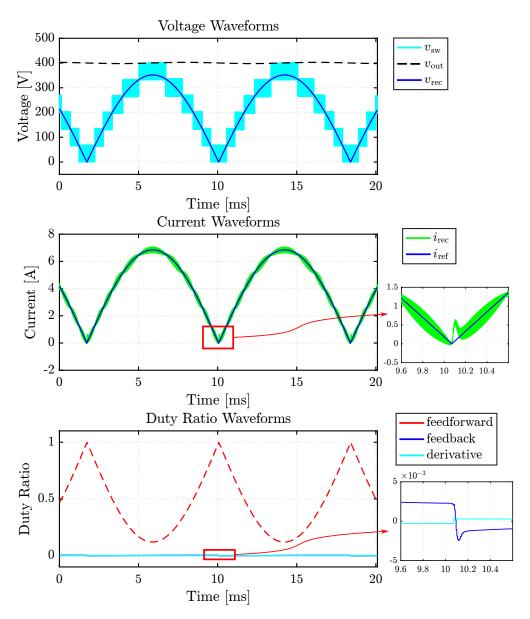

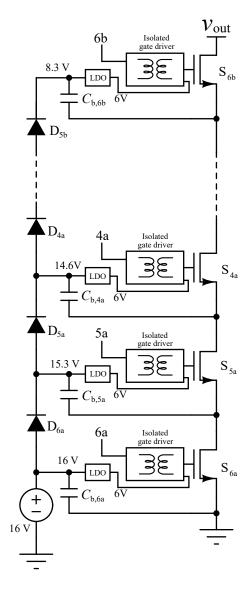

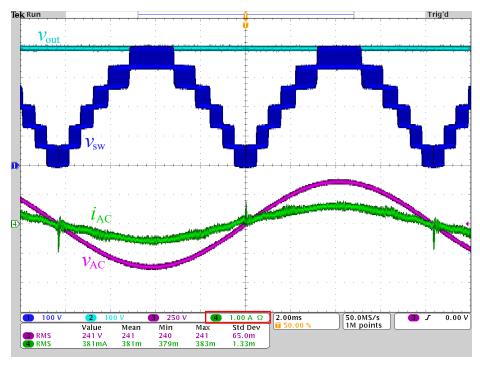

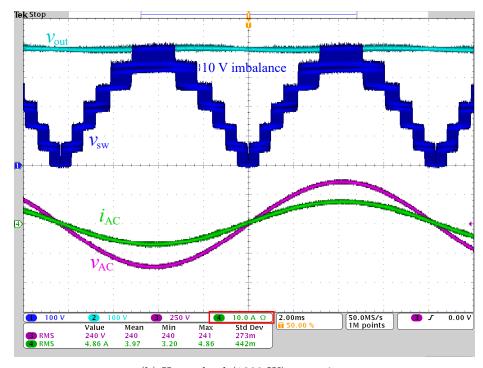

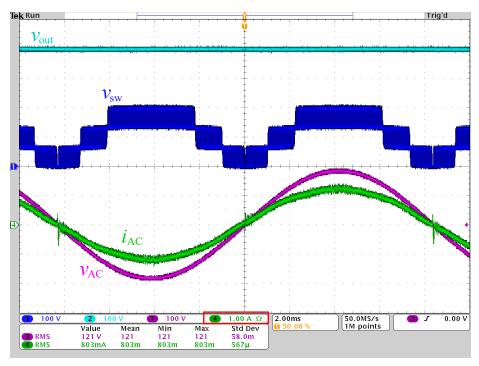

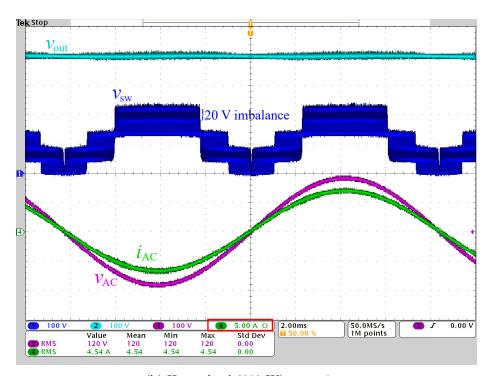

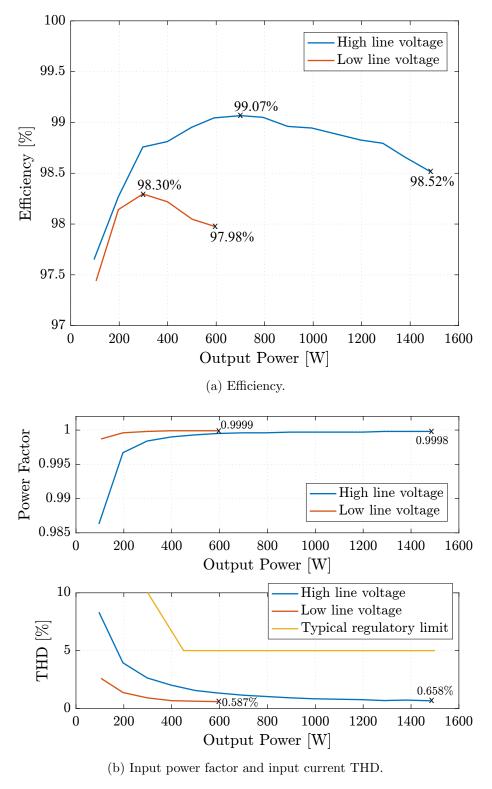

Chapter 8 presents a seven-level FCML converter design for a 1.5 kW PFC front end. The PFC control challenges when applying the FCML topology is analyzed in details and a feed-forward control scheme is developed to achieve excellent power factor and THD performance.

Chapter 9 presents the hardware prototype of the seven-level FCML based PFC front end. Various practical implementation issues are addressed. The high efficiency, high power density and high waveform quality are experimentally verified. Again, the experimental performance is compared with others reported in the literature.

Lastly, Chapter 10 summarizes the underlying reason why such high power density can be achieved with the proposed idea. Future work of this research is also suggested.

# CHAPTER 2

## ENERGY BUFFER BACKGROUND

### 2.1 Energy storage in single-phase AC-DC converter

As illustrated in (1.1), a twice line frequency power pulsation is present in the AC side power. Within each line cycle, this power pulsation needs to be absorbed and the associated energy stored in certain circuit elements when the pulsating power is positive; this energy is then released when the pulsating power is negative. Based on (1.1) and (1.2), the power of the energy storage element is given as

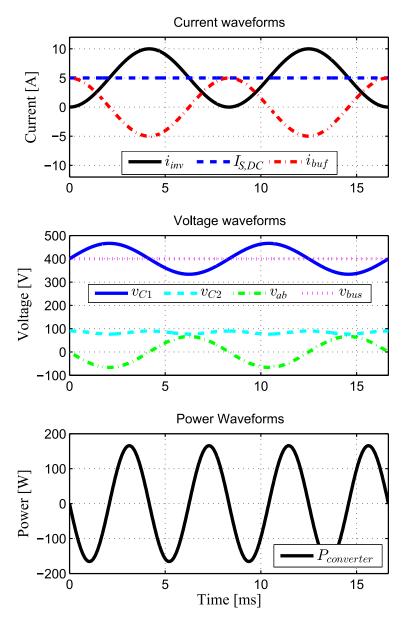

$$P_{buf} = P_{dc} - P_{ac} = \frac{1}{2} V_{AC} I_{AC} cos(2\omega t + \phi)$$

$$= \frac{P_{dc}}{cos\phi} cos(2\omega t + \phi). \tag{2.1}$$

The energy needs to be stored in each line cycle is given as

$$E_{buf} = \int P_{buf} dt = \frac{P_{dc}}{2\omega cos\phi} [sin(2\omega t + \phi) + \sigma], \qquad (2.2)$$

where  $\sigma$  is a constant and  $\sigma \geqslant 1$ , since the energy stored by a circuit element needs to be positive. The condition  $\sigma = 1$  is often selected to minimize the energy storage, but in certain situations there would be reasons to choose  $\sigma > 1$ , as will be discussed in Chapter 3. Therefore, the storage elements have to be designed to be *at least* capable of storing

$$E_{buf,peak} = \frac{P_{dc}}{\omega \cos \Phi}.$$

(2.3)

Note that in power converter designs, it is common to leverage a high switching frequency to reduce the energy storage requirement (and thus the energy storage element volume). However, in this scenario,  $\omega$  in (2.3) is fixed by the slow AC line frequency. Therefore, the single-phase AC-DC converter has to store a relatively large amount of energy and the volume of the energy storage element typically dominates the volume of the entire system.

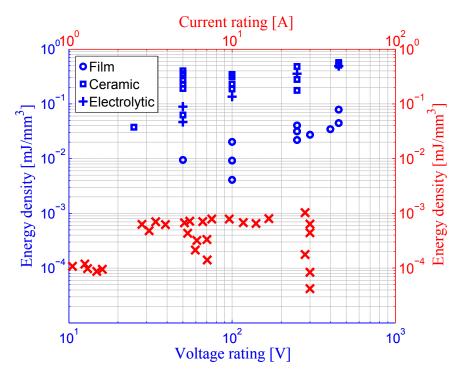

Figure 2.1: The energy density of selected capacitors measured in [10] and selected Coilcraft inductors calculated from the datasheet.

### 2.2 Energy density of storage elements

In twice-line frequency buffering, the most commonly considered storage elements are capacitors ( $E = \frac{1}{2}CV^2$ ) and inductors ( $E = \frac{1}{2}LI^2$ ). For high power density AC-DC converter design, it is important to consider the energy density of these components.

The power density of selected capacitors and inductor are plotted in Fig. 2.1. This voltage and current rating range is consider as it is applicable to the little box challenge design requirement considered as a baseline throughout this document. The inductors are selected from Coilcraft and their power density values are calculated from the datasheet with nominal inductance and saturation current rating. The capacitors are selected mostly from TDK and their power density values are all measured experimentally as presented in [10]. It is clear from Fig. 2.1 that in terms of power density, the best commercially available capacitors are about 500 to 1000 times better than the best commercially available inductors. Therefore, capacitors are often chosen as the energy storage component in single-phase AC-DC converters.

There are three major types of capacitors: electrolytic, ceramic and film. Electrolytic capacitors offer large capacitance at low cost, but they have relatively large equivalent series resistance (ESR), and thus high power loss and poor ripple current capability. Electrolytic

capacitors are unipolar, so they cannot withstand AC voltage. The reliability of electrolytic capacitors is relatively low and it is a bottleneck of the system reliability in many applications [11]. In comparison, film capacitors have low ESR, good ripple current capability and reliability, but the energy density is at least an order of magnitude lower. Ceramic capacitors have both good power density and low loss compared to the other two types. In fact, the best power density measured in Fig. 2.1 is achieved by an X6S ceramic capacitor rated at 450 V. Ceramic capacitors are also more reliable compared to electrolytic capacitors. For all these merits, ceramic capacitors are used extensively in all the prototypes in this work.

It is important to note some of the unique characteristics of ceramic capacitors as an energy storage element. The capacitance of ceramic capacitors is nonlinear and highly dependent on the voltage applied on the capacitor. This is often referred to as voltage de-rating. Typically, the capacitance of class II ceramic capacitors can decrease more than 70% from their nominal values when the applied voltage increases from zero to the rated voltage. Therefore, it is important to consider the large signal behavior of the ceramic capacitors when used as storage elements, and that is why experimental measurement in [10] are important to determine the actual energy density of the capacitor. The measured result in Fig. 2.1 indicates that the X6S ceramic capacitor, even after voltage de-rating, still offers the best power density.

It should also be noted from Fig. 2.1 that ceramic capacitors at different voltage ratings have approximately the same energy density. Although higher voltage leads to more energy stored, a capacitor rated at higher voltage typically has lower capacitance density, so the end result on energy density cancels out. At different voltage ratings, there might be small irregularities of power density due to practical issues like packaging footprint, but to the first order, they have approximately the same power density at different voltage rating, at least on the same order of magnitude. This means that for ceramic capacitors, there is limited or perhaps even no advantage to use high voltage rating capacitors. As long as the capacitors are charged fully to the rated voltage, it should make little difference which voltage rating is chosen. Note that the above argument is only valid for ceramics. For electrolytic and thin film capacitors, higher voltage rating does imply high energy density. This point can also be observed from Fig. 2.1. This work focuses on the use of ceramic capacitors, though, given its high energy density and high current ripple capability.

### 2.3 Capacitor passive decoupling

In single-phase AC-DC converters in practice, the simplest and most widely used power pulsation buffer nowadays is a large DC link capacitor, as shown in Fig. 2.2. This approach

Figure 2.2: Capacitor passive decoupling.

is often referred to as capacitor passive decoupling. Based on (2.3), in one cycle, the energy storage of the capacitor bank can be expressed as

$$E_{buf,max} - E_{buf,min} = \frac{P_{dc}}{2\pi f \cos \phi}$$

$$= E_c(V_{max}) - E_c(V_{min}) \qquad (2.4)$$

$$\approx \frac{1}{2}CV_{max}^2 - \frac{1}{2}CV_{min}^2$$

$$\approx \underbrace{\frac{1}{2}(V_{max} + V_{min})(V_{max} - V_{min})C}_{\text{average}}, \qquad (2.5)$$

where  $P_{dc}$  is the average power (i.e., the DC power) of the DC-AC converter, f is the line frequency and  $V_{max}$ ,  $V_{min}$  are the two extremes of the voltage across the capacitor bank. The energy storage requirement in one cycle is determined by the average load power (i.e.,  $\frac{P_{dc}}{2\pi f \cos \phi}$ ), and is fulfilled by charging and discharging the capacitors (i.e.,  $E_c(V_{max}) - E_c(V_{max})$ ). We may ignore the fact that C might be nonlinear and depends on the voltage, as it is especially the case for ceramic capacitors. Assume a constant C, then we arrive at (2.5). This assumption is made for the simplicity of analysis and the general conclusions of the following analysis is valid regardless of the nonlinearity of C.

According to (2.5), the capacitor bank needs to have enough capacitance C and voltage ripple (i.e.,  $V_{max} - V_{min}$ ) to provide the required power pulsation buffering capability. Note that as discussed in Section 1.1, voltage ripple on the DC bus is very undesirable. Most applications impose strict constraints (a few percentage of the average DC bus voltage) on the magnitude of the allowed voltage ripple on the DC bus. Therefore, to meet certain energy storage requirement, the capacitance C typically has to be very large. Such large capacitance

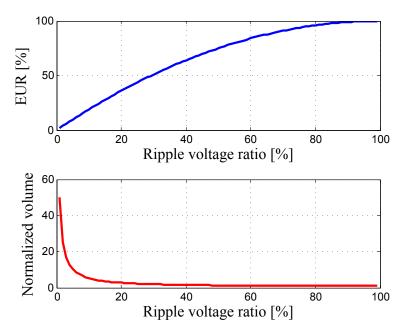

Figure 2.3: The energy utilization ratio (EUR) and passive decoupling capacitor volume (normalized over the volume at 100% EUR) as a function of the ripple voltage ratio on the DC bus.

is usually provided by a bulky electrolytic capacitor bank, as electrolytic capacitors offer large capacitance at low cost, and it is often the only economically viable solution given the large C needed. However, as mentioned in Section 2.2, electrolytic capacitors are known for their high power loss, low reliability and limited current ripple capability [11]. In fact, in practice the volume of the electrolytic DC bus capacitor bank is often limited by the ripple current capability [12], rather than the capacitance requirement of (2.5). Therefore, due to efficiency and reliability considerations, ceramic or metal film capacitors are often preferred, but the large volume and high cost becomes the major limitations. With either type of capacitor, the volume of the DC link capacitor bank typically dominates the volume of the overall AC-DC converter.

# 2.4 Energy utilization ratio

To better understand the problem of capacitor passive decoupling, let us define two important metrics. The first one is the ripple voltage ratio (RVR), which is simply the voltage ripple over the maximum voltage on the DC bus, i.e.,

$$\Gamma_{\text{RVR}} = \frac{V_{max} - V_{min}}{V_{max}}.$$

(2.6)

The second one is the energy utilization ratio (EUR) [13]. EUR of a single capacitor is defined as the peak energy exchanged in one line cycle over the full energy storage at the maximum rated voltage, i.e.,

$$\Gamma_{\text{EUR}} = \frac{E_{buf,peak}}{E_c(V_{max})} = \frac{E_c(V_{max}) - E_c(V_{min})}{E_c(V_{max})},$$

(2.7)

where  $E_{buf,peak}$  is defined in (2.3). The total volume of the energy storage element is determined by  $E_c(V_{max})$ , while the energy storage requirement is fulfilled by  $E_c(V_{max}) - E_c(V_{max})$ . EUR = 100% would be highly desirable as it implies that a certain energy storage requirement is fulfilled with the smallest capacitor volume possible.

For an active buffer structure with more than one energy storage capacitor, such as the series stacked buffer to be presented in this dissertation, EUR is typically calculated for all the capacitors in the structure, i.e.,

$$\Gamma_{\text{EUR}} = \frac{E_{buf,peak}}{\sum E_c(V_{max})},\tag{2.8}$$

where the sum is over all energy storage capacitors in the circuit. It is very important to note that, in general,

$$E_{buf,peak} \neq \sum E_c(V_{max}) - \sum E_c(V_{min}), \tag{2.9}$$

since not all the capacitors reach their maximum or minimum voltage at the same time.

Fundamentally, the problem of the capacitor passive decoupling is that the DC link capacitor bank needs to perform both energy storage and DC bus voltage regulation, but these two functionalities are contradicting to each other. Effective energy storage requires a large EUR while DC bus voltage regulation restricts the EUR to only a few percentage. To see this point, Fig. 2.3 plots the EUR of the capacitor bank as a function of the allowed RVR on the DC bus. For an application that allows 3% ripple on the DC bus, the EUR is only approximately 6%, resulting in a capacitor volume 17 times larger than the volume under 100% EUR.

The key to overcoming this limitation is to separate the energy storage and voltage regulation functionalities from the capacitors. The capacitors should be allowed to ripple more to improve EUR while being interfaced to the DC bus through an active converter to maintain a constant bus voltage. This approach is often referred to as active power pulsation decoupling, or active decoupling for short. Various embodiments of such schemes have been presented in the literature [14–16], which will be review in Chapter 3. Active decoupling,

however, usually introduces efficiency penalty, additional circuit elements and considerable complexity into the system, which designers should strive to minimize.

Consider the Google/IEEE lttle box challenge design example in Table 1.1. For this 2 kW inverter generating 60 Hz output, only 3% voltage ripple is permitted on the 400 V DC bus. If a conventional passive decoupling solution is used, it can be calculated that at least 1.1 mF is required for the DC link capacitor bank according to (2.5). Moreover, if practical ripple current limitations of electrolytic capacitors are taken into consideration, even more capacitors are typically needed. On the opposite extreme, if a 100% EUR is somehow achieved, then only 64  $\mu F$  of buffer capacitor is required. Practical active decoupling solutions will result in capacitance somewhere between these two extremes.

# CHAPTER 3

# REVIEW OF ACTIVE ENERGY BUFFER

#### 3.1 Overview

As reviewed in Section 2.1, the twice-line-frequency power ripple decoupling is a fundamental challenge in all single-phase AC-DC or DC-AC converters since the beginning. While some previous works focus on improving the passive DC link capacitors through component level optimizations [17] or system level tradeoffs [18–22], many works study active decoupling circuits. Many of the active decoupling circuit topologies to be reviewed in this chapter can be traced back to the earlier works in [23–34]. For example, Wang et al. [23] and Hsu et al. [24] represent the early work on the full-bridge active buffer with capacitor energy storage while Bose et al. [25] and Shimizu et al. [26] have a similar active circuit topology but with inductor energy storage. Martins et al. [27–29] propose a two-stage structure containing a high voltage intermediate bus with larger voltage ripples to reduce the required storage capacitor, while the first stage DC-DC converter keeps the DC side ripple-free; this structure is still widely used in various current works [35]. Moreover, Shimizu et al. [30, 31] and Kjaer et al. [32] propose an active buffer circuit integrated to the operation of a flyback converter. Kyritsis et al. [33,34] present some of the original ideas of the half-bridge active buffer with capacitor energy storage. These works form the basis of a rapid development of this area in the past decade [13–16,36–48]. Nowadays there are well over 50 variations of active decoupling buffers in the literature with different combinations of system architecture, converter topology and control method. While this dissertation will only review closely related works leading to the development of the series-stacked buffer architecture, comprehensive reviews on twice-linefrequency power decoupling can be found in [14–16, 49].

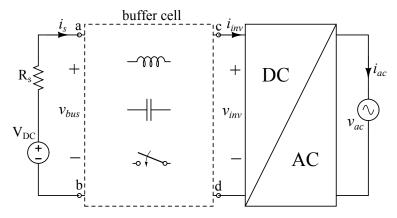

In this dissertation, they are classified as "independent decoupling" and "dependent decoupling" buffers, as it would be the best way to understand the logic flow. "Independent decoupling" means that the operation of the active buffer is independent of the rest of the AC-DC converter; that is, the active buffer is intended to be a plug-and-play replacement of the bulky DC bus capacitors in the capacitor passive decoupling solution. It should not

Figure 3.1: The concept of "independent decoupling". The active buffer cell and the inversion/rectification stage are two distinct parts in the system and operates independently.

change the operating point or the control method of the inversion/rectification stage. "Dependent decoupling", on the other hand, means that active buffer shares part of the circuit elements with the inversion/rectification stage and the control and operation of both parts are integrated together. These two approaches are closely related. One can often derive a "dependent decoupling" solution from a corresponding "independent decoupling" solution, or vice versa. This chapter mostly discusses "independent decoupling", as it is the necessary preparation to understand the series-stacked buffer architecture; "dependent decoupling" will only be discussed briefly.

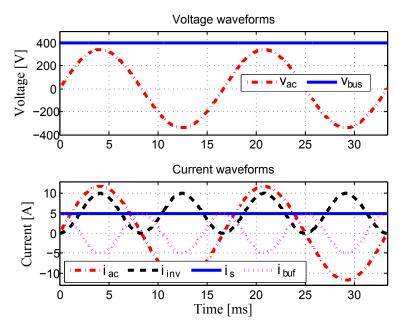

Figure 3.2: Waveforms of key voltage and current variables marked in Fig. 3.1 in two line cycles.

Figure 3.3: Capacitor passive decoupling solution fitting into the concept of buffer cell.

### 3.2 Buffer cell concept

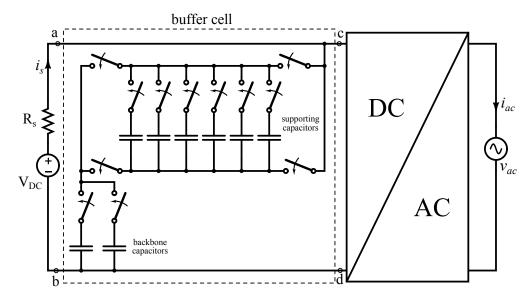

A high-level schematic of the "independent decoupling" buffer in an AC-DC system is shown in Fig. 3.1. Note that the analysis throughout this document applies equally to inverters and rectifiers in almost all cases unless otherwise stated, so the following analysis will assume an inverter system for simplicity of description.

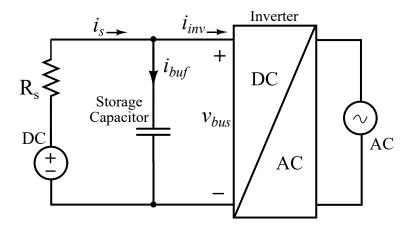

The active decoupling circuit can be abstracted as a two-port element (i.e., a buffer cell) inserted between the DC source and inversion stage. Some key voltage and current variables are marked in Fig. 3.1 and their ideal waveforms are plotted in Fig. 3.2. The voltage and current on the AC side are 60 Hz sine wave. Ideally, we would like the DC bus voltage and the DC side input current,  $i_s$ , to be constant. Under this condition, the power of the buffer cell is given in (2.1) and the energy it stores is given in (2.2). If the DC bus voltage is held constant, the current flowing into the active buffer cell,  $i_{buf}$ , follows a 120 Hz sine wave, i.e.,

$$i_{buf} = \frac{P_{buf}}{V_{bus}} = \frac{P_{dc}}{V_{bus}cos\phi}cos(2\omega t + \phi), \tag{3.1}$$

as shown in Fig. 3.2.

The capacitor passive decoupling discussed in Section 2.3 can fit into the buffer cell concept as shown in Fig. 3.3, and the current through the capacitor would be  $i_{buf}$ . Depending on the voltage ripple, the EUR of such a passive buffer cell is calculated in Fig. 2.3 and is expected be very low as discussed. Active buffer cells are therefore developed to improve the EUR so capacitor volume can be small, while preserving the same functionality of absorbing current and power mismatch. One example of such an active cell structure is shown in Fig. 3.4, where a magnetic-based converter interfaces the energy storage capacitor and the DC bus. The converter is controlled to shape its waveform, as shown in Fig. 3.2, such that power

pulsation is absorbed. Details of various types of buffer cells will be reviewed in this section.

#### 3.2.1 Buffer cell performance metrics

Before introducing any specific buffer cell structure, it would be of high interest to highlight a few performance metrics that allow quantitative comparison of their performance.

The first metric is EUR, which has been defined in Section 2.4. This parameter reflects the volume of the capacitor and improving EUR is the most important motivation of active decoupling.

The second metric is the total switch stress (TSS) of the converter, defined as

$$S = \sum_{i=0}^{n} (V_{max} I_{max}), \tag{3.2}$$

where the sum is over all switches in the converter,  $V_{max}$  is the maximum voltage blocked by the switch and  $I_{max}$  is the maximum current conducted by the switch. Typically, switch utilization ratio, defined as the power delivered over the switch stress, is considered for a converter. However, once the system power level is given, the power processed by the energy buffer is the same for all buffer cells (i.e., the power delivered is the same), so it is enough to consider only the TSS. Note that since TSS is obtained by summing over all switches, the effect of the switch count is also reflected in TSS. This metric is often a good indicator of the switch size, switching frequency and power loss. A good topology should minimize TSS.

The third metric is the power loss. A complete and precise calculation of all power losses in the converter is very difficult; therefore, we consider only a few major components in their approximate forms. The conduction loss, including both inductor DCR and transistor on-resistance, is given as

$$P_{cond} = (I_{ave}^2 + \frac{1}{12}\Delta I^2)[R_{on} + R_{DCR}], \tag{3.3}$$

where  $R_{DCR}$  is the DCR of the inductor and  $R_{on}$  is the on-resistance of all the transistors. The inductor core loss is given as [50]

$$P_{core} = k(\Delta I)^{\beta} f_s, \tag{3.4}$$

where k and  $\beta$  are empirical parameters,  $\Delta I$  is the inductor current ripple and  $f_s$  is the

switching frequency. The transistor output capacitor loss is given as

$$P_{Coss} = \frac{1}{2}C_{oss}V^2f_s, \tag{3.5}$$

where  $C_{oss}$  is the parasitic capacitance across the transistor drain-source. Lastly, the current-voltage overlap loss is given as

$$P_{op} = \frac{VI}{2} t_{tr} f_s, \tag{3.6}$$

where  $t_{tr}$  is the sum of transistor turn-on and turn-off time. Note that purpose of studying these loss equations here is not to calculate the specific value of loss, but rather to understand how the power loss scales with other circuit parameters such as voltage and current stress.

The fourth metric to consider is the voltage stress on the circuit components, especially the inductor. For certain current ripple and switching frequency, the value of inductance is directly determined by the voltage applied, i.e.,  $L \propto V$ . Moreover, the voltage stress usually affects the switching frequency and power loss of the converter as well, which might in turn increase the required inductance. High inductance limits the dynamic performance of the buffer cell and increase the inductor volume. Voltage stress should be minimized.

The fifth metric to consider is the inductor volume. Since one of the major purposes of active decoupling is to improve power density, care must be taken that the volume reduction due to higher EUR is not offset by the volume of the added components. The volume of the added component is often dominated by the inductor volume. As discussed in Section 2.2, we can assume a constant power density for all inductors regardless of the current rating level. Then the volume of the inductor is determined simply by its peak energy storage, i.e.,  $\frac{1}{2}LI_{max}^2$ . The inductance L is affected by voltage stress and frequency. For different converter designs with the same current but different voltage stress levels, a fair comparison can be made by making the entire converter have the same efficiency and inductor current ripple. Since all buffer cells process the same pulsation power, this means the same power loss for different designs. To maintain the same conduction loss, consider (3.3); when the voltage stress increases, to the first order, the transistor length increases proportionally for higher voltage rating, i.e.,  $l_{sw} \propto V$ ; to make the on-resistance the same, the width of the transistor will increase proportionally with voltage stress as well, i.e.,  $w_{sw} \propto V$ . This suggest that the gate capacitance of the transistor increases quadratically with the voltage stress. To maintain the same switching loss, we examine (3.6), (3.5) and (3.4). In (3.6), the transition time  $t_{tr}$  is dependent on many factors, but here suppose we want to keep the same  $\frac{dv}{dt}$  for the transition, so  $t_{tr} \propto V$  and thus  $P_{op} \propto V^2 f_s$ . In (3.5), the output capacitance  $C_{oss}$  is assumed a linear function of voltage rating, i.e.,  $P_{op} \propto V^3 f_s$ . In (3.4), since we try to keep the inductor current ripple the same,  $P_{core} \propto f_s$ . For simplicity, we average all the dependency and approximate all the switching loss as  $P_{sw} = P_{op} + P_{Coss} + P_{core} \propto V^2 f_s$ . This suggest that  $f_s \propto \frac{1}{V^2}$  to keep the switching loss the same. Moreover, note that  $\Delta I \propto \frac{V}{Lf_s}$ . To keep the inductor current ripple the same,  $L \propto V^3$ . Therefore, we can make the approximation that the inductor volume  $V_{ind} \propto \frac{1}{2} L I_{max}^2 \propto V^3 I^2$ . Therefore,  $V^3 I^2$  can be used as a performance metric to compare the inductor volume between different buffer cells. Therefore, we define the inductor volume index (IVI) as  $\frac{V^3 I^2}{V_{bus}^3 I_{DC}^2}$ , where  $V^3 I^2$  is normalized by bus voltage and average DC current.

The last metric to consider is the harmonic content in the voltages and currents of the buffer cell. A well-designed buffer cell has smooth 120 Hz or 60 Hz voltage and current waveforms, which makes the design of the local controller easy. The controller only needs to track a single frequency reference at 60 Hz or 120 Hz. Otherwise, certain buffer cells operate with spiky voltage and current waveform, which contains large harmonic contents. These high frequency contents need to be tracked by the controller as well, requiring very high control bandwidth, otherwise the power pulsation is not fully absorbed and there would be ripple on the DC bus. THD is a good indicator of the high frequency contents and the ripple if the buffer failed to track this high frequency content. As will be shown later in this chapter, for converters under high voltage stress and with large filter inductors, obtaining high bandwidth can be very difficult.

#### 3.3 Parallel-connected cell

A magnetic-based bi-directional power converter can be inserted between the DC bus and the energy storage capacitor such that one can control the conversion ratio to discharge the buffer capacitor more deeply while still maintaining a constant bus voltage. Since the energy storage capacitor is still connected across the DC bus but through a buffer converter, this structure is referred to as parallel-connected cell.

#### 3.3.1 Full-bridge buck cell

One example of such a structure is shown in Fig. 3.4, where a full-bridge converter interfaces the energy storage capacitor and the DC bus [40,51]. Note that this full-bridge converter is referred to as buck cell since it operates in buck mode when charging the capacitor, according to the convention in the literature [16], although it is bi-directional and operates in boost

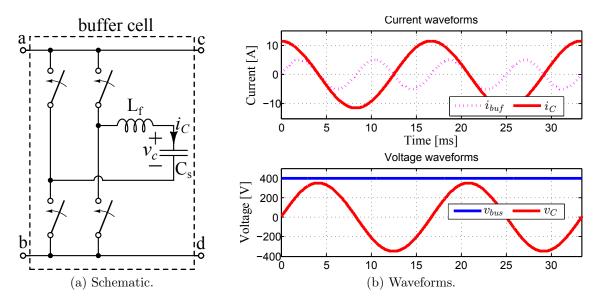

Figure 3.4: Schematic and operating waveforms of the full-bridge buck cell;  $C_s = 87 \ \mu F$  used to plot the waveform.

mode when discharging the capacitor.

With proper control, the full-bridge buck cell can absorb the instantaneous difference between  $i_s$  and  $i_{inv}$  to charge or discharge the energy storage capacitor  $C_s$ . The expression of the real-time energy stored by the capacitor is given in (2.2), so the capacitor voltage can be derived as follows,

$$\frac{1}{2}C_s v_c^2 = \frac{P_{dc}}{2\omega \cos\phi} [\sin(2\omega t + \phi) + \sigma],$$

$$\Rightarrow v_c = \pm \sqrt{\frac{2P_{dc}}{2\omega C_s \cos\phi} [\sin(2\omega t + \phi) + \sigma]}.$$

(3.7)

Note that this equation, along with all the equations in this section, is intended not for control purposes but only for analytical purposes. In other words, here it is assumed that a perfect control has been implemented and these equations describe the system behavior under perfect control. In this way, we can evaluate the theoretical performance limit of each buffer cell structure without considering the details of control implementations.

Considering (3.7), for the smallest capacitor volume,  $\sigma = 1$  can be chosen. Since it is a full-bridge converter,  $v_c$  can be bipolar, so the plus and minus sign in (3.7) can be selected

properly such that  $v_c$  is a smooth sine wave, i.e.,

$$v_{c} = \pm \sqrt{\frac{2P_{dc}}{2\omega C_{s}cos\phi}} \left[sin(2\omega t + \phi) + 1\right]$$

$$= \pm \sqrt{\frac{2P_{dc}}{2\omega C_{s}cos\phi}} \left[2cos^{2}(\omega t + \frac{\phi}{2} + \frac{3\pi}{4})\right]$$

$$= \sqrt{\frac{2P_{dc}}{\omega C_{s}cos\phi}} \left[cos(\omega t + \frac{\phi}{2} + \frac{3\pi}{4})\right]. \tag{3.8}$$

The reason to select a smooth sine wave over other possible waveforms is that such a waveform contains only 60 Hz content and zero THD. This makes the controller design very easy, as it only needs to track 60 Hz reference signals. A PI controller with low bandwidth or a proportional resonant controller with a single resonant frequency at 60 Hz can easily fulfill this task. As shown in Fig. 3.4b, the capacitor can be discharged from the rated voltage down to 0, indicating that the EUR is 100%. The capacitor current  $i_c$  is given as

$$i_c = C_s \frac{dv_c}{dt} = \sqrt{\frac{2\omega C_s P_{dc}}{\cos \phi}} \left[ \sin(\omega t + \frac{\phi}{2} - \frac{\pi}{4}) \right]. \tag{3.9}$$

The magnitude of the capacitor voltage can be adjusted by different value of  $C_s$ . The lower limit of  $C_s$  is that the capacitor voltage magnitude cannot exceed the DC bus voltage, i.e.,

$$\sqrt{\frac{2P_{dc}}{\omega C_s cos \phi}} \leqslant V_{bus},\tag{3.10}$$

otherwise it will cause over-modulation of the full-bridge converter. Therefore, for the little box challenge design example,  $C_s$  in this topology can be as small as 66  $\mu$ F rated at 400 V. Note that as discussed in Section 2.2, capacitors rated at different voltages have approximately the same power density; this means that the capacitor volume is minimized as long as EUR = 100%, regardless of the capacitor voltage rating. However, a high capacitor voltage magnitude leads to low capacitor current, which does offer benefits in terms of the minimization of TSS and inductor volume. In this structure, both TSS and inductor volume is minimized when (3.10) takes the equal sign. Since the capacitor voltage is bipolar, electrolytic capacitor cannot be used in this structure.

Figure 3.5: Schematic and operating waveforms of the half-bridge buck cell;  $C_s = 200 \ \mu F$  used to plot the waveform.

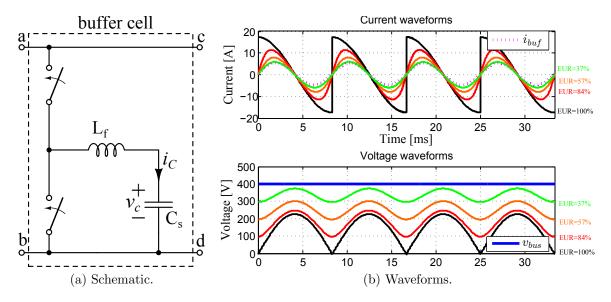

#### 3.3.2 Half-bridge buck cell

The switch count of a full-bridge buck cell can be reduced by half to form a half-bridge buck cell, as shown in Fig. 3.5a. In this structure, since one side of the capacitor is permanently connected to the ground, the capacitor voltage has to be unipolar. The analysis for full-bridge buck cell in (3.7) and (3.8) still holds, except that  $v_c$  is always positive, i.e,

$$v_c = \sqrt{\frac{2P_{dc}}{\omega C_s \cos\phi}} \left| \cos(\omega t + \frac{\phi}{2} + \frac{3\pi}{4}) \right| . \tag{3.11}$$

The capacitor current  $i_c$  has the same magnitude as given in (3.9), but is now a piecewise function with a discontinuous jump as shown in Fig. 3.5b. For this capacitor voltage waveform, EUR = 100%. However, with EUR = 100%, the capacitor is a rectifier sine wave, which contains not only 120 Hz components but large harmonics. The high harmonic contains in current and voltage impose challenges for controller design. In practice, a voltage bias is often added, i.e.,  $\sigma > 1$  in (3.7). As illustrated by Fig. 3.5b, this voltage bias decreases EUR but smooths out the spiky capacitor current and voltage, which is helpful for improving switch utilization and reducing inductor size.

Figure 3.6: Schematic and operating waveforms of the half-bridge boost cell;  $C_s = 200 \ \mu F$  used to plot the waveform.

#### 3.3.3 Half-bridge boost cell

The half-bridge buck cell can be reconfigured to form a half-bridge boost cell [52, 53], as shown in Fig. 3.6a. Since (3.7) is derived from conservation of energy and not specific to buck topology, it is still applicable to half-bridge boost cell except that now

$$v_c > V_{bus}, (3.12)$$

due to the boost configuration. The condition described in (3.12) is achieved by a large value of  $\sigma$  in (3.7), which further decreases the EUR. The voltage stress on the buffer converter components is also higher. A half-bridge buck-boost cell [54] can be derived as well, which imposes no limitation on the capacitor voltage so the EUR can be high, but the voltage stress on the buffer converter is the highest. Both the half-bridge boost cell [55] and half-bridge buck-boost cell suffer higher voltage stress while offering no obvious advantage over the half-bridge boost cell, unless the DC bus voltage on the original system is very low and the rating of the practical switch component is significantly under-utilized. Similarly, the full-bridge boost cell [56] and full-bridge buck-boost cell can be derived, but offer no obvious advantage over the aforementioned topologies.

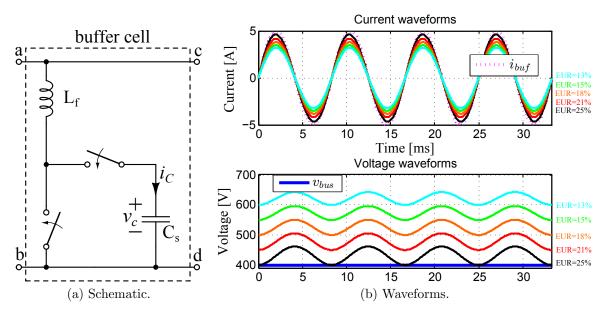

#### 3.3.4 Half-bridge split-capacitor cell

The capacitor voltage and current for half-bridge buck cell, even after certain voltage bias is added ( $\sigma > 1$  in (3.7)), contains large harmonic contents, which imposes challenges to controller design. One topology to eliminate the harmonic content while still having the low switch count of the half-bridge buck cell is the split-capacitor structure [38,57] as shown in Fig. 3.7a. The energy storage capacitor is split into two equal halves, i.e.,  $C_1 = C_2 = C_s$ . The half-bridge is connected to the mid-point of the split capacitors and control the voltage of that point. Again the energy stored in the capacitors is given in (2.2), therefore

$$\frac{1}{2}C_s v_1^2 + \frac{1}{2}C_s v_2^2 = \frac{P_{dc}}{2\omega \cos\phi} [\sin(2\omega t + \phi) + \sigma], \tag{3.13}$$

$$v_1 + v_2 = V_{bus}. (3.14)$$

Note that given the constraint (3.14),

$$\frac{1}{2}C_s v_1^2 + \frac{1}{2}C_s v_2^2 \geqslant \frac{C_s V_{bus}^2}{4},\tag{3.15}$$

where the equal sign is taken when  $v_1 = v_2 = V_{bus}$ . Therefore,

$$\frac{P_{dc}}{2\omega cos\phi} \left[ sin(2\omega t + \phi) + \sigma \right] \geqslant \frac{C_s V_{bus}^2}{4}$$

$$\Rightarrow \sigma \geqslant 1 + \frac{C_s V_{bus}^2}{4\frac{P_{dc}}{\omega C_s cos\phi}}.$$

(3.16)

Here for the highest EUR,  $\sigma$  should be minimized so we take the equal sign of (3.16). Then (3.13) and (3.14) can be solved as

$$v_{1} = \frac{1}{2}V_{bus} \pm \sqrt{\frac{P_{dc}}{2\omega C_{s}cos\phi}} [sin(2\omega t + \phi) + \sigma] - \frac{1}{4}V_{bus}^{2}$$

$$= \frac{1}{2}V_{bus} \pm \sqrt{\frac{P_{dc}}{2\omega C_{s}cos\phi}} [sin(2\omega t + \phi) + 1 + \frac{CV_{bus}^{2}}{4\frac{P_{dc}}{\omega C_{s}cos\phi}}] - \frac{1}{4}V_{bus}^{2}$$

$$= \frac{1}{2}V_{bus} \pm \sqrt{\frac{P_{dc}}{2\omega C_{s}cos\phi}} [sin(2\omega t + \phi) + 1]$$

$$= \frac{1}{2}V_{bus} + \sqrt{\frac{P_{dc}}{\omega C_{s}cos\phi}} [cos(\omega t + \frac{\phi}{2} + \frac{3\pi}{4})], \qquad (3.17)$$

$$v_{2} = V_{bus} - v_{1}$$

$$= \frac{1}{2}V_{bus} - \sqrt{\frac{P_{dc}}{\omega C_{s}cos\phi}} [cos(\omega t + \frac{\phi}{2} + \frac{3\pi}{4})]. \qquad (3.18)$$

The current through the filter inductor,  $i_L$ , is given as

$$i_{L} = i_{2} - i_{1} = C_{s} \frac{dv_{2}}{dt} - C_{s} \frac{dv_{1}}{dt}$$

$$= \sqrt{\frac{4\omega C_{s} P_{dc}}{\cos \phi}} \left[ \sin(\omega t + \frac{\phi}{2} - \frac{\pi}{4}) \right]. \tag{3.19}$$

The waveforms of  $v_1$ ,  $v_2$  and  $i_L$  are shown in Fig. 3.7b. The magnitude of the capacitor voltage is adjusted through the choice of  $C_s$ . Due to the buck topology,  $v_1$  and  $v_2$  must be lower than  $V_{bus}$ , i.e.,

$$\sqrt{\frac{P_{dc}}{\omega C_s cos \phi}} \leqslant \frac{1}{2} V_{bus}. \tag{3.20}$$

When the equal sign in (3.20) is taken, the highest EUR of 25% for this buffer cell structure is achieved. The minimum value of  $C_s$  is 132  $\mu$ F (rated at 400 V) considering the little box challenge design example. As shown in Fig. 3.7b, both the current and voltage of the capacitors are smooth 60 Hz waveforms with no harmonics. However, the current flowing through the filter inductor is very large, resulting in high TSS and IVI.

Figure 3.7: Schematic and operating waveforms of the half-bridge split-capacitor cell;  $C_1 = C_2 = C_s = 200 \ \mu F$  used to plot the waveform.

#### 3.3.5 Analysis and comparison

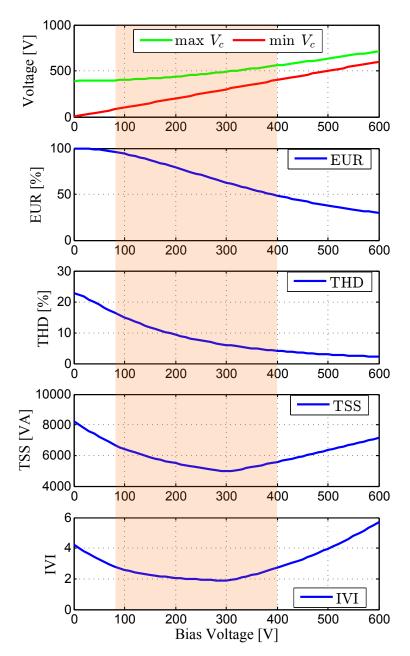

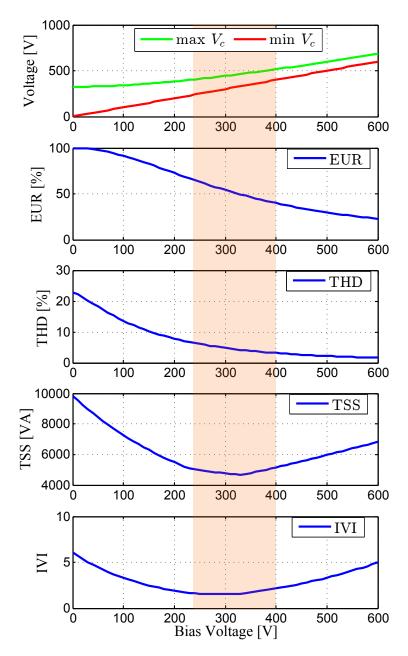

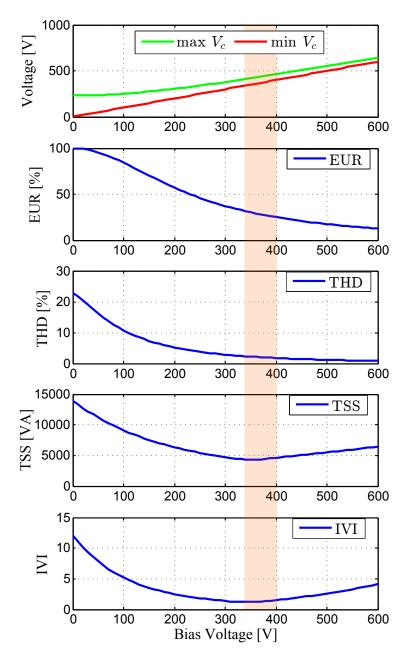

The performance metrics of all the aforementioned buffer cells are summarized in Table 3.1. For half-bridge buck converter and half-bridge boost converter, these metrics are dependent on the DC bias voltage on the energy storage capacitor as well as the capacitance. The performance metrics as a function of DC bias voltage is plotted in Figs. 3.8 to 3.10 for the difference values of  $C_s$ . As the DC bias voltage increase, the EUR decreases, and the THD in the signal decreases as well as the voltage and current becomes smoother and smoother as shown in Fig. 3.5b and Fig. 3.6b. The TSS and IVI first decrease with DC bias voltage for the buck cell as the current stress in the converter decreases, and increase with DC bias voltage for the boost cell as the voltage stress increases. Note that a certain range of bias voltage DC bias voltage (marked by colored area in Fig. 3.8 to Fig. 3.10) is not viable with either buck or boost converter because it results in capacitor voltage both above and below bus voltage. The minimum point of TSS and IVI on the curve is at the left boundary point, which corresponds to the point where in buck configuration the highest voltage on the energy storage capacitor within a cycle is exactly the bus voltage.

The results in Table 3.1 and Figs. 3.8 to 3.10 reveal the tradeoff between EUR and other performance metrics. While EUR is the motivation to study active decoupling, the buffer structure with 100% EUR will not give the smallest overall size due to the large volume of inductors and power loss of the converter. The full-bridge buck cell has the best EUR but relatively large TSS and IVI. The half-bridge split-capacitor cell aims at reducing the

Table 3.1: Performance metrics of various buffer cells calculated with the little box challenge design example

| Buffer cell                                                            | max EUR                                 | min<br>current<br>stress | min<br>voltage<br>stress | min TSS                     | IVI             | THD             | capacitor<br>polarity |

|------------------------------------------------------------------------|-----------------------------------------|--------------------------|--------------------------|-----------------------------|-----------------|-----------------|-----------------------|

| full-bridge buck                                                       | 100%                                    | 10 A                     | 400 V                    | $4{\times}4000~\mathrm{VA}$ | 4               | 0               | bipolar               |

| half-bridge buck                                                       | about 100% to<br>15%, , see<br>Fig. 3.8 | ≤10 A                    | 400 V                    | see Fig. 3.8                | see<br>Fig. 3.8 | see<br>Fig. 3.8 | unipolar              |

| half-bridge boost                                                      | about 15% to 0%, see Fig. 3.8           | 10 A                     | ≽400 V                   | see Fig. 3.8                | see<br>Fig. 3.8 | see<br>Fig. 3.8 | unipolar              |

| half-bridge<br>split-capacitor                                         | 25%                                     | 20 A                     | 400 V                    | 2×8000 VA                   | 16              | 0               | unipolar              |

| Stacked<br>switched-capacitor<br>cell                                  | about 10% to 50%, see Fig. 3.12         | 5 A                      | ≪400 V                   | high                        | NA              | NA              | bipolar               |

| Series-connected (for<br>parameters in<br>Fig. 3.15, not<br>optimized) | 33.6%                                   | 5 A                      | 100 V                    | $4 \times 500 \text{ VA}$   | 0.0156          | 0               | unipolar              |

| Series-stacked (for<br>parameters in<br>Sec. 4.2, not<br>optimized)    | 42%                                     | 5 A                      | 90 V                     | $4 \times 450 \text{ VA}$   | 0.0114          | 0               | unipolar              |

switch count of the full-bridge buck cell but actually has worse performance metrics. The half-bridge buck cell and half-bridge boost cell allow for flexibility in adjusting the balance between EUR and other parameters and the right tradeoff will result in the smallest volume among all parallel connected cells. However, harmonics in the voltage and current signal remains a control challenge for these structures.

Certain variations of the parallel-connected cells might offer small advantages over other variations, but parallel-connected cells in general suffer severe problems. The buffer converter is directly connected to the DC bus and thus under that full voltage stress of the DC bus voltage. Consequently, for the added buffer converter, high-voltage, relatively slow-switching transistors have to be used, which limits the achievable switching frequency, leading to a large filter inductor,  $L_f$ . In other words, the voltage stress of the parallel-connected cells is lower bounded by the bus voltage and the current stress is lower bounded by the DC current. Therefore, it is not possible to build a parallel connected cell with IVI < 1 or TSS <  $V_{bus} \times I_{dc}$ . Note that as discussed in Section 2.2, the energy density of inductors are 500 to 1000 times lower than that of capacitors. The volume reduction from the smaller energy storage capacitor is often offset by the volume overhead introduced by the buffer converter itself. Most comparable parallel connected cell design in the literature [38,41,51–54] have filter inductors on the order of several mH, resulting in a very large inductor volume.

Figure 3.8: Voltage swing range of the energy storage capacitor, EUR, THD, TSS and IVI of half-bridge buck cell and half-bridge boost cell as a function of DC bias voltage in the energy storage capacitor. These plots are generated with  $C_s = 70~\mu\text{F}$ .

Another major limitation of parallel-connected cells is the efficiency penalty incurred by the buffer converter. As illustrated in (2.1), an average of  $\frac{2}{\pi}P_{ave}$  power pulsation is flowing into and then out of the buffer cell in each cycle. Therefore, to the first order, the overall

Figure 3.9: Voltage swing range of the energy storage capacitor, EUR, THD, TSS and IVI of half-bridge buck cell and half-bridge boost cell as a function of DC bias voltage in the energy storage capacitor. These plots are generated with  $C_s = 100 \ \mu\text{F}$ .

efficiency of the entire AC-DC converter is approximately

$$\eta \approx \eta_{main} - \frac{2}{\pi} \underbrace{(1 - \eta_{buf})}_{\text{efficiency penalty}},$$

(3.21)

where  $\eta_{main}$  is the efficiency of the inversion/rectification stage and  $\eta_{buf}$  is the efficiency

Figure 3.10: Voltage swing range of the energy storage capacitor, EUR, THD, TSS and IVI of half-bridge buck cell and half-bridge boost cell as a function of DC bias voltage in the energy storage capacitor. These plots are generated with  $C_s = 200 \ \mu\text{F}$ .

of the buffer converter. Even if the buffer converter can be made efficient through careful design (which is challenging given the high TSS), since it is processing a large portion of the total power, it can still incur significant power loss. High power loss typically results in larger heat sinking devices (heat sink and fans), which further undermine the goal of high power density.

Figure 3.11: Schematic of a stacked switched capacitor cell [13, 44]. Note there are n backbone capacitors mainly for energy storage and m supporting capacitors mainly for voltage regulation.

To summarize this analysis, EUR is typically not the most important metric when designing for high power density. Since inductor volume often dominates the overall volume, it is more important to design for low TSS and IVI while maintaining a reasonable EUR. The buffer cells to be discussed next follows this method.

### 3.4 Stacked switched-capacitor cell

An alternative approach to magnetic-based parallel-connected cells is the stacked switched-capacitor (SSC) buffer [13, 44]. One embodiment of the SSC buffer is shown in Fig. 3.11, which consist of two backbone capacitors and six supporting capacitors. The operation of the SSC buffer is very involved and interested readers are referred to [13] for details.

On a very high level, the SSC buffer consists of an array of capacitors and switches. As the capacitors charge and discharge, the SSC buffer reconfigures the array in different series and parallel combinations to regulate the DC bus voltage. Obviously, this configuration is free of magnetic components, so large inductor volume is no longer a concern. Compared to a magnetic-based converter that continuously processes the buffer power, the SSC buffer takes advantage of the natural stacking of capacitor voltages to maintain the DC bus voltage and only exercises the switches a few times in each line cycle to adjust the stacking. Hence, the power loss associated with the SSC architecture is greatly reduced.

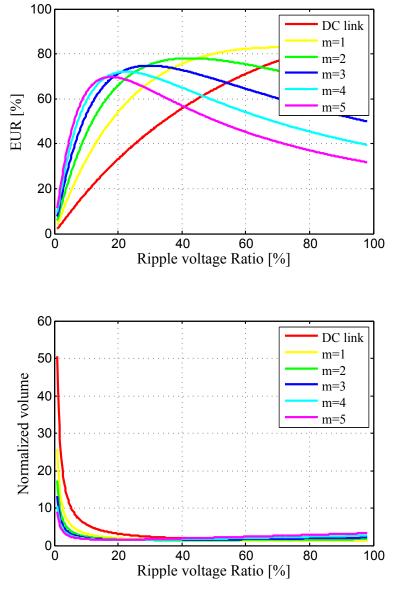

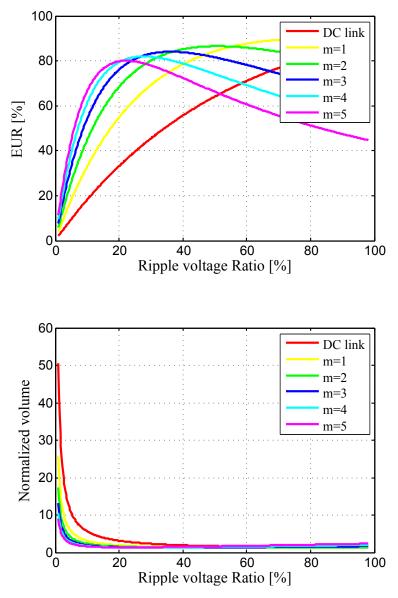

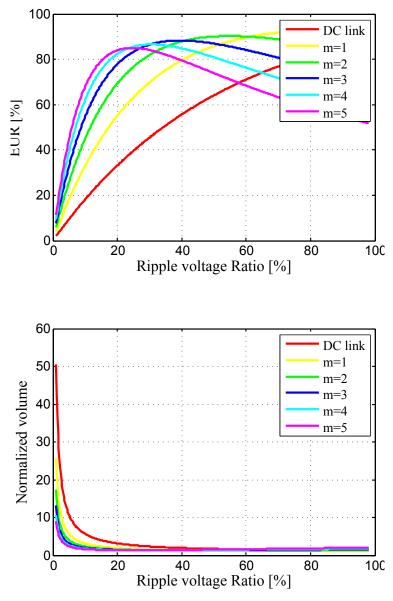

Figure 3.12: The energy utilization ratio (EUR) and SSC capacitor volume (normalized over the volume at 100% EUR with passive DC link capacitor) as a function of the ripple voltage ratio on the DC bus. The number of backbone capacitors is one and the number of supporting capacitors is m shown in the legend. The EUR and normalized volume of passive DC link capacitor solution is plotted as a reference.

While magnetic-based parallel-connected cells can theoretically eliminate the DC bus ripple completely, SSC only limits the ripple to certain percentage by design. Therefore, similar to the passive DC link capacitor decoupling, the EUR of SSC is limited by the allowed ripple on the DC bus. The EUR and normalized capacitor as a function of the allowed ripple on the DC bus is plotted in Figs. 3.12 to 3.14 for different number of backbone and supporting capacitors. SSC offers significant improvement over passive DC link capacitor, but the EUR

Figure 3.13: The energy utilization ratio (EUR) and SSC capacitor volume (normalized over the volume at 100% EUR with passive DC link capacitor) as a function of the ripple voltage ratio on the DC bus. The number of backbone capacitors is two and the number of supporting capacitors is m shown in the legend. The EUR and normalized volume of passive DC link capacitor solution is plotted as a reference.

is relatively low when only a small ripple is allowed on the DC bus. This is because the configurations of SSC are discrete in nature, so the bus voltage experiences a discontinuous jump whenever the SSC reconfigures. To meet a strict ripple requirement (e.g., a few percent), a complicated circuit with a large number of backbone and supporting capacitors has to be built. The total switch count of SSC is given as n+m+4, so the number of transistors is large, leading to a high TSS although the voltage stress on each individual transistor is

Figure 3.14: The energy utilization ratio (EUR) and SSC capacitor volume (normalized over the volume at 100% EUR with passive DC link capacitor) as a function of the ripple voltage ratio on the DC bus. The number of backbone capacitors is three and the number of supporting capacitors is m shown in the legend. The EUR and normalized volume of passive DC link capacitor solution is plotted as a reference.

reduced compared to magnetic-based parallel connected cells. Therefore, despite the fact that no inductor is needed in SSC, the large number of switches and their auxiliary circuits (i.e., the signal level shifting and gate driving circuit) occupy a large PCB area, undermining the goal of high energy density. The above analysis is summarized in Table 3.1.

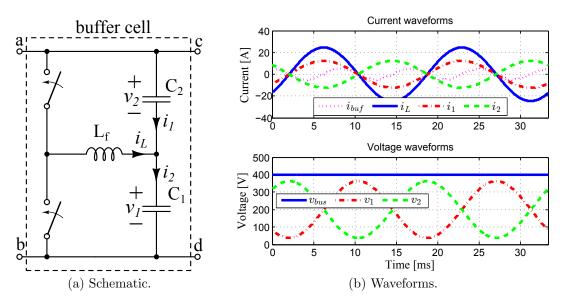

# 3.5 Series-connected cell

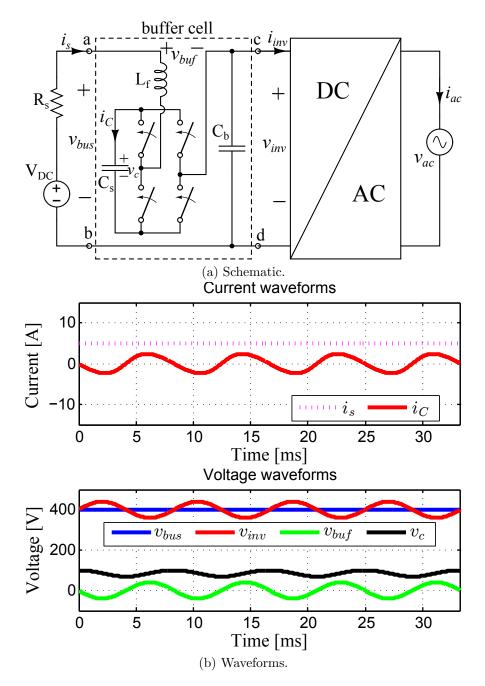

Figure 3.15: Schematic and operating waveforms of the series connected cell (series voltage compensator in [58, 59]). The waveform is simulated with  $C_s = 200~\mu\text{F}$  and  $C_b = 150~\mu\text{F}$ . The DC bias on  $C_s$  is 100 V.

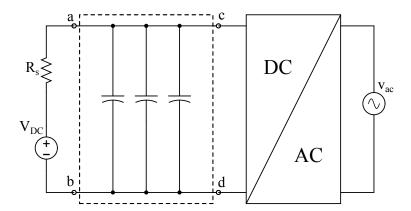

Despite the negative impact on the volume, inductors are generally necessary in active decoupling buffers to continuously regulate the bus voltage and minimize ripple. However, if we want to avoid high voltage stress on the inductor, the buffer converter cannot be

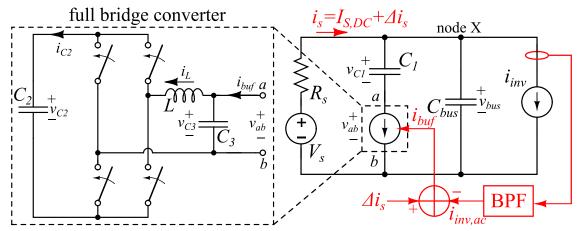

connected across the DC bus. A series-connected buffer cell is proposed [58, 59] as shown in Fig. 3.15a. For the parallel-connected cell and SSC cell, the inversion stage is directly interfaced with the DC bus, i.e.,  $v_{inv} = v_{bus} = v_{buf}$  in Fig. 3.15; series-connected cell, however, is connected in series with the inverter, i.e.,  $v_{bus} = v_{buf} + v_{inv}$ . The bulk energy storage capacitor,  $C_b$ , is allowed to have a relatively large ripple to improve EUR, while the a seriesconnected full-bridge converter with a supporting capacitor,  $C_s$ , changes its output voltage  $v_{buf}$  complimentary to the ripple on  $C_b$  (the ripple in  $v_{inv}$ ), such that the DC bus voltage is maintained constant, as shown in Fig. 3.15b. Note that this is similar to SSC in the sense that the stacking of two capacitors with complimentary voltage maintains the bus voltage.  $C_b$  is similar to the backbone capacitors and  $C_s$  is similar to the supporting capacitors in SCC. The difference is that now the voltage of  $C_s$  is regulated through a full-bridge converter instead of directly stacking on top of  $C_b$ , so very smooth and continuous regulation can be achieved. The series connection of the buffer converter allows the buffer converter to see only the voltage ripple magnitude, so the voltage stress on the buffer converter and its inductor is greatly reduced. Moreover, the buffer converter only process the power corresponding to the ripple voltage, so the efficiency penalty on the overall system is also reduced. The performance metrics calculated for the series-connected cell is listed in Table 3.1. Note that this result is calculated for the particular parameter selection given in Fig. 3.15, which has not been optimized. Even so, series-connected cells have shown superior performance especially on TSS and IVI. A systematic procedure to optimized series-connected cell is still an area of ongoing research.

Note that this configuration does affect the operation of the inversion stage to some extent. The input to the DC side of the inversion stage is no longer a constant DC but with a large 120 Hz waveform. This by itself is usually not a problem if the control loop of the inversion stage has enough bandwidth. However, the voltage on the DC side has to be always higher than the AC side on an H-bridge converter. This means the voltage swing on  $C_b$  is limited. For example, for the little box challenge design, the voltage amplitude of the AC output has to be 340 V. This effectively limits the voltage swing of  $C_b$  to only 60 V above and below the 400 V bus, as shown in Fig. 3.15b. Therefore, although series-connected cell offers some flexibility to tradeoff EUR for TSS and IVI, the range of tradeoff is limited. If the headroom between AC side voltage and DC side voltage is smaller due to system requirements (e.g., some PFC front ends under extreme cases may take high line voltage of 264 V RMS AC and output 375 V DC), then the room left for series-connected optimization might be too small. After all, the ripple is only reduced on one side while the other side that is directly connected to the capacitor lacks voltage regulation, which is unacceptable in many applications.

### 3.6 Dependent decoupling buffer

All the aforementioned buffer solutions in this chapter are classified as "independent decoupling" as their operation is independent of the AC/DC converter operation. The "independent decoupling" buffers, despite their topological variations, all serve as an inherently "add-on" component to the converter system. This "add-on" characteristics determines that all "independent decoupling" buffers suffer at least from two shortcomings: the buffer stage requires extra active components to build (i.e., increased active component count, not only the power transistors but also components for control implementation); the buffer stage will always reduce the overall efficiency of the system (despite the fact that this efficiency reduction might be very small, as in the series-stacked buffer architecture to be presented).

Another class of active buffer solutions, referred to as "dependent decoupling" here, has been proposed to solve these shortcomings. This class of solutions feature the integration of the active buffer hardware and control into the inversion/rectification stage, to reduce the switch count and to improve the overall efficiency. Now since the two parts are merged, their control and operation are no longer independent but tightly coupled, thus referred to as "dependent decoupling".

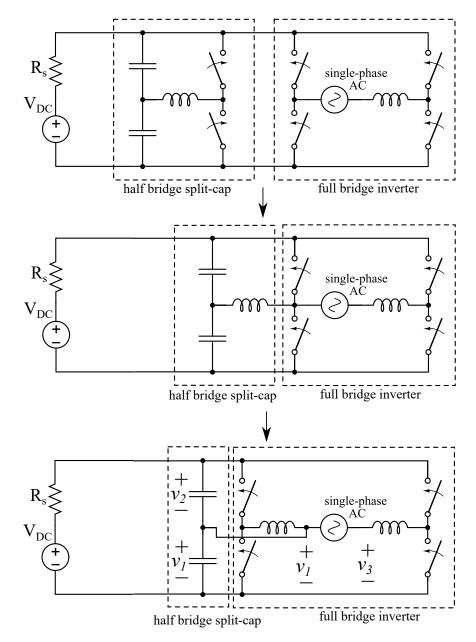

"Dependent decoupling" is closely related to "independent decoupling" in terms of circuit structure. In fact, one can often derived a "dependent decoupling" structure from its "independent decoupling" counterpart, or vice versa. This derivation is often referred to as multiplexing. As an example, one can start with a half-bridge split-cap buffer cell and a full-bridge inverter given in Fig. 3.16; the adjacent two half-bridge structures in the buffer cell and full-bridge inverter has certain hardware redundancy and can be multiplexed together. Furthermore, the inductor in the full-bridge inverter can split into two halves (same in total inductance and inductor volume) and one-half can be shared with the buffer cell to eliminate the original buffer cell inductor. The resulting structure has been proposed in [41,43] and referred to as active-filter-integration (AFI). The operation and control of AFI has been well studied and interested readers are referred to [43] for details. It has been shown in [43] that unlike "dependent decoupling" buffers that always reduce the overall system efficiency, AFI can actually improve the system efficiency at heavy load range, although it still reduces system efficiency at light load range.

Although the operation of "dependent decoupling" solutions will not be discussed in detail, it should be pointed out that the reduced component count in these structures comes at the cost of reduced operation flexibility. The essence of "dependent decoupling" is to modulate the common mode voltage of the AC output. The energy storage capacitor is moved to the output to be charged and discharged by the common mode voltage to provide energy

Figure 3.16: Step-by-step derivation of a dependent decoupling buffer structure from a half-bridge split-cap independent decoupling solution.

buffering. This means that the output common mode voltage is fully determined by the buffering requirement and is no longer an extra degree of freedom in the design. Recall that in full-bridge inverter it is preferable to set the common mode output voltage to zero to reduce the voltage stress as well as common mode EMI. Now with the common mode voltage used for energy buffering, the DC bus voltage must be raised to a higher value to allow enough headroom for the AC output waveform.

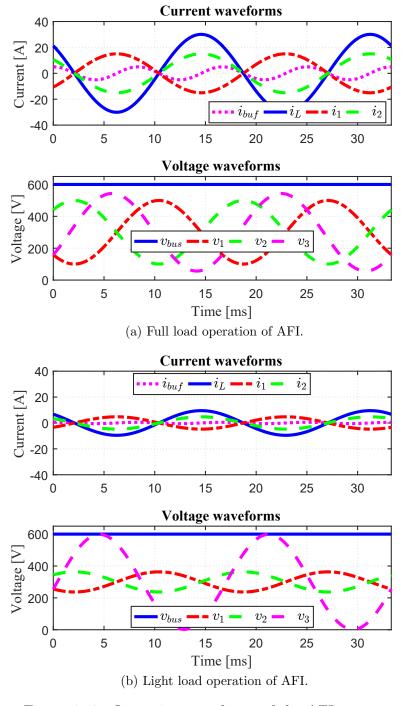

Take the AFI structure as an example, whose operation waveform is plotted in Fig. 3.17.