# INVESTIGATION OF SYSTEM-LEVEL ESD INDUCED SOFT FAILURES

BY

# NICHOLAS ADAM THOMSON

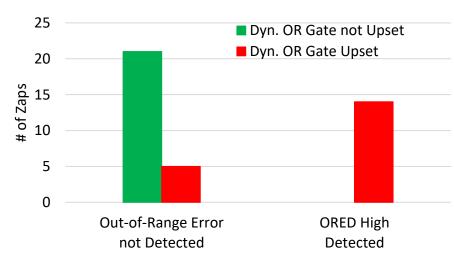

# DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2017

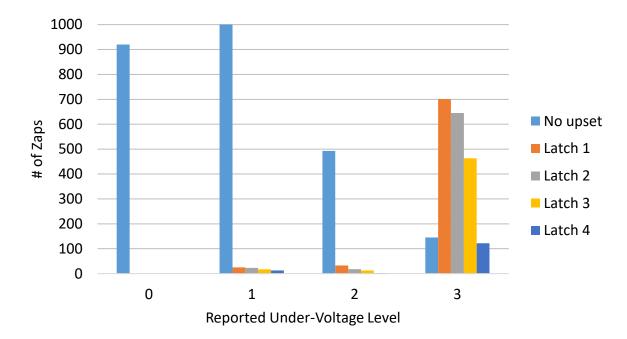

Urbana, Illinois

Doctoral Committee:

Professor Elyse Rosenbaum, Chair Professor Deming Chen Assistant Professor Songbin Gong Professor José Schutt-Ainé

## ABSTRACT

Electrostatic discharge (ESD) is a common phenomenon that can have negative implications for the performance of systems during operation. ESD is a brief, high-current stress that when applied to a functional system, can cause a variety of problems ranging from temporary system malfunction to permanent failure of components within the system and/or the system itself. Permanent failure of components, also known as hard failure, is a well-studied area among the ESD community with established practices in place for mitigating the stress and improving the reliability of the system. While further improvements with regard to hard-failure protection can always be made, this work will focus on the aspects of soft failures. Soft failures encompass any type of disruption to the system that, in general, can be recovered from, for example by powercycling the system. An example of a soft failure could be the erasure of data within some memory elements of an embedded computer that cause programmed routines to fail. By restarting the system, the data will be regenerated and written into the memory elements and proper functionality is returned. While seemingly innocuous, the temporary failure of crucial systems, for example medical or automotive systems, could lead to severe consequences. This dissertation surveys the type of sensitive logic that could be susceptible to soft failures. Custom hardware which utilizes these elements has been designed and fabricated. Experiments with this hardware has yielded evidence of soft failures and lead to a preliminary understanding of the mechanisms responsible for those soft failures. While strong support for these hypothesized mechanisms has been obtained, future work must be completed to ascertain the validity of the conclusions drawn from the preliminary results.

ii

# TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION                         |    |

|-------------------------------------------------|----|

| CHAPTER 2: CHIP-BOARD ESD PROTECTION            |    |

| 2.1 IO Protection                               | 5  |

| 2.2 Supply-Rail Protection                      | 6  |

| 2.3 Board Protection                            |    |

| CHAPTER 3: SYSTEM-LEVEL TESTING                 | 10 |

| 3.1 IEC 61000-4-2 Test Setup                    |    |

| 3.2 Discharges to Mobile vs. Tethered Systems   |    |

| 3.3 Measurements during IEC 61000-4-2 Testing   |    |

| CHAPTER 4: SOFT FAILURES OBSERVED WITHIN AN EUT |    |

| 4.1 Test Chip 1 Overview                        |    |

| 4.2 Test System 1 Overview                      |    |

| 4.3 IEC 61000-4-2 Testing of Functional System  |    |

| 4.3.1 Glitches on Signal Lines                  |    |

| 4.3.2 Static Latch Upsets                       |    |

| 4.3.3 Upsets in Dynamic Logic                   |    |

| 4.3.4 Bit Flips in the Shift-Register           |    |

| 4.3.5 Upsets to USB Functionality               |    |

| 4.3.5 Hard Failures                             |    |

| CHAPTER 5: ADVANCED NOISE MONITORS              |    |

| 5.1 New Test Chip Overview                      |    |

| 5.1.1 Supply-Voltage Monitors                   |    |

| 5.1.2 Static Latches                                  |     |

|-------------------------------------------------------|-----|

| 5.1.3 Dynamic OR Gates                                |     |

| 5.1.4 Shift-Registers                                 | 74  |

| 5.2 Circuit Board and Test Set-Up Designs             | 77  |

| 5.3 IEC 61000-4-2 Testing of New Test System          |     |

| 5.3.1 Power Supply Noise Detected by Voltage Monitors |     |

| 5.3.2 Static Latch Upsets                             |     |

| 5.3.3 Bit Flips Due to Input Glitches                 |     |

| 5.3.4 Effects of Reduced Supply Voltage               | 102 |

| 5.3.5 Zaps to a Protected System                      |     |

| CHAPTER 6: FUTURE WORK                                | 108 |

| REFERENCES                                            | 110 |

# **CHAPTER 1:**

# **INTRODUCTION**

Semiconductor devices may be subjected to electrostatic discharge (ESD) many different times during their fabrication, packaging, handling, installation, and use [1]. ESD is a brief stress on the device that can last hundreds of nanoseconds with current amplitudes reaching tens of amps. So much current being shunted through the semiconductor device causes heating that can lead to thermal failure. This current may also create potential differences on the device that can damage gate dielectrics of metal-oxide-semiconductor (MOS) structures. Because of this, devices must be designed to withstand ESD.

Typically, dedicated ESD protection devices are added to a system. These protection devices are placed within a semiconductor device, on a printed circuit-board within the system, or at both locations. Deciding where to place ESD protection is not straightforward. This ESD device needs to be sized large enough to handle the current levels that result at the targeted ESD level. Placing large devices on-chip results in additional area requirements that increase the costs of the integrate-circuit. Placing stand-alone protection devices on the printed-circuit board (PCB) requires additional parts to be ordered and large PCB area to accommodate the product. Minimizing the total system cost may lead to discontent between integrated-circuit (IC) manufacturers and system designers. Thus it is important to understand how the ESD stress propagates through the system and to identify potential vulnerabilities. This will allow the smallest amount of protection that is sufficient for adequate device operation during an ESD event.

Failure to adequately protect against the ESD stress can result in two types of failures: hard failure or soft failure. Hard failures are permanent catastrophic failure of the device. Hard failures have long been studied and mature methodologies for protection have been developed.

Soft failures represent a relatively new challenge to ESD designers. A soft failure is a type of disturbance to a system that is recoverable [2]. These could include erasure of data stored in a memory element that results in an inability of the system to continue operating, or the failure of an input/output (IO) cell to properly read in logical values. Due to the proliferation of embedded computers and sequential-logic, soft failures have quickly become a topic of interest in the ESD community. Some industries, e.g. automotive or medical, have a strict intolerance to soft failure [3]. In these industries, a soft failure could result in a temporary system failure that leads to a safety hazard.

Since large amplitude current or voltage is typically required to cause hard failures, direct current injection usually causes hard failures to occur along the main discharge current path. Thus, hard failures have traditionally been studied on the component level. This could mean that unpackaged wafers are probed and ESD current is injected, or the leads of package parts could be probed and stressed. Standards such as Human-Body Model (HBM) [4], and Charged-Device Model (CDM) [5] exist for characterizing a component's hard-failure level resulting from different ESD stresses. However, soft failures can occur from logic-level switching and thus could appear due to noise that couples to logic from distant zaps. For this reason, studying soft failures within a component under direct ESD injection is not sufficient. The interactions of several components within a functioning system must be considered. A system, in this context, is a functioning device that may consists of several packaged components on multiple PCB. Interconnects between components and ESD could be the means of coupling noise. Thus, system-

level ESD-generated soft failures are not necessarily restricted to devices along the main discharge path. Soft failures could result at any location within a semiconductor due to power noise generated at one IO.

In [6] a system is characterized for susceptibility to soft failures by scanning a probe across a test system while applying a stress in the form of radiated fields. This method allows for sensitive signal traces to be identified, but lacks the sensitivity required to localize the source of soft failures within an IC. Further, this method does not apply a stress to the system that is compatible with the widely used standard for system-level ESD testing (IEC 61000-4-2 [7]) and thus may not reflect the soft failures that would occur during such a test. In [8] and [9], a test system is stressed with injected ESD current while various traces are directly probed with a voltage probe. While this technique could be adapted to work with the IEC 61000-4-2 standard, the scope is once again limited to board-level analysis as it is impractical to probe traces within an IC. Also, the use of conductive probes will tether the system to earth ground which in turn can greatly affect the current path and lead to unrealistic upsets. In [10] and [11] direct probing was used in conjunction with accurate IC modeling to glean insight into what is occurring on the IC. However, this method still suffers from system alterations required for direct probing. In [12] a custom IC was fabricated with a high-speed oscilloscope incorporated on die. This method does allow on-chip noise waveforms to be measured, as opposed to the previous measurement practices. However, the test chip and test system used are highly specialized and thus not suitable for use outside of dedicated experimental work.

This work attempts to observe soft failures within a test system and uncover the mechanisms that cause these failures at the board and IC levels. Methods used within this work will strive to preserve the integrity of the testing standards and be applicable to all types of test

systems by avoiding the addition of conductive tethers to the test system and by avoiding the use of external measurement equipment during ESD testing.

## **CHAPTER 2:**

# **CHIP-BOARD ESD PROTECTION**

An important topic when evaluating any ESD failure is the method that was used to protect the various devices within the system from the ESD stress. Protection elements could be circuits within components, stand-alone circuits on a PCB, or discrete devices placed at key locations. The protection devices control the flow of current through the system and thus impact what failure mechanisms could arise. This chapter will introduce the various protection elements used within this work.

#### 2.1 IO Protection

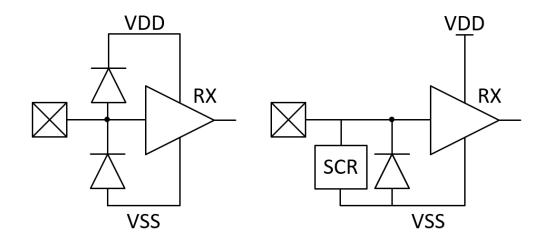

If ESD current reaches an integrated circuit (IC, chip) within a system, that current may enter into that component. If it enters through an IO, ESD protection devices are included to shunt that current away from the sensitive IO circuitry and clamp the ESD voltage to safe levels. In this work, diodes and silicon-controlled rectifiers (SCR) are used. Figure 1 illustrates the use of dualdiode (DD) protection on the left and SCR protection on the right.

Figure 1: Schematic representation of dual-diode (DD) protection (left) and SCR protection (right).

Dual-diode (DD) protection consists of a "top diode" placed between the positive supply rail (VDD) and the IO and a "bottom diode" placed between the IO and the ground rail (VSS). With this configuration positive stress with respect to VDD will turn on the top diode and current will be shunted to the VDD rail away from the sensitive receiver (RX) circuitry. Similarly, for negative stress with respect to VSS will turn on the bottom diode and shunt current to VSS. SCR protection utilizes an SCR with some triggering circuit which will turn on the main protection device once the IO-to-VSS voltage achieves the designed threshold voltage. Thus, the SCR protects against positive ESD stress with respect to VSS. For negative stress with respect to VSS the "reverse-diode" will turn on and shunt the current. The SCR has a parasitic diode associated with its layout that will act as a reverse-diode, however, additional PN junctions can be added to augment the parasitic diode.

#### 2.2 Supply-Rail Protection

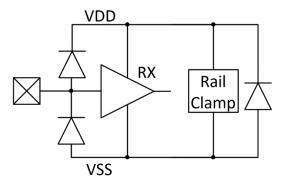

Dual-diode and SCR protection elements shunt current to the supply rails, but an additional protection device must be included to maintain the chip's power-supply voltage or chip-wide damage could result. Further, for component-level ESD, ESD stress can be applied between any IO, VDD, or VSS pin. Thus, for a positive stress applied between an IO and VSS, for example, DD protection will shunt the stress up to VDD, but cannot supply a return path to VSS. To satisfy these needs a rail clamp is used. Figure 2 depicts DD protection with the rail clamp between the power supply rails. When the rail clamp turns on, it shunts current from the VDD rail to the VSS rail. The parasitic diodes associated with all N-well and P-substrate contacts act together with any ESD diode placed between VDD and VSS to shunt current from VSS to VDD when required. The rail clamp also acts as the main protection device for stress injected between the chip's power-supply pins.

Figure 2: DD ESD protection with rail clamp.

In many ICs, several power domains are used to power different types of circuit blocks. For example, the IO ring of a chip may be powered with a higher voltage than the core circuitry. Further, the core logic may also have several domains to isolate the noise generated from fastswitching digital logic from the power supply used for analog circuitry. To ensure noise isolation, the references for these different domains must also be isolated. Having separate references can cause vulnerabilities for ESD stress. For example, if the power-supply pin for the IO domain is stressed with respect to the reference for core-logic domain, there is no dedicated path for that ESD current to pass from one domain to the other. Thus the current would likely cause a failure as it creates a path through the substrate. Anti-parallel diodes (APD) are used in this situation to allow a path between the reference nets of various power domains. Figure 3 illustrates a complete on-chip ESD protection strategy with APD. The APD allows current to flow in either direction once a potential difference develops between the two supply-domain reference-nets that is large enough to forward bias one of the diodes. Small magnitude noise will be insufficient to turn on a diode, allowing it to be isolated from the other net. During an ESD event, any potential difference between the two nets will turn on a diode before it becomes large enough to cause breakdown within the chip. The current flow will allow the potentials to equalize within safe levels.

Figure 3: Cross-domain ESD protection. The APD circuit allows current to flow, in either direction, once a large enough potential difference develops between two domain reference nets.

#### 2.3 Board Protection

So far only on-chip protection has been discussed. Stand-alone protection devices can be placed on the same printed circuit-board (PCB) as the main IC. These protection devices work to shunt current away from other sensitive devices on the PCB and reduce the stress seen by those devices. By using on-board protection, chip-level protection can be reduced (not removed) and free up the costly silicon area for other uses. A common dedicated on-board protection element is the transient voltage suppressor (TVS). For ESD applications, the TVS is usually made up of diodes. Shunt paths can be placed between the IO to be protected and board ground, board power, or both. Further, TVS devices can have unidirectional or bidirectional shunt paths. One example of a bidirectional shunt from the IO signal line to board ground is a Zener diode. During a positive ESD stress injected into the board IO trace with respect to ground, the Zener diode will turn on and start shunting current to ground once the breakdown voltage of the Zener diode is reached. For a negative zap, the diode will conduct once it is forward biased.

TVS diodes are selected based on their topology, ESD protection rating, and their input capacitance. The TVS topology dictates what stresses can be protected against. For example, a TVS between an IO and board ground cannot protect against a stress between the IO and the board power-supply unless other shunt paths exist between the board power-supply and the board ground. The ESD protection rating is the maximum stress that the TVS is designed to handle without failure. Finally, the input capacitance limits the types of signal lines the TVS can be placed at. Small form-factor TVS with very low input capacitance (< 1 pF) are useful for high-speed signal lines where larger devices with higher capacitance may only be suitable for low-speed lines.

#### **CHAPTER 3:**

# SYSTEM-LEVEL TESTING

As mentioned in Chapter 1, system-level testing is required for the study of soft failures. Soft failures are, by definition, interruptions to a system that is functional. Several standards have been developed for system-level ESD testing. This work will focus on the International Electrotechnical Commission (IEC) 61000-4-2 standard [7]. This standard is widely used for the study of ESD to portable devices (such as cellphones, tablets, or laptops) as well as larger equipment (e.g. desktop computers).

#### 3.1 IEC 61000-4-2 Test Setup

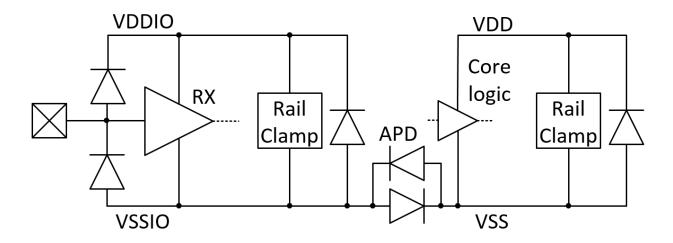

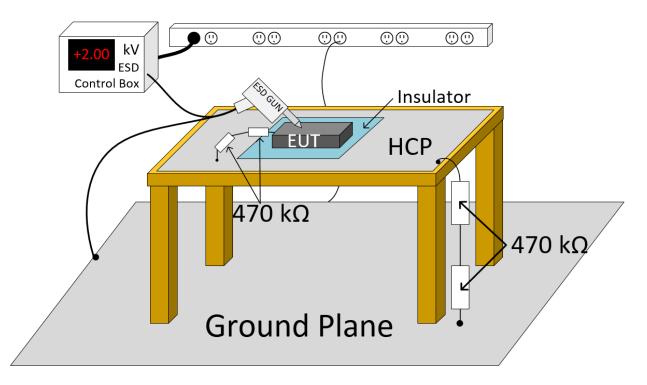

The IEC 61000-4-2 test setup is shown in Figure 4. The test setup consists a horizontal coupling plane (HCP) elevated above a ground plane on top of a non-conducting table. The HCP is electrically isolated from the ground plane except for the inclusion of two 470 k $\Omega$  resistors. These resistors slowly bleed charge from the HCP to the ground plane after zaps, but prevent the majority of current from flowing between the HCP and ground plane during the ESD event. Similarly, when the equipment under test (EUT) is tested in a mobile configuration, two 470 k $\Omega$  resistors are included to bleed any stored charge from the EUT to the HCP. The ground plane is connected to earth ground via a connection to the building's power outlet as well as tied to the ESD generator's ground via the ground strap from the ESD gun.

The EUT is placed on the HCP atop an insulating sheet. The insulator prevents any electrical connection between exposed metal on the EUT and the HCP. It also provides a more robust dielectric between the EUT and the HCP. The EUT can, and should, be tested in all of its common use scenarios. Most importantly certain mobile devices should be tested in a truly mobile

fashion, i.e. with no electrical connection to any other equipment or ground, or in a tethered fashion, e.g. plugged into a charging apparatus that may supply a connection to ground. The differences between mobile and tethered setup and the effect it has on the discharge waveform will be presented in Section 3.2.

Figure 4: IEC 61000-4-2 test setup.

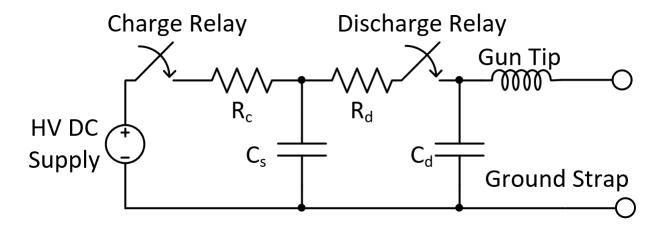

The ESD stress is applied via the ESD gun. The gun is charged from the HV ESD generator box and discharge via an internal relays when the gun is triggered. A simplified schematic of the gun's internal circuitry is shown in Figure 5. The HV DC supply represents the high-voltage supply within the ESD control box (see Figure 4). The storage capacitance,  $C_s$ , is charged through the charge relay and the charge resistance,  $R_c$ . Capacitance is also formed between the gun and objects in its surroundings. This capacitance, represented by  $C_d$ , will also charge along with  $C_s$ . When the gun is triggered, the discharge relay closes discharging  $C_s$  and  $C_d$

through the discrete discharge resistance,  $R_d$ , and out of the gun tip. An inductance associated with the gun tip is included. It is used to meet the risetime specifications.

Figure 5: Schematic of circuitry within the ESD gun.  $R_c$  is the charging resistance,  $R_d$  is the discharge resistance.  $C_s$  is the discrete storage capacitance within the gun.  $C_d$  represents the capacitance that exists between the gun and its surroundings.

Several types of testing are specified in [7]. Contact discharge is carried out by bringing the gun tip into contact with the EUT prior to triggering the gun. This is the most severe zap, with respect to hard failures, as the current from the gun is directed into the EUT. A second type of discharge is an air discharge. During and air discharge, the gun is triggered before making contact with the EUT. Subsequently the gun is brought into close proximity with the EUT until a discharge is detected. A third type of discharge is an indirect discharge. These stresses are performed by contact discharge to the vertical coupling plane (VCP; not shown in Figure 4), or HCP. Similar to the HCP, the VCP is an isolated conductor that is vertically oriented and placed near the EUT. Since contact discharge represent the most severe stress, they are the only discharges that have been studied up to this point. The number of tests, stress level, and location of testing depend on the discharge type being used. For this study, contact discharges have been applied up to the failure level of the EUT (determined through measurement) to system ground and to signal lines. Further the EUT should be tested in all realistic application scenarios. For this

reason the EUT in this study is subjected to stress in a mobile (battery-powered) and tethered (powered by a DC supply connected to the building's power supply) configurations.

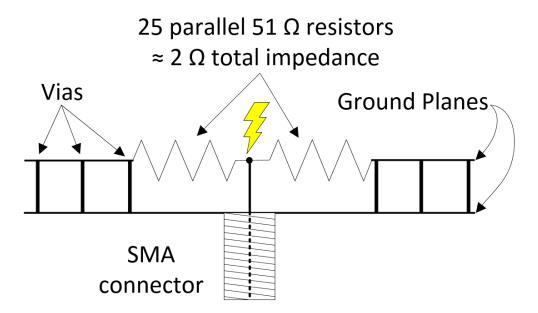

According to the specification [7], the waveform produced by the ESD apparatus is defined for zaps to a 2  $\Omega$  target. The target used in the standard is constructed of two concentric circular conductors separated by a resistive gap that provides the 2  $\Omega$  impedance. A 50  $\Omega$  conical adapter line is used to taper the form factor of the target down to a BNC connector, maintaining a 50  $\Omega$  characteristic impedance along its length. The voltage across the target is measured by an oscilloscope connected to the BNC connector. Since the ESD gun was professionally calibrated by the manufacturer a high-accuracy target is not needed for periodic verification of the ESD gun's calibration. Thus to avoid the high cost of a commercial calibration target, a simplified target was constructed for calibration verification. A cross section of the 2  $\Omega$  target manufactured for this study is illustrated in Figure 6.

Figure 6: Cross section of the 2  $\Omega$  target. The resistors represent a disk resistor with 2  $\Omega$  total impedance. The center of the disk resistor is the zap location and is connected to the center conductor of the SMA connector. The top and bottom ground planes are connected together with vias and are connected to the SMA connector's outer conductor.

The target was fabricated from a two-sided copper clad board. A circle was etched into the top copper and 25 51- $\Omega$  resistors were soldered around the circle to form approximately 2  $\Omega$  total resistance with low series inductance. An SMA connector was soldered on the backside with the center conductor passed through the board to the center of the etched circle and the outer conductor soldered to the bottom ground plane. An array of holes were drilled through the ground planes and wires were inserted to act as vias connecting the two planes.

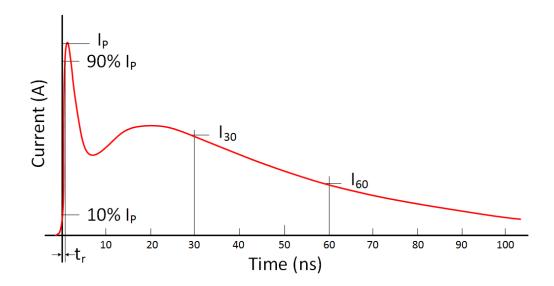

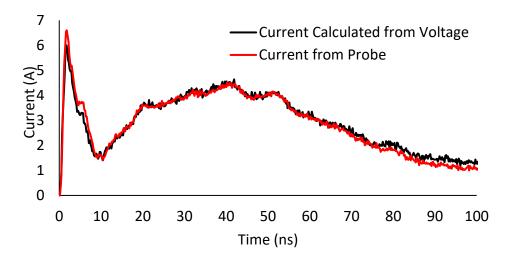

By connecting this SMA connector to an oscilloscope while zaps are applied to the center terminal, the discharge waveform from the gun can be captured. The standard recommends placing the oscilloscope inside a shielded enclosure, but this is not required unless measurements indicate that indirect coupling paths influence the calibration results. Figure 7 shows the waveform as defined by the specification and Figure 8 shows the waveform measured using the 2  $\Omega$  target. The parameters marked on the graph in Figure 7: I<sub>p</sub>, I<sub>30</sub>, I<sub>60</sub>, and t<sub>r</sub> are specified (within tolerances) by [7]. Table 1 indicates the values of these parameters for the four levels of contact discharge. Note that the zero reference for the time axis is defined as the point where the current waveform reaches 10 % of its peak (labeled as 10 % I<sub>p</sub> in Figure 7). As a rule of thumb, the peak current, I<sub>p</sub>, is 3.75 A/kV, the current at 30 ns, I<sub>30</sub>, is 2 A/kV, and the current at 60 ns, I<sub>60</sub>, is 1 A/kV. Comparing the waveforms of Figure 7 (illustrated) and Figure 8 indicate that the waveforms measured across the simplified 2  $\Omega$  target exhibit a similar shape, but have different time characteristics. These differences can be attributed to the simplifications made to the calibration setup.

Figure 7: Discharge waveform from the ESD gun into a 2  $\Omega$  target. Important values that are specified in the IEC 61000-4-2 standard have been marked.

Figure 8: Current calculated from the voltage measured across the 2  $\Omega$  target compared to the current measured with a current probe placed around the gun tip during a 2 kV discharge.

Table 1: Waveform parameters specified for contact discharge into a 2  $\Omega$  target.

| Level | Precharge Voltage     | First Peak Current | Rise Time                  | Current at 30 ns           | Current at 60 ns           |

|-------|-----------------------|--------------------|----------------------------|----------------------------|----------------------------|

|       | V <sub>pre</sub> (kV) | Ip (A), ±15 %      | t <sub>r</sub> (ns), ±25 % | I <sub>30</sub> (A), ±30 % | I <sub>60</sub> (A), ±30 % |

| 1     | 2                     | 7.5                | 0.8                        | 4                          | 2                          |

| 2     | 4                     | 15                 | 0.8                        | 8                          | 4                          |

| 3     | 6                     | 22.5               | 0.8                        | 12                         | 6                          |

| 4     | 8                     | 30                 | 0.8                        | 16                         | 8                          |

#### 3.2 Discharges to Mobile vs. Tethered Systems

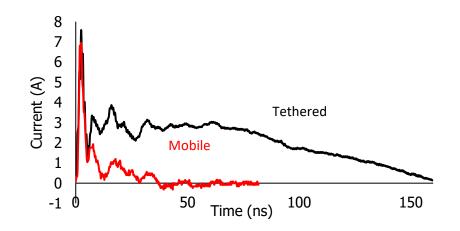

Since many systems today are designed to be completely mobile, testing needs to be carried out on systems in this configuration. On the flip side, mobile devices spend a good amount of time tethered to other devices, primarily for charging purposes. The design of a robust product thus requires that these systems be tested in a tethered configuration as well. While being produced from the same ESD gun, the waveforms delivered to a mobile system vary greatly from those delivered to a tethered system. Figure 9 shows the waveforms of discharges into a tethered and mobile EUT. The waveforms were measured using a current probe placed around the tip of the ESD gun during a 2 kV contact discharge. Measurement techniques will be discussed in more detail in Section 3.3. The two waveforms show a similar first peak, but vastly different second peak. The discharge path of the mobile device is simply made up of displacement currents between the EUT and the HCP or other surrounding objects. Since the capacitance associated with these objects is small, this discharge path has a high-pass filter characteristic. Thus only high-frequency components can travel to a mobile EUT. This can be seen in the mobile waveform of Figure 9 where the fast first peak and subsequent oscillations are observed. The first peak of the discharge waveform is similar to both the tethered and mobile EUT because the first peak is attributed to the parasitic capacitance between the gun and its surroundings ( $C_d$  in Figure 5), and the discharge path through displacement current which is common to both the tethered and mobile configurations.

The tether used to connect the EUT to the power supply is typically two wires, similar to a twisted pair, of considerable length (0.5 m). Due to its length and construction, the tether appears to the system as a highly inductive tie to the power supply. This inductance acts as low-pass filter, thus allowing lower-frequency components of the discharge to travel through the EUT. The main

charge transfer from the gun to the EUT is seen during the second peak which is created by the storage capacitor,  $C_s$  (see Figure 5), which is much larger than  $C_d$  and thus has a slower discharge. Further, the second peak of the waveform in Figure 9 looks much different than that of the specification shown in Figure 7. This is again due the inductance of the power-supply cable that connects the EUT to ground.

Figure 9: Comparison of discharge waveform into a mobile system and tethered system.

#### 3.3 Measurements during IEC 61000-4-2 Testing

In order to study the cause of soft failures, it is useful to study the waveforms that occur during system-level ESD testing. The specifications of [7], do not provide methods for waveform measurement outside of the required measurements through the 2  $\Omega$  target. Two methods of making these measurements are considered: the use of a current probe around the gun tip, and direct voltage measurement within the system.

A current probe placed around a conductor will generate a voltage proportional to the current traveling through the conductor. By placing a current probe around the tip of the ESD discharge gun, the current that is discharged into the EUT can be measured. Current probes will add a small series impedance into the conductor which is being measured, but overall has little effect on the system. However, since a current probe can only detect changes in magnetic field, the probe will have a high-pass filter characteristic. Within this work a Fischer F-65A current probe is used. This probe has a -20 dB gain with a bandwidth from 100 kHz to 1 GHz. To test the accuracy of the current probe during system-level ESD zaps, the current probe was used during a discharge to the 2  $\Omega$  target. The current through the 2  $\Omega$  target can be calculated from the voltage waveform obtained through the SMA connector (see Figure 6). This is compared to the current measured directly from the current probe in Figure 8. Overall the two waveforms show very good agreement. Differences can be seen in the first peak; these can be attributed to the assumption that the disk resistor is a perfect 2  $\Omega$  load. In reality the 2  $\Omega$  target is constructed with large ground planes which will form a parasitic capacitance,  $C_p$ , between the zap point and ground. This capacitance is in parallel with the 2  $\Omega$  target resistance and will result in a low-pass filter. This will affect the measured first peak especially, since the higher-frequency components will see a smaller impedance.

While the above method is simple it can only supply information about what current is entering the EUT. It is highly desirable to capture waveforms appearing within the system, for example at an IC pin. The current waveform at the IC pin may be different from that at the gun tip due to the filtering effect of the circuit board. Direct voltage measurements can be taken within an EUT by soldering a rigid coaxial cable to the desired test-point within the system. In order to ensure that the highest frequency content of the ESD event (0.8 ns rise-time) is captured, a 3 GHz oscilloscope with 50  $\Omega$  input impedance is used. Inserting a low-impedance (50  $\Omega$ ) shunt to ground into a functional EUT would have a large impact on the system's performance, thus in order to reduce the current flow through the oscilloscope a high-impedance pick-off is used. It is important to note that added resistance will degrade the bandwidth of the measurement, thus the series resistance must be carefully chosen to prevent the measurement bandwidth from becoming

too small. Unlike current-probe measurements, direct voltage probing is highly invasive; the center conductor is isolated with a large resistance, but the ground of the cable is directly connected to the ground of the EUT.

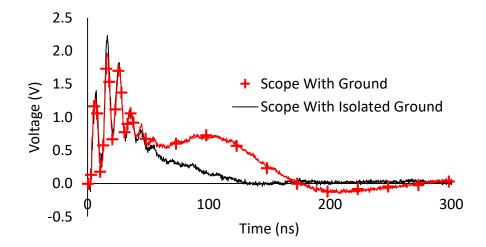

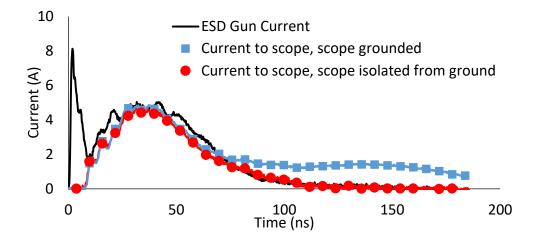

In one experiment, an ESD gun was discharged into the ground plane on a special test board. In the center of this test board is a mock-IC whose IOs consist of SMD resistors connected between the IO pad and board ground. The mock-IC also has power supply pads and ground pads with ample decoupling capacitance placed nearby. This test board was placed on the IEC61000-4-2 test bed in a mobile configuration, so the current return path is through the various board-toground capacitances, e.g. board to table and table to ground plane. A high-impedance pick-off was used so that the induced voltage waveform at a mock-IC power pad could be measured using an oscilloscope; however, this introduces a second ground return path. ESD current was injected into one of the board traces that terminates at a mock-IC IO. During ESD, the incoming current wave initially "sees" only the near-end of the pick-off, which is a 450  $\Omega$  resistor in series with the 50  $\Omega$  coaxial line going to the scope. Depending on the length of the cable, the effects of the oscilloscope (or other measurement device) will appear after a delay. The waveform at the oscilloscope was recorded for two cases: (1) the oscilloscope chassis is connected to earth-ground via the power cable and (2) a large resistor is inserted in the oscilloscope ground return. In the two cases, the impedance of the ESD current return path to the gun is different. Both measurement results are shown in Figure 10. The two waveforms appear nearly identical during the first 50 ns of the discharge, but an additional current peak is observed when the oscilloscope is connected to earth-ground in the usual manner.

Figure 10: Direct probing of signals on a test board; traces are terminated to emulate an IC load. The current flowing to the grounded oscilloscope (proportional to the voltage waveforms shown) is much different than with a ground-isolated oscilloscope.

This additional peak is caused by excess current flowing through the oscilloscope's grounded chassis. The ESD current charges the board with respect to earth ground. When the oscilloscope's chassis is isolated, the current will leak through the oscilloscope and through the high impedance. However, when the oscilloscope's chassis is shorted to earth ground, a much larger current can flow through this short. To confirm this, the 2  $\Omega$  target was again zapped, this time the current probe was placed around the coaxial cable that goes from the target to the scope. This measurement yields the current waveform traveling along the shield of the coaxial cable, but not opposed by current traveling through the center conductor. Figure 11 shows the current injected into the 2  $\Omega$  target and current measured by the current probe. Almost all of the current associated with the second peak of the ESD discharge can be attributed to this current flowing through the oscilloscope isolated from earth ground. Once more, an additional current peak (around 140 ns) is seen in the case where the oscilloscope is not isolated. Thus it is clear that the addition of direct voltage measurements effectively tethers the system precluding it from use on mobile systems. Even if direct voltage measurements are applied

to tethered systems, the additional ground return path will affect the discharge path and could change the system's response.

Figure 11: Current measured by a current probe placed around the coaxial cable from the 2  $\Omega$  target to the oscilloscope. Ideally the current to scope would be zero, but significant current is allowed to flow. Further, when the oscilloscope is grounded to earth ground, an additional peak is detected around 140 ns.

## **CHAPTER 4:**

# SOFT FAILURES OBSERVED WITHIN AN EUT

In order to study the mechanisms responsible for soft failure within a system during ESD stress, a suitable system must be acquired. While it is possible to purchase any consumer device and subject it to ESD stress, such experiments would be unwieldy for investigative work. Without detailed knowledge of the inner workings of the system, identifying the source of soft failures may prove difficult or impossible. Further, intricate systems such as cellphones, may have many complex circuits that could experience soft failure concurrently and obfuscate the results. Instead a custom test chip was fabricated in a 130-nm CMOS technology [13]. Further, to test this test chip in a functional state a corresponding test board was also designed and fabricated. Together this system becomes the EUT for the following investigations. By utilizing custom test equipment, detailed system design is on-hand facilitating a deeper knowledge of the mechanisms behind observed soft failures.

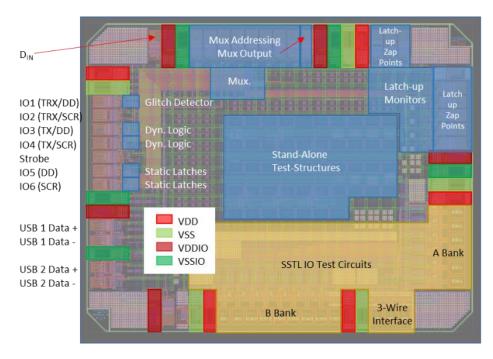

#### 4.1 Test Chip 1 Overview

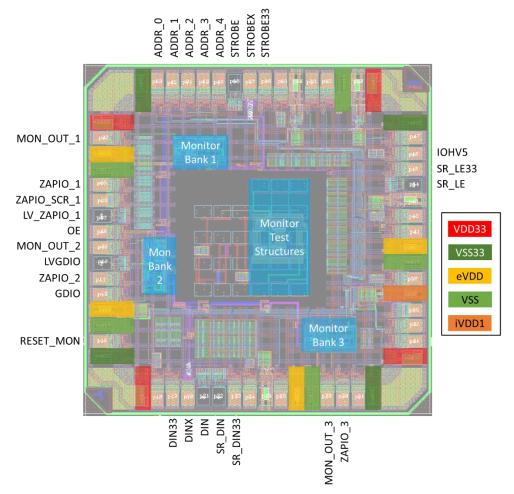

The test chip layout is shown in Figure 12. The test chip has two main power domains. The core circuitry and the SSTL IO test circuits lie within the 1.5 V domain,  $V_{DD}$ . Each  $V_{DD}$  cell contains a 2 mm active clamp. The 3.3 V supply,  $V_{DDIO}$ , provides power to all the CMOS IO circuits; each  $V_{DDIO}$  cell contains a 5.5mm active clamp. The rail clamp trigger circuits are optimized for power-on ESD [14], [15]. The  $V_{DDIO}$  bus was subjected to 100 ns power-on TLP (w.r.t.  $V_{SSIO}$ ); leakage current measurements indicate that at least one of the several  $V_{DDIO}$  clamps distributed around the pad ring suffers hard failure when 18 A is injected onto the pad ring. In an analogous measurement, one of the several  $V_{DD}$  clamps fails when 8 A is injected between the  $V_{DD}$  and  $V_{SS}$  buses. Each  $V_{SSIO}$  cell contains 500  $\mu$ m perimeter anti-parallel diodes to  $V_{SS}$ .

Figure 12: Chip layout view.

In Figure 12, the pad cells labeled IO1 through IO6 are CMOS IOs that connect to external pins which will undergo ESD zapping; these pads have either dual-diode or DTSCR protection, as indicated by the labels "DD" and "SCR." DTSCR protection devices are augmented by a reverse diode to achieve good protection against stress of both polarities. All six of these pad cells contain a bi-directional transceiver ("TRX"); however, by selective exclusion of key interconnects, IO3 and IO4 were configured as transmitters ("TX"), and IO5 and IO6 were configured as ESD-protected dummy cells. These dedicated zap IOs, as well as all of the 3.3 V control signal receivers, include a Schmitt trigger for noise resilience.

Two USB transmitters are included on-chip; each outputs a differential square-wave near the 480 Mbps operating speed of USB 2.0. Each USB transmitter is driven by an independent onchip ring oscillator. The output pins of USB transmitter #1 have dual-diode ESD protection, while the output pins of transmitter #2 have DTSCR protection.

Fourteen of the pad cells contain bidirectional SSTL IO test circuits [16]. As indicated on the bottom-right side of Figure 12, the SSTL IOs lie in two groups, labeled bank A and bank B. Each side contains six working SSTL transceivers; additionally, two non-functional SSTL transceivers were included on bank B for a component-level ESD study. The operating state of the SSTL block is programmable, allowing for selection between TX and RX modes and for adjustment of the on-die termination resistance. The SSTL block is programmed by an on-chip shift-register via a three-wire interface (serial data, serial clock and latch enable). The three-wire interface receivers are powered from the low-voltage domain and consist of a simple CMOS buffer with DD protection. Each time this block is reconfigured, the chip power consumption is changed. Banks of logic gates are included on the test chip. The stored data may be read-out before and after an ESD zap, in order to detect ESD-induced logic errors. The output of the selected logic gate is connected to an output pin through the on-chip multiplexer ("MUX").

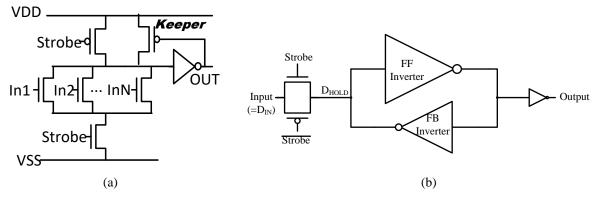

In Figure 12, each of the two blocks marked "Dyn. Logic" contains eight Domino Logic OR gates [17]; the schematic is shown in Figure 13(a). These logic gates are labeled 0-15, corresponding to their addresses. Table 2 describes these gates. In Figure 12, the two blocks labeled "Static Latches" each contain 16 latches, labeled 16-47, corresponding to their addresses. Each static latch consists of a bistable element (cross-coupled inverters) accessed via a transmission gate; the schematic is shown in Figure 13(b). The latches vary in terms of the inverter sizing, layout orientation, and the distance from the IO ring [17]. Table 3 describes the various latches.

Figure 13: Dynamic logic (a) and static latch (b) topology.

Table 2: Dynamic logic gates are located near IO3 and IO4. Each of these gates is a Domino OR circuit. The MUX address selects the indicated gate's output for read-out. In the column marked "Input," an entry of "Tied low" indicates that all the gate's inputs are tied low. An entry of "D<sub>IN</sub> pin" indicates that N-1 inputs are tied low, and one input is driven through a buffer chain from the D<sub>IN</sub> pin.

| MUX      | Address   | N. # - 6 :     | Input               |  |

|----------|-----------|----------------|---------------------|--|

| IO3 (DD) | IO4 (SCR) | N: # of inputs |                     |  |

| 0        | 8         | 4              | Tied low            |  |

| 1        | 9         | 16             | Tied low            |  |

| 2        | 10        | 4              | Tied low            |  |

| 3        | 11        | 16             | Tied low            |  |

| 4        | 12        | 4              | Tied low            |  |

| 5        | 13        | 4              | Tied low            |  |

| 6        | 14        | 4              | D <sub>IN</sub> pin |  |

| 7        | 15        | 16             | D <sub>IN</sub> pin |  |

Table 3: Static latches are located near IO5 and IO6. The MUX address selects the indicated gate's output for readout. The distance indicated is given in arbitrary units, with larger numbers indicating a greater distance.

| MUX  | Address | Distance | Relative   | Relative   |

|------|---------|----------|------------|------------|

| IO5  | IO6     | from IO  | size of FF | size of FB |

| (DD) | (SCR)   |          | inverter   | inverter   |

| 16   | 32      | 1        | 2          | 1          |

| 17   | 33      | 1        | 4          | 2          |

| 18   | 34      | 1        | 6          | 3          |

| 19   | 35      | 1        | 6          | 2          |

| 20   | 36      | 1        | 6          | 1          |

| 21   | 37      | 1        | 6          | 3          |

| 22   | 38      | 1        | 6          | 2          |

| 23   | 39      | 1        | 6          | 1          |

| 24   | 40      | 2        | 2          | 1          |

| 25   | 41      | 3        | 2          | 1          |

| 26   | 42      | 4        | 2          | 1          |

| 27   | 43      | 5        | 2          | 1          |

| 28   | 44      | 6        | 2          | 1          |

| 29   | 45      | 7        | 2          | 1          |

| 30   | 46      | 8        | 2          | 1          |

| 31   | 47      | 9        | 2          | 1          |

Data are written into the logic circuits described above only when an external strobe signal is set to the appropriate value; the strobe is applied at the pad labeled "Strobe." When strobe is low, the static latches hold their previous data and the dynamic logic gates are in evaluate mode.

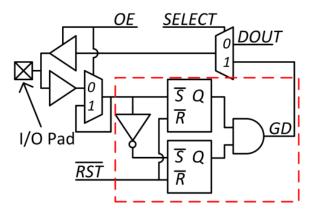

A "glitch detector" was included because coupled noise at an input pin can produce logic errors [13]. The glitch detector circuit is shown in Figure 14. This circuit was placed inside the IO1 pad cell and will detect a logic level change at the IO1 pin due to ESD discharges elsewhere in the system. The glitch detector is active when the OE control signal is low. When the logic level at the input changes, GD switches from low to high, maintaining this value until the latches are reset. The rightmost multiplexer allows the IO to output either GD or D<sub>OUT</sub>. The leftmost multiplexer keeps the signal at the input of the glitch detector constant when OE is high (activating the output driver); without it, the signal output by the glitch detector would be fed back into the glitch detector.

Figure 14: Glitch detector schematic.

ESD-induced logic upset (data change) can be detected by reading out the contents of each static latch and dynamic OR gate after an ESD zap. The output of a USB transmitter can be observed before, during and after an ESD zap to observe the effect of ESD on a high-speed, free-running circuit.

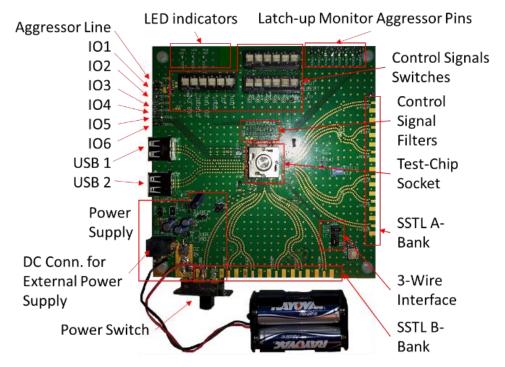

4.2 Test System 1 Overview

The system-under-test is a four-layer FR4 circuit board, shown in Figure 15. The test system can be powered by a DC supply or by a battery pack (pictured). Independent linear low-dropout (LDO) regulators supply each of the power domains:  $V_{DDIO}$  (3.3V),  $V_{DD}$  (1.5V), and  $V_{DDLED}$  (3.3V), the last of which provides power for the LEDs described below. Adequate decoupling capacitance is included on each of the power nets, including large tantalum capacitors and smaller ceramic capacitors. SMD decoupling capacitors were placed near the chip, following best practices.

An on-board LED provides a visual readout of logic high signals from the multiplexer output and a second LED enables data readout from IO1, the glitch detector circuit's output. The LEDs are driven by a separate buffer IC that is powered from the V<sub>DDLED</sub> domain.

Figure 15: Board photograph.

Some of the chip IO pins are intended to undergo ESD zapping; test points are placed at the board-edge ends of traces that terminate at these pins. A zap is initiated by a contact discharge to a test point. Test points provide direct access to IO1-IO6. An additional test point is connected to a trace that is adjacent to the signal trace that goes to IO1. This neighbor line is referred to as the "aggressor line;" the aggressor line is terminated near the test chip by a short circuit to ground. Zaps are applied to the aggressor line in experiments that utilize the glitch detector inside IO1; in these experiments, IO1 is set to receive mode and its input is set to either logic low or logic high. The logic input for IO1 is supplied by an on-board buffer IC. IO1 can also be directly connected to a test-point on the board's edge. The desired input source for IO1 is selected by soldering a 0  $\Omega$ resistor to one of two pads on the board.

The control signal switches drive the multiplexer address pins and the on-chip control lines, and are used to input data to the latches and dynamic logic. Address and control pins are not intended to be zapped; robust signal filters are placed on board near these pins of the test chip to minimize ESD-induced disturbances.

A 0.1  $\Omega$  precision resistor is inserted in series with the V<sub>DD</sub> on-board voltage regulator. A multimeter is used to measure the voltage across this resistor. This allows the quiescent current draw (I<sub>DDQ</sub>) to be measured before and after an ESD gun discharge. I<sub>DDQ</sub> changes with the operating state of the SSTL block. An unintentional change in the circuit operating state constitutes a soft failure.

#### 4.3 IEC 61000-4-2 Testing of Functional System

ESD discharges were applied to the powered-up system according to the IEC61000-4-2 standard. To observe the effects of an earth-ground connection, the system was tested in a mobile configuration (i.e. powered from a battery pack) and in a tethered configuration (i.e. powered from a grounded DC supply). Gun discharges were applied to several key locations on the board, which varied in accordance with experiment being carried out.

#### 4.3.1 Glitches on Signal Lines

The first experiment is designed to identify the conditions under which ESD-induced coupled noise at an IO pin is large enough to produce a logic error. The glitch detector, located inside IO1, was activated, and the IO was set to receive mode. The input to IO1 was driven through a buffer whose input is shorted to either supply rail by one of the control switches. Gun zaps were applied to the aggressor line adjacent to the IO1 signal trace. A minimum of five zaps were applied for each test and the test was repeated on a second test chip. Finally, the entire experiment was repeated using a tethered configuration by powering the test system from a precision DC supply. Table 4 summarizes the occurrence of detected glitches. The following syntax is introduced to ease this discussion. For a signal line that is initially driven low, a glitch

Table 4: Occurrence of glitches at IO1 when zaps are applied to the aggressor line. The percentage of zaps resulting in a detected glitch is indicated. A dash indicates that no tests were performed at that particular voltage level. The EUT is tested in both mobile and tethered configurations.

| Aggressor Line Zaps         |        |          |          |          |          |

|-----------------------------|--------|----------|----------|----------|----------|

|                             |        | Mobile   |          | Tethered |          |

| $ \mathbf{V}_{\text{pre}} $ | Glitch | Positive | Negative | Positive | Negative |

| (kV)                        | Туре   | Zap      | Zap      | Zap      | Zap      |

| (K V)                       |        | Upsets   | Upsets   | Upsets   | Upsets   |

| 0.5                         | (0→1)  | 0%       | 0%       | 0%       | 0%       |

| 0.55                        | (0→1)  | 0%       | 20%      | -        | 20%      |

| 0.57                        | (0→1)  | 0%       | 80%      | -        | 60%      |

| 0.6                         | (0→1)  | 0%       | 100%     | 0%       | 80%      |

| 0.7                         | (0→1)  | 0%       | 100%     | 0%       | 100%     |

| 0.8                         | (0→1)  | 0%       | -        | 0%       | -        |

| 0.85                        | (0→1)  | 0%       | -        | 60%      | -        |

| 0.9                         | (0→1)  | 40%      | -        | 100%     | -        |

| 0.95                        | (0→1)  | 100%     | -        | 100%     | -        |

| $\geq 1$                    | (0→1)  | 100%     | 100%     | 100%     | 100%     |

| 0.5                         | (1→0)  | 0%       | 0%       | 0%       | 0%       |

| 0.55                        | (1→0)  | 0%       | -        | -        | -        |

| 0.6                         | (1→0)  | 40%      | -        | 60%      | 0%       |

| 0.65                        | (1→0)  | 100%     | -        | -        | -        |

| 0.7                         | (1→0)  | 100%     | 0%       | 100%     | 0%       |

| 0.8                         | (1→0)  | -        | 0%       | 100%     | 0%       |

| 0.9                         | (1→0)  | -        | 0%       | 100%     | 80%      |

| 0.95                        | (1→0)  | -        | 100%     | -        | -        |

| $\geq 1$                    | (1→0)  | 100%     | 100%     | 100%     | 100%     |

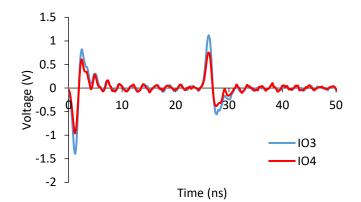

occurs when that line is subsequently driven high (perhaps briefly). This will be denoted as  $(0\rightarrow 1)$ . The polarity of the zap that caused the glitch will be prefixed. Thus,  $+(1\rightarrow 0)$  indicates that a positive zap caused a signal level to go from high to low. From Table 4, it is observed that the minimum pre-charge voltage at which  $-(0\rightarrow 1)$  glitches occur is lower than that of  $+(0\rightarrow 1)$ . Conversely,  $+(1\rightarrow 0)$  has a lower threshold than  $-(1\rightarrow 0)$ . This indicates that the trace to IO1 is inductively coupled to the aggressor line. The initial di/dt of the rising edge of positive zaps (or falling edge of negative zaps) induces a current in the IO1 signal line that flows out of the chip (or into the chip for falling edges). An example of this coupled current can be seen in Figure 16.

Figure 16: Coupled waveform observed on an unpopulated board at the IO1 pad location. 100 V TLP discharges were applied to IO3 and IO4 as indicated. The TLP pulse had 25 ns width and 1ns rise/fall times.

Positive TLP current pulses were injected into IO3 and IO4 on an unpopulated test board. The voltage induced at the IO1 pad was monitored. Large negative peaks are observed for the leading (rising) edges of the TLP pulses; conversely, large positive peaks are observed for the trailing (falling) edges. Despite the susceptibility for  $+(1\rightarrow 0)$  and  $-(0\rightarrow 1)$  glitches,  $+(0\rightarrow 1)$  and  $-(1\rightarrow 0)$  glitches do still occur; just at higher stress levels. This suggests that the second edge of the fast transient, while able to cause glitches, is less severe than the first edge. The presence or absence of a tether has no apparent effect on the glitch occurrence thresholds. Thus the amount of delivered charge has little impact on the occurrence of glitches, but rather the first peak of the IEC pulse, which is common to discharge waveforms into both tethered and mobile configurations

(see Figure 9), is the source of the noise. This too is expected as the first peak has much larger di/dt than the second peak and it is the di/dt that is responsible for inductive coupling.

In addition to inductive coupling, there is another possible source for the observed glitches. ESD noise may have induced a logic error at the buffer IC that drives this trace and the pin. To ascertain whether this contributes to the cause of the glitches, an additional experiment was conducted. IO1 was driven low either by the buffer IC (as above) or via a small-valued pull-down resistor. However, since the glitch detector's input and output share a pin, a suitable pull-down resistor must not overly load the glitch detector's output driver. A  $47\Omega$  resistor was used, which allows for a 0.7V output-high voltage and a 0V output-low voltage. Three zaps were applied to the aggressor line and again to the USB shield for each configuration and the glitch detector was monitored after each. Table 5 summarizes the results of this experiment. The occurrence of glitches is not reduced by eliminating the buffer IC, indicating that noise is coupled directly to the test chip rather than indirectly to the test chip via the buffer IC.

|                            | 7                                 | A T:                            |  |

|----------------------------|-----------------------------------|---------------------------------|--|

| $V_{PRE}$                  | Zaps to Aggressor Line            |                                 |  |

| (kV)                       | Buffer IC                         | Resistive Pull-Down             |  |

| 0.2                        | 0 %                               | 0 %                             |  |

| 0.5                        | 0 %                               | 0 %                             |  |

| 1                          | 0 %                               | 33 %                            |  |

| 1.5                        | 66 %                              | 100 %                           |  |

| 2                          | 100 %                             | 100 %                           |  |

| VPRE                       | Zaps to USB Shield                |                                 |  |

| (kV)                       | Buffer IC                         | Resistive Pull-Down             |  |

| ()                         | Dunier IC                         | Resistive I ull-Down            |  |

| 4                          | 0 %                               | 0 %                             |  |

| . ,                        |                                   |                                 |  |

| 4                          | 0 %                               | 0 %                             |  |

| 4<br>5                     | 0 %<br>0 %                        | 0 %<br>0 %                      |  |

| 4<br>5<br>6                | 0 %<br>0 %<br>0 %                 | 0 %<br>0 %<br>0 %               |  |

| 4<br>5<br>6<br>7           | 0 %<br>0 %<br>0 %<br>33 %         | 0 %<br>0 %<br>0 %<br>0 %        |  |

| 4<br>5<br>6<br>7<br>8      | 0 %<br>0 %<br>0 %<br>33 %<br>33 % | 0 %<br>0 %<br>0 %<br>0 %<br>0 % |  |

| 4<br>5<br>6<br>7<br>8<br>9 | 0 %<br>0 %<br>33 %<br>33 %<br>0 % | 0 %<br>0 %<br>0 %<br>0 %<br>0 % |  |

Table 5: Glitch detection results with different signal trace drivers. IO1 is being driven low by either a buffer or a resistive pull-down. Each entry represents the percentage of  $+(0 \rightarrow 1)$  glitches detected out of three zaps.

ESD zaps were also applied to the signal traces for IO2 through IO6. In this case, ESD current will enter the test chip, in contrast to the previous experiment. The results are shown in Table 6; entries are grouped by their ESD protection methods. There is a proximity effect; when zaps are applied to signal traces that are progressively farther from IO1 (while comparing similar protection devices) a higher pre-charge voltage is needed to cause an upset (glitch) at IO1. This result was to be expected since inductive coupling decreases with increased distance between aggressor and victim. For discharges into IOs, upsets occur at even lower pre-charge voltages than in the previous experiment in which the "aggressor line" was zapped. This is attributed to the presence of additional noise mechanisms; when an IO pin is zapped, ESD current enters the chip produces supply noise and/or couples strongly to neighboring bondwires. Considering zaps to IOs regardless of the protection devices used as the distance from IO1 to the zap pin increases, the probability that a glitch is induced does not decrease in a perfectly monotonic fashion. This is attributed to the differences in the ESD protection used at the various IOs. IO3 and IO5 have DD protection while IO4 and IO6 have SCR protection. During an ESD event, the input impedance at Table 6: Occurrence of  $+(1\rightarrow 0)$  glitches at IO1. Zaps were applied to the indicated IO. The EUT was in its mobile configuration. As zaps are applied farther from the IO1 the threshold for upsets increases. Only IOs with the same

protection (SCR) are compared.

|                  | Zapped IO#     |      |      |               |      |

|------------------|----------------|------|------|---------------|------|

| V <sub>pre</sub> | SCR Protection |      |      | DD Protection |      |

| (kV)             | 2              | 4    | 6    | 3             | 5    |

| 0.2              | 20%            | 0%   | 0%   | 0%            | 0%   |

| 0.3              | 100%           | 40%  | 0%   | 80%           | 0%   |

| 0.4              | 100%           | 100% | 0%   | 100%          | 0%   |

| 0.5              | 100%           | 100% | 0%   | 100%          | 0%   |

| 0.6              |                |      | 0%   | -             | 0%   |

| 0.7              | 100%           | 100% | 80%  | 100%          | 0%   |

| 0.8              |                |      | 100% | -             | 100% |

| 0.9              |                |      | 100% | -             | 100% |

| 1                | 100%           | 100% | 100% | 100%          | 100% |

| 2                | 100%           | 100% | 100% | 100%          | 100% |

the pin (impedance from the pin to the board ground) is different for the cases of DD and SCR protection. The input impedance affects the ESD current waveform at the pin and therefore the magnitude of the noise coupled to IO1 and the glitch detector.

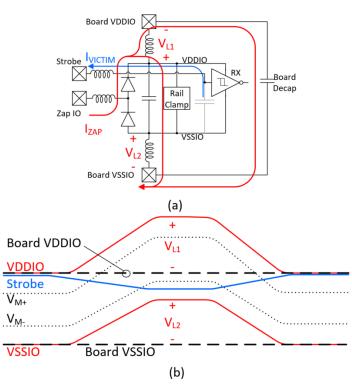

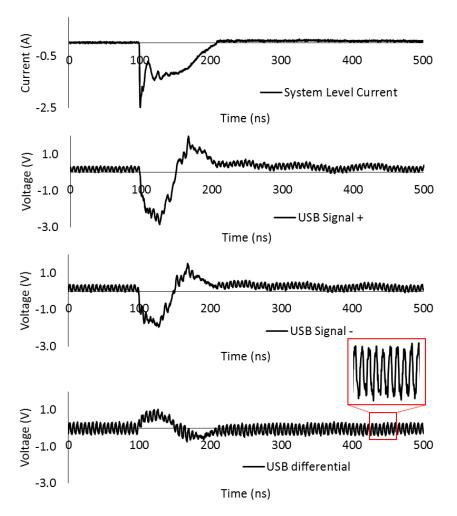

The schematic of the chip-level IO being zapped and the victim IO (e.g. Strobe) where glitches occur is shown in Figure 17(a). When ESD current is injected into the zap IO, a glitch that results from the induced noise may be detected at the victim IO. Such noise may drive the victim IO temporarily to logic high or logic low. Figure 17 depicts the rising-edge of an ESD discharge into an IO. Two on-chip mechanisms work in tandem to cause a  $(1 \rightarrow 0)$  glitch. The first mechanism is induced noise on the on-chip supply rails. For this example, the stress current must pass through the ESD protection to the VDDIO supply rail. The dV/dt caused by this current will initially trigger the rail clamp to turn on. The rail clamp and on-chip decoupling capacitance will both provide paths to the VSSIO supply rail. This current must then flow out of the chip through the VSSIO bondwires to board ground. After some time, the current will begin to flow more readily through the VDDIO bondwires and return to board ground via the decoupling capacitance. The change in current flowing through the bondwires associated with either the VDDIO or VSSIO pins will cause a voltage drop to form across the bondwires. This leads to a transient decoupling effect between the chip and board VDDIO/VSSIO lines due to the inductance of the bondwires. Figure 17(b) illustrates a simplified depiction of this decoupling. The potential on the VDDIO and VSSIO rails elevates w.r.t. board VSSIO causing the switching thresholds, V<sub>M+</sub> and V<sub>M-</sub>, of the Schmitt trigger IO to elevate as well. However, the Strobe signal potential, which is generated on the board, is not affected by this on-chip supply decoupling. The second mechanism is coupling of noise to neighboring IOs. In the example of Figure 17, the magnetic field generated by the initial edge of the positive discharge will cause a current, IVICTIM, to flow out of the Strobe

line. This current will ultimately work to discharge the parasitic capacitance associated with the receiver circuitry. Figure 17(b) illustrates the resulting change in the on-chip Strobe signal level w.r.t. board VSS. As mentioned previously, for traces that run parallel to each other on-board, the ESD current inductively couples to neighboring traces as well, and can further increase the noise seen at the victim IO. Thus the drop in the Strobe signal and the increase of the switching thresholds both work together to cause a  $+(1\rightarrow 0)$  glitch for the leading edge of this example stress. Following a similar procedure for the other cases:  $+(0\rightarrow 1)$  during the trailing edge,  $-(0\rightarrow 1)$  during the leading edge, and  $-(1\rightarrow 0)$  during the trailing edge, all yield similar results.

Figure 17: (a) Schematic representation of the aggressor and victim IO on chip. Due to the bondwire inductance, injected ESD current (I<sub>ZAP</sub>) can cause chip VSSIO and VDDIO to rise w.r.t. their board levels. Further, I<sub>ZAP</sub> can induce a current in nearby signal lines (I<sub>VICTIM</sub>). (b) VDDIO and VSSIO are elevate w.r.t. to board ground due to the voltage drop across the bondwires. Strobe is pulled low due to the current exiting its pin. Together Strobe is pulled below the lower threshold (V<sub>M</sub>.) of the receiver.

Gun zaps were next applied to the USB connector shield. (Note that metal connector

shields undergo contact discharge during IEC61000-4-2 testing of a fully assembled, enclosed

system.) The connector shield is tied to the ground plane of the system. The USB connector is not

nearby the glitch detector. Zaps were applied to a USB connector shield and the percentage of glitches observed are recorded in Table 7. A minimum of five zaps were conducted for each test case and the results from two test chips were tabulated. The failure threshold, i.e. minimum precharge voltage that induces a glitch, is much larger than in the previous experiments. As in the previous experiments,  $-(0\rightarrow 1)$  glitches have a lower threshold than  $-(1\rightarrow 0)$ , and  $+(1\rightarrow 0)$  glitches have a lower threshold than  $+(0\rightarrow 1)$  glitches. In this experiment, the ESD current is injected to the board's ground plane, and thus the glitches are not the result of inductive coupling between parallel traces, as had been the case in the previous experiments. There are two possible mechanisms for the glitches. Noise may be induced on the signal line by the magnetic field radiated from the gun tip. Or, the zaps to the ground plane might be causing the ground potential to bounce. These potential fluctuations would be strongly coupled to the power plane by the large

|                  |                     | USB      | Shield Zaps |          |          |

|------------------|---------------------|----------|-------------|----------|----------|

|                  |                     | Mo       | bile        | Tetl     | nered    |

| V <sub>pre</sub> | Glitch              | Positive | Negative    | Positive | Negative |

| (kV)             | Type                | Zap      | Zap         | Zap      | Zap      |

|                  |                     | Upsets   | Upsets      | Upsets   | Upsets   |

| $\leq 4$         | (0→1)               | 0%       | 0%          | 0%       | 0%       |

| 5                | (0→1)               | 0%       | 0%          | 0%       | 0%       |

| 6                | $(0 \rightarrow 1)$ | 0%       | 33%         | 0%       | 0%       |

| 7                | $(0 \rightarrow 1)$ | 0%       | 66%         | 0%       | 100%     |

| 8                | $(0 \rightarrow 1)$ | 0%       | 100%        | 0%       | 100%     |

| 9                | $(0 \rightarrow 1)$ | 0%       | 100%        | 100%     | 100%     |

| 10               | (0→1)               | 0%       | 100%        | 100%     | 100%     |

| 11               | (0→1)               | 33%      | 100%        | 100%     | 100%     |

| 12               | (0→1)               | 100%     | 100%        | 100%     | 100%     |

| $\leq 4$         | (1→0)               | 0%       | 0%          | 0%       | 0%       |

| 5                | (1→0)               | 100%     | 0%          | 0%       | 0%       |

| 6                | (1→0)               | 100%     | 0%          | 40%      | 0%       |

| 7                | (1→0)               | 100%     | 0%          | 100%     | 0%       |

| 8                | (1→0)               | 100%     | 0%          | 100%     | 0%       |

| 9                | (1→0)               | 100%     | 0%          | 100%     | 40%      |

| 10               | (1→0)               | 100%     | 0%          | 100%     | 100%     |

| 11               | (1→0)               | 100%     | 0%          | 100%     | 100%     |

| 12               | $(1\rightarrow 0)$  | 100%     | 100%        | 100%     | 100%     |

Table 7: Occurrence of glitches when zaps were applied to a USB shield (board ground). The EUT was tested in both mobile and tethered configurations.

on-board decoupling capacitance, resulting in little change in the effective supply voltage given by  $V_{DDIO} - V_{SSIO}$ . There would be relatively little coupling to the IO1 signal trace and thus its potential would be stationary, at least initially. A positive zap would elevate the ground reference for VDDIO, causing a logic-high input signal to temporarily appear low, while for large amplitude negative zaps, a logic-low input signal could briefly appear to have switched high.

There is no systematic difference between the results for the tethered and mobile configurations of the EUT, except that the tether tends to reduce the margin between positive and negative glitch thresholds. The lack of a strong effect is not unexpected. The tether connects the board ground plane to the power supply ground through the series inductance of the supply cable; this cable has a high impedance on the short time scale during which the ground bounce is severe.

#### 4.3.2 Static Latch Upsets

The static latch test circuits are programmed using signals DIN and Strobe. The noise on the corresponding on-board traces is minimized by the use of an RC filter and Zener diode; furthermore, these traces are not subjected to contact ESD. Zaps are applied to IOs 1 through 6 and the data are read out after each zap to see if any upsets (bit flips) have occurred. To eliminate differences between the IO circuits which might confound the data analysis, IO1 through IO4 were put into high-Z mode to make them similar to IO5 and IO6, which have no driver. A minimum of five zaps were applied to each IO at a given pre-charge voltage. The experiment was repeated on a second test chip. For these experiments, strobe was set to low. When the strobe is low, the latch is supposed to "hold" its logic value; this function is effected by the transmission gate shown in the schematic of Figure 13.

For gun precharge voltages up to  $\pm 8$  kV, no upsets were observed when the stored data matched the input data. However, when the latch input data (D<sub>IN</sub>; see Figure 13) and the stored

data (D<sub>HOLD</sub>) were different, upsets occurred at precharge voltages as low as  $\pm$  0.5 kV, as indicated in Table 8 (system in mobile configuration) and Table 9 (system in tethered configuration). In these experiments, if even one static latch was upset, all were. Further, storing a logic high versus logic low had no impact on the likelihood of an upset taking place. The zap polarity does not strongly affect the upset percentages for zaps to the two IOs nearest the strobe line. However, for zaps to one of the two more distant IOs (3 and 6), the polarity strongly affects the likelihood of upset. Negative zaps to IO3 (DD protection) and IO6 (SCR protection) cause

|       | Zapped IO# |       |      |       |      |       |  |  |  |  |

|-------|------------|-------|------|-------|------|-------|--|--|--|--|

| Vpre  | 1          | 2     | 3    | 4     | 5    | 6     |  |  |  |  |

| (kV)  | (DD)       | (SCR) | (DD) | (SCR) | (DD) | (SCR) |  |  |  |  |

| -2    | 100%       | 100%  | 100% | 100%  | 100% | 100%  |  |  |  |  |

| -1    | 0%         | 100%  | 100% | 100%  | 100% | 100%  |  |  |  |  |

| -0.5  | 0%         | 0%    | 100% | 100%  | 100% | 100%  |  |  |  |  |

| -0.25 | 0%         | 0%    | 0%   | 80%   | 80%  | 0%    |  |  |  |  |

| 0.25  | 0%         | 40%   | 20%  | 80%   | 100% | 60%   |  |  |  |  |

| 0.5   | 0%         | 100%  | 0%   | 100%  | 100% | 100%  |  |  |  |  |

| 1     | 0%         | 100%  | 100% | 100%  | 100% | 100%  |  |  |  |  |

| 2     | 100%       | 100%  | 100% | 100%  | 100% | 100%  |  |  |  |  |

Table 8: Zaps were applied to IOs 1-6 with the EUT in its mobile setup. The IO being zapped is in high-Z mode.The table lists the percentage of zaps that resulted in static latch upsets at each test condition.

Table 9: Same experiment as for Table 4 except that the EUT is in its tethered setup. Zaps were applied to each of the IOs.

|                          | Zapped IO# |        |         |        |         |  |  |  |  |

|--------------------------|------------|--------|---------|--------|---------|--|--|--|--|

| V <sub>pre</sub><br>(kV) | 2 (SCR)    | 3 (DD) | 4 (SCR) | 5 (DD) | 6 (SCR) |  |  |  |  |

| -2                       | 100%       | 100%   | 100%    | 100%   | 100%    |  |  |  |  |

| -1                       | 100%       | 100%   | 100%    | 100%   | 100%    |  |  |  |  |

| -0.5                     | 40%        | 100%   | 100%    | 100%   | 100%    |  |  |  |  |

| -0.25                    | 0%         | 0%     | 100%    | 40%    | 0%      |  |  |  |  |

| 0.25                     | 0%         | 20%    | 100%    | 60%    | 20%     |  |  |  |  |

| 0.5                      | 40%        | 40%    | 80%     | 100%   | 100%    |  |  |  |  |

| 1                        | 100%       | 100%   | 100%    | 100%   | 100%    |  |  |  |  |

| 2                        | 0%         | 100%   | 100%    | 100%   | 100%    |  |  |  |  |

roughly equal numbers of upsets. However, positive zaps to IO6 caused more upsets to occur than positive zaps to IO3. This may indicate that for positive zaps, the top diode reduces the stress, and the noise coupling, more than the SCR does.

Based on the above, it is concluded that ESD is inducing noise on Strobe and this results in the inadvertent clocking-in of new data. Further support for this assertion may be found by considering the positional dependence of the upset threshold. The upset threshold is lowest when the zaps are applied to IO4 and IO5; at the IC, the Strobe pin is right between the pins for IO4 and IO5 (see Figure 12). Despite the robust on-board filtering of the Strobe signal line, logic level glitches appear to be causing upsets within the static latches. To further mitigate board-level noise coupling, the strobe line was shorted to ground very close to the socket and some experimentation was repeated. This short had no discernable effect on the occurrence of upsets, and thus it is assumed that glitches are induced on Strobe due to noise coupling inside the package.

Additionally, tests were performed to discern whether the state of the output driver at the zap pin affects the upset occurrences. IO3 and IO4 were configured as transmitters and zapped in both output high ( $D_{OUT} = 1$ ) and output low ( $D_{OUT} = 0$ ) states. Zaps were applied both with the output high and low. Table 10 shows the static latch upset percentage for each case, obtained at a precharge level of  $\pm 0.5$  kV and  $\pm 1$  kV, and with  $D_{IN} \neq D_{HOLD}$ . As in the previous experiment, zaps to IO4 cause upsets to occur more often than do zaps to IO3. Minor variations in the upset percentage are attributed to a different test chip being used for each dataset. It was found that the state of the output driver did not impact the occurrence of upsets in the static latches. To induce latch upset in the case that  $D_{IN} = D_{HOLD}$ , even higher precharge voltages had to be used. At +8 kV, two of the five chips tested had repeatable upsets. Upsets did not occur at lower precharge voltages, or with negative polarity.

|                  | Zapped IO# |               |                |      |               |                |  |  |  |  |

|------------------|------------|---------------|----------------|------|---------------|----------------|--|--|--|--|

| V <sub>pre</sub> |            | 3             |                | 4    |               |                |  |  |  |  |

| (kV)             | Hi-Z       | Output<br>Low | Output<br>High | Hi-Z | Output<br>Low | Output<br>High |  |  |  |  |

| -1               | 100%       | 100%          | 100%           | 100% | 100%          | 100%           |  |  |  |  |

| -0.5             | 100%       | 100%          | 100%           | 100% | 100%          | 100%           |  |  |  |  |

| 0.5              | 0%         | 0%            | 0%             | 100% | 100%          | 100%           |  |  |  |  |

| 1                | 100%       | 100%          | 100%           | 100% | 100%          | 100%           |  |  |  |  |

Table 10: Static latch upsets from ESD gun zaps to IO3 and IO4. The output transmitters were enabled and the output level was varied. The latches' data inputs  $(D_{IN})$  were set opposite to the stored data  $(D_{HOLD})$ .

For completeness, the static latches were monitored for upsets following zaps to the USB shield (board ground-plane). These tests were performed with  $D_{IN}$  opposite  $D_{HOLD}$ . Only one upset was observed at 12 kV. Furthermore, this upset only changed the value of data stored in latches at the following addresses: 16, 20, 23-31, 32, 36, 39-47. These latches all contain the smallest feedback ("fb") inverter, as indicated in Table 3. When a glitch occurs on the Strobe line, the transmission gate is transparent for a short time allowing the  $D_{IN}$  signal to pass to the flip-flop. If this glitch is especially brief, the input to the flip-flops within the latches may not be sustained long enough for all of the latches to upset. It is not surprising that the set of latches with the smallest feedback inverter is most susceptible to this change since a smaller feedback inverter is less capable of sustaining the data when a transient is presented at the input of the flip-flop.

### 4.3.3 Upsets in Dynamic Logic

The dynamic OR gates are in the pre-charge state when Strobe = 0 and evaluate when Strobe = 1. During ESD testing, the dynamic node is first precharged (the gates' outputs will be low) and subsequently all of the inputs to the dynamic stage (refer to Figure 13(a)) are held low and the gate is placed in evaluate mode. This will place all of the dynamic nodes into their high-

impedance states. If the OR gate's output is observed to have changed state from low to high following ESD, it can be assumed that the charge stored on the dynamic node was erased. In this experiment, zaps were applied to IO3 and IO4. These IOs were chosen due to their proximity to the bank of dynamic logic gates within the core of the test chip.

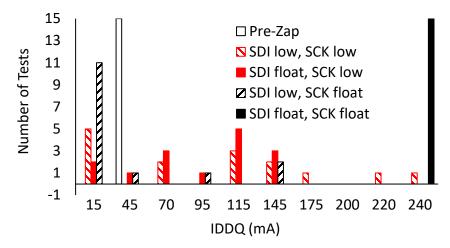

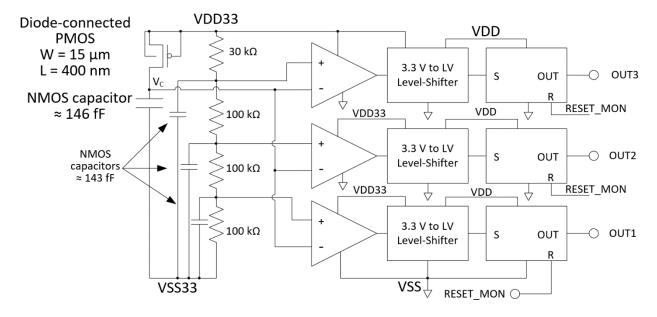

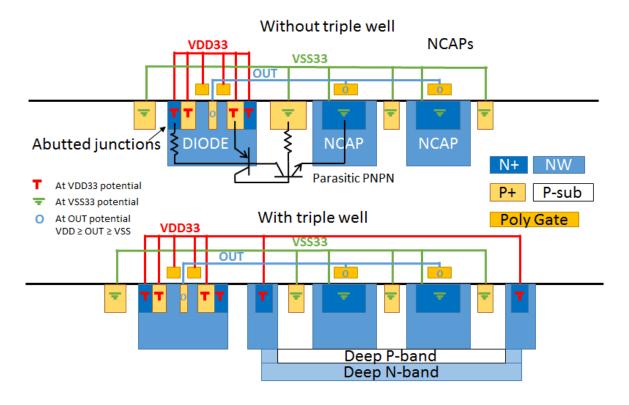

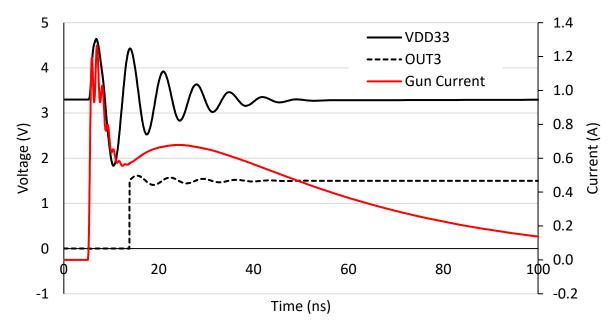

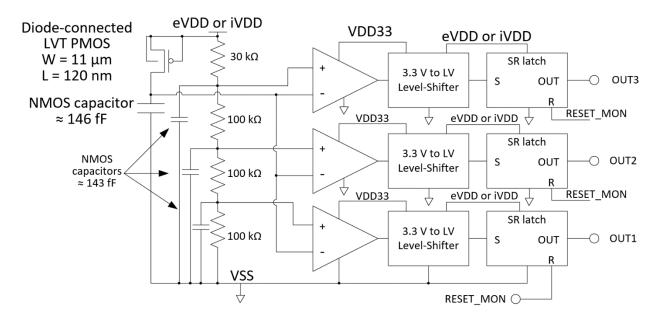

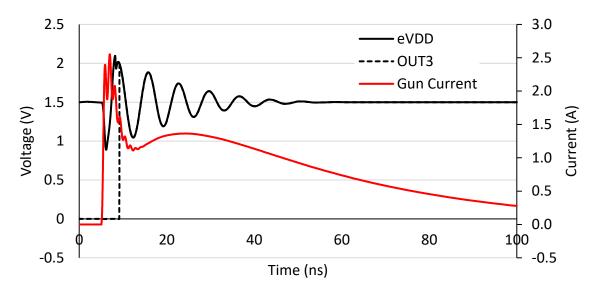

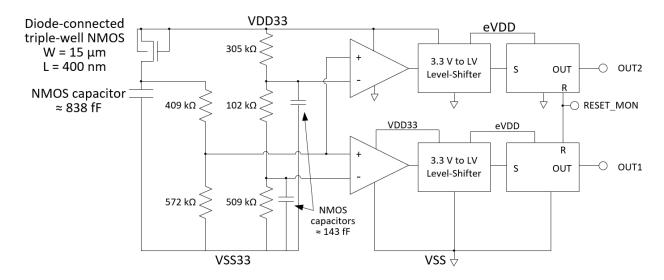

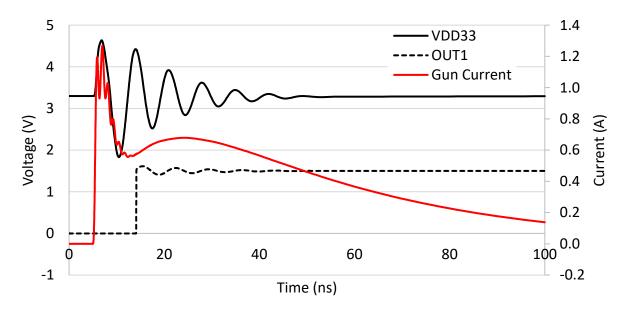

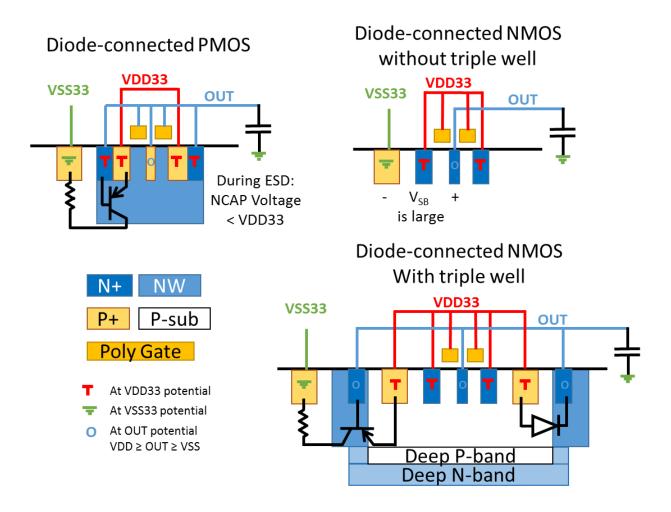

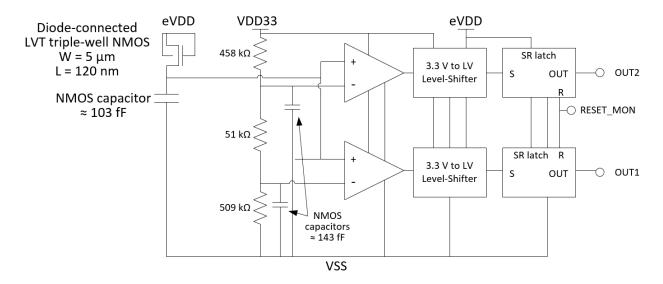

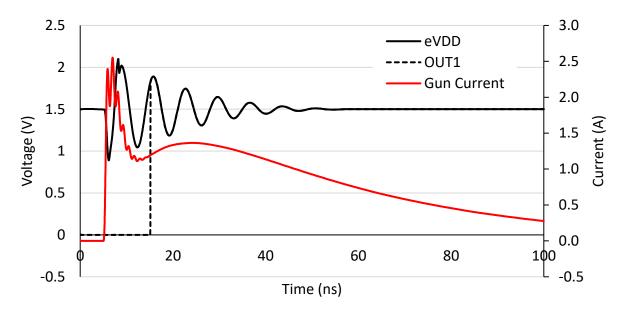

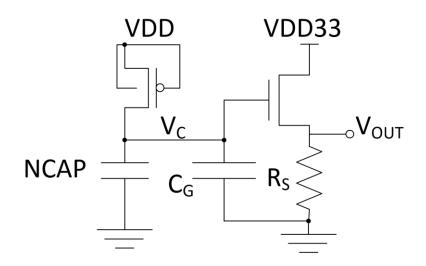

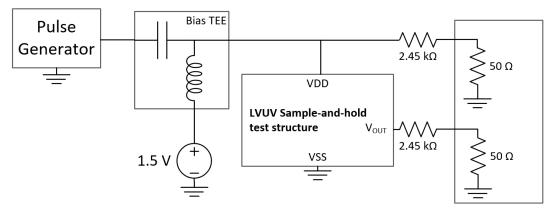

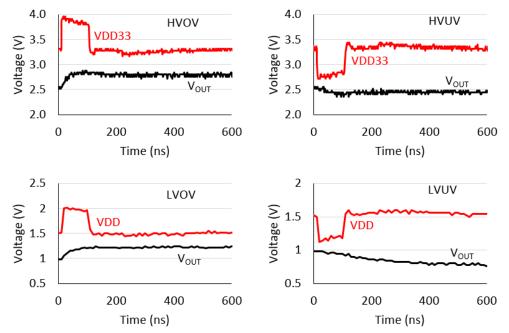

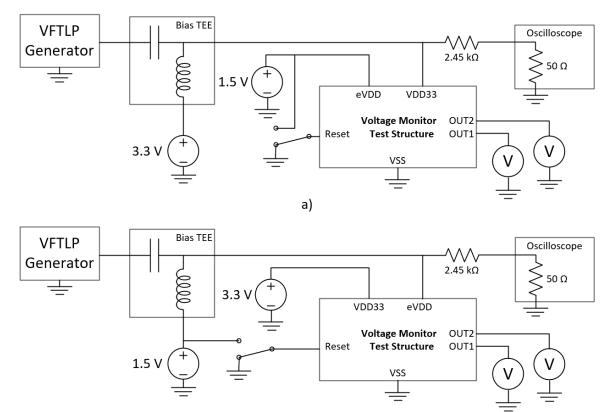

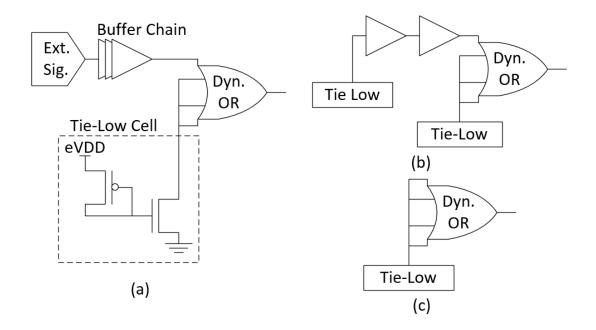

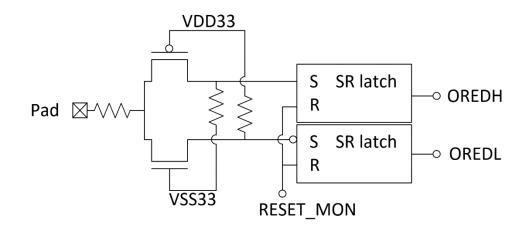

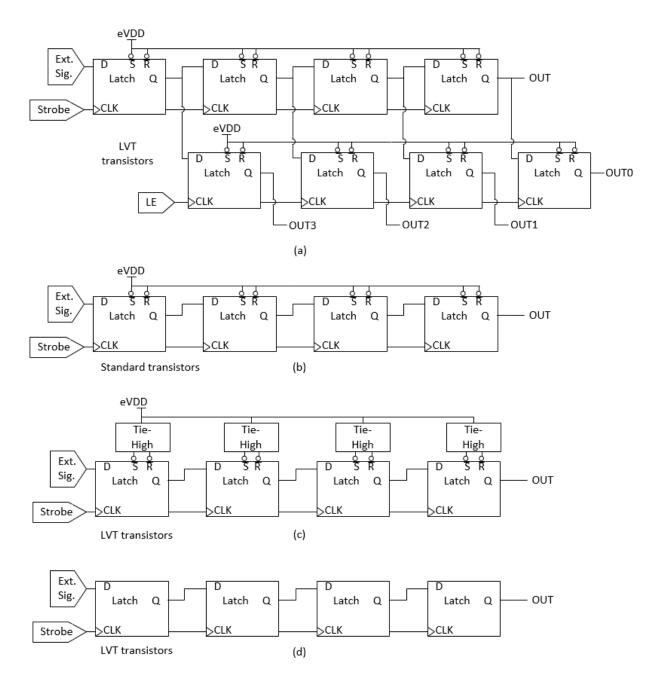

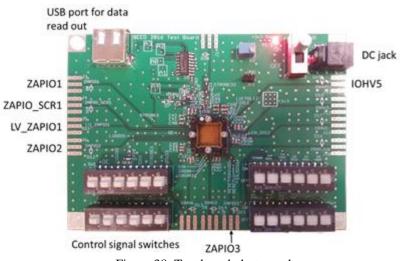

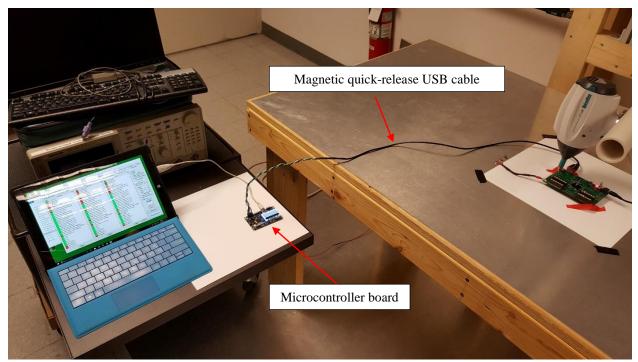

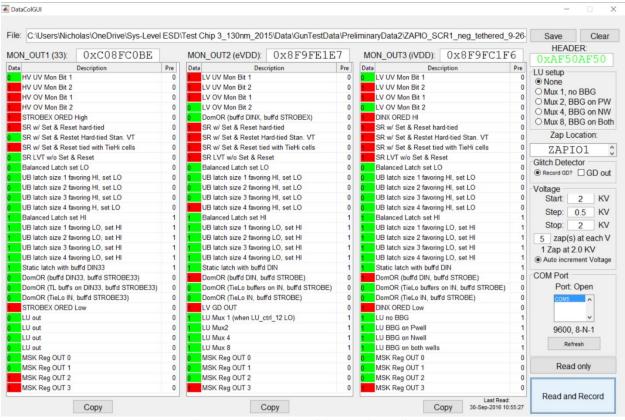

For zaps to the mobile system, only gates that had a "driven input," i.e., an input signal that ultimately originated at pin DIN, were observed to upset (addresses 6, 7, 14 and 15). The gates that have only tied-low inputs do not upset. Thus when upsets are indicated, only the gates with driven inputs are considered. Once again, a minimum of five zaps were applied for each test case and the experiment was repeated on two test chips. Table 11 provides a summary of the upsets observed when the EUT was in its mobile configuration. If any single gate was observed to upset, all of the gates did so. Only positive polarity discharges caused upsets. These upsets occurred in a window between 1 kV and 6 kV. Only zaps to IO3 caused upsets; no upsets were observed following zaps to IO4. Further, the IOs' setting—high-Z, output-low, or output-high—was found to have little influence on the results.