838583

REPORT CSG-25

DECEMBER 1983

# **COORDINATED SCIENCE LABORATORY** COMPUTER SYSTEMS GROUP

LOAN COPY

## A COMPREHENSIVE FAULT MODEL FOR CONCURRENT ERROR DETECTION IN MOS CIRCUITS

DANIEL LEE HALPERIN

COLLEG

APPROVED FOR PUBLIC RELEASE. DISTRIBUTION UNLIMITED.

**UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN**

| <u>Unclassif</u> ied |

|----------------------|

|----------------------|

THAITY CLASSIFICATION OF THIS PAGE

## PEROPT DOCUMENTATION PAGE

|                                                                                     | REPORT DOGGIMA                     |                                                        |                  |                 |               |

|-------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------|------------------|-----------------|---------------|

| BREPORT SECURITY CLASSIFICATION<br>Unclassified                                     |                                    | 15. RESTRICTIVE M                                      | IARKIINGS        |                 |               |

| 28. SECURITY CLASSIFICATION AUTHORITY                                               | 3. DISTRIBUTION/A                  | VAILABILITY C                                          | F REPORT         | ·····           |               |

| N/A                                                                                 |                                    | Approved for                                           | r public re      | lease, dist     | ribution      |

| 3. OECLASSIFICATION/OOWNGRADING SCHEDULE<br>N/A                                     |                                    | Approved for public release, distribution<br>unlimited |                  |                 |               |

| PERFORMING ORGANIZATION REPORT NUMBERIS)                                            |                                    | 5. MONITORING ORGANIZATIKON REPORT NUMBER (S)          |                  |                 |               |

| 696-25                                                                              |                                    | N/A                                                    |                  |                 |               |

| A NAME OF PERFORMING ORGANIZATION                                                   | 66. OFFICE SYMBOL                  | 74. NAME OF MONITORING ORGANIZATION                    |                  |                 |               |

| University of Illinois                                                              | (ATapplication)<br>N/A             | Office of Naval Research                               |                  |                 |               |

| ADDRESS (Rity. State and ZYP Code)                                                  |                                    | 76. ADORESS (City.                                     | State and ZIP Co | ile)            |               |

| j 1101 W. Springfield Avenue                                                        |                                    | 2511 Jeffer                                            |                  | - +             |               |

| Constitua, LETINOIS DIOUL                                                           |                                    | Arlingtom,                                             | Virginia 2       | 22202           |               |

| NAME OF FUNDING/SPONSORING                                                          | 86. OFFICE SYMBOL                  | 9. PROCUREMENT                                         | NSTRUMENT ID     |                 | i u Miblera   |

| GRGANIZATION<br>Naval Electronics Syst. Comm.                                       | (M/opplicel/le)<br>N/A             | N00039=80=C                                            | -0556            |                 |               |

| . ADDRESS (City, State and ZIP Code)                                                | 1                                  | 10. SOURCE OF FUI                                      | NDING NOS.       | •               |               |

| 2511 Jefferson Davis Highway<br>Arlingtom, Virginia 22202                           |                                    | PROGRAM<br>ELEMENT NO.                                 | PROJECT<br>NO.   | TASK<br>NO.     | WORK UNIT     |

| 7 TI DLE Include Security Class (leastion) A COM<br>MODEL FOR CONCURRENT ERROR DECT |                                    |                                                        | N/A<br>s         | N/A             | N/A           |

| PERSONAL AUTHOR(S) Daniel Lee                                                       | Halperín                           |                                                        |                  |                 |               |

| A TYPE OF REPORT 136. TIME C                                                        | OVERED                             | 14. DATE OF REPOI                                      |                  |                 |               |

| SUPPLEMENTARY NOTATION                                                              | TO                                 | December 10                                            | <u>, 1983</u>    | 2               | 06            |

| N/A                                                                                 |                                    |                                                        |                  |                 |               |

| COSATI CODES                                                                        | 1a SUBJECT TERMIS (C               |                                                        |                  |                 |               |

|                                                                                     | Concurrent Erro<br>MOS Circuits, P |                                                        |                  |                 |               |

| ······································                                              | Algebra, Totall                    |                                                        |                  |                 |               |

| ABSTRACT Continue on reverse & necessary and                                        |                                    |                                                        | 0                |                 |               |

| A comprehensive fault mo                                                            |                                    |                                                        |                  |                 |               |

| imtegrated circuits. This fa                                                        |                                    |                                                        |                  |                 |               |

| Afailures in MOS imtegrated ci                                                      |                                    |                                                        |                  | -               |               |

| are used to determine the behat this analysis that many types                       |                                    |                                                        |                  |                 |               |

| not well-defined. In particul                                                       |                                    |                                                        |                  |                 |               |

| values that are neither logic                                                       |                                    |                                                        |                  |                 |               |

| of indeterminate faults is de                                                       | ÷ ÷                                | -                                                      |                  |                 |               |

| shown that most traditional f                                                       | ault models are                    | unable to mod                                          | el the beh       | avior of a c    | circuit       |

| with an indeterminate fault c                                                       | orrectly.                          |                                                        |                  |                 |               |

| Ternary algebra is used                                                             | to facilitate th                   | e analysis of                                          | circuits wi      | nich recei∀e    | 2             |

| indeterminate value inputs.                                                         |                                    |                                                        |                  |                 |               |

| for the propagation of indete                                                       |                                    | 0                                                      |                  |                 | 1fi ((over))  |

| 915TRIBUTION/AVAILABILITY OF ABSTRAC                                                | _                                  | 21. ABSTRACT SECL                                      |                  |                 |               |

| ELASSIFIED/UNLIMITED & SAME AS RPT.                                                 |                                    | Unclassifie                                            | ď                |                 |               |

| A NAME OF RESPONSIBLE INDIVIDUAL                                                    |                                    | 225. TELEPHONE NI                                      |                  | ZZZ. OFFICE SYN | <b>1901</b> , |

|                                                                                     |                                    | APPECAGE SURG CO                                       | /"               | NOME            |               |

EDITION OF 1 LAN 73 IS OBSOLETTE.

Unclassified

#### <u>Unclassified</u>

## SECURITY CLASSIFICATION OF THIS PAGE

many cases, an indeterminate value can propagate through a circuit even when a Boolean valu cannot propagate.

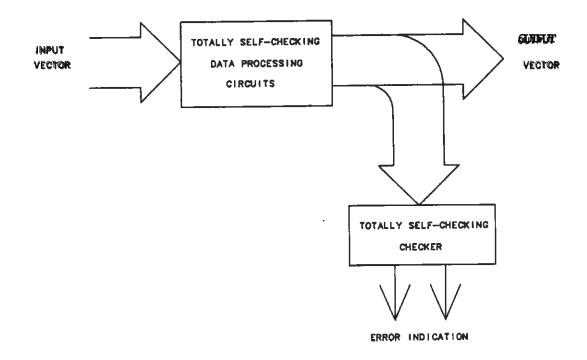

The methodology of totally self-checking systems is used to provide concurrent error detection. It is shown that the traditional definitions of the totally self-checking property are inappropriate for failures which include indeterminate faults. A new definition of the totally self-checking property is developed which is compatible with indeterminate faults. It is shown that under our fault models, duplication may be used to provide a totally self-checking implementation for any function. Procedures are developed to determine if a function has an implementation using a separable code which may provide concurrent error detection at a lower cost than duplication. Issues involved in the interconnection of several totally self-checking circuits are considered, as well as the requirements for checkers in systems which may experience indeterminate failures.

١

ā

## m Vin MARCORRERENSIS EVERILATE MARCE POR CONGREGENTIERROR POSTECCION NINIMORS CIRCULTS'S

BHY

## DANLEL LEE HALPERIN

B.S., University of Tennessee, 1978 M.S., University of Hilineis, 1981

## THESIS

Submitted in partial fulfillment of the requirements for the degree of Dostor of Philosophy in Electrical Engineering min the Gasdaate College of the g University of 111 inclis at urbana champaign, 1984

Urbehans ,1111 honeis

#### A COMPREHENSIVE FAULT MODEL FOR CONCURRENT ERROR DETECTION IN MOS CIRCUITS

Daniel Lee Halperim, Ph.D. Department of Electrical Engineering University of Illinois at Urbana-Champaign, 1984

A comprehensive fault model is developed for concurrent error detection in MOS integrated circuits. This fault model is based on a thorough examination of physical failures in MOS integrated circuits. Models of MOS circuits are also developed which are used to determine the behavior of these circuits under failure. It is found from this analysis that many types of physical failures may result in logic signals that are not well-defined. In particular, it is shown that physical failures may lead to constant values that are neither logic 0 nor logic 1, timing failures, or oscillation. The concept of indeterminate faults is developed to describe the behavior of such failures. It is shown that most traditional fault models are unable to model the behavior of a circuit with an indeterminate fault correctly.

Ternary algebra is used to facilitate the analysis of circuits which receive indeterminate value inputs. Using ternary algebra, necessary conditions are developed for the propagation of indeterminate values through a circuit. It is shown that in many cases, an indeterminate value can propagate through a circuit even when a Boolean value cannot propagate.

The methodology of totally self-checking systems is used to provide concurrent error detection. It is shown that the traditional definitions of the totally self-checking property are inappropriate for failures which include indeterminate faults. A new definition of the totally self-checking property is developed which is compatible with indeterminate faults. It is shown that under our fault models, duplication may be used to provide a totally self-checking implementation for any function. Procedures are developed to determine if a function has an implementation using a separable code which may provide concurrent error detection at a lower cost than duplication. Issues involved in the interconnection of several totally self-checking circuits are considered, as well as the requirements for checkers in systems which may experience indeterminate failures.

#### Acknowledgment

The author wishes to express deepest thanks to his advisor, Dr. Ed Davidsom, for his support, encouragement, and advice throughout this thesis project. He is deeply appreciative for the many long hours Dr. Davidson spent assisting with this thesis. The author would also like to thank Dr. Janak Fatel, Dr. Jacob Abraham, and Dr. Dan Gajski for serving on his final committee. Finally, the author would like to thank his colleagues in the Computer Systems Group for their support, ideas, and friendship.

The author would like to dedicate this thesis to his parents, Joseph and Sita Halperin, and to his wife, Beverly. The support, sacrifices, and understanding provided by the author's family have made his education in general and this thesis in particular possible.

## TABLE FOR FCONTENTS'S

| Chapter<br>Chapter                                                          | Page<br>Page                                                                                                                                            |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 <sup>1</sup> * II <del>P</del> #J@dve%ign                                 | 1                                                                                                                                                       |

| 1111. EfterrDDetectionSCtartgBies.                                          | <b>1</b>                                                                                                                                                |

| 11,22. FEATLt MODELS                                                        | <b>4</b> <sup>1</sup> <sub>4</sub>                                                                                                                      |

| 11,22,11. Ssingle Sance Art Frankt Model                                    | <b>6</b>                                                                                                                                                |

| 11.22.22. Uwiddineettionall Faultt Model                                    | <b>6</b> ,                                                                                                                                              |

| 11.22.33. Britigging Haultt Model                                           | 6<br>7 <sub>7</sub>                                                                                                                                     |

| 11.22.44. Structle Open Really Mostell                                      | <b>9</b>                                                                                                                                                |

| 11.33. Oququulaw of Research                                                | 12<br>12                                                                                                                                                |

| 2. Physical Failure Modes for MOS Integrated Cincuits                       | <b>14</b>                                                                                                                                               |

| 2.1. Interconnect Failures                                                  | 15                                                                                                                                                      |

| 2.1.1. Metal Interconnect Failures                                          | 17                                                                                                                                                      |

| 2.1.2. Polysilicon Interconnect Failures                                    | 21                                                                                                                                                      |

| 2.1.3. Diffusion Interconnect Failures                                      | 22                                                                                                                                                      |

| 2.1.4. Dielectric Failures                                                  | 24                                                                                                                                                      |

| 2.2. Transistor Failures                                                    | 27                                                                                                                                                      |

| 2.2.1. Parameter Shift Failures                                             | 27                                                                                                                                                      |

| 2.2.2. Breakdown Failures                                                   | 29                                                                                                                                                      |

| 2.3. Radiation-Induced Soft Failures                                        | 144<br>15<br>17<br>17<br>22<br>224<br>227<br>227<br>229<br>0<br>30                                                                                      |

| 2<br>3. Bohavitor of Failed Circuits                                        | <b>32</b><br>32                                                                                                                                         |

| 3.11. Summery of Failure Mechanisms                                         | 32                                                                                                                                                      |

| 3.2. Circuit Models                                                         | 36                                                                                                                                                      |

| 3.2.11. Static NMOS Dimenter Model                                          | <b>41</b>                                                                                                                                               |

| 3.22.22. Strattic (CMOS Timester Model                                      | <b>32</b><br><b>36</b><br><b>41</b><br><b>53</b><br><b>57</b><br><b>63</b><br><b>63</b><br><b>63</b><br><b>76</b><br><b>7</b><br><b>79</b><br><b>79</b> |

| 33. 22. 33. Dynamic NNKOS Inverter Modell                                   | 53<br><b>57</b>                                                                                                                                         |

| 33 33. Response off Failed Circuites                                        | 63                                                                                                                                                      |

| 33 33 11. Response of Cliccuits with Shorts                                 | <b>63</b>                                                                                                                                               |

| 33 33 22. Response of Circuits with Opens                                   | 76                                                                                                                                                      |

| 333333. Response off Circutts tooNoise                                      | 79 <b>9</b>                                                                                                                                             |

| 3344. REsponse off GGodd CEicaits too thee Olupput off as FEiled            |                                                                                                                                                         |

|                                                                             | 80<br>80<br>81<br>81                                                                                                                                    |

| 334411.Metasable eOppration                                                 |                                                                                                                                                         |

| 334.422. R Bay quotes e of f Combrinatait in the IL Logicic                 | 88<br>88                                                                                                                                                |

| 4.4. Coorcement te Error rD Detectricion no fo fPlPhyisticka 1F Fallumese s | <b>102</b>                                                                                                                                              |

| 44.1. Indeterminate Fultes                                                  | 102<br>102                                                                                                                                              |

| 44.1.1. Termany Algebra                                                     | <b>102</b><br>104                                                                                                                                       |

## TABLE OF CONTENTS (cont.)

| Chapter                                                                          | Page                 |     |

|----------------------------------------------------------------------------------|----------------------|-----|

| 4.1,2. The Effects of Hezerds on Sensitization                                   | 109                  |     |

| 4.2. Concurrent Error Detection                                                  | 114                  |     |

| 4.2.1, Totally Self-Checking Circuits                                            | 114                  |     |

| 4.2.2. Checker Strategy                                                          | 1 <b>21</b>          |     |

| 4.3. CED under a Simplified Indeterminate Fault Model                            | 128                  |     |

| 4.3.1. Fault Model Assumptions                                                   | 128                  |     |

| 4.3.2. Separable Codes                                                           | 134                  |     |

| 4.3.3. Finding Economical Totally Self-Checking Imple-                           |                      |     |

| mentations                                                                       | 140                  |     |

| 4.3.4. Check Vector Gemenation                                                   | 156                  |     |

| 4.4. CED Under a General Single Failure Indeterminate Fault                      |                      |     |

| Model                                                                            | 168                  |     |

| 4.4.1. Fault Model Assumptions and Properties                                    | 168                  |     |

| 4.4.2. Economical Implementations for the General In-<br>determinate Fault Model | 173                  | 173 |

| 4.4.3. Check Vector Generation                                                   | <b>1718</b> 78       |     |

| 4.5. Checker Requirements                                                        | 179                  | 179 |

| 5. Conclusion                                                                    | 185                  |     |

| 5.1. Evaluation of Fault Model                                                   | 185                  | 185 |

| 5.1.1. Fault Model Accuracy                                                      | <b>185</b> 85        |     |

| 5.1.2. Ease of Analysis                                                          | 189                  | 189 |

| 5.1.3. Cost of Fault Tolerance                                                   | <b>191</b> 91        |     |

| 5.2. Summery                                                                     | <b>194</b> 94        |     |

| 5.3. Suggestions for Future Research                                             | <b>197</b> 97        |     |

|                                                                                  |                      |     |

| References                                                                       | <b>19<u>9</u></b> 99 |     |

| Vita                                                                             | 20 <u>¢</u> 06       |     |

¥

## LISTI OF HIGHRERES

| Fia                             | ure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Figure                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page          |

| 1.1.                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page          |

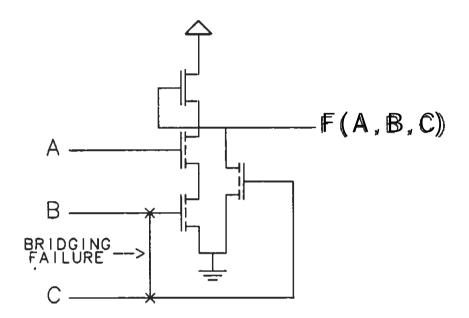

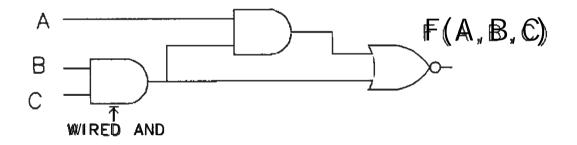

| 1.1*2,                          | An Example of a Wired-AND Bridging Fault<br>A CMOS NAND Gate with a Stuck-Open Fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

| <b>1.2</b> .<br>1.3.            | A CMOS NAND Gate with a Stuck-Open Fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10            |

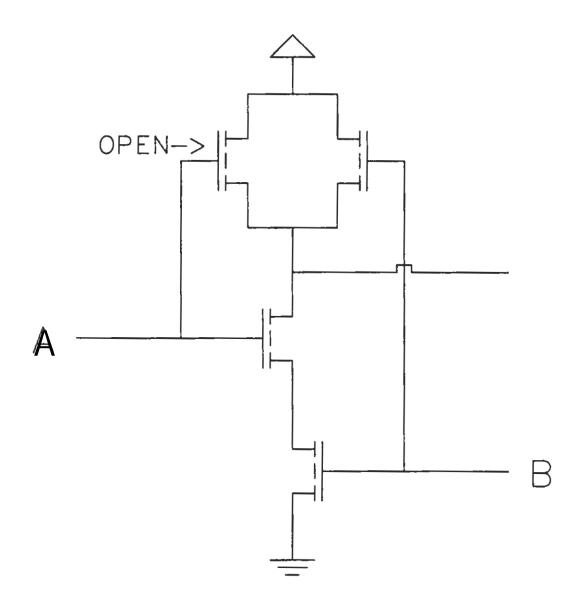

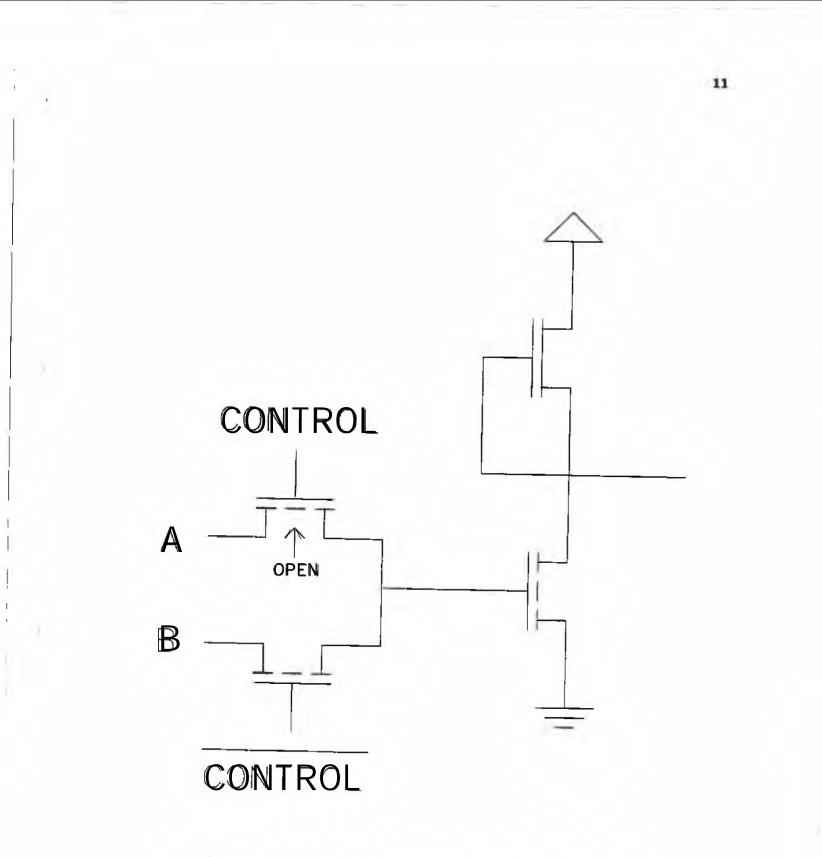

| 1.3.                            | An NMOS Siggentie ith a Style cropped and it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11            |

| 2,1.<br><b>2.1</b> .            | SummyrbfofschlahingeFettfors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16            |

| 3.1.                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

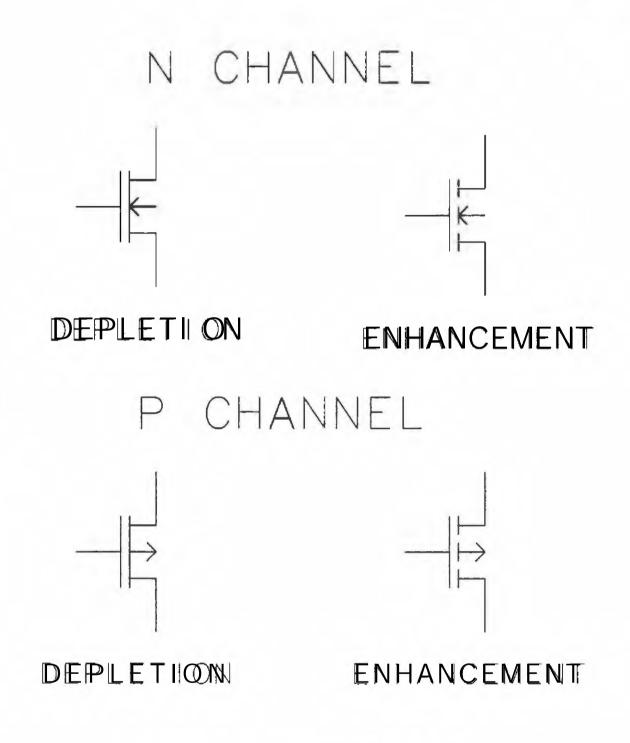

| 3,1,2.                          | MOSOST Transfectors y Storios s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37            |

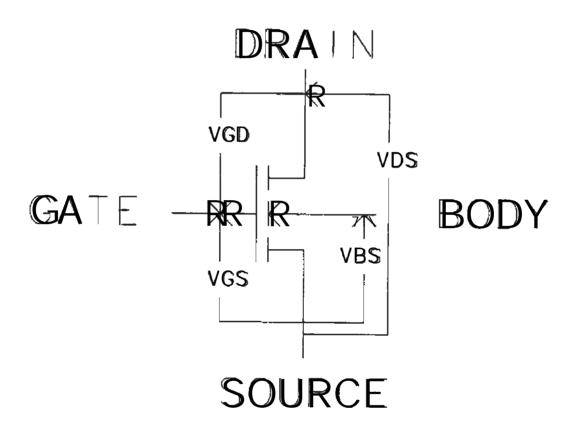

| 3.2.                            | Definitions of Voltages and Polarities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39            |

| 3 3.4                           | NMOS IntereserCfieget                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42            |

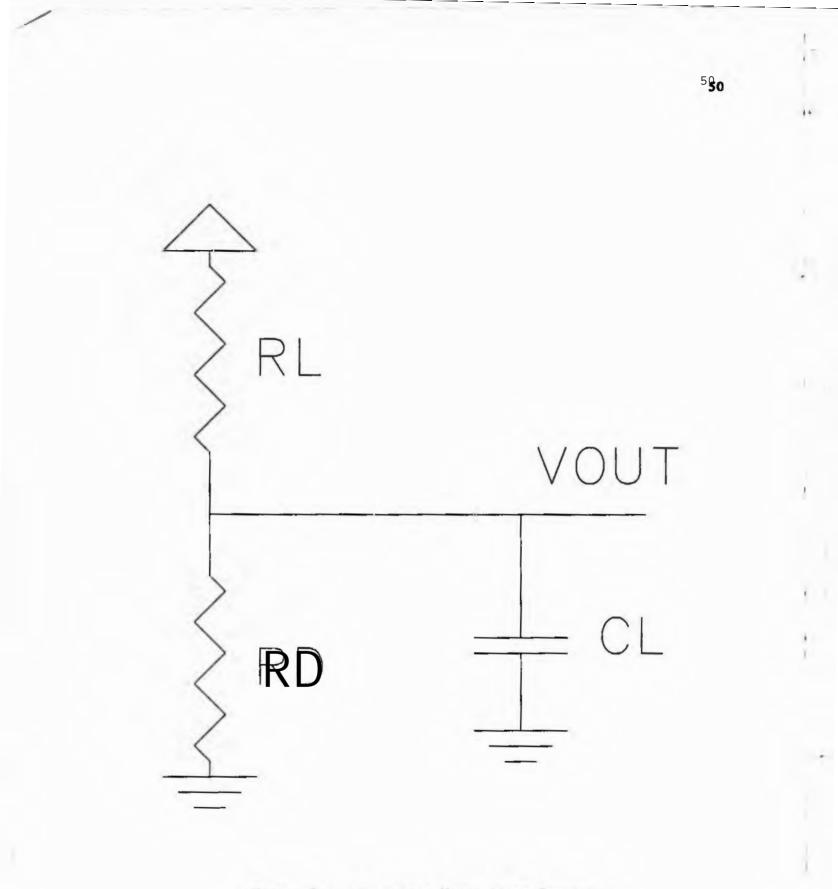

| 3 <sub>3</sub> 4 <sub>5</sub> . | RBssietive MWadtlopfan IAvverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50            |

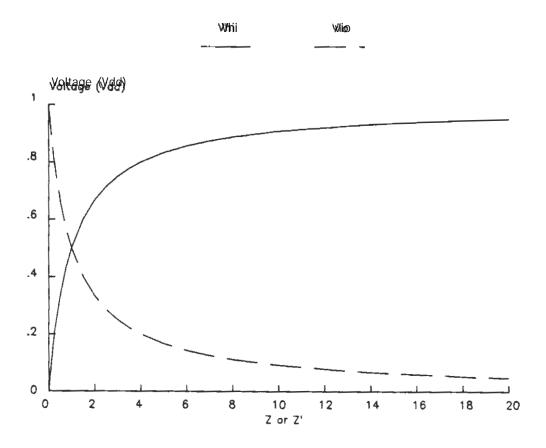

| 3356                            | Voltage Limits vs. Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51            |

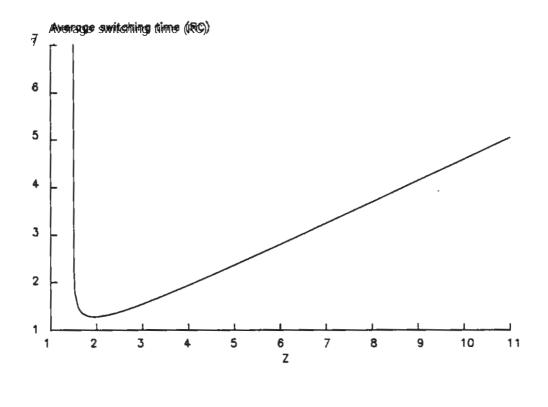

| 33.67                           | Awerge Switching Timeevs. Z2 Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54            |

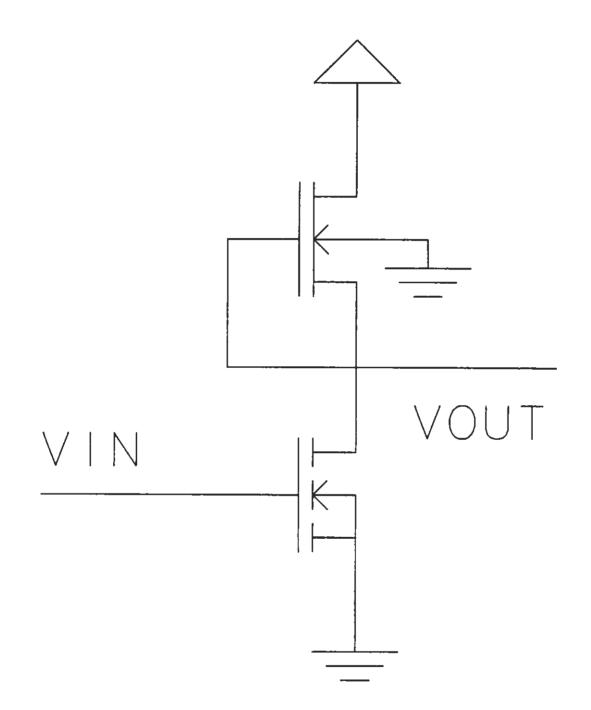

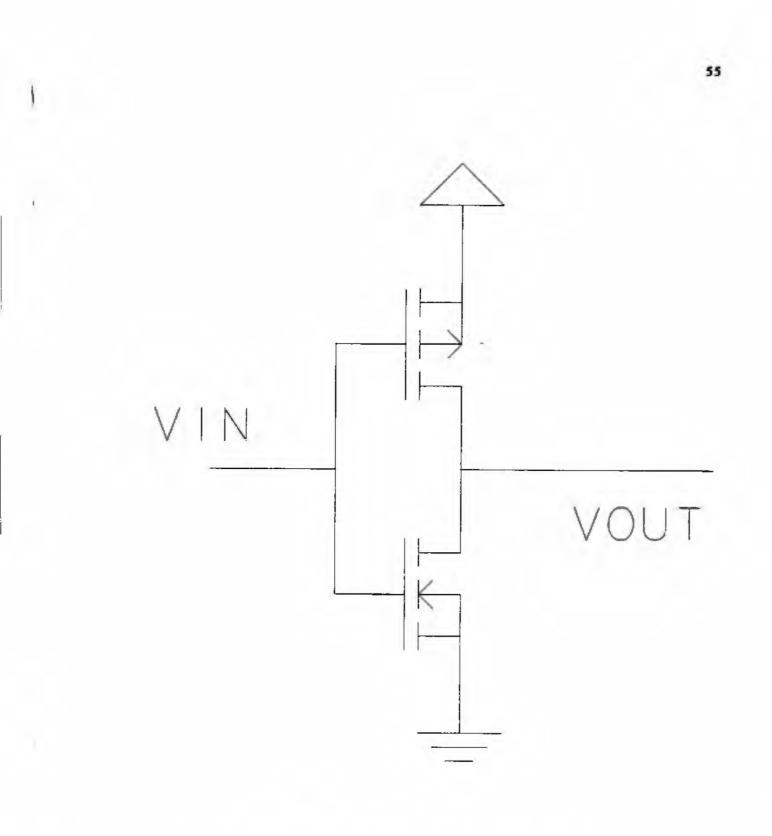

| 3.78.                           | CHOSS ILventer Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55            |

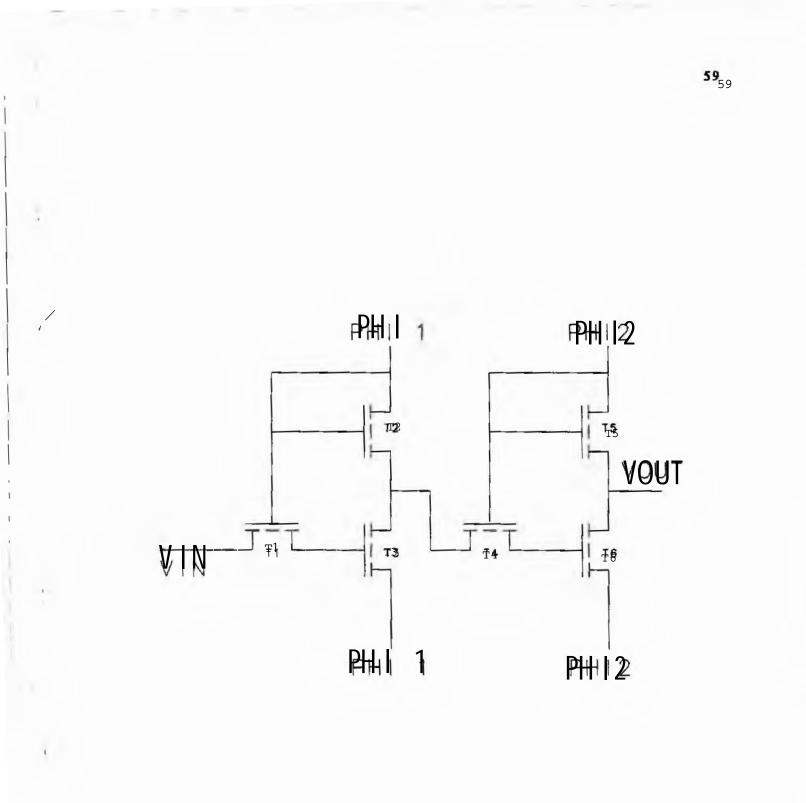

| <b>3.8</b> .                    | Dynamic Shift Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 595           |

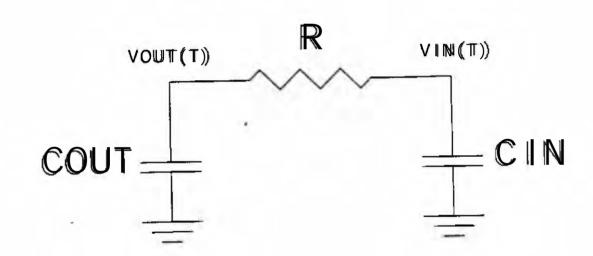

| <b>3.9</b> .<br>3.10.           | Resistive Model of Coupling Transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 629           |

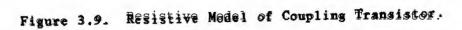

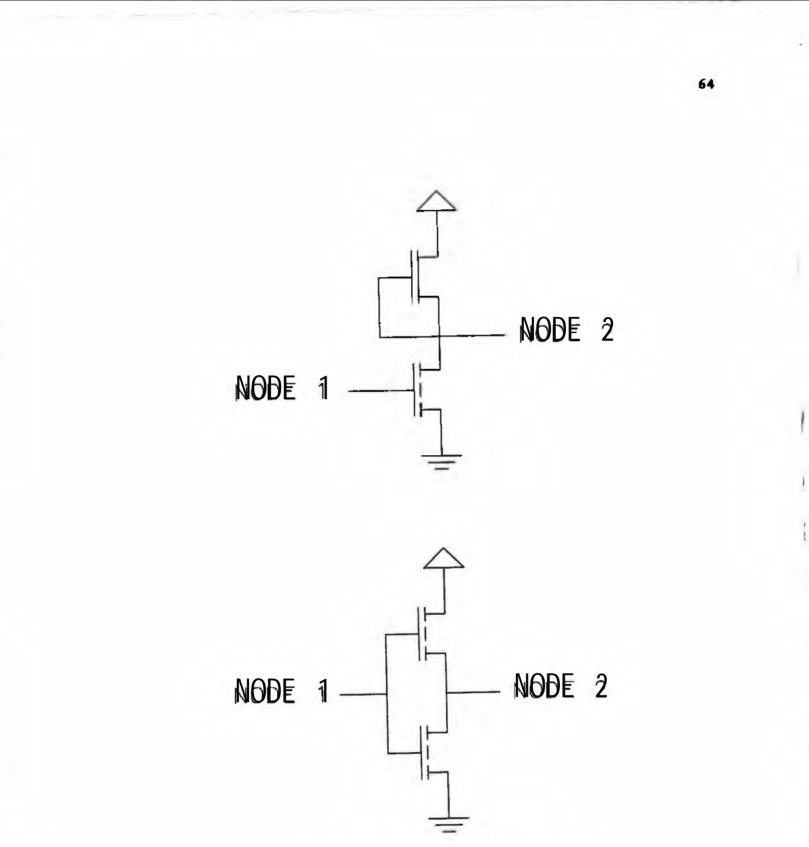

| 3.10.<br>3.10.                  | NMUS and CNOS Lawerters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64            |

| <b>3.11</b> .<br>3.12.          | Output Node to Input Node Short                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67            |

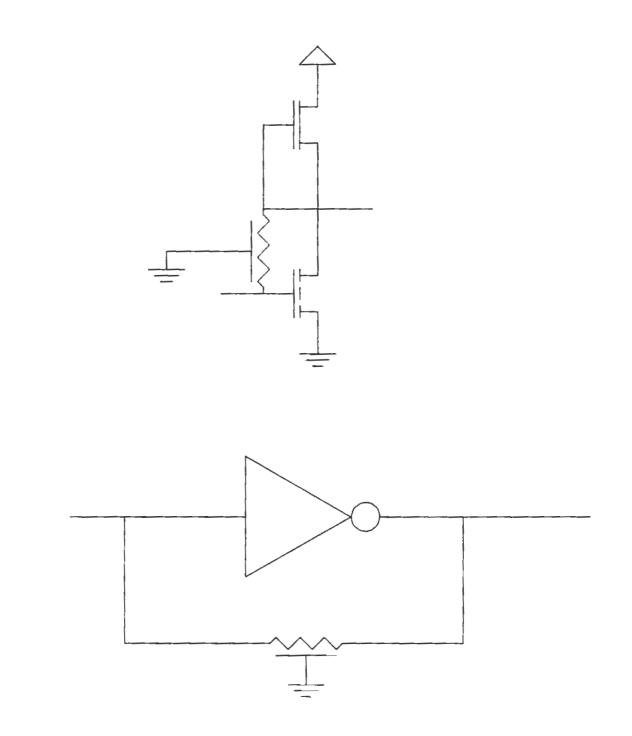

| 3.12.<br>3.12.<br>3.13.         | Resistive Model of Failed Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63            |

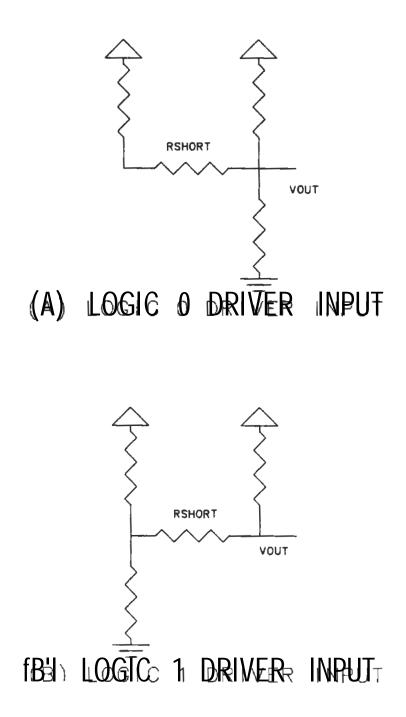

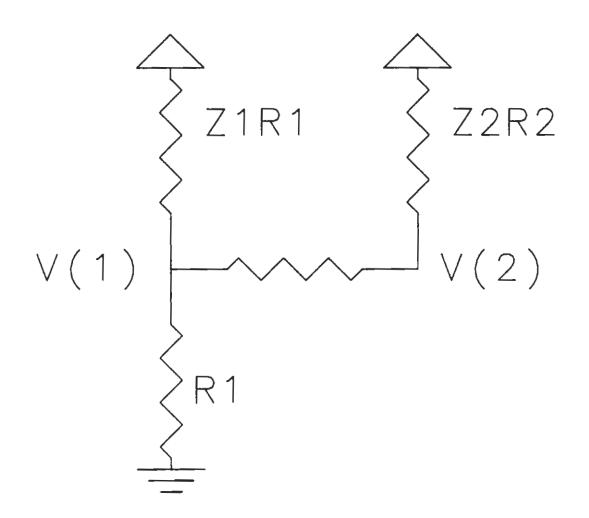

| 3.13.<br>3.13.<br>3.14.         | Resistive Model of Two Outputs Shorted Together                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>9</b> 2    |

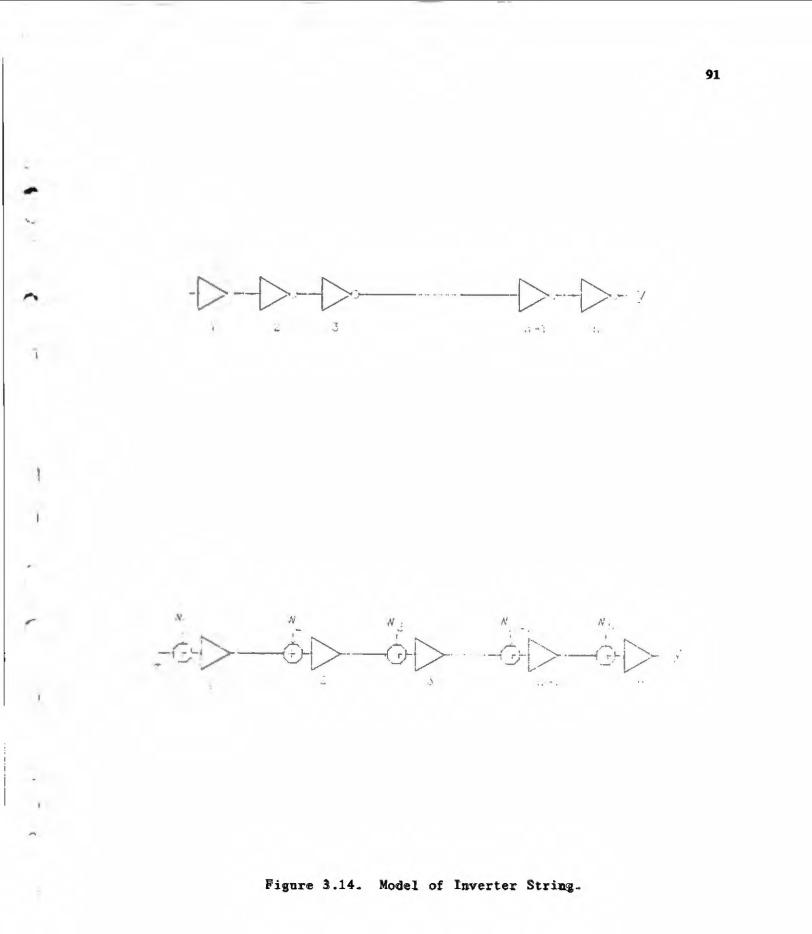

| 3.14.<br>3.14.<br>3.15          | Resistive Model of Two Outputs Shorted Together<br>M: ; 1r: 18 MOdel of TWO<br>Model of Inverter String                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3₽            |

| 3.15                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91            |

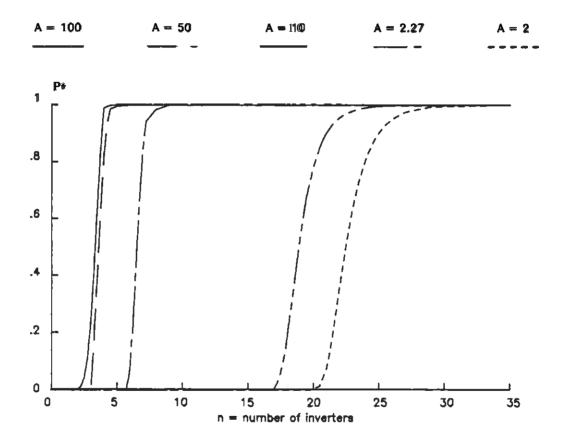

| 3.16                            | Probability of x 2 a vs. Number of Inverters for<br>Small Noise Small Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 94            |

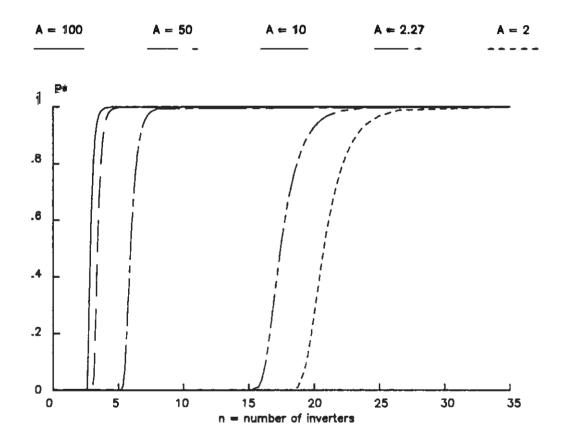

| 3.16.                           | Probability of  y  ≥ a vs. Number of Inverters for<br>Large Noise 1 ° vs* N™ b*r of Inverters for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 94            |

|                                 | Large Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 96            |

| 4.1.                            | manual algorithm manual and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 96            |

| 4.2.1.                          | TEFRAYyAAsgebra Truch Tebres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 106           |

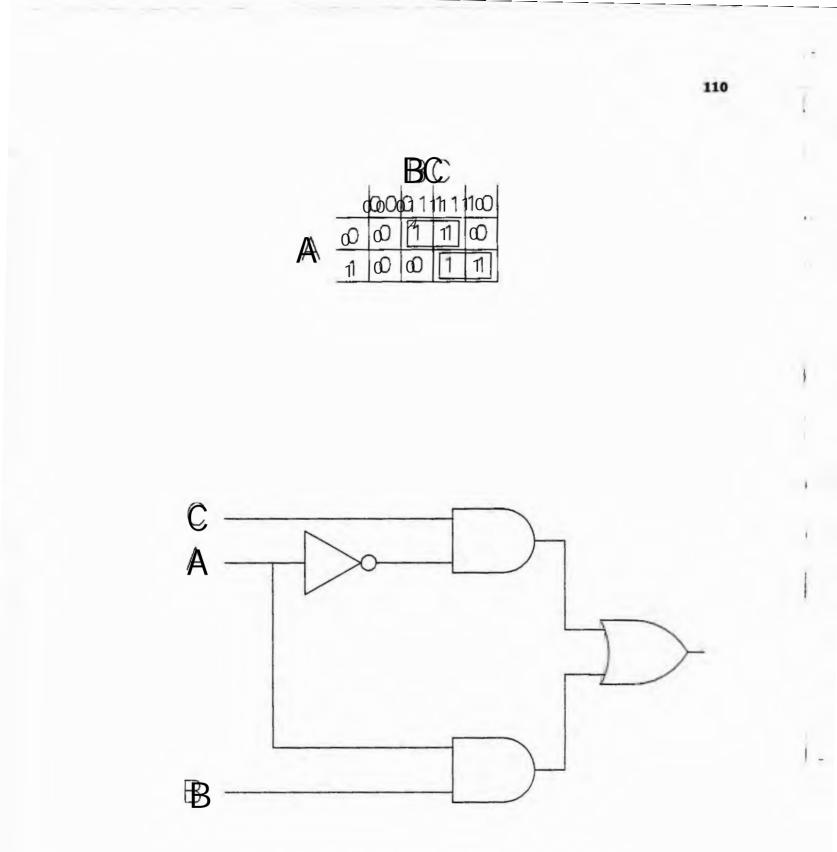

| 4.32.                           | ERREAD'S e offaa StatigeHEREE'S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1990          |

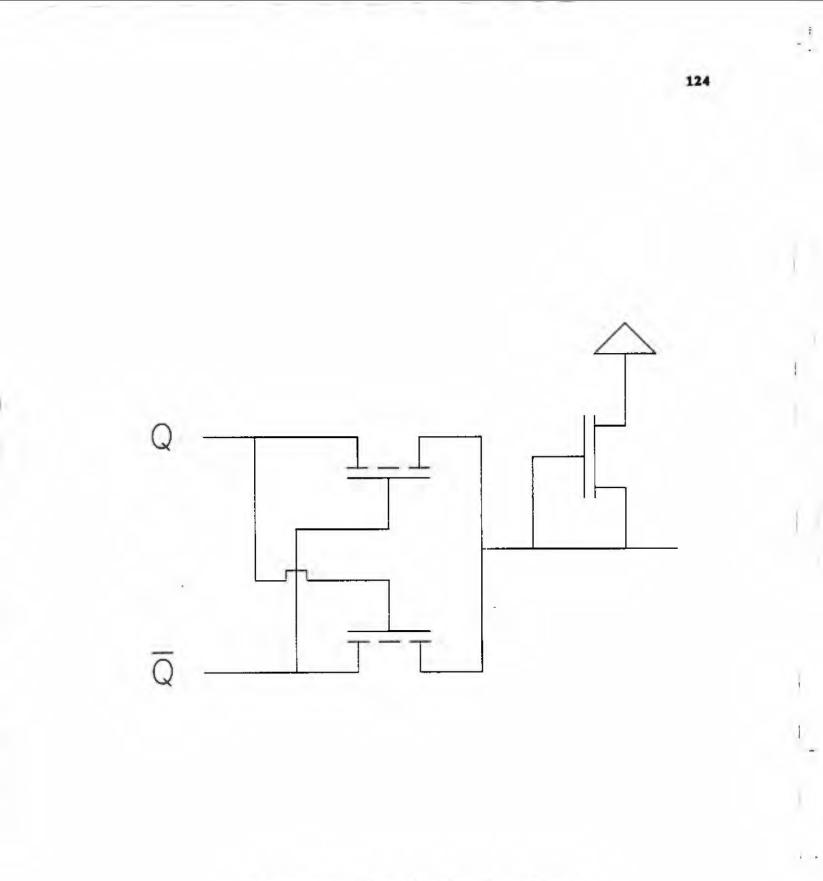

| 4.4.3.                          | Totally yStal feback king Modelel e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 119           |

| 4.5.4.                          | Moleanstalabs e Doese cignon Ciscitit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1184          |

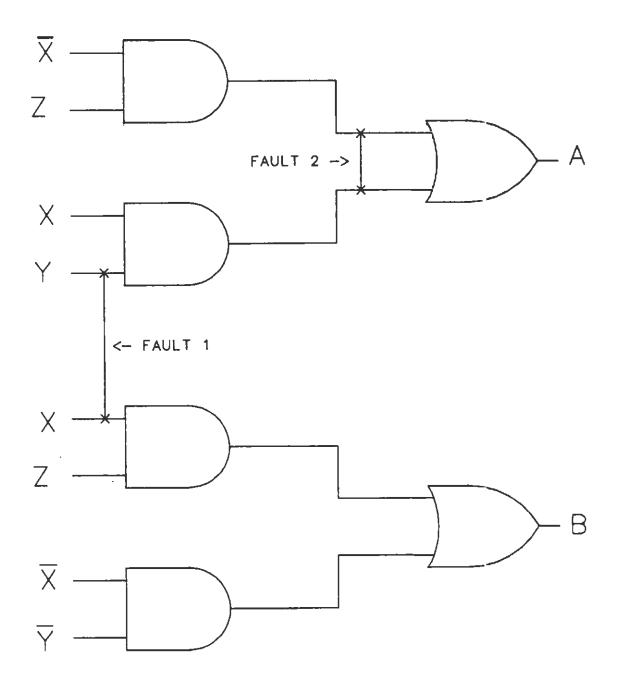

| 4.6.5.                          | Twoy Jygge so to fB1Biroigtiging graffentist s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12130         |

| 4.4.6.                          | Possible facuari tInforpeneoretratation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13033         |

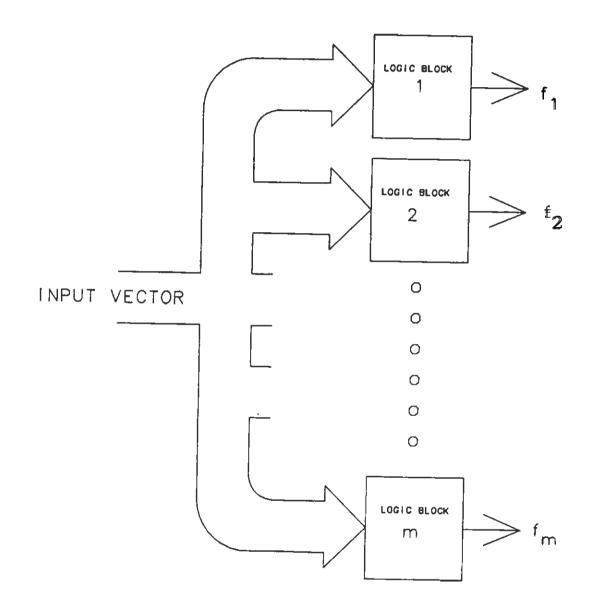

| 4.8:7.                          | Circuit Implementation with Shared Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13 <b>335</b> |

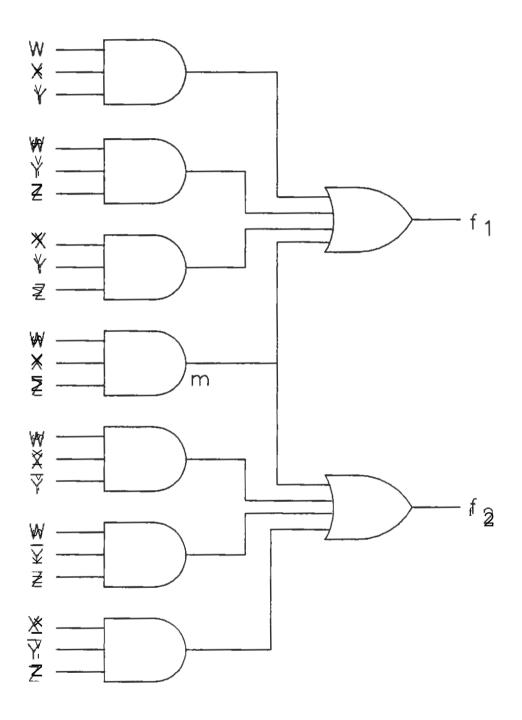

| 4.9.8.                          | Full Adder Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13643         |

| 4.10.                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14 <b>346</b> |

| 4.11.                           | and a second s | 14950         |

| <b>4,12</b>                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 <b>957</b> |

| 4 13.12.                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15759         |

| 4.14.13.                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 159174        |

| 4.14.                           | Addam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17476         |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 176           |

**vi** vi

#### CHAPTER 1

#### Introduction

#### <u>1\*1\* Error Detection Strategies</u>

As integration levels increase and more and more devices are placed on an integrated circuit, it becomes increasingly difficult to insure that a circuit and the system it is part of are operating properly. There are two basic approaches to this problem: off-line testing and concurrent error detection.

In off-line testing, the system is stopped periodically and a test procedure is performed. This test may be performed by the system itself, or an external tester may be used to stimulate the circuit and check its results. If the system successfully completes the test, then the assumption is made that the system is operating correctly. If the system fails the test, then the system is faulty. In this approach, since it is unknown exactly when the system failed, all computations performed since the last successful test procedure must be presumed erromeous.

The main advantage of using off-line testing is its simplicity. In most cases, only a very modest amount of additional on-chip hardware is required. Unfortunately, there are also many disadvantages. Because of the poor observability and controllability of VLSI circuits, it is very difficult to derive a test procedure that will completely test an entire

integrated circuit. Often it is necessary to add additional logic on the integrated circuit to increase its controllability and/or observability [1]: In addition, during the time the system is off-line for testing, it cannot perform any useful computation and thus system throughput is degraded. Since there is no way of pinpointing exactly when a failnre has occurred; all results produced since the last successful testing procedure must be discarded. Alternatively some type of check-pointing scheme can be used. This approach involves saving enough of the system state and data so that all computations performed since the last successful test procedure can be repeated. The most serious drawback of off-line testing# however# is its inability to protect against intermittent errors. It has been reported [2] that between 90 and 98 percent of failures in computers are nonpermanent in nature. Off-line testing gives little if any protection against nonpermanent failures. Therefore, for any system in which we must immediately know when a failure has occurred (i.e.# any type of real-time system) or for any system in which we expect a major fraction of errors to be intermittent, off-line testing is inadequate.

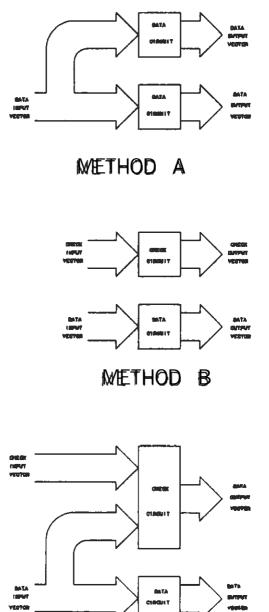

The second approach to this problem is concurrent error detection. In this approach# the system is divided up into one or more blocks called modules. The inputs (including both data and control vectors) and outputs of each module must be encoded with an appropriate code. Obviously# such encoding requires additional logic. These codes are selected so that when most failures occur# the result of a computation will either be correct or a non-codeword. Checkers are placed at the output of each module. These checkers are used to detect non-codewords and thus indicate an error.

Concurrent error detection has several advantages. When an error occurs, the checkers immediately provide an error indication. With off-line testing, an error indication is only given after the off-line test procedure is performed. The lack of information concerning the precise time at which the failure occurred requires computations to be repeated. An immediate error indication eliminates the need to repeat computations. Protection is albee provided aggainst intermittent failures. If an intermittent failure results in an error, it will be detected. Therefore, concurrent error detection is well suited for real time systems and any system in which intermittent failures are a significant percentage of total failures.

The presence of checkers can greatly increase the observability of the circuit. If enough checkers are used, it is possible to completely or very nearly completely test a circuit simply by normal operation. Complete testing during normal operation prevents a buildup of undetected failures (the so-called "latent faults" problem). Since any concurrent error detection technique can only handle a limited number of failures, a buildup of latent faults can result in an error not being detected. If the checkers do not provide enough observability to detect all possible faults during normal operation, periodic testing must be used to detect any latent faults.

The major disadvantage of concurrent error detection is the additional logic required. The codes used for data and control vectors

3

require redundant bits. Extra logic is needed to process these bits. Additional logic is also needed for checkers. The logic which must be added to implement concurrent error detection can be significant. Depending on exactly which concurrent error detection scheme is used; the additional logic required may be more than 100 percent of the original system. Whether this type of extra cost is justified is obviously an engineering judgment. It is possible to use only concurrent error detection for those parts of the system which are either judged most likely to fail or whose failure would be most serious. Depending on what portions of the circuit are protected, significant savings of hardware are possible. A technique has been developed recently for various arithmetic computations [3]. This technique employs time redundancy rather than logic redundancy. Although it is not applicable to all functions, time redundancy, where it is applicable, can provide concurrent error detection with only a very modest amount of additional logic but at the cost of additional time.

## 1.2. Fault Models

The purpose of a fault model is to describe the behavior of a physical failure in a manner that will allow us to predict the logical behavior of the failed system. Since in general, a physical failure affects the analog behavior of a circuit (i.e., gain, time constants, etc.) it may be very difficult to describe exactly how the failure will alter the logical behavior of the system. A fault model has three important attributes: accuracy, ease of analysis, and cost of fault tolerance.

4

i

If the fault model does not accurately describe the logical behavior of physical failures, then it is of little use. The quality of an error detection scheme is measured by the fraction of faults in the fault model which are detectable. Clearly, if the model does not accurately describe the behavior of physical failure, this measure is of little use.

Two factors contribute to the ease of analysis of a fault model: the number of faults which must be considered, and the complexity of the fault behavior. Any system which contains many thousands of logic elements will also have a large number of possible faults. The behavior described by the fault model must be simple enough to allow analysis of the system. For off-line testing, we must determine whether the test procedure will detect each fault. For concurrent error detection, we must insure that the encoding used will allow detection of an incorrect result. If the fault model is too complex, this analysis will be too difficult to perform and the fault model will be impractical. One technique which can greatly reduce the number of faults is fault collapsing. Fault collapsing can be done when two or more faults are indistinguishable. Fault collapsing makes it is possible to reduce significantly the number of faults which need to be considered.

Cost of fault tolerance is a very important consideration since it strongly affects system cost. For off-line testing, cost of fault tolerance determines how large the test procedure must be. It may also influence the complexity of the tester hardware. For concurrent error detection, cost of fault tolerance determines how much extra logic must be added to the original system. Cost of fault tolerance is usually highly dependent on the exact nature of the error detection scheme and the target system.

The selection of a fault model requires a tradeoff between accuracy; ease of analysis; and cost of fault tolerance. Since these requirements are usually conflicting; the choice is never easy. In the past; a variety of fault models have been proposed.

#### 1.2.1. Single Stuck-At Fault Model

The single stuck-at fault model assumes that any physical failure will cause one node (wire) of the circuit to become permanently either a logic 1 or a logic 0. This model is extremely easy to use and is by far the most common fault model in use. It was first proposed when logic elements were built from discrete devices and is generally accurate in describing the behavior of failures in such devices [4]. Unfortunately, its accuracy is much poorer for the highly integrated logic elements which make up most of today's systems.

## 1.2.2. Unidirectional Fault Model