UILU-ENG-03-2218 CRHC-03-09

# ENHANCEMENT OF THE ILLINOIS SCAN ARCHITECTURE FOR MULTIPLE SCAN INPUTS AND TRANSITION FAULTS

Mihir Atul Shah

Coordinated Science Laboratory 1308 West Main Street, Urbana, IL 61801 University of Illinois at Urbana-Champaign

| REPORT                                                                                                                                                                                                    | DOCUMENTATION F                                                                                                                                                                                                               | AGE                                                                                                                                                                                                                                       | Form Approved<br>OMB NO. 0704-0188                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public reporting burden for this collection<br>gathering and mantaining the data need<br>collection of information, including sugge<br>Davis Highway, Suite 1204, Arlington, VA                           | of Information is estimated to average 1 hour per<br>ad, and completing and reviewing the collection of<br>stions for reducing this burden, to Washington He<br>22202-4302, and to the Office of Management ar                | response, including the time for reviewi<br>information. Send comment regarding to<br>adquarters Services, Directorate for info<br>ad Budget, Paperwork Reduction Project                                                                 | ng instructions, searching existing data sources,<br>his burden estimates or any other aspect of this<br>ormation Operations and Reports, 1215 Jefferson<br>ct (0704-0188), Washington, DC 20503.                     |

| 1. AGENCY USE ONLY (Leave blan                                                                                                                                                                            |                                                                                                                                                                                                                               | 3. REPORT TYPE A                                                                                                                                                                                                                          | ND DATES COVERED                                                                                                                                                                                                      |

| TITLE AND SUBTITLE<br>Enhancement of the I<br>Scan Inputs and Tran                                                                                                                                        | llinois Scan Architectu<br>sition Faults                                                                                                                                                                                      | re for Multiple                                                                                                                                                                                                                           | 5. FUNDING NUMBERS<br>SRC 99-TJ-717                                                                                                                                                                                   |

| AUTHOR(S)<br>Mihir Atul Shah                                                                                                                                                                              |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |

| 7. PERFORMING ORGANIZATION<br>University of Illino<br>Coordinated Science<br>1308 W. Main St.<br>Urbana, IL 61801                                                                                         | is                                                                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                     | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER<br>UILU-ENG-03-2218<br>(CRHC-03-09)                                                                                                                                       |

| SPONSORING/MONITORING<br>Semiconductor Resear<br>P.O. Box 12053<br>Research Triangle Pa                                                                                                                   |                                                                                                                                                                                                                               | ES)                                                                                                                                                                                                                                       | 10. SPONSORING / MONITORING<br>AGENCY REPORT NUMBER                                                                                                                                                                   |

| I. SUPPLEMENTARY NOTES                                                                                                                                                                                    |                                                                                                                                                                                                                               | <b>_</b>                                                                                                                                                                                                                                  |                                                                                                                                                                                                                       |

|                                                                                                                                                                                                           |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |

| 2a. DISTRIBUTION / AVAILABILIT                                                                                                                                                                            | Y STATEMENT                                                                                                                                                                                                                   |                                                                                                                                                                                                                                           | 12 b. DISTRIBUTION CODE                                                                                                                                                                                               |

| Approved for public releas                                                                                                                                                                                | se; distribution unlimited.                                                                                                                                                                                                   |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |

| B. ABSTRACT (Maximum 200 wor                                                                                                                                                                              |                                                                                                                                                                                                                               | I                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       |

| important. As tr<br>complexity of test<br>the test application<br>the reduction of test<br>needs to be stored.<br>effectiveness in re<br>for further reducin<br>chains, called Mul<br>of groups, which of | ing increases. This leads to<br>a process, which increases the<br>st cost by shortening test app<br>We give an analysis of the<br>ducing test data volume and<br>ag test data volume and test<br>tiple Group ILS. In addition | ne smaller and transi<br>an increase in the test<br>le test cost. In this the<br>dication time and redu-<br>Illinois Scan Architec<br>test application time.<br>application time invo<br>n, we present several a<br>oup ILS. Lastly, we e | istor density increases, the<br>time for test generation and<br>sis, we present methods for<br>cing the volume of data that<br>ture (ILS) and determine its<br>We propose a new method<br>olving the grouping of scan |

| 4. SUBJECT TERMS ILS, s                                                                                                                                                                                   | hared scan-in, multiple                                                                                                                                                                                                       | groups, transitio                                                                                                                                                                                                                         | n. 15. NUMBER IF PAGES                                                                                                                                                                                                |

| fault                                                                                                                                                                                                     |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                           | 73<br>16. PRICE CODE                                                                                                                                                                                                  |

| 7. SECURITY CLASSIFICATION<br>OR REPORT<br>UNCLASSIFIED                                                                                                                                                   | 18. SECURITY CLASSIFICATION<br>OF THIS PAGE<br>UNCLASSIFIED                                                                                                                                                                   | 19. SECURITY CLASSIFIC<br>OF ABSTRACT<br>UNCLASSIFIED                                                                                                                                                                                     | UL                                                                                                                                                                                                                    |

| SN 7540-01-280-5500                                                                                                                                                                                       |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                           | Standard Form 298 (Rev. 2-89)<br>Prescribed by ANSI Std. 239-18<br>298-102                                                                                                                                            |

#### ENHANCEMENT OF THE ILLINOIS SCAN ARCHITECTURE FOR MULTIPLE SCAN INPUTS AND TRANSITION FAULTS

BY

#### MIHIR ATUL SHAH

B.S., University of Illinois at Urbana-Champaign, 2001

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2003

Urbana, Illinois

## ABSTRACT

As VLSI circuits continue to become more complex, the cost of testing becomes increasingly important. As transistor feature sizes become smaller and transistor density increases, the complexity of testing increases. This leads to an increase in the test time for test generation and the test application process, which increases the test cost. In this thesis, we present methods for the reduction of test cost by shortening test application time and reducing the volume of data that needs to be stored. We give an analysis of the Illinois Scan Architecture (ILS) and determine its effectiveness in reducing test data volume and test application time. We propose a new method for further reducing test data volume and test application time involving the grouping of scan chains, called Multiple Group ILS. In addition, we present several algorithms for the reduction of groups, which can be used for Multiple Group ILS. Lastly, we extend the ILS methodology for testing transition faults and provide an analysis. To my parents

Î

# ACKNOWLEDGMENTS

I would like to thank my adviser, Prof. Janak Patel, for all his help and guidance with my research, and also for pointing me in the right direction when I needed it. Also I am thankful of my family for supporting me and encouraging me to finish my work. Lastly, I am thankful for my friends for delaying my research and making me appreciate my stay here at the University of Illinois.

# TABLE OF CONTENTS

| CI | HAPT | TER PA                                             | GE |

|----|------|----------------------------------------------------|----|

| 1  | INT  | TRODUCTION                                         | 1  |

|    | 1.1  | Organization of the Thesis                         | 5  |

| 2  | INT  | TRODUCTION TO ILLINOIS SCAN ARCHITECTURE           | 6  |

|    | 2.1  | Test Generation Procedure for ILS                  | 7  |

|    | 2.2  | Experimental Results                               | 8  |

|    | 2.3  | Summary                                            | 18 |

| 3  | MU   | JLTIPLE GROUP ILS                                  | 19 |

|    | 3.1  | Introductory Information                           | 19 |

|    |      | 3.1.1 Preliminary example                          | 20 |

|    |      | 3.1.2 Compatibility definitions                    | 22 |

|    | 3.2  | Test Generation Procedure                          | 23 |

|    |      | 3.2.1 Compatibility analysis                       | 24 |

|    | 3.3  | Experimental Results                               | 27 |

|    | 3.4  | Multiple Group ILS Using Only a Single Mode        | 35 |

|    | 3.5  | Summary                                            | 37 |

| 4  | GR   | OUP REDUCTION FOR MULTIPLE GROUP ILS               | 38 |

|    | 4.1  | Addition of Inverse Chains for Compatibility       |    |

|    |      | Analysis                                           | 38 |

|    | 4.2  | Edge Reduction of an Incompatibility Graph         | 40 |

|    |      | 4.2.1 Edge reduction using compatibility relations | 40 |

|    |      | 4.2.2 Edge reduction using multiple ATPG runs      | 42 |

|    |      | 4.2.3 Edge reduction using vector elimination      | 44 |

|   | 4.3 | Summary                                                | 47 |

|---|-----|--------------------------------------------------------|----|

| 5 | ILS | WITH TRANSITION FAULTS                                 | 48 |

|   | 5.1 | Preliminaries on Transition Faults                     | 48 |

|   | 5.2 | Transition Fault Implementation for Full-Scan Circuits | 49 |

|   |     | 5.2.1 Modifications to the ATPG and fault simulator    | 50 |

|   | 5.3 | Test Generation Procedure for ILS                      | 51 |

|   | 5.4 | Experimental Results                                   | 53 |

|   | 5.5 | Summary                                                | 59 |

| 6 | CO  | NCLUSIONS AND FUTURE RESEARCH                          | 60 |

|   | 6.1 | Future Research                                        | 61 |

|   | REI | FERENCES                                               | 63 |

# LIST OF TABLES

1

-

| TA  | BLE                                                             | PA | GE |

|-----|-----------------------------------------------------------------|----|----|

| 2.1 | Characteristics of Tested Circuits                              |    | 9  |

| 2.2 | Results for Full Scan Circuits                                  |    | 10 |

| 2.3 | Results for Various ILS Configurations for Circuit s38584.1     |    | 12 |

| 2.4 |                                                                 |    | 15 |

| 2.5 | Test Data Volume Reduction Using ILS                            |    | 16 |

| 3.1 | Results for Multiple Group ILS on Various Configurations        |    | 28 |

| 3.2 | Test Data Volume Reduction Using Multiple Group ILS             |    | 31 |

| 3.3 | Test Application Time Reduction Using Multiple Group ILS        |    | 33 |

| 3.4 | Experimental Results for Multiple Group ILS Using a Single Mode |    | 36 |

| 4.1 | Characteristics of Given Industrial Circuit                     |    | 45 |

| 4.2 | Test Data Volume for Circuit A Using Vector Elimination         |    | 46 |

| 5.1 | Results for Full Scan Circuit for Transtition Faults            |    | 54 |

| 5.2 | Test Application Time Reduction Using ILS for Transition Faults |    | 57 |

| 5.3 | Test Data Volume Reduction Using ILS for Transition Faults      |    | 58 |

# LIST OF FIGURES

| FIG | URE                                                                      | PAGE |

|-----|--------------------------------------------------------------------------|------|

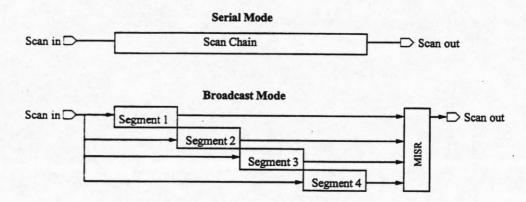

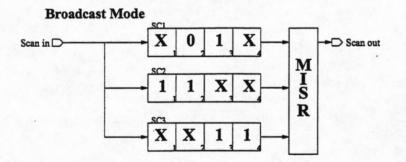

| 2.1 | Two Modes of Illinois Scan Architecture                                  | 6    |

| 2.2 | Test Generation Procedure for ILS                                        | 8    |

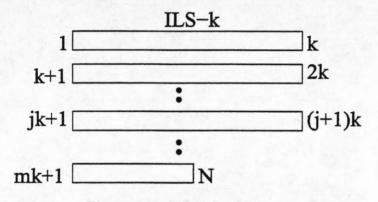

| 2.3 | ILS-k Configuration                                                      | 11   |

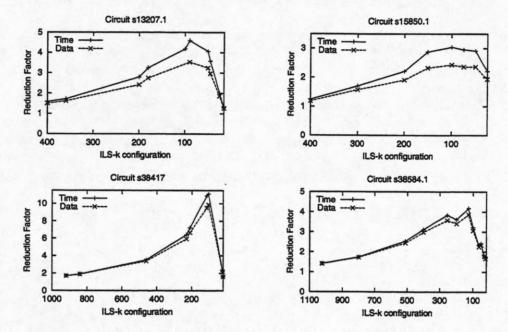

| 2.4 | Time and Data Reduction Factor versus ILS Configuration                  | 18   |

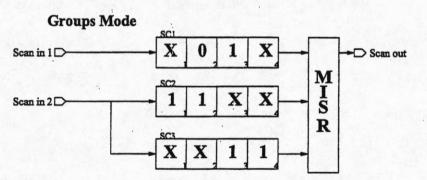

| 3.1 | Example of an Untestable Fault in Broadcast Mode of ILS                  | 20   |

| 3.2 | Previous Example Using Groups Mode                                       | 21   |

| 3.3 | Test Procedure for Using Broadcast and Groups Mode                       | 24   |

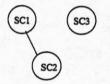

| 3.4 | Incompatibility Graph for Example Shown in Figure 3.1                    | 25   |

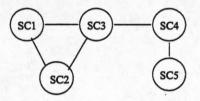

| 3.5 | Incompatibility Graph with Maximum Clique of Size 3 (SC1,SC2,SC3)        | 26   |

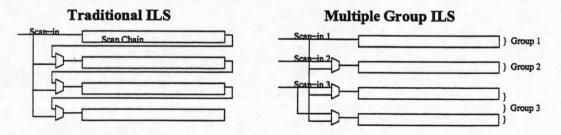

| 3.6 | Structure of Traditional ILS versus Multiple Group ILS                   | 34   |

| 4.1 | Procedure for Compatibility Analysis Using Both Inverted and Noninverted |      |

|     | Chains                                                                   | 39   |

| 4.2 | Example of Compatibility Relations between ILS Configurations            | 41   |

| 4.3 | Procedure for Edge Reduction Using Multiple ATPG Runs                    | 43   |

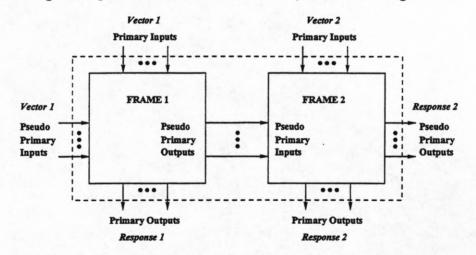

| 5.1 | Two Frame Circuit Using the Functional Justification Technique [15]      | 49   |

| 5.2 | Modification of the ATPG to Inject a Transition Fault                    | 51   |

| 5.3 | Test Generation Procedure for ILS for Transition Faults                  | 52   |

## CHAPTER 1

## INTRODUCTION

As VLSI circuits continue to become more complex, the cost of testing becomes increasingly important. Current trends in VLSI still uphold Moore's Law, which predicts that the number of transistors per chip will double every 18 to 24 months. This is due to the approximate 10.5% reduction of transitor feature sizes every year, which allows for a 22.1% per year increase in transistor density [1]. This increase in density leads to increasing complexity of the test generation and application process, which increases the the time for testing. In fact, it has been shown that automated test equipment (ATE) is not evolving as fast as the circuits they test. As a result, testing time is becoming even more expensive. Therefore, it is imperative that testing time be reduced in order to reduce overall testing cost. In testers with insufficient high-speed memory to store all test vectors, multiple loading of test patterns from slower memory is required. Thus, the amount of test data has an indirect impact on test time. In this thesis, we address the issue of reducing tests costs by shortening test application time and reducing the volume of data that needs to be stored.

With the growing complexity of circuits, structured test techniques have replaced functional testing as the only way to achieve high fault coverage while maintaining short tester and development times [2]. Full scan is a structured test technique that has been widely adopted by industry because of the reduction in test complexity that it achieves. This is accomplished by making every flip-flop in the circuit controllable and observable by adding hardware that, during scan mode, converts all flip-flops in the circuit into a shift register. Thus, the entire state of the circuit can be controlled by shifting in values, and similarly the state can be observed by shifting out values. For test generation, this converts the circuit from a difficult sequential problem into an easier combinational problem, at the expense of increasing test application time.

Even though it is an improvement over functional testing, the test application time for full scan is still too long for many circuits. In addition, large test data volume becomes an issue when considering tester memory depth. If the test data exceeds the tester depth, then slower storage devices will have to be accessed during test application, further lengthening the test time. Also, if more faults are considered than just stuckat testing, such as transition fault testing, then test data volume becomes even more significant.

Many improvements have been suggested to reduce test data volume and application time. One such method is using built-in-self-test (BIST), which provides on-chip test pattern generation and output comparison. In order to achieve sufficient fault coverage, using BIST alone is normally insufficient, and must be combined with standard scan approaches. Several proposed methods [3, 4, 5] have shown that using a hybrid of test pattern generation (ATPG) and BIST are effective in reducing tester data volume while still maintaining high fault coverage. Implementing BIST, however, introduces complications. There is an increase in area and routing when adding the BIST controller. Logic and signal changes/additions are needed to accommodate the additional hardware. All these factors greatly increase the complexity of the design, which leads to an increase in the development time of the chip [2].

An alternative to BIST is the Illinois Scan Architecture (ILS) [6]. Originally proposed as a technique for embedded cores, ILS can be used on standalone chips as well. Under the ILS methodology, there are two modes, broadcast and serial. In broadcast mode, the entire scan chain of the circuit is broken up into smaller scan chains, which all get scanned in with identical data supplied on a single pin. In serial mode, conventional scan patterns are created to test any faults not covered by broadcast mode. A case study of the Illinois Scan Architecture [2] on an industrial circuit showed that because of the parallelism involved in broadcast mode, there is a significant reduction in test data volume and application time, while introducing less of an area and routing penalty than other BIST implementations.

Other methods have been proposed to improve the original ILS methodology. An incremental algorithm [7] for ILS test generation was proposed which created an efficient way for finding the most optimal ILS configuration. A reconfigurable technique used with ILS was shown to reduce test data volume by decreasing the number of patterns applied in serial mode [8]. In this thesis, we propose a new technique involving ILS to further reduce test data volume by further eliminating the need for serial patterns, accomplished by the intelligent use of multiple groups of scan chains. Previous studies [2, 9] have demonstrated that using multiple groups instead of the one group used in traditional ILS

broadcast mode can be beneficial, but the groups were predetermined without using any compatibility analysis.

Recently, a reconfigurable scan-chain architecture [10] was proposed which used compatibility analysis of scan chains for the assignment of groups. The algorithm worked iteratively, assigning each scan chain to one out of a fixed number of groups, then finding test patterns for that configuration for all undetectable faults, and running compatibility analysis on the remaining undetectable faults and then reassigning groups and testing, until all faults were detected. While it was shown that there was a significant reduction in data volume, there are some drawbacks to this method. First, because several configurations are needed for the circuit, there is extensive usage of the test generator. In addition, one method of compatibility analysis [11] involves making several ATPG runs to identify compatibility relations, thus making the use of the test generator even more extensive. Another drawback is that the other method of compatibility analysis used [12] assumes that a set of precomputed test patterns are available, which is not always the case. Our new method of using ILS with groups only uses one or two configurations, and does not need any precomputed patterns or separate ATPG runs for compatibility analysis.

Studies [13, 14] have shown that stuck-at faults may not be sufficient enough to cover all defects. As circuit time becomes more crucial, it may be necessary to perform additional tests to cover delay defects. Path delay tests are effective but hard to generate for full coverage because of the large size of circuits and their large path sets. An easier alternative is to use transition fault testing. Although these tests are not effective for all delay defects, they are useful in testing localized delay defects of large amounts of delay. Also, transition tests are easy to generate as they require only minimal modifications to a stuck-at fault test generator. While several methods [15, 16] have been proposed to create test generators for transition faults, little work has been done to reduce the test data volume created by these generators. In this thesis, we will apply the ILS techniques to transition faults to reduce data volume and test application time. ILS with transition faults is described in [2] using the skewed load technique [17]. In our testing we will be using the functional justification technique, described in [15].

## **1.1** Organization of the Thesis

The rest of this thesis is organized as follows. An introduction to Illinois Scan Architecture is presented in Chapter 2. The new method for test generation involving multiple scan chain groups, called Multiple Group ILS, is presented in Chapter 3. Algorithms for the reduction of groups using Multiple Group ILS are described in Chapter 4. Using ILS for transition fault testing is presented in Chapter 5. Finally, Chapter 6 discusses the conclusions and directions for future research.

### **CHAPTER 2**

# INTRODUCTION TO ILLINOIS SCAN ARCHITECTURE

The Illinois Scan Architecture (ILS) was first introduced in [6]. An overview of the architecture is provided here.

The architecture is shown in Figure 2.1, which represents the two modes of operation that it consists of. The top part of the figure shows a regular scan chain, which is known as Serial Mode. The bottom part of the figure shows the scan chain broken up into segments, called the Broadcast Mode. Here the scan-in pin that originally went into the entire scan chain now feeds into each of the scan chain segments. Thus, each segment will be inputted the same data in parallel. Note this shared scan-in idea has been reported in previous work [18]; however, this was limited to testing several independent circuits in parallel. As shown by the figure, the outputs of the scan chains are compressed

Figure 2.1 Two Modes of Illinois Scan Architecture

into a multiple input signature register (MISR). This is similar to the output response calculation found in BIST implementations. Like BIST implementations, in order to prevent corrupting the MISR signature, certain design rules must be followed, such as avoiding unknown states, internal bus conflicts, among others.

The additional hardware required for this architecture includes multiplexers for each scan chain segment, which are needed to switch between the two modes of operation. In addition, a MISR is needed with a size equal to the number of scan chain segments. It was shown that even with pessimistic assumptions, the addition of this hardware and the additional routing needed only caused a minor increase in the design area of a chip, less than what is needed for previously reported BIST implementations [2]. Also it is important to note that no additional test pins are required other than the ones already used for full scan.

### 2.1 Test Generation Procedure for ILS

As mentioned previously, the ILS technique requires two modes of operation, broadcast and serial. First test generation is performed in broadcast mode. However, because all the scan chain segments are receiving the same data, there are many constraints which are added on the test patterns, which make many faults untestable. Serial mode is then used to generate tests for all the undetectable faults in broadcast mode. This is because in this mode, there are no constraints on the test patterns and thus full fault coverage will be achieved.

- (1) Generate a test set B under Broadcast Mode. Perform static compaction on B. Identify the set of faults, U, that are undetectable.

- (2) Generate a test set S under Serial Mode targeting only the faults in U. Perform static compaction on S.

- (3) Fault simulate test set S for all faults, and remove the detected faults from the complete fault list.

- (4) Perform static compaction on test set B using the remaining faults from the previous step or regenerate B under Broadcast Mode using only these faults.

- (5) Output the final test set  $T = B \cup S$ .

Figure 2.2 Test Generation Procedure for ILS

The procedure we used for test generation with ILS is outlined by the steps in Figure 2.2. Note that although the serial patterns are only produced for the undetectable faults in broadcast mode, they also detect many more faults. Therefore, as shown in steps 3 and 4, all faults detected by serial mode are removed from the complete fault list and broadcast patterns are re-generated or compacted using only the remaining faults. Test pattern generation was accomplished by using ATOM [19], a robust combinational circuit ATPG. Static compaction was performed using a double detection and reverse order fault simulation technique [20].

### 2.2 Experimental Results

The test procedure mentioned above was performed using some of the ISCAS 89 benchmark [21] circuits. Table 2.1 shows the characteristics of the tested circuits. The columns in this table represent the name of the circuit, the number of primary inputs, the number of primary outputs, the number of flip-flops, the number of gates, the total amount of collapsed faults, and the total number of detectable faults, respectively.

| Circuit  | Inputs | Outputs | Flip-Flops | Gates  | Total<br>Faults | Detectable<br>Faults |

|----------|--------|---------|------------|--------|-----------------|----------------------|

| s13207.1 | 62     | 152     | 638        | 7951   | 9815            | 9664                 |

| s15850.1 | 77     | 150     | 534        | 9772   | 11 725          | 11 336               |

| s38417   | 28     | 106     | 1636       | 22 179 | 31 180          | 31 015               |

| s38584.1 | 38     | 304     | 1426       | 19 253 | 36 303          | 34 797               |

Table 2.1 Characteristics of Tested Circuits

First, test generation using the conventional full scan version of each circuit was conducted, and then static compaction was performed. All runs were performed on an AMD 900 MHz machine with 256 MB of memory. In order to compare the usefulness of the ILS architecture, test application time and test data volume needed to be measured. For a full scan circuit, it was assumed that the parallel access technique is used to access primary inputs and outputs of the circuit. During this process, the first vector is shifted in, and then after that shifting in a new vector and shifting out the response are performed simultaneously. Then the test application time, measured by the number of test cycles, is computed as

#### F + (1 + F) \* V

where F is the number of flip-flops and V is the number of vectors in the test set. It is assumed that only one scan pin is used in the test application process. The test data volume for full scan circuits is calculated as

$$(PI+F)*V$$

where PI is the number of primary inputs, F is the number of flip-flops, and V is the number of test vectors. For comparison purposes with ILS configurations, we assume the outputs are compressed, and thus they are not included in the calculation for data volume. Table 2.2 shows the results of test generation on the full scan circuits. The columns in this table represent the circuit name, the number of test vectors after using the ATPG and performing static compaction, the number of cycles needed to test the circuit, the number of bits needed to be stored in the tester, and the total test time including both the test generator and static compaction.

| Circuit  | Test<br>Vectors | Test<br>Cycles | Test Data<br>(bits) | Total Time<br>(s) |

|----------|-----------------|----------------|---------------------|-------------------|

| s13207.1 | 468             | 299 690        | 327 600             | 9.6               |

| s15850.1 | 432             | 231 654        | 263 952             | 11.0              |

| s38417   | 921             | 1 509 313      | 1 532 544           | 40.7              |

| s38584.1 | 634             | 906 144        | 928 176             | 34.5              |

Table 2.2 Results for Full Scan Circuits

Next, test generation is performed for the circuits using various ILS configurations. It is necessary first to describe some definitions related to the ILS architecture. For a given circuit, let the flip-flops be numbered 1,2,...,N, as given in the conventional scan chain configuration. For an ILS-k configuration, the scan chain is divided into smaller segments, each with a length of k flops. Because divisions are not necessarily perfect, the last scan chain may have a shorter length. The ILS-k configuration is illustrated in Figure 2.3. There are a total of m scan chain segments, where m - 1 of them are of length k, while the last chain segment is less than length k. Every segment receives identical data in parallel. For example, if a scan chain of length 100 were divided into 5 scan chain segments, flops 1, 21, 41, 61, and 81 would all receive the same data, since they are in the same position for every segment.

Figure 2.3 ILS-k Configuration

The test procedure for the ILS circuit was described in the preceding section. Various configurations for each circuit were tested in order to find the configuration that produced the most optimal results. ILS configurations were made by modifying the netlist of the full scan circuit, by connecting all scan chain segments to a single scan-in pin. The longest overall runtime for this procedure was approximately 10 min on 12 different configurations of circuit s38584.1. Table 2.3 shows experimental results for circuit s38584.1. The columns represent the ILS configuration, the number of scan chains, the number of broadcast patterns before reverse-order fault simulation (RFS), the fault coverage of

the broadcast patterns, the additional faults that are undetectable in broadcast mode, the serial patterns needed to test those additional faults, the fault coverage of the serial patterns, the amount of broadcast vectors after RFS, and finally the fault coverage of these remaining broadcast patterns. 'Baseline' in column 1 refers to the full scan version of the circuit. From this table it is evident that, in general, as the length of the chain

|          |               | Broadcast 1<br>(Pre-RF |       |            | Serial<br>Mode |       | Broadcast Mode<br>(Post-RFS) |       |

|----------|---------------|------------------------|-------|------------|----------------|-------|------------------------------|-------|

| Config   | Num<br>Chains | Patterns               | FC%   | Add<br>Red | Patterns       | FC%   | Patterns                     | FC%   |

| Baseline | 1             | 0                      | 0     | 0          | 634            | 95.85 | 0                            | 0     |

| ILS-1024 | 2             | 946                    | 95.83 | 8          | 2              | 46.76 | 618                          | 49.09 |

| ILS-800  | 2             | 918                    | 95.75 | 36         | 17             | 63.57 | 616                          | 32.28 |

| ILS-512  | 3             | 956                    | 95.71 | 51         | 25             | 67.45 | 626                          | 28.40 |

| ILS-400  | 4             | 957                    | 95.62 | 84         | 32             | 69.57 | 605                          | 26.28 |

| ILS-256  | 6             | 936                    | 95.34 | 187        | 52             | 77.43 | 623                          | 18.42 |

| ILS-200  | 8             | 863                    | 95.04 | 293        | 99             | 86.80 | 534                          | 9.05  |

| ILS-128  | 12            | 902                    | 94.47 | 503        | 100            | 85.12 | 564                          | 10.73 |

| ILS-100  | 15            | 846                    | 94.27 | 576        | 162            | 89.44 | 481                          | 6.41  |

| ILS-64   | 23            | 726                    | 91.69 | 1515       | 254            | 92.08 | 401                          | 3.77  |

| ILS-50   | 29            | 770                    | 93.05 | 1017       | 247            | 91.66 | 406                          | 4.19  |

| ILS-32   | 45            | 655                    | 89.69 | 2239       | 342            | 93.54 | 309                          | 2.31  |

| ILS-25   | 58            | 606                    | 89.87 | 2172       | 367            | 93.76 | 281                          | 2.09  |

Table 2.3 Results for Various ILS Configurations for Circuit s38584.1

(column 1) decreases and the number of scan chain segments (column 2) increases, the number of broadcast patterns (column 3) decreases. This is due to the fact that as there are more parallel scan chain segments, there are tighter constraints on the ATPG because of increased redundancies, which cause many more undetectable faults, as shown by column 5. Since there are fewer detectable faults, fewer vectors are needed to test them. As the number of undetectable faults go up, more serial vectors will be needed to test them, shown in column 6. Since the serial vectors will test many more faults than what they are needed for, reverse-order fault simulation of the serial vectors and compaction eliminates many of the broadcast vectors that are now redundant. This form of compaction proves to be very effective, as shown by the comparison of Pre-RFS broadcast patterns (column 3) to the Post-RFS broadcast patterns (column 8).

When the ILS configuration is in broadcast mode, the tester only needs to shift in and shift out the length of the longest chain segment, since all the segments are being accessed in parallel. Thus the test application time, or test cycles, for broadcast mode is computed as

$$F_{LSC} + (1 + F_{LSC}) * V_B$$

where  $F_{LSC}$  is the length of the longest segment and  $V_B$  is the number of broadcast vectors required. Similarly, due to the parallel access of the ILS configuration, the tester does not need to store data for all the flops, but only for the length of the longest scan chain segment. The test data volume for broadcast mode is then computed as

$$(PI + F_{LSC}) * V_B$$

where PI is the number of primary inputs,  $F_{LSC}$  is the length of the longest chain in Broadcast Mode, and  $V_B$  is the number of broadcast vectors required. Note the outputs for an ILS configuration are compressed through a MISR, and thus they do not need to be specifically stored.

Table 2.4 shows the experimental results for the test application time required for various ILS configurations of all tested circuits. The columns in these table represent the circuit being tested, the ILS configuration, the number of serial patterns required, the tester cycles required for these serial patterns, the number of scan chain segments in broadcast mode, the final number of broadcast patterns needed after RFS, the tester cycles required to apply these patterns, the total tester cycles required including serial and broadcast mode, and finally the test application time reduction factor. The reduction factor is calculated as the ratio of the total cycles needed for the conventional full scan circuit (indicated by 'Baseline') to the total cycles needed for a particular ILS configuration.

The experimental results for test data volume for various ILS configurations of the tested circuits are shown in Table 2.5. The columns in this table represent the circuit being tested, the ILS configuration, the number of serial patterns required, the amount of data bits that needs to be stored in the tester for these serial patterns, the number of scan chain segments in broadcast mode, the final number of broadcast patterns needed after RFS, the amount of data bits that needs to be stored in the tester to be stored in the tester for these broadcast patterns, the total amount of data bits that needs to be stored for both broadcast and serial modes, and finally the reduction factor. The reduction factor is calculated as the ratio of the total bits needed to be stored for the full scan circuit to the total bits needed to be stored for a particular ILS configuration.

|           |          | Serial   | Mode           | Br            | Broadcast Mode |                |                 |                     |

|-----------|----------|----------|----------------|---------------|----------------|----------------|-----------------|---------------------|

| Circuit   | Config   | Patterns | Test<br>Cycles | Num<br>Chains | Patterns       | Test<br>Cycles | Total<br>Cycles | Reduction<br>Factor |

|           | Baseline | 468      | 299 690        | -             | 0              | 0              | 299 690         | 1.00                |

|           | ILS-400  | 3        | 2555           | 2             | 465            | 186 865        | 189 420         | 1.58                |

|           | ILS-360  | 9        | 6389           | 2             | 465            | 168 225        | 174 614         | 1.72                |

| s13207.1  | ILS-200  | 25       | 16 613         | 4             | 449            | 90 449         | 107 062         | 2.80                |

|           | ILS-180  | 18       | 12 140         | 4             | 441            | 80 001         | 92 141          | 3.25                |

|           | ILS-100  | 44       | 28 754         | 7             | 425            | 43 025         | 71 779          | 4.18                |

|           | ILS-90   | 41       | 26 837         | 8             | 422            | 38 492         | 65 329          | 4.59                |

|           | ILS-50   | 85       | 54 953         | 13            | 370            | 18 920         | 73 873          | 4.06                |

|           | ILS-45   | 105      | 67 733         | 15            | 345            | 15 915         | 83 648          | 3.58                |

|           | ILS-25   | 221      | 141 857        | 26            | 237            | 6187           | 148 044         | 2.02                |

|           | ILS-15   | 359      | 230 039        | 43            | 81             | 1311           | 231 350         | 1.30                |

|           | Baseline | 432      | 231 654        | -             | 0              | 0              | 231 654         | 1.00                |

|           | ILS-400  | 34       | 18 724         | 2             | 420            | 168 820        | 187 544         | 1.24                |

|           | ILS-300  | 19       | 10 699         | 2             | 416            | 125 516        | 136 215         | 1.70                |

|           | ILS-200  | 45       | 24 609         | 3             | 399            | 80 399         | 105 008         | 2.21                |

| s15850.1  | ILS-150  | 35       | 192 59         | 4             | 406            | 61 456         | 80715           | 2.87                |

|           | ILS-100  | 72       | 39 054         | 6             | 366            | 37 066         | 76 120          | 3.04                |

|           | ILS-75   | 95       | 51 359         | 8             | 355            | 27 055         | 78 414          | 2.95                |

|           | ILS-50   | 118      | 63 664         | 11            | 314            | 16 064         | 79 728          | 2.91                |

|           | ILS-25   | 184      | 98 974         | 22            | 232            | 6057           | 10 5031         | 2.21                |

|           | Baseline | 921      | 1 509 313      | -             | 0              | 0              | 1 509 313       | 1.00                |

|           | ILS-920  | 9        | 16 369         | 2             | 937            | 863 897        | 880 266         | 1.71                |

|           | ILS-840  | 11       | 19 643         | 2             | 920            | 774 560        | 794 203         | 1.90                |

|           | ILS-460  | 11       | 19 643         | 4             | 884            | 407 984        | 427 627         | 3.53                |

| s38417    | ILS-230  | 15       | 26 191         | 8             | 905            | 209 285        | 235 476         | 6.41                |

|           | ILS-210  | 23       | 39 287         | 8             | 804            | 169 854        | 209 141         | 7.22                |

|           | ILS-115  | 21       | 36 013         | 15            | 883            | 102 543        | 138 556         | 10.89               |

|           | ILS-105  | 34       | 57 294         | 16            | 741            | 78 651         | 135 945         | 11.10               |

|           | ILS-23   | 405      | 664 621        | 72            | 456            | 10 967         | 675 588         | 2.23                |

| 1919-1-1  | ILS-21   | 562      | 921 630        | 78            | 283            | 6247           | 927 877         | 1.63                |

|           | Baseline | 634      | 906 144        | -             | 0              | 0              | 906 144         | 1.00                |

|           | ILS-1024 | 2        | 4280           | 2             | 618            | 634 474        | 638 754         | 1.42                |

|           | ILS-800  | 17       | 25 685         | 2             | 616            | 494 216        | 519 901         | 1.74                |

| 1 1 1 1 1 | ILS-512  | 25       | 37 101         | 3             | 626            | 321 650        | 358 751         | 2.53                |

|           | ILS-400  | 32       | 47 090         | 4             | 605            | 243 005        | 290 095         | 3.12                |

|           | ILS-256  | 52       | 75 630         | 6             | 623            | 160 367        | 235 997         | 3.84                |

| s38584.1  | ILS-200  | 99       | 142 699        | 8             | 534            | 107534         | 250 233         | 3.62                |

|           | ILS-128  | 100      | 144 126        | 12            | 564            | 72 884         | 217 010         | 4.18                |

| #         | ILS-100  | 162      | 232 600        | 15            | 481            | 48 681         | 281 281         | 3.22                |

|           | ILS-64   | 254      | 363 884        | 23            | 401            | 26 129         | 390 013         | 2.32                |

|           | ILS-50   | 247      | 353 895        | 29            | 406            | 20 756         | 374 651         | 2.42                |

|           | ILS-32   | 342      | 489 460        | 45            | 309            | 10 229         | 499 689         | 1.81                |

|           | ILS-25   | 367      | 525 135        | 58            | 281            | 7331           | 532 466         | 1.70                |

| Table 2.4 Test Application Time Reduction Using | ILS |  |

|-------------------------------------------------|-----|--|

|-------------------------------------------------|-----|--|

Í

|          | 1. 1. 1. Salar | Serial   | Mode        | Br            | oadcast Mo | ode         |               |                     |

|----------|----------------|----------|-------------|---------------|------------|-------------|---------------|---------------------|

| Circuit  | Config         | Patterns | Mem<br>bits | Num<br>Chains | Patterns   | Mem<br>bits | Total<br>bits | Reduction<br>Factor |

|          | Baseline       | 468      | 327 600     | -             | 0          | 0           | 327 600       | 1.00                |

|          | ILS-400        | 3        | 2100        | 2             | 465        | 214 830     | 216 930       | 1.51                |

|          | ILS-360        | 9        | 6300        | 2             | 465        | 196 230     | 202 530       | 1.62                |

| s13207.1 | ILS-200        | 25       | 17 500      | 4             | 449        | 117 638     | 135 138       | 2.42                |

|          | ILS-180        | 18       | 12 600      | 4             | 441        | 106 722     | 119 322       | 2.75                |

|          | ILS-100        | 44       | 30 800      | 7             | 425        | 68 850      | 99 650        | 3.29                |

|          | ILS-90         | 41       | 28 700      | 8             | 422        | 64 144      | 92 844        | 3.53                |

|          | ILS-50         | 85       | 59 500      | 13            | 370        | 41 440      | 100 940       | 3.25                |

|          | ILS-45         | 105      | 73 500      | 15            | 345        | 36 915      | 110 415       | 2.97                |

|          | ILS-25         | 221      | 154 700     | 26            | 237        | 20 619      | 175 319       | 1.87                |

|          | ILS-15         | 359      | 251 300     | 43            | 81         | 6237        | 257 537       | 1.27                |

|          | Baseline       | 432      | 263 952     | -             | 0          | 0           | 263 952       | 1.00                |

|          | ILS-400        | 34       | 20 774      | 2             | 420        | 200 340     | 221 114       | 1.19                |

|          | ILS-300        | 19       | 11 609      | 2             | 416        | 156 832     | 168 441       | 1.57                |

|          | ILS-200        | 45       | 27 495      | 3             | 399        | 110 523     | 138 018       | 1.91                |

| s15850.1 | ILS-150        | 35       | 21 385      | 4             | 406        | 92 162      | 113 547       | 2.32                |

|          | ILS-100        | 72       | 43 992      | 6             | 366        | 64 782      | 108 774       | 2.43                |

|          | ILS-75         | 95       | 58 045      | 8             | 355        | 53 960      | 112 005       | 2.36                |

|          | ILS-50         | 118      | 72 098      | 11            | 314        | 39 878      | 111 976       | 2.36                |

|          | ILS-25         | 184      | 112 424     | 22            | 232        | 23 664      | 136 088       | 1.94                |

|          | Baseline       | 921      | 1 532 544   | -             | 0          | 0           | 1 532 544     | 1.00                |

|          | ILS-920        | 9        | 14 976      | 2             | 937        | 888 276     | 903 252       | 1.70                |

|          | ILS-840        | 11       | 18 304      | 2             | 920        | 798 560     | 816 864       | 1.88                |

|          | ILS-460        | 11       | 18 304      | 4             | 884        | 431 392     | 449 696       | 3.41                |

| s38417   | ILS-230        | 15       | 24 960      | 8             | 905        | 233 490     | 258 450       | 5.93                |

|          | ILS-210        | 23       | 38 272      | 8             | 804        | 191 352     | 229 624       | 6.67                |

|          | ILS-115        | 21       | 34 944      | 15            | 883        | 126 269     | 161 213       | 9.51                |

|          | ILS-105        | 34       | 56 576      | 16            | 741        | 98 553      | 155 129       | 9.88                |

|          | ILS-23         | 405      | 673 920     | 72            | 456        | 23 256      | 697 176       | 2.20                |

|          | ILS-21         | 562      | 935 168     | 78            | 283        | 13 867      | 949 035       | 1.61                |

|          | Baseline       | 634      | 928 176     | -             | 0          | 0           | 928 176       | 1.00                |

|          | ILS-1024       | 2        | 2928        | 2             | 618        | 656 316     | 659 244       | 1.41                |

|          | ILS-800        | 17       | 24 888      | 2             | 616        | 516 208     | 541 096       | 1.72                |

|          | ILS-512        | 25       | 36 600      | 3             | 626        | 344 300     | 380 900       | 2.44                |

| 1. 123   | ILS-400        | 32       | 46 848      | 4             | 605        | 264 990     | 311 838       | 2.98                |

|          | ILS-256        | 52       | 76 128      | 6             | 623        | 183 162     | 259 290       | 3.58                |

| s38584.1 | ILS-200        | 99       | 144 936     | 8             | 534        | 127 092     | 272 028       | 3.41                |

| 1.11     | ILS-128        | 100      | 146 400     | 12            | 564        | 93 624      | 240 024       | 3.87                |

|          | ILS-100        | 162      | 237 168     | 15            | 481        | 66 378      | 303 546       | 3.06                |

| -        | ILS-64         | 254      | 371 856     | 23            | 401        | 40 902      | 412 758       | 2.25                |

| 11 1. 14 | ILS-50         | 247      | 361 608     | 29            | 406        | 35 728      | 397 336       | 2.34                |

|          | ILS-32         | 342      | 500 688     | 45            | 309        | 21 630      | 522 318       | 1.78                |

|          | ILS-25         | 367      | 537 288     | 58            | 281        | 17.703      | 554 991       | 1.67                |

Table 2.5 Test Data Volume Reduction Using ILS

.

It can be seen from both Tables 2.4 and 2.5 that as the length of the scan chains decrease and number of scan chain segments increase, the data volume and application time reduction factors start to increase, and then eventually end up decreasing. This is because as the length of the scan chains start to decrease, there are less flops that need to be shifted and stored, which causes the broadcast test cycles and memory bits to decrease. However, as the broadcast vectors start to decrease, more serial vectors are needed. Because serial vectors are costly in terms of both test application time and data volume, this increased cost starts to offset the reduction in cost from using smaller chain segments. Eventually, with a small enough scan chain length, the cost of needing serial vectors dominates over the cost of the broadcast vectors, which causes the reduction factor to decrease.

Figure 2.4 graphically shows the trend of reduction factor for test application time and test data volume versus the length of the longest scan chain segment. Both the application and data volume curves follow the same trends, since the only variable in both equations is the amount of flops that need to be shifted in/out, and stored, respectively. The maximum test application time reduction factor varies for every circuit, from 3.04 for circuit s15850.1 all the way to 11.1 for circuit s38417. The same is true for the maximum test data volume reduction factor, where values vary from 2.43 for circuit s15850.1 all the way to 9.88 for circuit s38417. For all cases, the maximum test application time reduction factor and the maximum test data volume reduction factor occurred using the same configuration. Although it is clear that there is a significant reduction in both test application time and test data volume for all tested circuits, it is not evident how to determine the optimal configuration without experimentation first.

Figure 2.4 Time and Data Reduction Factor versus ILS Configuration

### 2.3 Summary

In this chapter, the ILS architecture was implemented and investigated for several circuits, in order to determine its effectiveness. The results presented show a significant improvement in the reduction of both test application time and test data volume compared to the convention full scan technique.

## **CHAPTER 3**

# **MULTIPLE GROUP ILS**

In the preceding chapter, it was shown that using the ILS architecture is effective for both reducing the test application time and test data volume. This is accomplished by the use of broadcast mode, where several scan chains get shifted in identical data in parallel. However, because of this parallelism, there are increased redundancies when generating tests, which causes a loss in fault coverage, prompting the need for a serial mode which will then cover the remaining undetected faults. This mode is expensive both in terms of test application time and data volume. Therefore, a new method, called Multiple Group ILS, is proposed to eliminate the use of serial mode by using multiple groups of scan chain segments. Furthermore, we show that by using these groups, it is possible to eliminate broadcast mode as well.

# 3.1 Introductory Information

In order to understand the test procedure for Multiple Group ILS, it is first necessary to provide some background information related to the ILS architecture. In the following subsections, an example is given as an introduction and thereafter some definitions are provided.

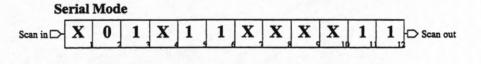

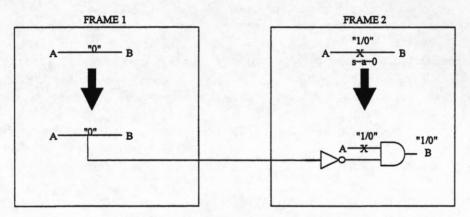

### 3.1.1 Preliminary example

First, it is important to illustrate why certain faults become untestable for an ILS design in broadcast mode, as shown in Figure 3.1. The top portion shows an example of a partially specified serial mode pattern for a 12-flop circuit needed to test a certain fault that would be undetectable in broadcast mode. The bottom portion shows what this pattern would look like if it were 'folded over' and applied to the ILS structure in broadcast mode. Investigating the second column (the second bit position from the left for all the scan chains), scan chain one (SC1) needs a 0, while scan chain 2 (SC2) needs a 1. Since all the scan chains have the same scan-in pin, it is not possible to shift in both values at the same time, thus making this test vector inapplicable which in turn may make a fault untestable in broadcast mode. In general, for ILS designs in broadcast mode, a scan chain is said to be incompatible with another scan chain if, in the pattern needed to test a certain fault, there exists at least one bit position (column) where the

Figure 3.1 Example of an Untestable Fault in Broadcast Mode of ILS

two scan chains have conflicting binary values, i.e, one scan chain needs a one and the other needs a zero, or vice versa. In Figure 3.1, SC1 was incompatible with SC2 as they had conflicting values in the second bit position. Note that don't cares, marked by X's, do not conflict with any other values, and thus SC3 is compatible with both SC1 and SC2.

If two scan chains are incompatible with each other for a particular fault, then this fault will be untestable in broadcast mode. In the preceding chapter, serial mode was used to cover these untestable faults. In this chapter, a new solution is proposed, as depicted by the Figure 3.2. Here a second pin is introduced, which is connected to the bottom two scan chains, SC2 and SC3. Since SC1 and SC2 have different input pins, they are no longer incompatible, thus making the fault testable. SC2 and SC3 form one 'group' of scan chains, as they share the same scan-in pin, while SC1 is another group, and hence this arrangement is called Groups Mode. Note that while a pin is added on the input side, the output side remains the same as the conventional ILS configuration, with all scan chains connected to a MISR.

Figure 3.2 Previous Example Using Groups Mode

### 3.1.2 Compatibility definitions

In this subsection, we present some definitions that were introduced in the previous example.

- Two scan cells are said to be *compatible* if and only if no fault becomes untestable as a result of tying the two cells to a single input [11].

- (2) Two scan chains are said to be *compatible* if and only if every pair of scan-cells that receive the same logic value are compatible [22].

Since the exact analysis for determining all pairwise compatibilities is computationally complex, we resort to a fast analysis which obtains a subset of all compatibilities. This analysis is based on a partially specified complete test set. This procedure was used as a first step in the more thorough procedures of [11] and [22].

By folding a given test set on an ILS organization, one can determine if two scan chains are compatible by simply noting an absence of value conflicts. Any two chains not found to be compatible by this procedure are termed *potentially incompatible*. Since the test set based on compatibility analysis does not find *all* compatibilities, any incompatible pairs found can only be said to be potentially incompatible. A further analysis (e.g., another test set) may determine that potentially incompatible pairs are indeed compatible. In other words, our procedure finds a super-set of actual incompatibilities. It is sufficient (but not necessary) to remove these incompatibilities to achieve complete fault coverage. This is the basis of our procedure for altering the ILS structure such that all potential incompatibilities are removed. In subsequent sections, we will drop the adjective "potential" for incompatibilities.

# 3.2 Test Generation Procedure

In the example described in the previous section, a group configuration for scan chains was created for one particular fault. In this section, we describe the test procedure for creating the proper group configuration for testing *all* undetectable faults in broadcast mode for a given circuit. Figure 3.3 gives an outline of the test procedure used to generate patterns for Multiple Group ILS using both broadcast and groups modes. First, test generation for broadcast mode is performed. Then, for the remaining undetected faults, an ATPG without random-fill is used to generate serial patterns. Compatibility analysis of these serial patterns is then performed, which is detailed in the following subsection. After the correct group configuration has been found, we perform test generation for groups mode for only the undetectable faults in broadcast mode. Since groups mode will test more faults than what it is needed for, reverse-order fault simulation (RFS) for groups mode is then performed and all detected faults are removed from the complete fault list. Test patterns for broadcast mode are then re-generated, or compacted, using this new fault list.

Test pattern generation with random-fill was performed by using ATOM [19], while generation without random-fill was accomplished by using a modified version of ATOM. Static compaction for fully specified patterns was performed using a double detection and reverse order fault simulation technique [20], while compaction for partially specified

- (1) Regenerate the netlist for broadcast mode. Generate a test set B under Broadcast Mode. Perform static compaction on B. Identify the set of faults, U, that are undetectable.

- (2) Regenerate the netlist for serial mode. Using a non-filling ATPG, generate a partially specified test set S tagerting only the faults in U. Perform static compaction on S to remove redundant vectors.

- (3) Perform compatability analysis for all patterns in S to find a group configuration.

- (4) Regenerate the netlist for groups mode. Generate a test set G under Groups Mode targeting only the faults in U. Perform static compaction on G.

- (5) Fault simulate test set G for all faults, and remove the detected faults from the complete fault list.

- (6) Regenerate the netlist for broadcast mode. Perform static compaction on test set B using the remaining faults from the previous step or regenerate B under Broadcast Mode using only these faults.

- (7) Output the final test set  $T = B \cup G$ .

Figure 3.3 Test Procedure for Using Broadcast and Groups Mode

patterns was performed using a simpler forward and reverse order single detection scheme [1].

### 3.2.1 Compatibility analysis

In order to determine the optimal configuration of groups, it is necessary to perform compatibility analysis on the scan chains. In general, the objective is to form the minimal amount of groups so that all scan chains within any group are compatible, as this will result in the least amount of test data volume that needs to be stored. To accomplish this, first an incompatibility graph, with all the scan chains as nodes, needs to be created from the serial patterns generated by the non-random-fill ATPG. It is essential not to have any randomly-filled inputs as this will lead to extraneous incompatibilities between scan chains. The process is simple: like the example in the previous section, for each serial pattern generated, we 'fold over' the pattern into the scan chains used in broadcast mode and for every bit position, determine if there are conflicting values. When a conflict arises, we note which chains are conflicting, and add an edge between the two scan chains, represented as nodes in the incompatibility graph. Thus for the example in the previous section, the graph would look as shown in Figure 3.4, which depicts that SC1 is incompatible with SC2, while SC3 has no incompatibilities.

Figure 3.4 Incompatibility Graph for Example Shown in Figure 3.1

Note that the same graph is used for all the serial patterns generated; edges are added between scan chains if new incompatibilities are found.

After the incompatibility graph has been created, a graph coloring algorithm is applied, which will assign a specific color to every node such that no two nodes connected by an edge will have the same color. Here, assigning colors to nodes is equivalent to assigning a group number, or scan-in pin, to a scan chain. The graph coloring algorithm will attempt to assign the minimal number of colors (groups) while following the restriction that two adjacent nodes (two incompatible scan chains) cannot be of the same color (group number). For the example shown in Figure 3.4, SC1 and SC2 have to be different colors, while SC3 can be any color. Thus a minimum of two colors are needed, which corresponds to a minimum of two scan-in pins, or groups needed for testing. Although in the preceding example it was trivial to determine the coloring, in general determining the optimal coloring for a graph with many edges can be a difficult problem. For the incompatibility graphs generated in our procedure, a graph coloring algorithm based upon the DSATUR algorithm [23] was utilized. The algorithm first attempts to find the maximum clique size in the graph, which corresponds to finding the maximum number of nodes that are all connected to each other. For example, in the graph in Figure 3.5, the maximum clique is of size 3, since SC1, SC2, and SC3 are all interconnected.

Figure 3.5 Incompatibility Graph with Maximum Clique of Size 3 (SC1,SC2,SC3)

This maximum clique number then represents the lower bound of the number of colors needed, as every node in that clique needs to be a different color, since they are all interconnected. Those nodes are then colored first, as suggested in [24].

Then a heuristic method is applied for the rest of the graph. A simple explanation of the algorithm is provided here. For more details on the exact algorithm, see [23, 25, 26]. The algorithm works by looking at node in the graph with the highest saturation degree first, which is defined as the number of different colors found for all adjacent nodes. If more than one node shares this highest saturation degree, then the algorithm attempts to find the node with the highest unlabeled degree, defined as the largest number of uncolored adjacent nodes. If there is still more than one node left, then one is chosen randomly. After a node is chosen, it is assigned the lowest feasible color, depending on the color of its adjacent nodes. This process is repeated until all nodes are colored. This will result in a configuration of groups for which there are no incompatibilities, which will be then be used for groups mode.

# 3.3 Experimental Results

The test procedure was performed on the same circuits from the ISCAS 89 benchmark described in the preceding chapter. All tests were run on the same machine as well, an AMD 900 MHz with 256 MB of memory. The longest overall run time was approximately 35 min for the 10 configurations of circuit s38417. This time is longer than the traditional ILS procedure because of a few reasons. First, smaller chain length configurations are used, which causes the ATPG to run longer as there are more redundancies in the circuit. Second, extra time is needed for compatibility analysis and the extra serial pattern ATPG run required for this analysis. In addition, compaction for partially specified vectors takes more time than compaction for fully specified vectors.

Table 3.1 shows experimental results for the tested circuits. The columns represent the circuit being tested, the ILS configuration, the number of scan chains, the number of broadcast mode patterns generated before reverse-order fault simulation (RFS), the additional undetectable faults caused by this ILS configuration, the number of vectors created by the nonfilling ATPG to cover these undetectable faults, the number of groups found after compatibility analysis, the number of groups mode vectors, and finally the number of broadcast mode patterns remaining after fault simulation of the groups mode patterns.

| Circuit  | Config        | Num<br>Chains | Pre-RFS<br>Broadcast<br>Vectors | Addnl<br>Red<br>Faults | Num<br>Topoff<br>Vectors | Num<br>Groups | Num<br>Group<br>Vectors | Post-RFS<br>Broadcast<br>Vectors |

|----------|---------------|---------------|---------------------------------|------------------------|--------------------------|---------------|-------------------------|----------------------------------|

|          | ILS-100       | 7             | 588                             | 211                    | 57                       | 5             | 38                      | 427                              |

|          | <b>ILS-90</b> | 8             | 588                             | 100                    | 63                       | 4             | 40                      | 422                              |

|          | ILS-75        | 9             | 588                             | 126                    | 88                       | 5             | 145                     | 311                              |

| s13207.1 | ILS-45        | 15            | 568                             | 209                    | 130                      | 5             | 94                      | 351                              |

|          | ILS-25        | 26            | 323                             | 1969                   | 890                      | 6             | 223                     | 236                              |

|          | ILS-15        | 43            | 239                             | 1909                   | 852                      | 7             | 350                     | 86                               |

|          | ILS-10        | 64            | 155                             | 2505                   | 1110                     | 8             | 385                     | 55                               |

|          | ILS-6         | 107           | 69                              | 3054                   | 1311                     | 9             | 425                     | 18                               |

|          | ILS-125       | 5             | 504                             | 148                    | 74                       | 4             | 52                      | 369                              |

|          | ILS-100       | 6             | 519 .                           | 122                    | 87                       | 5             | 71                      | 366                              |