UILU-ENG-93-2250 CRHC-93-22

Center for Reliable and High-Performance Computing

# PROPERCAD II: A RUN-TIME LIBRARY FOR PORTABLE, PARALLEL, OBJECT-ORIENTED PROGRAMMING WITH APPLICATIONS TO VLSI CAD

Steven Parkes John A. Chandy Prithviraj Banerjee

Coordinated Science Laboratory College of Engineering UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

Approved for Public Release. Distribution Unlimited.

| UNCLAS                  | SIFIED                           | F THIS PAGE                        |                                                                         | S. S. S. S. S.                                  |                                                                                                                  |                            |                            |  |

|-------------------------|----------------------------------|------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|--|

|                         |                                  |                                    | REPORT DOCU                                                             | MENTATION                                       | PAGE                                                                                                             | all and the                | an and the second second   |  |

| 1a. REPORT SE           | CURITY CLASS                     | IFICATION                          |                                                                         | 1b. RESTRICTIVE                                 | MARKINGS                                                                                                         |                            |                            |  |

| Unclass                 |                                  |                                    |                                                                         | None                                            |                                                                                                                  |                            |                            |  |

| 2a. SECURITY            | CLASSIFICATIO                    | N AUTHORITY                        |                                                                         |                                                 | N/AVAILABILITY                                                                                                   |                            |                            |  |

| 2b. DECLASSIF           | ICATION / DOW                    | NGRADING SCHEDU                    | JLE                                                                     |                                                 | tion unlim                                                                                                       | c release;<br>ited         |                            |  |

|                         | G ORGANIZAT<br>-ENG-93-22<br>CRH | ION REPORT NUMB<br>250<br>C- 93-22 | ER(S)                                                                   | 5. MONITORING                                   | ORGANIZATION                                                                                                     | N REPORT NUMB              | ER(S)                      |  |

| Coordin                 | PERFORMING<br>nated Scie         |                                    | 6b. OFFICE SYMBOL<br>(If applicable)<br>N/A                             |                                                 | MONITORING OR<br>conductor H                                                                                     | GANIZATION<br>Research Con | rporation                  |  |

| 6c. ADDRESS (           |                                  |                                    |                                                                         | 7b. ADDRESS (C                                  | ity, State, and 2                                                                                                | ZIP Code)                  |                            |  |

|                         | . Springf:<br>, IL 6180          | leld Avenue<br>)1                  |                                                                         | Research T                                      | riangle Par                                                                                                      | rk, NC 27                  | 709                        |  |

| 8a. NAME OF<br>ORGANIZA | TION                             | nsoring<br>a                       | 8b. OFFICE SYMBOL<br>(If applicable)                                    | 9. PROCUREMENT INSTRUMENT IDENTIFICATION NUMBER |                                                                                                                  |                            |                            |  |

| 8c. ADDRESS (           | City, State, and                 | ZIP Code)                          |                                                                         | 10. SOURCE OF                                   | FUNDING NUM                                                                                                      | BERS                       |                            |  |

|                         | 7                                | Ъ                                  |                                                                         | PROGRAM<br>ELEMENT NO.                          | PROJECT<br>NO.                                                                                                   | TASK<br>NO.                | WORK UNIT<br>ACCESSION NO. |  |

| 11. TITLE (Incl         |                                  |                                    |                                                                         | 1                                               |                                                                                                                  |                            |                            |  |

|                         | Programm                         | Pro                                | perCADII: A Run-<br>ications to VLSI                                    |                                                 | for Portal                                                                                                       | ble, Paralle               | el, Object-                |  |

|                         |                                  |                                    | n, John A. Chand                                                        |                                                 |                                                                                                                  |                            |                            |  |

| 13a. TYPE OF<br>Technic |                                  | 13b. TIME C                        | TO                                                                      | 14. DATE OF REPO<br>93-11-30                    |                                                                                                                  | th, Day) 15. PA            | GE COUNT                   |  |

| 16. SUPPLEME            |                                  |                                    |                                                                         |                                                 | 10 A.                                                                                                            | 1                          |                            |  |

| 17.                     | COSATI                           | CODES                              | 18. SUBJECT TERMS                                                       | Continue on rever                               | se if accessary                                                                                                  | and identify by I          | block number)              |  |

| FIELD                   | GROUP                            | SUB-GROUP                          |                                                                         |                                                 | and the second |                            | ject-oriented,             |  |

|                         |                                  |                                    | algorithms, v                                                           |                                                 |                                                                                                                  |                            |                            |  |

|                         |                                  |                                    | y and identify by block                                                 | ·                                               |                                                                                                                  |                            |                            |  |

| la                      | rge comput                       | ing problems re                    | bility of parallel pla<br>emains restricted to<br>arallel application d | a fairly narrow                                 | v set of appli                                                                                                   | cations. This              | is due                     |  |

| ·a                      | lack of sop                      | histicated enviro                  | onments for parallel<br>is increasing, the con                          | l application de                                | evelopment.                                                                                                      | Further, thou              | gh the                     |  |

| sy                      | stems does                       | not appear to b                    | e similarly increasir<br>ular architecture, it                          | ng. Given that                                  | most develop                                                                                                     | oment enviror              | nments                     |  |

|                         |                                  | installed machin                   |                                                                         |                                                 |                                                                                                                  |                            | •                          |  |

| 20. DISTRIBU            | TION / AVAILA                    | BILITY OF ABSTRAC                  | r                                                                       | 21. ABSTRACT                                    | SECURITY CLASS                                                                                                   | IFICATION ·                |                            |  |

|                         |                                  |                                    | RPT. DTIC USER                                                          |                                                 |                                                                                                                  |                            | E EXMON                    |  |

|                         |                                  | E INDIVIDUAL                       |                                                                         | and the second second                           | E (Include Area C                                                                                                | Code) 22c. OFFIC           | E STMBOL                   |  |

| DD FORM 1               | 473, 84 MAR                      | 83                                 | APR edition may be used                                                 |                                                 | SECUR                                                                                                            | ITY CLASSIFICATIO          | ON OF THIS PAGE            |  |

| All other | editions | are | obso | lete. |

|-----------|----------|-----|------|-------|

UNCLASSIFIED

## UNCLASSIFIED URITY CLASSIFICATION OF THIS PAGE

In this research, we address these problems through the application of two significant technologies; object-oriented design techniques and the actor model of concurrent computation. Our approach is manifested in the ProperCAD II library, a C++ object library supporting actor concurrency on parallel architectures based on contemporary microprocessor technologies and appropriate for applications demonstrating medium-grain parallelism. The development of the library has been driven in general by the requirements of large, unstructured problems, which have not proven amenable to techniques used in scientific computing, and in particular by the requirements of VLSI CAD applications. The efficacy of our approach and implementation is demonstrated through ProperHITEC, a parallel implementation of the HITEC algorithm for automatic test pattern generation, and ProperPLACE, a parallel implementation of the TimberWolf simulated-annealing algorithm for cell placement.

# ProperCAD II: A Run-Time Library for Portable, Parallel, Object-Oriented Programming with Applications to-VLSI CAD

Steven Parkes parkes@uiuc.edu John A. Chandy j-chandy@uiuc.edu Prithviraj Banerjee p-banerjee@uiuc.edu

Center for Reliable and High-Performance Computing University of Illinois 1308 W. Main Urbana, IL 61801

This research was supported in part by the Semiconductor Research Corporation under grant 93-DP-109.

# Abstract

Despite the increasing availability of parallel platforms, their wide-spread use in the solution of large computing problems remains restricted to a fairly narrow set of applications. This is due in part to the difficulty of parallel application development which is itself largely the result of a lack of sophisticated environments for parallel application development. Further, though the number of parallel platforms is increasing, the convergence of parallel architectures and operating systems does not appear to be similarly increasing. Given that most development environments are targeted towards a particular architecture, it is difficult to amortize development costs over a wide base of installed machines.

In this research, we address these problems through the application of two significant technologies, object-oriented design techniques and the actor model of concurrent computation. Our approach is manifested in the ProperCAD II library, a C++ object library supporting actor concurrency on microprocessor-based parallel architectures and appropriate for applications demonstrating medium-grain parallelism. The development of the library has been driven in general by the requirements of large, unstructured problems, which have not proven amenable to techniques used in scientific computing, and in particular by the requirements of VLSI CAD applications. The efficacy of our approach and implementation is demonstrated-through ProperHITEC, a parallel implementation of the HITEC algorithm for automatic test pattern generation, and ProperPLACE, a parallel implementation of the TimberWolf simulated-annealing algorithm for cell placement.

# Table of Contents

1

1

I

1

1

I

I

I

1

1

| 1 | Introduction 1                            | L |

|---|-------------------------------------------|---|

|   | 1.1 Parallel and Distributed Computing    | l |

|   | 1.1.1 Hardware Architectures 1            | L |

|   | 1.1.2 High-level Programming Models       | 3 |

|   | 1.2 VLSI Computer-Aided Design 12         | 2 |

|   | 1.3 Approach                              | 3 |

|   | 1.4 Report Overview                       | ł |

|   |                                           |   |

| 1 | Run-Time Library 17                       | , |

| ~ | Overview 19                               |   |

| 2 |                                           |   |

|   |                                           |   |

|   |                                           |   |

|   | 2.1.2 Constraints                         |   |

|   | 2.2 Library Components                    |   |

|   | 2.3 Related work                          |   |

|   | 2.3.1 Actor Languages                     |   |

|   | 2.3.2 Non-actor Language-based Approaches |   |

|   | 2.3.3 Library-based Approaches 24         | ł |

| 3 | Actor Interface 25                        | 5 |

|   | 3.1 Actor Model                           | 5 |

|   | 3.2 Library Interface                     | 5 |

|   | 3.2.1 Actors                              | 5 |

|   | 3.2.2 ActorNames                          | 7 |

|   | 3.2.3 ActorMethods 28                     | 3 |

|   | 3.2.4 Messages and Continuations          | ) |

|   | 3.2.5 NewActorMethods                     | ) |

|   | 3.2.6 Aggregates                          | 1 |

|   | 3.2.7 Distributions                       | 2 |

|   | 3.2.8 AggregateNames                      | 2 |

|   | 3.3 Meta-programming Interface 33         | 3 |

|   | 3.3.1 System Aggregates                   | 3 |

|   | 3.3.2 Task Queues and Priorities          | 3 |

i

# TABLE OF CONTENTS

| 4  | 4.1       Overview                                                                                                                                                                                  | <ul> <li>35</li> <li>35</li> <li>35</li> <li>38</li> <li>39</li> <li>40</li> </ul> |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 5  | Performance                                                                                                                                                                                         | 42                                                                                 |

| 11 | Applications                                                                                                                                                                                        | 45                                                                                 |

| 6  | 6.1 Related Work                                                                                                                                                                                    | <b>47</b><br>47<br>48<br>52<br>54                                                  |

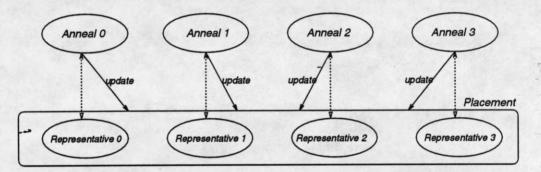

| 7  | 7.1 Simulated Annealing for Placement         7.2 Parallel Placement         7.2.1 Parallel evaluation within each move         7.2.2 Parallel evaluation of multiple moves         7.3 ProperPLACE | <b>55</b><br>56<br>56<br>56<br>58<br>60                                            |

| 8  | Conclusions                                                                                                                                                                                         | 62                                                                                 |

ii

I

I

I

# Acknowledgments

The authors would like to gratefully acknowledge the support of the Argonne National Laboratory, the San Diego Supercomputer Center, and the National Center for Supercomputer Applications.

----

# Introduction

1

The desire to employ multiple processors to solve difficult problems has, to date, remained largely unfulfilled for all but a restricted, albeit significant, set of applications, namely the numerical problems found in scientific applications and the database problems found in large transaction-processing applications. Although significant problems occur in many other fields, the techniques used in scientific and transaction-processing applications have not proven equally effective on more general, unstructured problems. Moreover, due to the restricted nature of previous problems, the solutions that have been developed have typically been designed for a particular architecture; for more general problems, in order to target the broad range of installed machines, a degree of portability not previously required becomes necessary. Similarly, to meet cost constraints, potential solutions must be compatible with preexisting code which has historically not been the case.

This chapter provides, as motivation for the work in the sequel, an introduction to both parallel computing and VLSI applications. It introduces the approach taken in this research and highlights the most significant contributions.

-

# 1.1. Parallel and Distributed Computing

Parallel and distributed computing, the process of using multiple processing elements to solve a computing problem, has existed almost as long as computers themselves. This section provides a broad overview of the hardware and programming models in existence today.

# 1.1.1. Hardware Architectures

Traditionally, parallel and distributed architectures could be cleanly divided into two classes, *shared memory* architectures and *message passing* architectures. In recent years, *logically shared*, *physically distributed* architectures such as the Kendall Square KSR-1[1] have been introduced. Additionally, with the rapid increase in interconnectivity via local- and wide-area networks, virtually all machines support some form of message passing interconnection, giving rise to so-called hybrid architectures.

This section considers the key characteristics of each of these architecture classes. It should be noted that these are *hardware* architectures and do not necessarily reflect the programming model as viewed by the application programmer. It is possible, via compilers, run-time libraries, and operating systems, to implement any of the application programming models of the next section on any of the hardware architectures presented below. We use the term *low-level programming model* to describe the model supported directly by the hardware and *high-level programming model* to

## CHAPTER 1. INTRODUCTION

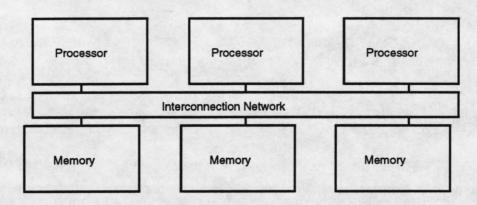

Figure 1.1 Shared memory multiprocessor.

describe the model provided to the applications developer. High-level models will be considered in Section 1.1.2.

## **Shared Memory**

Shared memory architectures are constructed from a number of processing and memory modules which are connected via an interconnection network (see Figure 1.1.) In the first generation of shared memory machines, processing modules generally lacked memory other than that represented by the registers in each CPU and the interconnection network was a bus. Both of these characteristics led to scaling problems. To improve performance, local caches were added to each processor; while this drastically cut the latency of memory references it introduced problems of cache-coherency. More advanced interconnection networks were also developed, including cross-bar and multistage networks.

Even though the addition of cache mechanisms has enabled the scaling of shared memory machines to larger sizes, the difficulty of maintaining cache coherence typically limits the feasibility of this approach to tens of processors.

# **Message Passing**

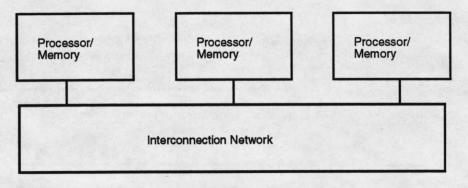

In message passing architectures, each processing module consists of both a processor and local memory. Processor modules are interconnected by a network (see Figure 1.2.) Typically, network bandwidths are at least an order of magnitude less than those of the buses in shared memory machines. The most significant characteristic of message passing systems is that each processor has its own individual address space; access to the network is explicit, via primitives such as send and receive. The bandwidth of the network in these architectures has traditionally been less than that of shared memory machines and often varies between different pairs of processors. As a result, these architectures are considered more scalable than shared memory architectures. Machines of this type have been built with thousands of processors. Of course, the lower bandwidth of the network means that many algorithms that perform well on shared memory machines may perform poorly on message passing architectures.

# 1.1. PARALLEL AND DISTRIBUTED COMPUTING

Figure 1.2 Message passing multiprocessor.

# Logically Shared, Physically Distributed Memory

In the late '80s, a new architecture was developed using techniques borrowed from both the shared memory and message passing architectures. This architecture uses hardware components similar to those developed for message passing to implement a low-level programming model mirroring shared memory. Thus, though an interconnection network is used, the hardware does not support send and receive primitives. Instead, the low-level programming model is a uniform address space and the hardware detects accesses to non-local memory, sending the appropriate messages to gain access to the necessary data. Consistency in these systems is usually maintained via a combination of hardware software in a mechanism called a directory[2]. Contemporary machines in this class are Non-Uniform Memory Architecture (NUMA) machines such as the Stanford DASH[2] and Cache-Only Memory Architecture (COMA) machines such as the KSR-1[1].

# Hybrid Shared Memory and Message Passing

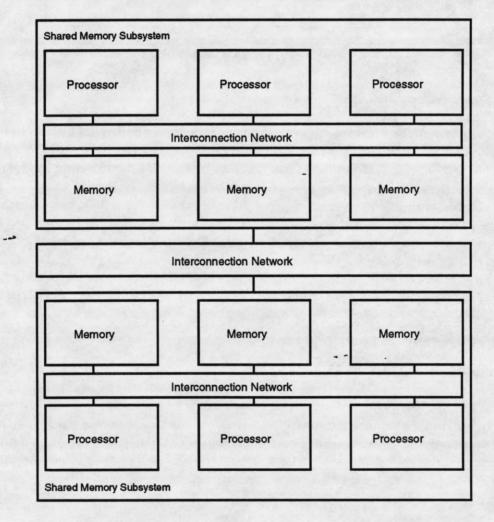

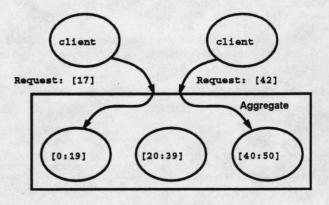

Hybrid architectures combine both shared memory and message passing architectures. Some processors will share a uniform address space; otherwise communication requires explicit sends and receives (see Figure 1.3.) With the recent dual growth in workstation clusters and desktop multiprocessors, hybrid machines are becoming ubiquitous. Further, MPP manufactures are beginning to consider hybrid architectures for their machines; the INTEL Paragon supports configurations which have shared memory multiprocessors at each node within the mesh interconnect.

# 1.1.2. High-level Programming Models

In this context, "high-level" means the programming model as seen by the applications programmer, not the operating system designer. The overall programming model can be broken into two fundamental components, the *communication model* and the *thread model*. Though a complete model requires aspects of both components, considering the components separately helps clarify the issues involved while making more explicit the space of possible complete models. While only a few combinations are currently in use, almost any combination of a communication model and a thread model could form a new complete programming model. We reiterate that these models are high-level and thus with proper software support could be implemented on any of the hardware architectures described in the previous section. For current purposes, we are not concerned with

Figure 1.3 Hybrid multiprocessor.

# 1.1. PARALLEL AND DISTRIBUTED COMPUTING

**Before:** a = 1; b = 2; c = 3; d = 4;

| Thread 1 | Thread 2 |  |  |

|----------|----------|--|--|

| a = 5;   | c = b;   |  |  |

| b = 10;  | d = a;   |  |  |

| •        | +        |  |  |

#### After: one of

a = 5; b = 10; c = 10; d = 5; a = 5; b = 10; c = 10; d = 1; a = 5; b = 10; c = 2; d = 5; a = 5; b = 10; c = 2; d = 1;

Figure 1.4 Communication and Consistency in Shared Memory.

the cost of high-level models on dissimilar low-level models.

#### **Communication Model**

The communication model defines how the "threads" of a program coordinate data interchange amongst themselves. Though we use the term 'thread' in this section, we defer precise specification of a thread to the sequel. For the purposes of this section, threads may be considered an active execution environment (stack) which vies for processor time with other threads.

**Shared Memory** In the shared memory programming model, the application sees a single flat address space. Communication is implicit, through access to shared variables. To fully support such a model, a method of interprocessor synchronization is necessary, usually implemented at the lowest level via atomic operations such as test-and-set or through higher-level abstractions such as semaphores. The exact semantics of a semaphore, i.e., busy-wait versus rescheduling, cannot be defined precisely without reference to a thread model.

Specifying the exact semantics of shared memory machines is complicated by the existence of different *consistency models*. With hardware support for caching and load/store reordering, the most conservative model of shared data consistency, *sequential consistency*[3], is prohibitively expensive. Thus in addition to the uniform address space, a shared memory model must explicitly define the aspects, both deterministic and non-deterministic, of access to shared memory.

An example of shared memory communication is shown in Figure 1.4. In the figure, two threads access two shared integer variables, a and b. Because the model specifies a shared address space, the variables exist at the same addresses in both threads. The figure demonstrates the consistency problem. Though the first thread stores 5 into a followed by storing 10 into b, it

## CHAPTER 1. INTRODUCTION

Figure 1.5 Communication through Message Passing.

is possible, under certain consistency models, for the second thread to see the change to b before seeing the change to a.

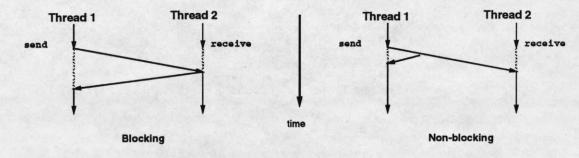

**Message Passing** In the message passing model, a send primitive is used to send data from one thread to another thread. An explicit receive operation must be executed before the data is available to the receiving thread. Figure 1.5 shows two possible ways communication can occur in a message passing model. In the blocking case, the send operation does not complete until the corresponding receive operation has begun. This style of communication is one of the types supported by the Thinking Machines CM-5 CMMD library. In the non-blocking case, the send operation completes when the necessary data are copied out of the application buffer; it is not necessary that the corresponding receive be executed. This type of message passing is common on the INTEL iPSC hypercubes. Variations on message passing provide for broadcasting, multicasting, synchronous and asynchronous communication, and typed messages.

## **Thread Models**

There are two principal thread models, which we will call physical and virtual.

**Physical Threads** In a physical thread model, the thread, as seen by the application program, is a processing element and generally available for "exclusive" use by the application. If the code running on a thread executes a blocking call, the entire thread is blocked for the duration of the call.

The physical model includes those systems which provide more threads than processors but for which the developer cannot rely on the underlying run-time library efficiently handling a number of threads vastly greater than the number of available processors.

**Virtual Threads** In a virtual thread model, the number of threads visible to the program is typically not related to the number of processing elements. Applications developers think in terms of a number of threads convenient for the application at hand. It is the responsibility of the underlying language and run-time support to map these virtual threads to physical processors. When a virtual thread blocks, it is expected that the underlying run-time support will find another virtual thread to schedule. This model is often referred to as *light-weight threads*.

## 1.1. PARALLEL AND DISTRIBUTED COMPUTING

#### **Complete Models**

A complete model is created by combining a communication model with a thread model and then specifying the semantics of the interaction between the two components. We consider three complete high-level models. Many more are possible, but the examples serve to demonstrate the issues involved.

**Unix Shared Memory Multiprocessor** The model of a Unix shared memory machine combines the shared memory and physical thread components. The underlying consistency model is that of the underlying hardware and varies from architecture to architecture. The model is considered physically threaded because the Unix operating system—in particular, the scheduler—does not perform well when the number of kernel-scheduled threads is much greater than the number of processors (e.g., 100 times or more.)

**MPI** The message passing interface (MPI) model is a send-receive model currently being standardized by a consortium of manufactures and users. The model is similar to the programming interfaces on the INTEL iPSC and Paragon multicomputers and supplied by libraries such as PVM[4] and Express[5].

The basic model provides a send/receive interface over a physically-threaded model. Programs written for this model are written for a fixed number of processors. While they can be parameterized by the size of the machine, the model provides little or no support for context switching a physical thread over multiple virtual threads.

In the MPI interface, the basic send/receive model is augmented with such concepts as process groups and environments, making the interface more applicable to virtual threads. Experience with the advanced virtual thread interface for message passing systems is, to date, limited.

Actor An actor model is based on continuation passing[6] using virtual threads. From the programmer's point of view, an actor is an object with its own thread of control that at most times is blocked waiting for a message—a continuation execution of one of its methods.

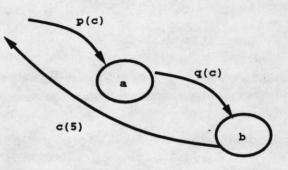

Continuation passing is similar to message passing but omits the explicit receive operation. Instead, each message sent contains enough information to determine the action to be invoked by the receiver. This model is much like the active messages model[7]. Figure 1.6 shows how continuation passing might occur in a C++-like language. In continuation passing style (CPS), execution of a member function is initiated through the execution of a continuation. In the figure, execution of the member p for actor a is initiated though calling a continuation and is represented by the arc labeled p(c). In response, a executes a member function of b by creating a continuation, x, from the actor address and member function pointer and using function call syntax to call the continuation. The figure demonstrates one of the important characteristics of CPS; control flow need not be stack-based as it is in function call mechanisms. In the example, b need not return a value to a in order for it to return to the caller of a : :p; instead, using the continuation c passed to a : :p and then to b : :q, the result is communicated directly to the initial caller.

The actor model combines continuation passing with a virtual thread model. Most of the time the thread associated with an actor is blocked waiting for the continuation execution of one of its methods. When a continuation destined for the actor is executed, the appropriate member

CHAPTER 1. INTRODUCTION

```

class Actor {

int data;

int p(Continuation c)

{ ...

Continuation x ( b, q );

x(c);

...

}

int q(Continuation c){ ... c(5) ... }

};

```

Actor a, b;

Figure 1.6 Communication through Continuation Passing.

function is executed. As part of the execution, the actor may execute other continuations, create new actors, or perform computations, possibly with side effects.

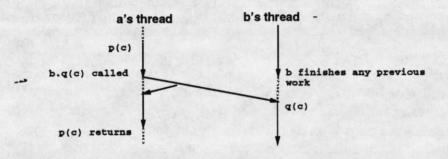

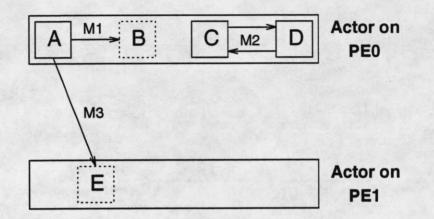

In a parallel context, continuations express parallelism because the call to a continuation returns after scheduling the future execution of the continuation body rather than synchronizing with the actual execution. Figure 1.7 shows how the execution of the code in Figure 1.6 might occur. a.p(c) is called via a continuation (not shown). In response, it does some processing and executes b.q(c) via a continuation. While processing the continuation call, the parameters are copied and a message is sent to the processor responsible for scheduling b's thread. As soon as the message send has started, a resumes its processing. At some later point, b finishes any previous continuation and becomes available to process the continuation from a. Each actor has a single virtual thread so only one message can be delivered at a time. The figure emphasizes the particular communication and thread models comprising the actor model. The communication style natural to actors is asynchronous; basing an actor implementation on a synchronous model would in most cases result in performance degradation. Since every actor has a thread and an actor is simply a concurrent object, actor programs typically have thousands if not hundreds of thousands of virtual threads. Thus, the virtual thread mechanism used by an actor implementation must be extremely efficient.

8

# 1.1. PARALLEL AND DISTRIBUTED COMPUTING

Figure 1.8 Spectrum of Parallelism. Arrows indicate increasing programmer effort.

**Comparison of MPI and Actors** With the MPI style interface much more well established, the actor model must provide significant benefits in performance or programmability to be considered useful.

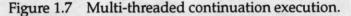

**Expression of Parallelism** One can view the gamut of parallelism as a one dimensional space with extremes representing completely serial and completely parallel programs (see Figure 1.8.) If we consider the MPI and actor programming styles, we see that they lie on opposite ends of the parallelism spectrum. For example, if we consider a send-receive code that sends two messages from a thread A to a thread B, in the most straightforward, synchronous case, parallelism is decreased by the imperative receive primitive:

| // Thread | 11     |       |    | // Thread | 1 2    |       |    |  |

|-----------|--------|-------|----|-----------|--------|-------|----|--|

| send( 2,  | type1, | data1 | ); | receive(  | type1, | data1 | ); |  |

| send(2,   | type2, | data2 | ); | receive(  | type2, | data2 | ); |  |

Though the semantics of the application may allow the messages to be processed in any order, the underlying model requires that the messages be received in the order sent and the serial nature of code execution implies that one receive command must precede the other. Though it is possible to express unordered reception via asynchronous send and receive primitives, such code is significantly more difficult to write. Thus, the basic MPI interface is represented at the left of the parallelism spectrum; the developer must apply *more* effort to express *more* parallelism.

In the actor model, message reception may occur as long as the actor is not processing a previous message. In contrast to the MPI case above, the actor will receive whichever message arrives at the actor thread first. There is, however, a dual to the MPI case; if there is a semantic dependency on message processing, the actor must handle the case where message reception order is reversed. In this case, the actor must delay processing of the second message until the first is received and processed. Thus, the actor model starts at the completely parallel end of the spectrum and requires that the programmer apply *more* effort to express *less* parallelism. The extreme amount of parallelism in an actor program can sometimes lead to difficulty in programming. To remedy this, most actor languages include constructs for shifting order maintenance from the programmer to the run-time system. As will be seen in Chapter 3, combing the actor model with an imperative language such as C++ also serves to simplify the expression of parallelism without putting an unacceptably large burden on the developer.

**Composability** Another point of comparison is the ease of *composability*, the process of taking two existing modules for solving unrelated problems and combining them into a single application

---

to solve a more complicated problem. For example, an application might require the processing of independent linear system solver and matrix multiplication problems. Composability, then, refers to the ability to take existing modules for solver and multiplication and to use them, without modification, to solve the appropriate subproblems.

In composability, physical thread-based models tend to fall short of the virtual techniques because partitioning, usually static, of available processors is required. Designers of message passing interfaces such as MPI are trying to implement ways of solving this problem but as yet there are no practical examples of such features.

Implementations of the actor model, being based on a virtual thread model, implicitly perform load balancing when a new actor is created. Thus, if an actor type exists for each of the solver and multiplication problems, an actor can be created for one without interfering with the other. It is the task of the run-time system to load balance and schedule the actors to take advantage of available processing elements.

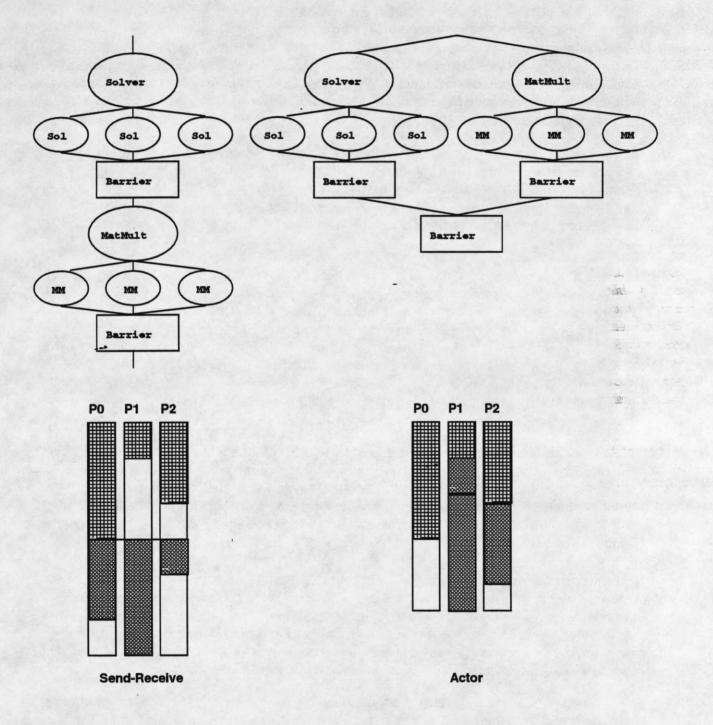

Figure 1.9 shows graphically the difference between typical message passing and actor implementations of the linear system solver and matrix multiplication problem. In the message passing case, we assume a function exists for each subproblem and that each function assumes it has full use of the multiprocessor. Thus, individually each of the two subproblems is solved in parallel but the two subproblems are sequentially ordered with barriers. If the matrices are sparse, as is typical, it is often difficult to use the processors efficiently. In the actor case, since each subproblem is represented by an actor, the two actors, and by extension, the subproblem actors, are created in parallel and only synchronized when the two operations are completed. The result is higher processor efficiency. (The barriers shown in the actor example are symbolic; though an actor model does not have blocking primitives, the combination of the code effectively creates barriers.)

Integration of Object-Oriented Design Techniques Since continuations are a language-based concept, their integration into object-oriented languages is relatively straightforward. In an object-oriented language, a continuation conceptually contains both the address of the target object and a pointer to the method to be invoked on the target object. The dynamic binding mechanism (virtual functions in C++) is invoked in exactly the same manner as it is for serial languages.

On the other hand, in the send-receive model communication looks more like an input/output operation. When a number of possibilities exist for the type of a received message, some sort of type-globbing mechanism is necessary in the receive primitive. Subsequently, a type switch, e.g.,

if ( type == a )

...

else if ( type == b )

is required. Type switches are difficult to maintain and anathema to object-oriented design. The elimination of the need for such constructs was one of the main impetuses for the development of the object-oriented methodology. Any technique, such as continuation passing, which obviates the need for type switches is considered highly desirable.

# 1.1. PARALLEL AND DISTRIBUTED COMPUTING

調査

\*

一た

1.000

# 1.2. VLSI Computer-Aided Design

The types of large, unstructured problems encountered in general computing are typified by those in electronic design automation for VLSI CAD. Examples of VLSI CAD problems are:

- ATPG Automatic test pattern generation (ATPG) for VLSI circuits is a difficult problem (NPcomplete) which is nonetheless critical if the quality of ever larger VLSI devices is to be maintained.

- **Synthesis** Owing to increasing circuit densities, the last decade has seen a considerable increase in interest in algorithms for the automatic synthesis of VLSI circuits. Industry consensus is that only through synthesis will it be possible to manage the design complexity of the current and coming generations of VLSI chips. Most synthesis algorithms are both memory and processor intensive and display a quality of results tightly coupled to the resources applied to the problem.

- Extraction Extraction is the process of taking a VLSI mask-level layout and extracting circuit connectivity and parametric values. The results of extraction are used to verify both design correctness and performance requirements, usually after automatic cell placement and routing. Extraction is typically performed in terms of rectangles on various masks of the layout; the number of these rectangles can approach 100 million on contemporary microprocessor designs. Few processors in industry have the resources to handle such a design efficiently. Given the frequency of this problem (extraction is usually iterated with design changes to verify changes and to update extracted parametric information), techniques to take advantage of all available resources are valuable.

- **Cell Placement and Routing** When logic design for a VLSI circuit has been completed, cell placement and routing are performed. With chips approaching tens of millions of gates, the complexity of these problems is enormous. Moreover, one of the most popular techniques for placement, simulated annealing, is an inherently expensive operation. As in most other CAD tasks, the quantity of resources applied to the problem has a direct impact on the quality of results.

With the preponderance of evidence indicating that virtually any method of managing the algorithm development process and any technique for improving quality through the application of additional resources would appear promising, it is perhaps surprising that neither parallel processing nor object-oriented techniques are well represented in the CAD development community. To date, with few exceptions, the only use of either technology is almost exclusively in the area of graphical user interfaces(GUIs). This situation is not without justification:

• For more than a decade, most CAD development has been performed in the C programming language and until the advent of C++ use of an object-oriented language implied the sacrifice of existing code, an unacceptable alternative. With the availability of C++, adoption is slowly occurring. C++ is easily an order of magnitude more complicated than C and is still undergoing rapid development; development tools are only now attaining the degree of stability needed for even the most aggressive commercial development.

# 1.3. APPROACH

- Due to a lack of widely available libraries (again, outside the GUI area) much of the promise

of C++ remains to be realized. Given the ability of C++ to trade flexibility for efficiency,

the process of generating reusable code is made more complicated by the fact that the set

of design choices, in terms of flexibility versus overhead, for one application may not be

acceptable for another; CAD problems, with their inherent complexity and size, are known

to be sensitive to overheads in area or space.

- Until recently, the wide-spread availability to CAD users of parallel platforms has been severely limited. Supercomputers have in general been limited to the restricted applications mentioned previously and thus the techniques developed for these platforms have had no place for application in the CAD community. This situation leads to a chicken-and-the-egg problem: with little availability of parallel platforms, interest in parallel solutions to CAD problems has been relatively low. With only limited development of parallel applications, little impetus exists for CAD users to explore the cost-benefit tradeoff of parallel platforms, even though the costs associated with VLSI development and fabrication are high and timeto-market is a critical factor.

- The generation of *useful* parallel algorithms has also been impeded by concurrent rapid improvement in serial algorithms. Often by the time a parallel CAD algorithm is completed, it lags significantly behind the quality, and sometimes even the performance, of contemporary serial algorithms.

# 1.3. Approach

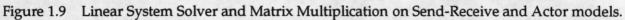

Based on past experience, a strong argument can be made that any practical, parallel, unstructured application—and CAD applications in particular—must be based on models and implementations that are portable across the widest variety of parallel machines, scalable to the maximum degree feasible, and based initially upon the best available serial algorithm. These constraints are explicitly addressed in the approach taken in the ProperCAD project. The goal of the project is the development of a library which provides a seamless, high-level programming model across a variety of parallel architectures along with a set of applications based on that model that address the most significant tasks in electronic design automation [9, 10, 11].

The main portion of the work reported here is the development of a layered library which can be used as the basis for porting serial algorithms to an abstract parallel machine. The library is divided into two layers. The lower half, the abstract parallel architecture, interfaces with underlying hardware and system software to provide a consistent interface across a wide variety of parallel machines including heterogeneous combinations of parallel architectures. The upper half, the actor interface, is an implementation of the actor-model of concurrency which, through abstraction, simplifies the task of writing parallel applications. The actor interface helps the application designer avoid dealing with low level, architecture-dependent issues.

Specific contributions of this work are:

1. A library approach to portable, actor-based parallelism in a strongly- and statically-typed language.

-2

# CHAPTER 1. INTRODUCTION

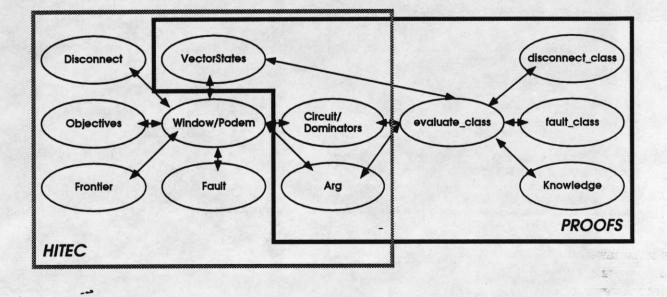

Figure 1.10 An overview of the ProperCAD project [8].

- 2. A set of classes for controlling, or meta-programming, an actor system on contemporary medium-grain machines.

- An implementation of aggregates with additional features applicable to medium-grain computation.

- 4. An abstract parallel architectural model, with an object library-based implementation, which is capable of describing the full range of contemporary parallel architectures.

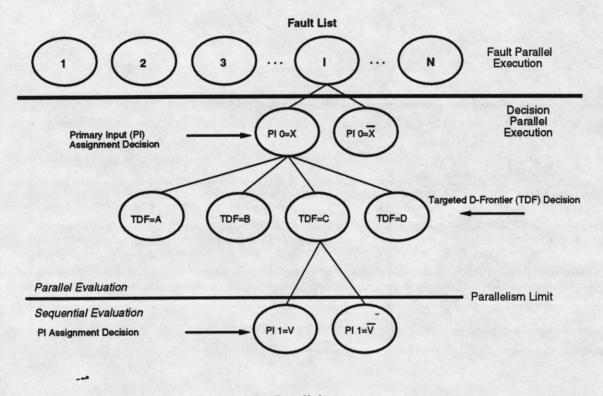

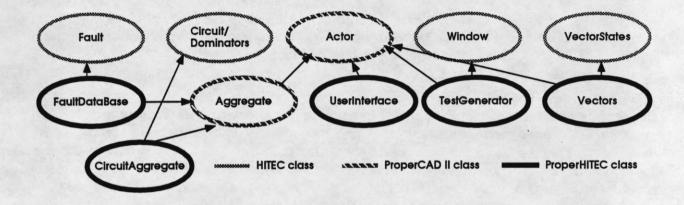

- 5. A parallel algorithm for ATPG, incrementally derived from a well-known top performing algorithm, which achieves significant multiprocessor utilization without degradation of resultant quality.

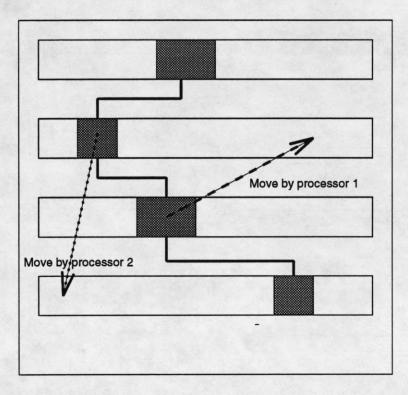

- 6. A parallel algorithm for cell placement which achieves significant multiprocessor utilization without degradation of resultant quality.

# 1.4. Report Overview

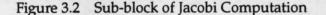

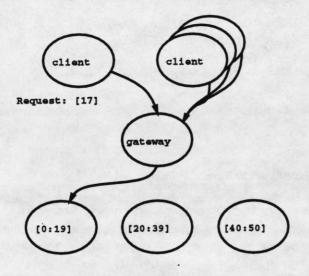

The sequel is broken into two parts. The first part presents our approach to concurrent objectoriented computing. A small numeric kernel, the Gauss-Jacobi algorithm for the solution of partial differential equations, is used to exemplify the approach. Individual chapters present an overview of the library, the low-level abstract parallel architecture, the high-level actor interface, and the results of the Jacobi kernel on a number of parallel platforms.

# 1.4. REPORT OVERVIEW

The second part details two CAD applications, ATPG and cell placement. Each problem is described along with a description of the serial algorithm which forms the basis for the parallel application. The parallel application is then described and performance results presented.

----

CHAPTER 1. INTRODUCTION

# Part I Run-Time Library

-

# 2 Overview

# 2.1. Approach

The approach to parallelism taken in this research is the development of a library which provides simultaneously a high-level, object-oriented abstraction to application programmers and an underlying run-time implementation of that interface tuned to the highest efficiency possible. The library enables an application designer to incrementally apply object-oriented programming mechanisms to develop a parallel application while maintaining compatibility, i.e., sharing code, with an existing serial application. This approach differs from previous work in a number of ways, most notably in the sets of target architectures, applications, and languages.

# 2.1.1. Targets

In this work, we specifically target those architectures developed atop contemporary microprocessor technologies, supporting medium-grain parallelism. Likewise, the target application set consists of those applications which require medium-grain parallelism. The term *medium-grain* requires some clarification.

# **Medium-grain Parallel Architectures**

It is fairly simple to quantify the difference between fine-grain architectures and others, fine-grain architectures being those having upwards of a thousand processors, network latency on the order of a few microseconds, and per-node memory sizes on the order a few kilobytes per MIP of processing power[12].

Coarse-grain applications are ones for which the ratio of computation to communication is very high. Rather than trying to define an exact level of performance to differentiate coarse-grain applications, it is helpful to consider protection boundaries. If processes must validate all communication with other processes for complete safety, we would consider such communication coarse-grain. The motivation for such differentiation is that the overhead implied by such checking usually places a lower bound on the cost of communication, thus limiting performance as communication requirements increase.

Medium-grain architectures cover the wide but ill-defined range between fine- and coarsegrain architectures. Current machines from Thinking Machines, Intel, and Cray fit within this class, as do clusters of workstations incorporating the most recent networking technologies. For the purpose of this work, we consider clusters of workstations connected via an Ethernet LAN to be medium-grain machines. Depending on the speed of routers and bridges, even workstations connected to multiple Ethernet segments could provide enough performance for some applications.

#### Medium-grain Parallel Applications

While it is difficult to quantify the characteristics which make an application medium-grain, the library demonstrates this leaning in the interface it provides to the programmer. The library provides a set of parallel constructs which can be used to express parallelism while not precluding the use of native constructs provided in the language. In contrast, fine-grain parallel languages such as the original actor languages differ in that all constructs are implicitly parallel[13]. Though it is possible to express programs in the library using exclusively parallel interfaces, the performance of such an application on the targeted architectures is not likely to be high.

Even more difficult to distinguish is medium-grain parallelism from coarse-grain parallelism. The most significant difference between the medium-grain target here is the integration with the target language. Medium-grain implementations try to reduce the conceptual barrier between parallel and serial constructs. Additionally, on coarse-grain systems parallel constructs such as message passing typically cross hardware protection boundaries and incur significantly more overhead than the equivalent medium-grain operation. Just as an application aimed at fine-grain parallelism is likely to perform poorly on a medium-grain system, an application written for medium-grain parallelism is likely to suffer on an architecture where communication is burdened with large overheads.

# 2.1.2. Constraints

Several significant constraints were placed on the design space that was explored in development of the library. Most constraints were a result of the targeted application communities and practical usability.

#### C++

The overriding constraint was that the implementation be in either C or C++, with a noted preference for C++. The choice of C++ was made for two reasons. First, C++ has a level of expressiveness not found in other object-oriented languages. Unlike most object-oriented languages, C++ has the ability to express very low level constructs. This ability is critical to CAD applications which manipulate huge datasets and where even small overheads in data structures or functions can have dramatic impacts on application performance. C++ is also available on virtually all machines, parallel machines being notorious for lacking all but the most basic programming support. In view of this last observation, no extensions to either C++ or the programming environment were considered, such extensions being likely to prohibit the use of existing compilers and debuggers.

#### Portability

The wide variety of extant medium-grain parallel architectures makes the issue of portability extremely important; an implementation that is difficult to port would have little chance of success. Therefore, a major goal of the library design process was to try to isolate any machine-dependencies from both the application developer and, to the greatest extent feasible, the components of the library itself.

## 2.2. LIBRARY COMPONENTS

| Actor Interface | e (AIF)                                 |

|-----------------|-----------------------------------------|

| Virtual Threa   | ads                                     |

| Continuation    | n Passing Style                         |

| Support for:    |                                         |

| Load Bala       | ncing                                   |

| Prioritizat     | lon                                     |

|                 | lel Archicture (APA)<br>read Management |

| Memory Mar      |                                         |

|                 | tion Management                         |

| oominumea       |                                         |

| Virtual Mach    | ine Configuration                       |

| Virtual Mach    | line Configuration                      |

Figure 2.1 The ProperCAD II Library

# 2.2. Library Components

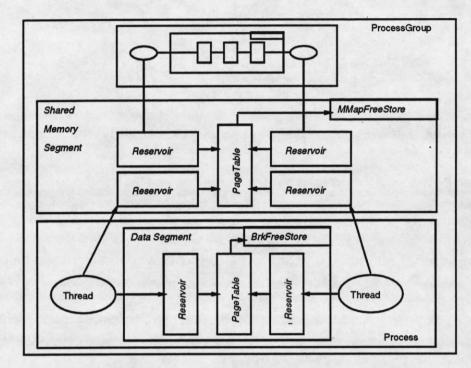

To simultaneously maximize the portability and efficiency of the library, the library was broken into two distinct interfaces (see Figure 2.1.) The upper level of the library, the Actor Interface (AIF), provides a high-level programmer interface, one that helps the application developer limit complexity, via abstraction and encapsulation, without limiting parallelism. The Actor Interface is based closely on the Actor paradigm and supports several advanced features such as aggregates (collections of actors) and meta-programmability.

The lower of the two interfaces, the Abstract Parallel Architecture (APA), provides a set of objects and interfaces which can be used to describe and utilize resources needed by virtually any programming model, across a wide variety of architectures. Such resources include processor threads, synchronization primitives, and memory management functions.

# 2.3. Related work

There are many approaches to concurrent object-oriented programming, covering wide ranges of both techniques and targeted platforms and applications. Since the work presented in the sequel is based on the Actor model targeted to medium-grain parallel architectures, previous work in these areas is considered in detail. Alternate approaches are considered more briefly. Previous work is divided into language-based work and library-based work, with languages further broken into actor and non-actor models.

# 2.3.1. Actor Languages

The Actor model for concurrent computing was first proposed by Hewitt[14] and subsequently refined and codified by Agha[13, 15]. In its original form, it is a message-driven model targeted towards fine-grain, massively parallel platforms.

A number of pure actor languages have been implemented since the proposal of the original model. Following the original model, most Actor languages are functional, i.e., side-effect free, and untyped. The majority of implementations are targeted to fine-grain concurrency on massively-parallel MIMD architectures. Few of the original actor languages were actually implemented on distributed machines. The earliest languages were Act[13], Act1[16], Act2[17], Act3[13], Sal[13], and ABCL/1[18]. A more recent contribution, with an emphasis on reflection, is MERING IV[19]. Of particular note is the HAL language of Houck and Agha[20] which was implemented on top of the Charm programming system[21]. HAL is a truly distributed implementation and is notable for having formed the basis for further exploration into extensions of the Actor model.

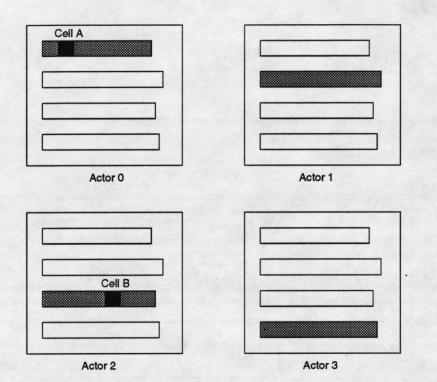

# Aggregates

Chien[12] recognized the need for a multi-access interface to augment the serial interface of Actors. He proposed aggregates as collections of actors which present a unified, yet multi-access, interface to client code. Key to aggregates is support for efficient intra-aggregate addressing. Chien developed an actor language, Concurrent Aggregates (CA), which in addition to the features of actors, aggregates, and intra-aggregate addressing, provides support for first-class continuations and messages.

The Concert system of Chien, Karamcheti and Plevyak[22, 23], is a compiler and run-time support system for CA on stock hardware, i.e., such contemporary parallel machines as Thinking Machines' CM-5 and Intel's Paragon. The emphasis of the Concert system is on extensive compiler analysis and optimization.

# ActorSpaces

Recently, Agha and Callsen[24] have proposed ActorSpaces as a technique for extending the actor model to open systems. ActorSpaces offer an alternate approach to collections of actors than that of aggregates. Rather than the fixed-size, homogeneous collections of actors in CA, ActorSpaces represent variable-sized heterogeneous collections of actors. The emphasis in ActorSpaces is on providing an open interface, via which an actor can communicate with other actors without knowing *a priori* of the existence of the other actors, something not possible in the basic actor model.

# Charm

Charm[25, 21, 26] was developed specifically to address the need for a portable, parallel interface and implementation for parallel programming across a wide variety of both shared memory and message passing architectures. Charm differs from other actor languages in that it is targeted to medium-grain architectures rather than the fine-grain architectures. Among the most significant and unique features of Charm are:

#### 2.3. RELATED WORK

**Imperative-Language Interface** Charm represents an extension of the C programming language with extensions to support actor- and aggregate-like characteristics. With a few exceptions, most of the the imperative constructs of C are retained. Recently, with the introduction of Charm++, the C-language model of Charm has been extended to a C++-based interface.

**Meta-programming features** Charm provides developer-visible models for the operation of the underlying run-time system in the areas of load-balancing and prioritized message delivery. Strategies in both areas can be selected from a set of alternatives at link-time. Of particular note is work with lexicographically-ordered message priorities applied to search problems[27].

**Library Types** Charm provides a library of object types with parallel semantics such as read-only variables, distributed computation types such as accumulators, and distributed mappings.

The first phase of the ProperCAD project, to which this work is a successor, was based upon Charm and many of the issues addressed in this work reflect the experience gained in using Charm.

# 2.3.2. Non-actor Language-based Approaches

Significant work has been done in concurrent object-oriented computing not based upon the actor model. We consider in particular C- and C++-oriented solutions.

Gannon and Lee[28] developed pC++, an extension of C++ with support for distributed data structures. The flavor of pC++ is much that of High-Performance FORTRAN (HPF). pC++ provides support for distributed collections of arbitrary types, both array-based and tree-based, with full support for the C++ mechanisms of derivation and dynamic-binding.

Compositional C++, or CC++, proposed by Chandy and Kesselman[29] takes an alternate approach to parallelism; where in pC++ processor control is implicit in the parallel data structures, in CC++ parallelism is achieved though imperative constructs which cause particular code fragments to be executed concurrently on different processing threads. CC++ also provides a number of synchronization primitives necessary for a thread-oriented programming interface.

The Experimental Systems Kernel, or ES-Kit, of Leddy and Smith[30] is implemented via modifications to an existing C++ compiler and as such tries to stay true to the spirit and syntax of C++. In ES-Kit, pointers are extended to address a global namespace and remote execution is represented by the execution of a method call though a pointer to a non-local address. Object distribution is either automatic or under program control via the C++ placement syntax[31]. The fundamental parallelism constructs in ES-Kit are remote procedure calls (RPCs) and futures[32].

The Amber system[33], derived from Presto[34], is an extension of C++ targeted specifically toward a workstation cluster running the Topaz operating system[35]. In Amber, the approach is to explicitly locate a shared datum on a particular node and then to cluster Topaz threads on that node. When access is made to a remote node, the run-time system traps to the Amber kernel and the thread of control is transferred to the processor on which the data value resides.

COOL, developed by Chandra, Gupta, and Hennessy[36], is also based on thread-explicit extensions to C++, in this case targeted towards shared memory architectures in general and the Dash architecture in particular. COOL provides a full-range of classical synchronization constructs.

Linda, developed by Carriero and Gelernter[37], represents a relatively radical approach to concurrent processing. In Linda, shared data are represented by a shared *tuple-space* to which all functions have access. Elements in the tuple space are key-value pairs which are accessed via pattern matching on the key. This formulation has particular benefit in logic-programming and artificial-intelligence and was one of the motivations for the development of the ActorSpaces extension to the actor model.

POOL-T, developed by America[38], is based upon message passing but uses synchronous message passing rather than the asynchronous message passing of actors. POOL-T is targeted particularly towards large system development on medium-parallelism architectures and was developed from the beginning with an interest in applying formal methods for proving program correctness.

# 2.3.3. Library-based Approaches

One of the most attractive aspects of library-based approaches is that they are at least to a first approximation compatible with existing compilers and other development tools. Again, we consider C and C++ libraries.

ACT++ is a C++ library-based implementation of the actor paradigm developed by Kafura and Lee[39]. ACT++ implements an Actor base class which supports the actor model primitives, *new*, *send*, and *become*. Additionally, ACT++ supports an RPC-style of actor method invocation[13]. ACT++ supports the use of normal (non-actor) C++ objects, but only as private, non-shared acquaintances of an actor. ACT++ is targeted toward medium-grain architectures but implementation details on parallel architectures have not yet been reported.

The Paragon project of Chase, Cheung, Reeves and Smith[40] is implemented via a C++ library for support of distributed data structures. Support is provided for distributed arrays, both through partitioning and replication.

PVM, developed by Sunderam et al.[4] is a widely used library for parallel programming on local area network-connected processors and, recently, a number of parallel architectures. The library provides C and FORTRAN interfaces for synchronous and asynchronous message passing and provides support for heterogeneity of processing elements, both in data representation and processing power. Included tools provide particularly strong support for easy machine configuration, debugging, and performance analysis.

p4, developed by Butler and Lusk at Argonne National Laboratory[41], provides a similar message passing interface to that of PVM and also adds an interface for shared memory. In addition to supporting network-connected processors, p4 provides support for a wide range of parallel platforms.

# **3** Actor Interface

The actor model is the high-level and preferred interface for application development. In this chapter we consider the objects in the ProperCAD II library that support an actor model. We begin with an examination of the original actor model.

# 3.1. Actor Model

The fundamental object in an Actor paradigm is the actor. An actor is an object which communicates with other actors by sending messages. Message delivery in an Actor system is *reliable*, *unordered*, and *fair*. Reliability guarantees that messages that are sent will be delivered. Delivery, however, is unordered; two messages sent from one actor to another are not guaranteed to be received in the order sent. Fairness guarantees that no actor can delay indefinitely the processing of a message by flooding a receiver with messages.

All actions an actor performs are in response to messages; i.e., the model is message-driven. When a message is received, the receiving actor can perform a number of actions in response. The possible actions are use the send primitive to send a message to an existing actor; use the new primitive to create a new actor; and use the become primitive to change its behavior.

**send** An actor can send a message to any actor for which it knows the receiving actor's name.<sup>1</sup> Actors know their own name and can determine the name of any actor they create. Actor names can be communicated as part of the contents of a message. Otherwise, an actor cannot determine the name of an arbitrary actor and thus cannot send such an actor a message. This property is key to the formalism of the actor model but is also important in that it facilitates encapsulation in software design. The send operation completes when the message has been passed to the run-time system; delivery is asynchronous.

**new** An actor can create new actors using the new primitive. Creating a new actor is similar to sending a message; the actual birth of the actor is asynchronous with respect to the execution of the creating actor.

**become** An actor can change its behavior via the become primitive. The utility of the become operation is unclear in languages such as C++ which have side-effects. Since it has not yet been shown to be useful in targeted algorithms, we omit further discussion.

<sup>&</sup>lt;sup>1</sup>Agha[13] refers to these names as mail-addresses.

# CHAPTER 3. ACTOR INTERFACE

| C++ Object      | AIF Object     | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| object          | Actor          | An actor has parallel semantics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| none            | Aggregate      | C++ has no built-in collection types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| object pointer  | ActorName      | ActorNames are pointers to Actors or Aggregates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| none            | AggregateName  | AggregateNames are pointers to Aggregates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| member function | ActorMethod    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| constructor     | NewActorMethod | the first of the second s |

| none            | Continuations  | A Continuation is a bound member function pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| value           | Message        | Used as argument to continuations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 3.1 Comparison of C++ and AIF objects