# A PORTABLE SOFTWARE TOOL FOR MEASUREMENT OF TRANSIENT ERRORS IN COMMERCIAL MICROPROCESSORS

Karen E. Wells and Janak H. Patel

N

Coordinated Science Laboratory University of Illinois at Urbana-Champaign 1308 West Main Street, Urbana, IL 61801

| REPORT                                                                                                                                                                                                                                                          | Form Approved<br>OMB NO. 0704-0188                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gathering and maintaining the data needed<br>collection of information, including suggest                                                                                                                                                                       | f information is estimated to average 1 hour per res<br>, and completing and reviewing the collection of inf<br>ions for reducing this burden, to Washington Heado<br>2202-4302, and to the Office of Management and                                                                                         | ormation. Send comment regardin<br>uarters Services. Directorate for in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ng this burden estimate or any other aspect of this<br>Information Operations and Reports, 1215 Jefferson                                                                                                                                                                                                                                                                                    |

| 1. AGENCY USE ONLY (Leave blank)                                                                                                                                                                                                                                | 2. REPORT DATE<br>May 2001                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AND DATES COVERED                                                                                                                                                                                                                                                                                                                                                                            |

| 4. TITLE AND SUBTITLE<br>A Portable Software Tool for M<br>Microprocessors                                                                                                                                                                                      | leasurement of Transient Error                                                                                                                                                                                                                                                                               | rs in Commercial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5. FUNDING NUMBERS<br>NASA-JPL-1215699                                                                                                                                                                                                                                                                                                                                                       |

| 6. AUTHOR(S)<br>Karen. E. Wells and Janak. H.                                                                                                                                                                                                                   | Patel                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                              |

| 7. PERFORMING ORGANIZATION NAMI<br>Coordinated Science Laborator<br>University of Illinois at Urbana<br>1308 West Main Street<br>Urbana, Illinois 61801-2307                                                                                                    | ry                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8. PERFORMING RGANIZATION<br>REPORT NUMBER<br>UILU-ENG-01-2210<br>(CRHC-01-01)                                                                                                                                                                                                                                                                                                               |

| 9. SPONSORING/MONITORING AGENC<br>Jet Propulsion Laboratory<br>4800 Oak Grove Drive<br>Pasadena, CA 91109                                                                                                                                                       |                                                                                                                                                                                                                                                                                                              | 10. SPONSORING/MONITORING<br>AGENCY REPORT NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              |

| 11. SUPPLEMENTARY NOTES<br>The views, opinions and/or find<br>official position, policy or decisi<br>12a. DISTRIBUTION/AVAILABILITY STA                                                                                                                         | ion, unless so designated by othe                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | and should not be construed as an           12b. DISTRIBUTION CODE                                                                                                                                                                                                                                                                                                                           |

| Approved for public release; di                                                                                                                                                                                                                                 | stribution unlimited.                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                              |

| The REE project attempts to impudevoted to bringing commercial s<br>and are therefore susceptible to tr<br>The software tool developed for t<br>radiation. It will estimate the loca<br>high-level language C and is brok<br>designed to be portable across sev | rove the reliability of commercial<br>supercomputing technology into sp<br>ansient errors due to alpha-particl<br>his research runs on a microproce<br>ation of any errors encountered an<br>ten down into separate routines fo<br>yeral different platforms and is int<br>technique of power supply disturb | off-the-shelf (COTS) more accean correct of the second correct of | ration and Experimentation (REE) project.<br>microprocessors by supporting research<br>essors are typically not radiation hardened<br>ace environments.<br>Sure the error rate of a processor exposed to<br>in these errors. The program is written in<br>the unit in a microprocessor. The tool is<br>al information about the state of system.<br>ented that verify the tool is capable of |

| 14. SUBJECT TERMS                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15. NUMBER OF PAGES<br>62                                                                                                                                                                                                                                                                                                                                                                    |

| Error detection, SEU, Microproce<br>Error latency                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16. PRICE CODE                                                                                                                                                                                                                                                                                                                                                                               |

| 17. SECURITY CLASSIFICATION<br>OF REPORT<br>UNCLASSIFIED                                                                                                                                                                                                        | 18. SECURITY CLASSIFICATION<br>OF THIS PAGE<br>UNCLASSIFIED                                                                                                                                                                                                                                                  | 19. SECURITY CLASSIFIC<br>OF ABSTRACT<br>UNCLASSIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                              |

1

Ì

1

Ì

İ

### A Portable Software Tool for Measurement of Transient Errors in Commercial Microprocessors

Karen E. Wells and Janak H. Patel University of Illinois at Urbana-Champaign

#### ABSTRACT

This research describes a software tool that was written to support NASA's Remote Exploration and Experimentation (REE) project. The REE project attempts to improve the reliability of commercial off-the-shelf (COTS) microprocessors by supporting research devoted to bringing commercial supercomputing technology into space. COTS microprocessors are typically not radiation hardened and are therefore susceptible to transient errors due to alphaparticle radiation found in space environments.

The software tool developed for this research runs on a microprocessor to detect and measure the error rate of a processor exposed to radiation. It will estimate the location of any errors encountered and output information on these errors. The program is written in the high-level language C and is broken down into separate routines for each testable hardware unit in a microprocessor. The tool is designed to be portable across several different platforms and is intended to provide crucial information about the state of the system. Using the physical fault injection technique of power supply disturbances, results are presented that verify the tool is capable of detecting errors within the processor.

Key Words: Error detection, SEU, Microprocessors, Control flow error, Fault injection, Error rate, Error latency

This material is based upon work supported by the NASA-JPL under Award No. 1215699

# TABLE OF CONTENTS

1

ſ

Î

Ĵ

Î

.

| 1  | INTRODUCTION                                                                                                                                                                                                                            | 1 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2  | RELATED WORK                                                                                                                                                                                                                            | 4 |

| 3  | TRANSIENT ERROR OVERVIEW.         3.1       Single-Event Upsets.         3.2       Analysis of Transient Faults.         3.3       Fault Models.                                                                                        |   |

| 4  | SOFTWARE ERROR DETECTION TECHNIQUES         4.1         Time Redundancy         4.2         Consistency Checks                                                                                                                          |   |

| 5  | PROCESSOR MODEL                                                                                                                                                                                                                         |   |

| 6  | TESTING THE INTEGER UNITS         6.1       Addition         6.2       Subtraction         6.3       Multiplication         6.4       Division         6.5       Logical AND         6.6       Logical OR         6.7       Logical XOR |   |

| 7  | TESTING THE REGISTER UNIT         7.1       Fault Model         7.2       Functional Vectors                                                                                                                                            |   |

| 8  | TESTING THE LOAD/STORE UNIT.<br>8.1 Fault Model.<br>8.2 Functional Vectors.                                                                                                                                                             |   |

| 9  | TESTING THE INSTRUCTION FETCH UNIT         9.1       Fault Model         9.2       Functional Vectors                                                                                                                                   |   |

| 10 | TESTING THE BRANCH PROCESSING UNIT                                                                                                                                                                                                      |   |

| 11 | FAULT INJECTION METHODS         11.1 Radiation Injection         11.2 Power Supply Disturbances                                                                                                                                         |   |

| 12 | EXPERIMENTAL RESULTS                                                                                                                                                                                                                    |   |

|    | 12.5 Results                                                 |    |

|----|--------------------------------------------------------------|----|

|    | 12.5.1 Power supply disturbances                             |    |

|    | 12.5.2 Weak radiation exposure                               |    |

|    | 12.5.3 Temperature increases coupled with power supply distu |    |

| 13 | 3 CONCLUSIONS AND FUTURE WORK                                |    |

|    | REFERENCES                                                   | 51 |

|    | APPENDIX A REETOOL USER'S GUIDE                              |    |

|    | A.1 Setting Up the Board with the Serial Connection          |    |

|    | A.2 Using vDESKTOP                                           |    |

|    | A.2.1 Establishing a serial connection                       |    |

|    | A.2.2 Downloading the visionWARE file and updating the firm  |    |

|    | A.3 Running the Program                                      |    |

|    | A.4 Statistical Output                                       |    |

|    | A.5 Making Changes to the Program                            |    |

1

Î

Î

ľ

Ĵ

I

Ì

## LIST OF TABLES

Ĵ

Ì

Ì

Ĵ

1

P

Į

1

Ĵ

Ĵ

| Table                                                       | Page |

|-------------------------------------------------------------|------|

| 1: Minimum Test Set for Ripple Carry Adders Under MCFM [19] | 20   |

| 2: Vectors for Integer Multiplication.                      |      |

| 3: Dependent Integer Multiplication Vectors.                | 23   |

| 4: Vectors for Integer Division.                            | 23   |

| 5: Dependent Integer Division Vectors                       |      |

| 6: Truth Table for AND Function.                            |      |

| 7: Truth Table for OR Function.                             |      |

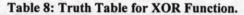

| 8: Truth Table for XOR Function.                            |      |

| 9: Operations and Running Times for Each Routine.           |      |

| 10: Results from the Power Supply Disturbance Experiments.  |      |

| 11: Command Line Options for REETool.                       |      |

| Figure                                                      | Page |

|-------------------------------------------------------------|------|

| 1: Time Redundancy Example.                                 |      |

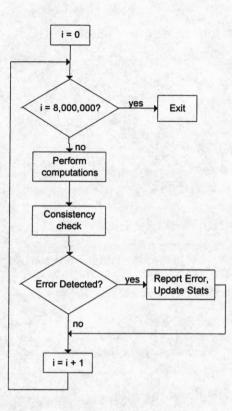

| 2: Flowchart for Functional Unit Routines.                  |      |

| 3: MPC750 Processor Block Diagram.                          |      |

| 4: Example Code for Independent Integer Addition Operations |      |

| 5: Example Code for Dependent Integer Addition Operations.  |      |

| 6: Example Code for the Logical AND Routine.                |      |

| 7: Example Code for the Logical OR Routine.                 |      |

| 8: Example Code for the Logical XOR Routine                 |      |

| 9: Example Code for the Register Unit.                      |      |

| 10: Example Code for the Load/Store Unit                    |      |

| 11: Example Machine-Level Instructions.                     |      |

| 12: General Instruction Format                              |      |

| 13: Example Code for the Intruction Fetch Unit.             |      |

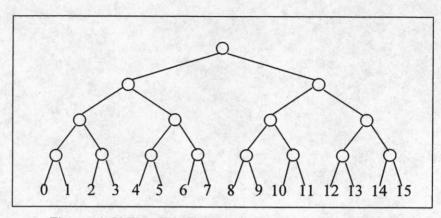

| 14: If-Then-Else Tree for the Branch Prediction Unit.       |      |

| 15: Example Code for the Branch Processing Unit.            |      |

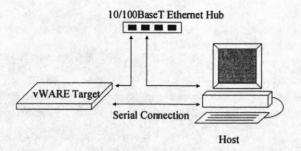

| 16: Sample Hardware Setup.                                  |      |

## LIST OF FIGURES

I

1

I

Î

P

Į

1

1

Ĵ

#### **1** INTRODUCTION

This research describes a software tool that was written to support NASA's Remote Exploration and Experimentation (REE) project. The work was supported by the NASA Jet Propulsion Laboratory (JPL).

#### 1.1 Background

The prevention of system failure in space applications is extremely important. The consequences of failures can be costly and hazardous. Of particular concern are temporary errors, specifically, those due to transient faults. Transient faults are induced by external perturbation such as power supply fluctuations or radiation. In space applications, they are predominantly caused by alpha particle radiation. As a result, many companies aim to produce radiation-hardened systems to be used in space programs. However, these systems are often more costly, higher in volume, higher in mass and power consumption, and lower in performance than components presently available off-the-shelf. In particular, today's microprocessors that are available commercially have many advantages over those in radiationhardened systems. Commonly referred to as commercial off-the-shelf (COTS) components, these microprocessors are readily available, of high packaging density, cheap, capable of supporting extensive software, and consume relatively low power [1]. With the increased use of software in space and the drive toward smaller, faster, better, and more cost-effective satellites, COTS systems are attractive for use in computer-based satellite systems. However, since COTS microprocessors are not radiation-hardened, they are much more vulnerable to transient failures [2]. As a result, various tools and methodologies are being researched to tolerate the effects of radiation on COTS microprocessors in space applications.

The NASA Remote Exploration and Experimentation (REE) project attempts to improve the reliability of COTS microprocessors by supporting research devoted to bringing commercial supercomputing technology into space. The design of highly reliable computer systems requires a thorough understanding of errors in the underlying COTS components, of which a microprocessor is the principal part. There are many factors that make a microprocessor more susceptible to radiation induced upsets. However, there is currently little data for analyzing and

detecting transient errors in microprocessors. The research described in this paper is part of the REE project and employs a new method for detecting errors in a microprocessor due to radiation. A high-level software tool has been created to detect and characterize radiation-induced errors in space borne applications running on COTS components.

#### 1.2 Software Tool Description

The software tool developed for this research runs on a microprocessor to measure the error rate and estimate the location of any errors encountered. It is broken down into separate routines for each testable hardware unit in a microprocessor and it keeps count of the number of errors found in each unit. In this research, a testable hardware unit can be defined as a collection of circuitry where most transient errors occurring in that circuitry can be detected and attributed to that circuitry in a high-level language. Typically, a microprocessor is made up of many hardware units, several of which are testable. Chapter 5 describes in further detail the general hardware units of a microprocessor and which ones are considered to be testable from a high-level language.

Each routine in the program uses a sequence of computations that are performed millions of times in a loop as a way of testing the specific hardware. The operations in each routine are chosen in such a way as to maximize the switching activity in the corresponding circuitry. Also, the error latency in a given unit is minimized by flooding it with millions of operations per second. This increases the error coverage by utilizing as much of the circuitry as possible as fast as possible.

There are many advantages of this self-monitoring software tool for error measurements. It has excellent potential for accurate localization of a single-event upset (SEU) to within a small functional block. Errors found by this tool will have a latency of only a few instruction cycles in most cases. Also, the probability of capturing an SEU is very high with the use of enhanced signal activities and the creation of sensitized paths. The tool is portable to different systems and can be used during long space missions to periodically measure the error rates. The error rates can vary during a long mission due to a changing environment and possibly due to aging of the electronics on the chip. Such a tool can give an early warning to the system of increased error rates.

Some assumptions are made for the tool to work successfully. The type and frequency of the errors are assumed to be such that the error rate is not so high as to crash the monitoring tool very frequently. The only data in that case would be the system crash rate, not an error rate. The errors that do not cause an immediate crash are the most worrisome. They are also far more likely than catastrophic errors, and if they are not detected early, they can multiply and lead to a system crash or to additional new errors. For these reasons, the most interesting case for measurement is for infrequent SEUs.

I

#### 2 RELATED WORK

Determining the suitability of COTS microprocessors for space applications is a subject of ongoing research. Normally, this involves predicting the expected single-event upset (SEU) rate in the microprocessor when it is flown in space. This is generally done using ground-based radiation tests where the device to be tested is exposed to an appropriate particle beam, and subsequently checked to determine if there have been any state changes. The results from these tests are used to predict the underlying SEU rate of the device. Over the last several years, many ideas related to testing the effects of SEUs on microprocessors have been presented:

- In [2], software tools are presented for predicting the rate and nature of observable SEUinduced errors in microprocessor systems. These tools are built around a commercial microprocessor simulator and are used to analyze real satellite application systems.

- In [3], the impact of physical fault injection of transient faults on processor execution is assessed. The fault injection is based on two complementary methods using (1) heavyion radiation, and (2) power supply disturbances. Approximately 12,000 transient faults were injected into the target microprocessor, a Motorola MC6809E 8-bit CPU, running three different workloads. Three error-detection mechanisms (two software-based mechanisms and one watchdog timer) were combined and used to detect as many errors as possible.

- Also, in [4], two generations of the 80Cx86 microprocessor family and two floatingpoint digital signal processors (DSP) were tested for single-event effects (SEE). The SEE rates for each of the device types were measured and the upset vulnerability was correlated to the size of the program running on each processor.

- In [5], the SEU rates of the Pentium MMX and Pentium II microprocessors using proton irradiation are determined. An evaluation of the performance of these microprocessors in the space radiation environment is also presented. Test software was used to determine the SEU behavior of the ALU, FPU, registers, and cache memory functional blocks of the microprocessors. A comparison is given of each processor's susceptibility to proton irradiation in various modes of operation.

- Similarly, in [6], SEE test results are given for the Intel 80386 family and the 80486 microprocessor. Both single-event upset and latchup conditions were monitored.

- Another study by Asenek [7] predicts the rate of observable SEU-induced errors in a

microprocessor system by measuring the errors in terms of the SEU application crosssection as opposed to the SEU cross-section as a function of the device's technology

only. A software tool is used to do the predictions as the microprocessor executes real

application software. Results obtained from simulating the nature of SEU-induced

errors are shown to correlate with ground-based radiation test data.

Although this work offers useful information on the susceptibility of a particular microprocessor to transient errors, the data is still somewhat limited. They all present data for specific microprocessors and do not attempt to localize the errors. Also, none of the tools is portable to other systems. It is more desirable to produce results that can be applied to any system and to run the tools on any microprocessor, which is what this research attempts to do.

Another area of related work is that done by the NASA Remote Exploration and Experimentation (REE) project itself. The REE Project is working to incorporate a custom, but architecturally insensitive, software implemented fault tolerance (SIFT) middleware layer, as well as a generic library of algorithm-based fault tolerance (ABFT) techniques, to enable the direct use of latest generation commercial hardware and software components in future space systems. This strategy will allow high throughput computation even in the presence of relatively high rates of radiation-induced transient upsets as well as in the presence of permanent faults. Previous work in this area includes:

- A first-generation testbed presented in [8] is created to test the above concepts. The testbed is equipped with fault injection capabilities and is constructed out of COTS hardware and software. The methodology used to develop a detailed radiation fault model for the REE testbed architecture is discussed. Also, result checking is suggested as a way of enforcing hardware/software reliability. Result checking relies on developing tests that can confirm the validity of operation output. Their work focuses on computation errors inherent in the system, rather than on environmentally induced faults.

- Huang and Abraham [9] introduce ABFT—a technique that encodes matrices using checksum matrices. These are then used to detect and correct faults in matrix

operations. They address matrix operations performed using processor arrays with regard to detecting errors generated by a faulty processor within the array.

• Jou and Abraham [10] present an ABFT error detection scheme for FFT networks. The method employs an encoding and decoding scheme to detect single errors.

Other work at the microprocessor level have primarily focused on vulnerability assessment and software detection methods:

- In [11] a detailed analysis of the vulnerability of the Z80 microprocessor, based on ionbombardment testing, is presented.

- In [12], a simulation tool called DYNAMO is used to study the effects of transient faults in large digital circuits.

- In [13], a series of experiments aimed at error analysis through the physical insertion of faults have been conducted at the NASA AIRLAB test-bed facility. An experimental analysis is presented to study the susceptibility of a microprocessor-based jet engine controller to upsets caused by current and voltage transients.

- In [14], a hierarchical error detection framework for a software implemented fault tolerance (SIFT) layer is proposed for a distributed system. A four-level error detection hierarchy is proposed in the context of Chameleon, a software environment for providing adaptive fault-tolerance in an environment of COTS system components and software. The design and implementation of a software-based distributed signature-monitoring scheme is described.

- In [15], the design and evaluation of a preemptive control signature technique (PECOS) for on-line detection of control flow errors is presented. The technique uses assertions that can be embedded in the assembly language code and that are triggered by control flow instructions in the code. PECOS can detect errors in control flow that spans multiple subroutines or source files as well as control-flow, which is determined at runtime. Software-based error injection techniques are used to evaluate PECOS.

- In [16], PECOS is used in combination with a data audit subsystem to eliminate failsilence violations, reduce the incidence of crashes, and eliminate hangs. Softwareimplemented error injection is performed to evaluate the system.

All of the above studies are based on low-level hardware-specific techniques. The research described in this paper differs in that the tool used to detect and locate transient errors is portable

across multiple platforms and can be used in a multitude of setups. The goal in using COTS microprocessors is to reduce cost and increase performance. Our tool supports that by providing error analysis while not limiting the type of microprocessors or systems to be used.

Į

#### **3 TRANSIENT ERROR OVERVIEW**

A transient error is an error that can appear and disappear within a very short period of time. They are temporary or nonpermanent and may arise in a working circuit during its operation due to a variety of noise sources [12]. For example, internal noise sources such as power transients and capacitive and inductive crosstalk are common causes, as well as external noise sources such as cosmic particle hits (e.g., alpha particles) [6]. Cosmic particles are the common cause of transient errors in space applications; therefore, it is the alpha particle hits that are of most interest in this work. However, the other sources of transient errors can be used for test purposes.

#### 3.1 Single-Event Upsets

A single-event upset (SEU) is a type of transient error that is commonly caused by alpha particle radiation. A SEU is a soft error introduced when an ionizing heavy ion penetrates the depletion region of a reversed-biased pn-junction. The heavy ion affects only stored information by changing bit values from 0 to 1 or vice versa. The majority of heavy ions affect only single bits. No hardware is damaged by the ions. The SEUs are assumed to occur randomly both in time and in position within a circuit. Typically the transient introduced by an alpha particle lasts only for a very short period of time, on the order of a fraction of a nanosecond [3].

Transient faults and SEUs are produced in today's microprocessors in several ways. Such things as lower supply voltages and lower transistor threshold values make a microprocessor more susceptible to transient errors. Also, lower noise margins, current leakage, and charge injections in dynamic circuits contribute to the susceptibility of microprocessors to SEUs. The higher density of interconnects and the high slew rate of logic signals together make crosstalk due to capacitive coupling a serious problem. Some circuit defects such as resistive shorts and opens are missed by the manufacturing tests.

#### 3.2 Analysis of Transient Faults

It has been reported that transient faults account for 80% or more of the failures in digital systems [12]. The effect of these transient faults is to change the behavior of the digital circuit in

some unexpected manner, often producing incorrect results. If the digital system is a critical application, such as a biomedical, space, military, or avionic application, the results could be catastrophic. If the critical areas in the circuit that are more susceptible to transient-fault disturbances are identified, appropriate actions may be taken to prevent those catastrophes.

To analyze the nature of SEU-induced errors in microprocessor systems, it is useful to predict the rate of observable SEU-induced errors in microprocessor systems and to identify and classify the errors into different categories. It is also useful to understand whether the occurrence of an SEU will cause a system to fail catastrophically or to simply lose service for short duration. This is essential in justifying its suitability for a particular application or mission.

SEUs affecting data are associated with upsets in the execution units such as the ALU, FPU, or data cache. SEUs affecting control result in program flow errors (sequencing errors), upsets in the instruction fetch unit or the branch prediction unit. These are more severe than data errors since SEUs affecting control would be expected to cause an exception. However, SEUs affecting data are particularly troublesome because they typically have fewer obvious consequences than an SEU affecting control. It should be noted that since memory will be error detecting and correcting, faults to memory would be largely screened; most data faults will therefore affect the microprocessor or its cache.

In [7], results were obtained from simulating the nature of SEU-induced errors in a microprocessor as well as results from radiation tests causing SEUs. The experiments in this paper used an 8052 microprocessor system executing the COTS2 operating system program [7]. For the radiation tests, of the 131 observed errors, approximately 31% were due to transient errors, 64% were resets, 5% were propagated errors. This data is useful because it gives us a feel for the type and frequency of errors we should expect in a microprocessor exposed to radiation.

#### 3.3 Fault Models

Fault models are typically used to help us characterize the behavior of errors. We make the assumption that faults behave according to some fault model. This allows us to specifically define the types of faults that will be considered and the behavior these faults will have [14]. Also, we can represent the behavior of physical occurrences. Several defects are usually mapped to one fault model. Fault models are not 100% accurate, but they make problems tractable and represent the types of faults that can occur. The general fault model used for transient faults in

this research includes incorrect signal values caused by coupled disturbance. These disturbances include those due to particle irradiation. The fault models and types of errors expected for specific microprocessor units are presented in Chapter 5.

Since the software tool designed in this project is intended for use in space applications where radiation exposure is imminent, a radiation fault model proves to be helpful. In a nonradiation hardened system, faults due to radiation are not prevented, but rather allowed to occur. The error (the logical manifestation of the fault as seen by the system or software) or a subsequent manifestation due to propagation of the error is then detected and handled by the software [8]. Clearly, the design of such a system is dependent on a detailed understanding of the types of faults that will occur, the errors generated by these faults, and the rate at which they will appear.

It is useful to predict what types of errors will be generated, under what conditions the system will become bogged down in error handling, and under what conditions errors will propagate through the system error detection and containment boundaries. It is for this reason we have developed the software tool described in this paper. Its ultimate purpose is to output a real-time error rate so that decisions can be made on the vulnerability of the system as well as individual components of the processor.

The principle faults for the REE environments are single bit flips; however, there is an expectation that multiple bit flips will become more prevalent due to shrinking feature sizes [8]. In this fault mode, several physically adjacent cells may be disrupted by the passage of a single energetic particle. However, these single-event multiple upsets are still relatively rare and for this research, they are not considered.

From a high-level point of view, faults due to radiation can be grouped into two types:

- Latch faults include latches, flip-flops, memory cells, and any other structure that persistently stores a bit. 'Visible' latches are included, such as data registers, as are 'invisible' latches, which are used to implement structures such as instruction pipeline stages and processor register reservation scoreboards [8].

- *Gate faults* occur when a SEU happens at approximately the same time as a clock transition, thus causing the gate to flip its effective bit value [8].

Due to the tight timing required for a gate fault to propagate to, and be latched by, a register, faults in latches are tens of thousands of times more likely than faults at the gate level, or

combinatorial logic. As the clock rate increases, this difference will shrink due to the increased fraction of time available for combinatorial logic to present erroneous values to registers, which may then latch these transients [8].

The goal of this section is to provide a basic idea of what types of faults are expected from radiation and how these faults relate to errors that may be produced. More information on these types of faults and the fault model structure can be found in [8]. The types of errors expected in specific functional blocks of a microprocessor from this fault model can be found in Chapter 5. Also, the functional modules of each unit are examined to determine the effects of errors on their behavior.

#### **4 SOFTWARE ERROR DETECTION TECHNIQUES**

Many software fault detection techniques have been implemented in the past. However, all of these techniques attempt to change the original application code in some way, or they are coded completely in machine language, which makes them very difficult to port to other systems. Also, they are often nondeterministic in that it is unknown what instruction sequences will be executed and what the results of various operations in the application will be at any given time. The tool described in this thesis is a stand-alone program that was written from scratch in a high-level language, therefore making it deterministic as well as portable. It is known in advance what instructions will be executed and what the results of those instructions should be. This allows the use of some common software error detection techniques such as time redundancy and consistency checks to detect the transient errors occurring in a COTS microprocessor.

#### 4.1 Time Redundancy

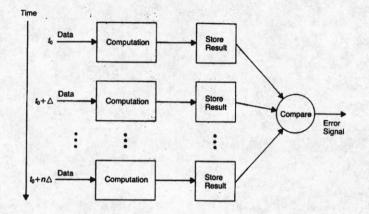

Time redundancy is a method that uses the repetition of computations in ways that allow errors to be detected. Figure 1 illustrates this idea with a block diagram. The fundamental concept is to perform the same computation two or more times and compare the results to determine if a discrepancy exists. If an error is detected, the computations can be performed again to see if the disagreement remains or disappears [17]. If the discrepancy remains, then there is a permanent error present; however, if the discrepancy disappears, then a transient error has occurred.

#### 4.2 Consistency Checks

Consistency checks are used as another means of capturing transient errors in software. They use a priori knowledge about the characteristics of information to verify the correctness of that information. For example, when adding two known numbers, such as 2 and 3, we know that the result should be 5. If the result is not 5 at the moment it is checked, then some sort of error is present. Combining this idea with the time redundancy method above, the addition can be performed several times, and if the result is consistently something other than 5, there is most

likely a permanent error present. However, if the result is 5 most of the time and something other than 5 the rest of the time, then there is likely a transient error occurring.

Figure 1: Time Redundancy Example.

The software program described in this paper uses consistency checks as the primary methods of detecting errors. A loop consisting of a group of operations that are checked for correctness upon completion is executed millions of times. Figure 2 illustrates the basic flowchart used for each routine when testing the functional units of the microprocessor.

.

#### **5 PROCESSOR MODEL**

To aid in localizing any errors encountered, the microprocessor is represented in terms of its functional hardware units. A fault model is then developed for each of these functional units. In this way, computations can be generated to test each unit without the detailed knowledge of how the instruction sequencing and control section for each unit are implemented. Also, some units can be broken down into smaller units if it is possible to localize errors to smaller areas in the circuitry. For example, the integer unit can be broken down into an add unit, a subtract unit, a multiply unit, etc., because they all use different hardware that can be tested explicitly from a high-level program. However, some units, such as the branch processing unit, cannot be broken down further because it is impossible to write a high-level computation that will exclusively test its subunits such as the branch prediction hardware.

Also, for portability purposes, some basic assumptions are made about the processor when developing the software tool. First, it is assumed that the registers are of size 32 bits. Second, it is assumed that certain execution and control units exist in all COTS processors. It is understood that there are other units unique to specific processors, for example a vector unit; however, these are not targeted directly in this version of the software tool. Third, because there are many ways to implement each functional unit, we will concentrate on obtaining high switching on the inputs and outputs and assume that this will maximize the activity in any given design.

The execution units assumed to be common to all COTS processors as well as their subunit circuitry that can be tested are as follows:

- Integer units 1 and 2

- Addition

- Subtraction

- Multiplication

- Division

- Logical AND

- Logical OR

- Logical XOR

- Register unit

- Floating point unit

- Addition

- Subtraction

- Multiplication

- Division

- Data cache unit

- Load/store unit

The control units assumed to be common to all COTS processors are:

- Instruction fetch unit

- Branch processing unit

The instruction fetch unit encompasses components such as the instruction cache, the instruction register, the dispatch unit, and any other hardware involved in fetching instructions. The branch processing unit includes hardware such as the branch target instruction cache, the branch history table, control registers, and any other circuitry involved in branch prediction.

There are other units not mentioned above that are extremely difficult to test from a highlevel program and are therefore left out when generating the test routines. For example, detecting errors occurring in the memory management unit (MMU), the reservation stations, the completion unit, and the bus interface unit cannot be thoroughly and exclusively accomplished in a high-level program. Also, differentiating between errors in the L1 and L2 cache is difficult. But, even though errors in these units are not tested for explicitly, many other operations that are performed will utilize these units, and if errors occur, it is possible that they will be detected indirectly.

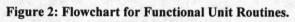

The preliminary version of the tool developed in this research was written for a Motorola PowerPC processor – the MPC750. A block diagram of this processor is shown in Figure 3. The MPC750 processor contains all of the units described previously and provides a basis for the software tool. The results presented in Chapter 12 are gathered from testing the tool on the MPC750.

Figure 3: MPC750 Processor Block Diagram.

The following chapters present more detail on how the testing was done for each unit. However, it should be pointed out that the work for this research was split between two students and, as a result, only certain units are discussed in this thesis. For a detailed description on how the data cache and the floating point unit were tested, please refer to the thesis to be written by Hari Kommaraju [18].

### **6 TESTING THE INTEGER UNITS**

It is assumed that any COTS processor used in the space applications will have at least two integer units. Typically, these integer units have slightly different purposes. In the MPC750 processor shown in Figure 3, integer unit 1 is used for all integer computations, whereas integer unit 2 is used only for addition. There may be other integer units in other processors, but we will assume that it is sufficient to test for two.

I

In general, integer unit 1 is assumed to encompass the following operations:

- Addition

- Subtraction

- Multiplication

- Division

- Logical AND

- Logical OR

- Logical XOR

Each of the above operations uses different logic within the integer unit and each requires a different operational code (opcode) value in the corresponding instruction. Any errors found while performing the above operations can be attributed to the particular logic for that operation.

Integer unit 2 is assumed to provide only addition. The specific details of how the processor decides which integer unit an addition instruction will be allocated to are unknown. As a result, integer unit 2 must be tested in conjunction with integer unit 1. To guarantee that integer unit 2 is utilized, integer unit 1 must be busy. This is accomplished by issuing integer multiplies in between integer additions. Since integer unit 2 can only do additions, the multiplications are sent to integer unit 1 and the subsequent additions will be sent to integer unit 2.

Any error in the integer units can be covered with the appropriate fault model. Each integer operation can be broken down into several identical logic gates that can be referred to as cells. Each cell represents the computation for one "slice" of the data. For example, the adder cell performs the addition of 3 bits and the logical AND cell performs the AND of 2 bits. The general fault assumption at the cell level is that a faulty cell can change its behavior in any arbitrary way,

as long as it remains a combinational circuit [19]. Also, an appropriate cell fault model can cover any fault in the intercell array.