UILU-ENG-86-2232 CSG-56

# COORDINATED SCIENCE LABORATORY College of Engineering

# PARALLEL TESTING FOR PATTERN SENSITIVE FAULTS IN SEMICONDUCTOR RANDOM ACCESS MEMORY

Pinaki Mazumder Janak H. Patel

UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

Approved for Public Release. Distribution Unlimited.

\_

.

-

Unclassified . SECURITY CLASSIFICATION OF THIS PAGE

| REPORT DOCUM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                    |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REPORT SECURITY CLASSIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16. RESTRICTIVE MARKINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SECURITY CLASSIFICATION AUTHORITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3. DISTRIBUTION/AVAILABILITY OF REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Approved for public re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10000                                                                                                                                                                                                                                                                                                                                              |  |  |

| DECLASSIFICATION/DOWNGRADING SCHEDULE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>Approved for public release;</li> <li>distribution unlimited</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| ERFORMING ORGANIZATION REPORT NUMBER(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5. MONITORING ORGANIZATION REP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ORT NUMBER(S)                                                                                                                                                                                                                                                                                                                                      |  |  |

| UILU-ENG-86-2232 (CSG-56)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NA                                                                                                                                                                                                                                                                                                                                                 |  |  |

| NAME OF PERFORMING ORGANIZATION 66. OFFICE SYMBOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 78. NAME OF MONITORING ORGANIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ATION                                                                                                                                                                                                                                                                                                                                              |  |  |

| ordinated Science Laboratory (If applicable)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Contractor Bernard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Generales                                                                                                                                                                                                                                                                                                                                          |  |  |

| iversity of Illinois, Urbana                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Semiconductor Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Semiconductor Research Corporation                                                                                                                                                                                                                                                                                                                 |  |  |

| ADDRESS (City, State and ZIP Code)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7b. ADDRESS (City, State and ZIP Code)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nin alle sin periodi anti anti anti anti anti anti anti ant                                                                                                                                                                                                                                                                                        |  |  |

| 01 W. Springfield                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| bana, IL 61801                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P. O. Box 12053                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| , and, 12 01001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Research Triangle Park                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | , NC 27709                                                                                                                                                                                                                                                                                                                                         |  |  |

| NAME OF FUNDING/SPONSORING 86. OFFICE SYMBOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9. PROCUREMENT INSTRUMENT IDER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TIFICATION NUMBER                                                                                                                                                                                                                                                                                                                                  |  |  |

| ORGANIZATION (If applicable)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SRC RSCH 84-06-049-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| ee 7a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SAC ASCH 04-00-049-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| ADDRESS (City, State and ZIP Code)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10. SOURCE OF FUNDING NOS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PROGRAM PROJECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TASK WORK UNIT                                                                                                                                                                                                                                                                                                                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ELEMENT NO. NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | NO. NO.                                                                                                                                                                                                                                                                                                                                            |  |  |

| ee 7b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| TITLE (Include Security Classification. Parallel Testing for Patter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | n N/A N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | N/A N/A                                                                                                                                                                                                                                                                                                                                            |  |  |

| nsitive Faults in Semiconductor Random Access Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| PERSONAL AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Pinaki Mazumder, Janak H. Patel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| TYPE OF REPORT 13b. TIME COVERED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14. DATE OF REPORT (Yr., Mo., Day)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15. PAGE COUNT                                                                                                                                                                                                                                                                                                                                     |  |  |

| Technical FROM TO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - June, 1986                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26                                                                                                                                                                                                                                                                                                                                                 |  |  |

| SUPPLEMENTARY NOTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    |  |  |

| COSATI CODES 18. SUBJECT TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (Continue on reverse if necessary and identify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | by block number)                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ve Neighborhood Pattern Sensitive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Tranta                                                                                                                                                                                                                                                                                                                                             |  |  |

| Active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Fault,                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Neighborhood Pattern Sensitive Fa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Fault,                                                                                                                                                                                                                                                                                                                                             |  |  |

| Bit Lin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | es, Word Lines, Sense Amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fault,                                                                                                                                                                                                                                                                                                                                             |  |  |

| Bit Lin<br>ABSTRACT (Continue on reverse if necessary and identify by block num                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | es, Word Lines, Sense Amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fault,<br>ult,                                                                                                                                                                                                                                                                                                                                     |  |  |

| Bit Lin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | es, Word Lines, Sense Amplifiers<br>ber,<br>m for pattern sensitive faults deter<br>t RAM organized in $k \ge 1$ subarra<br>of number of bit lines to number<br>hoods pattern sensitive faults in F<br>oposed technique can be implement<br>dditional hardware is minimal. If<br>bk + 13k transistors ( which is at<br>overhead known to date in any R<br>bility and the additional circuit<br>ransistor d-RAM. Eventhough the<br>todified architecture can be readily<br>).<br>21. ABSTRACT SECURITY CLASSIFICA<br>Unclassified<br>22b. TELEPHONE NUMBER [2] | Fault,<br>nult,<br>ection in large size RAM<br>ays in $97.5\sqrt{\frac{n}{ke}}$ time<br>of word lines. The test<br>RAM. The existing RAM<br>ted very easily. The test<br>b is the number of bit<br>yout $3\sqrt{n}$ transistors if<br>AM circuit with parallel<br>for each bit line can fit<br>proposed test algorithm<br>y used to speed up other |  |  |

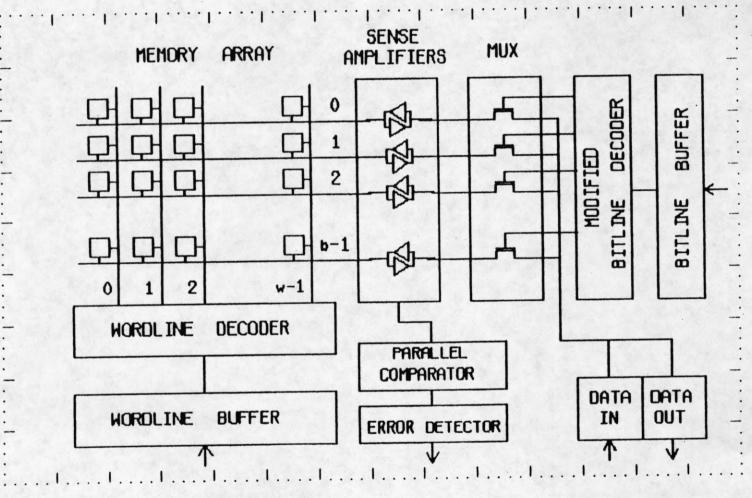

| Bit Lin.<br>ABSTRACT (Continue on reverse if necessary and identify by block number<br>This technical report proposes a new test algorithm<br>with high circuit density. The algorithm tests an $n$ -bit<br>where $e$ is the eccentricity and is defined as the ratio of<br>algorithms detect both the active and passive neighborh<br>architecture has been modified very little so that the pro-<br>algorithms are not generated within the chip and the a-<br>lines in a subarray, then the additional overhead is $3k$<br>k = e = 1) including the error latches. This is the lowest<br>testing capability. The low overhead allows high relias<br>within the $3\lambda$ to $6\lambda$ pitch width in high density single to<br>is designed to detect the pattern sensitive faults, the m-<br>conventional algorithms of complexity $O(n^k)$ to $O(n^{k/2})$<br>DISTRIBUTION/AVAILABILITY OF ABSTRACT<br>CLASSIFIED/UNLIMITED $\Xi$ SAME AS RPT. $\Box$ DTIC USERS $\Box$ | es, Word Lines, Sense Amplifiers<br>ber,<br>m for pattern sensitive faults detern<br>t RAM organized in $k \ge 1$ subarration<br>for number of bit lines to number<br>hoods pattern sensitive faults in F<br>oposed technique can be implement<br>dditional hardware is minimal. If<br>bk + 13k transistors (which is all<br>overhead known to date in any Rubility and the additional circuit<br>ransistor d-RAM. Eventhough the<br>odified architecture can be readily<br>).<br>21. ABSTRACT SECURITY CLASSIFICA<br>Unclassified                            | Fault,<br>nult,<br>ection in large size RAM<br>ays in $97.5\sqrt{\frac{n}{ke}}$ time<br>of word lines. The test<br>RAM. The existing RAM<br>ted very easily. The test<br>b is the number of bit<br>bout $3\sqrt{n}$ transistors if<br>AM circuit with parallel<br>for each bit line can fit<br>proposed test algorithm<br>v used to speed up other |  |  |

| Bit Lin.<br>ABSTRACT (Continue on reverse if necessary and identify by block number<br>This technical report proposes a new test algorithm<br>with high circuit density. The algorithm tests an $n$ -bit<br>where $e$ is the eccentricity and is defined as the ratio of<br>algorithms detect both the active and passive neighborh<br>architecture has been modified very little so that the pro-<br>algorithms are not generated within the chip and the a-<br>lines in a subarray, then the additional overhead is $3k$<br>k = e = 1) including the error latches. This is the lowest<br>testing capability. The low overhead allows high relias<br>within the $3\lambda$ to $6\lambda$ pitch width in high density single to<br>is designed to detect the pattern sensitive faults, the m-<br>conventional algorithms of complexity $O(n^k)$ to $O(n^{k/2})$<br>DISTRIBUTION/AVAILABILITY OF ABSTRACT<br>CLASSIFIED/UNLIMITED $\Xi$ SAME AS RPT. $\Box$ DTIC USERS $\Box$ | es, Word Lines, Sense Amplifiers<br>ber,<br>m for pattern sensitive faults deter<br>t RAM organized in $k \ge 1$ subarra<br>of number of bit lines to number<br>hoods pattern sensitive faults in F<br>oposed technique can be implement<br>dditional hardware is minimal. If<br>bk + 13k transistors ( which is at<br>overhead known to date in any R<br>bility and the additional circuit<br>ransistor d-RAM. Eventhough the<br>todified architecture can be readily<br>).<br>21. ABSTRACT SECURITY CLASSIFICA<br>Unclassified<br>22b. TELEPHONE NUMBER [2] | Fault,<br>nult,<br>ection in large size RAM<br>ays in $97.5\sqrt{\frac{n}{ke}}$ time<br>of word lines. The test<br>RAM. The existing RAM<br>ted very easily. The test<br>b is the number of bit<br>bout $3\sqrt{n}$ transistors if<br>AM circuit with parallel<br>for each bit line can fit<br>proposed test algorithm<br>v used to speed up other |  |  |

SECURITY CLASSIFICATION OF THIS PAGE

----

.

ł

## Parallel Testing for Pattern Sensitive Faults in Semiconductor Random Access Memory

Pinaki Mazumder & Janak Patel Coordinated Science Laboratory University of Illinois Urbana, IL 61801. June, 1986

#### ABSTRACT

This technical report proposes a new test algorithm for pattern sensitive faults detection in large size RAM with high circuit density. The algorithm tests an *n*-bit RAM organized in  $k \ge 1$  subarrays in  $97.5\sqrt{\frac{n}{ke}}$  time where *e* is the eccentricity and is defined as the ratio of number of bit lines to number of word lines. The test algorithms detect both the active and passive neighborhoods pattern sensitive faults in RAM. The existing RAM architecture has been modified very little so that the proposed technique can be implemented very easily. The test algorithms are not generated within the chip and the additional hardware is minimal. If *b* is the number of bit lines in a subarray, then the additional overhead is 3bk + 13k transistors ( which is about  $3\sqrt{n}$  transistors if k = e = 1) including the error latches. This is the lowest overhead known to date in any RAM circuit with parallel testing capability. The low overhead allows high reliability and the additional circuit for each bit line can fit within the  $3\lambda$  to  $6\lambda$  pitch width in high density single transistor d-RAM. Eventhough the proposed test algorithm is designed to detect the pattern sensitive faults, the modified architecture can be readily used to speed up other conventional algorithms of complexity  $O(n^k)$  to  $O(n^{k/2})$ .

Keywords: RAM, Passive Neighborhood Pattern Sensitive Fault, Active Neighborhood Pattern Sensitive Fault, Bit Lines, Word Lines, Sense Amplifiers

#### 1. INTRODUCTION

Over the past one decade, random access memory (RAM) size is being quadrupled in about every two to four years. This has been made possible by scaling down the feature width by a factor of 6, increasing the overall chip dimension by six fold and finally reducing the individual cell area by a ratio of 90:1 (as shown in Table 1). Lewyn and Meindl [1] have enumerated the physical limits of VLSI dynamic RAMs and have shown that 64M bit dRAM (having an access time of 50 nsec) can be realized using  $0.35\mu$  technology and the conventional VLSI packaging. A further extension to 256M bit dRAM can be achieved by increasing the die size to  $1.2 \text{ cm}^2$  and cooling the chip by liquid nitrogen. This enormous prospect of RAM design has posed a number of challenges to the RAM test engineers. Conventional test algorithms like marching test and GALPAT [2] can not economically test these large size RAM chips. GALPAT having a test complexity of  $4n^2+4n$  for an n bit RAM will need about 800 days to test a 4M bit RAM chip with 100 nsec access time. Moreover, these tests have been designed to detect only stuck-at faults and restricted

| Memory<br>Size<br>(bits) | Feature<br>Width<br>(µ) | Storage<br>Area<br>( cm <sup>2</sup> ) | Cell<br>Area<br>( $\mu^2$ ) | Pitch<br>Width<br>(µ) | Year |

|--------------------------|-------------------------|----------------------------------------|-----------------------------|-----------------------|------|

| 4K                       | 7                       | 0.07                                   | 1764                        | 6                     | 1973 |

| 16K                      | 5                       | 0.1                                    | 800                         | 6                     | 1976 |

| 64K                      | 3                       | 0.15                                   | 216                         | 5                     | 1978 |

| 256K                     | 2                       | 0.3                                    | 96                          | 5                     | 1982 |

| 1M                       | 1.3                     | 0.2                                    | 20                          | 4                     | 1984 |

| 16M                      | 0.5                     | 0.3                                    | 1.5                         | 3                     | ?    |

| 64M                      | 0.35                    | 0.6                                    | 0.7                         | 3                     | ?    |

Table 1: Cell and Array Geometric Parameters in RAM

## **1 INTRODUCTION**