UILU-ENG-91-2211 CRHC-91-7

Center for Reliable and High-Performance Computing

# A FEATURE TAXONOMY AND SURVEY OF SYNCHRONIZATION PRIMITIVE IMPLEMENTATIONS

Andy Glew Wen-mei Hwu

Coordinated Science Laboratory College of Engineering UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

Approved for Public Release. Distribution Unlimited.

SECURITY CLASSIFICATION OF THIS PAGE

I

.

| REPORT DOCU | MENTATION | PAG |

|-------------|-----------|-----|

|-------------|-----------|-----|

|                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           |                   | REPORT DOCU                                                                                                                                                                                                                                                                                         | MENTATION                                                                                                                                                                                                                                              | PAGE                                                                                                                                                                                        |                                                                                                                                                                     |                                                              |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| . REPOR                                                                                                                                                                                                                                                      | T SECURITY CLASSI                                                                                                                                                                                                                         | FICATION          |                                                                                                                                                                                                                                                                                                     | 16. RESTRICTIVE                                                                                                                                                                                                                                        | MARKINGS                                                                                                                                                                                    |                                                                                                                                                                     |                                                              |  |  |  |

| Unclassified<br>2a. SECURITY CLASSIFICATION AUTHORITY                                                                                                                                                                                                        |                                                                                                                                                                                                                                           |                   | None                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                        |                                                                                                                                                                                             |                                                                                                                                                                     |                                                              |  |  |  |

|                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           |                   | 3. DISTRIBUTION / AVAILABILITY OF REPORT                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                        |                                                                                                                                                                                             |                                                                                                                                                                     |                                                              |  |  |  |

|                                                                                                                                                                                                                                                              | none                                                                                                                                                                                                                                      |                   |                                                                                                                                                                                                                                                                                                     | Approved                                                                                                                                                                                                                                               | for public                                                                                                                                                                                  | release;                                                                                                                                                            |                                                              |  |  |  |

| 2b. DECLASSIFICATION / DOWNGRADING SCHEDULE<br>none                                                                                                                                                                                                          |                                                                                                                                                                                                                                           |                   |                                                                                                                                                                                                                                                                                                     | distribut                                                                                                                                                                                                                                              | tion unlimi                                                                                                                                                                                 | ted                                                                                                                                                                 |                                                              |  |  |  |

| PERFOR                                                                                                                                                                                                                                                       | MING ORGANIZATI                                                                                                                                                                                                                           | ON REPORT NUME    | ER(S)                                                                                                                                                                                                                                                                                               | 5. MONITORING                                                                                                                                                                                                                                          | ORGANIZATION                                                                                                                                                                                | REPORT NUMBE                                                                                                                                                        | ER(S)                                                        |  |  |  |

| UI                                                                                                                                                                                                                                                           | LU-ENG-91-22                                                                                                                                                                                                                              | 11                | CRHC91-7                                                                                                                                                                                                                                                                                            | none                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |                                                                                                                                                                     |                                                              |  |  |  |

|                                                                                                                                                                                                                                                              | OF PERFORMING                                                                                                                                                                                                                             |                   | 6b. OFFICE SYMBOL                                                                                                                                                                                                                                                                                   | 7a. NAME OF M                                                                                                                                                                                                                                          | ONITORING ORG                                                                                                                                                                               | ANIZATION                                                                                                                                                           |                                                              |  |  |  |

|                                                                                                                                                                                                                                                              | dinated Scie                                                                                                                                                                                                                              |                   | (If applicable)                                                                                                                                                                                                                                                                                     | NCR Corpo                                                                                                                                                                                                                                              | ration                                                                                                                                                                                      |                                                                                                                                                                     |                                                              |  |  |  |

|                                                                                                                                                                                                                                                              | versity of Il                                                                                                                                                                                                                             |                   | N/A                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                        |                                                                                                                                                                                             |                                                                                                                                                                     |                                                              |  |  |  |

| ADDRE                                                                                                                                                                                                                                                        | ISS (City, State, and                                                                                                                                                                                                                     | d ZIP Code)       |                                                                                                                                                                                                                                                                                                     | 7b. ADDRESS (CH                                                                                                                                                                                                                                        | ty, State, and Zli                                                                                                                                                                          | P Code)                                                                                                                                                             |                                                              |  |  |  |

| 1101                                                                                                                                                                                                                                                         | W. Springfi                                                                                                                                                                                                                               | leld Avenue       |                                                                                                                                                                                                                                                                                                     | Personal                                                                                                                                                                                                                                               | Computer D:                                                                                                                                                                                 | ivision - C                                                                                                                                                         | lemson                                                       |  |  |  |

|                                                                                                                                                                                                                                                              | na, IL 6180                                                                                                                                                                                                                               |                   |                                                                                                                                                                                                                                                                                                     | 1150 Ande                                                                                                                                                                                                                                              | erson Dr.                                                                                                                                                                                   |                                                                                                                                                                     |                                                              |  |  |  |

|                                                                                                                                                                                                                                                              | OF FUNDING/SPO                                                                                                                                                                                                                            | NSORING           | 86. OFFICE SYMBOL                                                                                                                                                                                                                                                                                   | 9. PROCUREMEN                                                                                                                                                                                                                                          |                                                                                                                                                                                             | DENTIFICATION                                                                                                                                                       | NUMBER                                                       |  |  |  |

|                                                                                                                                                                                                                                                              | NIZATION<br>same as 7a                                                                                                                                                                                                                    |                   | (if applicable)                                                                                                                                                                                                                                                                                     | S. PROCOREIVIEN                                                                                                                                                                                                                                        |                                                                                                                                                                                             |                                                                                                                                                                     | NOMBER                                                       |  |  |  |

| ADORE                                                                                                                                                                                                                                                        | SS (City, State, and                                                                                                                                                                                                                      | ZIP Code)         |                                                                                                                                                                                                                                                                                                     | 10. SOURCE OF                                                                                                                                                                                                                                          |                                                                                                                                                                                             | ERS                                                                                                                                                                 |                                                              |  |  |  |

|                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           |                   |                                                                                                                                                                                                                                                                                                     | PROGRAM                                                                                                                                                                                                                                                | PROJECT                                                                                                                                                                                     | TASK                                                                                                                                                                | WORK UNIT                                                    |  |  |  |

|                                                                                                                                                                                                                                                              | same as 7b.                                                                                                                                                                                                                               |                   |                                                                                                                                                                                                                                                                                                     | ELEMENT NO.                                                                                                                                                                                                                                            | NO.                                                                                                                                                                                         | NO.                                                                                                                                                                 | ACCESSION NO                                                 |  |  |  |

|                                                                                                                                                                                                                                                              | Glew, Andy a<br>OF REPORT                                                                                                                                                                                                                 | 13b. TIME         | COVERED                                                                                                                                                                                                                                                                                             | 14. DATE OF REPO                                                                                                                                                                                                                                       | DRT (Year, Month                                                                                                                                                                            | h, Day) 15. PA                                                                                                                                                      |                                                              |  |  |  |

| 3a. TYPE<br>Tech<br>6. SUPPL                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                           | 13b. TIME<br>FROM |                                                                                                                                                                                                                                                                                                     | 14. DATE OF REPO<br>February                                                                                                                                                                                                                           |                                                                                                                                                                                             | <b>h, Day)</b> 15. PAG<br>51                                                                                                                                        | GE COUNT                                                     |  |  |  |

| 3a. TYPE<br>Tech<br>6. SUPPL                                                                                                                                                                                                                                 | OF REPORT<br>nical<br>EMENTARY NOTAT<br>none                                                                                                                                                                                              | 13b. TIME<br>FROM | COVERED TO                                                                                                                                                                                                                                                                                          | February                                                                                                                                                                                                                                               | 1991                                                                                                                                                                                        | 51                                                                                                                                                                  |                                                              |  |  |  |

| 3a. TYPE<br>Tech<br>6. SUPPL                                                                                                                                                                                                                                 | OF REPORT<br>mical<br>EMENTARY NOTAT<br>none<br>COSATI                                                                                                                                                                                    | 13b. TIME<br>FROM | TO TO                                                                                                                                                                                                                                                                                               | February                                                                                                                                                                                                                                               | 1991<br>The if necessary an                                                                                                                                                                 | 51<br>nd identify by b                                                                                                                                              | Nock number)                                                 |  |  |  |

| 3a. TYPE<br>Tech<br>6. SUPPL                                                                                                                                                                                                                                 | OF REPORT<br>mical<br>EMENTARY NOTAT<br>none<br>COSATI                                                                                                                                                                                    | 13b. TIME<br>FROM | COVERED TO                                                                                                                                                                                                                                                                                          | February<br>Continue on reven<br>or, synchron                                                                                                                                                                                                          | 1991<br>The if necessary an                                                                                                                                                                 | 51<br>nd identify by b                                                                                                                                              | Nock number)                                                 |  |  |  |

| 3a. TYPE<br><u>Tech</u><br>6. SUPPLI<br>7.<br>FIELD<br>9. ABSTR<br>Comp<br>these<br>Input,<br>This<br>synch<br>other<br>chron                                                                                                                                | COSATI<br>none<br>COSATI<br>GROUP<br>GROUP<br>CACT (Continue on<br>puter systems that<br>processors. This<br>t/Output (I/O) unit<br>report considers in<br>forms of synchro                                                               | 13b. TIME<br>FROM | TO TO<br>18. SUBJECT TERMS (<br>multiprocess)                                                                                                                                                                                                                                                       | February<br>(Continue on reversion, synchron)<br>or, synchron<br>cessing<br>number)<br>require mechanism<br>gle Central Process<br>tiple CPUs in mult<br>ation primitives. (<br>use hardware supp<br>relusion. Only the                                | 1991<br>is if necessary and<br>ization, com-<br>sing Unit (CPU<br>iprocessor system<br>Of the several do<br>ort for this is mode<br>to we level quest                                       | 51<br>nd identify by t<br>mputer arch<br>nization betwee<br>J) and intelligen<br>ms.<br>lifferent types of<br>ore common, an<br>tion of how syr                     | <b>Nock number</b> )<br>nitecture,<br>n<br>n<br>nt           |  |  |  |

| <ul> <li>3a. TYPE<br/><u>Tech</u></li> <li>5. SUPPLI</li> <li>7.<br/>FIELD</li> <li>7.<br/>FIELD</li> <li>9. ABSTR</li> <li>Comp<br/>these<br/>Input,</li> <li>This<br/>synch<br/>other<br/>chrom<br/>perfo</li> <li>20. DISTR</li> <li>20. DISTR</li> </ul> | COSATI<br>none<br>COSATI<br>O GROUP<br>COSATI<br>O GROUP<br>RACT (Continue on<br>puter systems that<br>processors. This<br>t/Output (I/O) unit<br>report considers the<br>inonization, mutual<br>forms of synchro-<br>nization is perform | 13b. TIME<br>FROM | TO<br>TO<br>18. SUBJECT TERMS (<br>multiprocess<br>parallel pro<br>by and identify by block<br>to intelligent processors<br>pronization between a singuronization between mult<br>on details of synchroniza-<br>ng) is emphasized, becau<br>built on top of mutual ex-<br>to the higher level quest | February<br>(Continue on reversor, synchron:<br>cessing<br>number)<br>require mechanism<br>gle Central Proces<br>tiple CPUs in mult<br>ation primitives. (<br>use hardware supp<br>cclusion. Only the<br>ions of when and<br>21. ABSTRACT S<br>Unclass | 1991<br>is if necessary and<br>ization, com-<br>ssing Unit (CPU<br>iprocessor system<br>Of the several do<br>ort for this is mode<br>bow level quest<br>where synchronic<br>ECURITY CLASSIF | 51<br>nd identify by b<br>mputer arch<br>nization betwee<br>J) and intelligen<br>ms.<br>lifferent types of<br>ore common, an<br>tion of how syr<br>ization should b | Mock number)<br>hitecture,<br>n<br>ht<br>of<br>d<br>h-<br>ee |  |  |  |

All other editions are obsolete.

UNCLASSIFIED

#### 19.

We are concerned with the systems of moderate price and performance that make up most of the computer marketplace. Shared memory systems with cache consistency protocols using a shared bus or a simple interconnect such as a crossbar switch are considered. Figure 1.1 illustrates such a generic multiprocessor system. Multistage interconnection networks are not considered except in passing, because such architectures are costly and will be used mainly by high-performance supercomputers and specialized processors in the next decade. Distributed memory and message passing systems are not considered because, although possibly in the modest price range, the mechanisms investigated in this research do not apply.

The rest of this report is structured as follows: Chapter 2 presents a taxonomy of synchronization features. It defines terms for future use. Chapter 3 surveys other work, particularly proposed cache and bus protocols for synchronization. Chapter 3 also surveys the implementation of synchronization primitives on a wide number of actual implementations, both academic and commercial, and conveys a sense of the present state of the art. Chapter 2 makes forward references to systems in Chapter 3 that demonstrate features of the taxonomy.

These chapters were originally introductory material to an MS thesis [29]. The survey was undertaken to see if the idea proposed by this thesis, the bus abandonment lock, was original. The taxonomy was developed to organize the information in the thesis. The full thesis contains an earlier version of the taxonomy and survey, a description of the bus abandonment lock, simulation experiments, and observations of the synchronization behavior of real systems.

We hope that the taxonomy of Chapter 2 will be useful to others, although it has been our experience that most taxonomies are seldom used by anyone except their author. We have, therefore, emphasized descriptions of features rather than a global classification of systems.

### A Feature Taxonomy and Survey of Synchronization Primitive Implementations

Andy Glew and Wen-Mei Hwu Center for Reliable and High-Performance Computing, Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, 1101 W. Springfield, Urbana, IL 61801 a-glew@@uiuc.edu

December 14, 1990

# Contents

I

| 1 | Intr | oductio  | on        |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 5  |

|---|------|----------|-----------|----------|--------|------|-----|---|---|------|--|------|-----|------|------|------|--|--|----|

| 2 | Tax  | onomy    |           |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 7  |

|   | 2.1  | Introdu  | iction    |          |        |      |     |   |   |      |  |      |     | <br> | <br> | <br> |  |  | 7  |

|   | 2.2  | Synchro  | onization | n Witho  | ut Ato | mic  | RM  | W | s |      |  |      |     | <br> | <br> |      |  |  | 7  |

|   | 2.3  | Instruct | tion Set  |          |        |      |     |   |   |      |  |      |     | <br> | <br> | <br> |  |  | 7  |

|   |      |          | Releasin  |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 8  |

|   |      |          | Acquirir  |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 8  |

|   |      |          | 2.3.2.1   | Simple   |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 9  |

|   |      |          | 2.3.2.2   | The w    |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 10 |

|   |      |          | 2.3.2.3   | Comp     |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 11 |

|   |      |          | 2.3.2.4   | Comp     |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 11 |

|   | 2.4  |          | y         |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 12 |

|   |      | 2.4.1    | Special   | versus r | ormal  |      |     |   |   |      |  |      |     |      |      |      |  |  | 12 |

|   |      |          | Distribu  |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 14 |

|   | 2.5  |          |           |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 14 |

|   |      |          | Protoco   |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 14 |

|   |      |          | Spinloo   |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 15 |

|   | 2.6  |          | nnects    |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 18 |

|   | 2.0  |          | Intercon  |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 18 |

|   |      |          | Bus trai  |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 18 |

|   |      |          | 2.6.2.1   |          | ck .   |      |     |   |   |      |  |      |     |      |      |      |  |  | 18 |

|   |      |          | 2.6.2.2   |          | ransac |      |     |   |   |      |  |      |     |      |      |      |  |  | 19 |

|   |      |          | 2.6.2.3   | Out-o    |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 21 |

|   | 2.7  |          | ng        | -        |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 22 |

|   | 2.1  | Duntern  | ng        |          |        | •••• | • • |   |   | • •  |  |      | • • |      |      |      |  |  |    |

| 3 | Sur  | vev      |           |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 23 |

|   | 3.1  |          | iction .  |          |        |      |     |   |   | <br> |  | <br> |     |      | <br> |      |  |  | 23 |

|   | 3.2  | Papers   |           |          |        |      |     |   |   | <br> |  | <br> |     |      | <br> |      |  |  | 24 |

|   | 3.3  |          | ıs        |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 25 |

|   |      |          | Alliant   |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 25 |

|   |      | 3.3.2    | BBN T     | C2000 .  |        |      |     |   |   | <br> |  | <br> |     |      | <br> |      |  |  | 25 |

|   |      | 3.3.3    | Cray X-   | MP       |        |      |     |   |   | <br> |  | <br> |     |      | <br> |      |  |  | 26 |

|   |      |          | Encore    |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 26 |

|   |      |          | Gould N   |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 27 |

|   |      |          | MIPS-b    |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 27 |

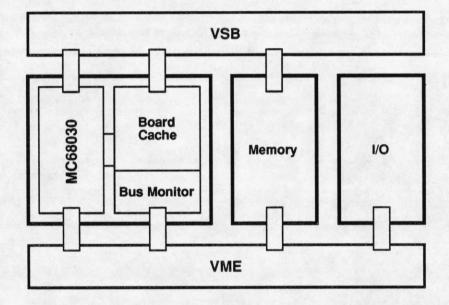

|   |      |          | MVME      |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 29 |

|   |      |          | Pyrami    |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 31 |

|   |      |          | Sequent   |          |        |      |     |   |   |      |  |      |     |      |      |      |  |  | 31 |

|     | 3.3.10 | SPUR                         | 31 |

|-----|--------|------------------------------|----|

|     | 3.3.11 | VAX                          | 32 |

| 3.4 | Microp | ocessors                     | 33 |

|     | 3.4.1  | Acorn RISC Machine           | 33 |

|     | 3.4.2  | AMD 29000                    | 33 |

|     | 3.4.3  | IBM RS/6000                  | 34 |

|     | 3.4.4  | Intel 80x86                  | 34 |

|     | 3.4.5  | Intel i860                   | 35 |

|     | 3.4.6  | MIPS                         | 35 |

|     | 3.4.7  | Motorola 680x0               | 35 |

|     | 3.4.8  | Motorola 88000               | 36 |

|     | 3.4.9  | National Semiconductor 32xxx | 36 |

|     | 3.4.10 | SPARC                        | 36 |

| 3.5 | Busses |                              | 36 |

|     | 3.5.1  | VME                          | 36 |

|     | 3.5.2  | VSB                          | 36 |

|     | 3.5.3  | NuBus                        | 37 |

|     | 3.5.4  | FUTUREbus                    | 37 |

|     | 3.5.5  | FUTUREbus+                   | 37 |

|     | 3.5.6  | Other busses                 | 38 |

| 3.6 | Conclu |                              | 38 |

|     |        |                              |    |

| Sun | nmary  |                              | 43 |

A Partial Gang Support

# List of Tables

| 3.1 | Alliant CCB signals.                                                                     | 25 |

|-----|------------------------------------------------------------------------------------------|----|

| 3.2 | Synchronization instructions.                                                            | 39 |

| 3.3 | Synchronization interconnects — systems                                                  | 40 |

| 3.4 | Standard bus support for synchronization                                                 | 41 |

| 3.5 | Synchronization memory — noting the type of memory or the instructions used to access it | 41 |

| 3.6 | Cache protocols for synchronization.                                                     | 42 |

# List of Figures

| 1.1  | Generic multiprocessor system.                                                              | 5  |

|------|---------------------------------------------------------------------------------------------|----|

| 2.1  | Instructions to acquire a lock.                                                             | 8  |

| 2.2  | Test-and-set.                                                                               | 9  |

| 2.3  | Compare-and-swap.                                                                           | 9  |

| 2.4  |                                                                                             | 10 |

| 2.5  | Fetch-and-add implemented using a lock.                                                     | 10 |

| 2.6  | Locks in special lock memory.                                                               | 13 |

| 2.7  | Locks in memory mapped special lock memory.                                                 | 13 |

| 2.8  | Locks in normal memory.                                                                     | 13 |

| 2.9  | Locks in tagged normal memory.                                                              | 13 |

| 2.10 | Special synchronization memory, distributed copies next to each processor, updated across a |    |

|      | special synchronization interconnect (e.g., Sequent SLIC).                                  | 15 |

| 2.11 | Special synchronization memory, one centralized copy, accessed across the normal memory     |    |

|      | bus (e.g., Sequent ALM).                                                                    | 15 |

| 2.12 | Test-and-set spinloop                                                                       | 16 |

| 2.13 | Test-and-test-and-set spinloop.                                                             | 16 |

| 2.14 | Anderson's fetch-and-add software queue spinlock algorithm.                                 | 17 |

| 2.15 | Graunke's exchange-with-memory software queue spinlock algorithm                            | 17 |

| 2.16 | Bus transactions for synchronization.                                                       | 18 |

| 2.17 | Bus transactions — exclusive bus lock                                                       | 19 |

| 2.18 | Bus transactions — split RMW.                                                               | 19 |

| 2.19 | Bus transactions — split read.                                                              | 20 |

| 2.20 | Bus transactions — split read and write                                                     | 20 |

| 2.21 | Bus transactions — out-of-order RMW                                                         | 22 |

| 2.22 | Bus transactions — implied write.                                                           | 22 |

|      |                                                                                             |    |

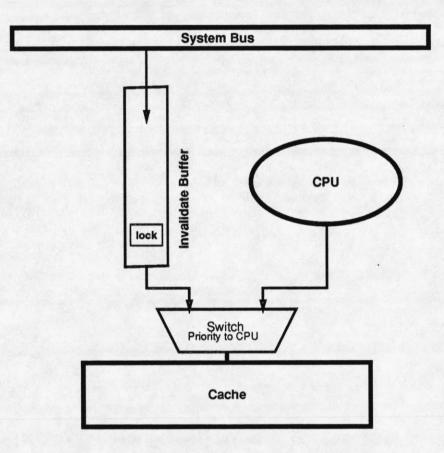

| 3.1  |                                                                                             | 27 |

| 3.2  | Gould NP1, spinlock blocking invalidation.                                                  | 28 |

| 3.3  |                                                                                             | 30 |

| 3.4  | ARM swap instruction.                                                                       | 33 |

| A.1  | Advising the operating system about lock usage.                                             | 45 |

### Chapter 1

### Introduction

Computer systems that contain multiple intelligent processors require mechanisms for synchronization between these processors. This includes synchronization between a single Central Processing Unit (CPU) and intelligent Input/Output (I/O) units, as well as synchronization between multiple CPUs in multiprocessor systems.

This report considers the implementation details of synchronization primitives. Of the several different types of synchronization, *mutual exclusion* (*locking*) is emphasized, because hardware support for this is more common, and other forms of synchronization can be built on top of mutual exclusion. Only the low level question of *how* synchronization is performed is discussed, not the higher level questions of *when* and *where* synchronization should be performed.

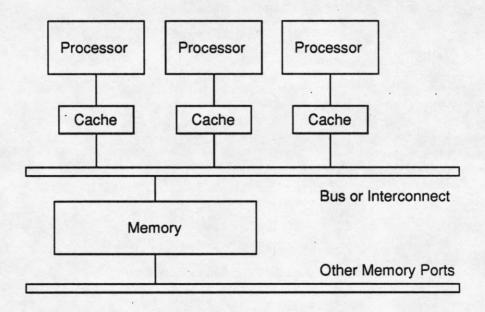

Figure 1.1: Generic multiprocessor system.

We are concerned with the systems of moderate price and performance that make up most of the computer marketplace. Shared memory systems with cache consistency protocols using a shared bus or a simple interconnect such as a crossbar switch are considered. Figure 1.1 illustrates such a generic multiprocessor system. Multistage interconnection networks are not considered except in passing, because such architectures are costly and will be used mainly by high-performance supercomputers and specialized processors in the next decade. *Distributed memory* and *message passing* systems are not considered because, although possibly in the modest price range, the mechanisms investigated in this research do not apply.

The rest of this report is structured as follows: Chapter 2 presents a taxonomy of synchronization features. It defines terms for future use. Chapter 3 surveys other work, particularly proposed cache and bus protocols for synchronization. Chapter 3 also surveys the implementation of synchronization primitives on a wide number of actual implementations, both academic and commercial, and conveys a sense of the present state of the art. Chapter 2 makes forward references to systems in Chapter 3 that demonstrate features of the taxonomy.

These chapters were originally introductory material to an MS thesis [29]. The survey was undertaken to see if the idea proposed by this thesis, the bus abandonment lock, was original. The taxonomy was developed to organize the information in the thesis. The full thesis contains an earlier version of the taxonomy and survey, a description of the bus abandonment lock, simulation experiments, and observations of the synchronization behaviour of real systems.

We hope that the taxonomy of Chapter 2 will be useful to others, although it has been our experience that most taxonomies are seldom used by anyone except their author. We have, therefore, emphasized descriptions of features rather than a global classification of systems.

### Chapter 2

### Taxonomy

#### 2.1 Introduction

Synchronization methods may be divided into two classes: those that require special hardware support in the form of atomic Read-Modify-Write (RMW) operations and those that do not. The former are our chief concern, since they are far more common; the latter will be discussed briefly in the next section.

#### 2.2 Synchronization Without Atomic RMWs

Synchronization between a single producer and a single consumer process is trivial, using only simple reads and writes. A number of other synchronization techniques similarly rely on single-writer variables and monotonicity for applications such as enforcing data dependencies between concurrent loop iterations [71].

The earliest algorithm for mutual exclusion of two contending processes requiring only ordered atomic read and write operations is attributed to Dekker by Dijkstra [17]. Dijkstra [16] generalizes this to Nprocesses. Knuth [48] points out that, although Dijkstra's algorithm ensures that all processes are not simultaneously blocked, it is still possible that an individual process may be blocked forever. Knuth suggests a modification that guarantees that a process will eventually enter the critical section, although it may have to wait while other processes perform the critical section  $O(2^N)$  "turns." The worst-case waiting time is reduced to  $O(N^2)$  turns by de Bruijn [12] and O(N) turns by Eisenberg and McGuire [22]. Peterson [58] presents simpler versions of Dekker's 2-process and Dijkstra's N-process algorithms. Lamport's [50] "Bakery" algorithm has a worst-case waiting time of O(N) turns and is more tolerant of process failures in the critical section. Raynal surveys these and several other synchronization algorithms in his book [59]. More recently, Woo [70] explains how to recycle timestamps in Lamport's algorithm.

All of these algorithms require O(N) storage and O(N) time to acquire a lock without contention. They are unwieldy, and most textbooks quickly assume that atomic RMWs are provided in hardware, and move on to higher level issues such as the implementation of semaphores, monitors, and other concurrency structures. The remainder of this report, however, considers the implementation of atomic RMWs for synchronization in detail.

#### 2.3 Instruction Set

There are two basic synchronization operations that an instruction set must support: (1) acquiring a lock, and (2) releasing a lock. A third operation is frequently used in test-and-test-and-set style spinlocks, such as are discussed in Section 2.5.2: (3) testing a lock. Other operations that may be supported in the instruction set, such as barrier operations, or parallel loop control are much less common and will not be considered.

#### 2.3.1 Releasing and testing a lock

Of these three operations, only acquiring a lock requires an atomic RMW operation. Two issues arise with respect to releasing and testing a lock: (a) Are special instructions provided for releasing and testing a lock, or are normal memory operations used? (b) Is releasing a lock needlessly symmetric with respect to acquiring a lock?

Although releasing a lock and testing a lock are semantically equivalent to ordinary memory operations, their performance characteristics are quite different. Caches, for example, take advantage of locality: a processor is more likely to access a variable that it has used recently than is a different processor that has not used the variable. A synchronization variable, however, is quite likely to be accessed immediately by a different processor [29]. Similarly, the desired memory system behaviour of testing a lock may be very different from normal reads. Section 3.3.5 shows how the use of a normal instruction to test a lock could dramatically decrease performance in an existing system. Special instructions for releasing and testing a lock provide hints to the memory system that may improve performance.

Section 2.6.2.2 shows how a distinct instruction for lock release is desirable in a system with split RMW bus transactions, so that lock release can be distinguished from ordinary memory writes and subjected to the memory interlock that ensures atomicity. Moreover, as coherency models (Section 2.7) evolve, a special instruction for releasing a lock may assume a new semantic role. A widely used model ensures memory consistency only at synchronization operations; it may be desirable to have the choice of ensuring memory consistency either at lock acquisition or at lock release. Some architectures, such as the VAX, prohibit mixing interlocked and normal memory accesses to the same location; others, such as the MVME141, permit intermixing, but may lose cache consistency for these locations.

Some systems have provided instructions for releasing a lock that are symmetric with respect to the instructions for acquiring a lock. This is overkill: lock release does not require an atomic operation, and using an unnecessary atomic operation may exact a performance penalty (Section 3.3.5).

#### 2.3.2 Acquiring a lock

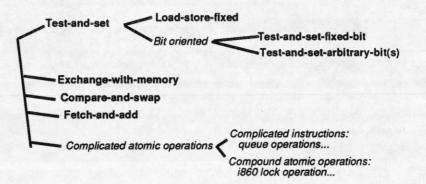

Fine distinctions between atomic RMW instructions are useful because of important differences in implementation complexity. Figure 2.1 shows such a classification, with complexity increasing from top to bottom.

Figure 2.1: Instructions to acquire a lock.

Section 2.3.2.1 discusses the simple instruction set primitives. Sections 2.3.2.2, 2.3.2.3, and 2.3.2.4 describe the last two items, the problem of building up complicated atomic operations. Appendix A proposes a mechanism to solve this problem.

#### 2.3.2.1 Simple synchronization primitives

Let us examine the synchronization primitives provided by a processor instruction set. RMW primitives such as *test-and-set* are the most common. Test-and-set's semantics are presented in Figure 2.2.

test-and-set(lock): \* temp ← lock \* lock ← 1 return temp

Figure 2.2: Test-and-set.

Atomicity is provided for the operations marked \*, usually by the processor blocking interrupts locally and asserting a LOCK signal externally throughout the read and write operations required.

Minor differences in the details of test-and-set have an important effect on the implementation. Some test-and-set instructions modify arbitrary individual bits within a word in memory. These are called *test-and-set-arbitrary-bit(s)*. Since few processors and busses let bits be individually addressed, this requires one bus operation to read the word containing the bits to be changed, a processor operation that changes the bits, and another bus operation to write the bits back. This prevents the implied write bus operations of Section 2.6.2.3 from being used. Some test-and-set instructions address only a fixed bit of each word, typically the most- or least-significant bit. These test-and-set-fixed-bit operations are more easily used with out-of-order bus operations and snooping caches.

Exchange-with-memory is more powerful than test-and set, writing an arbitrary value to memory, but exchange-with-memory is often used in a stylized manner where the values exchanged are only 0 and 1. Graunke and Thakkar's queue lock [33] uses the full power of exchange. It is convenient to write the smallest size location that can be separately addressed by a write partial bus transaction.<sup>1</sup> Taking away the ability to write an arbitrary value yields a test-and-set operation that addresses a byte or a word rather than a bit. This load-store-fixed<sup>2</sup> operation can be implemented so that the write does not travel across the bus (Section 2.6.2). Of all the simple synchronization operations, load-store-fixed leads to the simplest advanced implementation, in terms of out-of-order bus protocols for synchronization and cache snooping.

Compare-and-swap is a primitive that can "short-circuit" after testing the value of the synchronization variable. Its semantics are described in Figure 2.3.

compare-and-swap(loc,old,new)

\* temp ← loc

\* if temp = old

\* then loc ← new

return temp

#### Figure 2.3: Compare-and-swap.

This version is as implemented in the IBM 370. It can be used to add an element to a queue, failing if other processors are performing the same operation simultaneously, or in a number of other optimistic concurrency control approaches. Herlihy [36] shows that compare-and-swap can be used to build nonblocking and wait-free concurrent data structures, and that none of the other primitives discussed in this section are

<sup>&</sup>lt;sup>1</sup> For example, a 64-bit bus may have byte lane signals that permit individual 8-bit bytes to be written.

<sup>&</sup>lt;sup>2</sup> The differing dash lengths in load-store-fixed are deliberately designed to distinguish between the separate actions of loading the old value of the lock, and storing a fixed value.

of equal power. If the compare operand is always zero, giving *compare-fixed-and-swap*, fewer bus operations are required in advanced implementations. Compare-fixed-and-swap may be used to write the identity of the lock holder to the lock.

Fetch-and-add is a more complicated operation than test-and-set or compare-and-swap, as shown by Figure 2.4. Fetch-and-add may be implemented in a serial manner, like any other RMW operation. However, fetch-and-add operations may be combined, in the interconnection network of large computer systems such as the NYU Ultracomputer [31] or IBM RP3, or on a bus, as in the Alliant FX. Several processors can receive unique loop indexes, for example, simultaneously. Fetch-and-add can be generalized for arbitrary fetch-and-op operations; indeed, all the other simple synchronization primitives may be thought of as special cases of fetch-and-op [31].

fetch-and-add(loc,inc)

\* temp ← loc

\* loc ← loc+inc

return inc

Figure 2.4: Fetch-and-add.

#### 2.3.2.2 The waiting for a nonrunning process problem

Sometimes it is necessary to perform complicated instruction sequences atomically. For example, if a processor is adding an element to a list in shared memory, other processors should not access the list until all of the pointers have been changed.

In other computer applications, complex operations are built up out of simpler instructions. This may not be practical for complex atomic actions. The RMW primitives described above might be used to acquire and release a lock, as depicted in Figure 2.5, which implements a fetch-and-add operation using mutual exclusion. However, if a user process is preempted or suffers a page fault while in the critical section, the lock may be held for a very long time. Other processes spinning to acquire the lock waste resources uselessly. This is the *waiting for a nonrunning process* problem. With fair-share and preemptive scheduling, this is only a performance problem, not a correctness problem, but in other situations deadlock may result.

```

acquire lock

load r1 \leftarrow loc

add r1 \leftarrow r1 + inc

store r1 \rightarrow loc

release lock

```

#### Figure 2.5: Fetch-and-add implemented using a lock.

This is not a multiprocessor problem. Processes running on different processors can always use a software locking protocol to provide exclusive access to a data structure. The problem is caused by context switching on the local processor. There would not be a problem if the user process could lock down resources such as virtual memory, preventing a page fault in the middle of the critical section, and if the user could block interrupts, preventing preemption by the operating system. Many systems provide limited facilities to lock down resources, such as plock() [64]. However, their use usually requires software "root" privilege. Interrupt blocking usually requires hardware privilege. If any user can block interrupts, then a multiuser system can be hung by a malicious or error-prone user with an infinite loop in a critical section. The problem here is not giving the user the ability to block interrupts, but placing a time limit on it.

#### 2.3.2.3 Complicated atomic instructions

Some processors provide complicated atomic operations as single instructions. The Motorola 680x0's CAS2 instruction performs a compare-and-swap operation on two locations at once, and can be used for doubly linked list operations. However, many systems using the Motorola chips do not implement the bus protocol required to make CAS2 atomic, and provide only the more primitive TAS test-and-set operation.

Digital's VAX architecture provides atomic, noninterruptible, operations that insert at the head and tail of doubly linked queues. Since the amount of work in performing these operations is fixed, interrupts cannot be blocked for an arbitrary amount of time. The queues can be addressed relatively as well as absolutely, so that they can be used for synchronization between processes that do not have the same address mapping, or between processes and drivers.

The Gould NP1 also provided atomic queue operations. In addition to the queue operations that required a fixed amount of work, there was an operation to insert in a priority ordered queue that might potentially require scanning all of the elements of the queue. This instruction was removed in subsequent versions of the architecture. It was faster to emulate the queue operations in macrocode inside the kernel, but since the user could not execute the privileged operations required to block interrupts, and since system call overhead would have drowned out the time advantage of macrocode, the atomic queue operations were provided to the user.

Operating System (OS) intervention may be required to perform complicated atomic actions, on systems that do not provide sufficiently high level synchronization instructions in hardware. The BBN TC2000 [6], a large switch-based Non-Uniform Memory Access (NUMA) machine, for example, has only the exchange-with-memory **xmem** primitive available in the instruction set. The TC2000's nX UNIX-based operating system provides the following operations as system calls: fetch-and-add, fetch-and-and, fetch-and-or, compare-and-swap, an atomic clear-then-add operation that can be used for fetch-and-add of a bitfield, as well as atomic operations to find the leading 0 or 1 bit and complement it.

Complicated atomic operations as primitives, whether provided by hardware as instructions or by software as system calls, however, are always limited. The user cannot add to the set of primitive atomic operations. The next section discusses mechanisms that let the user build arbitrary atomic operations.

#### 2.3.2.4 Compound atomic operations

Many systems, such as the AMD 29K, let software explicitly control the lock signal on the bus by writing to a control register. In combination with interrupt blocking, arbitrary instruction sequences can be made atomic, but this usually requires hardware privilege.

A more general solution is provided by the Intel i860. Its lock instruction asserts a signal on the external interface, and blocks interrupts, for up to 32 instructions. In other words, interrupt blocking is unprivileged and time limited. Reasonably complicated atomic operations can be coded entirely within this 32 instruction critical section. The critical section must be coded as a transaction with a commit phase, doing no writes before all possible places where an exception can occur have been passed. The operating system can detect when a page fault occurs within such a lock critical section, and will restart after a fault at the lock instruction. After a page fault, the operating system will ensure that the faulted-in page is made resident, and that other resources required by the critical section are available, in order to guarantee forward progress. This operating system support may require the operating system to interpret the instructions of the critical section to determine what resources are required.<sup>3</sup> The complexity is comparable to that of ensuring that all the pages necessary for address translation of a complicated instruction like VAX MOVC3, on a system with paged page tables, are resident.

Gang scheduling avoids the waiting for a nonrunning process problem by swapping out all threads of a parallel process if any one of them faults. This is wasteful: if there are N processes, one which has been

<sup>&</sup>lt;sup>3</sup>Stylized code and user-provided hints may be used — for example, no more than 4 pages may be touched by such a transaction, and registers R0..R3 contain addresses in these pages. Compiler support may be necessary to implement these conventions.

preempted and another which is waiting for a resource held by the the preempted process, the remaining N-2 processes could be accomplishing useful work which will be delayed if the entire gang of N processes is swapped out. A compromise for a throughput oriented operating system would be to leave the remaining N-1 processes running, including the spinning process (whose identity the operating system is not aware of) if there are no processes which are not in the gang to run; but if there are M < N - 1 other processes runnable, then only N - M processes of the gang will run. In other words, partial gangs are permitted to run only on an otherwise idle system. Random chance determines whether the spinning process is part of the N - 1 - M process partial gang. A better approach is to tell the operating system which processes are spinning on a lock and are good candidates for preemption, and which processes hold locks and should be preempted only as a last resort. Appendix A sketches such a proposal.

#### 2.4 Memory

The next two sections discuss aspects of synchronization memory. Section 2.4.1 discusses the architectural issue of whether the synchronization memory is special, or indistinguishable from normal memory. Section 2.4.2 discusses the implementation issue of whether the synchronization memory is distributed or centralized. The first is an architectural issue because it affects the programming model visible to human programmers or high level language compilers, although the decision has important consequences for implementation cost and performance. The second is an implementation issue because it affects only the cost or performance of one of the synchronization memory models from Section 2.4.1.

#### 2.4.1 Special versus normal

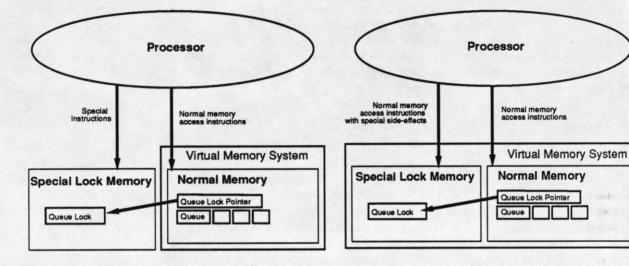

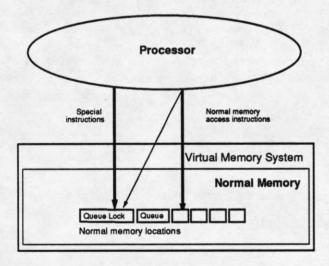

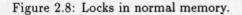

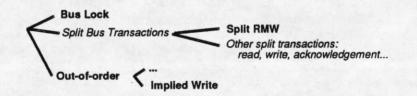

Synchronization schemes may be classified according to whether they use special synchronization memory or normal memory (Figures 2.6, 2.7, 2.8, and 2.9).

- Distinct special memory: Synchronization variables are placed in registers which must be accessed by special instructions. Examples include the Alliant FX [63], the Cray X-MP [39], and the Sequent Balance's SLIC gates [68].

- Mapped special memory: Synchronization is done in special memory, which can be mapped into user address space and accessed via ordinary load and store instructions which have special, atomic, sideeffects. Examples include the Sequent Balance ALM [68].

- Normal memory: Synchronization variables are placed in normal memory locations, but are accessed via special atomic operations. This is the most prevalent.

- Tagged normal memory: Some systems use locks that are associated with normal memory locations, but are hidden in tags and are not normal data. Examples include HEP full/empty bits [13], and IBM 801 storage [10].

- These different types of synchronization memories raise several issues:

- Special synchronization instructions.

- Protection.of synchronization memory.

- Number of synchronization variables.

Special synchronization instructions: Synchronization in distinct special memory and normal memory requires special instructions. Programmers in high level languages may not be able to access these instructions directly, and may be forced to code in assembly when explicitly using synchronization. Parallelizing compilers may be able to use these instructions implicitly. Normal compiled code can be used to access locations in mapped special synchronization memory, but code generators must be made aware of side-effects from accesses to synchronization variables, using mechanisms such as C's volatile directive.

Figure 2.6: Locks in special lock memory.

Figure 2.7: Locks in memory mapped special lock memory.

Figure 2.9: Locks in tagged normal memory.

**Protection of synchronization memory**: Distinct special synchronization memory must either be restricted to privileged users, or some mechanism must be provided to prevent nonprivileged users of the special purpose synchronization store from interfering with each other. Virtual memory mechanisms already provide protection for mapped and normal synchronization memory.

Number of synchronization variables: Synchronization variables in special memory, mapped or unmapped, must be allocated separately from user data structures in normal memory. The association between user data structures and their synchronization variables must somehow be made, by convention, address arithmetic, or pointers (as indicated in Figures 2.6 and 2.7). Usually, however, special synchronization memory provides only a limited number of locks, many fewer than the number of memory locations. Libraries may be provided to multiplex a large number of virtual locks on a small number of hardware locks [62]. Synchronization techniques based on normal memory have no arbitrary resource restrictions (other than the fundamental one of running out of memory).

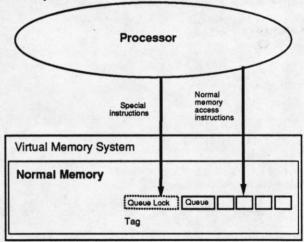

#### 2.4.2 Distributed versus centralized

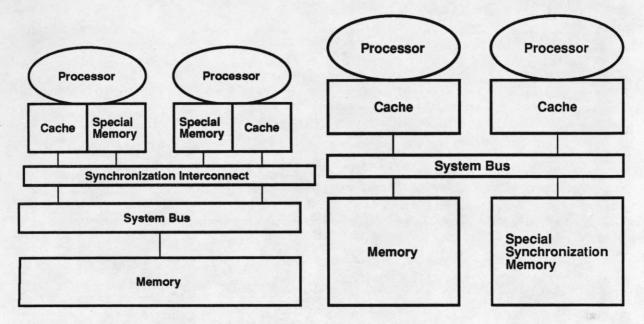

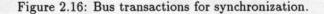

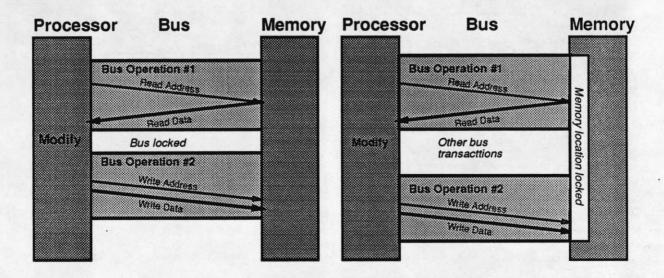

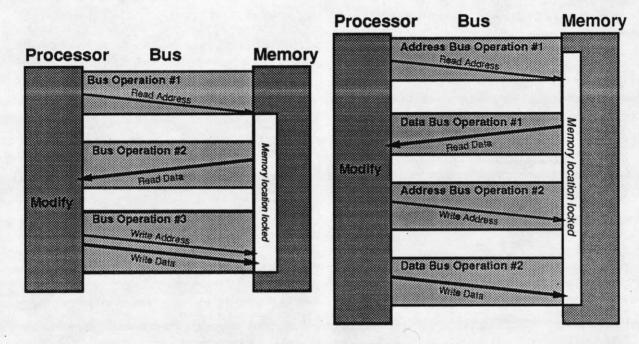

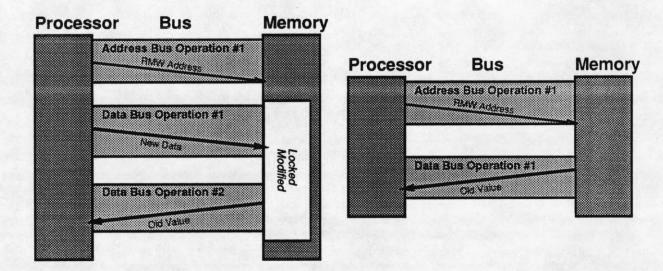

Memory used for synchronization may be distributed or centralized. Distributed synchronization memory maintains a local copy of all the synchronization variables at each processor, broadcasting changes at one processor to all other processors. No single memory is privileged with respect to the others. Centralized synchronization memory has a central "master copy" or primary source for each synchronization variable. Usually, this is of the form of a single physical resource, but there may be multiple physical memories for synchronization, perhaps closer to one processor than another. Also, a centralized memory may have multiple cached copies. Nonetheless, a synchronization variable's "home" is in only one of these memories.