# AUTOMATA & SEQUENTIAL MACHINES, A SURVEY

Herbert Y. Chang

**REPORT R-168**

1

5

1 24

JUNE, 1963

COORDINATED SCIENCE LABORATORY UNIVERSITY OF ILLINOIS URBANA, ILLINOIS

Contract DA-36-039-TR US AMC 02208(E) DA Project 3A-99-25-004

The research reported in this document was made possible by support extended to the University of Illinois, Coordinated Science Laboratory, jointly by the Department of the Army, Department of the Navy (Office of Naval Research), and the Department of the Air Force (Office of Scientific Research) under Department of Army Contract DA-36-039-TR US AMC 02208(E).

### TABLE OF CONTENTS

page

Ĵ

ľ

J

| INTRODUCTION                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| , THE MODELS, DEFINITIONS AND NOTATIONS | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.1 Moore's Model                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2 Mealy's Model                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.3 Finite-State Model-I                | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.4 Finite-State Model-II               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.5 Non-Printing Tape Machine           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| , CHARACTERIZATION OF MACHINES          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1 Input-Output Signal Set Method      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.2 W-Machine Program Method            | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ANALYSIS AND SYNTHESIS                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1 The Notion of Experiments           | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2 Decomposition of Machines           | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.3 On Machine Synthesis Techniques     | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CONCLUSION                              | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FERENCES                                | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                         | <pre>THE MODELS, DEFINITIONS AND NOTATIONS<br/>2.1 Moore's Model<br/>2.2 Mealy's Model<br/>2.3 Finite-State Model-I<br/>2.4 Finite-State Model-I<br/>2.5 Non-Printing Tape Machine<br/>CHARACTERIZATION OF MACHINES<br/>3.1 Input-Output Signal Set Method<br/>3.2 W-Machine Program Method<br/>ANALYSIS AND SYNTHESIS<br/>4.1 The Notion of Experiments<br/>4.2 Decomposition of Machines<br/>4.3 On Machine Synthesis Techniques<br/>CONCLUSION</pre> |

#### 1. INTRODUCTION

Automata theory is becoming the core of many modern physical sciences. The theory of switching and sequential circuits is merely a branch of this new field of science. In spite of the rapid growth of new concepts and ideas of automata theory in recent years, only a limited number of applications is seen in computer design practice. A partial reason may be due to an engineer's unfamiliarity with the abstract notions being employed in the literature of automata theory. An attempt is made therefore to study the important contributions of this new field of science to the practical problems encountered in the area of sequential machine theory. The investigation concerning design and analysis is taken from an engineer's viewpoint with emphasis on the established theoretical results and possible routes for future development. Familiarity with notions of Huffman-Moore-Mealy is assumed. In the first section, various models of sequential machines are defined. Methods of characterizing machines other than the usual flow table or state diagram approach are pointed out in the second section. Finally, a number of results and problems concerning analysis and synthesis are mentioned.

# 2. THE MODELS, DEFINITIONS AND NOTATIONS

Among various classes of automata - fixed and growing, discrete and continuous, synchronous and non-synchronous, deterministic and probabilistic, and finite-state and infinite-state<sup>[75]</sup> - models of sequential machines are usually classified as the class of fixed discrete synchrouous deterministic finite-state automata, or simply <u>finite automata</u> in short. In this section, we will introduce some of the common models that are discussed in the literature.

#### 2.1 Moore's Model

E.F. Moore<sup>[79]</sup> was among one of the first to investigate the abstract properties of sequential circuits. According to his notion, a <u>sequential</u> <u>machine</u> is a machine which has a finite number of <u>states</u>, a finite number of possible input symbols, and a finite number of possible output symbols. The behavior of the machine is strictly deterministic in that the present state of the machine depends only on its previous input and previous state, and the present output depends only on the present state.

If we denote by  $\sum$  the set of possible inputs whose elements are  $I_1$ ,  $I_2, \ldots, I_m$ ,  $\Delta$  as the set of possible outputs whose elements are  $Z_1, Z_2, \ldots, Z_p$ ; and Y as the set of (internal) states whose elements are  $q_1, q_2, \ldots, q_n$ ; where n,m, and p are finite; and furthermore, if we call  $\delta$  the <u>next state</u> function and  $\lambda$  the <u>output</u> function, then the description of Moore's model can be transformed into the mathematical expressions:

$q_{j} = \delta (I_{i}, q_{i})$  $Z_{j} = \lambda (q_{j})$  $q_{i}, q_{j} \in Y, I_{i} \in \sum$  $Z_{i} \in \Delta$

2:(2-1)

where subscript i denotes previous moment and j denotes present moment on the time scale. If  $\delta$  is defined for all possible pairs of (I, q); I  $\in \sum_{i=1}^{n}$ ,  $q \in Y$ ,

then we say the machine is <u>complete</u>; otherwise, the machine is called . incomplete\*. In other words, output and next state of an incomplete machine are not defined for every input.

Since the output depends only upon the state and not upon the input,  $\lambda(I_1, Q) = \lambda(I_2, Q)$ , for  $q \in Y$ , and any  $I_1, I_2 \in \Sigma$ , this model is also called input **independent** machine. We must not, however, be confused by the name "input **independent**" and fail to recognize the fact that the next state does depend on the input, so that a sequence of outputs  $\lambda(J, Q)$  does depend on the input sequence J whenever J has a length greater than 1.

#### 2.2 Mealy's Model

Mealy's<sup>[76]</sup> definition of sequential machine<sup>†</sup> is contained in the definition of what he called a switching circuit.

A switching circuit is a circuit with a finite number of inputs, outputs, and (internal) states. Its present output combination and next state are determined uniquely by the present input combination and the present state. If the circuit has one internal state, we call it a <u>combinational</u> circuit, otherwise, we call it a sequential circuit (machine).

Again, the definition can be characterized by the equations:

$q_{k} = \delta(I_{j}, q_{j})$  $Z_{j} = \lambda(I_{j}, q_{j})$

where subscripts j and k denote present moment and next moment, respectively, on time scale.

Moore's and Mealy's model have been shown by Cadden<sup>[22]</sup> to be equivalent in the sense that every system describable by one model is shown to be describable by the other also. More discussions on the behavior equivalence of these

According to Huffman's terminology, the terms "complete" and "incomplete" are equivalent to the terms "completely specified" and "incompletely specified", respectively.

'Mealy actually used the word "circuit", the difference between a sequential machine and a sequential circuit does not seem to be in existence, from a mathematical point of view, see S. Seshu<sup>[96]</sup>

See Section 2.2 for reference.

3

(2-2)

two models can be found in papers by S. Seshu<sup>[96]</sup> and A. Gill.<sup>[34]</sup>

In the field of automata studies, there has not been a unique definition of <u>automaton</u> that every writer agrees upon. The complexity of the problem often forces the writer to define new terms, and give new names on various occasions to suit his special purpose. It is, therefore, rather difficult to correlate all models of automata with Moore-Mealy's notion. We will only mention a few models which have the closest similarities related to sequential machines.

#### 2.3 Finite-State Model-I

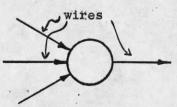

A. Burks and H. Wang<sup>[19]</sup> discuss a model of finite automata which appears to be general enough to represent any other models of its kind. Before we introduce their model, we need a few definitions. By <u>junctions</u> we mean the ends of wires which do not impinge on a switching-element circle or a delayelement rectangular, (Figure 1).

Switching Element

Delay Element

Figure 1. Switching Element and Delay Element

A junction with no output wires attached to it is called an <u>input junction</u>. All others are called internal junctions.

An (finite) automaton is a fixed finite structure with a fixed number of input junctions and a fixed number of internal junctions such that: (a) each junction is capable of having two states, (b) the states of input junctions at every moment are arbitrary, (c) the states of the internal junctions at time zero are distinguished, (d) the internal state (i.e., the states of the internal

junctions) at time t+l is completely determined by the states of all junctions at time t and input junctions at time t+l according to some pre-assigned law (which is embodied in the given structure).

COriin other words, this model can be characterized by two arbitrary effective transformations  $\tau$  and  $\lambda$  from pairs of integers to integers. These integers are drawn from finite sets  $\{I\}$ ,  $\{S\}$ , and  $\{O\}$ . Set  $\{S\}$  contains a distinguished integer  $\mathcal{J}$ . Transformations are given:

$$S(0) = \int_{0}^{0} S(t+1) = \tau[I(t), S(t)]$$

(2.3)

$$O(t) = \lambda[I(t), S(t)]$$

Apart from the fact that a particular initial state is specified, this model is essentially the same as Mealy's.

#### 2.4 Finite-State Model-II

Closely related to Moore's model is the class of <u>two-symbol</u> <u>finite</u> automata defined by C.Y. Lee.<sup>[67]</sup>

A two-symbol finite automaton consists of

- (a) A finite number of internal states,  $q_0, q_1, \dots, q_n$

- (b) An alphabet of two symbols:  $S_0=0$ ,  $S_1=1$

- (c) A map M whose domain and range are both subsets of the set of state-symbol pairs. If M is defined over state-symbol pair \$\fig(q\_i,S\_j)\$, then M(q\_i,S\_j)\$ is another pair (q\_k,S\_r). The symbol S\_r is called an <u>output symbol</u>, and is completely determined by q\_i; that is, S<sub>r</sub> is independent of the <u>input symbol</u> S<sub>j</sub>.

- (d) An initial state  $q_0$ , which can reach every state  $q_i$ ,  $0 < i \le n$  via some suitable input sequence of symbols.

This class of finite automata, as pointed out by Lee, can be regarded as a subfamily of Turing machines  $\begin{bmatrix} 102 \end{bmatrix}$  and also a subfamily of W-machines.  $\begin{bmatrix} 103 \end{bmatrix}$

2.5 Non-Printing Tape Machine<sup>[89]</sup>

Intuitively, a non-printing tape machine may be regarded as a black box with a reading head and a one-dimensional tape. A yes-or-no question, interpreted as any arbitrary <u>finite</u> sequence of symbols from a finite alphabet, is represented by a tape. The reading head then reads the tape one symbol at actime. After each reading, it advances the tape one unit and reads the next symbol. The process stops when it runs out of tape. At this point, the machine answers the question by indicating a YES or a NO.

Now we are ready to give a formal definition of this model.

A <u>Non-Printing Tape Machine</u> over the alphabet E is a system  $U=(S,M, \checkmark_O, F)$ where S is a finite non-empty set (the <u>internal</u> states of U), M is a function defined on the cartesian product S x E of all pairs of states and symbols with values in S (the table of transitions or "moves" of U),  $\checkmark_O$  is an element of S (the <u>initial</u> state of U), and F is a subset of S (the designated <u>final</u> states of U).

If  $\Lambda$  is denoted as the empty tape with no symbols; T as the class of all tapes, then we have the relations:

$$M(J,\Lambda) = J, \text{ for } J \in S$$

$$M(J,X; \sigma) = M(M(J,X), \sigma), \text{ for } J \in S, x \in T, \text{ and } \sigma \in E \qquad (2-4)$$

$$M(J,X;y) = M(M(J,X),y), \text{ for } J \in S, x, y \in T$$

In addition to models mentioned above, there are still many other models whose structure and behavior bear close relations to that of Moore and Mealy models. Nerve nets<sup>[66],[72]</sup> and W-machines<sup>[68]</sup> (printing automata) are merely two of the many examples. A few abstract models are also discussed by Ginsburg in his papers<sup>[47],[51]</sup>

To avoid ambiguity, we shall consider a sequential machine or simply a <u>machine</u> to be Mealy's model, unless otherwise specified. The terms <u>finite</u> <u>automaton</u> and machine are taken to be interchangable. In other words, a machine is characterized by the expressions:

$$u_{k} = S(I_{j}, q_{j})$$

$$(2-5)$$

$$u_{j} = \lambda(I_{j}, q_{j})$$

which is the same as (1-2). We shall denote a machine S with n (internal, states, m inputs, and p outputs as  $S_{(n,m,p)}$ . A machine S is said to be strongly connected<sup>[79]</sup> if for any ordered pair  $(q_i,q_j)$  of states of S, there exists a sequence of inputs which will take the machine from state  $q_i$  to state  $q_i$ .

#### 3. CHARACTERIZATION OF MACHINES

The most important and most difficult part of synthesis of a sequential machine is the problem of stating exactly what this machine should do. The complexity of synthesis procedure depends, to a great extent, on the precision and simplicity of how the problem is specified. In this section, we intend to discuss some of the topics on methods to characterize machine actions that are related to concepts of automata theory. We will not, however, discuss the use of conventional "flow table" or a combination of state diagram and truth-table descriptions since these techniques are commonly known in practice. Interested readers may refer to papers by Huffman<sup>(61)</sup>, Moore<sup>(79)</sup>, and Mealy.<sup>(76)</sup>

#### 3.1 Input-Output Signal Set Method

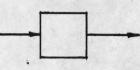

Let us think of a sequential machine as a black box with a finite number of input terminals and a finite number of output terminals (Figure 2).

Inputs

Figure 2. A 'Black Box' Machine

The black box is required to do certain things whenever a combination of input signals is present at input terminals so that a certain configuration of output signals will appear at output terminals. In other words, the black box acts like an input-output transducer subject to some given operating conditions. A natural way to characterize machine's action is therefore to specify the desired input-output configurations at these terminals. Machine's operation is synchronous. Signals are observed only at discrete moments of time, thus they can be applied in sequences according to some arbitrary time scale. We shall call this kind of input-output sequence characterization the input-output signal set<sup>[67]</sup> specification, or in more familiar words, the regular expression language<sup>[73] [13]</sup> specification.

A question arises here: What properties should a signal set possess in order to characterize a machine? The concepts of representation and realization of input-output signal sets are discussed by Kleene<sup>[66]</sup>; Copi, Elgot and Wright<sup>[23]</sup>; Rabin and Scott<sup>[89]</sup>; Lee<sup>[67]</sup>; Arden<sup>[4]</sup>; McNaughton and Yamada<sup>[73]</sup>; and many others (see bibliography).

Without loss of generality, let us represent the time scale by integers 0,1,2,...,t<sup>.</sup> with 0 denoting the origin and t the present moment. At any time t, every signal at a terminal is assumed to take one of the two binary values, 0 or 1. An input (or output) configuration then becomes an ordered n-tuple of 0's and 1's. Along the time scale, sequences of input and output ordered n-tuples are called <u>input sequence</u> and <u>output sequence</u>, respectively. Among sets of input sequences, in order to distinguish one set that is applicable to a machine from those that are not, the notion of <u>event</u> is introduced.<sup>66</sup> An <u>event</u> is a subset of the set of all input sequences. It <u>occurs</u> when the actual input sequence belongs to this subset. An event E is said to be <u>realized</u> by a machine if and only if the signal at output terminal is 1 at the time of application of the last symbol of any input sequence denoted by E. Some events are realizable with combinational circuits but some others require circuits with memory (sequential machines).

Combinational circuits are often referred to as <u>definite automata</u> in the terminology of automata theory. More precisely, a <u>definite automaton</u> is a machine whose output at any time t is uniquely determined by the direct inputs at times t-l+1, t-l,...,t-1,t (l is finite). An event is <u>definite</u> if it is characterized by finite sets of sequences whose occurrences depend on the last  $l(\geq 1)$  moments of time, t-l+1, t-l,...,t. The realizability of definite events is discussed in papers by Kleene<sup>[66]</sup>; Copi, Elgot and Wright<sup>[23]</sup> with instantaneous logic, and by Arden<sup>[4]</sup> with both instantaneous logic and delay logic. The important result is that every definite event is realizable by a definite automaton using logical devices consisting of AND-gate, ORgate, inverters and delays only, and every definite automaton represents a definite event. A number of topics concerning definite automata and definite events have been discussed by Perles, Rabin and Shamir<sup>[88]</sup>; and by Brazozowski<sup>[13]</sup>.

Events that characterize finite automata (or sequential machines) are so-called <u>regular events</u>. A few preliminary definitions are needed before we discuss the regularity of events. By <u>concatenation</u> of two events S and T, written as S \* T, we mean the set of all sequences formed by a member of S followed by a member of T. <u>Iterate</u> of S and T, written as  $S^*T$ , means the smallest set of all sequences of S,  $S \cdot T$ ,  $S \cdot S \cdot T$ ,  $S \cdot S \cdot S \cdot T$ , ..., etc. If T is empty, then  $S^*T$ , which can be written as  $S^*$ , means the smallest set of sequences of  $\phi$  (empty set), S, S  $\cdot S$ , S  $\cdot S$ , S  $\cdot S$ , ... etc. Finally, the <u>union</u> of S and T, written as S v T, means the set of all sequences consisting of members of S and T.

<u>Regular events</u> are defined recursively as follows: (1) every event consisting of finite set of sequences is regular, (2) the concatenation of two regular events is regular, (3) the iterate of a regular event on a regular event is regular, (4) the union of two regular events is regular, (5) no event is regular unless its being so follows from (1), (2), (3), (4). It is apparent that definite events are regular, but regular events are not necessarily definite in general.

If we denote symbols in sequences by alphabet  $\{0,1\}$ , and let  $\phi$  be the unit set of null sequences, i.e., sequence of zero length, and let  $\Lambda$  be the empty set of sequences, regular events then can be described by a language called regular expressions. Regular expression is defined recursively as follows: (1) a string consisting of a single 0, a single 1, a single  $\phi$  or a single  $\Lambda$  is a regular expression, (2) if P and Q are regular expressions, then so are  $P \vee Q$ ,  $P \cdot Q$  and  $P^*$ , (3) no other string of symbols is a regular expression unless its being so followed from (1) and (2). Thus an event is regular if and only if it can be described by a regular expression. Here we give an example showing how regular expression specifies an input signal set. Suppose the word description for a one-input and one-output machine is given as: "The output is 1 if and only if the binary value: of input sequence is equal to  $2^{n}+1$  (n > 1) since the last output 1 (disregarding the output at t=0)." In regular expression language, this specification is equivalent to =[1(0)<sup>1</sup>], which is the set consisting of sequences 11, 101, 1001, 10001, ..., etc. A sample of this signal set is:

Kleene indicates that any finite automaton can be characterized by a regular expression and every regular expression can be realized by such an automaton, and hence answers our question.

For machines having only one-input and one-output terminal, regular expression language appears to be an ideal way to specify machine's action. The language is precise, allows no ambiguity, and moreover, can be written out in one line in contrast to flow tables and state diagrams. It is better related to word description of a sequential machine. In spite of these advantages, up to now, the language is however not commonly adopted in design practice. Two of the main reasons are: (1) lack of thorough understanding of the language. Some important problems are still unsolved, such as algorithms for determining equivalence of regular expressions, i.e., whether they represent the same signal set; the search for the existence of "canonical forms" (minimal complexity) of regular expressions; and problems relating algebraic manipulations. of regular expressions, (2) as number of input and output terminals increases. the number of regular expressions needed to complete a specification of a machine also increases. The complexity of synthesis procedure increases accordingly. Even for a machine of moderate size, say 8 input-output terminal pairs, the problem becomes so complicated that a designer would rather choose a flow table or state diagram approach.

#### 3.2 W-Machine Program Method

Another way of characterizing a sequential machine is by means of a socalled W<sup>±</sup>machine program<sup>[67],[68]</sup> The idea of a programmable machine is introduced by H. Wang.<sup>[103]</sup> Every W-machine is made up of an exterior mechanism and an internal program structure. The exterior of a W-machine consists of (1) an alphabet of two symbols 0 and 1, (2) a one-way tape, potentially infinite to the right, which is divided into squares. Each square is either <u>marked</u> (symbol 1) or <u>erased</u> (symbol 0), (3) a read-write head which is capable of marking or erasing a square; and (4) a control mechanism to carry out instructions of the program structure. The internal program structure of

W-machine is an ordered list of instructions, called the <u>program</u> of W-machine which is executable by the control mechanism. The types of instructions are (1) e; erase the square under scan (by the read-write head), (2) m; mark the square under scan, (3) +; move the read-write head one square to the right, (4) -; move the read-write head one square to the left, (5) t(A); transfer to the instruction whose address is A if the scanned square is marked, otherwise transfer to next instruction in the program. C.Y. Lee<sup>[67]</sup> has shown that such a W-machine with S instructions is completely equivalent to a Turing machine with not more than S states and every Turing machine with n states is completely equivalent to a W-machine with not more than 10n+1 instructions. Here the term "completely equivalent" means what can be done with one can also be done with the other, no more and no less. For example, a 1-state Turing machine described by flow table:

| State | Symbol |       |  |  |

|-------|--------|-------|--|--|

| State | 0      | 1     |  |  |

| q     | m,+,q  | e,-,q |  |  |

is completely equivalent to a W-machine described by a program:

| Addresses | Instructions    |

|-----------|-----------------|

| 1         | t(3)            |

| 2         | m,+,t(3),m,t(2) |

| 3         | e,-,t(3),m,t(2) |

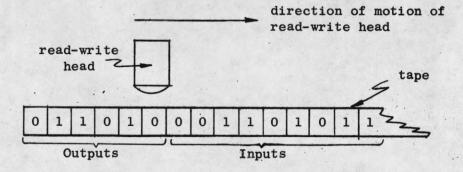

If the instruction "-" is deleted from the program of a W-machine, we obtain a W<sup>+</sup>machine. A W<sup>+</sup>machine is essentially a finite automaton which can be characterized by input-output sequences. The input sequence of symbols of such an automaton may be considered to be copied on the tape of W<sup>+</sup>machine, with the initial input symbol on the leftmost square of the tape. The operation of W<sup>+</sup>machine is such that it first scans the initial square, writes the output symbol (0 or 1) on the square being scanned, moves one square to the right; and then again scans the square under the read-write head, writes the output symbol, moves one square to the right, and so on to the next state. An output sequence is constituted with symbols in squares to the left of read-write head (Figure 3).

Figure 3. A Read-Write Head and a Tape

In other words, the "next state" and next output symbol are determined by the "present state" and present input symbol of the machine. Hence, any set of input signal set that characterizes a finite automaton also characterizes a W-machine and vice versa. Every finite automaton with states is completely equivalent to a W-machine with not more than 10s+1 instructions, and every W-machine with b instructions differs from a finite automaton of not more than 2b+1 states by at most one unit of delay in the output. Like the situations encountered before in the discussion of regular expressions, the questions of equivalence of programs and that of finding an algorithm to minimize the number of individual instructions in any program also appear unanswered.

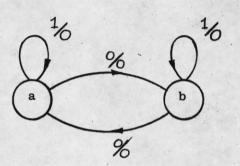

It is understandable that the techniques of characterizing sequential machines, by state diagrams or flow tables, by regular expressions (inputoutput sequences), or by programs of W-machine, are closely related to one another. These languages are readily translated from one form into include another.  $^{[64],[57],[73]}$  In synthesis, preference of selecting one over others depends on the type and size of machine and designer's taste. In view of this, it seems even at present moment, we are still lacking a sufficiently general and convenient method that would yield an adequate description of sequential machine specifications. In closing, let us illustrate the mentioned methods of characterizing machines by an example. Suppose the state diagram of a Mealy's model is given as shown in Figure 4.

Figure 4. A Two-State Mealy's Model

The state diagram can be transformed into a regular expression. [73]: 1\*0(01\*0)\*1\* (state "a" is assumed to be the initial state). Likewise, it can be transe. formed into a flow table or a program as shown in Figure 5 and Figure 6.

.....

-

\*\*

| State | Symbol  |        |  |

|-------|---------|--------|--|

| State | 0 -     | 1      |  |

| a     | -e.,+,b | e,+,a  |  |

| b     | e,+,a   | -m,+,b |  |

### Figure 5. Flow Table of Machine of Figure 4

| Addresses | Instructions    |

|-----------|-----------------|

| 1         | t(3)            |

| 2         | e,+,t(4)        |

| 3         | e,+,t(1),m,t(2) |

| 4         | m,+,t(4),m,t(1) |

Figure 6. Program of Machine of Figure 4

#### 4. ANALYSIS AND SYNTHESIS

#### 4.1 The Notion of Experiments

In problems of analysis and synthesis of finite automata, we often wish to learn the answers to some questions about the nature of the machine. In particular, topics concerning the initial and final states of a machine. the equivalence of states, the reduction of a machine to its reduced form and the equivalence of machines are of special practical and theoretical interest. Information about the condition of a machine can often be obtained by applying sequence(s) of inputs and observing the resulting outputs.<sup>[79]</sup> We shall call such a sequence of inputs I1, I2,..., If an experiment (of length  $\mathcal{J}$ ). Sometimes, an experiment (of length  $\mathcal{J}$ ) is also called a tape (of length b). For an incomplete machine, its output and next state are not defined for every input, we say that the machine has input restrictions. [8] Any experiment, which starting with the machine in state q<sub>i</sub>, violates no input restriction of state q, or any subsequent state, is called an acceptable experiment for state  $q_i$ . The acceptable experiments for a machine S(n,m,p) are the acceptable experiments for all n states of S. Clearly, any experiment is an acceptable experiment of a complete machine. Now we are ready to define some of the terms that were originated by E.F. Moore. A state q, of machine S is said to be indistinguishable from state q of machine T if and only if (1) every experiment acceptable for state  $q_i$  is also acceptable for state  $q_j$ and vice versa, and (2) every acceptable experiment performed on S starting in state q, produces the same output sequences as it would starting in q, State q is also said to be equivalent or compatible to state q. Similarly, a state q<sub>i</sub> of a machine S is <u>distinguishable</u> (<u>non-compatible</u>). from a state q<sub>i</sub> of a machine T if there exists an experiment of which the output sequence starting with machine S in state  $q_i$  differs from the output sequence starting with machine T in state q<sub>i</sub>. S and T, of course, may be the same machine. Furthermore, we said a machine S is distinguished if no two states in S are indistinguishable. Two machines S and T are said to be indistinguishable (or equivalent) if and only if for each state q<sub>i</sub> of S, there exists at least one equivalent state  $q_j$  of T, and for each state  $q_k$  of T, there exists at least one equivalent state q of S. Corresponding to each strongly connected

machine S, there is a machine T which has the following properties: (1) T is indistinguishable from S (2) T has a minimal number of states (3) no two states in T are equivalent, and (4) T is unique within permutations of relabeling of states. T is then called the <u>reduced form</u> of S.

The problem concerning length of experiments for determining the state is initiated by E.F. Moore. Although Moore dealt with input-independent complete machines, the results sometimes are applicable to the whole class of machines with minor changes.<sup>[76]</sup>, [22]

Moore investigated the lengths of experiments to distinguish states of sequential machine(s), and concluded that: (1) if  $S_{(n,m,p)}$  is an input independent distinguished complete machine, then any two states of S can be distinguished by an experiment of length n-1, and this bound can not be lowered, (2) if  $S_{(n,m,p)}$  and  $T_{(n,m,p)}$  are input-independent complete machines and some state  $q_i$  of S can be distinguished from state  $q_j$  of T, then they can be distinguished by an experiment of length 2n-1, which is also the lowest bound possible. C.C. Elgot and J.D. Rutledge<sup>[27]</sup> generalized Moore's result, (2) for machines having different number of internal states. That is, if S has n states and T has n' states, they showed that the bound in (2) becomes n'+n-2. This bound, however, does not appear to be the best one as one can readily check by letting n'=n.

Another kind of experiment of interest is the one which determines the (final) state of a machine upon receiving a sequence of inputs. This is also sometimes called <u>terminal state experiment</u><sup>[56]</sup> or <u>homing experiment</u>.<sup>[39]</sup> Moore has shown that for any input-independent machine  $S_{(n,m,p)}$  in which all n states are distinguishable, an experiment of length no more than  $\frac{n(n-1)}{2}$ is sufficient to determine the state of S at the end of the experiment. S. Ginsburg<sup>[41]</sup> considered a more general case. He defined that any experiment E, which is independent of the choice of an unknown state from a set A of admissible states of the machine as the initial state, to be a <u>uniform</u> <u>experiment</u> with respect to A. Then he estimated the length of uniform terminal state experiment to be  $\frac{1}{2}[n(k^2-k) + \frac{2k-k^3}{6}]$  for any set A of  $k \leq n$ states, and if k=n, the length is at most  $\frac{n(2n-1)(n-1)}{6}$ . At first, it seems rather important for us to notice that Moore assumed the machine initially was in an unknown initial state and the experiment performed was <u>potential</u> depending upon that particular state whereas Ginsburg considered experiments applied to a set of states. Consequently, we may raise the question: "Is it necessarily true that bounds on lengths of experiments be lower than that of uniform experiments?" To one's surprise, the answer is NO. As was shown by T.N. Hibbard, <sup>[56]</sup> the least upper bounds on the lengths of the two kinds of experiments were proved to be equal.

Hibbard defined the terms minimal experiment and minimal uniform experiment. If  $S_{(n,m,p)}$  is a machine and A is a subset of the set of states of S, then an experiment E for A is meant an experiment applied to each state in A. An experiment E for A is said to be minimal for A if the length of E is not greater than the length of any other experiment for A. A uniform experiment U for A is said to be minimal if the length of U is not greater than the length of any other uniform experiment for A. Hibbard concluded that for each distinguished complete machine S<sub>(n,m,p)</sub> and for each set A of k states of S,  $1 < k \leq n$ , if e(S,A) denotes the length of minimal terminal experiment for A and u(S,A) denotes the length of minimal uniform experiment for A, then

$Max\{e(S,A)|all S,A\} = Max\{u(S,A)|all S,A\} = \frac{(2n-k)(k-1)}{2}$  (4-1)

This result indicates that when k=n, the bound  $\frac{n(n-1)}{2}$  set up by Moore is in fact the best possible for complete machines in general.

In the case where  $S_{(n,m,p)}$  is input-independent, the bound is even lower:

$$Max\{e(S,A)|all S,A\} = Max\{u(S,A)|all S,A\} = \frac{(2n-k)(k-1)}{2} - (k-2)$$

(4-2)

Another problem of interest for sequential machine designers is to find the reduced form of a given machine. In the process of reducing the number of states of a machine to its minimum, compatible states play a pre-eminent role of removing redundancies.<sup>[61],[76]</sup> One of the necessary conditions for two states  $q_i$  and  $q_j$  to be compatible requires an inspection of all experiments that are acceptable to both  $q_i$  and  $q_j$ . This situation is indeed rather undesirable on account of the amount of labor involved. A possible way for improvement is to replace the phrase "inspection of all experiments" by "inspection of all experiments of length  $t \le k$ " where k is a positive integer. We are, then, dealing with the problem of finding the smallest integer k.

Ginsburg<sup>[42]</sup> pointed out that for two machines S and T with n and m states respectively, state  $q_i$  in S is compatible with state  $q_j$  of T if for each experiment E of length  $t \leq mn$ , which is acceptable to both  $q_i$  and  $q_j$ , the output sequences are identical, i.e.,  $\lambda_S(I_x, q_i) = \lambda_T(I_x, q_j)$ , for each  $E=I_1, I_2, \dots, I_x \dots I_t$  with  $1 \leq x \leq t$  and  $t \leq mn$ . Furthermore, this number mn can not be lowered. If S and T are the same machine, then mn is replaced by  $\frac{n(n-1)}{2}$  which is the same least upper bound on a state terminal experiment for a complete machine.

In the case where S and T are input-independent, C.Y. Lee<sup>[67]</sup> pointed out that the number t is upper bounded by mn-l but can not be lowered below mn-min. (m,n)+1. C.C. Elgot and J.D. Rutledge<sup>[27]</sup> indicated that the number mn-min. (n,m)+1 is in fact the least upper bound. The result was further strengthened by S. Ginsburg<sup>[50]</sup> who assumed that the number of states n of S is equal to or less than the number of states m of T, and proved the bound to be n(m-1)+1. A similar conclusion is also reached by M.O. Rabin and D. Scott.<sup>[89]</sup> They specified two machines S and T to be <u>equivalent</u> if the set of all tapes (experiments) accepted by S is equal to the set of all tapes accepted by T. An immediate result concerns the length of experiments which distinguishes two machines. If S and T are two machines with n and m states, S is not equivalent to T if and only if there exists an experiment of length t < mn which is accepted by S but not by T or vise versa.

Ginsburg<sup>[50</sup>] also indicated that the bound  $\frac{n(n-1)}{2}$  on the length of experiments for two states  $q_i$  and  $q_j$  of  $S_{(n,m,p)}$  to be compatible can be improved further if S is input-independent, that is, if  $S_{(n,m,p)}$  is input-independent,  $q_i$  and  $q_j$  in S are compatible if and only if for every experiment E, which is acceptable by both  $q_i$  and  $q_j$ , of length  $t \le k$ ; where  $k = \frac{n^2 - 2n}{4} + 1$  if n is odd, and  $k = \frac{n^2 - 2n + 1}{4} + 1$ , if n is even; the output sequences are identical.

As to the actual procedures for constructing experiments, a thorough discussion is taken up by Gill in his book <u>Introduction to the Theory of Finite</u> State Machines.<sup>[39]</sup> These results concerning bounds on length of experiments

may not yield instant application for machine simulation but the intrinsic concept of experiment performing certainly sets a guide to the analysis of properties of sequential machines. Some of the work still remains to be done in this area. Procedures for designing experiments to distinguish initial state or final state in a completely enumerational fashion and experiments to characterize and identify an unknown machine, and the possibility of applying concepts in this area to diagnosis of machines all deserve full attention.

#### 4.2 Decomposition of Machines

•

In view of the difficulties encountered in analysis and synthesis of complex finite state sequential machines, many properties of the <u>decomposition</u> of machines have been investigated.<sup>[37],[57],[108]</sup> If a machine can be decomposed into a number of smaller units, each of which is made of a simpler structure than the whole, the procedure of design, testing, troubleshooting and replacement can be greatly simplified. Decompositions are generally classified into three types of construction: cascade, parallel, and loopfree.

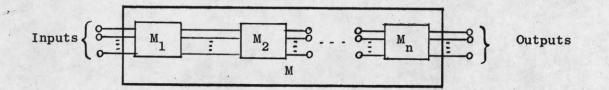

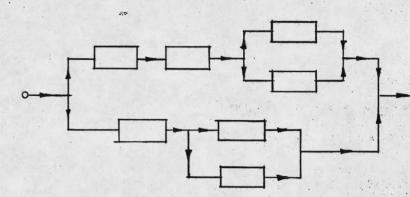

A machine M is called a <u>cascaded finite-state machine</u> <sup>[37]</sup> if it is constructed by cascading a finite number of machines  $M_1, M_2, \dots, M_n$  in series, (Figure 7).

#### Figure 7. Cascaded Finite-State Machine

Inputs of M are inputs of  $M_1$ , and outputs of M are that of  $M_i$ 's. The interconnections are such that outputs of  $M_i$  are identified with inputs of  $M_{i+1}$ , for  $1 \le i \le n-1$ . Several properties are apparent from this composition. If

$M_1, M_2, \ldots, M_n$  are machines with  $n_1, n_2, \ldots, n_n$  states, respectively, then M is a machine with n, .n, . n, .... .n, states. A machine with p states, where p is a prime number, is therefore not decomposable into simpler units unless some redundant states are added. If M is in reduced form, then every unit M. must necessarily be in reduced form also. Moreover, if one of the M. 's is not strongly connected, then M is not strongly connected. The decomposibility of a machine into two stages in cascade is discussed by Gill<sup>[37]</sup> and by Yoeli. Using connection matrix as a tool of analysis, Gill first defines a so-called n-m partition. The connection matrix [M] of a machine M with nom states is said to have a n-m partition if it can be partitioned into  $n^2$  m x m submatrices. Then the necessary condition for M to be decomposable into a m-state machine and an n-state machine in cascade is that an n-m partition must exist such that each row contains the same set of input symbols. This condition, however, is also sufficient as was pointed out by Hartmanis.<sup>[37]</sup> Yoeli uses the notion of transition graph (the conventional state diagram relative to a single input symbol) and properties of homomorphism between transition graphs to establish a necessary and sufficient condition for the decomposibility of M into two. A partition of state set of M is said to be admissible if it has the property that if any two states belong to the same class of partition, then their successors, relative to any input symbol, are again in the same class. In addition, an admissible partition is uniform if all classes contain the same number of states. A machine M then is said to be decomposible if and only if there exists a uniform admissible partition.

For a machine with  $m \cdot n$  states, there exists minimized partitions, the test for decomposibility is usually a laborious task. As an example, let us consider a 6-state machine<sup>[37]</sup> described by a connection matrix [M<sub>6</sub>] as:

|                   |     | _ 1        | 2     | 3     | 4     | 5 | 6     |   |

|-------------------|-----|------------|-------|-------|-------|---|-------|---|

|                   | 1   | 0          | 0     | (0/1) | 0     | 0 | (1/1) |   |

|                   | 2   | (0/1)      | 0     | (1/1) | Ο.    | 0 | 0     |   |

| [M <sub>6</sub> ] | = 3 | (0/1)      | 0     | (1/1) | 0     | 0 | 0     | Ľ |

|                   | . 4 | (1/1)      | 0     | (0/1) | . 0   | 0 | . 0   | 1 |

|                   | 5   | (1/1)<br>0 | (1/0) | 0     | (0/0) | 0 | 0     |   |

|                   | 6   | (1/1)      | (0/0) | 0     | 0     | 0 | 0     | 1 |

|                   |     |            |       |       |       |   | -     |   |

At first glance, whether  $[M_6]$  is decomposable is by no means obvious. After relabelling,  $[M_6]$  becomes  $[M_6']$  which is decomposable:

|              |        | 1.'   | 2'    | 3'    | 4'    | 5 * | 6'    |

|--------------|--------|-------|-------|-------|-------|-----|-------|

|              | 1'(=1) | Го    | (1/1) | 0     | (0/1) | 0   | 0     |

|              | 2'(=6) | (1/1) | 0     | 0     | 0     | 0:  | (0/0) |

| $[M'_{6}] =$ | 3'(=4) | (0/1) | 0     | 0     | (0/1) | 0   | 0     |

|              | 4'(=3) | (0/1) |       | 0     | (1/1) | 0   | . 0   |

|              | 5'(=5) | 0     | 0.    | (0/0) | 0     | 0   | (1/0) |

|              | 6'(=2) | (0/1) | 0     | 0     | (1/1) | 0   | 0     |

|              |        | -     |       |       |       |     |       |

Figure 8. Transition Graphs of  $M_6^{\prime}$

The partition states of  $M'_6$  into classes  $\{4',5',6'\}$  is clearly both admissible and uniform.

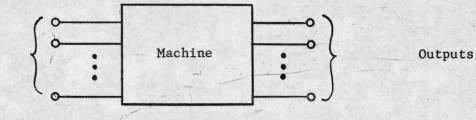

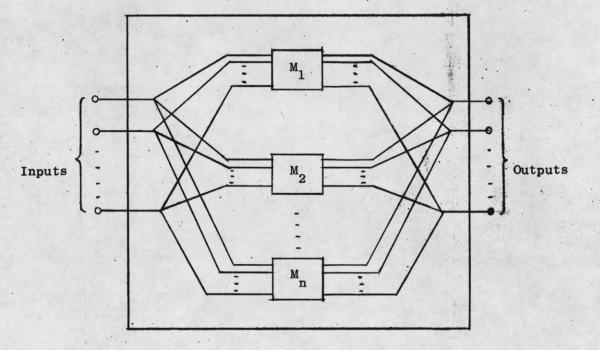

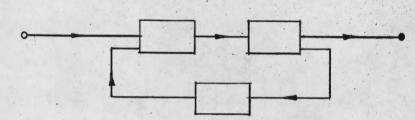

The decomposition of a sequential machine into several simpler ones operating in parallel was discussed by Hartmanis.<sup>[52]</sup> Each of the simpler machines operate on differently reduced information and the combination of these individual operations yields the desired results, (Figure 9). The decomposition of a complex operation into simpler operations carried out in parallel is also connected with the notion of partition. A partition II on the set

Figure 9. A Parallel Operating Machine

S is defined as a collection of disjoint subsets  $\{S_{\alpha}\}$  of S such that their union is S. Symbol 0 denotes the smallest partition on S in which each subset contains exactly a single element. Symbol I denotes the largest partition on S where the only subset is the set S itself. Suppose an operation \* is defined on the set S that a\*b is closed for any a,  $b \in S$ , we say a partition  $\Pi$  has the substitution property with respect to operation \* if A,B,C are disjoint subsets of S and a  $\in$  A, b  $\in$  B, a\*b=c  $\in$  C implies any other element a'  $\in$  A, b'  $\in$  B, then a'\*b' is also in C. The direct product of machine M, (with input set I,, state set  $S_1$ ) and machine  $M_2$  (with input set  $I_2$ , state set  $S_2$ ) is the machine M with input set equal to the cartesian product  $I_1 \times I_2$  and set of states  $S_1 \times S_2$ . Moreover, for given two partitions  $\Pi_1$  and  $\Pi_2$  on S, the partition  $\Pi_1 \circ \Pi_2$  means the set of all intersecting subsets due to  $\Pi_1$  and  $\Pi_2$ . Two sets U and V are chain connected if there exists a sequence of sets  $U=X_1, X_2, \cdots, X_n$  $X_n = V$  such that the intersection of  $X_i$  and  $X_{i+1}$  is not empty for  $1 \le i \le n-1$ . If A is a subset of partition of  $\Pi_1$ , by partition  $\Pi_1 + \Pi_2$  we mean the collection of subsets each of which contains A is the set union of all subsets of  $\Pi_1$  and  $\Pi_2$  which are chain connected to A. For example, if  $\Pi_1 = \{x; y; zw\}, \Pi_2 = \{xy, z\}$  then

$\Pi_1 \cdot \Pi_2 = \{x; y; z\}$  and  $\Pi_1 + \Pi_2 = \{xy; z, w\}$ . The necessary and sufficient condition for a machine M to be decomposable into two machines  $M_1$  and  $M_2$  whose direct product is isomorphic to M is then the existence of two nontrivial \*permutable partitions  $\Pi_1$  and  $\Pi_2$  with substitution properties for M such that:  $\Pi_1 + \Pi_2 = I$  and  $\Pi_1 \cdot \Pi_2 = 0$ . In another paper<sup>[54]</sup>, Hartmanis indicates that every loop-free realization of a sequential machine from n smaller machines corresponds to a set of n partitions  $\{\Pi_1 \cdot \Pi_2, \ldots, \Pi_n\}$  with the substitution property whose product is the zero partition 0;  $i_1 \cdot e_2$ ,  $\prod_{i=1}^n \Pi_{i=0}$ . By loop-free we mean that in a set of interconnected machines, no subset consisting of two or more machines forms a loop. Conversely, every such set of n partitions corresponds to a realization of the given machine from n smaller machines.

The significance of these results are shadowed by the fact that the authors use a state diagram as their starting point; nevertheless the concepts of decomposition may serve as stepping stones toward our ultimate goal of synthesis of sequential machines by means of interconnecting machines of less complexity and smaller sizes. Many problems remain unsolved, some even have not been formulated. The test of decomposability of course deserves improvement. An algorithmic procedure for the actual decomposition operation which is programmable on digital computers is also an immediate need. Problems of interconnecting machines to form various configurations, such as seriesparallel, loop with feedback (Figures 10,11) and the timing problem among each unit's inputs and outputs and their related properties likewise require: investigation.

Figure 10. An Example of Series-Parallel Interconnection of Machines

$<sup>\</sup>Pi_1$  and  $\Pi_2$  are permutable if any two blocks of A of  $\Pi_1$  and B of  $\Pi_2$  which are contained in the same block of  $\Pi_1 + \Pi_2$  have a nonempty intersection.

Figure 11. An Example of Interconnection of Machines with Loop Feedback

#### 4.3 On Machine Synthesis Techniques

Almost in every field of engineering science the task of design appears to be the most difficult one. A good engineering design often depends upon a careful application of formal procedures together with the ingenuity and experience of design engineers. This is of course no exception in the case of sequential machine synthesis. While a formal and compact procedure is still lacking, the present art of design relies heavily on the intuition and cleverness of the designer.

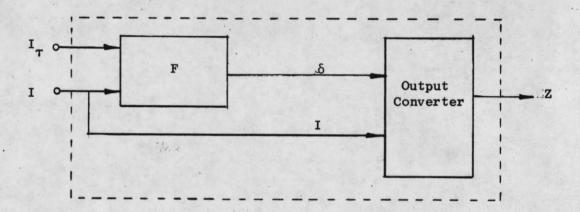

As pointed out previously, the first stumbling block encountered in sequential machine synthesis is the lack of a precise, formal and useful mathematical language to describe machine's desired function. Huffman's flowtable method, [61] Moore-Mealy's state diagram approach or the use of regular expressions prove to be powerful tools for small scale machines. With the design goal being emphasized on achieving reduced form machines, numerous problems on state-reduction<sup>[44]</sup> and state-assignment<sup>[53],[101]</sup> have been investigated. Aizeman, Gusev, Rozonoer, Smirnova and Tal<sup>[2]</sup> studied the reduction problem from a viewpoint of imposing restrictions on inputs. The most general case is the same as in Huffman's procedure in which no input restrictions are assumed, .t.e., all input sequences are permitted. If, however, a machine is only allowed to accept tapes in which successive repetitions of any input symbol do not occur in the input sequences, the number of states needed can be reduced relative to that when these input restrictions are removed. The machine is considered to consist of a "fast" automaton F which operates over fast cycles between input changes and an output converter, (Figure 12). If

we further restrict the successive inputs to the machine to be ordered pairs of the input alphabet  $\{I, I_{-}\}$ ,

Figure 12. A Machine Consisting of a Fast Automaton and an Output Converter

where  $I_T$  repeats the values of the I with a lag of  $T_T(\tau \text{ is the period of } F)$ , then the minimum number of states required is equal to the largest of  $\alpha_i$ , where  $\alpha_i$  is the number of distinct states  $Z_j$  into which each  $I_i$  transforms the automaton.

Generally speaking, the purpose of state-reduction is to remove redundant states in a primitive flow table or a state diagram. The well-known Huffman's state-merging technique is applicable only to complete machines. For machines that are not completely specified, the reduction problem is an exceedingly difficult one. At the present time no automatic procedure which generates the desired results without any enumeration is available. A partially enumerative procedure is given by Paull and Unger. [87] Although the procedure depends on the complexity of particular examples, it seems to be able to handle problems of moderate size. A more powerful technique has been developed by Ginsburg<sup>[42],[44]</sup> Part of his process is automatic and part of it depends on enumerating. The main disadvantage of Ginsburg's approach is that it is too "lengthy" to be useful to attack any practical problems since it is not programmable on a computer. Notion of state-reduction also bears a close relationship with the structure of a sequential machine. Sometimes the simplest realizations of a sequential machine can be destroyed by state reduction. [55] The necessary information flowneeded for realization of a machine word wheth as existing the stand

from smaller units may be disrupted by merging states. Hence a careful analysis on the structure of the machine should be made before we apply any reduction procedure.

By state-assignment we mean the assignment of codes to the internal states of sequential machine so as to obtain anceconomical logical realization. A practical and useful algorithm of state-assignment, which is applicable to both complete and incomplete machines, is described by Armstrong.<sup>[5]</sup> Although in some cases Armstrong's procedure will not attain truly economic realizations which are known to exist, it, however, has the superiority of being able to handle large problems, say machines with 100 states and 30 input symbols, with the aid of a digital computer. 'A somewhat different approach is taken by Hartmanis<sup>[53]</sup> and Stearns.<sup>[101]</sup> Their approach stresses upon the concept of assignments with reduced dependencies, i.e., each internal state variable at any time t depends only on a small subset of these variables at previous moment t-1 and on the input variables. The procedure may not always produce the most economical realization but the notions of <u>substitution property</u> and <u>partition pairs</u>, as defined in their papers, certainly play an important role in machine decompositions.

Apart from the flow-table method, there is Ginsburg's<sup>[45]</sup> technique by which a machine is synthesized from a set of finite input-output sequences. If input and output symbols are denoted by I and Z, respectively, then the set  $\sum = \{I_1^i, \ldots, I_{k(1)}^i; Z_1^i, \ldots, Z_{k(1)}^i; 1 \le i \le S, S \text{ is finite}\}$  is called a finite set of input-output sequences where superscripts denote the sequence number and subscripts denote the individual terms of the i<sup>th</sup> sequence. The procedure begins with finding a lower bound n on the number of states of a machine which can have the response required by certain input-output sequences. Then consider all such machines with n states. If none accepts all sequences in  $\sum_{i}$ , then consider all machines with n+l states, and then, if necessary, machines with n+2 states, ..., etc. Once such a machine is found, we are assured to have obtained a minimal machine. The result is profound but the amount of work that one has to do in carrying out this procedure is also tremendous if not impossible in a finite time.

AND A THE A MARK AND A

The synthesis technique of sequential machines from regular-expression languages was first described by McNaughton and Yamada.<sup>[73]</sup> Algorithms are

given for finding a state diagram corresponding to a regular expression and vice versa. A similar approach was discussed by Lee. [67] Lee shows that if the descriptions of flow-table (or its equivalent state diagram) for the machine realizing the regular expressions  $\alpha$  and  $\beta$  are known, then the flowtables corresponding to the regular expressions  $\alpha \vee \beta$ ,  $\alpha \circ \beta$  and  $\alpha^*$  can be constructed. Ultimately, the flow-tables of any regular expressions which are formed by applying operations "v", "." and "\*" a finite number of times on  $\alpha$  and  $\beta$  can also be constructed. Ott and Feinstein, [86] however, considered the problem from a somewhat different view point. They use the notion of socalled improper state diagram (ISD), which is simply the usual state diagram of a nondeterministic machine, [89] i.e., a machine that can be in any finite number of states simultaneously. They indicate that the occurrence of an event of any regular expressions can always be realized by a nondeterministic machine whose behavior is described by an improper state diagram; and for any improper state diagram, there exists an equivalent Mealy-type state diagram. Their construction method thus assures a realization for any given regular expression. The above mentioned results concerning synthesis techniques are, at this moment, only seen applications to small machines. For machines of reasonable size, say 20 feedback loops, the procedures become too complicated to handle.

#### 5. CONCLUSION

27

A brief study of the application of concepts of automata theory to analysis and synthesis of sequential machines has been made. The investigation was taken from an engineer's viewpoint and was by no means complete. After defining models of sequential machines, two ways of characterizing a machine, namely, the input-output signal set (or regular expression) method and the computer program method, were indicated. The discussion on analysis of machines was concentrated on experiment-performing, a way to examine a machine's structure by merely applying inputs and observing outputs; and machine decompositions. Lastly, some of the results and difficulties related to statereduction and state-assignment in machine synthesis procedures were mentioned.

#### REFERENCES

1.

2.

3.

7.

Aizerman, M.A., Gusev, L.A., Rozoner, L.I., Smirnova, I.M., and Tal, A.A., "Finite Automata", Automation and Remote Control, Part I, vol. 21, pp. 156-164, Oct.; Part 2, vol. 21, pp. 248-255, Nov. 1960. Review: IRE Trans. on Elec. Comp., vol. EC-10, p. 544, Sept. 1961.

(Some basic content and problems of theory of finite automata and possible ways of realizing finite automata are discussed.)

Aizeman, M.A., Gusev, L.A., Rozoner, L.I., Smirnova, I.M. and Tal, A.A., "On Methods for Realizing a Finite Automaton Whose Cyclical Nature is Determined by the Variation of the Input State", <u>Automation and Remote</u> <u>Control</u> (Automatika i Telemekhanika), vol. 21, pp. 1576-1594; 1960. Review: IRE Trans. on Elec. Comp., vol. EC-11, no. 3; June 1962.

(The paper studies 3 methods for an economical (in the sense of number of states) realization of a finite automaton specified by an equation (table), and operating in a cyclic manner determined by the variation in the states of its inputs.)

Aribib, M., "Turing Machines, Finite Automata and Neural Nets", J. Assoc. Comp., Mach., vol..8, no..4, pp. 467-475; Oct 1961.

(The author compares the notions of Turing machine, finite automaton and neural net and discusses theorems which are related to papers of Copi, Elgot and Wright; Rabin and Scott; and McCulloch and Pitts.)

4. Arden, D.N., "Delayed-Logic and Finite-State Machines", in <u>Switching</u> <u>Circuit Theory and Logical Design</u>, <u>Proc. of 2nd Annual Symp</u>., Detroit, <u>Mich.</u>, Oct.1961 and papers from the 1<sup>st</sup> Annual Symp., Chicago, Ill., Oct.1960, (published by AIEE, New York, N.Y.)

(Ancextension of Kleene's theory of neural nets and finite automata to the realization of sequential machines with delay elements. Two main results concerned with the relationships between the computational rate of devices of which the circuit is comprised, the complixity of the computation being performed by the circuit, and the delay in the circuit from the inputs to the outputs are described.)

Armstrong, D.B., "A Programmed Algorithm for Assigning Internal Codes to Sequential Machines", <u>IRE Trans. on Elec. Comp.</u>, vol EC-11, no. 4, pp. 466-473, Aug. 1962.

(A procedure for assigning codes to the internal states of a sequential machine which is applicable to both completely and incompletely specified states tables.)

- Ashenhurst, R.L., "The Decomposition of Switching Functions", Proc. Intnatl. Symp. Theory of Switching, Harvard Univ., Cambridge, Mass., Part 1, pp. 74-116; April 1957.

- Aufenkamp, D.D., "Analysis of Sequential Machines II", <u>IRE Trans. on</u> Elec. Comp., vol. EC-7, pp. 299-306; Dec. 1958.

- 8. Aufenkamp, D.D. and Hohn, F.E., "Analysis of Sequential Machines", IRE Trans. on Elec. Comp., vol. EC-6, pp. 276-285; Dec. 1957.

- Bartee, T.C., "Computer Design of Multiple-Output Logical Networks", <u>IRE Trans. on Elec.Comp.</u>, vol. EC-10, no. 1, March 1961, pp. 21-30. Review: <u>IRE Trans. on Elec. Comp.</u>, vol. EC-10, no. 3, Sept. 1961.

(Use of computer program to derive a set of minimal Boolean expressions)

describing a logical network with multiple outputs.) 10. Bellman, R., "Sequential Machines, Ambiguity and Dynamic Programming",

- J. Assoc. Comp. Mach., vol. 7, pp. 24-28, 1960.

- 11. Blokh, A. Sh., "Equivalent Transformations of Sequential Machines", (Avtomatika i Telemekhanika, vol. 21, no. 11, pp. 1490-1497, Nov. 1960) (translation: Automation and Remote Control, vol. 21, no. 11, May, 1961) Review: IRE Trans. on Elec. Comp., vol. EC-11, p. 94, Feb. 1962.

(The paper defines certain equivalent transformations of sequential machines and the corresponding structures of the machines.)

Brozozowski, J.A. and McClusky, E.J., "Signal Flow Graph Techniques for Sequential Circuit State Diagrams", U.S. Govt. Res. Rept., vol. 37, p. S-35(A); May 20, 1962.

(The application of signal flow graph techniques to the problem of characterizing sequential circuit state diagrams by regular expressions is discussed.)

Brozozowski, J.A., "A Survey of Regular Expressions and Their: Applications", <u>IRE Trans. on Elec. Comp.</u>, vol. EC-11, pp. 324-335; June 1962.

(The relation of regular expressions to sequential circuits is studied. Methods for constructing sequential circuits (state diagrams) from regular expressions and methods for obtaining a regular expression from a state diagram of a sequential circuit are discussed. Also mentioned are algebraic properties of regular expressions, and characteristics of improper state diagrams.)

Buchi, J.R., Elgot, C.C. and Holland, J.H., "Research in Automata Structure, Behavior and Design", College of Lit. and Arts, Michigan Univ., Ann Arbor, Mich., Final Report No. 2794-15-F; Nov. 1960.

(A summary of research on automata design algorithms in formal system of logic and theoretic computers with iterative structure and parallel action.)

15. Burks, A.W., "The Logic of Fixed and Growing Automata", Proc. Intnatl. Symp. on the Theory of Switching, April 2-5, 1957, in "The Annals of the Comput. Lab.", Harvard Univ., Cambridge, Mass., vol. 29, pp. 147-188; 1959. Review: IRE Trans on Elec. Comp., vol. EC-9, no. 4.; Dec. 1960.

(The main concern is discrete synchronous and deterministic computers.)

16. Burks, A.W., "Computation, Behavior, and Structure in Fixed and Growing Automata", Behavioral Sci., vol. 6, pp. 5-21; Jan. 1961.

(The theory of automata in relation to its internal behavior and the possibility of its being able to self-reproduce is discussed.)

17. Burks, A.W., Buchi, J.R., Elgot, C.C. and Wright, J.B., "Design Algorithms in Automata Languages", Dept. of Philosophy, Logic of Computers Group, Univ. of Michigan, Ann Arbor, Report No. 2755-11-F; July 1960.

(Reports on the design algorithms for automata languages.)

- Burks, A.W. and Copi, I.M., "The Logical Design of an Idealized General Purpose Computer", J. Franklin Inst., vol. 261, pp. 299-314 and 421-436; 1956.

- Burks, A.W. and Wang, H., "The Logic of Automata", J. Assoc. Comput. Mach., vol. 4, no. 2, pp. 193-218, no. 3, pp. 279-297; 1957. (The use of logical systems and techniques in analysis of the structure and behavior of automata.)

- 20. Burks, A.W. and J.B. Wright, "Theory of Logical Nets", Proc. IRE, vol. 41, no. 10, pp. 1357-1365, Oct. 1953.

(One of the first papers to apply rigorously two-valued logic to digital computer circuits. The idea of logical net along with "stroke element" and "delay element" are introduced. Sets of equations associated with various types - well-behaved, well-formed deterministic - of nets are discussed.)

21. Burks, A.W. and Wright, J.B., "Sequence Generators and Digital Computers", Univ. of Michigan, Rept. 03105-19-T, Feb. 1961.

(A generalization of the concepts of digital computers, finite automaton, logical net and other information-processing systems.)

22. Cadden, W.J., "Equivalent Sequential Circuits", IRE Trans. on Circuit Theory, vol. CT-6, pp. 30-34; 1959.

(The functional behavior of Moore's model and Mealy's model and Huffman's asynchronous machine are equivalent in the sense that one can be transformed into any other.)

- 23. Copi, I.M., Elgot, C.L. and Wright, J.B., "Realization of Events by Logical Nets", <u>J. Assoc. Comp. Mach.</u>, vol. 5, pp. 181-196; April 1958. (New formulation and new proofs of Kleene's work are presented. See Kleene (66).)

- 24. Curtis, H.A., "Multiple Reduction of Variable Dependency of Sequential Machines", J. Assoc. Comp. Mach., vol. 9, no. 3, pp. 324-345, July 1962.

- 25. Davis, A.S., "Markov Chains as Random Input Automata", Am. Math. Monthly, pp. 264-267, 1961.

26. Elgot, C.C., "Decision Problems of Finite Automata Design and Related Arithmetics", Trans. Am. Math. Soc., vol. 98, pp. 21-51; Jan. 1961.

(A class of problems concerning the existence of automata which produce specified mappings from input sets into output sets is considered in a formal manner.)

27. Elgot, C.C. and Rutledge, J.D., "Operations on Finite Automata", in Switching Circuit Theory and Logical Design", Proc. of Second Annual AIEE Symp., pp. 129-132; Sept. 1961.

(Unification of various points of view that have been adopted in the treatment of the synthesis of finite Automata.)

- 28. Elspas, B., "The Theory of Autonomous Linear Sequential Networks", <u>IRE Trans. on Circuit Theory</u>, vol. CT-6, pp. 45-60, 1959. (The relation between network logical structure and network sequential behavior is investigated.)

- 29. Fitch, F.B., "Representation of Sequential Circuits in Combinatory Logic", Phil. Sci., vol. 25, pp. 263-279, 1958.

- 30. Fleck, A.C., "Isomorphism Groups of Automata", J. Assoc. Comp. Mach., vol. 9, no. 4, pp. 469-476; Oct. 1962.

(Certain algebraic properties of automata and their relationship to the structure (properties of the next state function) of automata are discussed.)

31. Friedland, B., "Linear Modular Sequential Circuits", <u>IRE Trans. on</u> <u>Circuit Theory</u>, vol. CT-6, pp. 61-68, 1959.

(An extension of Huffman's concepts of synthesis and analysis of sequential circuits to the case when circuits comprise unit delays, modulo-p (p=prime) adders, and ideal amplifiers with integral values of gain < p.)

- 32. Friedman, J., "A Decision Procedure for Computations of Finite Automata", J. Assoc. Comp. Mach., vol. 9, no. 3, pp. 315-323; July 1962.

(A decision procedure to determine if two automata have the same computation.)

- 33. Ghiron, H., "Rules to Manipulate Regular Expressions of Finite Automata", <u>IRE Trans. on Elec. Comp</u>., vol. EC-11, no. 4, pp. 574-575, Aug. 1962.

(Some algebraic rules to manipulate regular expressions are presented.)

Gill, A., "Comparison of Finite-State Models", <u>IRE Trans. on Circuit</u> <u>Theory</u>, vol. CT-7, no. 2, pp. 178-179, June 1960.

(This note shows the "Moore Machine" and "Mealy Machine" are equivalent. Another paper is by Cadden, "Equivalent Sequential Machines".) 35. Gill, A., "Characterizing Experiments for Finite-Memory Binary Automata", <u>IRE Trans. on Elec. Comp.</u>, vol. EC-9, no. 4, pp. 469-471; Dec. 1960.

(Discuss properties and construction of "experiments" which determine the characteristics of a discrete automata with a finite memory.

36. Gill, A., "State-Identification Experiments in Finite Automata", Information and Control, vol. 4, pp. 132-154, 1961. Review: IRE Trans. on Elec. Comp., vol. EC-11, p. 584, Aug. 1962.

(A procedure for the construction of experiments to determine (1) initial state (2) terminal state of a machine.)

37. Gill, A., "Cascaded Finite-State Machines", <u>IRE Trans. on Elec. Comp.</u>, vol. EC-10, pp. 366-370, Sept. 1961. Review: <u>IRE Trans. on Elec. Comp.</u>, vol. EC-11, p. 94, Feb. 1962.

(A necessary condition is established for a machine to be decomposable into two machines in cascade.)

38. Gill, A., "A Note on Moore's Distinguishability Theorem", <u>IRE Trans.</u> on Elec. Comp., vol. EC-10, pp. 290-291, 1961.

(The Moore's theorem on length of minimal experiment which distinghishes states of two machines is improved.)

- 39. Gill, A., Introduction to the Theory of Finite-State Machines, McGraw-Hill Book Company, Inc., 1962.

- 40. Gillespie, R.G. and Aufenkamp, D.D., "On the Analysis of Sequential Machines", IRE Trans. on Electronic Computers, vol. EC-7, pp. 119-122; June 1958.

- 41. Ginsburg, S., "On the Length of the Smallest Uniform Experiment which Distinghishes the Terminal States of a Machine", J. Assoc. Comp. Mach. vol. 5, no. 3, pp. 266-280; July 1958.

(A bound is established on the length of minimal uniform experiment which determines the terminal state of a machine.)

- 42. Ginsburg, S., "On the Reduction of Superflous States in a Sequential Machine", J. Assoc. Comp. Mach., vol. 6, pp. 259-282; 1959.

- 43. Ginsburg, S., "A Synthesis Technique for Minimal-State Sequential Machines", <u>IRE Trans. on Elec. Comp</u>., vol. EC-8, pp. 13-24; 1959.

(A synthesis technique for minimal state sequential machines from a set of input-output sequences.)

- 44. Ginsburg, S., "A Technique for the Reduction of a Given Machine to a Minimal-State Machine", <u>IRE Trans. on Elec. Comp</u>., vol. EC-8, pp. 346-355; 1959.

- 45. Ginsburg, S., "Synthesis of Minimal-State Machines", <u>IRE Trans. on Elec.</u> Comp., vol. EC-8, pp. 441-449; 1959.

Ginsburg, S., "Connective Properties Preserved in Minimal-State Machines", J. Assoc. Comp. Mach., vol. 7, pp. 311-325; 1960.

(The design of a sequential machine and the properties of the connectives in the minimal state machine are discussed.)

47. Ginsburg, S., "Some Remarks on Abstract Machines", Trans. Am. Math. Soc., vol. 96, pp. 400-444; Sept. 1960.

(The abstract concept of Quasi-machine and related properties are introduced.)

- 48. Ginsburg, S., "Sets of Tapes Accepted by Different Types of Automata", J. Assoc. Comp. Mach., vol. 8, pp. 81-86; Jan. 1961.

(A number of different types of one-way automata and their family relationship are presented.)

- 49. Ginsburg, S., "A Comparison of the Work Done by Generalized Sequential Machines and Turing Machines", Tech. Memo. TM-604, pp. 1-16; March 1961.

- 50. Ginsburg, S., "Compatibility of States in Input-Independent Machines", J. Assoc. Comp., Mach., vol. 8, no. 3, pp. 400-404; July 1961.

(To find, for a certain class of machines, the smallest integer K having the property that, if two given states do non-contradictory work for all tapes of length less than or equal to K, these two states do noncontradictory work for all tapes for any length.)

- 51. Ginsburg, S., "Examples of Abstract Machines", <u>IRE Trans. on Elec. Comp.</u>, vol. EC-11, pp. 132-135; April 1962. Review: <u>IRE Trans. on Elec. Comp.</u>, vol. EC-11, pp. 721-722; Oct. 1962.

- 52. Hartmanis, J., "Symbolic Analysis of a Decomposition of Information Processing Machines", <u>Information and Control</u>, vol. 3, pp. 154-178; 1960.

(The study of decomposing (replacing) a complex finite state sequential machine by several simpler ones which operate in parallel and yield the same result.)

- 53. Hartmanis, J., "On the State Assignment Problem for Sequential Machines, I", <u>IRE Trans. on Elec. Comp.</u>, vol. EC-10, no. 2, pp. 157-164; June 1961. (A method for assigning internal states of a sequential machine is presented.)

- 54. Hartmanis, J., "Loop-Free Structure of Sequential Machines", Information and Control, vol. 5, pp. 25-43; 1962.

(With the properties of partitions with substitution and partition pairs, the author studies the realization of sequential machines from several smaller machines.) 55. Hartmanis, J. and Stearns, R.E., "Some Dangers in State Reduction of Sequential Machines", <u>Information and Control</u>, vol. 5, pp. 252-260; Sept. 1962.

(Reduction by merging states sometimes disrupted the systematic information flow in the unreduced machines and can destroy the simplest realizations of a sequential machine.

56. Hibbard, T.N., "Least Upper Bounds on Minimal Terminal State Experiments for Two Classes of Sequential Machines", <u>J. Assoc. Compt. Mach.</u>, vol. 8, no. 4, pp. 601-612; Oct. 1961.

(For a machine of n distinguished states, an experiment of length  $\frac{n(n-1)}{2}$  is the best possible bound to determine the state of this machine. For input independent machines, the bound is even lowered.)

57. Hohn, F.E., Seshu, S., and Aufenkamp, D.D., "The Theory of Nets", <u>IRE</u> Trans. on Elec. Comp., vol. EC-6, pp. 154-161; Sept. 1957.

(A unifying concept of a net is used as background for the theory of sequential machines.)

58, Holland, J.H., "Iterative Circuit Computers", Proc. Western Joint Conf., San Francisco, Calif., May 3-5, 1960; pp. 259-266.

(Mathematical characterizations for a given condition are related to a program which will establish a theory of adaptive system towards a concept of automaton generators.)

59. Holland, J.H., "A Universal Computer Capable of Executing an Arbitrary Number of Sub-Programs Simultaneously", Proc. 1959 Eastern Joint Computer Conf., Boston, Mass., Dec. 1-3, 1959; pp. 108-113.

(A universal computer which has iterative circuits and whose structure and behavior can be formulated in a manner which will provide a formal basis for a theoretical study of automata with changing structure.)

60. Holland, J.H., "Cycles in Logical Nets", J. of Franklin Institute, vol. 270, no. 3, pp. 202-226; Sept. 1960. Review: <u>IRE Trans. on</u> Elec. Comp., vol. EC-10, no. 2; June 1961.