O2016 Ahmed Mostafa Elkholy

#### DIGITAL ENHANCEMENT TECHNIQUES FOR FRACTIONAL-N FREQUENCY SYNTHESIZERS

BY

#### AHMED MOSTAFA ELKHOLY

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2016

Urbana, Illinois

Doctoral Committee:

Associate Professor Pavan Kumar Hanumolu, Chair Professor Elyse Rosenbaum Professor Pramod Viswanath Assistant Professor Robert Pilawa-Podgurski

## ABSTRACT

Meeting the demand for unprecedented connectivity in the era of internet-of-things (IoT) requires extremely energy efficient operation of IoT nodes to extend battery life. Managing the data traffic generated by trillions of such nodes also puts severe energy constraints on the data centers. Clock generators that are essential elements in these systems consume significant power and therefore must be optimized for low power and high performance. The focus of this thesis is on improving the energy efficiency of frequency synthesizers and clocking modules by exploring design techniques at both the architectural and circuit levels.

In the first part of this work, a digital fractional-N phase locked loop (FNPLL) that employs a high resolution time-to-digital converter (TDC) and a truly  $\Delta\Sigma$  fractional divider to achieve low in-band noise with a wide bandwidth is presented. The fractional divider employs a digital-to-time converter (DTC) to cancel out  $\Delta\Sigma$  quantization noise in time domain, thus alleviating TDC dynamic range requirements. The proposed digital architecture adopts a narrow range low-power time-amplifier based TDC (TA-TDC) to achieve sub 1ps resolution. Fabricated in 65nm CMOS process, the prototype PLL achieves better than -106dBc/Hz in-band noise and 3MHz PLL bandwidth at 4.5GHz output frequency using 50MHz reference. The PLL achieves excellent jitter performance of 490fs<sub>rms</sub>, while consumes only 3.7mW. This translates to the best reported jitter-power figure-of-merit (FoM<sub>J</sub>) of -240.5dB among previously reported FNPLLs.

Phase noise performance of ring oscillator based digital FNPLLs is severely compromised by conflicting bandwidth requirements to simultaneously suppress oscillator phase and quantization noise introduced by the TDC,  $\Delta\Sigma$  fractional divider, and digital-to-analog converter (DAC). As a consequence, their FoM<sub>J</sub> that quantifies the power-jitter tradeoff is at least 25dB worse than their LC-oscillator based FNPLL counterparts. In the second part of this thesis, we seek to close this performance gap by extending PLL bandwidth using quantization noise cancellation techniques and by employing a dual-path digital loop filter to suppress the detrimental impact of DAC quantization noise. A prototype was implemented in a 65nm CMOS process operating over a wide frequency range of 2.0GHz-5.5GHz using a modified extended range multi-modulus divider with seamless switching. The proposed digital FNPLL achieves  $1.9ps_{rms}$  integrated jitter while consuming only 4mW at 5GHz output. The measured inband phase noise is better than -96 dBc/Hz at 1MHz offset. The proposed FNPLL achieves wide bandwidth up to 6MHz using a 50 MHz reference and its FoM<sub>J</sub> is -228.5dB, which is at about 20dB better than previously reported ring-based digital FNPLLs.

In the third part, we propose a new multi-output clock generator architecture using open loop fractional dividers for system-on-chip (SoC) platforms. Modern multi-core processors use per core clocking, where each core runs at its own speed. The core frequency can be changed dynamically to optimize for performance or power dissipation using a dynamic frequency scaling (DFS) technique. Fast frequency switching is highly desirable as long as it does not interrupt code execution; therefore it requires smooth frequency transitions with no undershoots. The second main requirement in processor clocking is the capability of spread spectrum frequency modulation. By spreading the clock energy across a wide bandwidth, the electromagnetic interference (EMI) is dramatically reduced. A conventional PLL clock generation approach suffers from a slow frequency settling and limited spread spectrum modulation capabilities. The proposed open loop fractional divider architecture overcomes the bandwidth limitation in fractional-N PLLs. The fractional divider switches the output frequency instantaneously and provides an excellent spread spectrum performance, where precise and programmable modulation depth and frequency can be applied to satisfy different EMI requirements. The fractional divider has unlimited modulation bandwidth resulting in spread spectrum modulation with no filtering, unlike fractional-N PLL; consequently it achieves higher EMI reduction. A prototype fractional divider was implemented in a 65nm CMOS process, where the measured peak-to-peak jitter is less than 27ps over a wide frequency range from 20MHz to 1GHz. The total power consumption is about 3.2mW for 1GHz output frequency. The all-digital implementation of the divider occupies the smallest area of 0.017 mm<sup>2</sup> compared to state-of-the-art designs.

As the data rate of serial links goes higher, the jitter requirements of the clock generator become more stringent. Improving the jitter performance of conventional PLLs to less than  $(200 \text{fs}_{\text{rms}})$  always comes with a large power penalty (tens of mWs). This is due to the PLL coupled noise bandwidth trade-off, which imposes stringent noise requirements on the oscillator and/or loop components. Alternatively, an injection-locked clock multiplier (ILCM) provides many advantages in terms of phase noise, power, and area compared to classical PLLs, but they suffer from a narrow lock-in range and a high sensitivity to PVT variations especially at a large multiplication factor (N). In the fourth part of this thesis, a low-jitter, low-power LC-based ILCM with a digital frequency-tracking loop (FTL) is presented. The proposed FTL relies on a new pulse gating technique to continuously tune the oscillator's free-running frequency. The FTL ensures robust operation across PVT variations and resolves the race condition existing in injection locked PLLs by decoupling frequency tuning from the injection path. As a result, the phase locking condition is only determined by the injection path. This work also introduces an accurate theoretical large-signal analysis for phase domain response (PDR) of injection locked oscillators (ILOs). The proposed PDR analysis captures the asymmetric nature of ILO's lock-in range, and the impact of frequency error on injection strength and phase noise performance. The proposed architecture and analysis are demonstrated by a prototype fabricated in 65 nm CMOS process with active area of 0.25 mm<sup>2</sup>. The prototype ILCM multiplies the reference frequency by 64 to generate an output clock in the range of 6.75GHz-8.25GHz. A superior jitter performance of 190fs<sub>rms</sub> is achieved, while consuming only 2.25 mW power. This translates to a best FoM<sub>J</sub> of -251 dB.

Unlike conventional PLLs, ILCMs have been fundamentally limited to only integer-N operation and cannot synthesize fractional-N frequencies. In the last part of this thesis, we extend the merits of ILCMs to fractional-N and overcome this fundamental limitation. We employ DTC-based QNC techniques in order to align injected pulses to the oscillator's zero crossings, which enables it to pull the oscillator toward phase lock, thus realizing a fractional-N ILCM. Fabricated in 65nm CMOS process, a prototype 20-bit fractional-N ILCM with an output range of 6.75GHz-8.25GHz consumes only 3.25mW. It achieves excellent jitter performance of 110fs<sub>rms</sub> and 175fs<sub>rms</sub> in integer- and fractional-N modes respectively, which translates to the best-reported FoM<sub>J</sub> in both integer- (-255dB) and fractional-N (-252dB) modes. The proposed fractional-N ILCM also features the first-reported rapid on/off capability, where the transient absolute jitter performance at wake-up is bounded below 4ps after less than 4ns. This demonstrates almost instantaneous phase settling. This unique capability enables tremendous energy saving by turning on the clock multiplier only when needed. This energy proportional operation leverages idle times to save power at the system-level of wireline and wireless transceivers. To my parents, my wife, my beloved kids: Nour and Omar.

## ACKNOWLEDGMENTS

#### All gratitude to Allah

Pursuing my doctoral degree was mainly motivated by a genuine passion for research and innovation. During this long journey of dedication to accomplish world-class research contributions, I gained more insight and better understanding of many aspects of life, and I acquired invaluable skills and qualities personally and professionally. This was made possible only with the unconditional support and help that I have received from my family, friends, and colleagues. For that, I would like to thank all the people who made my Ph.D. journey enjoyable and such a pleasant experience.

First and foremost, I would not reach this moment of achievement without the unlimited support of my advisor and close friend Professor Pavan Kumar Hanumolu. I really could not imagine a better advisor for me specifically or for anyone else in general. I still remember the first day of my graduate school and meeting with Professor Hanumolu; I instantly felt attached to his wonderful personality and way of thinking. I am profoundly grateful to him for his excellent guidance, support, encouragement, and caring. I feel very fortunate to work under his supervision and be one of his group members over the course of my Ph.D. study. He always believed in my capabilities, pushed me to be better and to accomplish the impossible. I learned a lot from him in all aspects of problem-solving, teaching, writing, or presenting, where he is always committed to a very high standard. I enjoyed talking to him almost daily to discuss research problems and delve into new ideas. We constantly had gorgeous coffee trips that involved sharing experiences, giving advice, and discussions of all kinds. I am very thankful for his generosity, kindness, and genuine care.

I would like to thank Professor Elyse Rosenbaum, Professor Pramod Viswanath, and

Professor Robert Pilawa-Podgurski for being on my committee and for providing me with their kind comments. I also wish to thank Professor Stephen Levinson. I learned a lot from him, and I enjoyed listening to his experiences, stories and jokes that he tells during the classes. I am very thankful to Rachel Palmisano and Jeni Summers for their help in purchase orders, conference registrations, and many reimbursement forms, Jamie Hutchinson for editing my dissertation, and all the ECE staff members for their support.

I cannot imagine my tenure as a graduate student would have been as adorable and as enjoyable without the backing of my beloved friends. I would like to especially thank Saurabh Saxena, Guanghua Shu, Mrunmay Talegaonkar, Romesh Nandwana, Woo-Seok Choi, Tejasvi Anand, and Seong-Joong Kim. They were my officemates, my teammates, and my amicable friends. I have learned many things from them on the technical and personal levels, and we had many tape-outs together and shared unforgettable experiences. I will always be thankful for all of them. I also want to thank my group friends and colleagues Brian Young, Sachin Rao, Praveen Prabha, Karthikeyan Reddy, Ahmed Safwat Elmallah, Timir Nandi, Mostafa Gamal Ahmed, Dongwook Kim, Junheng Charlie Zhu, Daniel Coombs, Braedon Salz, Da Wei, Amr Khashaba, and Karim Megawer. I enjoyed interacting with Hariprasath Venkatram, Manideep Gande, Guan-Lin Su, Mingu Kang, and Peter Kairouz. I would like to thank also my friends at UIUC Mohamed Rashad, Ahmed Adel, Ayman Halabya, Marwan Alian, Amir Ayman, Ahmed Nabwaey, Ahmed Zafer, Moatassem Abdallah, Hatem Ibrahim, Amr Abdeen, Hazem Hossam, Ahmed Baghdady, and Sherif Abdo.

I am very thankful also to Amr Elshazly for friendship and for welcoming me during my first year. He has been my mentor and closest friend since I started my Ph.D. journey. I feel greatly indebted for his valuable advice and recommendations whether it is research, or personal. He is always there when I need him no matter what. I am fortunate to have him as my mentor, and I thank him from the bottom of my heart.

I would like to thank my mother, Nagwa Elnaggar, profoundly. She devoted her life to my brother and me. She always stands by me whenever I need her. She is my resort and savior in the darkest moments. Her genuine caring and unconditional support drive my life forward to achieve the impossible. I am deeply grateful to my father, Professor Mostafa Elkholy. He profoundly raised me to be the man I am today. Since my early childhood, he taught me how to play chess, instilled the sense of engineering, and taught me that giving up is not an option. His appreciation of science and knowledge triggered early-on my passion to research and continue learning. He always encourages me to do my best and commit to excellence. I would also like to thank my brother, Mohamed, for his love and friendship. I learned a lot from him over the course of my life, where we were almost inseparable in school, university, work, and even in our Ph.D. journeys here in the US. I am deeply grateful to my grandmother, Amina, who passed away just before I started my Ph.D. She was my hero, my safe haven, who I wanted to make the most proud of me.

Finally, but immensely, I would like to thank my adorable wife, Aya. She provided me with all the love, tenderness, and compassion I need. We started this journey together, and I really appreciate her precious support and help, in all the time of research and writing of this thesis. She endured unbearable responsibilities of our two gorgeous kids. Without her sacrifice and patience, I would not have accomplished this work.

# TABLE OF CONTENTS

| LIST O | F TABLES                                                   | xii  |

|--------|------------------------------------------------------------|------|

| LIST O | F FIGURES                                                  | xiii |

| CHAPT  | TER 1 INTRODUCTION                                         | 1    |

| 1.1    | Frequency Synthesizers Applications                        | 3    |

| 1.2    | Frequency Synthesizers Architectures                       | 5    |

| 1.3    | Dissertation Organization                                  | 11   |

| CHAPT  | TER 2 LOW POWER LC-BASED DIGITAL FRACTIONAL-N PLL          | 13   |

| 2.1    | Introduction                                               | 13   |

| 2.2    | TDC- and DTC-based Digital Fractional-N PLLs               | 16   |

| 2.3    | Proposed Wide-Bandwidth Digital FNPLL Architecture         | 19   |

| 2.4    | Building Blocks                                            | 27   |

| 2.5    | Measurement Results                                        | 35   |

| 2.6    | Conclusion                                                 | 41   |

| CHAPT  | TER 3 A 2.0-5.5 GHZ RING-BASED DIGITAL FNPLL WITH EXTENDED |      |

| RAI    | NGE MMD                                                    | 43   |

| 3.1    | Introduction                                               | 43   |

| 3.2    | Ring-Based Digital FNPLL Design Tradeoffs                  | 46   |

| 3.3    | Proposed Digital FNPLL Architecture                        | 49   |

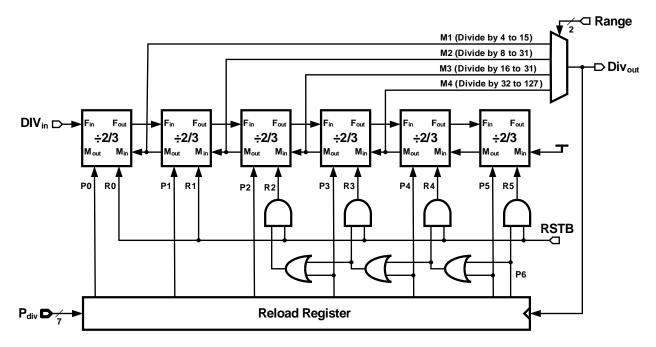

| 3.4    | Extended Range Multi-Modulus Divider (MMD)                 | 54   |

| 3.5    | Building Blocks                                            | 61   |

| 3.6    | Measurement Results                                        | 64   |

| 3.7    | Conclusion                                                 | 67   |

| CHAPT  | TER 4 LOW JITTER OPEN LOOP FRACTIONAL DIVIDERS             | 72   |

| 4.1    | Introduction                                               | 72   |

| 4.2    | Open Loop Fractional Synthesis                             | 74   |

| 4.3    | Building Blocks                                            | 81   |

| 4.4    | Measurement Results                                        | 83   |

| 4.5    | Conclusion                                                 |      |

| CHAPT | TER 5       INJECTION-LOCKED CLOCK MULTIPLIERS WITH FREQUENCY                                                                                       |    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| TRA   | ACKING LOOP                                                                                                                                         | 94 |

| 5.1   | Introduction                                                                                                                                        | 94 |

| 5.2   | Injection-Locked Clock Multiplication                                                                                                               | 97 |

| 5.3   |                                                                                                                                                     | 00 |

| 5.4   | Building Blocks                                                                                                                                     | 12 |

| 5.5   | Measurement Results                                                                                                                                 | 15 |

| 5.6   | Conclusion                                                                                                                                          | 21 |

| СНАРТ | ER 6 RAPID ON/OFF FRACTIONAL-N INJECTION-LOCKED CLOCK                                                                                               |    |

| MUI   | $ TIPLIERS \dots \dots$                       | 25 |

| 6.1   | Introduction $\ldots \ldots \ldots$ | 25 |

| 6.2   | Fractional-N Operation of ILCM                                                                                                                      | 28 |

| 6.3   | Rapid On/Off ILCM 13                                                                                                                                | 37 |

| 6.4   | Building Blocks                                                                                                                                     | 39 |

| 6.5   | Measurement Results                                                                                                                                 | 41 |

| 6.6   | Conclusion                                                                                                                                          | 44 |

| СНАРТ | TER 7 CONCLUSION                                                                                                                                    | 52 |

| REFER | ENCES                                                                                                                                               | 56 |

# LIST OF TABLES

| *                                            |                         |

|----------------------------------------------|-------------------------|

| Ring-based Digital FNPLL Performance Summary | 68                      |

| Fractional Divider Performance Summary       | 90                      |

| ILCM Performance Summary                     | 122                     |

|                                              |                         |

|                                              | TDC Performance Summary |

# LIST OF FIGURES

| 1.1  | Applications of clock generators in the era of internet of thinks (IoT)               | 2  |

|------|---------------------------------------------------------------------------------------|----|

| 1.2  | Block diagram of a serial link with embedded clocking.                                | 2  |

| 1.3  | Block diagram of a typical wireless transceiver.                                      | 3  |

| 1.4  | The role of frequency synthesizer in wireless transceivers illustrating the           |    |

|      | impact of its phase noise and spurious tones                                          | 4  |

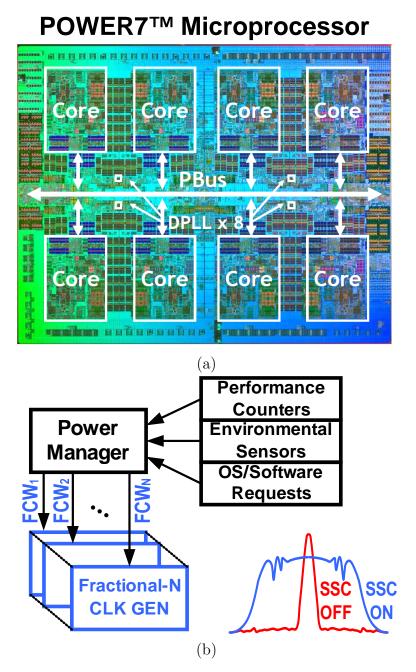

| 1.5  | (a) Die photo of an eight-core POWER7 microprocessor using per-core                   |    |

|      | clocking [1]. (b) Simplified block diagram of microprocessor frequency control.       | 6  |

| 1.6  | Simplified block diagram of integer-N charge pump PLL.                                | 7  |

| 1.7  | Linear model of charge pump PLL.                                                      | 8  |

| 1.8  | Simplified block diagram of analog FNPLL.                                             | 9  |

| 1.9  | Timing diagrams illustrating the fractional divider operation                         | 9  |

| 1.10 | Simplified block diagram of analog FNPLL with QNC.                                    | 10 |

| 2.1  | Block diagram of conventional digital FNPLL implementation using (a)                  |    |

|      | counter-based divider-less architecture, and (b) $\Delta\Sigma$ fractional divider    | 15 |

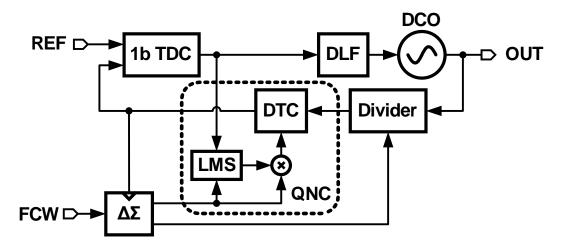

| 2.2  | Digital FNPLL architecture with $\Delta\Sigma$ quantization noise cancellation (QNC). | 16 |

| 2.3  | A DTC-based bang-bang phase detector (BBPD) digital FNPLL imple-                      |    |

|      | mentation.                                                                            | 18 |

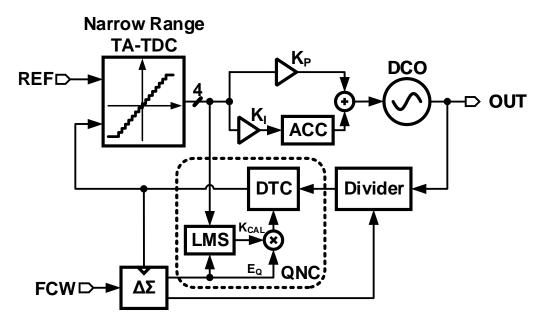

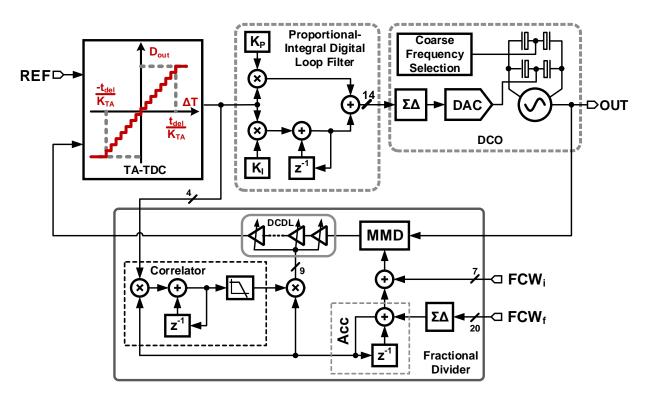

| 2.4  | Block diagram of the proposed digital FNPLL                                           | 21 |

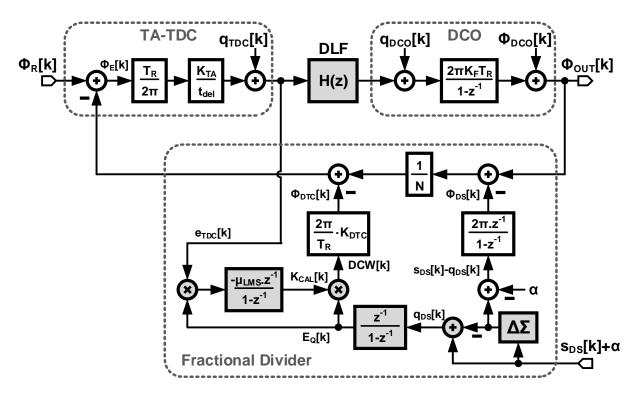

| 2.5  | Simplified discrete-time linear phase-domain model of the FNPLL                       | 23 |

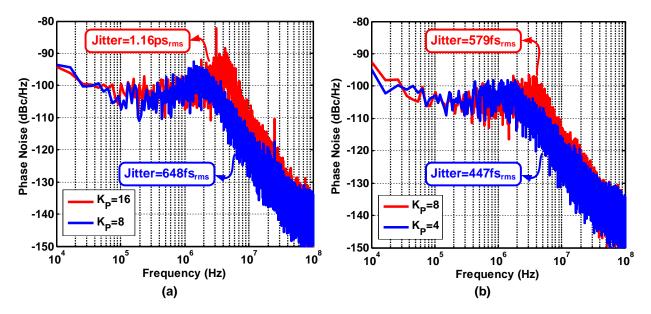

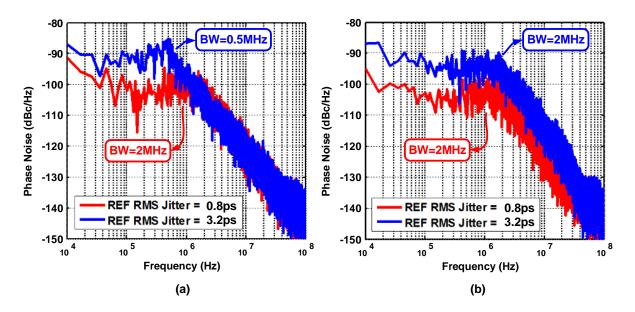

| 2.6  | Simulated output phase-noise spectrum, 5.003GHz output using 50MHz                    |    |

|      | reference, with different proportional gain settings for (a) conventional             |    |

|      | BBPD, and (b) proposed narrow range TA-TDC                                            | 26 |

| 2.7  | Simulated output phase-noise spectrum, 5.003GHz output using 50MHz                    |    |

|      | reference, with different reference noise jitter for (a) conventional BBPD,           |    |

|      | and (b) proposed narrow range TA-TDC                                                  | 26 |

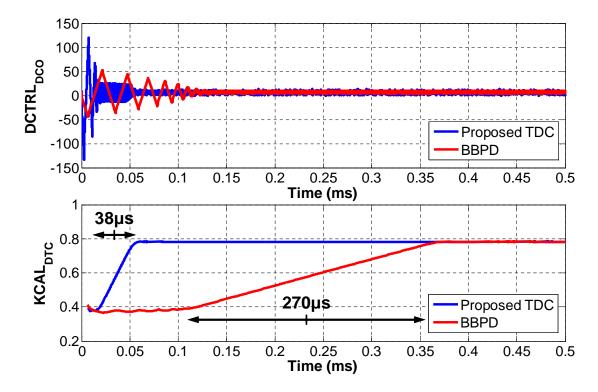

| 2.8  | Simulated settling behavior of (a) DCO control word and, (b) DTC cali-                |    |

|      | bration factor.                                                                       | 27 |

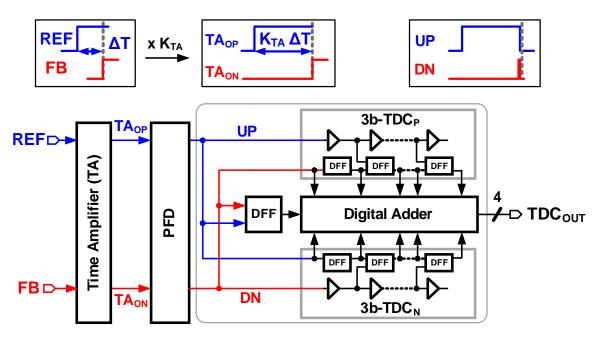

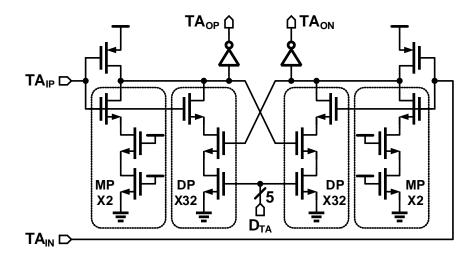

| 2.9  | Bock diagram of the proposed narrow range time-amplifier based TDC                    | 28 |

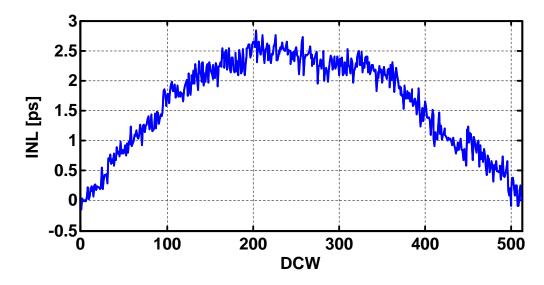

| 2.10 |                                                                                       | 29 |

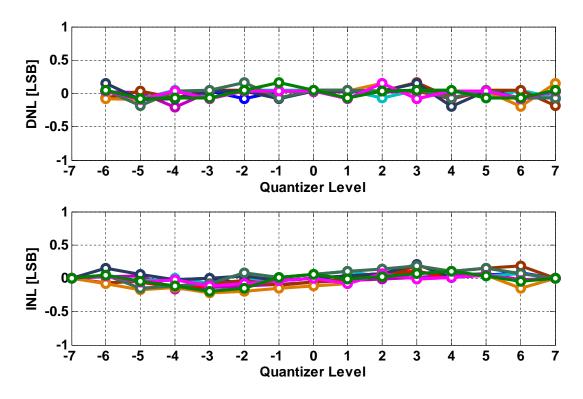

| 2.11 | Monte-Carlo post-layout simulated DNL and INL of TA-TDC: DNL [0.2LSB]                 |    |

|      | and INL [0.25LSB]                                                                     | 30 |

|      | LC-based DCO implementation.                                                          | 32 |

| 2.13 | Proposed truly fractional divider.                                                    | 33 |

|      |                                                                                       |    |

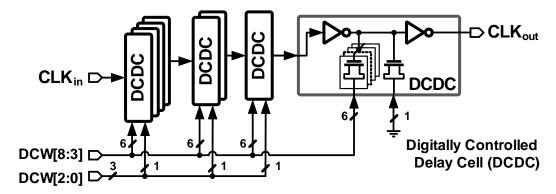

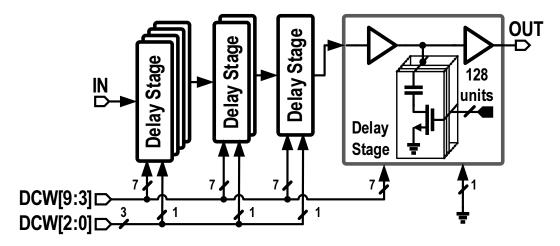

| 2.14       | The 9-bit digitally controlled delay line (DCDL) block diagram.                                        | 34         |

|------------|--------------------------------------------------------------------------------------------------------|------------|

| 2.15       | Post-layout Monte-Carlo simulations for the DCDL integral nonlinearity (INL).                          | 34         |

| 2.16       | Detailed block diagram of the proposed digital FNPLL                                                   | 35         |

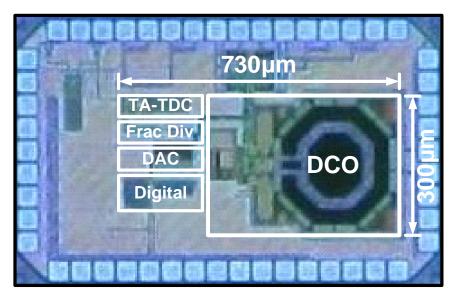

| 2.17       | Die photograph.                                                                                        | 36         |

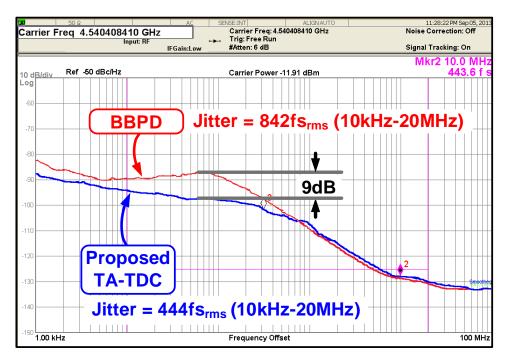

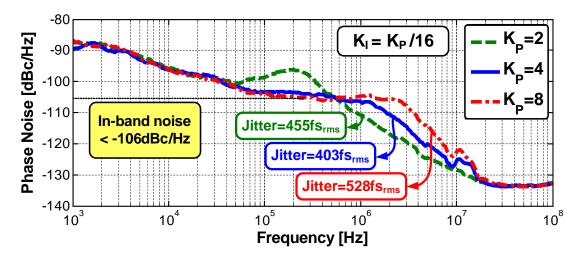

| 2.18       | Measured phase noise of the digital FNPLL at 4.5GHz for (a) conventional                               |            |

|            | BBPD, and (b) proposed TA-TDC.                                                                         | 36         |

| 2.19       | Measured phase noise for different BW settings (0.75MHz to 3MHz) at                                    |            |

|            | 4.5GHz output using 50MHz reference, obtained by varying the propor-                                   |            |

|            | tional path $(K_p)$ settings                                                                           | 37         |

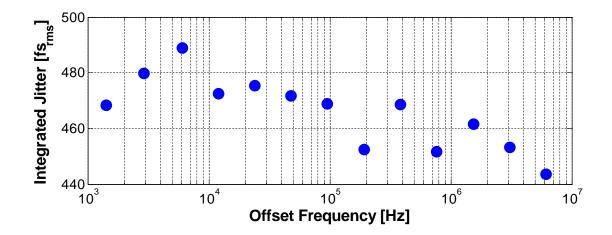

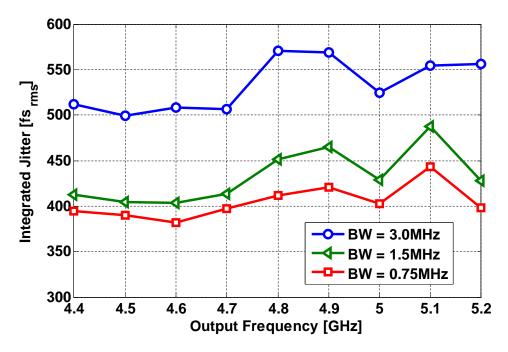

| 2.20       | Measured rms integrated jitter as a function of output fractional frequency                            |            |

|            | offset                                                                                                 | 37         |

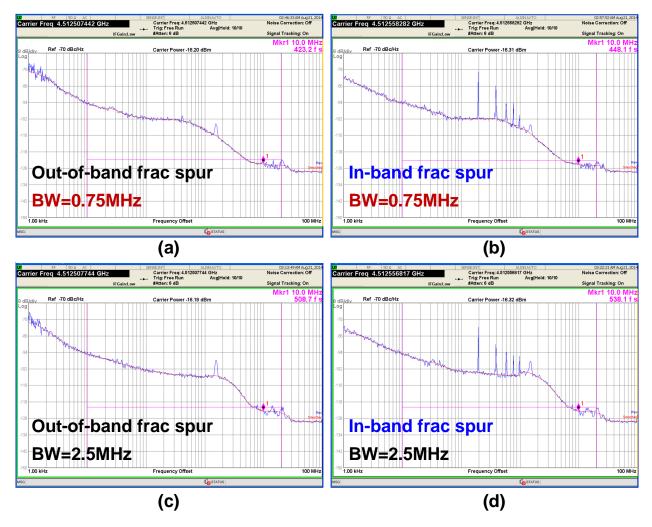

| 2.21       | Measured output spectra for (a) out-of-band fractional spurs and 0.75MHz                               |            |

|            | bandwidth, (b) in-band fractional spurs and 0.75MHz bandwidth, (c) out-                                |            |

|            | of-band fractional spurs and 2.5MHz bandwidth, and (d) in-band frac-                                   |            |

|            | tional spurs and 2.5MHz bandwidth.                                                                     | 38         |

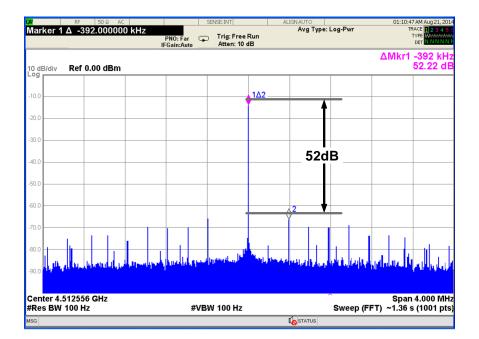

| 2.22       | Measured output spectrum at 4.5GHz output frequency and 392kHz frac-                                   |            |

|            | tional offset.                                                                                         | 39         |

| 2.23       | Measured rms integrated jitter as a function of the output frequency for                               |            |

|            | different bandwidth settings                                                                           | 41         |

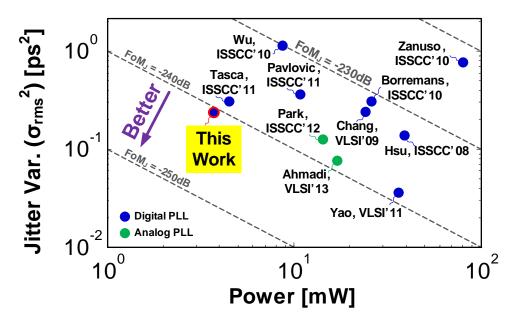

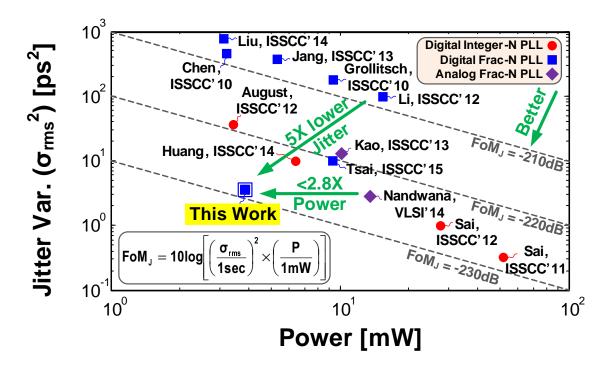

| 2.24       | FoM comparison.                                                                                        | 41         |

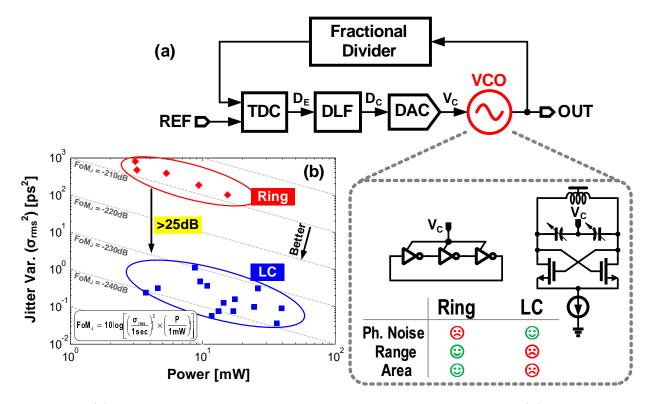

| 3.1        | (a) Digital FNPLL architecture using either ring- or LC-VCO. (b) Figure-                               |            |

| 0.1        | of-merit (FOM <sub>J</sub> ) of state-of-the-art LC- and ring-based digital FNPLLs                     | 44         |

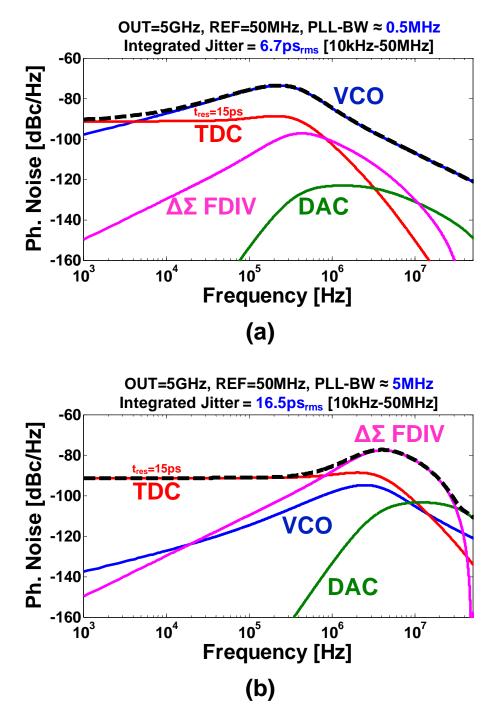

| 3.2        | Simulated digital FNPLL phase noise plots for two cases of bandwidths:                                 | 44         |

| 0.2        | (a) low bandwidth to suppress quantization error, and (b) high bandwidth                               |            |

|            | for VCO phase noise suppression.                                                                       | 47         |

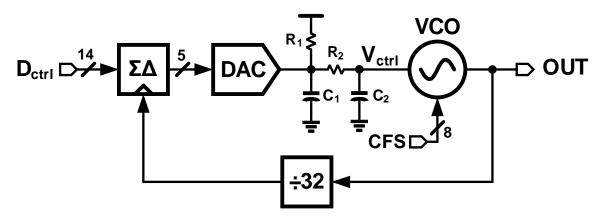

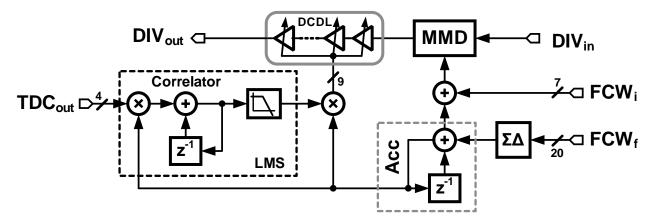

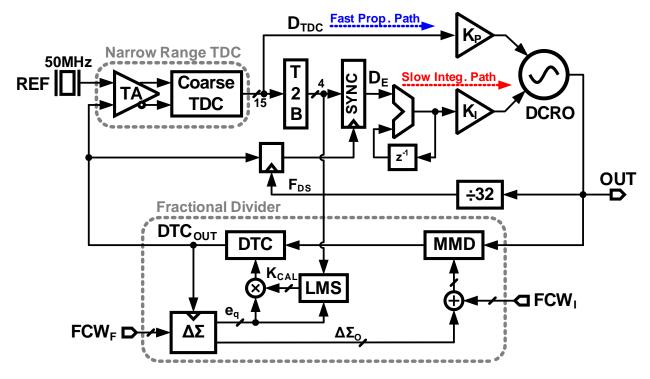

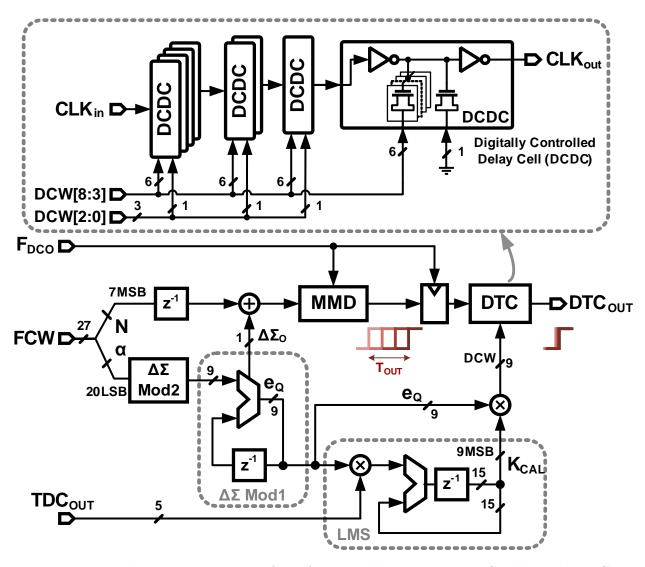

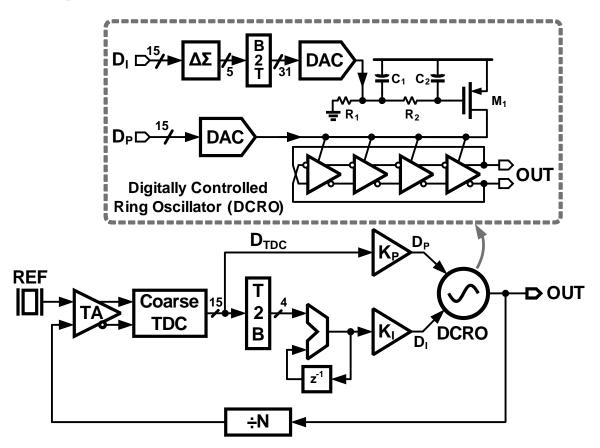

| 3.3        | Detailed block diagram of the proposed ring-based digital FNPLL.                                       | 47<br>50   |

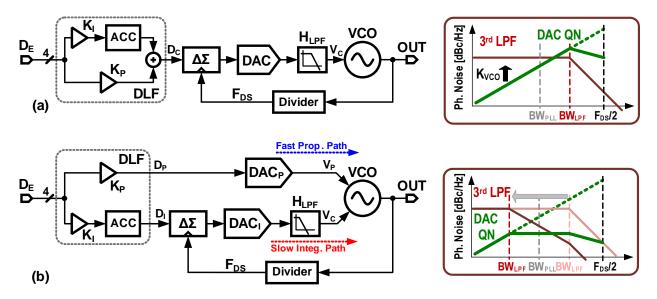

| 3.4        | (a) Conventional DAC and (b) proposed dual-path DAC                                                    | $50 \\ 50$ |

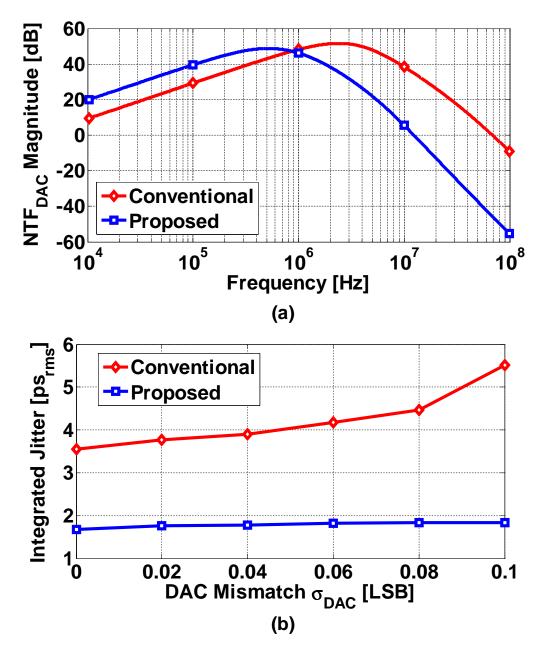

| 3.4<br>3.5 | (a) Simulated noise transfer function (NTF) of conventional and proposed                               | 50         |

| 5.5        | DACs. (b) Simulated integrated jitter of digital FNPLL using conventional                              |            |

|            | and proposed DACs.                                                                                     | 52         |

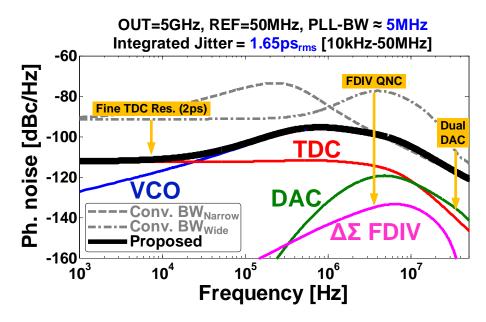

| 3.6        | Simulated phase noise of the proposed ring-based digital FNPLL.                                        | 52<br>53   |

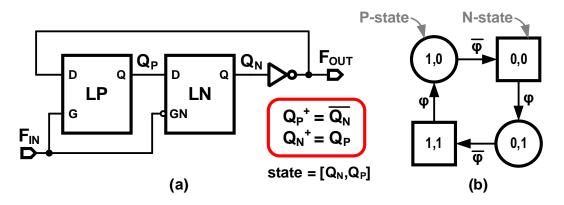

| 3.0<br>3.7 | Divide-by-2 cell: (a) block diagram and (b) its associated state diagram.                              | 55         |

| 3.8        | (a) Block diagram of a divide-by-2/3 cell. State diagrams: (b) in case of                              | 00         |

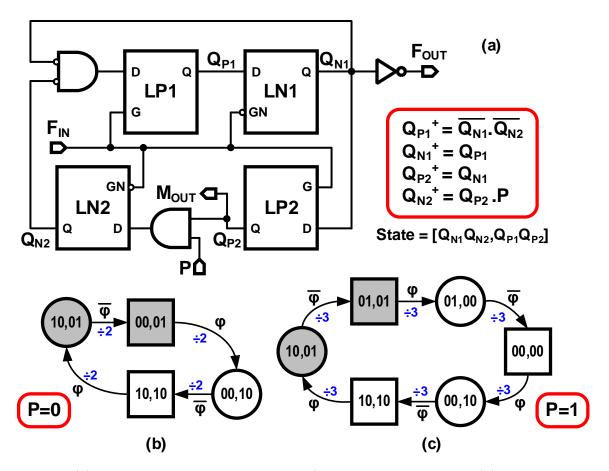

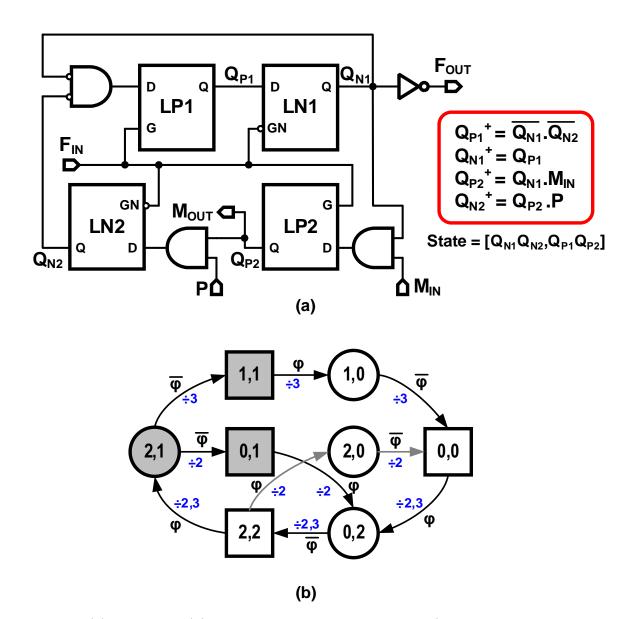

| 5.0        | P = 0 and (c) $P = 1$                                                                                  | 55         |

| 3.9        | (a) Block and (b) state diagrams for a divide-by-2/3 cell with modulus                                 | 00         |

| 0.9        | control $M_{IN}$                                                                                       | 57         |

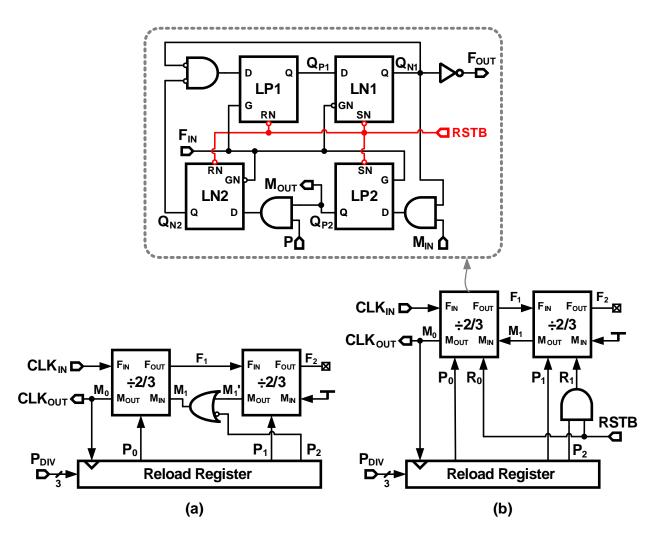

| 3.10       | (a) Conventional two-stage extended range MMD, and (b) proposed two-                                   | 51         |

| 0.10       | stage extended range MMD with seamless switching                                                       | 58         |

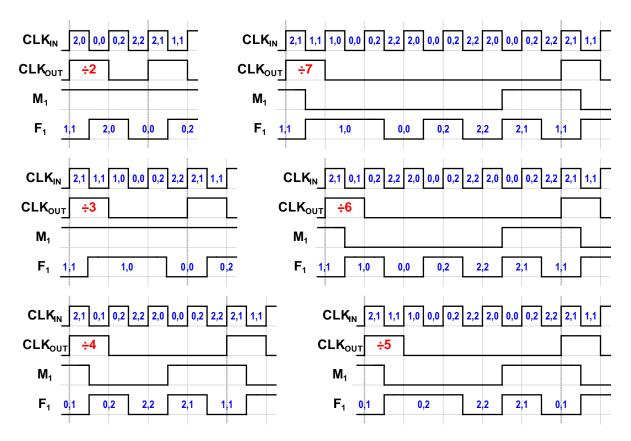

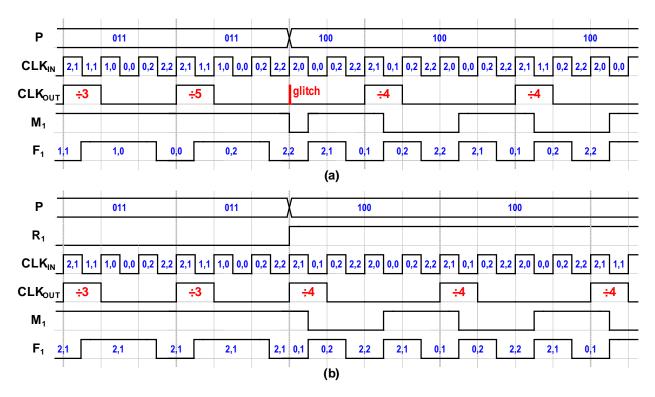

| 3 11       | Timing diagrams of the two-stage MMD for different division operations                                 | 90         |

| 0.11       | from 2 to 7. $\ldots$ | 59         |

| 3 19       | Timing diagrams of the two-stage MMD when division factor changes from                                 | 09         |

| 0.14       | 3 to 4 in case of (a) conventional MMD, and (b) proposed MMD with                                      |            |

|            | seamless switching.                                                                                    | 60         |

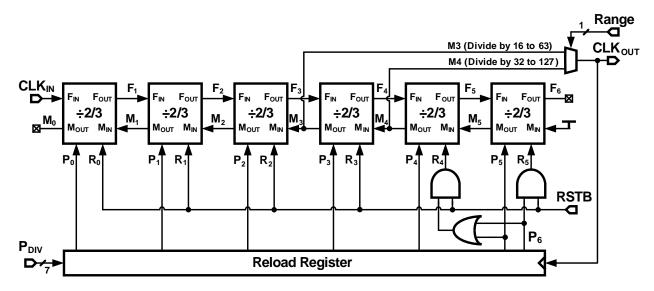

|            |                                                                                                        | 00         |

| 3.13 | Detailed block diagram of the proposed MMD with seamless switching across a wide division range from 16 to 127.                                                                    | 60       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.14 | Schematic of the digitally controlled ring oscillator (DCRO) with dual-<br>path control                                                                                            | 62       |

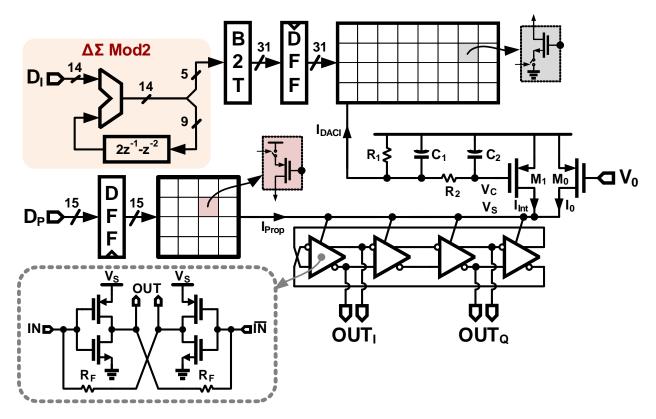

| 3.15 | Implementation details of the fractional divider with LMS calibrated DTC quantization noise cancellation scheme.                                                                   | 63       |

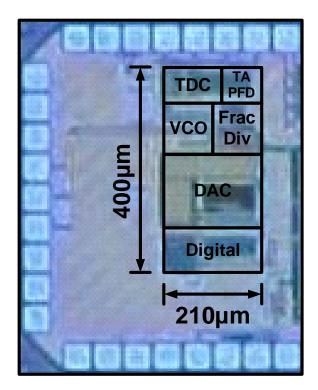

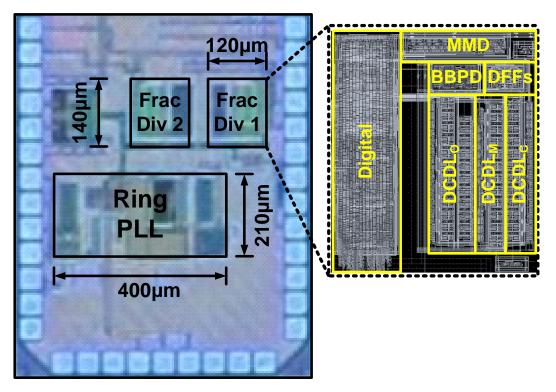

| 3.16 | Die photograph.                                                                                                                                                                    | 64       |

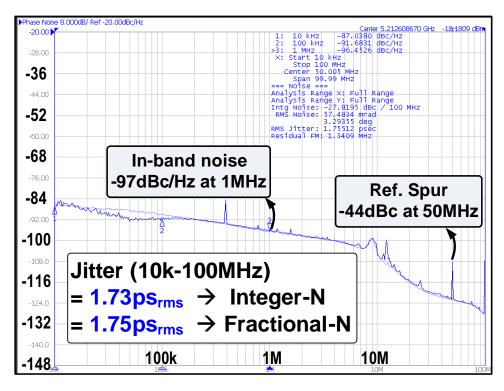

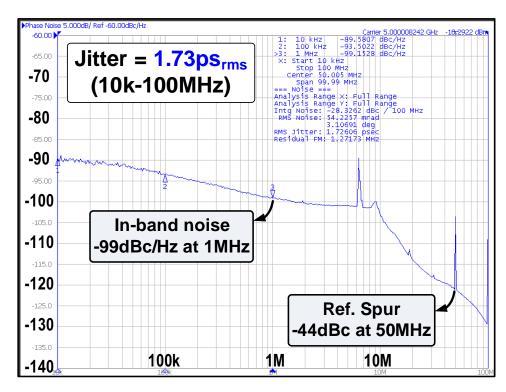

|      | Measured phase noise at 5.2GHz output frequency for integer-N and frac-<br>tional modes.                                                                                           | 65       |

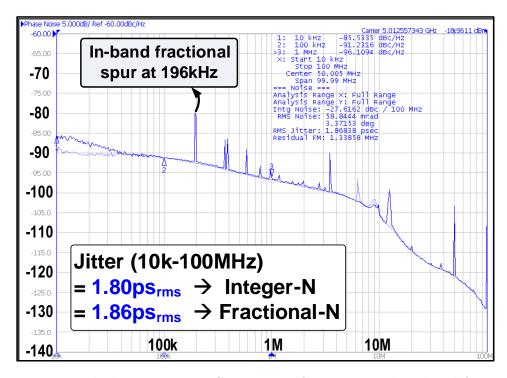

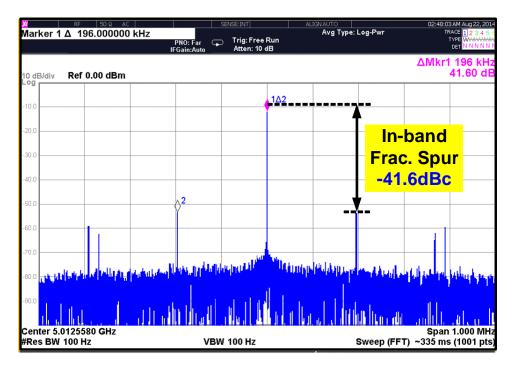

| 3.18 | Measured phase noise at 5GHz output frequency with in-band fractional spur at 196kHz offset.                                                                                       | 66       |

| 3.19 | Measured output spectrum at 5GHz output frequency and 196kHz frac-<br>tional offset.                                                                                               | 67       |

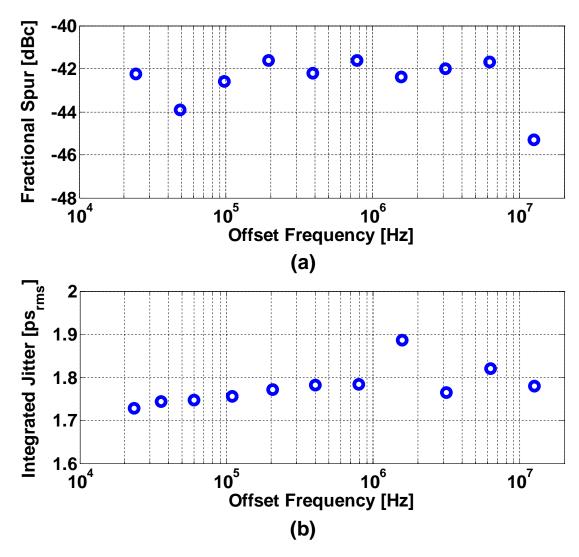

| 3.20 | (a) Measured fractional spur and (b) rms integrated jitter as a function of output fractional frequency offset.                                                                    | 69       |

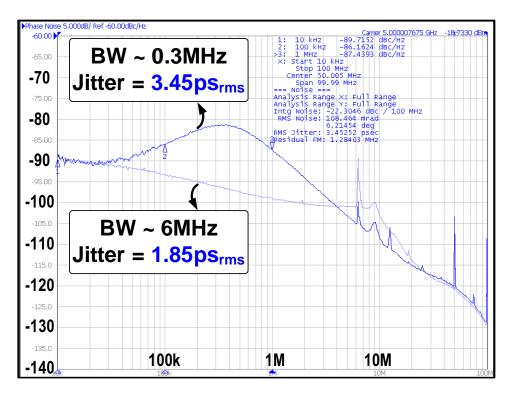

| 3.21 | Measured phase noise for narrow (0.3MHz) and wide (6MHz) BW settings<br>at 5GHz output using 50MHz reference.                                                                      | 70       |

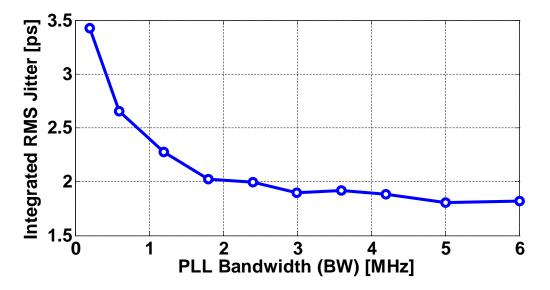

| 3.22 | Measured rms integrated jitter across different bandwidth settings at 5GHz output frequency.                                                                                       | 70       |

| 3.23 | $FoM_J$ comparison                                                                                                                                                                 | 70<br>71 |

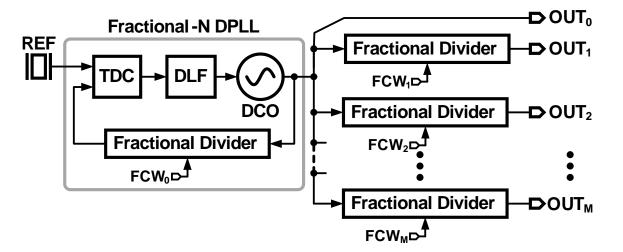

| 4.1  | Block diagram of the proposed multi-outputs all-digital clock generation<br>unit using open loop fractional dividers.                                                              | 73       |

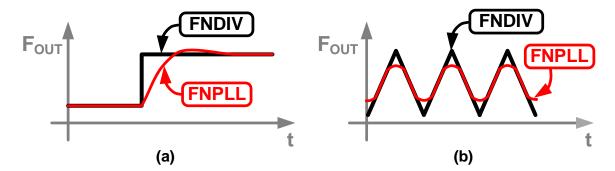

| 4.2  | Time-domain illustration comparing the proposed fractional divider to a conventional FNPLL in case of (a) instantaneous frequency switching, and (b) spread spectrum modulation.   | 74       |

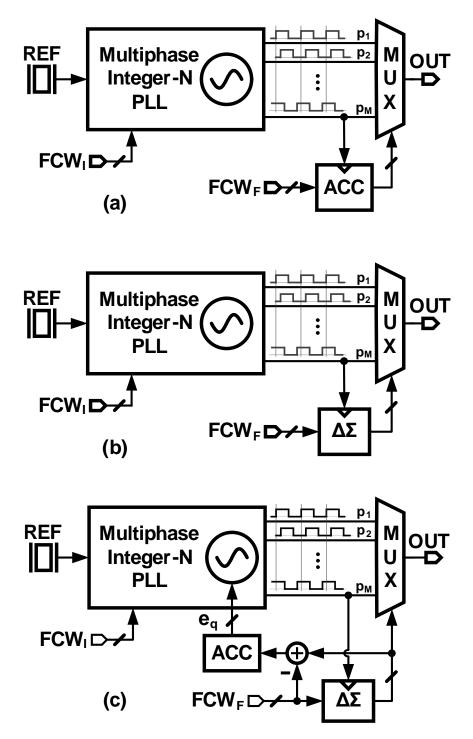

| 4.3  | Block diagram of open loop fractional-N synthesizers using (a) phase switch-<br>ing, (b) $\Delta\Sigma$ -based phase switching, and (c) $\Delta\Sigma$ -based phase switching with | -        |

| 4.4  | VCO-based QNC                                                                                                                                                                      | 76<br>77 |

| 4.4  | Simplified block diagram of the stand-alone open loop $\Delta\Sigma$ fractional divider.                                                                                           | 78       |

| 4.6  | Block and timing diagrams of the open loop FDIV with a DCDL fore-                                                                                                                  | 10       |

| 1.0  | ground calibration.                                                                                                                                                                | 79       |

| 4.7  | Detailed block diagram of the open loop FDIV with a DCDL background calibration.                                                                                                   | 80       |

| 4.8  | Detailed block diagram of the proposed MMD with seamless switching                                                                                                                 | 00       |

|      | across a wide division range from 4 to 127                                                                                                                                         | 81       |

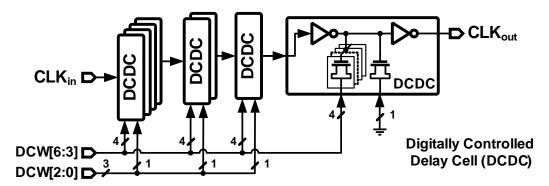

| 4.9  | The 7-bit digitally controlled delay line (DCDL) block diagram.                                                                                                                    | 82       |

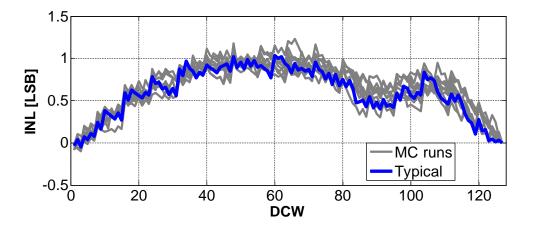

| 4.10 | Post-layout Monte-Carlo simulations for the DCDL integral nonlinearity (INL).                                                                                                      | 82       |

|      | Detailed block diagram of the ring-based digital PLL.                                                                                                                              | 83       |

|      | Die micrograph of the clock generation unit and zoomed-in FDIV layout                                                                                                              | 84       |

| 4.13 | Phase noise measurements of the digital PLL at 5GHz output frequency                                                                                                               | 84       |

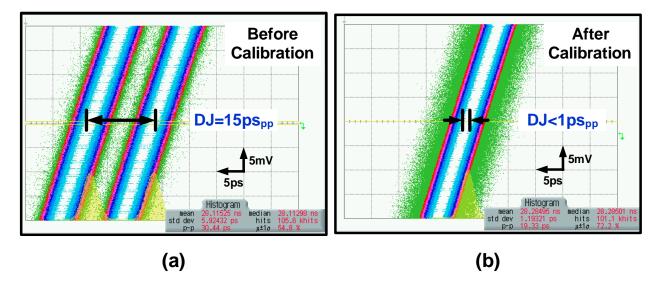

| 4.14 | Measured jitter histograms at 975MHz FDIV output frequency (a) before                                                                                                              | ~~       |

|      | and (b) after DCDL calibration.                                                                                                                                                    | 85       |

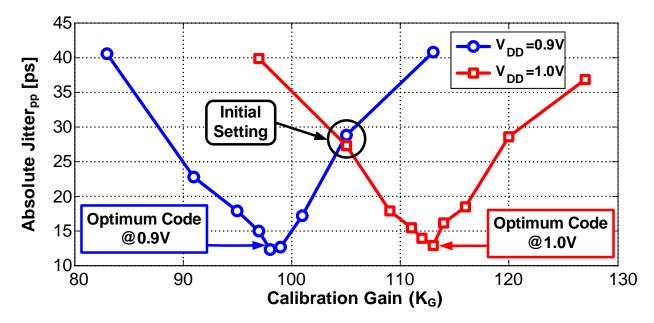

| 4.15 | Measured absolute peak-to-peak jitter as a function of the gain calibration<br>and $(K_{-})$ for different supply voltages | 85       |

|------|----------------------------------------------------------------------------------------------------------------------------|----------|

| 1 16 | code $(K_G)$ for different supply voltages                                                                                 | 50       |

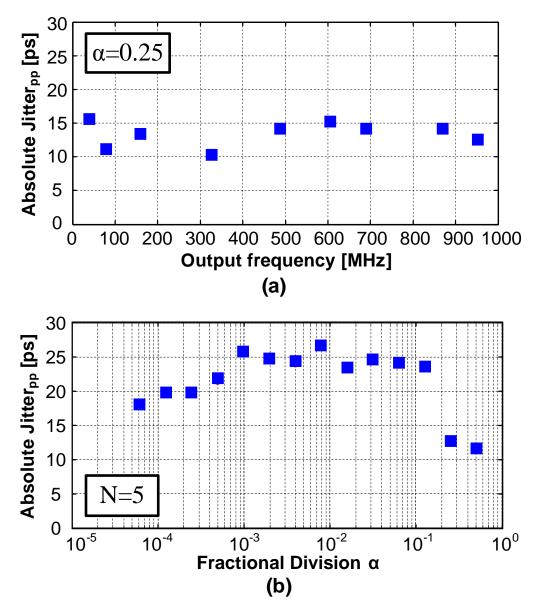

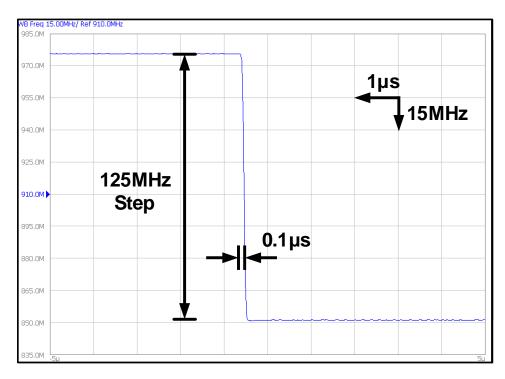

| 4.10 | · · · · · · · · · · · · · · · · · ·                                                                                        | 86       |

| 1 17 |                                                                                                                            | 87       |

|      |                                                                                                                            | 88       |

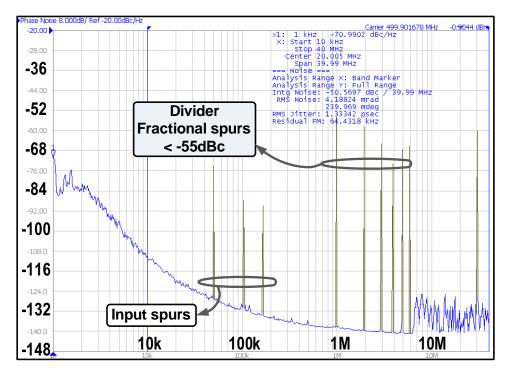

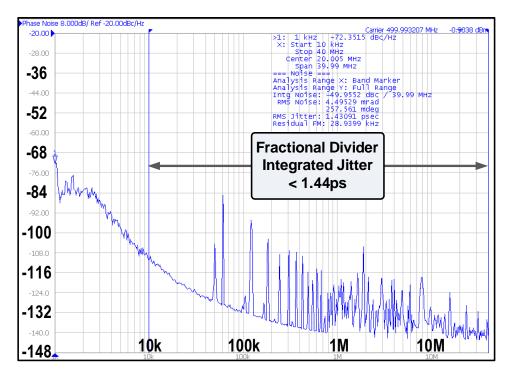

|      |                                                                                                                            | 00       |

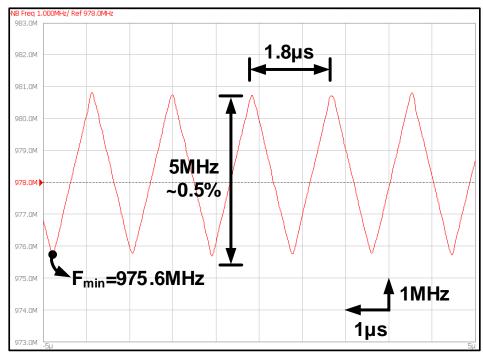

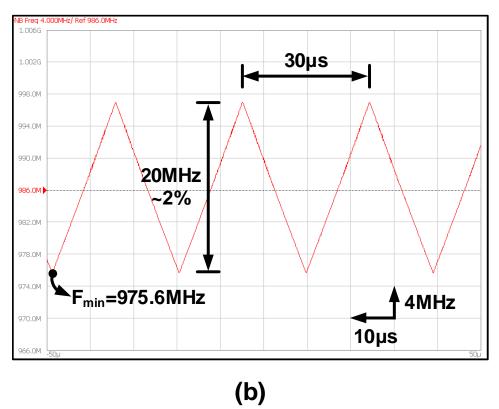

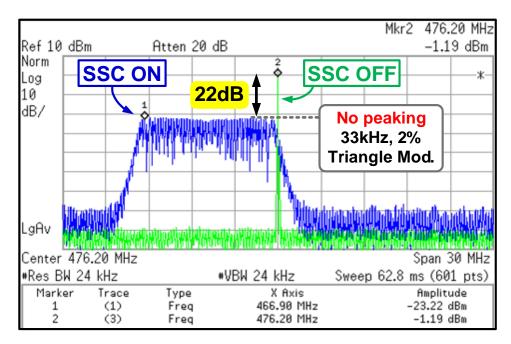

| 4.19 | Measured spread spectrum frequency modulation of the FDIV output in                                                        |          |

|      | time-domain in case of: (a) 5.5MHz triangle wave with $0.5\%$ modulation                                                   | 01       |

| 4.00 |                                                                                                                            | 91       |

|      |                                                                                                                            | 92<br>02 |

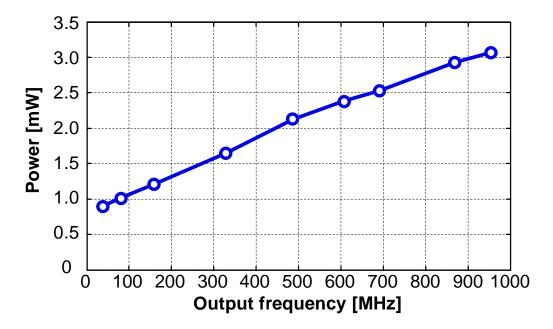

|      | 1 0 0                                                                                                                      | 92       |

| 4.22 | Measured power consumption of the stand-alone FDIV as a function of                                                        | 00       |

|      | the output frequency                                                                                                       | 93       |

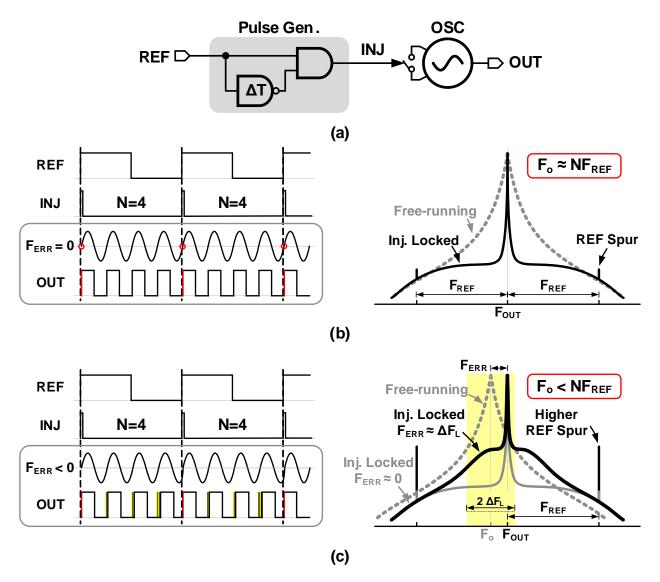

| 5.1  | (a) Sub-harmonic injection-locked oscillator. Timing diagram and output                                                    |          |

|      | spectrum of ILCM when (b) $F_{ERR} = 0$ , and (c) $F_{ERR} \approx \Delta F_L$ .                                           | 96       |

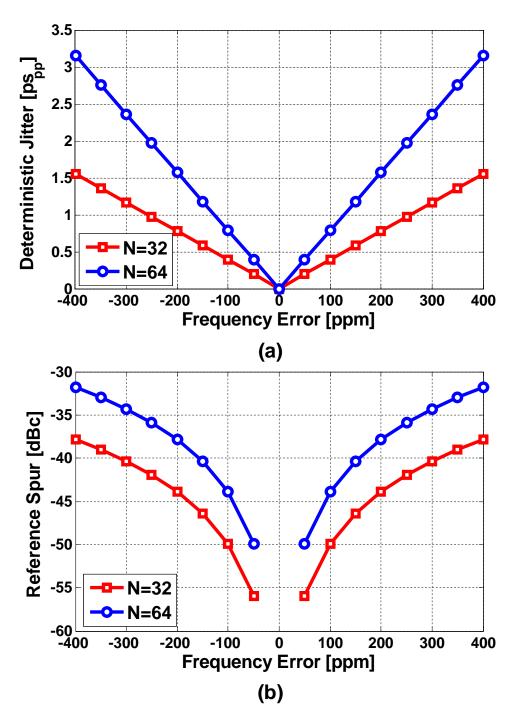

| 5.2  | (a) Deterministic jitter and (b) reference spur as a function of $F_{ERR}$ for                                             |          |

|      | N=32 and 64                                                                                                                | 98       |

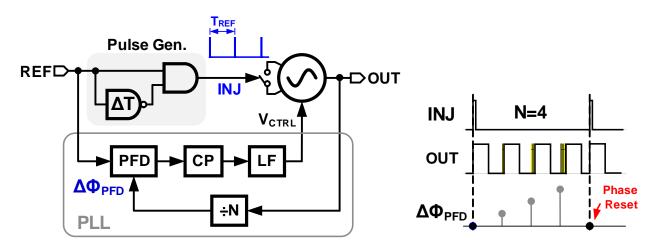

| 5.3  | A block diagram of conventional injection-locked PLL with an illustrating                                                  |          |

|      | timing diagram.                                                                                                            | 99       |

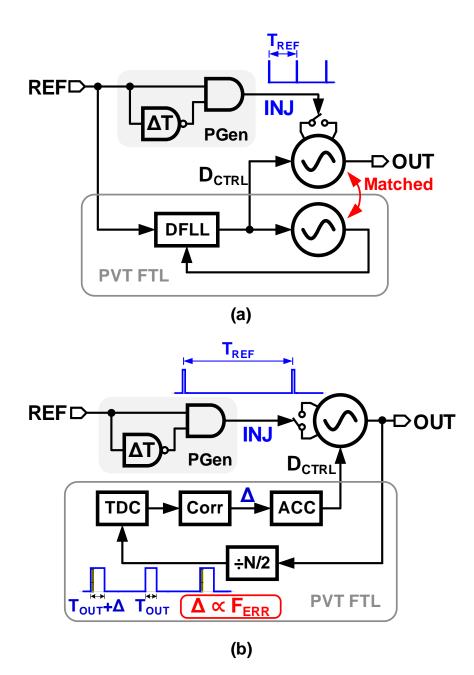

| 5.4  | Block diagram of ILCM with (a) replica-based FTL [97], and (b) TDC-                                                        |          |

|      | based FTL [99]                                                                                                             | 00       |

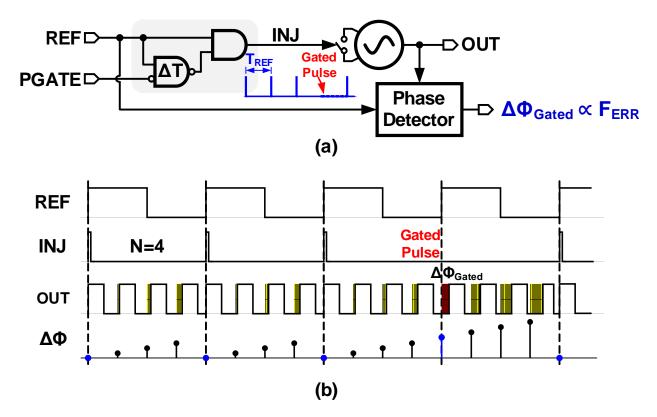

| 5.5  | (a) Conceptual diagram of the proposed pulse getting frequency error de-                                                   |          |

|      | tection. (b) Timing diagram                                                                                                | 01       |

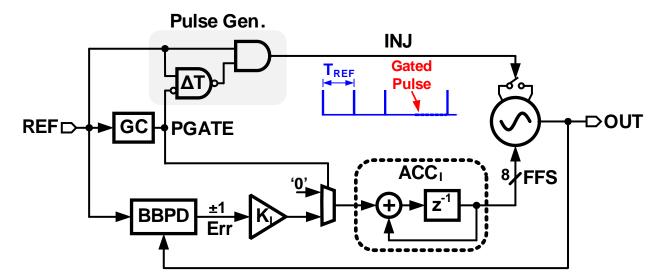

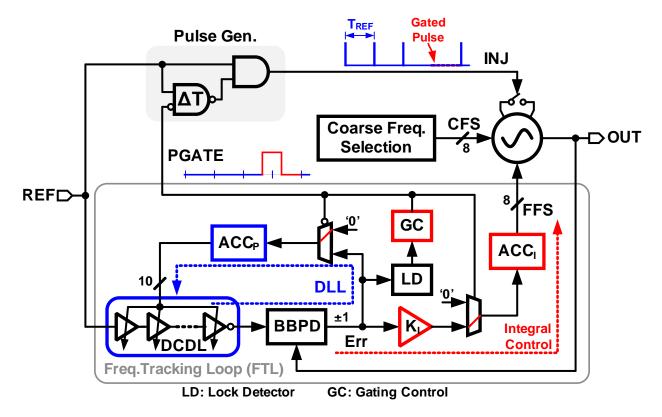

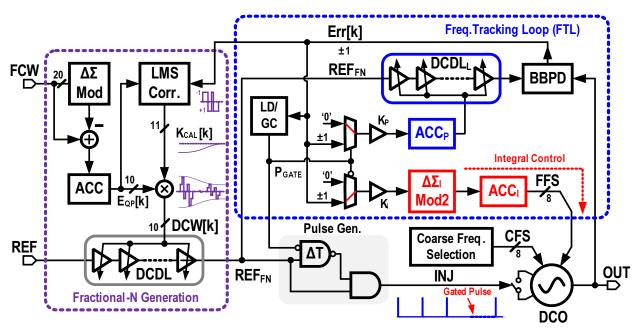

| 5.6  | Block diagram of the proposed frequency tracking loop (FTL)                                                                | 02       |

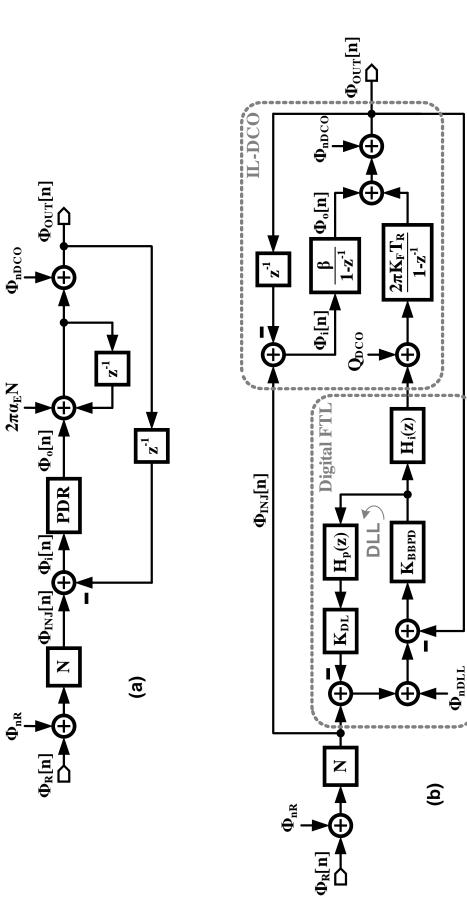

| 5.7  | Block diagram of the proposed injection locked clock multiplier (ILCM) 1                                                   | 03       |

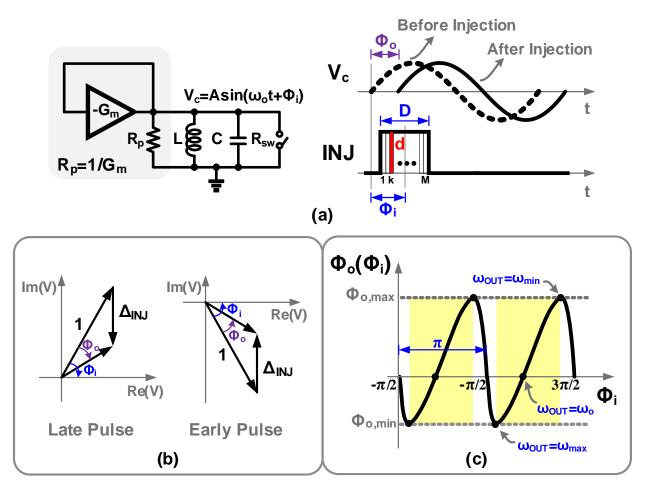

| 5.8  | PDR analysis. (a) LC oscillator simplified half circuit with an illustrating                                               |          |

|      | timing diagram, (b) voltage phasor diagram, and (c) PDR diagram 1                                                          | 05       |

| 5.9  | PDR analysis and simulation results in case (a) $R_{sw}=20\Omega$ , $D=20ps$ , (b)                                         |          |

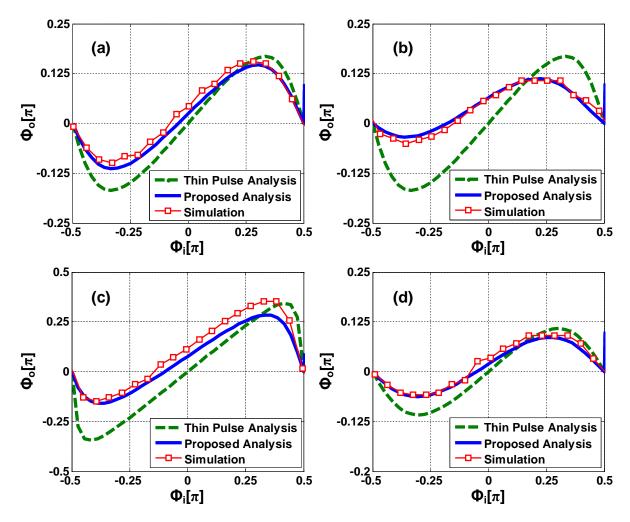

|      | $R_{sw}=40\Omega$ , D=40ps, (c) $R_{sw}=10\Omega$ , D=25ps, and (d) $R_{sw}=40\Omega$ , D=25ps 1                           | 09       |

| 5.10 | (a) Phase-domain model of sub-harmonic ILO, and (b) discrete-time phase-                                                   |          |

|      | domain model of the proposed ILCM                                                                                          | 11       |

| 5.11 |                                                                                                                            | 13       |

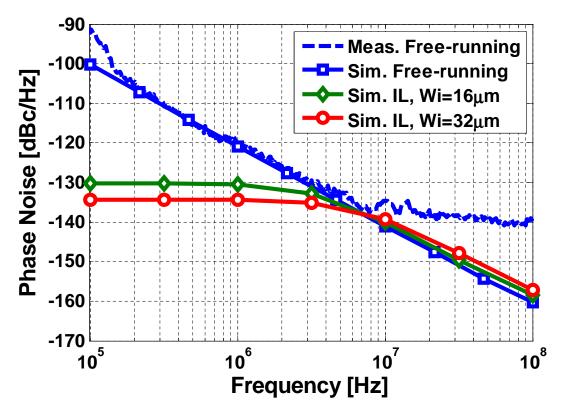

| 5.12 | Injection locked DCO phase noise measurement and simulation results at                                                     |          |

|      |                                                                                                                            | 14       |

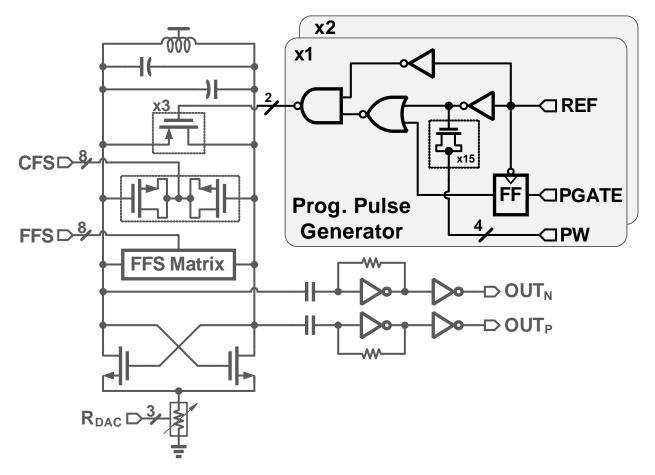

| 5.13 | Schematic of the programmable pulse generator                                                                              | 15       |

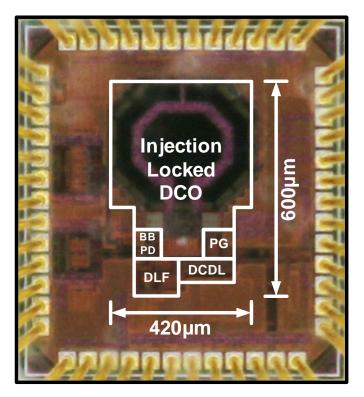

|      |                                                                                                                            | 16       |

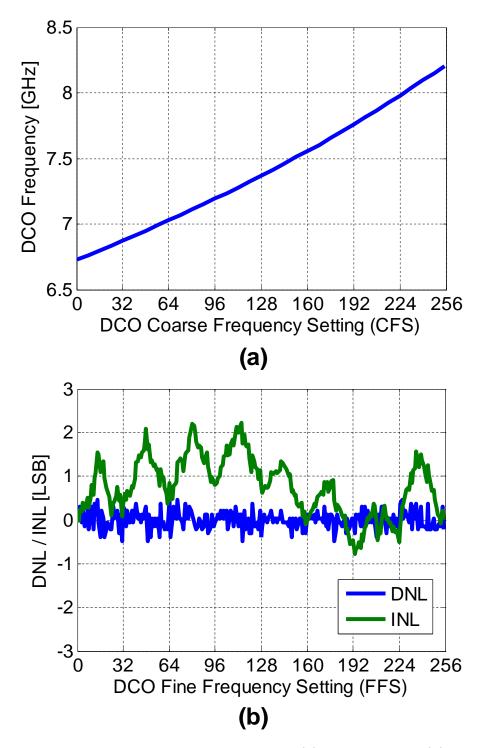

|      | Measured DCO tuning characteristics: (a) coarse tuning, (b) fine tuning                                                    |          |

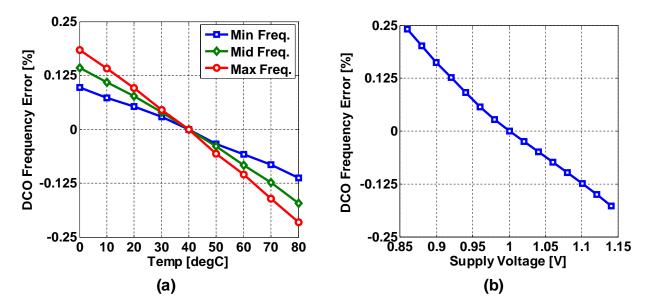

|      |                                                                                                                            | 17       |

| 5.16 | Measured DCO free-running frequency across (a) temperature, and (b) supply.1                                               | 18       |

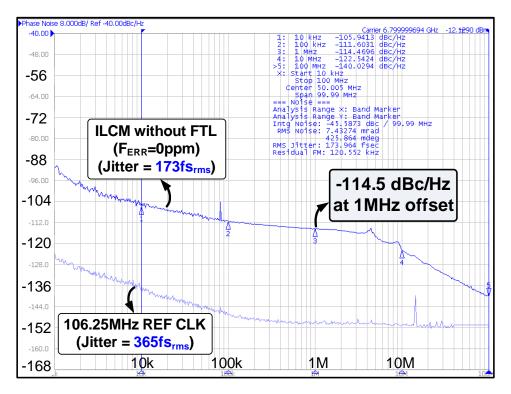

|      | Measured phase noise of the reference clock and ILCM output without                                                        |          |

|      |                                                                                                                            | 19       |

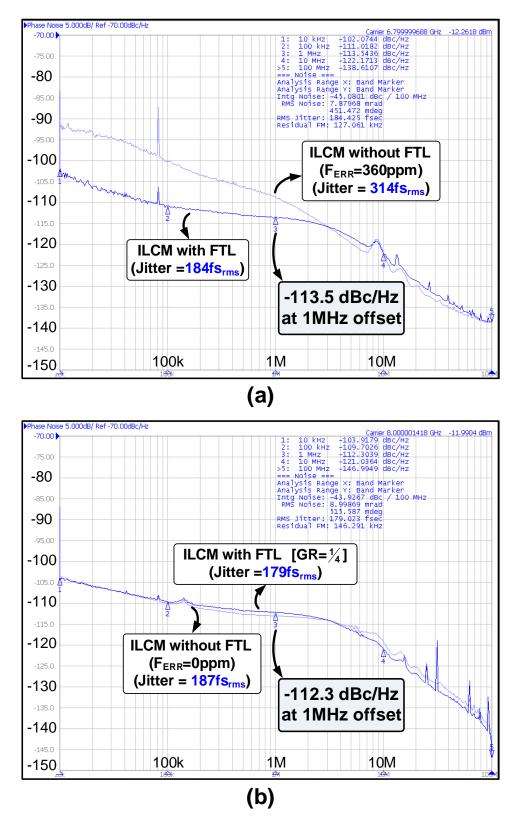

| 5.18 | Measured ILCM phase noise with FTL at (a) 6.8GHz, and (b) 8GHz 1                                                           | 20       |

| 00   |                                                                                                                            |          |

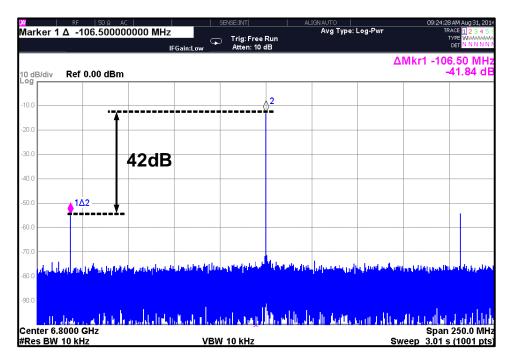

| 5.19       | Measured output spectrum of the proposed ILCM with FTL (at 6.8GHz, N=64)                           | 121        |

|------------|----------------------------------------------------------------------------------------------------|------------|

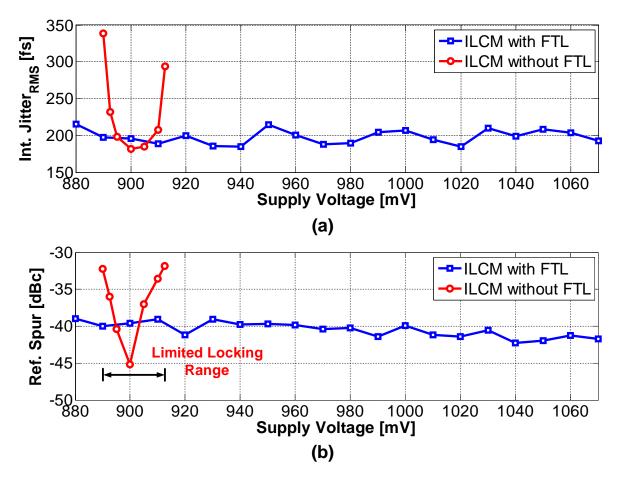

| 5.20       | (a) Measured integrated jitter, and (b) measured reference spur versus                             | 123        |

| 5 91       | supply voltage with and without FTL                                                                | 120        |

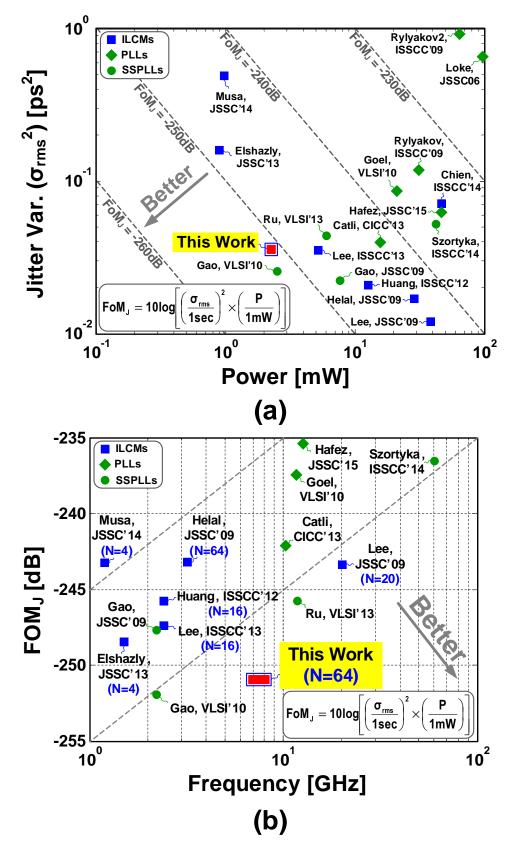

| 0.21       | FoM comparison. (a) Jitter and power comparison and (b) $FoM_J$ as a function of output frequency. | 124        |

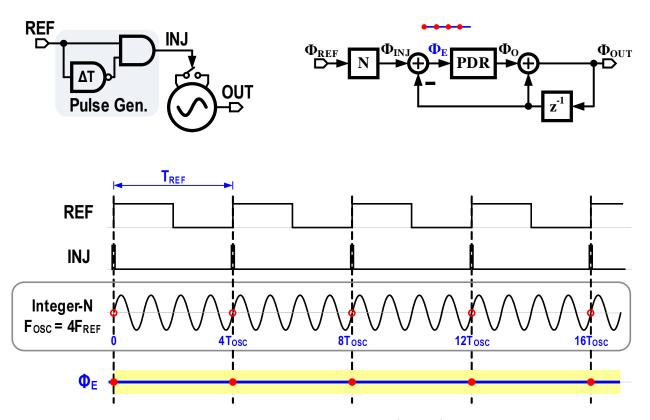

| 6.1        | Classical ILCM for integer-N multiplication $(N = 4)$ : schematic, discrete-                       |            |

|            | time model, and timing diagram.                                                                    | 126        |

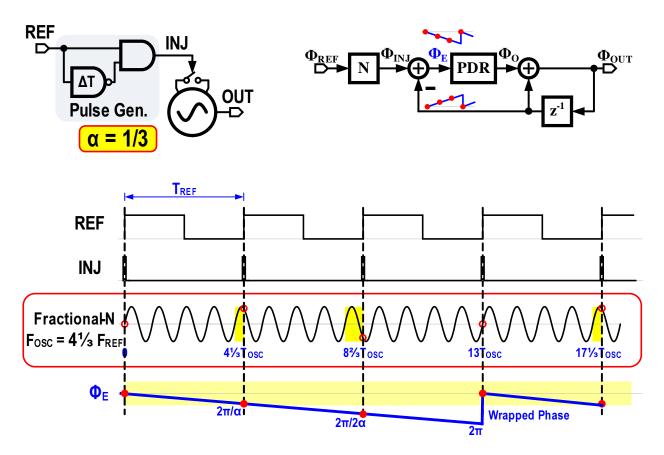

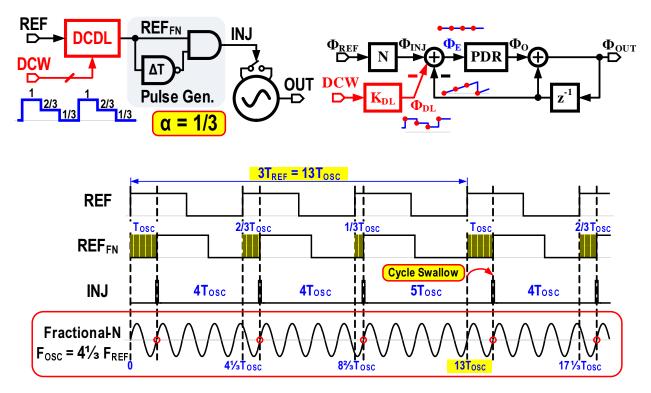

| 6.2        | Classical ILCM for fractional-N multiplication (N = 4 and $\alpha = 1/3$ ):                        |            |

|            | schematic, discrete-time model, and timing diagram.                                                | 129        |

| 6.3        | Fractional-N ILCM operation concept using delay modulation of the in-                              |            |

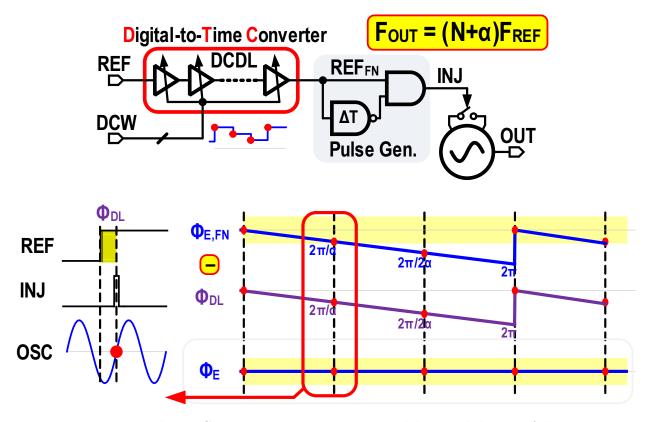

| <b>a</b> 4 | jection pulse.                                                                                     | 130        |

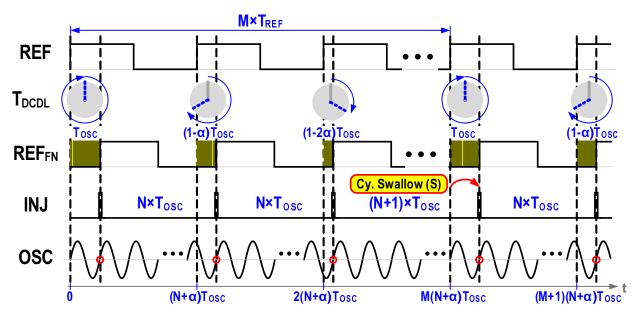

| 6.4        | Proposed ILCM for fractional-N multiplication (N = 4 and $\alpha = 1/3$ ):                         | 101        |

| с <b>г</b> | schematic, discrete-time model, and timing diagram.                                                | 131        |

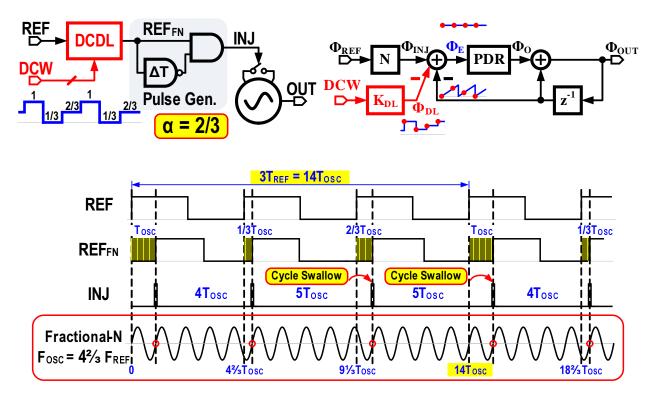

| 6.5        | Proposed ILCM for fractional-N multiplication (N = 4 and $\alpha = 2/3$ ):                         | 199        |

| 6.6        | schematic, discrete-time model, and timing diagram                                                 | 132<br>132 |

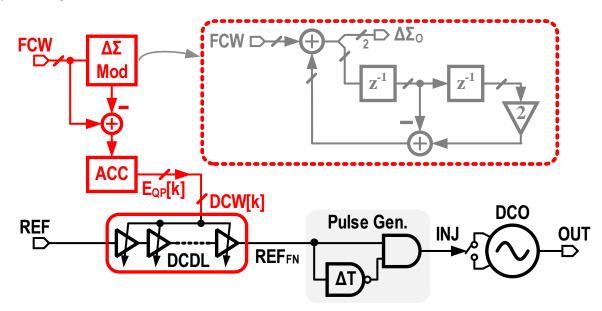

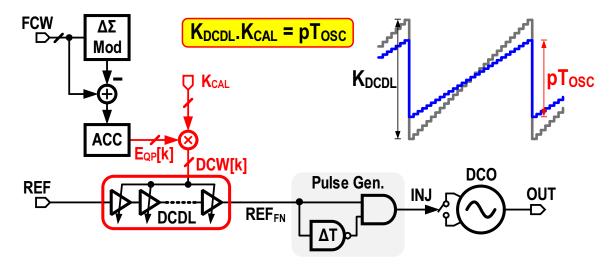

| 6.7        | Block diagram of the fractional-N ILCM using a second order $\Delta\Sigma$ modulator.              | 132        |

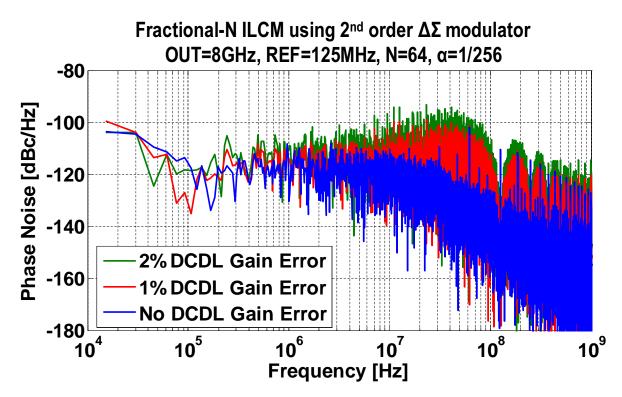

| 6.8        | Simulated output phase-noise spectrum, $8.0005$ GHz output using 125                               | 100        |

| 0.0        | MHz reference (N = 64 and $\alpha = 1/256$ ), with 0, 1%, and 2% DCDL                              |            |

|            | gain error                                                                                         | 134        |

| 6.9        | Fractional-N ILCM with a calibrated DCDL gain.                                                     | 134        |

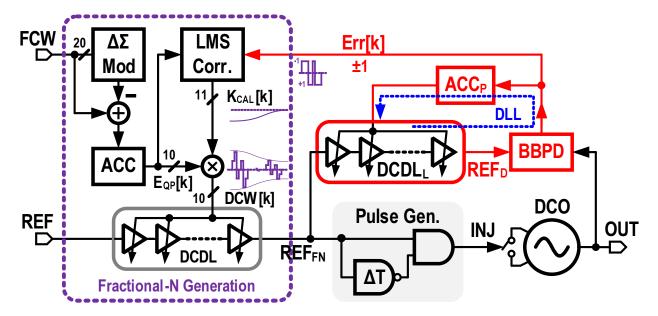

| 6.10       | Background LMS calibration scheme for scaling DTC gain in fractional-N                             |            |

|            | ILCM.                                                                                              | 135        |

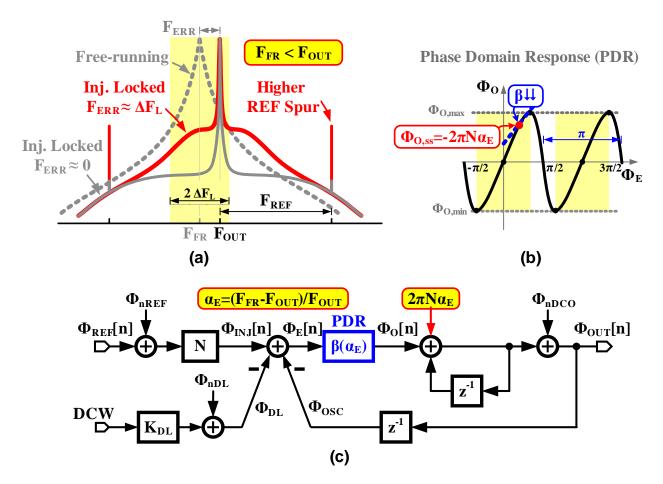

| 6.11       | The impact of frequency error: (a) output spectrum of ILCM, (b) phase                              |            |

|            | domain response, and (c) phase-domain noise model                                                  | 136        |

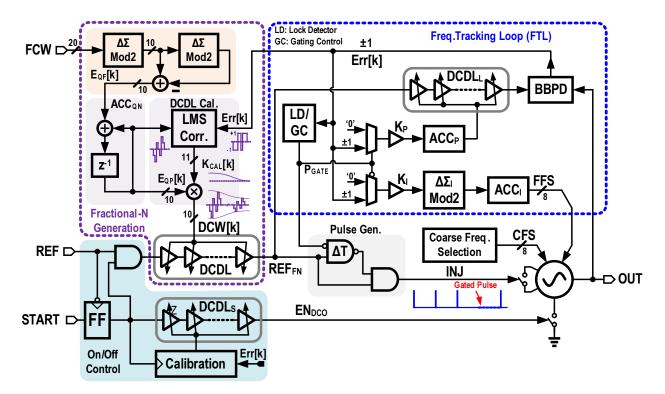

|            | Schematic of the proposed fractional-N ILCM with FTL                                               | 137        |

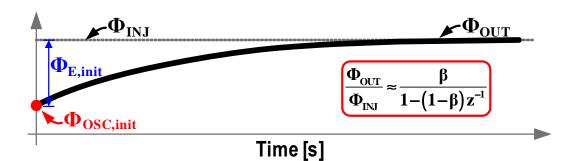

|            | Phase settling behavior of ILCM.                                                                   | 138        |

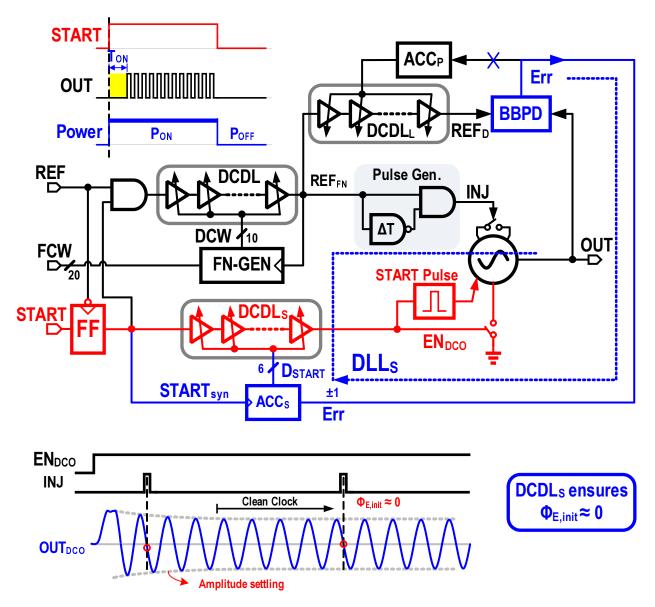

| 6.14       | Proposed rapid power-on-lock fractional-N ILCM architecture with back-                             | 100        |

| 0.15       | ground calibrated initial phase adjustment.                                                        | 139        |

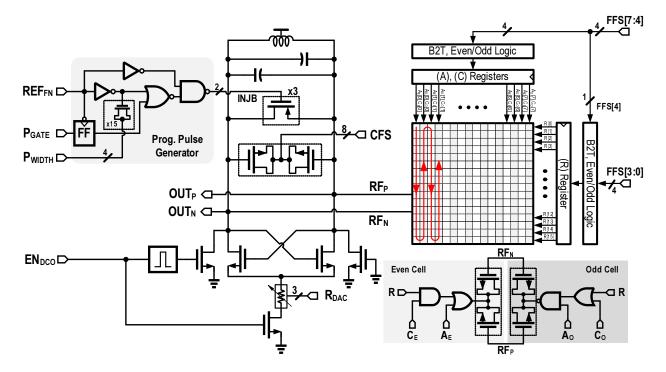

|            | LC-based injection locked DCO implementation.                                                      | 140        |

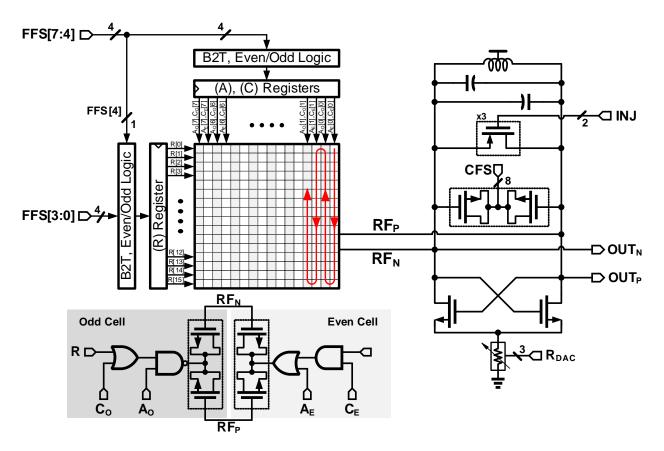

|            | Schematic of the DCDL.                                                                             | 141        |

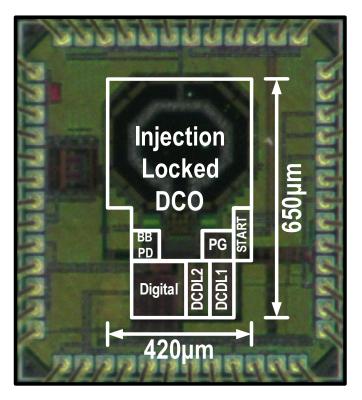

|            | Complete architecture of the proposed rapid on/off fractional-N ILCM Die photograph                | 142<br>143 |

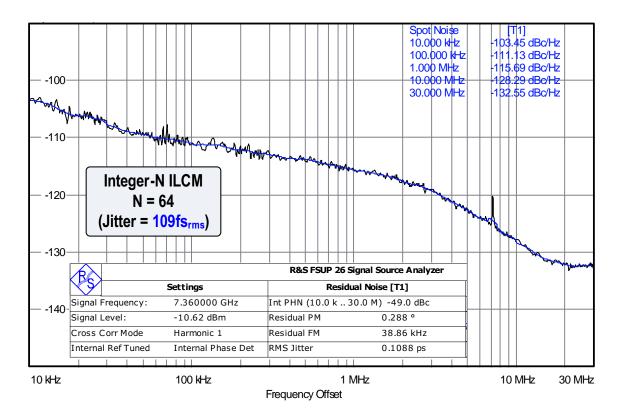

|            | Measured phase noise of the ILCM output in integer-N mode at 7.36GHz.                              | 143<br>144 |

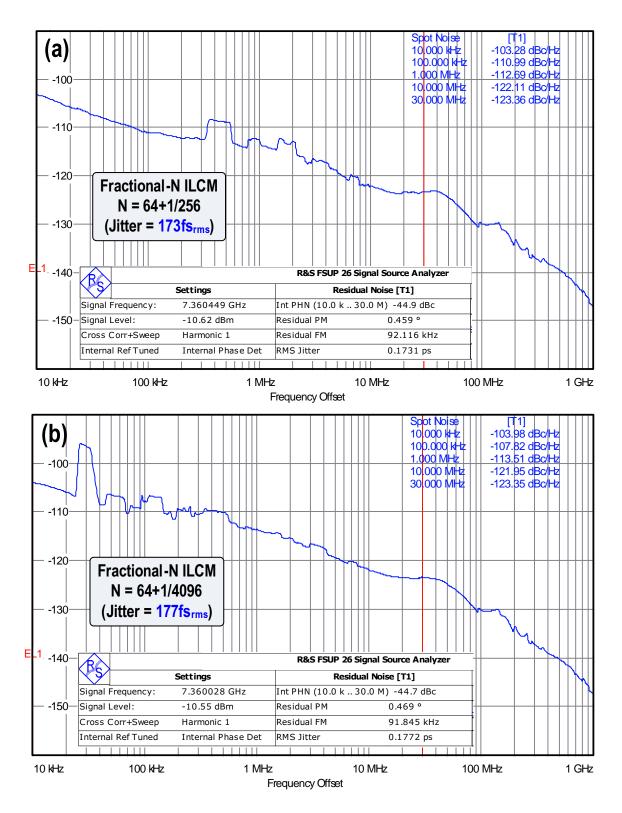

|            | Measured phase noise of the ILCM output in fractional-N mode at 7.36GHz                            | 144        |

| 0.20       | when (a) $\alpha = 1/256$ and (b) $\alpha = 1/4096$ .                                              | 147        |

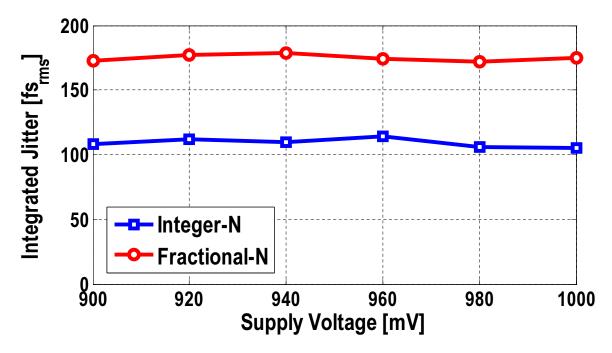

| 6.21       | Measured integrated jitter versus supply voltage with FTL in integer- and                          |            |

|            | fractional-N modes.                                                                                | 148        |

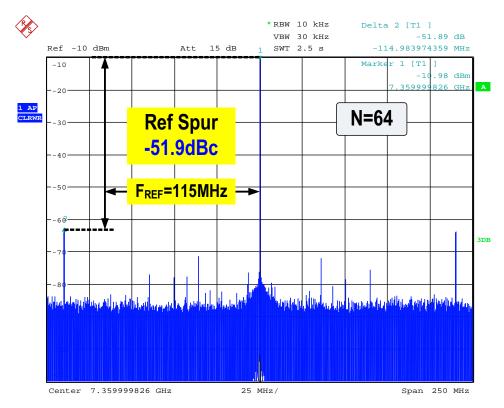

| 6.22       | Measured output spectrum of integer-N ILCM with FTL (at $7.36$ GHz, N=64).                         | 148        |

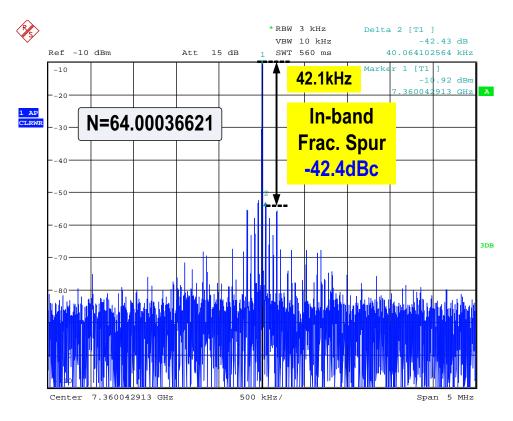

| 6.23       | Measured output spectrum of fractional-N ILCM with FTL (at 7.36 GHz, $$                            |            |

|            | N=64, $\alpha = 3/8192$ )                                                                          | 149        |

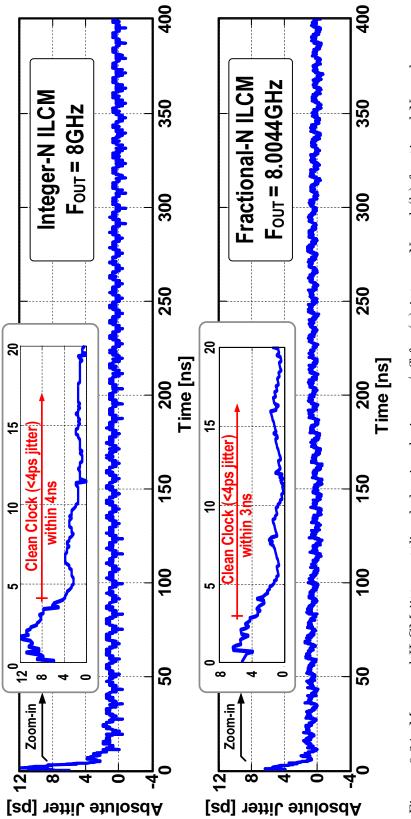

| 6.24 | Measured ILCM jitter settling behavior during on/off for (a) integer-N and |     |

|------|----------------------------------------------------------------------------|-----|

|      | (b) fractional-N modes                                                     | 150 |

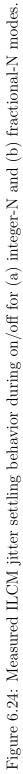

| 6.25 | Jitter-power $FoM_J$ comparison: integer-N mode                            | 151 |

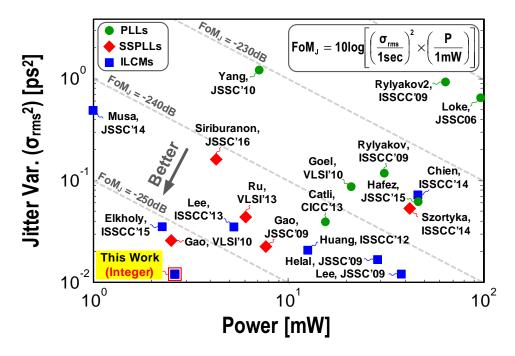

| 6.26 | Jitter-power $FoM_J$ comparison: fractional-N mode.                        | 151 |

# CHAPTER 1 INTRODUCTION

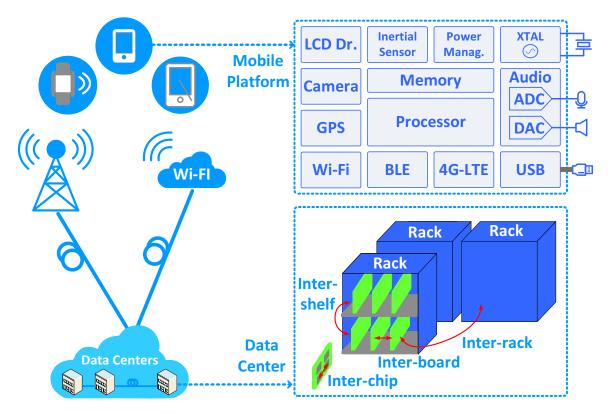

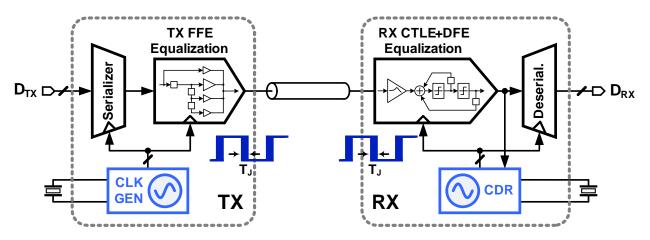

The internet is shaping our life today, where billions of cell phones, tablets, wearables, and internet of thinks (IoT) sensors are connected together. With this unprecedented connectivity, an energy bottleneck emerges at both ends: the battery operated mobile platforms and the data centers that support these bandwidth-intensive applications (see Fig. 1.1). In mobile platforms energy efficiency is essential to save the battery life, while in data centers energy efficiency is critical to save the electric power and cooling costs. Improving energy efficiency of data centers' network components is extremely important to sustain their growth. Fig. 1.2 shows a block diagram of a typical serial link architecture with embedded clocking used in data centers networks. At the transmitter side, parallel data stream is serialized into a high speed stream using a clean high frequency clock. A clock generator synthesizes this clock relying on an external crystal reference clock. At the receiver side, the clock and data recovery (CDR) extracts clock and data from the equalized received signal, then data is de-serialized into a low frequency parallel data stream. Clock generation at TX and clock and data recovery (CDR) at RX are major sources of power consumption in a link, and typically consume 35-50% of the total link power. This is mainly driven by the clock jitter requirements, which distorts both transmitted and recovered data and can limit the link bit-error rate.

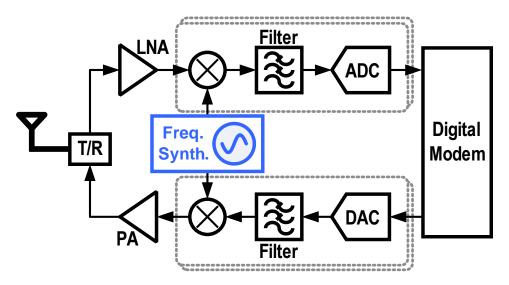

On the other hand, mobile platforms have many modules with diverse functionalities. Typically, different radios including 4G-LTE, Bluetooth, and WiFi are major sources of power consumption. A typical RF front-end of a WiFi radio is shown in Fig. 1.3 as an example. The role of the frequency synthesizer is very critical as it synthesizes the RF carrier of the transmitted signal, and it synthesizes the down-conversion signal at the receiver. Typically, the synthesizer consumes half of the total transceiver power. Other modules in

Figure 1.1: Applications of clock generators in the era of internet of thinks (IoT).

Figure 1.2: Block diagram of a serial link with embedded clocking.

the mobile platform like audio data converters, processors, and memory need clocks. We can clearly see that clock and frequency synthesizers play a critical role in different modules, and can limit their overall performance and power consumption. Therefore, enhancing the energy efficiency of frequency synthesizers is highly desirable.

Figure 1.3: Block diagram of a typical wireless transceiver.

#### 1.1 Frequency Synthesizers Applications

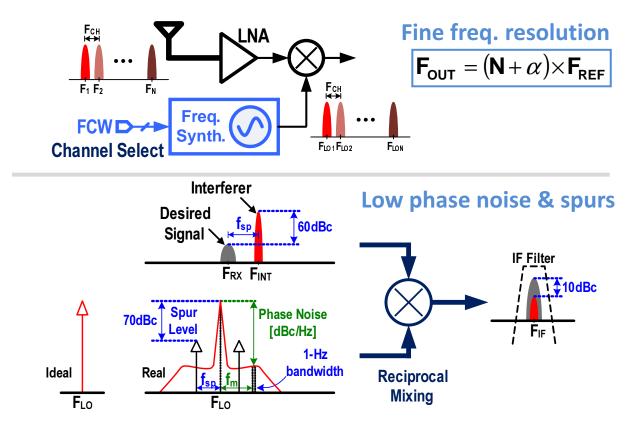

#### 1.1.1 Fractional-N Frequency Synthesizers for Wireless Transceivers

Wireless transceivers require a fractional-N frequency synthesizer with a very fine frequency resolution. By multiplying the reference frequency by a fractional factor  $(N + \alpha)$ , defined by the frequency control word (FCW), the carrier frequency of different channels is synthesized as shown in Fig. 1.4. Ideally, the synthesizer generates a perfect single tone, but in reality, its output spectrum has undesired phase noise and spurious tones. This corrupts the phasemodulated signals in the process of up-conversion or down-conversion. Another effect occurs in the receiver path in the presence of a large interferer signal as illustrated in Fig. 1.4. The spurs may down-convert the interferer signal into the signal bandwidth, degrading the receiver noise figure. For example, if the interferer is 60dB above the desired signal, then with a 70dBc spur, the corruption is only 10dB below the signal.

#### 1.1.2 Multi-standard Flexible SerDes

Wireline transceivers (or SerDes) usually use integer-N PLLs to meet the tight constraints on the clock jitter for various standards as depicted in Fig. 1.2. Recently, there is a growing demand for multi-standard-compliant transceivers integrated into a single chip with a wide

Figure 1.4: The role of frequency synthesizer in wireless transceivers illustrating the impact of its phase noise and spurious tones.

and continuous range of data-rates. To save the cost of multiple input crystal references, fractional-N frequency synthesis is highly desirable in both the transmitter and the receiver. A flexible fractional-N clock generator has to cover wide frequency range with fine frequency resolution to serve various standards. It has to provide multiple phases with stringent jitter performance with minimum power and area.

#### 1.1.3 Fractional-N Clocking for Micro-Processors

Modern multi-core processors use per core clocking (see Fig. 1.5(a)), where each core runs at its own speed [1]. The power manager takes input from environmental sensors, performance counters, and software requests, and continuously adjusts the frequencies of different cores as shown in Fig. 1.5(b). The core frequency can be changed dynamically to optimize for performance or power dissipation using a dynamic frequency scaling (DFS) technique. Changing the core clock frequency rapidly is required to enhance the energy efficiency. However, this process has to be carefully managed to ensure code execution without any interruption. Therefore, the frequency transitions have to be very smooth and well controlled with no undershoots. The second main requirement in processor clocking is the capability of spread spectrum frequency modulation. By spreading the clock energy across a wide bandwidth, the electromagnetic interference (EMI) is dramatically reduced as demonstrated in Fig. 1.5(b). Processors use programmable spread-spectrum clocking (SSC) to satisfy the electromagnetic compatibility (EMC) regulations.

#### 1.2 Frequency Synthesizers Architectures

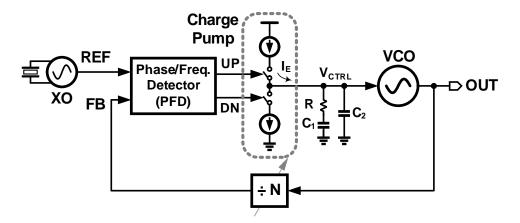

#### 1.2.1 Analog Integer-N PLL

Phase locked loop (PLL) is a feedback system that is used to obtain a highly stable output frequency. Analog charge pump PLL, shown in Fig. 1.6, has been the dominant architecture for frequency multiplication. It consists of a phase frequency detector (PFD), a charge pump (CP), a loop filter (LF), a voltage-controlled oscillator (VCO) and a feedback divider. Adding a divide-by-N block in feedback enables frequency multiplication. The PFD detects the phase/frequency error between the reference clock and the feedback clock, and correspondingly generates a pair of digital pulses to drive the CP. The CP then converts the digital pulses into current pulses that get filtered and converted into voltage through passive LF network. The simplest LF network consists of a resistor and a capacitor connected in series. The resulting control voltage ( $V_{CTRL}$ ) drives the VCO towards phase and frequency lock.

The negative feedback loop forces the divided-down VCO output phase to follow the reference clock phase. In steady state, the phase of the feedback clock is locked to the phase of the reference clock, where the phase error remains constant and ideally zero. This is why it is referred to as a phase locked loop. We use a feedback system based on phase rather than frequency to assure zero frequency error and exact frequency multiplication [2]. The

Figure 1.5: (a) Die photo of an eight-core POWER7 microprocessor using per-core clocking [1]. (b) Simplified block diagram of microprocessor frequency control.

output frequency is a multiple of the reference frequency:

$$F_{OUT} = N \times F_{REF} \tag{1.1}$$

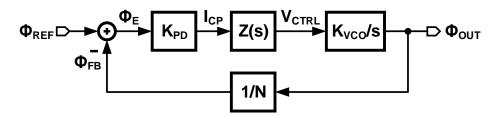

Like any other feedback system, PLL system has to be analyzed and designed carefully to guarantee loop stability. Ignoring the sampling nature of the PFD and the non-linear transient behavior of PLLs, a basic *s*-domain linear model is usually used for stability analysis. Each block is replaced by a linear representation of its function. PFD/CP is replaced by a difference block followed by a gain factor  $K_{PD}$ . The LF is replaced by its transfer function Z(s). The VCO is represented by a transfer function that simply relates its output  $F_{OUT}$  with  $V_{CTRL}$ , as:

$$F_{OUT} = F_O + K_{VCO} \times (V_{CTRL} - V_O)$$

(1.2)

where  $F_O$  is the VCO frequency when  $V_{CTRL} = V_O$ , and  $K_{VCO}$  is the VCO gain. Since phase is the integral of frequency, then the VCO can be replaced by a gain and an integrator  $K_{VCO}$ /s. A simple linear model of the PLL is shown in Fig. 1.7. In addition to stability analysis, this model is also used to study open and closed loop response, settling time, and phase noise of PLLs. Loop dynamics affect how the noise of each block appears at the output; for example, the VCO noise is high-pass filtered while reference, divider, and PFD/CP noise are low-pass filtered. Usually, the PLL bandwidth is chosen to optimize the overall jitter performance. While an integer-N PLL can achieve excellent jitter, its frequency resolution is limited by the reference frequency due to the nature of integer-N multiplication.

Figure 1.6: Simplified block diagram of integer-N charge pump PLL.

Figure 1.7: Linear model of charge pump PLL.

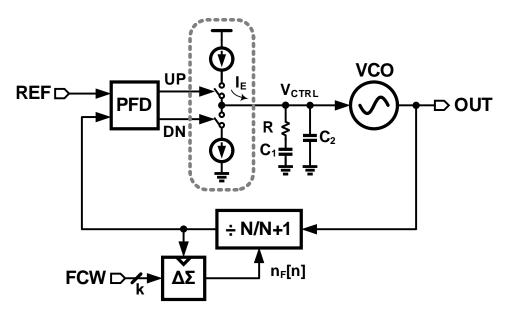

#### 1.2.2 Analog Fractional-N PLL

A fractional-N PLL (FNPLL) is an extension to integer-N PLL to perform fractional-N frequency multiplication with very fine frequency resolution (see Fig. 1.8), thus it can be used for phase modulation/frequency modulation (FM). Since the feedback divider is a digital circuit, it can only divide by an integer number. However, if the division factor is alternated between N and N + 1, effectively a fractional division is achieved. For example, N = 4 is used for 3 division cycles and N = 5 is used for 1 division cycle. On average, the input frequency is divided by 4.25. The simplest way to control the divider is passing a k-bit fractional control value  $\alpha$  to a k-bit digital accumulator. Then use the 1-bit carry out  $n_F[n]$  as a modulus control of the divider. The PLL still can lock in an average sense and the output frequency is related to the reference frequency by:

$$F_{OUT} = (N + avg(n_F[n])) \times F_{REF} = (N + \alpha) \times F_{REF}$$

(1.3)

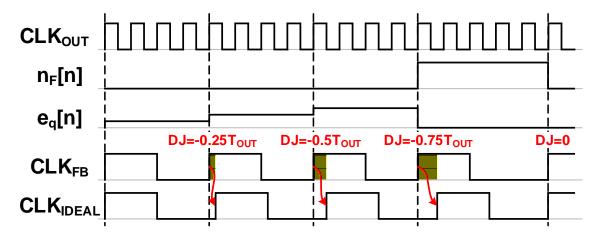

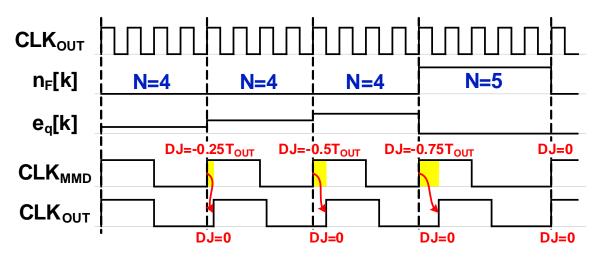

Although switching the division ratio instantaneously is simple to realize, this technique exhibits instantaneous frequency errors and introduces quantization noise  $e_q[n]$  into the loop.  $e_q[n]$  is low-pass filtered by the PLL feedback loop before appearing at the output as a deterministic jitter (DJ). Fig. 1.9 demonstrates the timing waveform of a fractional division of 4.25. A deterministic jitter of  $0.25 \times T_{OUT}$  appears in the feedback clock in the first cycle and accumulates to  $0.75 \times T_{OUT}$  by the third cycle. In the fourth cycle, the output clock aligns with the ideal clock. The deterministic jitter pattern repeats every four cycles and it is directly related to  $e_q[n]$  by  $DJ[n] = -e_q[n] \times T_{OUT}$ . This deterministic jitter will be filtered by the low-pass PLL transfer function before appearing at the output. Noise shaping techniques are commonly used to suppress in-band quantization noise in high resolution digital-to-analog converters (DACs). Similarly, noise shaping using digital delta-sigma ( $\Delta\Sigma$ ) modulators can reduce fractional divider quantization noise in FNPLL (which acts as a digital-to-frequency converter). By replacing the accumulator (which resembles a 1st order  $\Delta\Sigma$  modulator) by a higher order  $\Delta\Sigma$  modulator,  $e_q[n]$  is high-pass shaped, and exhibits more suppression by the same low-pass PLL transfer function.

Figure 1.8: Simplified block diagram of analog FNPLL.

Figure 1.9: Timing diagrams illustrating the fractional divider operation.

In many applications, suppressing  $e_q[n]$  by lowering the PLL bandwidth is undesirable, as it will increase the settling time and the VCO noise contribution. Because the fractional divider quantization noise is deterministic, conceptually it can be cancelled prior to the loop filter

Figure 1.10: Simplified block diagram of analog FNPLL with QNC.

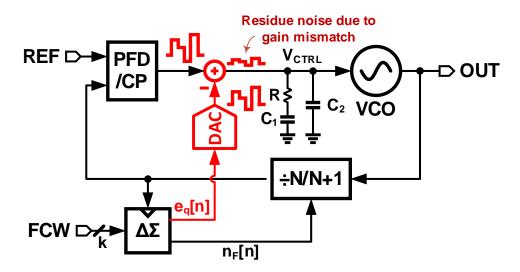

using a current DAC (see Fig. 1.10), thus eliminating the need for a narrow PLL bandwidth. The quantization noise cancellation (QNC) path extracts  $\Delta\Sigma$  quantization error  $e_q[n]$ , then converts it into a current pulse of duration  $T_{DAC}$  and amplitude  $-e_q[n] \times T_{VCO} \times I_{CP}/T_{DAC}$  for perfect QNC. However, in practice the gain of the DAC is never perfectly matched to the gain of the signal path through the PFD/CP as illustrated in Fig. 1.10. In [3], a sign-error least-mean-square (LMS) algorithm is used to adaptively calibrate the DAC gain to minimize the leaked quantization noise. Because of its high complexity and sensitivity to PVT variations, this technique does not provide an attractive solution.

#### 1.2.3 Digital Fractional-N PLL

With the advancement of CMOS technology, the performance of digital circuits is improved in terms of speed, power, and area. On the other hand, analog blocks do not really benefit from process scaling and usually encounter several design issues. Conventional charge-pump PLLs will suffer from capacitor leakage, current mismatch, and limited dynamic range. Recently, significant research efforts have focused on developing digital FNPLLs that obviate the need for large capacitors. Due to their highly digital nature, loop dynamics are easier to reconfigure and they are also easier to port from one process generation to other. For complex SoCs, developing a low jitter reconfigurable digital/synthesizable FNPLL with minimum area is highly desirable. However, like any mixed-signal feedback loop, the presence of an analogto-digital and a digital-to-analog conversion, represented by the time-to-digital converter (TDC) and the digitally controlled oscillator (DCO) respectively, introduces quantization errors in the loop. As a result, jitter performance of digital FNPLLs, especially those using ring oscillators, is grossly inferior to their analog counterparts.

In this dissertation, we developed novel injection locking and quantization noise cancellation techniques to mitigate the impact of quantization errors of the fractional divider, TDC, and DCO. We also implemented highly-scalable, digitally-enhanced realizations of frequency synthesis and clocking modules that can leverage the advancement of CMOS technology to minimize the power consumption.

#### 1.3 Dissertation Organization

The focus of this dissertation is on developing digital enhancement, injection locking, and noise cancellation techniques to realize low jitter, low power, fractional-N clocking schemes. The dissertation consists of seven chapters organized as follows:

Chapter 2 discusses the design of a low power LC digital FNPLL for wireless and wireline transceivers. It leverages a high resolution digital-to-time converter (DTC) to alleviate the TDC dynamic range requirements of conventional DPLLs. The proposed digital architecture uses a narrow range low-power time-amplifier based TDC (TA-TDC) with sub-1ps resolution to achieve wide PLL bandwidth and excellent jitter performance at a low power consumption.

Chapter 3 seeks to close the performance gap of ring-based PLLs compared to their LC counterparts, in order to leverage ring VCO merits of wide-range, multi-phases, and small area. The proposed digital FNPLL features a dual-path digital loop filter architecture to resolve the DAC quantization noise challenge, which is stressed by the large gain of ring VCOs. This maximizes the suppression of ring VCO phase noise. This chapter also discusses and analyzes the design details of a new, extended range, multi-modulus divider that enables seamless switching at the boundaries extension.

Chapter 4 presents a new multi-output clock generator architecture using open loop fractional dividers. The open loop architecture overcomes the bandwidth limitation in fractionalN PLLs. It enables flexible per-core clocking in modern multi-core processors with instantaneous dynamic frequency scaling with no overshoots, and unrestricted spread spectrum modulation to satisfy different EMI requirements.

Injection-locked clock multipliers (ILCMs) provide many advantages in terms of phase noise, power, and area compared to classical PLLs, but they suffer from a narrow lock-in range and a high sensitivity to PVT variations especially at a large multiplication factor (N). In Chapter 5, the design and analysis of low-jitter LC-based ILCM with a digital frequencytracking loop (FTL) is presented. It also introduces an accurate theoretical large-signal analysis for phase domain response (PDR) of ILCMs.

Chapter 6 seeks to extend the merits of ILCM to fractional-N and overcome its fundamental limitation to integer-N operation. The proposed architecture relies on DTC-based quantization noise cancellation (QNC) techniques to align the injected pulses to the oscillator's zero crossings, and hence ensures its phase locking. This chapter will discuss the means to realize rapid on/off operation, by which considerable energy saving is achieved by turning on the clock multiplier only when needed.

Finally, Chapter 7 concludes the discussion about the proposed design techniques, open loop fractional divider architecture, and rapid on/off injection locking clock multiplication architectures presented in this dissertation.

### CHAPTER 2

## LOW POWER LC-BASED DIGITAL FRACTIONAL-N PLL

#### 2.1 Introduction

Fractional-N phase locked loops (FNPLLs) are key building blocks in many systems-onchips (SoCs) and wireless transceivers [4–14]. FNPLLs offer flexibility in frequency planning using only a single-crystal reference clock and are therefore well-suited for realizing singlechip multi-standard solution in wireline applications. In all these applications, a wide PLL bandwidth is desirable as it helps improve both system- and circuit-level performance in multiple ways. For instance, it helps to improve jitter tolerance of wireline receivers [15, 16] and increase data modulation bandwidth and settling time in wireless transmitters [12,14]. At circuit level, wide bandwidth results in: (a) larger suppression of oscillator phase noise, which helps to reduce the power, (b) better immunity to pulling [17], and (c) faster settling time. However, achieving low jitter (<1ps<sub>rms</sub>) and wide bandwidth (2MHz - 5MHz) using less than 50MHz reference frequency is challenging mainly because of the presence of quantization error from feedback fractional divider and time-to-digital converter (TDC). For example, [11] suffers from degraded jitter performance when bandwidth is increased to 5MHz due to its band-bang phase detector (BBPD) quantization noise, while [10] relies on a high performance TDC with extensive calibration to achieve 3MHz bandwidth at the expense of large power and area.

Analog charge-pump PLL has been the most preferred architecture to implement fractional-N frequency generation. Using bandwidth extension techniques typically based on divider

<sup>\*© 2015</sup> IEEE. Part of this chapter is reprinted, with permission, from A. Elkholy, T. Anand, W.-S. Choi, A. Elshazly and P. K. Hanumolu, "A 3.7 mW Low-Noise Wide-Bandwidth 4.5 GHz Digital Fractional-N PLL Using Time Amplifier-Based TDC," in IEEE J. of Solid-State Circuits, vol. 50, no. 4, pp. 867–881, April 2015.

quantization noise cancellation (QNC), analog PLLs were shown to achieve wide bandwidth, excellent jitter and spurious performance as reported in [12–15]. However, an analog PLL loop filter occupies large area and is difficult to reconfigure. To overcome these drawbacks, digital DPLLs that obviate the need for large capacitors have been proposed [4]. Due to their highly digital nature, loop dynamics are easier to reconfigure and they are also easier to port from one process generation to other.

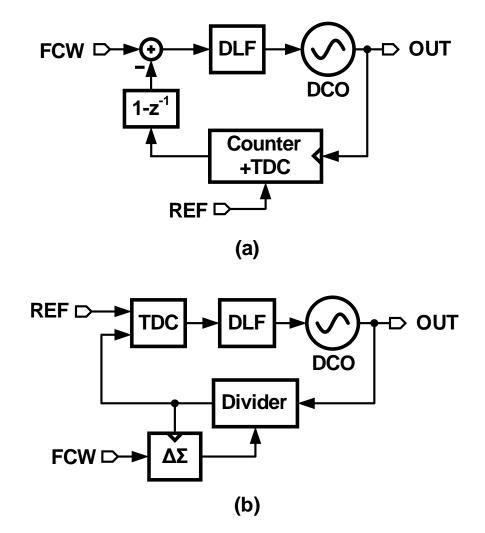

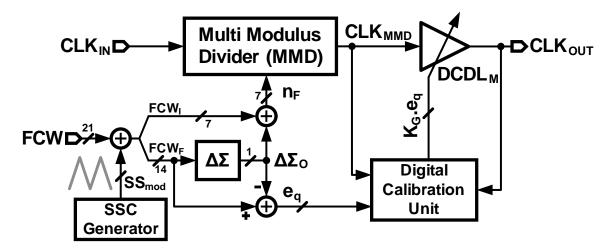

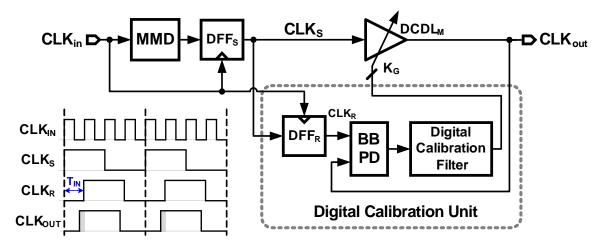

A digital FNPLL is most commonly implemented using one of the two architectures depicted in Fig. 2.1. The main difference between the two architectures is in the way the phase error is calculated. In the so called *phase domain* PLL, the phase of the oscillator is determined by counting the number of zero-to-one output transitions while the reference phase is obtained by accumulating the frequency control word (FCW) on every rising edge of the synchronized reference clock [4]. A simple arithmetic logic determines the phase error by subtracting the oscillator phase from the reference phase. Because counter-based phase detection provides an estimate of the phase only with an accuracy of one oscillator period, a high resolution TDC is used to measure the residual phase error. In the architecture shown in Fig. 2.1(b), the feedback divider implicitly accumulates the oscillator phase and the phase error between the reference clock and the divider output is determined by using a TDC [5]. In both the architectures, a high performance TDC with sub-ps resolution and at least one oscillator period measurement range is needed. Hence, we refer to both of them as TDC-based digital FNPLLs.

Recently, digital-to-time converter (DTC)-based digital FNPLLs were proposed to ease the resolution requirements of the TDC [9,18]. Based on the assumption that a high resolution DTC can be designed more power efficiently and with less hardware complexity compared to a TDC, a high resolution DTC is cascaded with a bang-bang phase detector (BBPD) to implement a digital FNPLL that behaves more over like an integer-N PLL [9]. However, BBPD, digitally controlled oscillator (DCO), and fractional divider introduce quantization errors at different points in the loop and their contribution to output phase noise increases with the loop bandwidth. Hence, a wide bandwidth PLL requires higher resolution TDC along with quantization noise cancellation techniques to mitigate fractional divider quantization noise, as described in Section 2.2. In other words, digital FNPLLs suffer from conflicting band-

Figure 2.1: Block diagram of conventional digital FNPLL implementation using (a) counter-based divider-less architecture, and (b)  $\Delta\Sigma$  fractional divider.

width requirements imposed by oscillator phase noise and the quantization error introduced by the TDC and fractional divider.

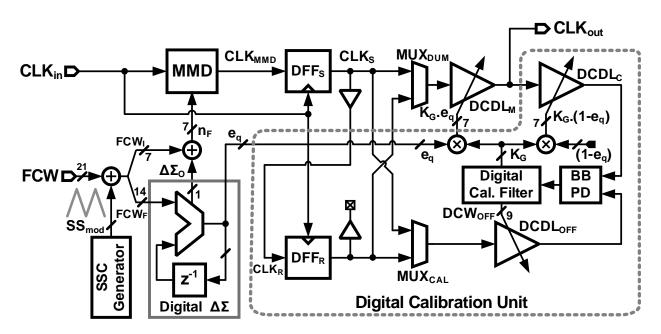

In this chapter, we present digital enhancement techniques to increase the bandwidth of DTC-FNPLLs [19]. Using a high resolution low-power time-amplifier (TA) based TDC (TA-TDC) in combination with a DTC, the FNPLL achieves an in-band noise of -106dBc/Hz and integrated jitter of  $490 f_{\rm srms}$  at 4.5GHz output frequency and has a bandwidth higher than 3MHz ( $F_{\rm REF}/16$ ). The entire PLL consumes 3.7mW from 1V supply and achieves an FoM of -240.5dB.

The rest of the chapter is organized as follows. After a brief overview of state-of-the-art digital FNPLLs in section 2.2, the proposed architecture is presented in section 2.3. The

circuit implementation of critical building blocks is illustrated next in section 2.4. The measured results from the test chip are shown in section 2.5. Finally, the key contributions of this chapter are summarized in section 2.6.

#### 2.2 TDC- and DTC-based Digital Fractional-N PLLs

A TDC-based digital FNPLL is obtained from a conventional charge-pump FNPLL by replacing the phase detector/charge-pump, analog loop filter, and VCO by TDC, digital loop filter, and DCO, respectively (see Fig. 2.1(b)). The TDC acts as a digital phase detector and its output is filtered by a digital loop filter and then used to control the DCO. Fractional-N operation is achieved by dithering the multi-modulus divider using a delta-sigma ( $\Delta\Sigma$ ) modulator. The most challenging aspect of designing a low noise, wide bandwidth, low power digital FNPLL is the design of a wide dynamic range, high resolution TDC. The dynamic range of the TDC must be large enough to measure the time difference between the reference clock and the dithered feedback clock. Consequently, the TDC range must be at least one DCO period when the fractional divider is dithered by a first order  $\Delta\Sigma$  modulator and several DCO periods for higher order modulators.

Figure 2.2: Digital FNPLL architecture with  $\Delta\Sigma$  quantization noise cancellation (QNC).

Because TDC quantization noise is low-pass filtered by the PLL's feedback loop, it limits in-band phase noise of the PLL. For instance, achieving -110dBc/Hz in-band phase noise of a

4GHz PLL operating with 40MHz reference requires the TDC resolution to be less than 3ps. Assuming second order  $\Delta\Sigma$  modulator in the fractional divider, the TDC has to cover at least 2 DCO periods ( $\sim$ 500ps), which is very difficult to achieve in practice. Additionally, nonlinearity of the TDC further exacerbates in-band noise by folding the shaped quantization noise of the  $\Delta\Sigma$  divider [7]. It is also shown to introduce in-band fractional spurs that are difficult to predict and hence are difficult to suppress. The detrimental impact of TDC quantization error on in-band noise and fractional spurs increases at wider PLL bandwidth, which puts even more stringent requirements on the TDC.

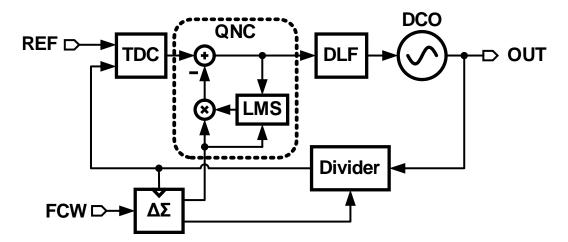

The  $\Delta\Sigma$  fractional divider quantization noise, E<sub>Q</sub>, impacts both analog and digital PLLs alike. Because  $E_Q$  is low-pass filtered by the PLL feedback loop, it can only be suppressed by lowering the PLL bandwidth, which is undesirable in many applications. As a result, several bandwidth extension techniques based on quantization noise cancellation (QNC) were proposed for both analog [12, 13, 20] and digital PLLs [5]. A digital QNC scheme, shown in Fig. 2.2, seeks to cancel  $E_Q$  by extracting the  $\Delta\Sigma$  quantization error, scaling it with a calibrated gain and subtracting it from the TDC output [5]. The digital implementation makes this technique insensitive to analog inaccuracies and PVT variations present in analog charge-pump PLLs. However, cancelling divider quantization noise after the TDC requires a high-performance wide-range TDC. Hence, high performance TDC is critical to the implementation of low noise wide bandwidth digital FNPLLs. Consequently, over the past decade, significant research efforts have focused on the design of wide dynamic range, high resolution, and highly linear TDCs. Several architectures have been proposed that mimic the operation of ADCs: flash (delay line [4], vernier lines [8], parallel delay lines [7]), two-step [21], pipelined [22], and noise shaped [5, 23]. Most of these techniques adopt analog-intensive design approaches with complex calibration schemes to achieve sub-gate delay resolution. As a result, they occupy large area and consume high power.

A DTC-based digital FNPLL shown in Fig. 2.3 was proposed as a power efficient alternative to TDC-based FNPLLs [7,9,24]. The DTC in the feedback path is used to cancel the  $\Delta\Sigma$  quantization noise at the output of the fractional divider. As a result, the TDC dynamic range requirement is relaxed. For instance, in [7], 4-bit DTC is implemented using 16-stage delay locked loop and a phase selection multiplexor to reduce  $E_Q$  by 1/16 and

Figure 2.3: A DTC-based bang-bang phase detector (BBPD) digital FNPLL implementation.

consequently relax the TDC requirements to 4-bit. However, the non-linearity of the DTC caused by mismatch between delay cells and routing paths severely degrades the spurious and in-band noise performance of the PLL. To mitigate these non-linear errors, complex background non-linearity calibration techniques such as those reported in [7] were employed at the expense of large area, high power, and long settling time. To overcome these drawbacks, a 10-bit DTC implemented using a digitally controlled delay line (DCDL) whose gain is accurately calibrated using a least-mean square (LMS) technique to implement a truly fractional divider was proposed in [9]. The high resolution DTC limits the input range of TDC to within the random noise range, as the reference and feedback clocks are now aligned as in the case of an integer-N PLL. Consequently, the wide range requirement of the TDC is alleviated and a simple 1-bit TDC or bang-bang phase detector (BBPD) is adequate [9].

A BBPD can be implemented power efficiently using a single flip-flop (FF). However, its large quantization error and grossly non-linear behavior limit its use in wide bandwidth PLLs. In [25], the non-linear dynamics of second-order BB-PLL are analyzed to find the condition for loop stability. The behavior of BB-PLLs is a strong function of loop gain and delay. If the loop gain is made large to achieve wide bandwidth, the steady-state of the BB-PLL becomes a bounded limit cycle, which manifests as undesirable fractional spurs and large peaking in the phase noise [26]. If the loop gain is reduced, BBPD operates in a random-noise limited regime and the PLL exhibits linear response. In [26], it was illustrated that there is optimal loop gain and consequently loop bandwidth that minimizes the PLL's overall noise. This optimum noise performance is usually achieved at relatively low PLL bandwidth (312kHz in [9]). Furthermore, the gain of BBPD operating in noise-limited regime depends on the noise at its input, which not only makes the loop dynamics difficult to control but also makes the PLL bandwidth sensitive to reference clock jitter [25].

In addition to the BBPD-related issues, the non-idealities of the DTC also have significant impact on the performance of the FNPLL. The integral non-linearity (INL) of the DTC causes imperfect QNC and appears as a periodic error at the BBPD input. If the magnitude of DTC INL is larger than random noise, it reduces BBPD gain and leads to an increase in the in-band phase noise and generation of spurious tones [24]. Finally, the architecture in [9] also suffers from long settling time for DTC gain calibration, as 1-bit is used only in LMS correlation. In view of these drawbacks, we propose a digital fractional-N PLL architecture that employs a narrow range high resolution TDC in addition to a truly fractional divider to achieve low jitter, wide bandwidth, and low power consumption.

# 2.3 Proposed Wide-Bandwidth Digital FNPLL Architecture