© 2016 Guanghua Shu

#### ENERGY-EFFICIENT WIRELINE TRANSCEIVERS

ΒY

#### **GUANGHUA SHU**

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2016

#### Urbana, Illinois

Doctoral Committee:

Associate Professor Pavan Kumar Hanumolu, Chair Associate Professor Rakesh Kumar Professor José Schutt-Ainé Professor Naresh Shanbhag

## ABSTRACT

Power-efficient wireline transceivers are highly demanded by many applications in high performance computation and communication systems. Apart from transferring a wide range of data rates to satisfy the interconnect bandwidth requirement, the transceivers have very tight power budget and are expected to be fully integrated. This thesis explores enabling techniques to implement such transceivers in both circuit and system levels. Specifically, three prototypes will be presented:  $(1) a 5 \,\mathrm{Gb/s}$  reference-less clock and data recovery circuit (CDR) using phase-rotating phase-locked loop (PRPLL) to conduct phase control so as to break several fundamental trade-offs in conventional receivers; (2) a 4-10.5 Gb/s continuous-rate CDR with novel frequency acquisition scheme based on bang-bang phase detector (BBPD) and a ring oscillator-based fractional-N PLL as the low noise wide range DCO in the CDR loop; (3) a source-synchronous energy-proportional link with dynamic voltage and frequency scaling (DVFS) and rapid on/off (ROO) techniques to cut the link power wastage at system level. The receiver/transceiver architectures are highly digital and address the requirements of new receiver architecture development, wide operating range, and low power/area consumption while being fully integrated. Experimental results obtained from the prototypes attest the effectiveness of the proposed techniques.

## ACKNOWLEDGMENTS

It is my great fortune to meet so many people who have made my Ph.D. journey challenging, rewarding, and memorable. I give them my heartfelt thanks for their contributions to my research and personal growth.

First and foremost, my gratitude to my advisor Prof. Pavan Kumar Hanumolu comes from the bottom of the heart, for his excellent guidance, encouragement, and patience. His vision in the field of integrated circuits keeps my eyes open, and his passion in research will always inspire me. Through the years, I have also been trying to pick up a little of his great ability to explain new concepts with clarity. I consider myself truly fortunate to work with him, the best research advisor one can wish for. I hope I can always count on his advice and friendship in the future.

I would also like to extend my sincerest thanks to Prof. Rakesh Kumar, Prof. José Schutt-Ainé, and Prof. Naresh Shanbhag for being on my doctoral committee. Their feedback has helped to extend my research horizon and improved the quality of this thesis. I am also indebted to Prof. Un-Ku Moon at Oregon State University, not only for his insightful lectures on circuit designs, but also for his kind support at various stages of my Ph.D. study. Thanks are also due to Prof. Franke and Laurie Fisher for providing a smooth transfer from Oregon State University to the University of Illinois. I am also grateful for Rachel Glasa, and subsequently Jennifer Summers, for their assistance in all kinds of administrative work, and James Hutchinson, for his excellent editorial help to improve the thesis quality.

I am also greatly indebted for all the help and mentorship I have received from: John Bulzacchelli (IBM), Mounir Meghelli (IBM), Dan Friedman (IBM), Jack Kenney (ADI), Ken Chang (Xilinx), Yong Liu (Broadcom), Jon Proesel (IBM), Tod Dickson (IBM), Alexander Rylyakov (Coriant), Mohamed Elzeftawi (Samsung), Jafar Savoj(Apple), and Ganesh Balamurugan (Intel). Their help and advice kept my eyes open about the research and development in industry, which is of great benefit to my graduate research.

Another important part of this journey is the great friends I have made over these years. They not only introduced great fun into my school life, but also played an essential role in my graduate research. Yue Hu, Xin Meng, Rui Bai, Yichen Zhao, Hui Guo, Luyang Yang, and Xun Sun helped me settle in the US smoothly, and made excellent company for my two years' stay in Corvallis. Sincere thanks to senior group members Amr Elshazly, Rajesh Inti, Qadeer Khan, Sachin Rao, Karthik Reddy, Wenjing Yin, and Brian Young for their guidance at the early stage of my Ph.D. study and for being forthcoming with their advice even after their graduations.

Ahmed Elkholy, Mrunmay Talegaonkar, Romesh Nandwana, Saurabh Saxena, Seong-Joong Kim, Tejasvi Anand, and Woo-Seok Choi carried on the journey to University of Illinois; they are really brilliant and enthusiastic colleagues and friends (including Praveen Prabha who missed the party in Illinois). This five years' time will always be deep in my memory, be it the late nights when we were fighting to catch up with the tape-out shuttle, or the short sneak-out during the busy conference schedule. Especially, I want to thank Woo-Seok Choi, Saurabh Saxena, and Mrunmay Talegaonkar. They have been perfect intellectual walls off which to bounce all kinds of different ideas. With a strong background in mathematics, Woo-Seok always finds the insightful abstract for the problems and often brings the ideas to a new level or disproves them before it gets too late. Saurabh is a perfect detail-oriented circuit designer. He always puts the discussion into circuit perspectives and brings the ideas down to the earth. Mrunmay is very knowledgeable and, more importantly, he always gives very objective suggestions with his insight, which has saved me many times from being biased by own limited view. Their help, along with that from other group members, is critical in completing this thesis research. The excellence of Prof. Hanumolu's group has been preserved with many recent new members. Junheng Zhu, Dongwook Kim, Mostafa Ahmed, Ahmed Elmallah, Da Wei, Timir Nandi, Danniel Coombs, Braedon Salz, Hyun-Jae Ko, and Tianyu Wang are a pleasure to work with. I hope they will have as much fun as I did, or even more, in such a great environment.

Last and most important, I wish to thank my family for their unconditional love and support. My parents believe in the value of education and did their best to provide me the best possible education, even if it means I need to study abroad far away from them. I thank my brother (Guangliang) for constantly caring about my progress and taking the whole responsibility as a son in the family when I am away. I am truly fortunate to have my wife (Yanliang) with me in the US. She is so patient and considerate of my extremely dynamic working hours, and even attempts to understand how circuits work although she is from a totally different professional area. They have my deepest gratitude for all their endless love and support. To them, I dedicate this thesis.

# TABLE OF CONTENTS

| LIST OF TABLES                                                                                                                                                                                                                                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LIST OF FIGURES                                                                                                                                                                                                                                        |  |

| CHAPTER 1 INTRODUCTION11.1 Motivation11.2 Thesis Organization2                                                                                                                                                                                         |  |

| CHAPTER 2WIRELINE TRANSCEIVER OVERVIEW52.1Transceiver Operation52.2CDR Performance Metrics112.3Conventional CDR Limitations162.4Summary19                                                                                                              |  |

| CHAPTER 3A REFERENCE-LESS CDR USING PHASE-ROTATINGPLL203.1Background213.2Proposed CDR Architecture233.3Circuit Design293.4Experimental Results36                                                                                                       |  |

| 3.5Summary45CHAPTER 4A CONTINUOUS-RATE DIGITAL CLOCK AND<br>DATA RECOVERY WITH AUTOMATIC FREQUENCY AC-<br>QUISITION484.1Automatic Frequency Acquisition514.2Overall CDR Architecture554.3Circuit Implementation594.4Experimental Results644.5Summary74 |  |

| 4.5Summary74CHAPTER 5AN ENERGY-PROPORTIONAL SOURCE-SYNCHRONOUSLINK WITH DVFS AND ROO TECHNIQUES765.1Energy-Proportional Link with DVFS and ROO775.2Circuit Implementation80                                                                            |  |

| 5.3 Experimental Results                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4 Summary $\ldots \ldots \ldots$     |

| CHAPTER 6 CONCLUSION                                                                                                                                   |

| 6.1 Conclusions $\ldots \ldots \ldots$ |

| 6.2 Future Work $\ldots \ldots \ldots$ |

| APPENDIX A RELIABILITY ANALYSIS OF PROPOSED FRE-                                                                                                       |

| QUENCY ACQUISITION SCHEME                                                                                                                              |

| A.1 FLL Locking Reliability with Conventional DCO 106                                                                                                  |

| A.2 FLL Locking Reliability with Fractional-N PLL-based DCO $$ . 108                                                                                   |

| APPENDIX B ANALYSIS OF LINKS WITH DVFS AND ROO                                                                                                         |

| TECHNIQUES USING QUEUE MODEL                                                                                                                           |

| B.1 Comparison between DVFS and ROO                                                                                                                    |

| B.2 Combine DVFS and ROO                                                                                                                               |

| B.3 Simulation Results                                                                                                                                 |

| APPENDIX C DISCUSSION ON $\alpha$ -POWER LAW MODEL FOR                                                                                                 |

| MOSFET AND ITS EFFECT ON DVFS                                                                                                                          |

| C.1 Scaling of Supply Voltage and Data Rate                                                                                                            |

| C.2 Scaling of Active Power of Difference Circuit                                                                                                      |

| C.3 Power Scaling of Link Transceivers with $\alpha\text{-Power Law Model}$ . 120                                                                      |

| REFERENCES                                                                                                                                             |

# LIST OF TABLES

| $3.1 \\ 3.2 \\ 3.3$ | PRPLL performance summary and comparison40RCK and SCK jitter versus different data sequences42Receiver performance summary and comparison45 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1                 | CDR performance summary and comparison with the state-<br>of-the-art designs                                                                |

| 5.1                 | Transceiver performance summary and comparison with<br>the state-of-the-art designs                                                         |

| C.1                 | Power scaling of link transceiver building blocks                                                                                           |

| C.2                 | Power distribution of a source-synchronous link transceiver                                                                                 |

|                     | $@ 10 Gb/s \dots \dots$               |

| C.3                 | Power distribution of an embedded clock link transceiver                                                                                    |

|                     | per channel @ $6.25$ Gb/s                                                                                                                   |

# LIST OF FIGURES

| $1.1 \\ 1.2$ | Application scenario of wireline transceivers               | 2  |

|--------------|-------------------------------------------------------------|----|

| 1.2          | (b) energy efficiency                                       | 3  |

| $2.1 \\ 2.2$ | Block diagram of a wireline transceiver                     | 5  |

| 2.3          | random NRZ/RZ patterns                                      | 7  |

| 2.0          | tween data (DIN) and clock (CK).                            | 8  |

| 2.4          | Link classification based on clocking schemes.              | 10 |

| 2.5          | Recover clock and data with VCO-based CDR                   | 10 |

| 2.6          | Equalizer compensates for channel loss                      | 11 |

| 2.7          | Receiver performance consideration.                         | 12 |

| 2.8          | Typical jitter transfer response.                           | 13 |

| 2.9          | Typical jitter tolerance response.                          | 14 |

| 2.10         | Jitter contribution in data eye diagram                     | 15 |

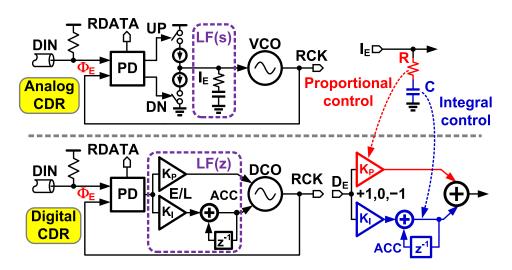

| 2.11         | Transition from analog CDR to digital CDR                   | 16 |

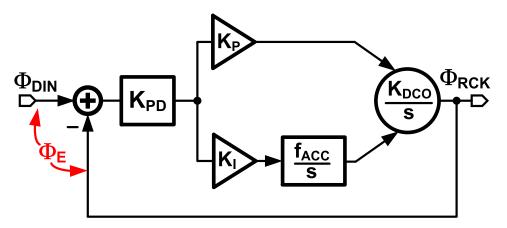

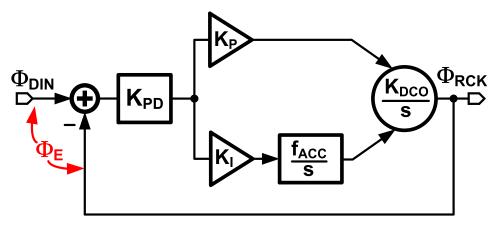

| 2.12         | Loop dynamics of VCO-based digital CDR                      | 17 |

| 2.13         | Relationship between JTRAN bandwidth and JTOL cor-          |    |

|              | ner frequency.                                              | 18 |

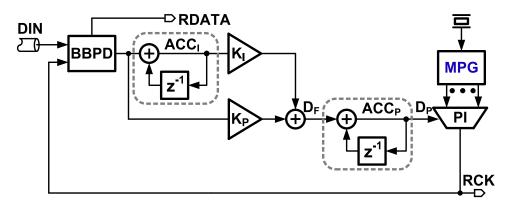

| 3.1          | Phase interpolator-based sub-rate CDR                       | 21 |

| 3.2          | Block diagram of a PRPLL.                                   | 23 |

| 3.3          | Evolution of the proposed CDR                               | 25 |

| 3.4          | Linearized phase-domain model of the proposed CDR           | 28 |

| 3.5          | Detailed schematic of the proposed reference-less PRPLL-    |    |

|              | based CDR.                                                  | 29 |

| 3.6          | Schematic of phase-rotating PLL with quadrant segmentation. | 30 |

| 3.7          | Phase-rotating process in PRPLL.                            | 31 |

| 3.8          | Schematic of combined XORPD and charge pump (XORPD-         |    |

|              | CP)                                                         | 32 |

| 3.9          | Schematic of the limiting amplifier.                        | 32 |

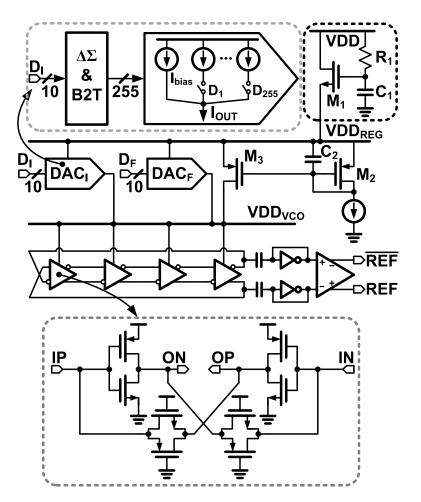

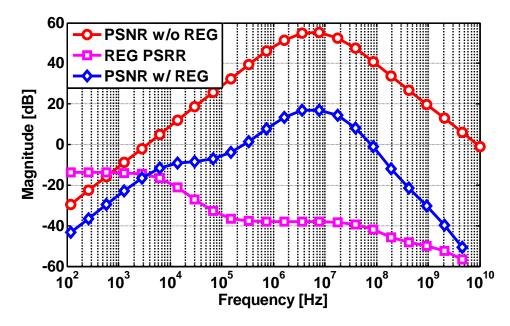

| 3.10         | Half-rate bang-bang phase detector.                         | 33 |

| 3.11         | Schematic of supply-regulated digitally controlled oscilla- |    |

|              | tor (DCO). $\ldots$                                         | 34 |

| 3.12  | Simulated CDR power supply noise rejection transfer func-                            |          |

|-------|--------------------------------------------------------------------------------------|----------|

|       | tions with and without the regulator                                                 | 36       |

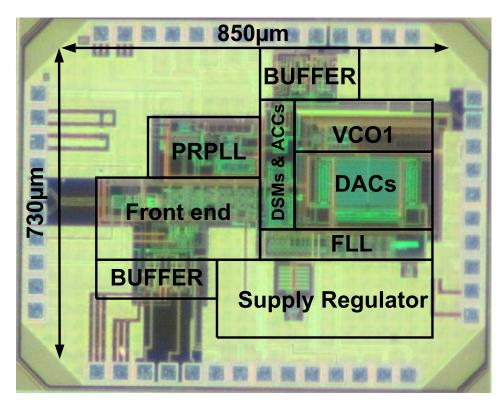

| 3.13  | Die micrograph                                                                       | 37       |

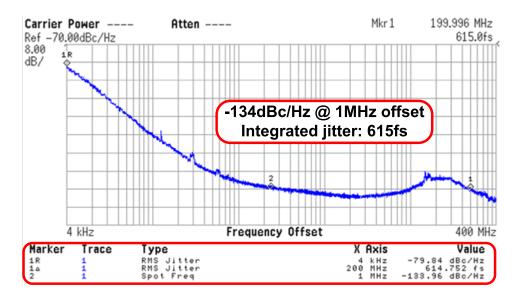

| 3.14  | Measured PRPLL phase noise plot                                                      | 37       |

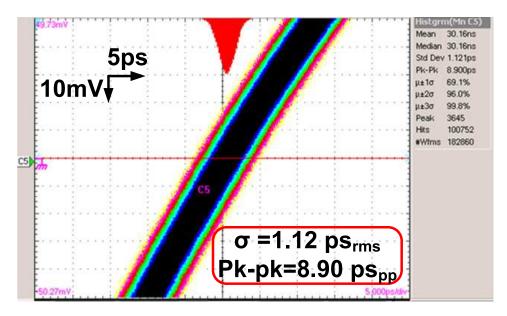

| 3.15  | PRPLL output jitter histogram                                                        | 38       |

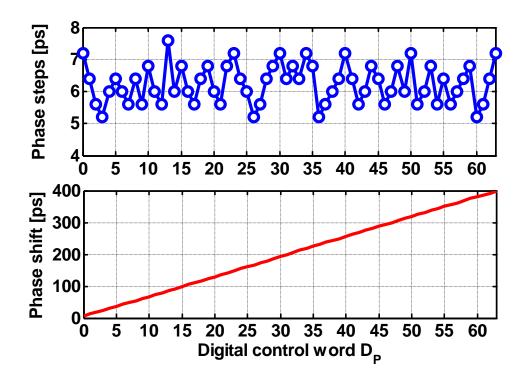

| 3.16  | Measured digital to phase transfer characteristics of the PRPLL.                     | 39       |

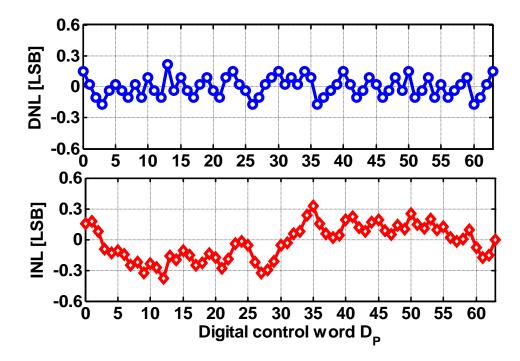

| 3.17  | Measured phase interpolation linearity (DNL and INL) of                              |          |

|       | the PRPLL                                                                            | 39       |

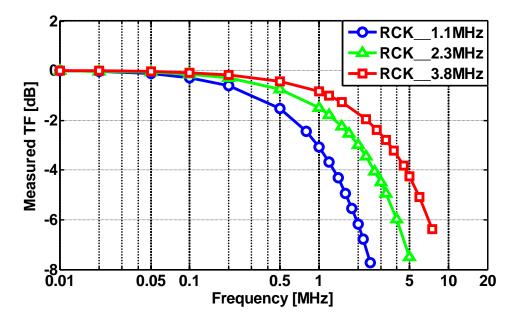

|       | Measured jitter transfer function with different gain settings                       | 41       |

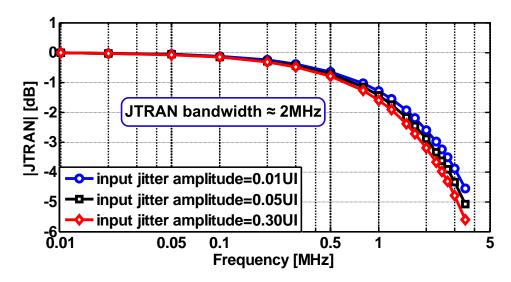

|       | Measured JTRAN with different input jitter amplitudes                                | 41       |

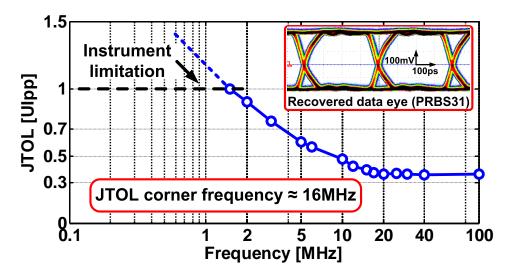

| 3.20  | Measured jitter tolerance with a BER threshold of $10^{-12}$<br>and PRBS7 input data | 42       |

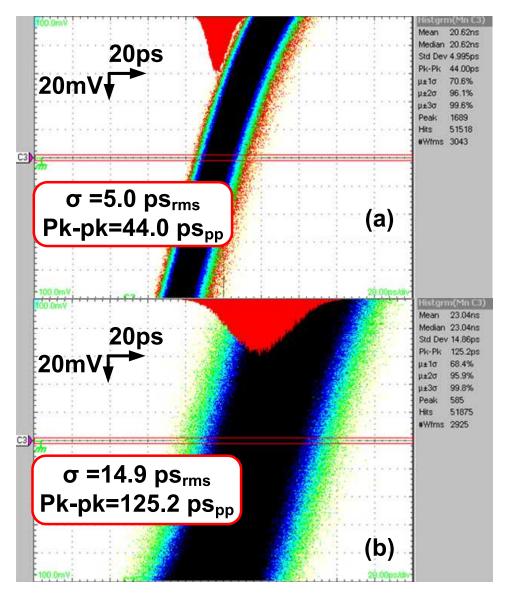

| 3.21  | Measured RCK and SCK jitter with PRBS31 input data:                                  |          |

|       | (a) RCK jitter, (b) SCK jitter                                                       | 43       |

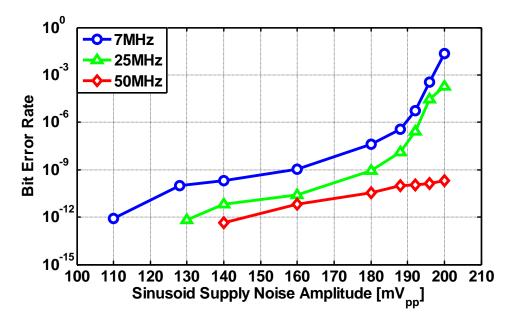

| 3.22  | Measured BER as a function of supply noise amplitude at                              |          |

|       | different noise frequencies with PRBS31 input data                                   | 44       |

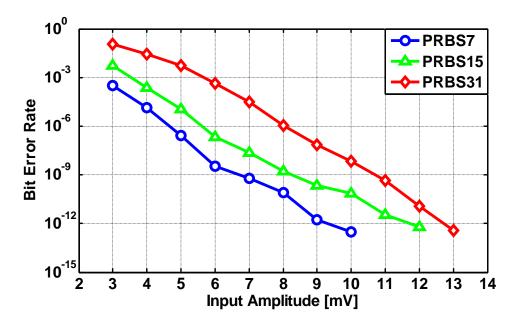

| 3.23  | Measured BER as a function of input amplitude for differ-                            |          |

|       | ent PRBS sequences.                                                                  | 45       |

| 4 1   |                                                                                      |          |

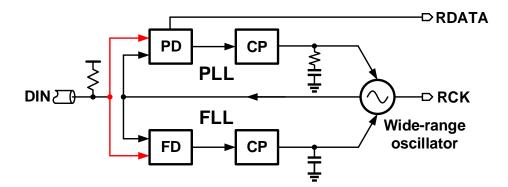

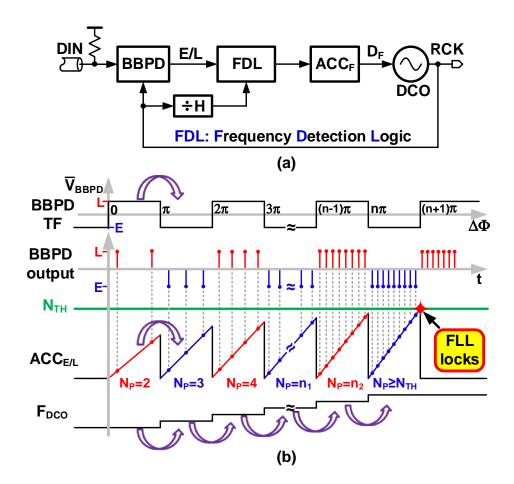

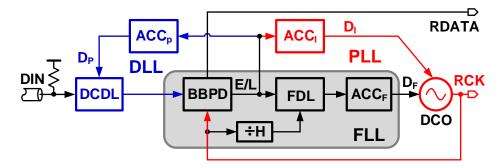

| 4.1   | Block diagram of a continuous-rate CDR with automatic                                | 10       |

| 4.0   | frequency acquisition.                                                               | 48       |

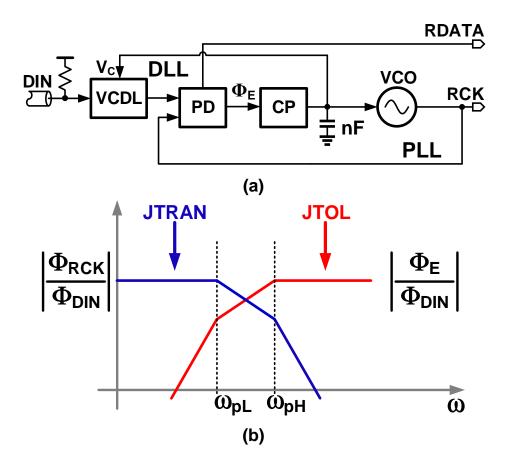

| 4.2   | (a) Analog D/PLL architecture with large loop filter capac-                          |          |

|       | itor, and (b) jitter transfer (JTRAN) and jitter tolerance                           | 50       |

| 4.0   | (JTOL) in D/PLL.                                                                     | 50       |

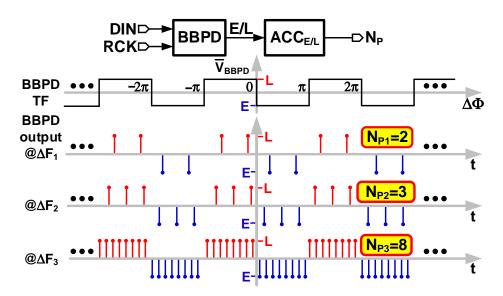

| 4.3   | Operations of a bang-bang phase detector.                                            | 52       |

| 4.4   | Principle of proposed frequency acquisition scheme: (a)                              |          |

|       | diagram of a BBPD-based frequency locking loop, and (b)                              | - 1      |

|       | operation of a BBPD-based frequency locking loop.                                    | 54       |

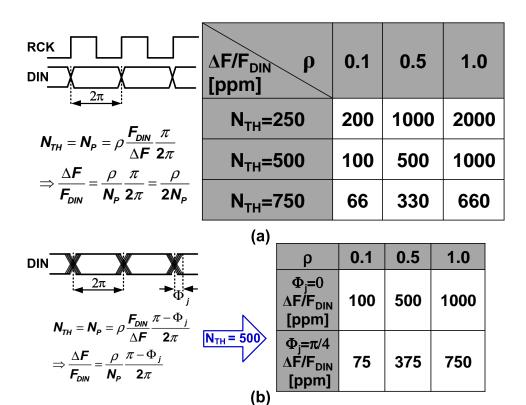

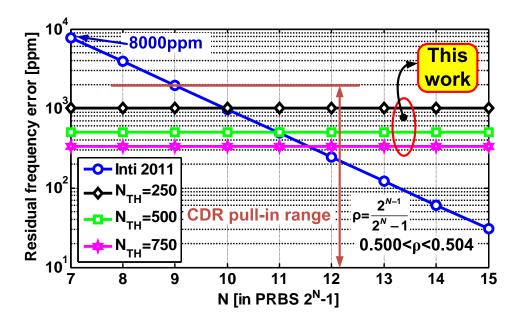

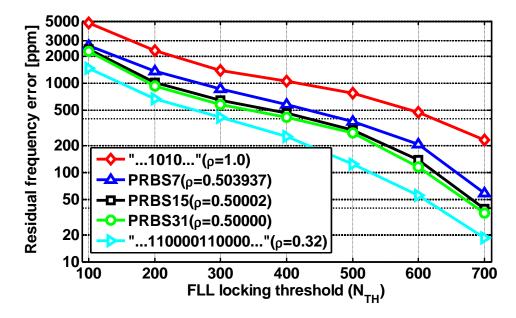

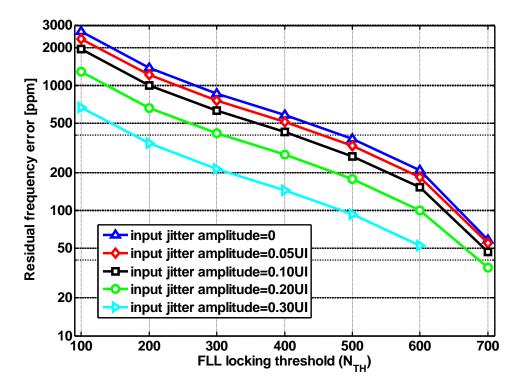

| 4.5   | Residual frequency error dependence on transition density:                           | 50       |

| 1.0   | (a) w/o jitter, and (b) w/ jitter. $\ldots$                                          | 56       |

| 4.6   | Residue frequency error comparison between proposed scheme                           | 50       |

| 4 🗁   | and SRCG.                                                                            | 56       |

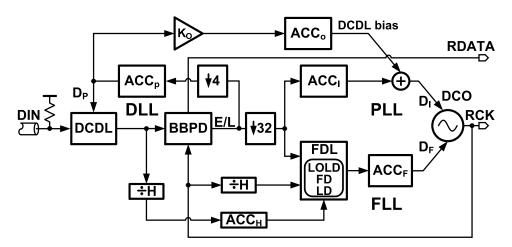

| 4.7   | Digital implementation of D/PLL CDR architecture                                     | 57       |

| 4.8   | Complete schematic of the proposed continuous-rate CDR                               | 58       |

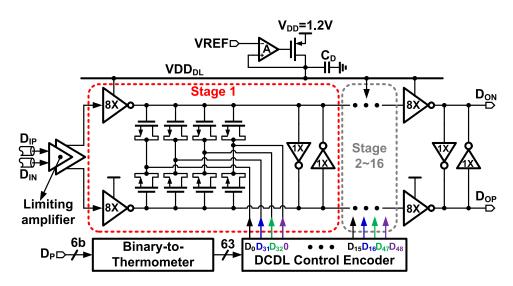

| 4.9   | Schematic of the digitally controlled delay line                                     | 60       |

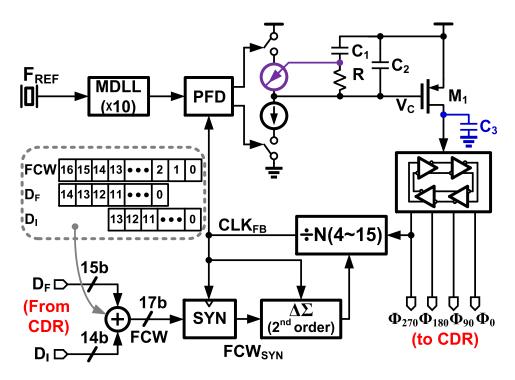

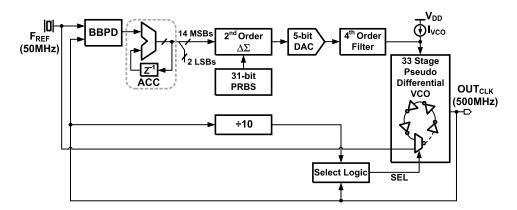

| 4.10  | Schematic of ring oscillator-based fractional-N PLL as DCO.                          | 61       |

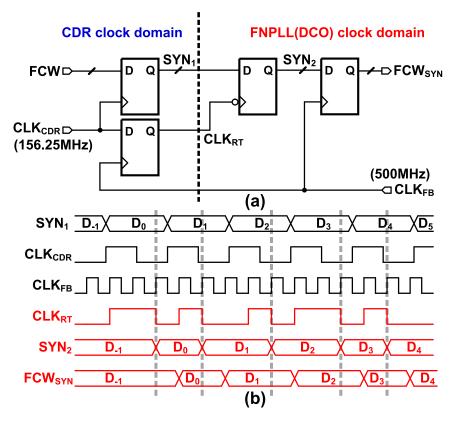

|       | FCW synchronization from CDR to DCO.                                                 | 62       |

|       | Schematic of the digital multiplying DLL (MDLL).                                     | 63       |

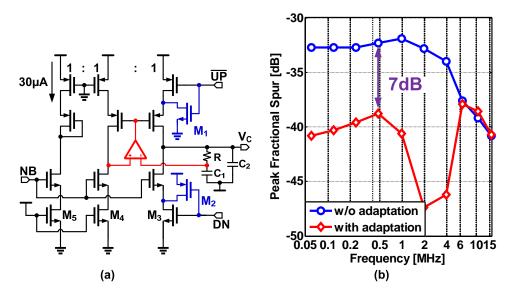

| 4.13  | Charge pump with adaptation loop: (a) circuit schematic,                             | C 4      |

| 1 1 1 | and (b) effectiveness on suppressing in-band fractional spurs.                       | 64       |

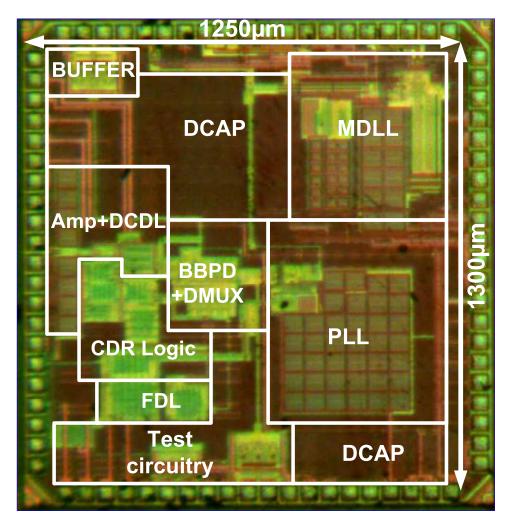

|       | Die micrograph.                                                                      | 65<br>66 |

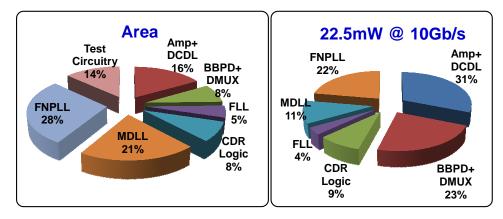

|       | Power and area breakdowns of the CDR prototype                                       | 66<br>67 |

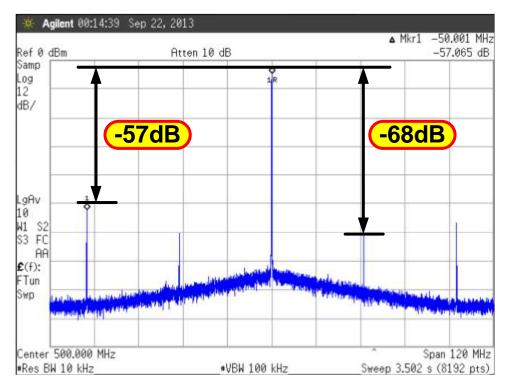

|       | Measured power spectrum of MDLL                                                      | 67<br>67 |

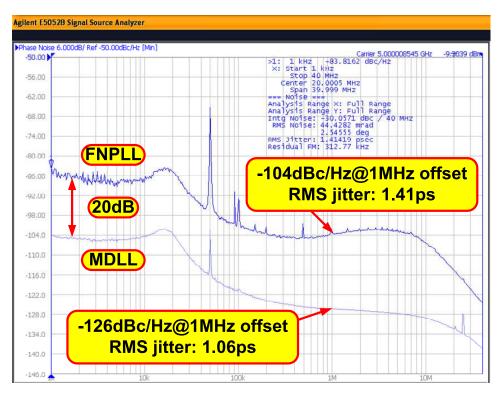

| 4.17  | Measured phase noise performance of FNPLL (DCO)                                      | 67       |

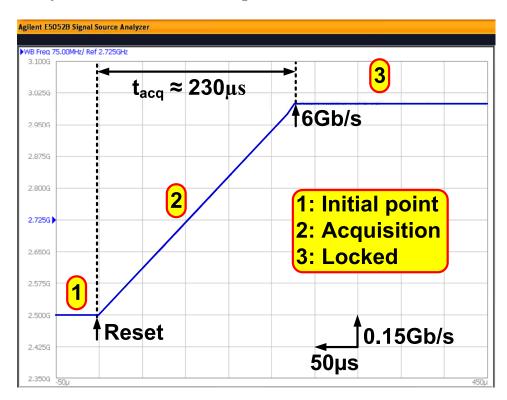

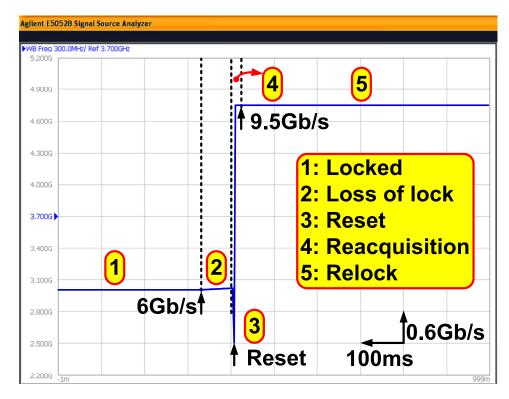

| 4.18 | Measured frequency acquisition process from initial fre-       | co |

|------|----------------------------------------------------------------|----|

| 4 10 | quency to 6 Gb/s data rate.                                    | 68 |

| 4.19 | Measured frequency acquisition process with data rate switch-  | co |

| 4.00 | ing from $6 \text{ Gb/s}$ to $9.5 \text{ Gb/s}$ .              | 69 |

| 4.20 | Measured residual frequency error versus locking threshold     | 70 |

| 4.21 | N <sub>TH</sub> at different transition densities              | 70 |

|      | $N_{TH}$ at different input jitter amplitudes with PRBS7 input |    |

|      | data                                                           | 71 |

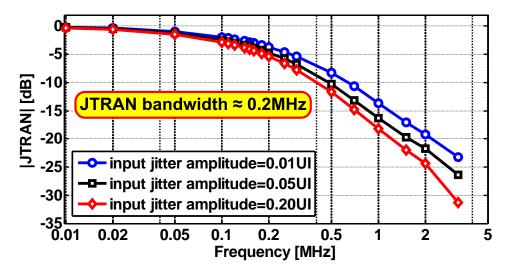

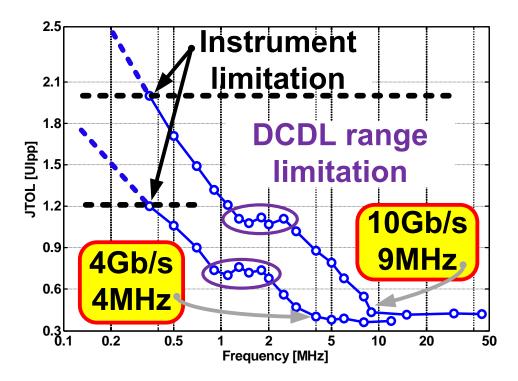

| 4.22 | Measured JTRAN with different input jitter amplitudes          | 72 |

|      | Measured jitter tolerance with PRBS7 input data at 10 Gb/s     |    |

|      | and 4 Gb/s.                                                    | 73 |

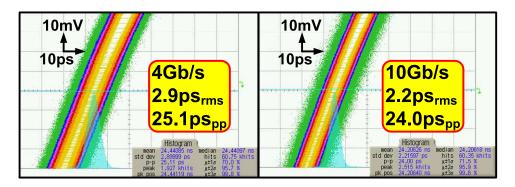

| 4.24 | Measured recovered clock jitter with PRBS31 input data:        |    |

|      | (a) at 5 Gb/s, and (b) at $10$ Gb/s                            | 73 |

|      |                                                                |    |

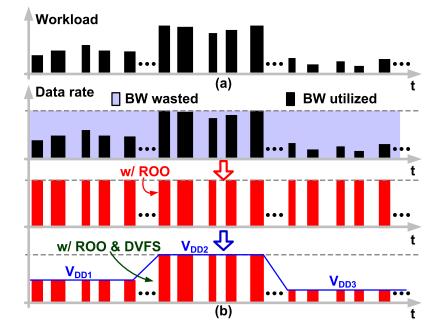

| 5.1  | Cut link power/bandwidth wastage with DVFS and ROO             |    |

|      | techniques                                                     | 78 |

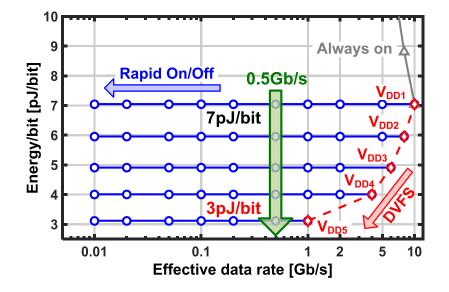

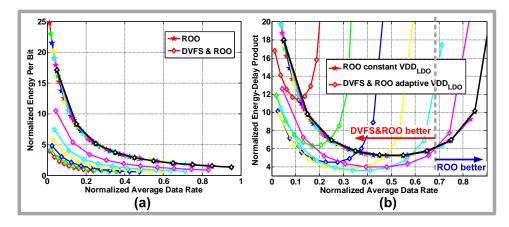

| 5.2  | Link energy efficiency with DVFS and ROO techniques            | 79 |

| 5.3  | Block diagram of source-synchronous link with DVFS and         |    |

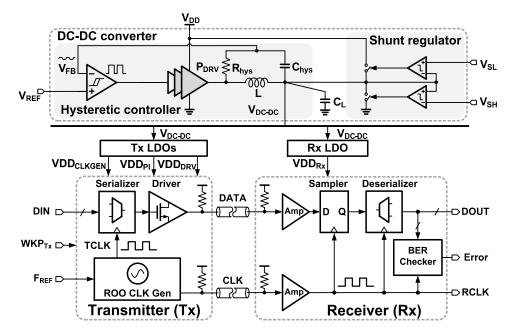

|      | rapid on/off capabilities                                      | 81 |

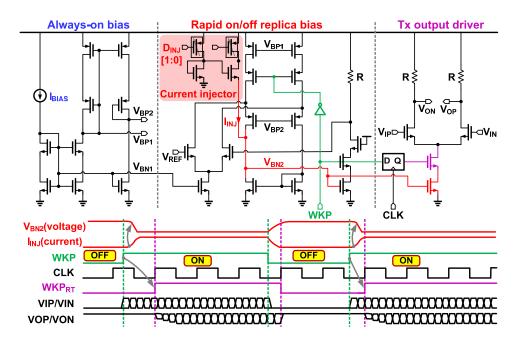

| 5.4  | Wake-up process of the energy-proportional transceiver         | 82 |

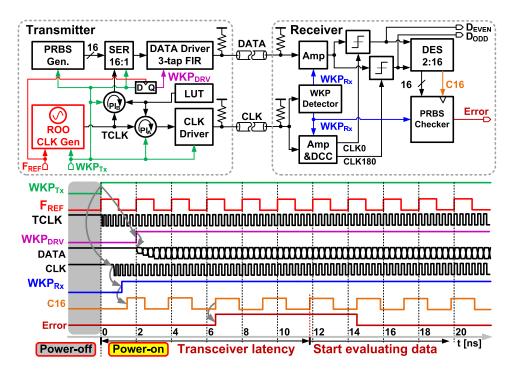

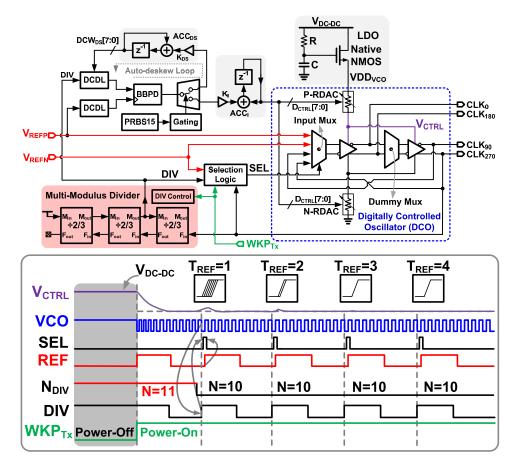

| 5.5  | (a) Current-mode hysteric converter. (b) Simulated line        |    |

|      | transient response.                                            | 83 |

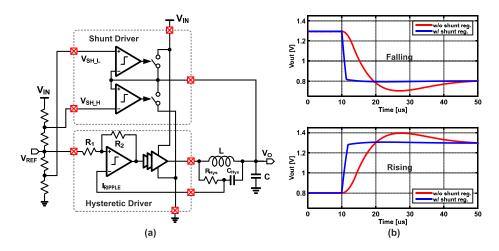

| 5.6  | Block diagram of rapid on/off multiplying delay-locked loop    |    |

|      | (MDLL) and timing diagram during wake-up process               | 84 |

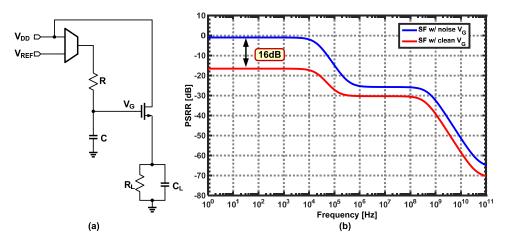

| 5.7  | (a) Source follower (SF) -based low dropout (LDO) voltage      |    |

|      | regulator. (b) Simulated PSRR of LDO                           | 85 |

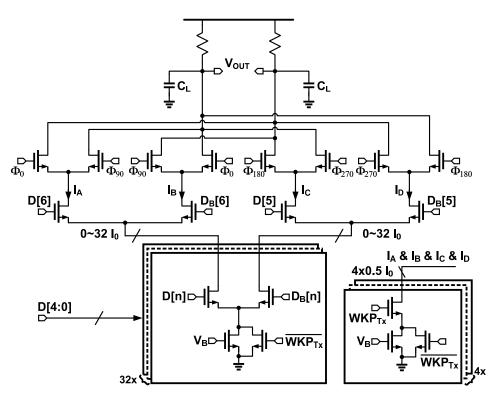

| 5.8  | Schematic of 7-bit phase interpolator                          | 86 |

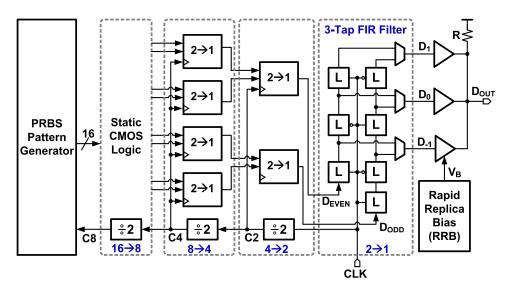

| 5.9  | Block diagram of energy-proportional transmitter with 3-       |    |

|      | tap FIR filter                                                 | 87 |

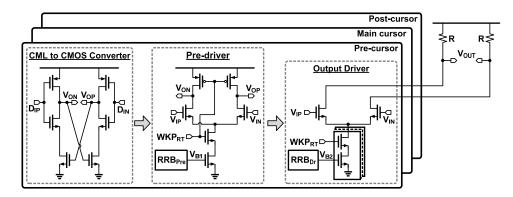

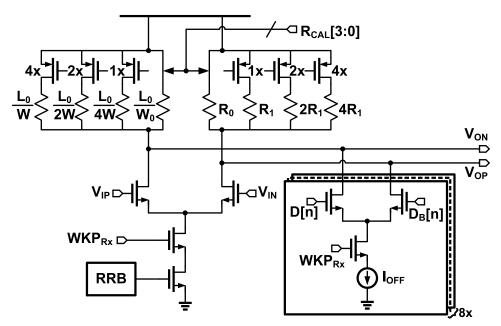

| 5.10 | Schematic of segmented CML output driver                       | 88 |

| 5.11 | Schematic and settling process of rapid replica biasing (RRB)  |    |

|      | circuit                                                        | 88 |

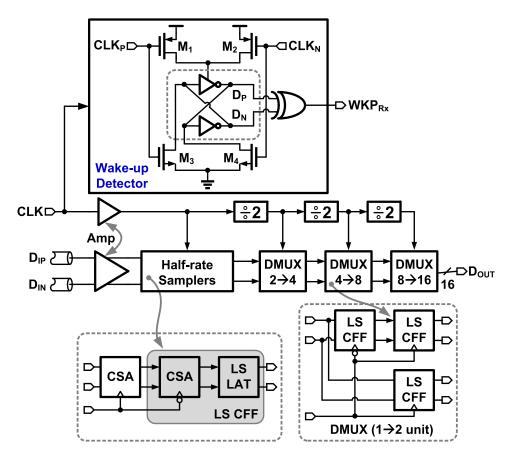

| 5.12 | Schematic of receiver data path                                | 89 |

|      | Schematic of Rx limiting amplifier with load resistor cali-    |    |

|      | bration and offset cancellation                                | 90 |

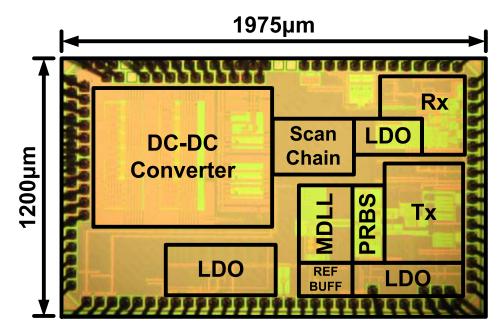

| 5.14 | Micrograph of the energy-proportional transceiver prototype.   | 91 |

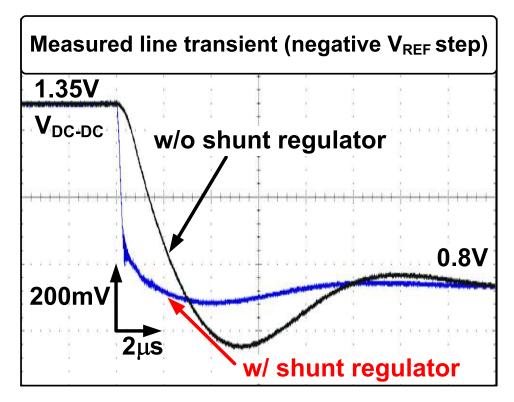

|      | Measured transient response of DC-DC converter: w/ and         |    |

|      | w/o shunt regulator.                                           | 92 |

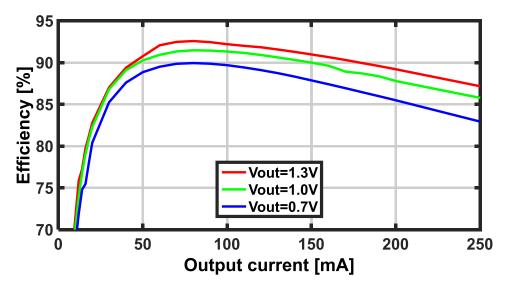

| 5.16 | Measured power efficiency of DC-DC converter.                  | 92 |

|      | Measured settling behavior of low dropout (LDO) voltage        |    |

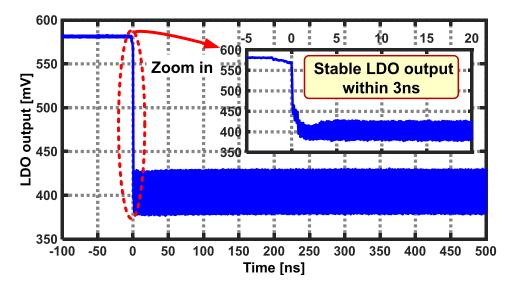

|      | regulator                                                      | 93 |

| 5.18 | Measured MDLL performance across different supply voltages.    | 93 |

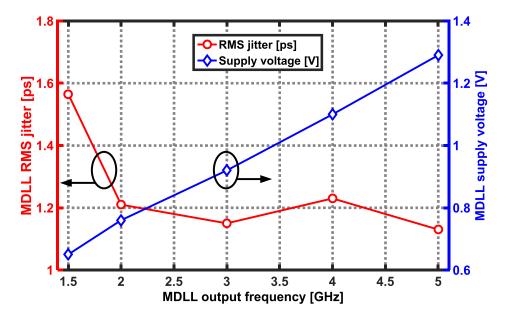

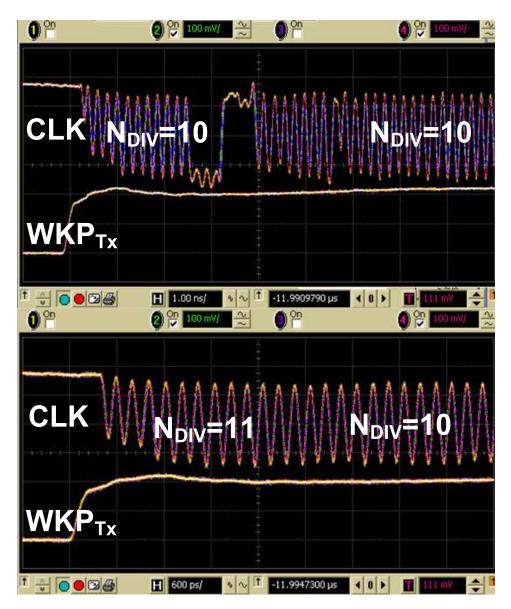

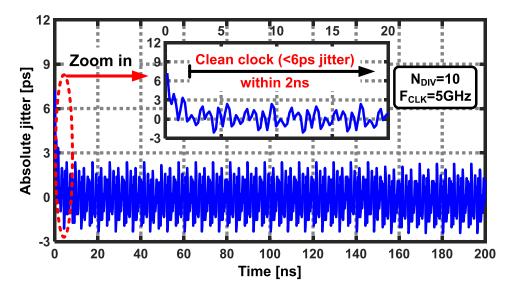

|      | Measured MDLL settling behavior with programmable divider.     | 94 |

| 5.20 | Measured MDLL jitter settling during wake-up process 95                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

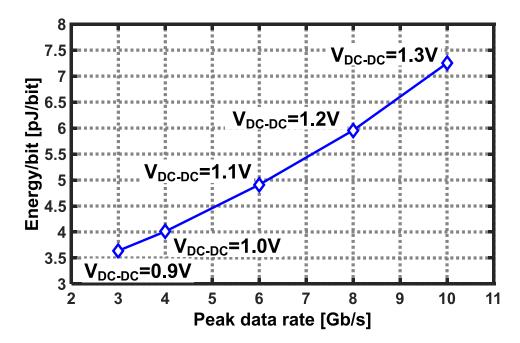

| 5.21 | Measured transceiver energy efficiency in DVFS mode 95                                                                                                |

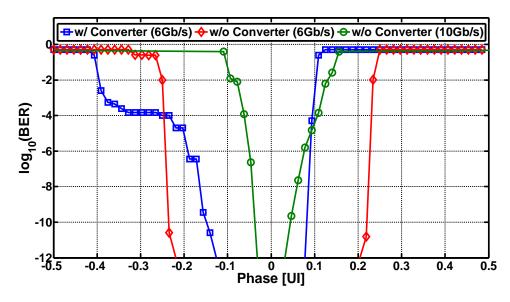

| 5.22 | Measured source-synchronous link bathtub cures 96                                                                                                     |

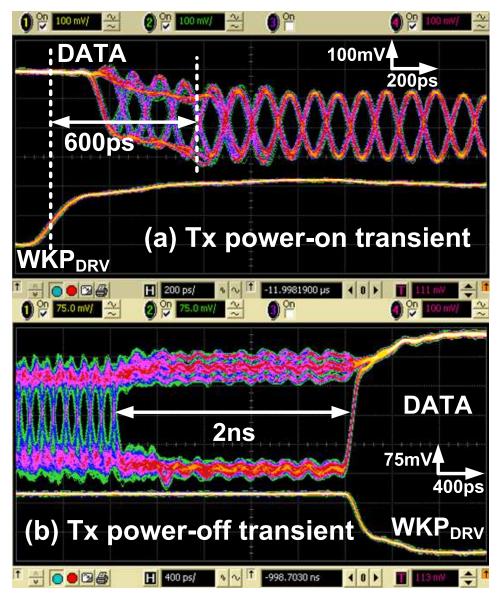

| 5.23 | Measured power on and off process of transmitter driver 97                                                                                            |

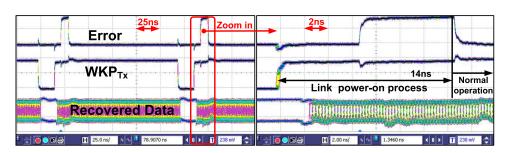

| 5.24 | Measured power on and off behavior of complete link with                                                                                              |

|      | less than 14 ns wake up time. $\dots \dots \dots$     |

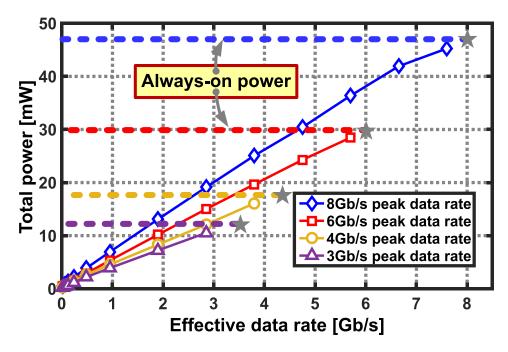

| 5.25 | Measured link power scaling capability with $500 \mathrm{x}$ range of                                                                                 |

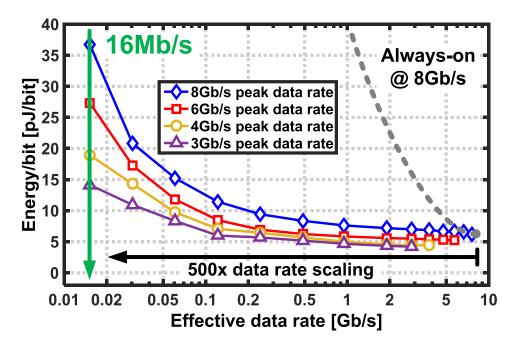

|      | data rate $(8 \text{ Gb/s to } 16 \text{ Mb/s})$                                                                                                      |

| 5.26 | Measured link energy-proportional operation capability with                                                                                           |

|      | 500x range of data rate (8 Gb/s to $16 \text{ Mb/s}$ ) 99                                                                                             |

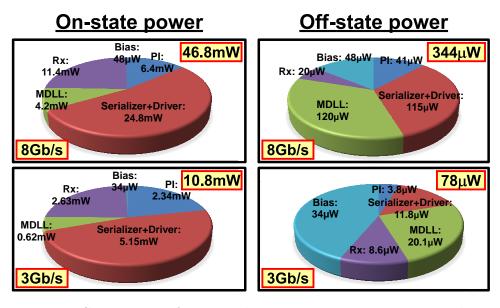

| 5.27 | Comparison of measured transceiver on-state power and                                                                                                 |

|      | off-state power at $8 \text{ Gb/s}$ and $3 \text{ Gb/s}$ 100                                                                                          |

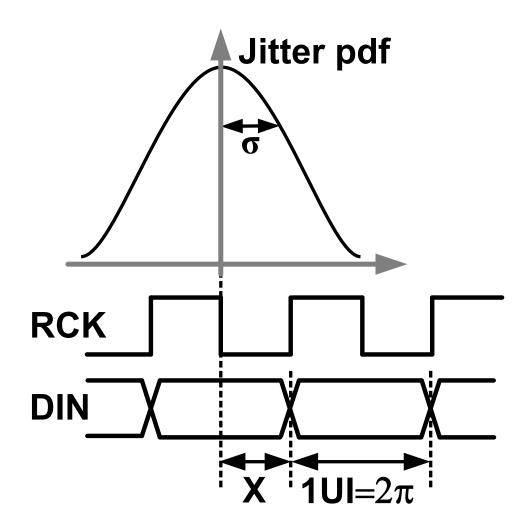

| A.1  | Sampling instance between RCK and DIN in the presence                                                                                                 |

| л.1  | of random jitter                                                                                                                                      |

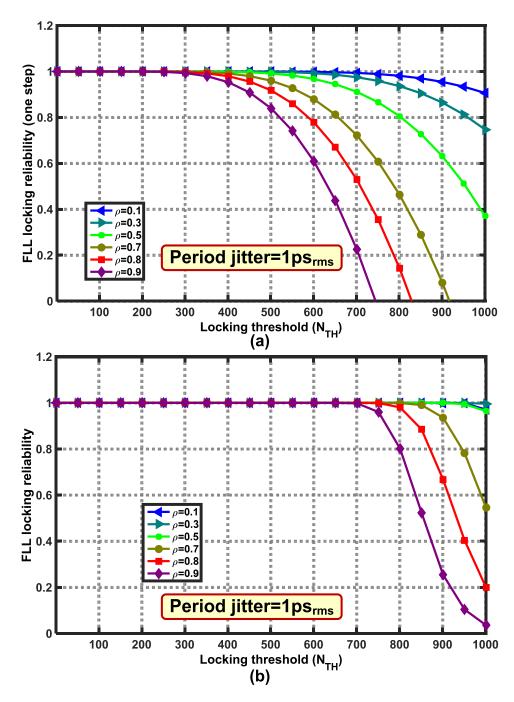

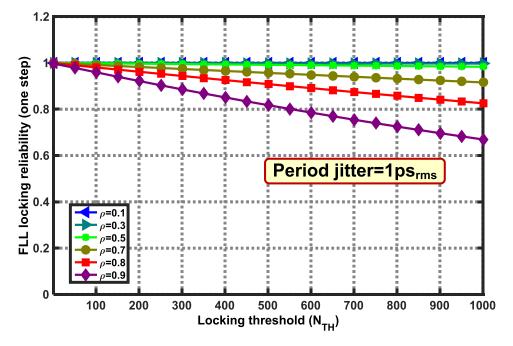

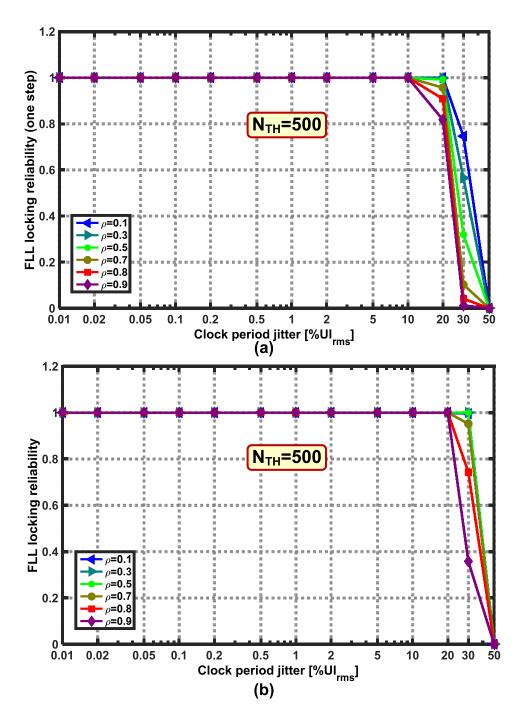

| A.2  | FLL locking reliability versus locking threshold $N_{TH}$ : (a)                                                                                       |

| 11.2 | one step reliability, (b) overall reliability                                                                                                         |

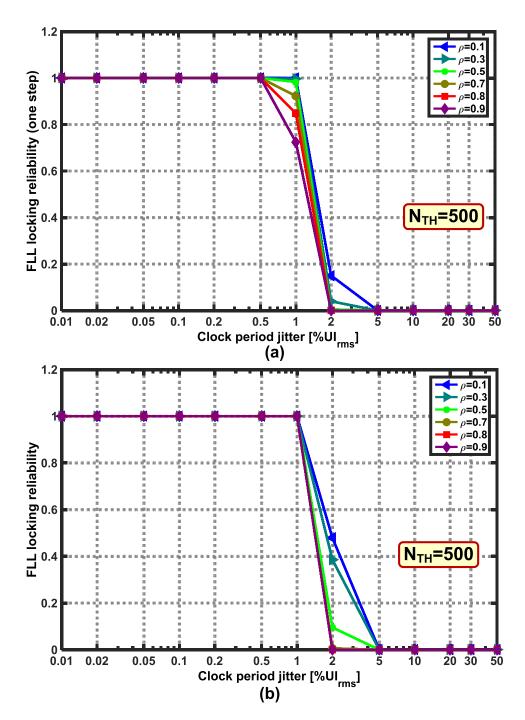

| A.3  | FLL locking reliability versus period jitter: (a) one step                                                                                            |

| 11.0 | reliability, (b) overall reliability                                                                                                                  |

| A.4  | FLL locking reliability versus locking threshold, $N_{TH}$ , with                                                                                     |

|      | fractional-N PLL-based DCO: (a) one step reliability, (b)                                                                                             |

|      | overall reliability.                                                                                                                                  |

| A.5  | FLL locking reliability versus period jitter with fractional-                                                                                         |

|      | N PLL-based DCO: (a) one step reliability, (b) overall reliability.111                                                                                |

| D 1  |                                                                                                                                                       |

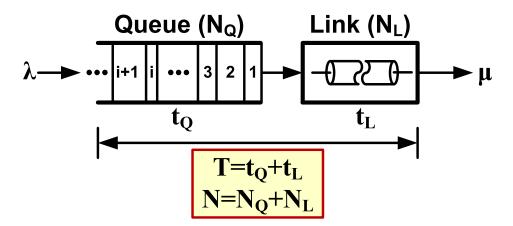

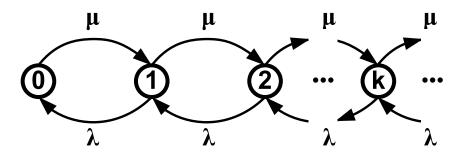

| B.1  | Queue model for serial links                                                                                                                          |

| B.2  | Queue model for serial links                                                                                                                          |

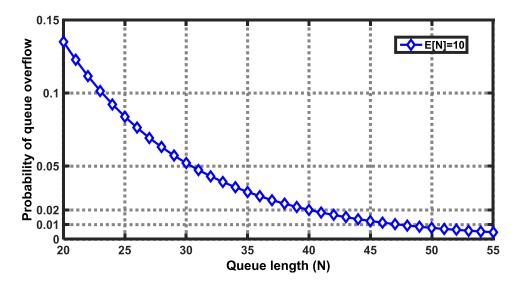

| B.3  | Queue length versus the probability of overflow (expected $115$                                                                                       |

| P /  | queue length is $E[N]=10$ )                                                                                                                           |

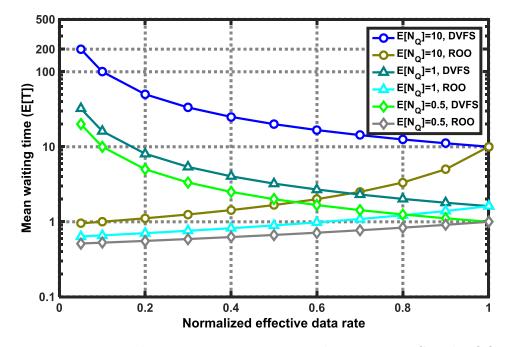

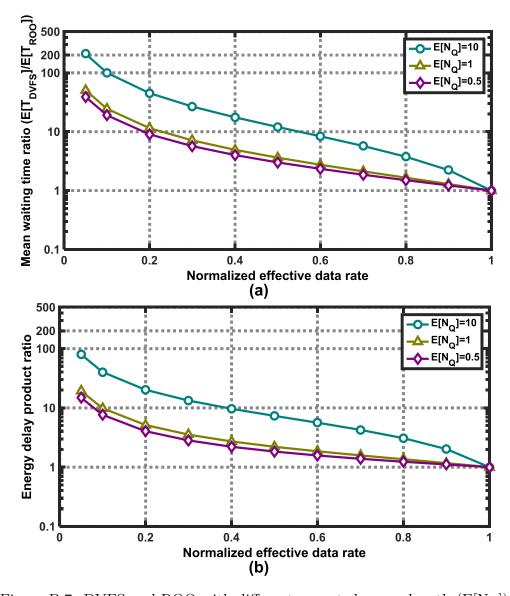

| B.4  | Expected waiting time comparison between DVFS and ROO with different expected queue length $(E[N_Q])$                                                 |

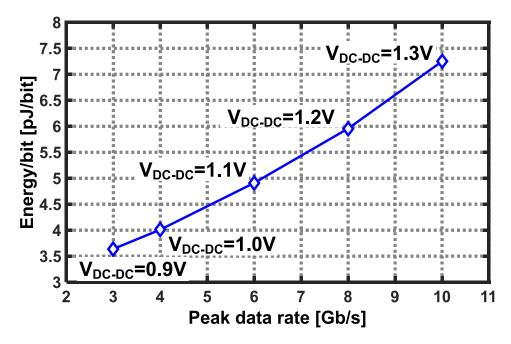

| B.5  | Measured transceiver energy efficiency at different peak                                                                                              |

| D.0  | data rates in DVFS mode (replot Fig. 5.21 for convenience). 117                                                                                       |

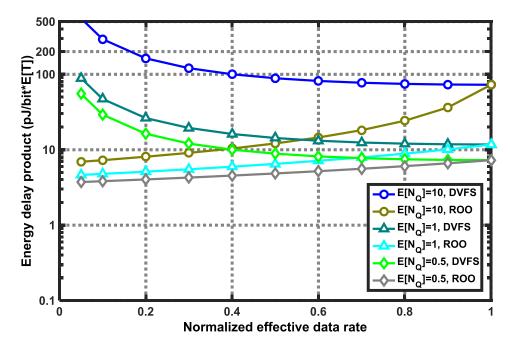

| B.6  | Energy delay product comparison between DVFS and ROO                                                                                                  |

| D.0  | with different expected queue length $(E[N_Q])$                                                                                                       |

| B.7  | DVFS and ROO with different expected queue length $(E[N_Q])$ :                                                                                        |

| D.1  | (a) ratio of expected waiting time, (b) ratio of energy delay                                                                                         |

|      | product                                                                                                                                               |

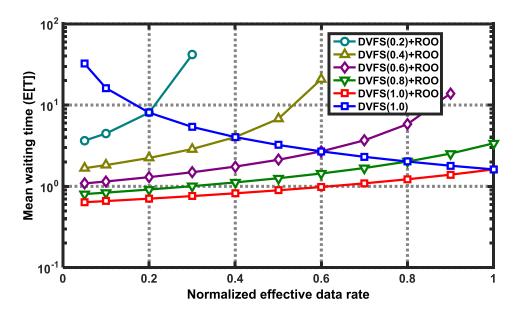

| B.8  | Expected waiting time with combined DVFS and ROO                                                                                                      |

|      | with expected queue length $E[N_Q] = 1. \dots $ |

| B.9  | Energy delay product with combined DVFS and ROO with                                                                                                  |

| -    | expected queue length $E[N_Q] = 1. \dots $      |

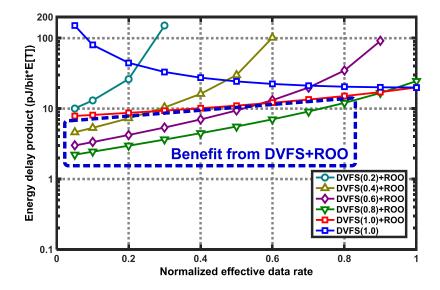

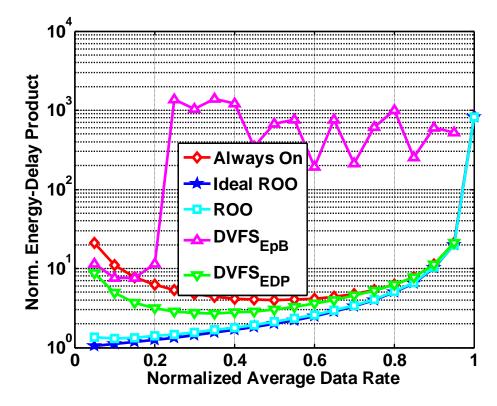

| B.10 | Simulated link energy delay product with M/M/1 queue model.122                                                                                        |

|      | · · –                                                                                                                                                 |

| B.11    | Simulated link performance with combined DVFS and ROO                                          |

|---------|------------------------------------------------------------------------------------------------|

|         | using $M/M/1$ queue model: (a) normalized energy per bit,                                      |

|         | (b) normalized energy delay product                                                            |

| $O_{1}$ | DVEC                                                                                           |

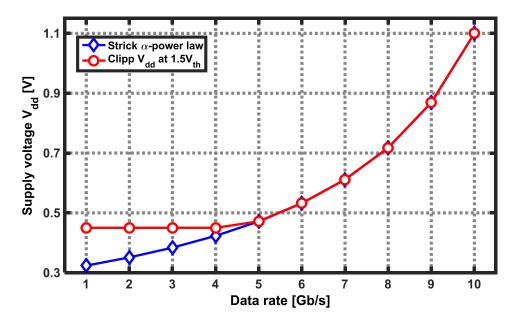

| C.1     | DVFS according to $\alpha$ -power law model for source-synchronous                             |

|         | transceiver in Chapter 5. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $125$ |

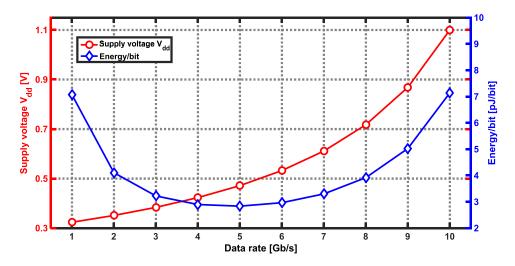

| C.2     | Data rate and energy/bit scaling according to $\alpha$ -power law                              |

|         | model for source-synchronous transceiver                                                       |

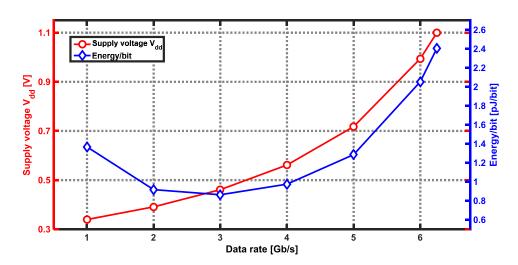

| C.3     | Data rate and energy/bit scaling according to $\alpha$ -power law                              |

|         | model for embedded clock transceiver                                                           |

# CHAPTER 1 INTRODUCTION

#### 1.1 Motivation

Thanks to the advancement of hardware and software technologies, gathering information from all walks of life has become pervasive. The amount of data generated has exploded exponentially, leading to the era of Big Data. The ability to store, access, and process data determines the usefulness of the acquired data. Memory subsystems, interconnection links, and processors perform data storage, communication, and computation, respectively. Traditionally, energy consumed for computation has been the predominant concern; however, with the explosion in data traffic, energy consumption issues have been extended to the entire system. In particular, the energy needed for data communication is becoming the bottleneck [1].

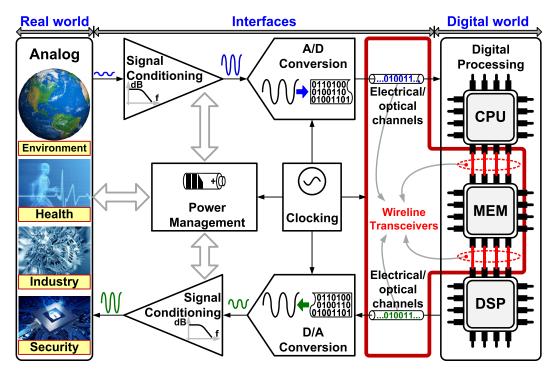

Wireline transceivers (also known as serial link transceivers) are the main building blocks to accomplish the data communication in digital format as illustrated in Fig. 1.1. They are commonly adopted to meet the data communication bandwidth requirement in various applications including CPU to CPU (or its peripheral devices) connection, network interfaces, backplane, and optical communication [2–5]. The achievable transceiver data rate (Gb/s), deciding the interconnect bandwidth, is limited by either transistor speed in a given technology and/or the channel bandwidth. Though techniques to deal with band-limited channels have been well established by using equalization, achieving high data rate and low bit error rate (BER) within a tight energy efficiency requirement ( $\leq 5 \,\mathrm{mW/Gb/s}$  or 5pJ/bit) continues to be a significant challenge. And this has been becoming the bottleneck in many complex and fast computation and communication systems.

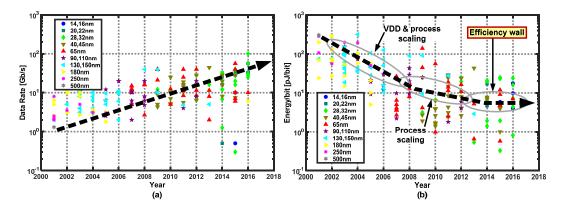

The trends of wireline transceiver data rate and energy efficiency in Fig. 1.2 simply reveals this challenge. Over the last 15 years, the requirement for data

Figure 1.1: Application scenario of wireline transceivers.

rate (wireline transceiver bandwidth) is constantly increasing to keep up with the demand in data communication bandwidth (Fig. 1.2(a)). The link energy efficiency in Fig. 1.2(b), however, is becoming more and more difficult to improve, especially in recent years, because the benefit from process scaling is diminishing due to the slowing pace of technology scaling (denoted as "efficiency wall" in analogy to the "power wall" in processor design). Therefore, both circuit and system level innovations are becoming more and more paramount to satisfy the demanding data communication bandwidth with good energy efficiency, in both high performance systems (such as data centers and supercomputer facilities) and low power systems (such as portable devices and sensor nodes in the Internet of Things (IoT)).

#### 1.2 Thesis Organization

This thesis aims to develop design techniques, at both circuit and system level, to improve the link energy efficiency. At circuit level, novel receiver architectures are explored to break several inherent trade-offs in conventional receivers, and extend receiver operation to a wide range of data rates with

Figure 1.2: Wireline transceiver trends in last 15 years: (a) date rate, (b) energy efficiency.

a stringent power budget. At system level, the thesis closely studies the feasibility of energy-proportional link, and aims to build wireline transceiver that can respond to the sparse data communication in many applications, thus achieving energy-proportionality over a wide range of utilization levels. In both directions, a highly digital design philosophy is applied to leverage the benefits from technology scaling. The thesis is organized as follows:

Chapter 2 reviews basic wireline transceiver operations, introduces various jitter metrics of the receiver, and highlights the limitations and trade-offs in conventional receivers.

Chapter 3 presents a highly digital receiver with phase-rotating phaselocked loop (PRPLL) to decouple the dependence between jitter transfer bandwidth and jitter tolerance corner frequency and eliminate the inherent peaking in jitter transfer function of the conventional receiver architecture. Similar to the delay-locked/phase-locked loop (D/PLL) receiver architecture, the bandwidth for oscillator phase noise suppression is reduced, causing inadequate jitter performance at recovery clock especially with ring oscillators. One solution to address this issue is detailed in the next chapter.

Chapter 4 proposes a reference-less frequency acquisition scheme using bang-bang phase detector (BBPD), and demonstrates a digital implementation of D/PLL receiver to eliminate the bulky loop filter capacitor and preserves the feature of decoupled jitter transfer and jitter tolerance in its analog counterpart. Furthermore, a fractional-N phase-locked loop (PLL) is introduced as a digitally controlled oscillator (DCO) to improve the recovery clock jitter performance, which resolves the remaining issue on clock jitter from Chapter 3.

Chapter 5 explores the energy-proportional operation concept in serial links, and demonstrates the first energy-proportional source-synchronous link transceiver that combines dynamic voltage-and-frequency scaling (DVFS) and rapid on/off (ROO) techniques with less than 14 ns exit latency.

Finally, the thesis is concluded in Chapter 6 with a summary of the contributions and directions for further research.

## CHAPTER 2

## WIRELINE TRANSCEIVER OVERVIEW

#### 2.1 Transceiver Operation

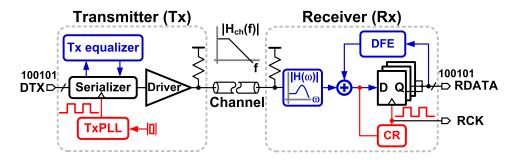

A basic wireline transceiver including a transmitter and a receiver is depicted in Fig. 2.1. The transmitter (Tx) consists four main blocks: transmitter phase-locked loop (TxPLL), serializer, equalizer, and output driver. The TxPLL generates a high-frequency on-chip clock using a low-frequency external crystal reference. The serializer multiplexes the data word input into a serial stream using TxPLL clock output and its divided versions. The equalizer adds pre-emphasis to the data stream to compensate for the channel dispersion and attenuation. The transmitter driver is responsible for driving the high speed serializer output onto the channel.

Figure 2.1: Block diagram of a wireline transceiver.

The receiver (Rx) consists of three important blocks: the clock recovery unit, the data samplers, and the equalizer. Usually, the clock recovery (CR) unit and the data samplers together are referred to as the clock and data recovery (CDR) circuit, which is the most critical component in a receiver (receiver and CDR are used interchangeably hereafter in this thesis and the exact meaning should be clear in the context). Based on system requirements, deserialization might be adopted at the receiver side to provide the output data stream at the required rate. Due to the serializer in Tx side and the deserializer in Rx side, serial link transceivers are also called SerDes systems. Similar to the Tx equalizer, the Rx equalizer also helps to mitigate the effect of channel imperfections. The basic operation of the transceivers can be understood in four main parts: signaling, clocking, recovering and equalizing methods. A brief description of each part is discussed here [6].

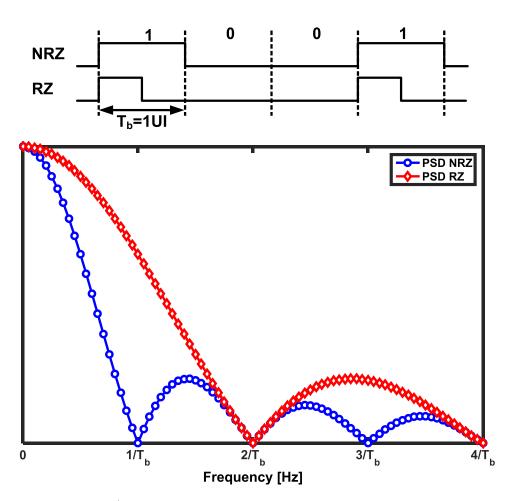

#### 2.1.1 Signaling

The most widely used signaling method is the non-return to zero (NRZ) format for the input data DIN. Fig. 2.2 illustrates transmitted waveforms for a known NRZ data pattern 1001. Also shown is the waveform for the less commonly used return-to-zero (RZ) format. Transmitting every bit requires  $T_b$  seconds or one unit interval (1 UI). NRZ data keeps constant during the interval, while RZ data has a 1 to 0 transition (usually at 0.5  $T_b$ ) if the transmitted bit is 1. The reason why the NRZ pattern is preferred can be better understood in frequency domain as shown in Fig. 2.2. Analyzing the power spectral density (PSD) for a long binary random sequence with equal transition density shows that the spectrum of NRZ data has the first spectral null at  $1/T_b$  whereas the first null of RZ data is at  $2/T_b$  [7,8], and spectra of the NRZ and RZ data are:

$$S_{\rm NRZ} = T_{\rm b} \left[ \frac{\sin(\pi f T_{\rm b})}{\pi f T_{\rm b}} \right]^2, \ S_{\rm RZ} = \frac{T_{\rm b}}{2} \left[ \frac{\sin(0.5\pi f T_{\rm b})}{0.5\pi f T_{\rm b}} \right]^2$$

(2.1)

A larger spread in the PSD for RZ data requires larger channel bandwidth, thereby making NRZ the preferred format for binary data transmission. At higher data rates ( $\geq 25 \text{ Gb/s}$ ), a multi-level signaling scheme, such as PAM4, is sometimes adopted to further confine the signal spectrum in order to reduce the burden of heavy equalization due to the channel impairment at high-frequency [9, 10].

#### 2.1.2 Clocking

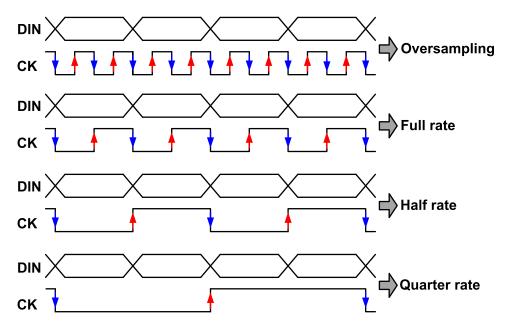

Link clocking scheme describes the relationship between input data (DIN) and sampling clock (CK). As shown in Fig. 2.3, based on the relative switching rates between data (DIN) and clock (CK), majority of the links operate

Figure 2.2: NRZ/RZ data waveforms and power spectral density for random NRZ/RZ patterns.

in either full rate ( $F_{CK} = F_{DIN}$ ), half rate ( $F_{CK} = F_{DIN}/2$ ), or quarter rate ( $F_{CK} = F_{DIN}/4$ ) clocking scheme. Choosing a sub-rate clocking scheme (half rate, quarter rate, or lower) reduces the maximum clock frequency for on-chip distribution, for which the power is usually above 20% of the overall power, and the percentage increases as the data rate goes higher [4]. The trade-off is that multiple phases are needed to operate in sub-rate, and achieving good phase spacing among phases is challenging. This is one main reason that further than quarter rate clocking scheme is not commonly used. Of course, there are receivers that have clock rate higher than the data rate, which is usually referred to as oversampling clocking schemes [11], but these are rarely adopted at high data rates ( $\geq 25 \text{ Gb/s}$ ) due to the difficulty in high-frequency clock generation and excessive power for clock distribution.

Figure 2.3: Clocking schemes based on the relative switching rates between data (DIN) and clock (CK).

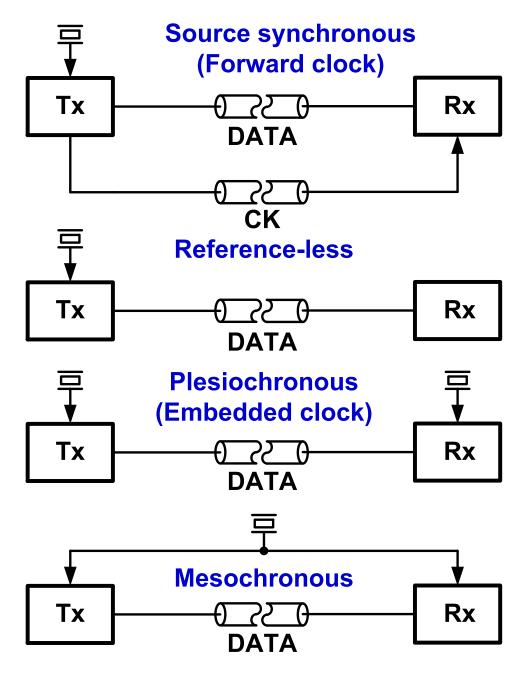

Serial link transceivers can also be classified based on the generation of clock in the receiver (Rx) side, as shown in Fig. 2.4. If the link has a dedicated channel to forward the clock from Tx to Rx side, it is referred to as a source-synchronous (forwarded clock) link. If Tx only transmits data to Rx and there is no crystal reference for Rx, it is known as reference-less clocking. In such links, the receiver derives sampling clock from random input with special frequency detectors [12, 13]. Reference-less transceivers are employed when a crystal reference cannot be afforded on the Rx side, or it is not practical

to use a dedicated clock channel. Repeater is one such application that will be covered more in Chapter 3 and 4.

If Rx does have a crystal reference, the link can be further classified into two types. On one hand, if the Rx uses a different crystal from Tx, it is called plesiochronous (embedded clock) link. On the other hand, if Rx shares the same crystal with Tx, the link is classified as mesochronous link. The main difference between plesiochronous and mesochronous links is that plesiochronous receivers must cover the frequency offset between two crystals (typically measured in parts-per-million (ppm)) [14].

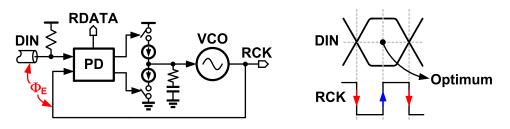

#### 2.1.3 Clock and Data Recovery

Clock and data recovery (CDR) is the most essential component of any receiver. The diagram of a CDR based on voltage-controlled oscillator (VCO) is shown in Fig. 2.5 [15]. This CDR loop is very similar to a type-II phaselocked loop except that the phase detector (PD) is operating on random data DIN. Intuitively, the main task of the CDR loop is to drive the rising edges of VCO output, recovered clock (RCK), to the center of data eye, which is the optimum sampling point for the samplers inside PD to retime DIN and generate recovered data RDATA. Taking a full rate system for example, in order to achieve optimum sampling, the negative feedback loop locks the falling edge of RCK to the transition of input data DIN. Since the rising edge is ideally 180 degrees away from the falling edge, it automatically samples DIN at the optimum position to get RDATA. Therefore, both clock (RCK) and data (RDATA) are recovered.

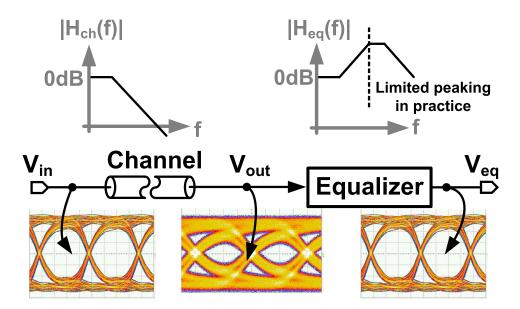

#### 2.1.4 Equalization

A bandwidth-limited channel causes inter-symbol interference (ISI) [6], which not only attenuates data amplitude but also introduces dispersion in phase and amplifies jitter, especially at higher data rates. As shown in Fig. 2.6, equalization is widely used to compensate for channel loss and minimize the amplification of jitter due to ISI. Equalization can be done either in the continuous-time domain or discrete-time domain (processing sampled data). The goal in both domains is to approximate the reciprocal of channel fre-

Figure 2.4: Link classification based on clocking schemes.

Figure 2.5: Recover clock and data with VCO-based CDR.

quency response,  $1/H_{ch}(s)$ , using  $H_{eq}(s)$ , which is the frequency equivalent response of equalizer. Ideally equalization can be performed either at the transmitter and/or receiver side, but the amount of equalization at the transmitter side is usually limited by the achievable peak swing at the driver. A discussion of various equalizer architectures and their trade-offs is presented in [6].

Figure 2.6: Equalizer compensates for channel loss.

## 2.2 CDR Performance Metrics

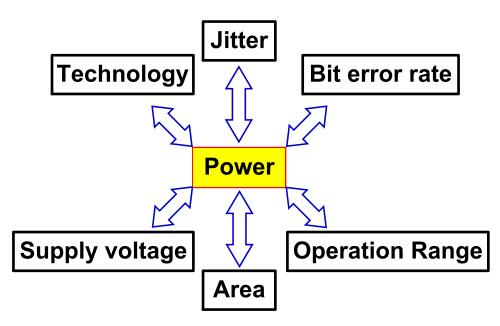

Generally, many factors need to be taken into account in CDR designs, such as power consumption, bit error rate (BER), jitter, operation range, and technology as shown in Fig. 2.7. BER is one high-level metric commonly used for characterizing the CDR performance, in which a lower BER is better. In addition, CDRs are also characterized in terms of what level of impairment (mostly at input data and recovery clock) can be tolerated while still achieving the required BER level. This includes three metrics related to jitter in the system: jitter generation (JGEN), jitter transfer (JTRAN), and jitter tolerance (JTOL) [16]. The definition details about the three performance metrics are addressed below.

Figure 2.7: Receiver performance consideration.

#### 2.2.1 Jitter Generation

The jitter generation (JGEN) evaluates the intrinsic jitter of the CDRs. It is measured as the output jitter in the CDR recovered clock, RCK, with no jitter presented at input data. Yet, ISI and other common impairments except jitter should be included at the input data. Taking the CDR in Fig. 2.5 for example, the main contributors of JGEN include: (1) VCO phase noise; (2) ripple on the control voltage (related to loop dynamics); (3) quantization error in digital implementations (Fig. 2.11); (4) ISI or similar common impairment from input data and inside CDRs; (5) supply and substrate noise. JGEN is usually presented as a root-mean-square (RMS) jitter value. Some filter may be applied at the input while measuring the JGEN performance depending on standard specification [17].

#### 2.2.2 Jitter Transfer

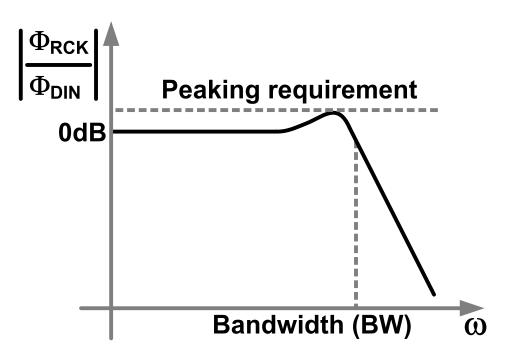

The jitter transfer (JTRAN) identifies the jitter magnitude at the output of a CDR with a given amount of input jitter at different frequencies. It is essentially the transfer function from CDR input to the output. To measure JTRAN performance, an input data sequence (usually a pseduorandom sequence), with its phase modulated by sinusoidal signal at a given frequency, is applied to the CDR. The jitter at the recovered clock output is measured, and the ratio between the output jitter and input jitter over different frequency gives jitter transfer. Generally, the JTRAN exhibits a low-pass characteristic with 0 dB gain at low frequency, and a typical JTRAN is shown in Fig. 2.8. Note that a jitter peaking exists due to a zero in second or higher order systems. The transfer function starts to roll off after the JTRAN bandwidth at a rate depending on the order of the CDRs (20 dB/decade for second order systems since the zero cancels out the roll off of one pole).

Figure 2.8: Typical jitter transfer response.

It is important to mention that the jitter transfer requirement differs from application to application. For example, high speed links for chip-chip communication do not require specific jitter transfer performance, and are instead focused on achieving sufficiently low BER, whereas in synchronous optical network (SONET) systems, jitter transfer, especially the peaking value ( $\leq 0.1 \text{ dB}$ ), is critical because the system has to ensure that jitter does not build up while traveling through multiple repeaters [18].

#### 2.2.3 Jitter Tolerance

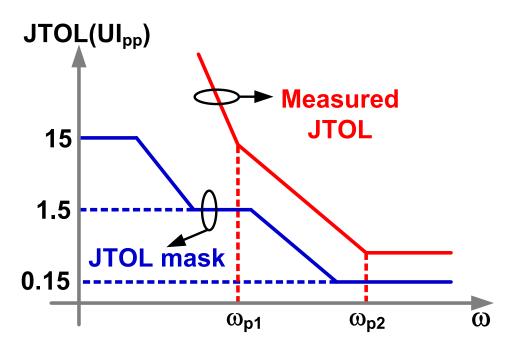

The jitter tolerance (JTOL) quantifies how much input jitter can be tolerated by a CDR loop with certain threshold of BER level. The requirement on JTOL is usually specified as minimum jitter amplitude, as a function of frequency, that must be tolerated while not exceeding a specific BER, shown as JTOL mask in Fig. 2.9. In the JTOL measurement, a pseudo-random

Figure 2.9: Typical jitter tolerance response.

input data sequence is applied to the CDR, and the phase of the sequence is modulated by a sinusoidal signal at a given frequency. The amplitude of the modulation keeps increasing until the measured BER exceeds the required BER level. Usually, the measured jitter tolerance performance at different frequencies is compared with the JTOL mask (Fig. 2.9) to see whether it satisfies the requirement.

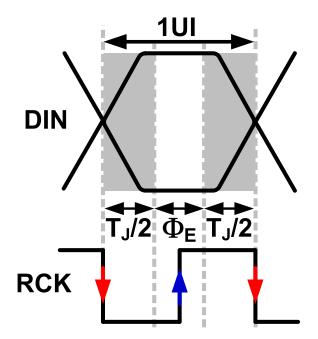

The process for generating JTOL mask is as follows. As shown in Fig. 2.10, the typical jitter contribution is shown within a data eye diagram, where 1 UI is the overall timing margin for samplers,  $T_J$  stands for CDR intrinsic jitter under certain BER level, and  $\Phi_E$  is the phase error caused by applied sinusoidal jitter,  $\Phi_{in}$ , for JTOL measurement. Assuming the open loop gain

Figure 2.10: Jitter contribution in data eye diagram.

of CDR is LG(s), the phase error is given as:

$$\Phi_{\rm E} = \frac{\Phi_{\rm in}}{1 + \rm LG(s)} \tag{2.2}$$

In order for the CDR to meet the BER requirement, the phase error,  $\alpha$  UI, introduced by input sinusoid jitter should not exceed the available sampling margin, which means:

$$\Phi_{\rm E} = \alpha < 1 - T_{\rm J} \tag{2.3}$$

With substitution of Eq. (2.2) into Eq. (2.3), the JTOL mask (bottom curve in Fig. 2.9) is given by:

$$\Phi_{\rm in} = \alpha (1 + \rm LG(s)) \tag{2.4}$$

and the measured JTOL performance (top curve in Fig. 2.10) is given by:

$$\Phi_{\rm in} < (1 - T_{\rm J})(1 + LG(s)) \tag{2.5}$$

### 2.3 Conventional CDR Limitations

Although conventional analog CDRs (top side of Fig. 2.11) can meet the performance requirements in most applications, the continued scaling technology in deep-submicron CMOS process imposes severe constraints such as current leakage, poor analog transistor gain, low supply voltage, and process variability. Overcoming such technology limitations in CDR designs often incurs penalties in terms of performance, area, power, time-to-market, and design flexibility. For instance, the area of the analog CDR is historically large due to the big capacitor in the loop filter. Transistor leakage in deep-submicron technology mandates the use of metal capacitors in place of high-density MOS capacitors, causing more than 3 times increase in the loop filter area. Moreover, in applications which require small peaking in jitter transfer, the loop filter capacitor is too large to be implemented on chip, and full integration of the CDRs becomes impossible [13].

Figure 2.11: Transition from analog CDR to digital CDR.

To overcome these drawbacks, digital CDRs (bottom side of Fig. 2.11) are emerging as attractive alternatives in high-speed wireline transceivers due to their robustness in process-voltage-temperature (PVT) variations, design flexibility, and good area and power efficiency. The key distinction is in the implementation of the loop filter: analog loop filter LF(s) versus digital loop filter LF(z). Both of them perform proportional control and integral control to stabilize the second-order loop. Yet, the digital loop filter realizes the function of a capacitor, which is essentially integration, with a digital accumulator to reduce the area and improve PVT robustness. Due to the reconfigurable nature of digital circuits, the digital loop filter also has more flexibility to control the CDR loop dynamics. The digital implementation is also power efficient for two reasons. First, a digital circuit can potentially operate at low supply voltage without degrading the performance, especially in deep-submicron technology. Second, in digital domain, signals can be decimated to lower speed for further processing to reduce the power consumption [13]. Of course, as with most digital circuits, quantization error will be introduced and the techniques to mitigate this error will be addressed in detail later.

Apart from the limitations in analog-type CDRs in deep submicron process, both analog and digital CDRs have two main inherent trade-offs with the conventional architecture. One is tightly coupled jitter transfer (JTRAN) bandwidth and jitter tolerance (JTOL) corner frequency, and the other is conflict between CDR jitter generation (JGEN) and JTRAN bandwidth. This section explains both trade-offs in detail with a linear analysis for digital CDR based on small signal model in Fig. 2.12, and serves as one motivation for the new CDR architectures.

Figure 2.12: Loop dynamics of VCO-based digital CDR.

In the first trade-off, the jitter transfer (JTRAN) bandwidth and jitter tolerance (JTOL) corner frequency are decided by the cut-off frequency of transfer functions  $H_{JTRAN}(s)$  and  $H_{JTRACK}(s)$ , respectively.

$$H_{\rm JTRAN}(s) = \frac{\Phi_{\rm RCK}}{\Phi_{\rm DIN}}(s) = \frac{\rm LG(s)}{1 + \rm LG(s)} = \frac{s\rho K_{\rm PD} K_{\rm P} K_{\rm DCO} + \rho K_{\rm PD} K_{\rm I} f_{\rm ACC} K_{\rm DCO}}{s^2 + s\rho K_{\rm PD} K_{\rm P} K_{\rm DCO} + \rho K_{\rm PD} K_{\rm I} f_{\rm ACC} K_{\rm DCO}}$$

(2.6)

$$H_{\rm JTRACK}(s) = \frac{\Phi_{\rm E}}{\Phi_{\rm DIN}}(s) = \frac{1}{1 + {\rm LG}(s)} = \frac{s^2}{s^2 + s\rho K_{\rm PD} K_{\rm P} K_{\rm DCO} + \rho K_{\rm PD} K_{\rm I} f_{\rm ACC} K_{\rm DCO}}$$

(2.7)

where  $\rho$  is the transition density of input data. For a heavily damped systems, both  $H_{\rm JTRAN}(s)$  and  $H_{\rm JTRACK}(s)$  have the same two real poles located at  $\omega_{\rm pL} \approx -K_{\rm I} f_{\rm ACC}/K_{\rm P}$  and  $\omega_{\rm pH} \approx -K_{\rm PD} K_{\rm P} K_{\rm DCO}$ , respectively, as shown in Fig. 2.13. In addition,  $H_{\rm JTRAN}(s)$  has a zero at  $\omega_{\rm z} = -K_{\rm I} f_{\rm ACC}/K_{\rm P}$ , which is the reason for the inevitable peaking of jitter transfer function in conventional architecture.

Figure 2.13: Relationship between JTRAN bandwidth and JTOL corner frequency.

From Fig. 2.13, it is important to note that both JTRAN bandwidth and JTOL corner frequency are decided by the higher pole  $\omega_{pH}$  (JTOL is shown as its scaled inversion,  $H_{JTRACK}(s)$ , for clear comparison). In other words, whenever one lowers JTRAN to reduce the input jitter transfer to output, the JTOL corner frequency is also compromised. Chapter 3 proposes a novel CDR architecture to decouple this trade-off with a low JTRAN bandwidth and a high JTOL corner frequency and eliminate the peaking at jitter transfer transfer at the same time.

For the trade-off between jitter generation (JGEN) and jitter transfer (JTRAN) bandwidth, the essential conflict is the bandwidth for filtering the input noise and VCO noise (the major contributor to JGEN). Specifically, the transfer function from input noise to output has low-pass characteristics and that of VCO noise is high pass. Both transfer functions have the same shape as  $H_{JTRAN}(s)$  and  $H_{JTRACK}(s)$  shown in Fig. 2.13. Similarly, the band-

widths of both transfer functions are decided by  $\omega_{\rm pH}$ , and there exists the trade-off.

The solution presented in Chapter 3 achieves low JTRAN bandwidth and high JTOL corner frequency to break the first trade-off, and eliminates the peaking at jitter transfer function. Yet this reduces the bandwidth for VCO noise suppression, decided by JTRAN bandwidth, which degrades the JGEN of the CDR. Novel architectures to decouple both trade-offs at the same time are under investigation in the future work.

#### 2.4 Summary

Basic operations of wireline transceivers are described, including signaling, clocking, clock and data recovery, and equalization. The CDR performance metrics are then discussed in detail with their definitions, characterization setup, and variation for different applications. A brief comparison between analog and digital CDRs is given to explain the limitation in analog CDRs and how the digital counterparts overcome the limits. Last, inherent trade-offs in conventional CDRs are discussed. The inherent trade-off in conventional CDRs and trends of transceiver energy efficiency motivate: (i) novel CDR architectures to break the trade-offs in conventional structure in Chapter 3 and 4; (ii) the concept of energy-proportional link transceiver to cut link power wastage at system level, thus improving the energy efficiency in Chapter 5.

## CHAPTER 3

## A REFERENCE-LESS CDR USING PHASE-ROTATING PLL

The receiver is a key building block in wireline communication where it performs the crucial function of recovering clock and re-timing the received data. It must recover data without errors and tolerate input jitter as quantified by the jitter tolerance (JTOL) metric in a power- and cost-efficient manner. To avoid the cost of a crystal oscillator needed for the CDR, frequency acquisition without using a reference clock is desirable. Additionally, CDRs used in repeater applications should have minimum peaking ( $\leq 0.1 \text{ dB}$ ) in the jitter transfer (JTRAN) function, and must satisfy stringent jitter generation (JGEN) requirement [15].

In this chapter, we demonstrate a CDR that employs a phase-rotating PLL (PRPLL) as a phase interpolator and achieves reference-less frequency acquisition [19]. Main features of the proposed CDR are discussed through comprehensive linear and stability analysis, along with detailed discussion on circuit implementation of the PRPLL and CDR building blocks. Fabricated in a 90 nm CMOS process, the prototype CDR consumes 13.1 mW power at 5 Gb/s and achieves a BER better than  $10^{-12}$ , 2 MHz JTRAN bandwidth with no peaking, 16 MHz JTOL corner frequency, and a recovered clock long-term jitter of 5.0 ps<sub>rms</sub>/44.0 ps<sub>pp</sub> with PRBS31 input data. The CDR can operate with negligible degradation in BER with 110 mV<sub>pp</sub> amplitude supply noise at the worst case frequency (7 MHz).

The rest of this chapter is organized as follows. Prior art on dual-loop CDRs is briefly discussed in Section 3.2, serving as another motivation for the proposed CDR presented in Section 3.3. The circuit implementation details of the proposed CDR are described in Section 3.4. The measured results are presented in Section 3.5, followed by a summary of the key contributions in Section 3.6.

#### 3.1 Background

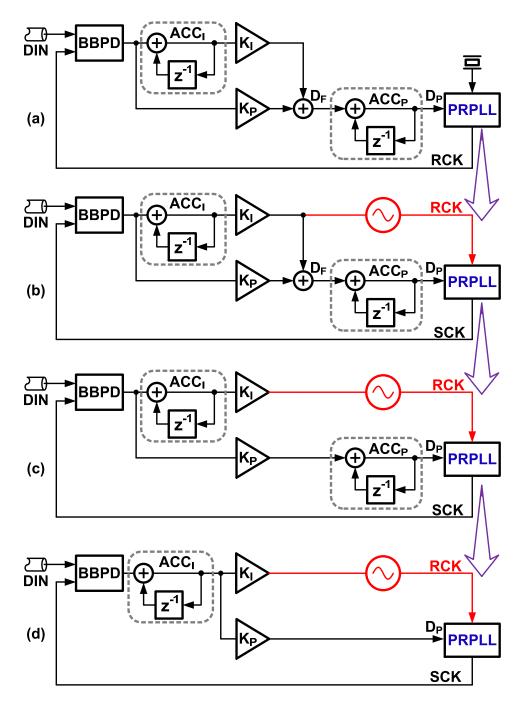

The phase interpolator-based (PI-based) CDR shown in Fig. 3.1 is one of the most commonly used CDR architectures [20–23]. Note that the phase accumulator (ACC<sub>P</sub>) and PI together is similar to the VCO or DCO function in Fig. 2.11 to provide infinite phase shift with a modulo of  $2\pi$ . The

Figure 3.1: Phase interpolator-based sub-rate CDR.

whole CDR is composed of a cascade of multiphase generator (MPG), typically implemented using a PLL or a delay-locked loop (DLL), and a main CDR, which is also known as clock and data recovery (CDR) loop, and CDR and CDR are used interchangeably in this proposal. Using a local reference clock, the MPG generates multiple equally-spaced phases at approximately the data rate and feeds them to the CDR loop. A bang-bang phase detector (BBPD) in the main CDR loop detects the sign of the phase error, and a digital proportional-integral loop filter processes BBPD output and generates the frequency control word,  $D_F$ . A digital accumulator, ACC<sub>P</sub>, integrates  $D_F$ and generates the phase control word,  $D_{\rm P}$ , which controls the phase interpolator (PI). The PI interpolates between MPG phases as governed by  $D_{\rm P}$ and generates recovered clock, RCK. By varying  $D_{\rm P}$ , the CDR loop drives the recovered clock phase to the center of the input data eye. By designing the phase accumulator  $(ACC_P)$  to roll-over (as opposed to saturating it), infinite phase shifting can be achieved to track the small frequency difference between the MPG output frequency and the incoming data rate [20].

There are many tradeoffs that one must consider while designing a PI-based CDR. First, because JTOL corner frequency is dictated by phase-tracking slew rate, it can be increased only by increasing PI step size (assuming the loop is operated at the maximum possible update rate). But this also increases phase quantization error and degrades JGEN [14,24]. Second, since JTRAN and JTOL are both governed by the same loop parameters, it is impossible to lower JTRAN to filter input jitter without reducing JTOL corner frequency [25]. Third, the non-linear transfer characteristic of BBPD causes loop gain to depend on input jitter, which makes it difficult to control JTRAN in a robust manner [15,26]. Finally, the design of phase interpolators is challenging due to the conflicting tradeoffs between linearity, noise sensitivity, operating range, area, and power [20,27]. Their power and area penalty is further exacerbated in sub-rate CDRs which require many PIs to generate multiple phases; for example, a half-rate CDR needs 4 phases and a quarter-rate CDR needs 8 phases [21,22].

Several techniques have been proposed to improve PI resolution and reduce its impact on JGEN [14,24,28]. PI quantization error was suppressed in [24] by filtering it using a PLL and the suppression was further improved in [14] by using a delta-sigma modulator to shape the quantization error out of band. Both these architectures are particularly amenable for sub-rate CDRs as they can generate multiple phases using a single PI. However, their effectiveness is limited by PI non-linearity and by the coupled PLL bandwidth tradeoff to simultaneously suppress VCO phase noise and PI quantization error ( $Q_n$ ). A low bandwidth is desirable to filter  $Q_n$  while a large bandwidth is needed to mitigate VCO phase noise [14, 27].

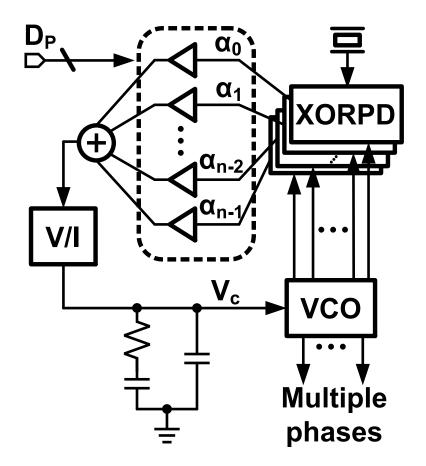

The phase-rotating PLL (PRPLL) proposed in [28] (shown in Fig. 3.2) presents an interesting phase shifting technique without using an explicit phase interpolator, and it overcomes the inherent non-linearity that comes with implementing interpolation in phase domain [27]. Different from a conventional charge-pump PLL, it consists of multiple XOR phase detectors whose output currents are weighted, summed, and filtered to generate the control voltage. By weighting the individual XOR outputs differently using control word D<sub>P</sub>, the amount of output phase shift can be varied. Compared to a conventional PI, thanks to the current-domain operation, the PRPLL approach exhibits superior digital-to-phase conversion linearity. Further, the output frequency being same as the input reference frequency mandates a high-frequency reference clock which allows the PRPLL to have a very high bandwidth. This helps to suppress VCO phase noise and reduce loop filter area. These advantages were exploited in [29,30], where the PRPLL was used

to interpolate between phases and implement sub-rate CDRs. However, the need for a high-frequency reference clock (at approximately the data rate) has restricted the widespread usage of PRPLLs in PI-based CDRs. In view of this, we seek to obviate the need for a reference clock and present a reference-less PRPLL-based CDR.

Figure 3.2: Block diagram of a PRPLL.

# 3.2 Proposed CDR Architecture

To arrive at the proposed architecture, we start with the PRPLL-based CDR (Fig. 3.3(a)). Note that, in steady state,  $ACC_I$  output represents the frequency error between the incoming data and the PRPLL output. Therefore, we postulate that frequency locking can also be achieved by tuning the PRPLL output frequency indirectly by tuning its reference clock frequency using  $ACC_I$  output. To this end, a digitally-controlled oscillator (DCO) is

used, as shown in Fig. 3.3(b), to generate reference clock for the PRPLL. In steady state, the DCO would be tuned to the data rate. We further observe that the newly added DCO path also implements the frequency control portion of the CDR and appears in parallel to the original frequency control path through phase accumulator  $ACC_P$ . Thus, it is unnecessary to feed  $ACC_I$  output into the phase-tuning port of the PRPLL. Applying this modification leads to the CDR depicted in Fig. 3.3(c), which can be redrawn as shown in Fig. 3.3(d). Looking at Fig. 3.3(d) reveals that the proposed CDR can be simply viewed as a Type-II CDR in which the proportional path is implemented in phase domain as opposed to digital (or analog) domain in conventional CDRs. As will be illustrated shortly, this way of implementing proportional control gives rise to many attractive features such as well controlled JTRAN, decoupled JTRAN/JTOL and JTRAN/JGEN behavior.

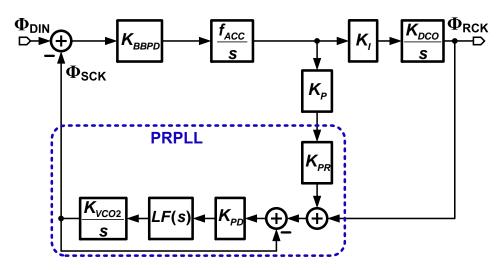

#### 3.2.1 Linear Analysis

A linear model of the proposed CDR is depicted in Fig. 3.4. BBPD is represented by its linearized gain,  $K_{BBPD}$ , given by [23]:

$$K_{BBPD} = \frac{1}{\sigma_i \sqrt{2\pi}} \tag{3.1}$$

where input jitter is assumed to have normal distribution with zero mean and a variance of  $\sigma_j^2$ . The loop gain of the CDR,  $LG_{CDR}(s)$ , is given by:

$$LG_{CDR}(s) = \rho K_{BBPD} \left( \frac{f_{ACC}}{s} K_P K_{PR} + \frac{f_{ACC}}{s} \frac{K_I K_{DCO}}{s} \right) \frac{LG_{PRPLL}(s)}{1 + LG_{PRPLL}(s)}$$

(3.2)

where  $\rho$  is input data transition density,  $K_{DCO}$  is digitally-controlled oscillator (DCO) gain,  $f_{ACC}$  is the frequency at which accumulators ACC<sub>P</sub> and ACC<sub>I</sub> are clocked, and  $K_{PR}$  is the phase interpolation gain of the PRPLL.  $LG_{PRPLL}(s)$  is the loop gain of the PRPLL and is equal to:

$$LG_{PRPLL}(s) = K_{PD}LF(s)\frac{K_{VCO2}}{s}$$

(3.3)

Figure 3.3: Evolution of the proposed CDR.

where  $K_{PD}$  and  $K_{VCO2}$  are gains of the PD and the oscillator, respectively. Since PRPLL bandwidth is designed to be much larger than that of the CDR,  $LG_{PRPLL}(s)/1 + LG_{PRPLL}(s) \approx 1$  in the vicinity of CDR transfer bandwidth. Using this simplification, input to RCK transfer function,  $H_{IN2RCK}(s)$ , can be calculated to be:

$$H_{IN2RCK}(s) = \frac{\Phi_{RCK}(s)}{\Phi_{DIN}(s)} = \frac{\rho K_{BBPD} f_{ACC} K_I K_{DCO}}{1 + LG_{CDR}(s)}$$

$$= \frac{\rho K_{BBPD} f_{ACC} K_I K_{DCO}}{s^2 + s\rho K_{BBPD} f_{ACC} K_P K_{PR} + \rho K_{BBPD} f_{ACC} K_I K_{DCO}}$$

(3.4)

The above equation reveals that there are two poles and importantly no zeros in the transfer function. Due to the absence of zeroes, jitter peaking can be completely eliminated simply by making the two poles to be real. Under this condition, the location of the two poles can be determined to be:

$$\omega_{p1} = \frac{-\rho K_{BBPD} f_{ACC} K_P K_{PR} + \sqrt{(\rho K_{BBPD} f_{ACC} K_P K_{PR})^2 - 4\rho K_{BBPD} f_{ACC} K_I K_{DCO}}{2}$$

$$= \frac{K_{PP}}{2} (-1 + \sqrt{1 - \frac{4K_{INT}}{K_{PP}^2}})$$

$$\approx -\frac{K_{INT}}{K_{PP}} = -\frac{\rho K_{BBPD} f_{ACC} K_I K_{DCO}}{\rho K_{BBPD} f_{ACC} K_P K_{PR}} = -\frac{K_I K_{DCO}}{K_P K_{PR}}$$

(3.5)

$$\omega_{\rm p2} = \frac{-\rho K_{\rm BBPD} f_{\rm ACC} K_{\rm P} K_{\rm PR} - \sqrt{(\rho K_{\rm BBPD} f_{\rm ACC} K_{\rm P} K_{\rm PR})^2 - 4\rho K_{\rm BBPD} f_{\rm ACC} K_{\rm I} K_{\rm DCO}}{2}$$

$$= \frac{K_{\rm PP}}{2} \left(-1 - \sqrt{1 - \frac{4K_{\rm INT}}{K_{\rm PP}^2}}\right)$$

$$\approx -K_{\rm PP} = -\rho K_{\rm BBPD} f_{\rm ACC} K_{\rm P} K_{\rm PR}$$

(3.6)

where  $\omega_{\rm p1}$  is the lower of the two pole frequencies. Because  $\omega_{\rm p1} \ll \omega_{\rm p2}$ , jitter transfer bandwidth (JTRAN) approximately equals to  $|\omega_{\rm p1}|$ .

The transfer function from input to SCK can be similarly calculated and is given by:

$$H_{IN2SCK}(s) = \frac{\Phi_{SCK}(s)}{\Phi_{DIN}(s)} = \frac{LG_{CDR}(s)}{1 + LG_{CDR}(s)}$$

$$= \frac{s\rho K_{BBPD} f_{ACC} K_P K_{PR} + \rho K_{BBPD} f_{ACC} K_I K_{DCO}}{s^2 + s\rho K_{BBPD} f_{ACC} K_P K_{PR} + \rho K_{BBPD} f_{ACC} K_I K_{DCO}}$$

(3.7)

Note that the above transfer function has the same two poles as those of  $H_{IN2RCK}(s)$ . However, much like in a conventional type-II PLL (and unlike  $H_{IN2RCK}(s)$ ), the transfer function contains a pole-zero pair ( $\omega_{p1}$  and  $\omega_{z1} = -K_I K_{DCO}/K_P K_{PR}$ ). If  $\omega_{p1}$  and  $\omega_{z1}$  perfectly cancel, as desired in most applications, the jitter tracking bandwidth (or equivalently JTOL corner frequency) equals  $\omega_{p2}$ . In case of imperfect cancellation, JTOL corner frequency varies in proportion to the cancellation inaccuracy. It is important to note that, in the proposed architecture, the mismatch in the pole-zero cancellation does not change jitter transfer (JTRAN) bandwidth, which is determined by the dominant pole ( $\omega_{p1}$ ) as illustrated earlier. Approximately, JTOL corner frequency is given by:

JTOL corner frequency =

$$|\omega_{p2}| \approx \rho K_{BBPD} f_{ACC} K_P K_{PR}$$

(3.8)

Based on the analysis presented thus far, two important observations can be made: (1) unlike conventional bang-bang CDRs, the JTRAN bandwidth of the proposed CDR is independent of the BBPD gain (see Eq. (3.5)). (2) JTRAN and JTOL bandwidths are completely decoupled, unlike in a conventional type-II CDR where they are both set by  $\omega_{p2}$  [15]. As a result of using voltage controlled delay line (VCDL) as the phase shifter in the data path, CDRs reported in [12,25,31] also possess this property. However, using a PRPLL in the clock path as proposed offers two main advantages. First, PRPLL consumes significantly less power compared to a VCDL designed to minimize inter-symbol interference in the input data. In other words, achieving long delay without attenuating input signal requires a large number of power hungry delay buffers [12]. Second, infinite phase shifting capability of the PRPLL eliminates the mid-frequency JTOL limitation that comes with limited range of VCDL [31].

#### 3.2.2 Stability Analysis

Compared to a conventional type-II CDR, the stability analysis of the proposed CDR is complicated since the PRPLL is embedded in the CDR loop. A common strategy to stabilize systems with embedded feedback loops is based on choosing widely separated individual loop bandwidths. However, this approach is complicated by the unpredictability of the CDR loop band-

Figure 3.4: Linearized phase-domain model of the proposed CDR.

width caused by non-linearity of the BBPD. In this work, the impact of PRPLL on the CDR loop stability is minimized by making the slew rate of phase tracking in the CDR to be much smaller than that of PRPLL loop [28]. Mathematically, this condition is expressed as follows:

$$\frac{\mathrm{K}_{\mathrm{P}}\Delta\Phi_{\mathrm{pp}} + \mathrm{K}_{\mathrm{I}}\Delta\Phi_{\mathrm{int}}}{2\pi \cdot \mathrm{T}_{\mathrm{ACC}}} \ll \mathrm{f}_{\mathrm{PRPLL}}$$

(3.9)

where  $\Delta \Phi_{\rm pp} = K_{\rm PR}$  and  $\Delta \Phi_{\rm int} = K_{\rm DCO}$  are the magnitudes of maximum phase deviations caused by proportional and integral control, respectively,  $f_{\rm PRPLL}$  is the bandwidth of PRPLL, and  $T_{\rm ACC}$  (= 1/ $f_{\rm ACC}$ ) is the update period of accumulators. Under this condition, the proposed CDR behaves much like a conventional type-II CDR and its stability can be ensured by choosing the proportional path gain to be much larger than the integral path gain. To this end, stability factor,  $\xi$  as defined below, must be chosen to be much greater than one [14].

Stability factor

$$\xi = \frac{K_P \Delta \Phi_{pp}}{K_I \Delta \Phi_{int}} \gg 1$$

(3.10)

In the proposed architecture, at an operating frequency of  $f_{VCO} = 2.5 \text{ GHz}$ ,  $\Delta \Phi_{pp} = \frac{2\pi}{64} \text{ rad/s}$ ,  $\Delta \Phi_{int} = \frac{2\pi}{6.25 \times 10^3} \text{ rad/s}$ ,  $K_P = 1/2$ ,  $K_I = 1/4$ , and  $f_{ACC} = f_{VCO}/4$ , the lower bound on  $f_{PRPLL}$  is about 5 MHz while the upper bound is approximately equal to 1/10 of the VCO frequency which can be as high as 250 MHz [32]. Stability factor is approximately 195. Having discussed the key features of the proposed CDR, the circuit implementation details are presented next.

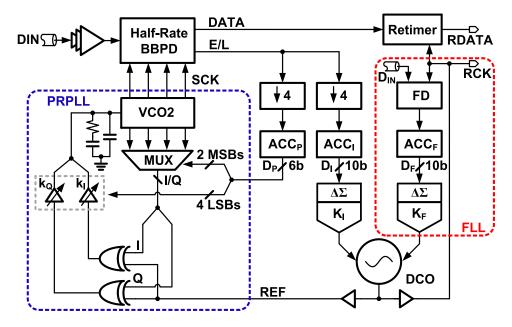

## 3.3 Circuit Design

Figure 3.5: Detailed schematic of the proposed reference-less PRPLL-based CDR.

The detailed schematic of the CDR is shown in Fig. 3.5 [19]. Input data, DIN, is buffered by a two-stage limiting amplifier and fed to a half-rate BBPD (HR-BBPD) whose output is decimated by a factor of 4 to ease the speed requirements of digital circuits such as accumulators [15]. The decimated BBPD output is fed to integral and proportional paths, which control the DCO and PRPLL separately.

The PRPLL provides four equally-spaced sampling clock phases (SCK) for HR-BBPD, and the retimer compensates timing difference between SCK and RCK to guarantee correct retimed data (RDATA). For frequency acquisition, a divide-by-1024 stage divides the input data to generate a stochastic reference clock for the frequency-locked loop (FLL) [13]. The FLL path consists of a divider-based frequency detector (FD), a 10-bit digital accumulator (ACC<sub>F</sub>), and a delta-sigma DAC whose gain is denoted as  $K_F$ . The rest of the section focuses on the circuit implementation details of the PRPLL and

key CDR building blocks.

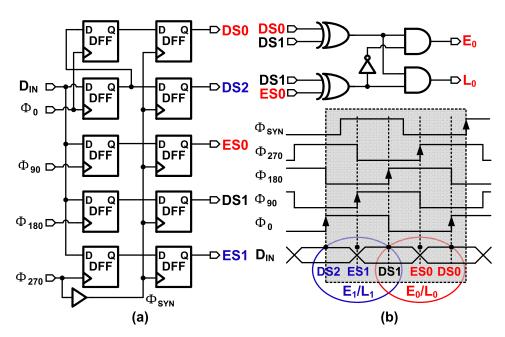

#### 3.3.1 Phase-Rotating PLL Design

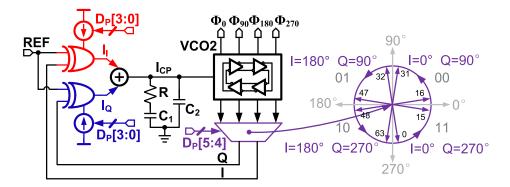

Figure 3.6: Schematic of phase-rotating PLL with quadrant segmentation.

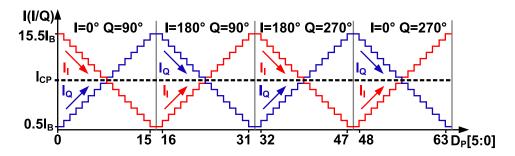

The block diagram of the PRPLL implemented in the prototype is shown in Fig. 3.6. Compared to the PRPLL in [28], two new techniques to improve phase interpolation linearity and power efficiency are proposed. The power dissipation in a conventional PRPLL is dominated by the XOR phase detectors and the voltage-to-current (V-I) converter needed to drive the passive loop filter. Current-mode logic (CML) XOR gates and the high-frequency V-to-I converter consume significant portion of the PRPLL power in [29]. In view of this, we propose a segmented phase interpolation to reduce the number of phase detectors and embed charge-pumps into CMOS XOR gates to eliminate high-bandwidth V-to-I converter (see Fig. 3.8). As shown in Fig. 3.6, segmentation is implemented by first selecting two adjacent clock phases, denoted as I/Q, corresponding to the quadrant in which phase interpolation occurs with the two most significant bits (MSBs) and using rest of the four least significant bits (LSBs) to vary currents  $I_I$  and  $I_Q$  in each of the two XOR phase detectors. To better illustrate the phase interpolation behavior, the relationship between PD output current and input control word,  $D_P$ , is depicted in Fig. 3.7. Note that the exact locking position is 90° apart from the quadrant decided by I/Q phases as depicted in Fig. 3.6 due to the behavior of XOR phase detectors. Further, this segmented approach of using a quadrant multiplexer and only two phase-detectors is easily scalable when dealing with a larger number of VCO phases to achieve better phase resolution in the PRPLL.

Figure 3.7: Phase-rotating process in PRPLL.

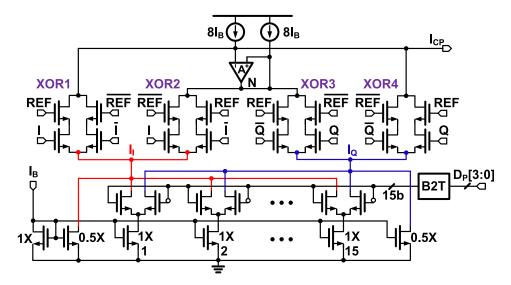

The proposed circuit that combines XOR phase detectors with charge pump (XORPD-CP) is shown in Fig. 3.8. It consists of four XOR phase detectors, a current steering DAC, two fixed current sources and a balancing amplifier. The current steering DAC controls the tail current of the XOR phase detectors using the digital codes from the CDR logic. The DAC has 15 unit current source elements, each steering current  $I_{LSB}$ . Each of the two fixed current sources sinks  $0.5 I_{\text{LSB}}$  current and helps to improve the speed of the DAC [33]. The DAC can sink a maximum of  $15.5 I_{LSB}$  current while the fixed current sources each pump  $8 I_{LSB}$  current. The outputs of the two main XOR phase detectors (XOR1, XOR4) are combined to generate the charge pump current  $I_{CP}$ . The complementary phase detectors (XOR2, XOR3) conduct when the main XOR phase detectors are off and steer current into the virtual ground node N. This maintains constant current sink through the DAC, thereby eliminating large voltage fluctuations on the DAC output nodes  $I_I$  and  $I_Q$ . A balancing amplifier further suppresses any residual voltage fluctuations and helps to improve PI linearity. It should be noted that the balancing amplifier does not require a large bandwidth as it is used only to maintain the steady state operating point of virtual ground node.

#### 3.3.2 Limiting Amplifier

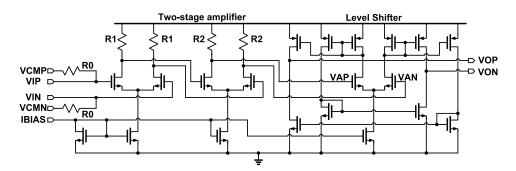

The schematic of the limiting amplifier used to buffer the input data is shown in Fig. 3.9. It is implemented using a cascade of two CML stages and a CML-to-CMOS converter. The combined gain and bandwidth of the two CML stages are about 22 dB and 2.6 GHz, respectively. A CML-to-CMOS converter serves the dual purpose of generating rail-to-rail CMOS outputs and isolating the CML stages from the BBPD kick-back noise.

Figure 3.8: Schematic of combined XORPD and charge pump (XORPD-CP).

Figure 3.9: Schematic of the limiting amplifier.

#### 3.3.3 Half-Rate Bang-Bang Phase Detector