# MULTIGATE MOSFETS FOR DIGITAL PERFORMANCE AND HIGH LINEARITY, AND THEIR FABRICATION TECHNIQUES

BY

#### YI SONG

#### **DISSERTATION**

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2016

Urbana, Illinois

#### **Doctoral Committee:**

Professor Xiuling Li, Chair Professor Milton Feng Associate Professor Pavan Kumar Hanumolu Assistant Professor Wenjuan Zhu

#### **ABSTRACT**

The aggressive downscaling of complementary metal—oxide—semiconductor (CMOS) technology is facing great challenges to overcome severe short-channel effects. Multigate MOSFETs are one of the most promising candidates for scaling beyond Si CMOS, due to better electrostatic control as compared to conventional planar MOSFETs.

Conventional dry etching-induced surface damage is one of the main sources of performance degradation for multigate transistors, especially for III-V high mobility materials. It is also challenging to increase the fin aspect ratio by dry etching because of the non-ideal anisotropic etching profile. Here, we report a novel method, inverse metal-assisted chemical etching (i-MacEtch), in lieu of conventional RIE etching, for 3D fin channel formation. InP junctionless FinFETs with record high-aspect-ratio (~ 50:1) fins are demonstrated by this method for the first time. The i-MacEtch process flow eliminates dry-etching-induced plasma damage, high energy ion implantation damage, and high temperature annealing, allowing for the fabrication of InP fin channels with atomically smooth sidewalls. The sidewall features resulting from this unique and simplified process ensure high interface quality between high-k dielectric layer and InP fin channel. Experimental and theoretical analyses show that high-aspect-ratio FinFETs, which could deliver more current per area under much relaxed horizontal geometry requirements, are promising in pushing the technology node ahead where conventional scaling has met its physical limits.

The performance of the FinFET was further investigated through numerical simulation. A new kind of FinFET with asymmetric gate and source/drain contacts has been proposed and simulated. By benchmarking with conventional symmetric FinFET, better short-channel behavior with much higher current density is confirmed. The design guidelines are provided. The

overall circuit delay can be minimized by optimizing gate lengths according to different local parasites among circuits in interconnection-delay-dominated SoC applications.

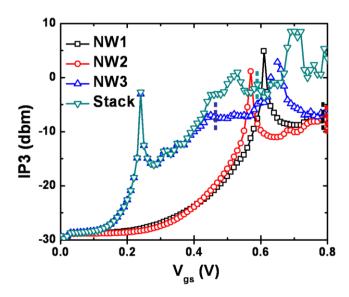

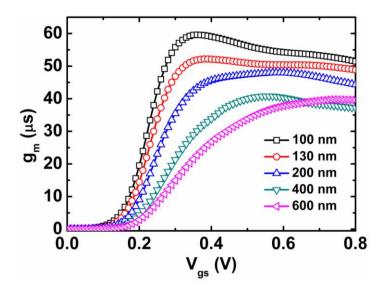

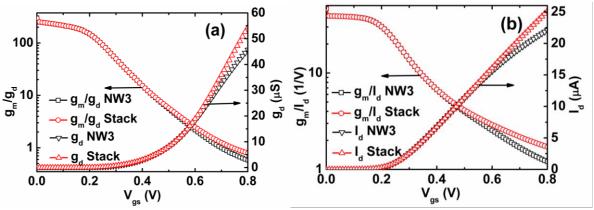

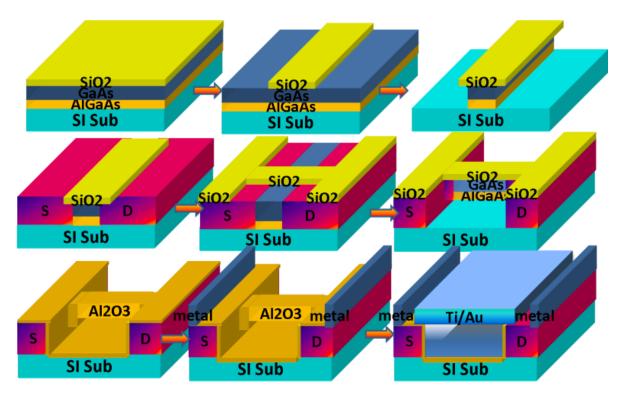

Continued transistor scaling requires even stronger gate electrostatic control over the channel. The ultimate scaling structure would be gate-all-around nanowire MOSFETs. We demonstrate III-V junctionless gate-all-around (GAA) nanowire (NW) MOSFETs for the first time. For the first time, source/drain (S/D) resistance and thermal budget are minimized by regrowth using metalorganic chemical vapor deposition (MOCVD) in III-V MOSFETs. The fabricated short-channel ( $L_g$ =80 nm) GaAs GAA NWFETs with extremely narrow nanowire width ( $W_{NW}$ = 9 nm) show excellent transconductance ( $g_m$ ) linearity at biases (300 mV), characterized by the high third intercept point (2.6 dBm). The high linearity is especially important for low power applications because it is insensitive to bias conditions.

To my mother and father

#### ACKNOWLEDGMENTS

My deepest appreciation goes to Prof. Xiuling Li, who gave me intensive guidance and support for my graduate study. It is my great fortune to study under her. She is wise and kind to provide me all kinds of support. She granted me a lot of freedom to explore new things and trusted me. All my accomplishments would be impossible without her precious help.

My gratitude goes to professors who gave their generous help, such as Prof. Milton Feng, Prof. Wenjuan Zhu and Prof. Pavan Kumar Hanumolu on my committee, who taught me and helped me intensively with thoughtful discussions. I thank the respected professors in ECE Illinois, who gave me great instruction during my Ph.D. study, such as Prof. Ilesanmi Adesida, Prof. Elyse Rosenbaum, Prof. Martin D F Wong, Prof. Kanti Jain and Prof. Eric Pop.

I thank all past and current members of Prof. Li's group for their great help and consistent support. They are Parsian Mohseni, Jae Choel Shin, Ryan Dowdy, Kevin Bassett, Xin Miao, Chen Zhang, Karthik Balasundaram, Kelson Chabak, Wonsik Choi, Seung Hyun Kim, Paul Froeter, Kyooho Jung, J. D. Kim, Lingyu Kong, and others.

I thank the previous and current Micro and Nanotechnology Laboratory staff including Edmond Chow, Yaguang Lian, Hal Romans, Ken Tarman, Clay Childers, Xin Yu and John Hughes for the good maintenance of cleanroom facilities. And I thank the staff in the Materials Research Lab, such as Tao Shang, for their precious support.

I thank the financial supports from the National Science Foundation (NSF) and the International Institute for Carbon Neutral Energy Research (I2CNER).

Finally, I sincerely appreciate my parents who support me with all kinds of encouragement and solicitude through all my life.

# TABLE OF CONTENTS

| CHAPTER 1 – INTRODUCTION                                                       | 1      |

|--------------------------------------------------------------------------------|--------|

| 1.1 Challenges for the down-scaling of metal-oxide-semiconductor field-effect  |        |

| transistors                                                                    | 1      |

| 1.2 Multigate MOSFETs                                                          | 2      |

| 1.2.1 Double-gate FinFETs                                                      | 3      |

| 1.2.2 Tri-gate and Pi-gate MOSFETs                                             | 6      |

| 1.2.3 Gate-all-around MOSFETs                                                  | 11     |

| 1.2.4 Junctionless mode multigate MOSFETs                                      | 16     |

| 1.2.5 Comparison between inversion mode and junctionless mode multigate MOSF.  | ETs 20 |

| CHAPTER 2 – METAL-ASSISTED CHEMICAL ETCHING FOR                                | III-V  |

| MULTIGATE MOSFET FABRICATION                                                   | 23     |

| 2.1 Problems with conventional dry etching for fin formation                   | 23     |

| 2.2 Principle of metal-assisted chemical etching                               | 24     |

| 2.3 Fabrication of high-aspect-ratio InP FinFET by MacEtch                     | 29     |

| 2.4 Device characterization and discussion                                     | 33     |

| 2.5 Theoretical investigation of the scaling behavior of high AR on JL FinFETs | 37     |

| 2.5.1 Device operating principle and optimization process                      | 38     |

| 2.5.2 Projections for the ultimate scaling performance                         |        |

| CHAPTER 3 – DEVICE STRUCTURE DESIGN FOR ULTIMATE SCALIN                        | IG OF  |

| MULTIGATE MOSFETS                                                              | 44     |

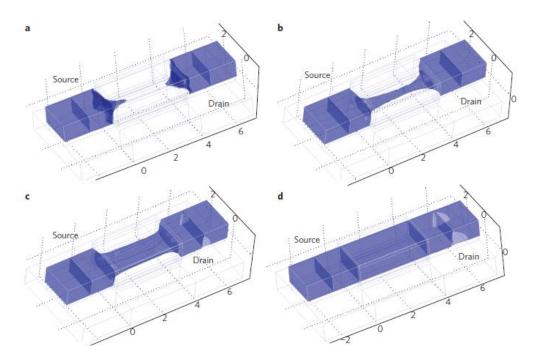

| 3.1 Challenges with the scaling of FinFETs                                     | 44     |

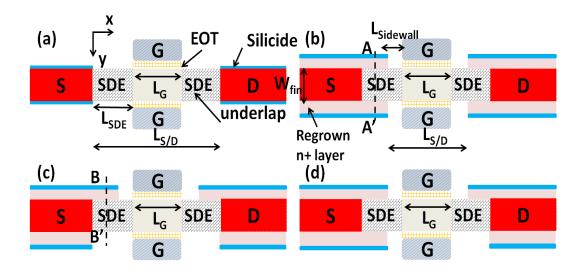

| 3.2 One-sided source/drain extension contact FinFET for low power applications | 47     |

| 3.2.1 Background of conventional symmetric SDE FinFETs                         | 47     |

| 3.2.2 Concept of one-sided SDE contact FinFETs                                 | 48     |

| 3.2.3 Performance analysis of one-sided SDE contact FinFETs                    | 51     |

| 3.3 Asymmetric gate FinFET for high performance system-on-chip (SoC)                                           |

|----------------------------------------------------------------------------------------------------------------|

| applications55                                                                                                 |

| 3.3.1 Underlapped gate to SDE doping and spacer design                                                         |

| 3.3.2 Design of asymmetric gate FinFETs                                                                        |

| 3.4 Scaling junctionless multigate field-effect transistors by step-doping                                     |

| 3.4.1 Problems with scaling of junctionless transistor                                                         |

| 3.4.2 Illustration for device structure with step-doping and simulation methodology 62                         |

| 3.4.3 Improved scaling performance by step-doping                                                              |

| CHAPTER 4 – GATE-ALL-AROUND NANOWIRE MOSFET FOR HIGH                                                           |

| LINEARITY LOW-POWER APPLICATION69                                                                              |

| 4.1 Motivations for improving linearity in MOS transistors                                                     |

| 4.2 Vertically-stacked individually-tunable nanowire field effect transistors for low                          |

| power operation with ultrahigh radio frequency linearity                                                       |

| 4.2.1 Device structure illustration and simulation methodology                                                 |

| 4.2.2 Device design for improving linearity by stacking nanowire channels                                      |

| 4.3 Improving linearity by junctionless gate-all-around nanowire transistors                                   |

| 4.3.1 Experimental process flow for junctionless gate-all-around nanowire transistor 79                        |

| 4.3.2 Device characterization and discussion                                                                   |

| CHAPTER 5 – FUTURE WORK                                                                                        |

| 5.1 Developing improved high-aspect-ratio FinFETs                                                              |

| 5.2 Developing MacEtch for other materials, like Ge, InAs, In <sub>0.53</sub> Ga <sub>0.47</sub> As and GaP 89 |

| 5.2.1 Achieving atomically smooth sidewalls with minimized interface states                                    |

| 5.2.2 Searching for CMOS compatible MacEtch catalyst                                                           |

| REFERENCES93                                                                                                   |

| APPENDIX A MODELING OF ONE-SIDED S/D CONTACT DOUBLE-GATE                                                       |

| FINFET                                                                                                         |

|                                                                                                                |

| APPENDIX B DETAILS OF ELECTRON BEAM LITHOGRAPHY FOR DEVICE                                                     |

| FABRICATION106                                                                                                 |

| APPENDIX C MACETCH OF INP SUSPENDED NANOWIRES 109                                                              |

#### **CHAPTER 1 – INTRODUCTION**

The integrated circuit (IC) industry has benefited from driving Moore's law for decades. Primarily by dimensional downscaling of the channel length, we can obtain higher performance, lower power consumption and more complex functionality per area, faster switching speeds, and reduced cost per transistor. As MOSFET feature dimensions shrink down to sub-20nm range, nanoscale processing encounters tremendous difficulties, for instance, severe short-channel effects, degraded driving ability, high-field effect, direct gate tunnelling current, high series resistance and nanopatterning issues, etc. Continuing Moore's law encounters unprecedented difficulties. Tremendous technical innovations are required to develop CMOS devices beyond the 10 nm technology node. Enormous efforts have been made in developing new materials, processes, and architectures for the next generation of transistors with shorter channel length [1].

#### 1.1 Challenges for the down-scaling of metal-oxide-semiconductor field-effect transistors

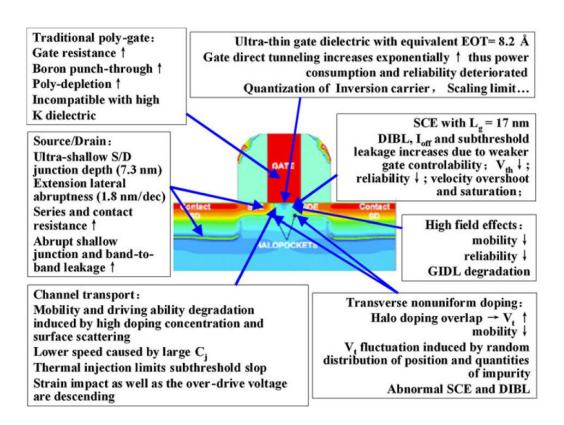

As the feature size of MOSFETs continues shrinking according to Moore's law, CMOS technology faces tremendous challenges, primarily due to severe short-channel effects (SCE). Figure 1.1 depicts the major challenges associated with scaling of channel length, and Table 1.1 summarizes the targets for scaling proposed by ITRS. The major innovations are based on the introduction of new high-k/metal gate stacks, advanced S/D technologies, mobility enhancement technologies and advanced multigate structures. In this thesis, the main focus will be developing advanced multigate transistor structures, both by device simulation design and new fabrication technologies.

Figure 1.1: Difficult challenges for the scaling of CMOS device. Reprinted with permission from [1].

Table 1.1: Summary of technology trend targets proposed by ITRS 2013 [2]

| year | Node name | Logic half | Fin half   | Fin width | 6-t SRAM   | $V_{dd}(V)$ | 1/CV/I   |

|------|-----------|------------|------------|-----------|------------|-------------|----------|

|      | (nm)      | pitch (nm) | pitch (nm) | (nm)      | size (μm²) |             | (1/psec) |

| 2017 | 7         | 25         | 19         | 6.8       | 0.038      | 0.8         | 1.75     |

| 2021 | 3.5       | 16         | 12         | 6.1       | 0.015      | 0.74        | 2.10     |

| 2025 | 1.8       | 10         | 7.5        | 5.4       | 0.006      | 0.68        | 2.52     |

### 1.2 Multigate MOSFETs

Novel device structures (e.g. nonplanar MOSFETs such as double-gate or tri-gated/ $\Omega$ -gated FinFET, and ultimately, gate-all-around FET) are indispensable for the continuous scaling of CMOS devices due to the effective suppression of short-channel effects. The device structures evolve from single-gated planar FET to fully gate-all-around MOSFET. The increased number of

gates enhances electrostatic control of the gate electrode over the charge carriers flowing from source to drain in the channel, and therefore reduces the short-channel effects.

### 1.2.1 Double-gate FinFETs

The scaling of planar MOSFETs is limited by severe transverse short-channel effects and longitudinal gate dielectric tunneling; moreover, the controllability of single-gate MOSFETs is much weaker than multigate MOSFETs (FinFETs or tri-gate transistor). FinFETs are promising candidates for nanoscale devices with 10-30nm gate length due to quasi-planar architecture and simplicity of fabrication process that is compatible with traditional CMOS process [3, 4]. FinFETs do not require dopant concentration as high as planar transistors and thus could suppress short-channel effects more effectively. The gate is self-aligned with S/D, and it is better for controlling electrostatic between S/D which results in near-ideal subthreshold gradient and excellent DIBL behavior.

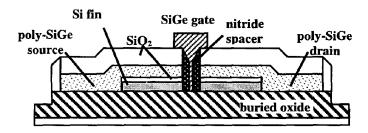

Figure 1.2: The early proposed self-aligned double-gate FinFETs on SOI substrate. Reprinted with permission from [5].

The first proposed self-aligned double-gate FinFET with gate-length of 45nm by quasi-planar process is shown in Figure 1.2 [5]. The deposited SiO<sub>2</sub> and SiN serve as hard mask, and then the fin structure is exposed by electron beam lithography. After the deposition of gate SiO<sub>2</sub> and in situ doped poly-silicon stack, the silicon S/D is etched with the fin protected by hard mask. Then a GeSi layer is deposited to form the raised S/D, and silicidation completes the process. The gate-last process is compatible with low-temperature high-k/metal gate integration. The ultra-

thin fin body significantly suppresses short-channel effects and the poly-SiGe raised S/D lowers the contact resistance. The fabricated devices show good performance characteristics with high on-current of 820  $\mu$ A/ $\mu$ m at V<sub>dd</sub>=1.2V.

As for UTB SOI double-gate MOSFETs using SiO<sub>2</sub>-based dielectrics, it is found that there exists a stringent confinement for scaling the thickness of the silicon body to reach the specifications of the ITRS in terms of drain and gate leakage current. Meanwhile, moderate gate-S/D underlap not only benefits the suppression of gate-induced drain leakage (GIDL) [6], but also could control the effective gate length by different bias, thus relaxing the requirement for ultra-narrow fin width.

Combing strain technologies such as compressive and tensile contact-etch-stop liners could improve the drive-current enhancement by a factor of 2 in both n- and p-FinFETs [7], and allow V<sub>dd</sub> scaling and trade enhanced carrier velocity for reduced inversion charge [8].

Metal-gate with tunable work-function is required to avoid applying high channel doping to achieve ideal V<sub>th</sub>. In addition, integration of metal gate with SOI FinFETs could induce strain to the Si(110) channel [9]. The adjusting requirement of gate work function for double FinFETs is relaxed compared with planar MOSFETs. The performance of nMOS and pMOS could be optimized simultaneously by adjusting gate work functions, achieving symmetrical V<sub>th</sub> and high I<sub>on</sub>.

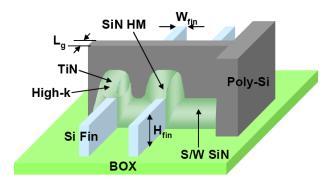

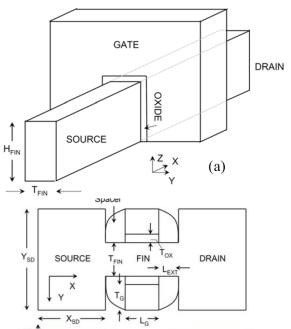

The device structure is shown in Figure 1.3. The fin structure is etched with nitride hard mask. Annealing in H<sub>2</sub> atmosphere is performed to reduce surface roughness. 3nm HfSiO and 3-20nm TiN are deposited using atomic layer deposition. The S/D implantation and Ni silicidation are performed after the nitride spacer formation. The poly-silicon is deposited at the end.

TiN layer with different thickness and deposition methods would induce different strain into the channel. Thin TiN and Ti-rich TiN corresponds to high tensile stress, while thick TiN deposited by atomiclayer or chemical vapor deposition corresponds to compressive stress. The discrepancy between different crystal orientations diminishes with the decrease of channel length; therefore, high performance of CMOS device with identical crystal orientation is promising.

Figure 1.3: FinFET integration with TiN metal gate-induced stress on SOI substrate. Reprinted with permission from [9].

FinFET is preferable for storage application because it could increase density due to its 3D nature. Recently, highly scaled FinFET SRAM cells, of area down to  $0.128\mu m^2$ , were fabricated using high- $\kappa$  dielectric and a single metal gate [10]. It is demonstrated that the un-doped FinFET SRAM cell has a significant advantage in read/write margin over a planar-FET SRAM cell, which would have higher  $\sigma V_{th}$  mainly caused by heavy doping into the channel region, further substantiating the superior scaling capability of FinFETs.

There are severe challenges such as the simplicity of the integration technology, high reliability and reproducibility, and ultra-high parasitic S/D resistance due to greatly suppressed effective contact area in multigate device (as well as UTB-SOI in the previous section). The complicated fabrication process also may induce severe parasitic parameters. The sub-20nm gate length device is greatly influenced by quantum confinement effects and has high sensitivity to

process variations [11]. Simulation results show that device performance has high sensitivity to the fin width variation [12] and gate work function variation [13] in sub-20nm regime. Great efforts are still required for the practicality of double-gate MOSFETs.

#### 1.2.2 Tri-gate and Pi-gate MOSFETs

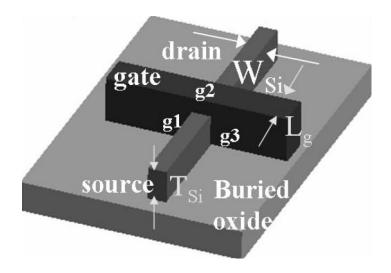

Figure 1.4: Illustration of the device structure of tri-gate MOSFETs. Reprinted with permission from [14].

The tri-gate MOSFET which has a top and two side gates on an insulating layer is superior to double-gate FinFET for further suppressing short-channel effects due to enhanced gate electrostatic control. Fully-depleted (FD) tri-gate CMOS transistors with 60nm physical gate lengths have been successfully fabricated on SOI substrates [14]. Figure 1.4 shows a schematic of the device structure of a tri-gate MOSFET. The transistors show near-ideal subthreshold gradient, excellent DIBL behavior and high drive current. The most significant aspect for tri-gate MOSFETs is the much-relaxed silicon body dimensions requirement for full depletion conditions, thus achieving excellent short-channel performance without tightening the lithography requirements.

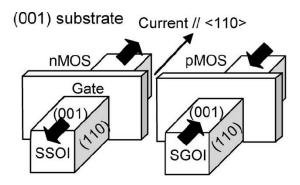

The mobility enhancement technologies are important for boosting tri-gate device performance. Novel schematic integration strategies are needed due to the complex threedimensional structures of tri-gate devices. Studies have shown that <1 1 0> current (or strain) direction is the best for strained tri-gate nMOS since 2.0×mobility enhancement in uniaxially strained silicon-on-insulator (SOI) tri-gate nMOS with (1 1 0) sidewall channels is obtained due to uniaxial strain inducing the repopulation of electrons from fourfold valleys to twofold valleys [15]. Figure 1.5 shows the ideal integration of different strain technology for tri-gate CMOS.

Figure 1.5: Proposed tri-gate CMOS structures, utilizing a SSOI nMOS and SGOI (GOI) pMOS with optimized uniaxial tensile and compressive stress and current flow direction. Reprinted with permission from [15].

As a result, a novel multigate device structure having a high uniaxial mobility channel by appropriately merging globally strained substrates with a local strain technique called lateral strain relaxation is developed [16]. The additive integration of channel materials, strain configuration and current flow direction is attractive for boosting tri-gate transistors. SiGe or Ge channels, (110) surface orientation/<110> channel direction and uniaxial compressive strain along <110> direction are used as pMOS boosters with additional advantages of low contact and S/D sheet resistances of p<sup>+</sup>-SiGe layers. The local Ge condensation technique is utilized to form local SGOI regions for pMOS on SSOI substrates [17]. The uniaxial stress could be formed on the SiGe channel by applying a lateral strain relaxation process. Strained Si directly on insulator (SSOI) substrates [18], where biaxial or uniaxial tensile strain is along the <100> current flow direction, could be used as nMOS boosters.

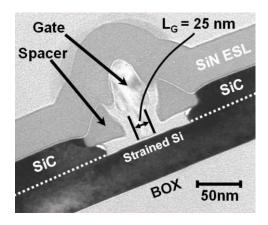

Si<sub>0.99</sub>C<sub>0.01</sub> S/D and tensile stress SiN etch-stop layer (ESL) could be combined as the stressor for boosting 25nm gate length n-FinFET performance by introducing large strain to channel as shown in Figure 1.6 [19]. The key of the fabrication process is selective epitaxy raised after Si<sub>0.99</sub>C<sub>0.01</sub> S/D and spacer formation, then LPCVD high stress SiN ESL deposition after S/D implantation and activation. This combination results in an encouraging 56% I<sub>Dsat</sub> enhancement over the control non-strained FinFETs.

Figure 1.6: TEM micrograph of tri-gate device featuring 25 nm poly-Si gate with a raised Si<sub>0.99</sub>C<sub>0.01</sub> S/D combined tensile stress SiN etch-stop layer. Reprinted with permission from [19].

The surface roughness and the shape of the sidewalls are found to be important for improving the performance of the strained-NW MOSFETs. A kind of anisotropic thermal etching technique in H<sub>2</sub> atmosphere is developed in order to fabricate strained Si and SiGe tri-gate nanowire (NW) MOSFETs with reduced line-edge roughness and smooth direction [20]. Mobility enhancement due to strain is observed for the reduced surface roughness scattering.

The contact resistance between the S/D silicide and Si-fin dominates the parasitic S/D resistance of multiple-gate FETs, which is a great barrier for scaling. Simply applying the selective epitaxial growth of Si on S/D regions is not enough to meet the semiconductor roadmap target for parasitic S/D resistance for aggressively scaled tri-gate CMOS [21]. Therefore, in order to reduce the S/D parasitic resistance in SiGe source/drain tri-gate devices, metal

germanosilicide is considered as the natural solution. Nickel germanosilicide (NiSiGe) is not suitable with morphological instability due to agglomeration and germanium (Ge) out-diffusion [22], while an appropriate concentration of Pt (about 10 at.%) could provide superior morphological stability and reduced Schottky barrier height for holes with an acceptable sheet resistivity. In consequence, this gives rise to an overall 18% enhancement in drive current performance compared with NiSiGe contact technology [23].

Fabrication of tri-gate MOSFETs on bulk substrate [24, 25] could combine the advantages of both a tri-gate device (reduced variability in performance and improved scalability) and planar bulk device (low substrate cost and capability for dynamic threshold-voltage control). The design considerations for tri-gate bulk MOSFETs are investigated through 3D numerical simulations [26]. The combination of retrograde channel doping with a multigate structure provides for superior electrostatic integrity, and the requirement of stringent aspect-ratio control is greatly relaxed. The tri-gate bulk MOSFET also provides reduced variability due to suppression of random dopant fluctuations and the flexibility of dynamic threshold-voltage control for further yield improvement and versatility.

The accumulation of the carrier density in the corners of highly doped channels may significantly influence the behavior of long-channel devices leading to "corner effects" [27], which are found to dominate the tri-gate device behavior in the subthreshold regime by 2D and 3D simulations [28]. The parasitic corner conduction could be efficiently suppressed in lightly doped short devices with narrow and high fins, rounded corners, and ultra-thin gate oxides.

The Pi-gate or  $\Omega$ -shape gate devices are intermediate between tri-gate and gate-all-around MOSFETs by extending the sidewalls into the buried oxide. They could offer electrical characteristics like gate-all-around MOSFET but without too much process complication.

Simulations show that Pi-gate gives rise to a virtual back gate which effectively enhances current drive and shields the back of the channel region from electric field lines from the drain [29].

An analytical model is derived to investigate body effects in tri-gate or Pi-gate devices based on the representation of capacitive coupling effects between the front- and back-gate and the channels [30]. The results show that the body factor is much smaller than in regular single-gate SOI devices because of the enhanced coupling between gate and channel, and because the lateral gates shield the device from the electrostatic field from the back gate. The extreme case is the gate-all-around transistor in which the channel is completely isolated from the substrate and thus has no body effects.

The corner effects in Pi-gate MOSFETs are investigated by directly solving the 2-D self-consistent Schrödinger-Poisson equation [31]. The results obtained are quite similar to a tri-gate device showing that low doped channel, thin gate oxide, and rounded corners in an aggressively scaled device are beneficial for suppressing corner effects. The critical point is to reduce the potential variations along the Si-SiO<sub>2</sub> interface, and the transition between fully and partial depletion is not an indicator for the elimination of corner effects.

The  $\Omega$ -shape gate device is superior to SNWFETs in terms of lower manufacturing complexity, and it has been clarified that the difference between the electrical characteristics of the surrounding-gate and the  $\Omega$ -shape gate nanowire MOSFETs with 70% coverage is insignificant [32]. Therefore, choosing the  $\Omega$ -shape gate device as the substitution for SNWFETs will also be an alternative solution [33].

The gate-all-around nanowire channel MOSFETs are classified as the quasi-ballistic transport channel that will be discussed in the next chapter.

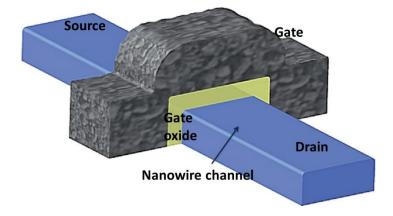

#### 1.2.3 Gate-all-around MOSFETs

As the device channel length scales, the enhanced injection from the source and the reduced scattering of quasi-ballistic transport of carriers is needed for fully-depleted low doped MOSFETs. Some advanced quasi-ballistic channel devices such as silicon nanowire MOSFETs, tunneling transistors and carbon nanotubes, will possibly be utilized in the later stages of the roadmap.

Silicon nanowire gate-all-around MOSFETs which feature a quasi-ballistic transport mechanism are considered to be one of the most promising candidates for the end of the semiconductor roadmap for they have the best gate control, excellent current conduction and suppression of short-channel effects. Many critical technical difficulties, such as the definition of the under gate and the compatibility with traditional CMOS fabrication flow, have been demonstrated in the fabrication of SNWFETs both on SOI and bulk substrate.

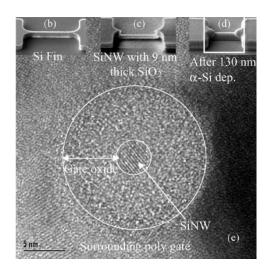

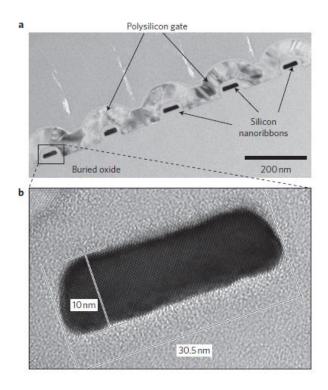

Fabrication of nanowire GAA MOSFET on SOI substrate is easier due to the naturally existing sacrificed buried oxide, and the mainstream of fabricating SNWFETs on SOI substrate is based on the stress limited oxidation mechanism [34]. N. Singh et al. fabricated the silicon nanowire GAA CMOS device and the corresponding inverter with diameter of less than 5nm by traditional top-down CMOS process as shown in Figure 1.7 [35, 36]. The active area region and silicon fin are defined by KrF phase-shift mask lithography and dry etch. 140nm length nanowire is formed during dry oxidation. The gate electrode is defined wider than the nanowire to form low source/drain series resistance and facilitate the definition of the under-gate. The nanowire CMOS device featuring 180 nm long nanowire and 5nm diameter shows high I<sub>on</sub>/I<sub>off</sub> (10<sup>6</sup>). The on-current could be further improved by reducing the channel length and gate dielectric thickness. The excellent short-channel effects demonstrate the superior gate controllability and

thus could relax the urgent requirement of thin gate oxide. There is no sharp corner because of no kink curves in the output characteristics. The substrate bias effects are eliminated due to the shielding effects of poly-silicon to the body.

Figure 1.7: Silicon nanowire GAA MOSFETs fabricated by stress-limited oxidation method on SOI substrate. Reprinted with permission from [35].

A serious problem with SNWFETs on SOI substrate is the enormous source/drain series resistance caused by ultra-thin silicon body. This could be settled by the integration of a Schottky barrier source/drain structure [37]. The silicide/nanowire junction is similar to an ohmic contact in silicon nanowire transistors at high gate bias due to improved source/drain injection. Potential barrier as low as 215 meV for the hole and 665 meV for the electron could be achieved by aluminum inter-diffusion process [38]. A NiSi silicide Schottky barrier source/drain CMOS device has been fabricated using dopant segregation technology. The device shows high  $I_{on}/I_{off}(10^5)$ , near ideal DIBL (10m V/V) and Ss (60 mV/dec). The Schottky barrier nanowire nMOS with erbium silicided source/drain has also been demonstrated utilizing the low barrier between Er and n-type Si [39]. Another possible solution is the optimization of the doping profiles of source/drain extension and silicidation process [40]. The absolute value of the driving current of SNWFETs is always small due to finite conduction area. Therefore, the enhancement

of driving current by strain technology is quite necessary. The integration of high-level uniaxial tensile strain into SNWFETs was achieved on SOI substrate [41]. An average of 2× enhancement in current drive and intrinsic transconductance has been demonstrated for NW widths from 50nm down to 8nm, indicating the promise of this approach for deeply scaled SNWFETs.

Innovative breakthroughs also have been made in recent years on bulk fabrication process due to no self-heating effects or floating-body effects, lower cost, and compatibility with the-state-of-art bulk silicon planar process. A Damascene dummy gate process which features a unique epitaxial SiGe serving as a factitious sacrificial layer on bulk substrate has been proposed by Suk et al. [42, 43], and a method of direct etch silicon to produce the under-gate has been put forward by Tian et al. [44]. Later, Pott et al. proposed a local oxidation method to realize local SOI structure facilitate for producing nanowire on bulk substrate [45].

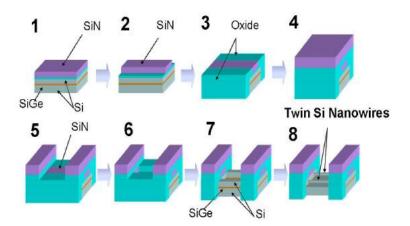

Figure 1.8: Process flow schematic diagram for twin Si nanowire FET(TSNWFET) fabrication using Damascus dummy gate technology and SiGe as the sacrificed layer. Reprinted with permission from [42] .

Figure 1.8 shows a typical process flow schematic diagram for twin Si nanowire FET fabrication using Damascus dummy gate technology. SiGe/Si layers are epitaxially grown followed by SiN hard-mask deposition and trimming. High density plasma (HDP) oxide fills in the trench region to form the STI isolation and another SiN layer is deposited. After Damascene-

gate photo process, the dummy gate layer between photo resist layers and trimmed hard-mask SiN layer is removed. The exposed Si area is trenched by using the oxide dummy layer as a hard mask. Finally, the field oxide is recessed and the subsequent exposed SiGe layer is removed with high selectivity to Si. An optional H<sub>2</sub> annealing is applied to smooth the cross-sectional shape of nanowires.

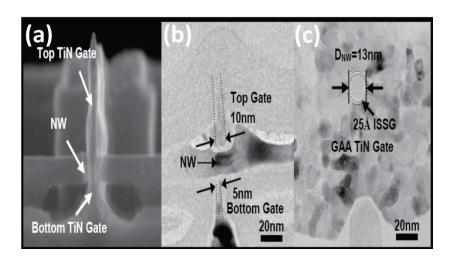

In order to further scale the gate length of SNWFET, a precisely controlled isotropic etching process is utilized to shrink the bottom part of the surrounding TiN gate into the sub-10nm regime, the same as the top part, as shown in Figure 1.9. The fabricated sub-10nm SNWFETs on bulk Si substrate with 13-nm-diameter silicon nanowire channel show on-state currents of  $1494/1054 \,\mu\text{A}/\mu\text{m}$  and off leakage currents of  $102/6.44 \,\text{nA}/\mu\text{m}$  for N/PMOS, respectively [43].

Figure 1.9: VSEM image of SA GAA structure (a), TEM images of 10nm top gate/5nm bottom gate (b) and 13-nm-diameter silicon nanowire as well as 25Å ISSG gate oxide (c). Reprinted with permission from [43].

The V<sub>th</sub> increases with the reduction of nanowire diameter (DNW) due to the surface potential boosting and the quantum-confinement-induced band-gap broadening [46]. The short-channel effects improve with the decrease of DNW because of enhanced electrostatic integrity (EI) of the nanowire channel. The area-normalized current density inversely increases proportionally to

DNW reduction, which shows that the volume inversion becomes more dominant as DNW decreases [47].

Admittedly, S/D parasitic resistance ( $R_{SD}$ ) becomes extremely severe in this structure due to the ultra-thin nanowire S/D extension. The effective channel length ( $L_{eff}$ ) of SNWFET, which is greater than the physical  $L_g$  as the result of the injection point moving out of the gate edge in highly resistive nanowire S/D, causes not only performance degradation but also mobility underestimation. DIBL improves with the reduction of gate oxide thickness ( $T_{ox}$ ) because thinner  $T_{ox}$  can more effectively reduce the fringing field so as to suppress drain field penetration into the channel. The on-current becomes saturated as  $T_{ox}$  is below about 30 Å. Therefore,  $T_{ox}$  remains relatively thick to keep high performance as well as to suppress gate leakage current for the SNWFET.

The main issue of fabricating nanowire GAA MOSFETs on bulk substrate is the formation of the sacrificial layer. Moreover, growing a uniform thin oxide around the nanowire is difficult due to the oxidation rate dependence on crystalline orientation. Very sharp silicon corners with thin grown gate oxides can be a reliability concern because of very high electric fields when the transistor is turned on. Minimizing the parasitic parameters with continuing shrinking of the gate length, and placing more nanowires within a certain width to boost its on-current, are intractable problems.

The industry has demonstrated that the multigate transistor indeed brought significant benefits for transistor scaling. Using multigate structure to scale transistors into the sub-10 nm era is quite promising.

#### 1.2.4 Junctionless mode multigate MOSFETs

Conventional inversion mode transistors have met significant challenges associated with the source/drain (S/D) region, which is one of the key elements for improving SCE immunity and preventing punch-through [48]. Abrupt and ultrashallow junctions are required and the gradient needs to be as high as possible. The S/D parasitic resistance becomes high when the junction depth scales down below 10 nm. The thermal budget required by source/drain dopant activation is also a severe problem when integrated with high-k gate dielectric. Very complicated methods have been developed to achieve ultrashallow junction for S/D formation [49], regardless of the potential of greatly increased sophistication and cost. Therefore, people are considering eliminating the PN junction in transistor operation.

Figure 1.10: Schematic of an n-channel nanowire transistor. Reprinted with permission from [50].

The first principle of the JL MOSFET was proposed in [51] by simulation. Figure 1.10 shows the basic schematic of nanowire multigate JL MOSFETs. The name of the transistor can be simplified as a "gated resistor". When the device is turned on, the entire channel region can be regarded as neutral when considering the simplest situation that  $V_{ds}$  is low and in flat band condition. The transistor is just behaving like a highly doped resistor. The carriers are conducted in the bulk region instead of the surface as compared with the traditional inversion mode junction

based transistors. Admittedly, the mobility is lowered in the highly doped region due to increased dopant scattering. However, when considering scaling the gate length of MOSFETs into the sub-100 nm region, the inversion mobility is comparable to the bulk mobility in the highly doped region.

Figure 1.11: Electron concentration contour plots in an n-type junctionless gated resistor. (a) below  $V_{th}$ , (b), slightly above  $V_{th}$ , (c) higher  $V_g$ , (d) flat band. Reprinted with permission from [50].

Figure 1.11 shows the electron concentration contour plot for an n-type JL MOSFET. It can be clearly observed that the conduction path is located near the center of the nanowire. It significantly reduces the surface scattering compared with the regular transistor. When increasing the gate bias over the flat-band voltage, the channel becomes accumulated such that the on-current would be further increased upon the increase of V<sub>GS</sub>. When reducing the gate bias below the flat band voltage, the channel is partially depleted so that the conducting width (neutral area) becomes narrower. When the gate bias reaches threshold voltage, the neutral channel looks like a string-shape connecting source and drain. When the gate bias is below the

threshold voltage, the device is turned off and the whole channel region becomes fully depleted. The leakage current is mainly due to trap-assisted gate tunneling instead of gate-induced drain leakage effects (GIBL) [52].

There are many unique properties regarding the JL MOSFETs. First, the transconductance degrades much more slowly when gate voltage is increased due to bulk conduction mechanism. Actually, this is good for exploring the devices with high linearity as will be discussed in Chapter 4; second, the degradation of mobility with temperature is much lower than in the inversion mode transistor. This is because the mobility in JL MOSFETs is limited by impurity scattering while mobility in lightly doped inversion mode MOSFETs is limited by photon scattering. The impurity scattering has much less dependence on temperature than photon scattering. Third, the intrinsic delay time for traditional inversion mode transistor is:

$$\tau = \frac{CV}{I} \approx \frac{C_{ox}W_{si}LV_{DD}}{\mu C_{ox}(W_{si}/L)(V_{DD} - V_{th})^2} \approx \frac{L^2}{\mu V_{DD}}$$

(1.1)

while the intrinsic delay for JL MOSFET is

$$\tau = \frac{CV}{I} \approx \frac{C_{ox}W_{si}LV_{DD}}{q\mu N_D(T_{si}W_{si}/L)V_{DD}} \approx \frac{C_{ox}L^2}{q\mu N_DT_{si}}$$

(1.2)

where  $W_{si}$  is the width of the device, L the gate length,  $V_{DD}$  the supply voltage and  $C_{ox}$  the gate oxide capacitance,  $T_{si}$  is the thickness of the silicon and  $N_D$  the doping concentration. As shown in (1.2), we could find that the intrinsic delay decrease as EOT reduces in JL MOSFET. This is a merit indicating that we do not have to aggressively scale EOT to increase switching speed. The JL MOSFET is more immune to short-channel effects because the gate controlled depletion region extends into the SDE which provides a longer effective channel length. Simply increasing the doping concentration can bring about significant performance boost. There is indeed an imperfection in JL MOSFETs. The variability of the threshold voltage is greater than that in the

conventional ultrathin body SOI transistor. This is because the conduction channel is the entire body instead of just the surface. The change of thickness of the body directly reflects the change of conduction current. The surface conduction device has less dependence on channel thickness (body region) variation. However, this problem could be solved by precise epitaxy/etching technology to achieve thin films with variation less than 0.2 nm. It can also be alleviated by adopting some other technology as discussed later.

Figure 1.12: TEM of cross-section of silicon JL FETs. (a) Five parallel devices with a common polysilicon gate electrode. (b) Magnification of a single nanowire. Reprinted with permission from [50].

An example of silicon-on-insulator technology for the fabrication of JL MOSFETs is shown in Figure 1.12. The fabrication starts with commercial SOI wafers, and silicon nanowires are defined by e-beam lithography with thickness of 10 nm and tens of nanometers width. Ion implantation is employed to achieve uniform high doping within the nanowires after gate oxide growth. The high doping is required to ensure a high driving current and low source/drain

resistance. In order to fully deplete the channel during off-state, the geometries need to be extremely small. The gate electrode was formed by LPCVD deposition of amorphous silicon. After gate doping, the samples were annealed in N<sub>2</sub> ambient for 30 mins. The gate was patterned by RIE etching. The SiO<sub>2</sub> protective layer was patterned and Ti/W-Al metallization process was used for contact.

One difference from the inversion mode transistor is that we have to use P+ poly-silicon for NMOS but N+ poly silicon for PMOS in order to obtain appropriate V<sub>th</sub>. The aspect ratio is less than one in this particular case, which is not area efficient. In this way, we developed a new semiconductor etching technology to achieve much higher aspect ratio as will be discussed in Chapter 2.

#### 1.2.5 Comparison between inversion mode and junctionless mode multigate MOSFETs

Table 1.2 summarizes the merits and drawbacks for both inversion mode and junctionless mode MOSFET. Clearly, there are many advantages of Junctionless mode MOSFET over the inversion mode MOSFET. First, it has lower thermal budget because there is no implantation and high temperature annealing in the fabrication process flow of the junctionless MOSFET. The majority carriers are in the center of the channel instead of the surface, where the electric fields are weaker compared with the surface region. Therefore, mobility is less degraded with the increase of surface electric field in the junctionless mode MOSFET. This is the origin of higher linearity in junctionless mode transistors compared with inversion mode transistors which will be discussed in Chapter 4. Since the scattering is photon-determined scattering rather than surface scattering, mobility is less degraded with the increase of temperature in junctionless mode MOSFETs. The delay is dependent on Cox, which relaxes the urgent requirement of increasing

$C_{ox}$  when scaling. The major drawback of the junctionless mode MOSFET is its larger  $V_{th}$  fluctuation due to fin width variation, which is due to the factor that it is a bulk conduction transistor that is sensitive to the fin width.

Table 1.2 Comparison between junctionless mode and inversion mode MOSFET

|                             | Junctionless mode MOSFET | Inversion mode MOSFET |

|-----------------------------|--------------------------|-----------------------|

|                             |                          |                       |

| SCE control                 | Controversial            | Controversial         |

| Cost/Thermal Budget         | Low                      | High                  |

| Mobility vs Electron field  | Less                     | More                  |

| degradation                 |                          |                       |

| Mobility vs Temperature     | Less                     | More                  |

| degradation                 |                          |                       |

| Intrinsic delay             | Dependent on Cox         | Independent on Cox    |

| -                           |                          |                       |

| V <sub>th</sub> fluctuation | More                     | Less                  |

The most controversial debate is whether immunity to SCEs is improved in junctionless mode MOSFET. Collinge et al. [53] claim that SCE are less serious in the junctionless mode transistor because in off-state, the depletion region controlled by the gate fringing fields can be extended laterally to the source/drain extension region. This results in a longer effective channel length in off-state, which effectively blocks the leakage paths. The subthreshold slope as well as gate electrostatic control over the channel is better than in a conventional inversion mode transistor. However, Rios et al. [54] discovered a contradictory conclusion that inversion mode transistor should be better in terms of SCE control. They claimed SCE are worse due to the larger effective EOT in junctionless mode MOSFET since the majority carriers are travelling away from the surface. The gate electrostatic potential control losses are due to the larger EOT. They fabricated short-channel (26 nm) junctionless mode and inversion mode FinFET and compared the DC characteristics, confirming theory. The conclusion from Intel Corporation might sound good, but the junctionless mode MOSFET should have its own market in some

specific areas, such as ultra-high-aspect-ratio FinFET where uniform S/D doping is not easy and high linearity, high temperature stability applications due to its unique operating principle.

# CHAPTER 2 – METAL-ASSISTED CHEMICAL ETCHING FOR III-V MULTIGATE MOSFET FABRICATION

Nanostructure formation is the key process factor for multigate MOSFET fabrication. For transistor applications, nanostructures with smooth interfaces and extremely narrow feature sizes are critical for high performance improvement. Traditional dry etching by reactive ion implantation is a mainstream way to generate nanostructures, but has many shortcomings and is getting harder to scale down. Wet chemical etching usually provides good interface for nanostructures, but it can only deal with large dimensions. A new etching method that combines the merits of dry and wet etching is highly demanded.

## 2.1 Problems with conventional dry etching for fin formation

Shrinking the transistor size horizontally is only one side of the coin. We might be able to obtain higher on-state current per unit area by fully utilizing the bulk substrate conductivity as the channel, that is, exploring performance enhancement in the longitudinal direction instead of horizontal direction. One key point is that we must keep the lateral dimension narrow enough to maintain sufficient gate electrostatic control. Therefore, FinFETs with high-aspect-ratio (AR) fins might be one of the ideal device structures to satisfy the requirements.

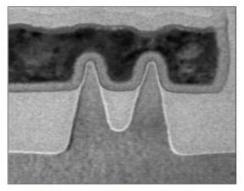

The conventional well-known etching method, neither dry etch nor wet etch, can readily produce high AR fins with ideal vertical sidewall due to the non-ideal anisotropic etching profile. The tapered sidewall is due to the difficulty of making the reaction flow contact the surface and the fact that the reaction product evaporates as etching proceeds deeper. Figure 2.1 shows the cross section of state-of-the-art fins dry etched showing the non-vertical sidewalls. Due to the non-ideal anisotropic profile, there is a large leakage path at the wider bottom side such that the highest aspect ratio of the fins is less than 10:1.

What is worse, the plasma-based reactive ion dry etching causes irreversible damage to the sidewalls when fabricating FinFETs, particularly for III-V channels [55, 56], where such damage is difficult to repair compared to Si-based channels in CMOS technology. Sidewall damage induces a disordered interface between the high-k gate dielectric and semiconductor channel, which impedes the carrier surface mobility and degrades device sub-threshold characteristics [57]. Moreover, sophisticated techniques [58] are required to improve the selectivity over different materials by dry etching. Dry etching needs to be performed in an expensive high vacuum system. For the above reasons, dry etching hinders progress toward aggressively scaled FinFETs. On the other hand, pure wet chemical etching usually does not degrade the crystallographic integrity and has high selectivity, but it is only suitable for large features (>1 µm).

22 nm 1<sup>st</sup> Generation Tri-gate Transistor

14 nm 2<sup>nd</sup> Generation Tri-gate Transistor

Figure 2.1: Cross section TEM images of commercial FinFETs at 22nm and 14 nm by Intel. Reprinted from Intel website http://www.intel.com.

#### 2.2 Principle of metal-assisted chemical etching

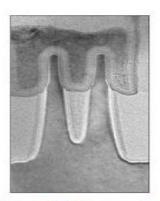

MacEtch was first proposed in [59]. Metal serves as a hard mask as well as a catalyst that initiates the chemical etching by injecting holes to the substrate. There is a Schottky barrier

between metal and substrate which behaves like a barrier for hole injection. Different metals have different barrier heights with a certain material, thus the etching behaves much differently. It is worth noting that there is no etching without metals. Figure 2.2 illustrates the chemical reaction at the metal/substrate interface.

Figure 2.2: Schematic of Au/semiconductor interface for the mechanism of MacEtch. Reprinted with the permission from [60].

MacEtch comprises two steps: a charge transfer process and a mass-transfer process. In the charge transfer process, the metal (Au) catalyst and semiconductor (InP) can be considered as a cathode and anode, respectively. The metal catalyst provides electrons which react with the oxidant  $H_2O_2$  at the cathode as:

$$H_2O_2 + 2H^+ \rightarrow 2H_2O + 2h^+$$

The appropriate work function of metal is the key to achieve the charge transfer process.

Holes are generated in this step and further react with InP and H<sub>2</sub>O at the anode (InP): [61]

(i)

$$InP + 4H_2O + 8h^+ \rightarrow InPO_4 + 8H^+$$

, or

(ii)  $InP + 0.55H_2O + 8h^+ \rightarrow 0.5In_2O_3 + H_3PO_4 + 8H^+$

In the mass-transfer process, the generated In- and InP based oxides are dissolved in H<sub>2</sub>SO<sub>4</sub>.

There is a significant difference between the inverse MacEtch presented here and the traditional MacEtch. In our structure, there is thick P-rich oxide layer right beneath the metal catalyst which prevents further oxidation. Au catalyst is responsible for the formation of an interfacial, P-based oxide layer that cannot be dissolved in H<sub>2</sub>SO<sub>4</sub> during MacEtch. Therefore, the following etching preceded by the hole diffusion into the InP substrate. The thin In-rich oxide layer along the sidewalls can be dissolved by H<sub>2</sub>SO<sub>4</sub>, and MacEtch is proceeding.

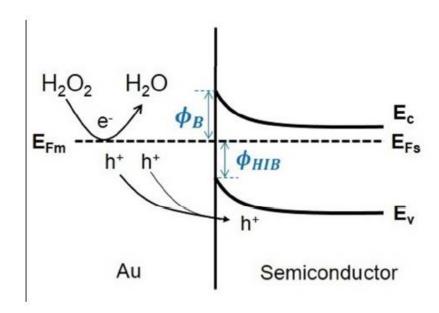

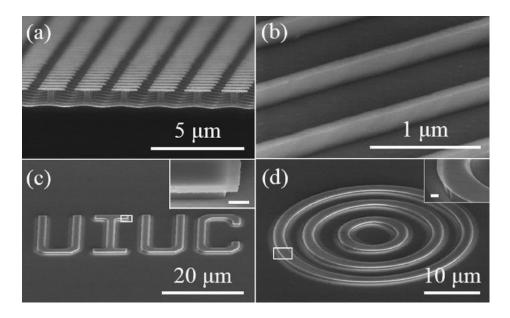

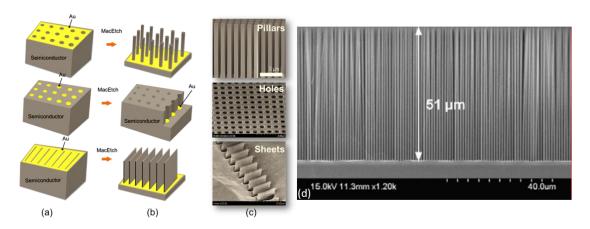

From the crystallographic dependence study, we found the Au patterns oriented at 45° relative to the primary <110> flat on (100) surface, which is good to form perfectly anisotropic etching profile. This is because the facets with the low index {010} planes instead of high-index planes are most exposed to the etching solutions. The concentrations of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> were optimized to obtain the best controllable etch rate and vertical etching profiles. The top P-rich oxide layer collapsed onto the sidewall after MacEtch and was removed by dilute HF solution. Figure 2.3 shows the InP nanostructures with different patterns. The structures include highly ordered arrays of nanopillars from ~1.1 µm<sup>2</sup> Pt square pads (Figure 2.3(a); note that the InP pillars are directly beneath the Pt pads), arrays of nanoscale fins after Au removal (Figure 2.3(b)), microscale mesas forming the letters UIUC (Figure 2.3(c); inset shows a highmagnification view of squared area from the letter 'I' where the InP block sits directly beneath the Au pad), and circular InP microstructures from concentric Au rings (Figure 2.3(d)). These images demonstrate that the i-MacEtch process can be implemented to fabricate threedimensional (3D) InP micro and nanostructures from various metal patterns, whether the pattern is linear, circular, discrete, or continuous. The comparison of two noble metals widely used for MacEtch, Pt and Au, is studied first. The Pt and Au layers were patterned by SL on the InP

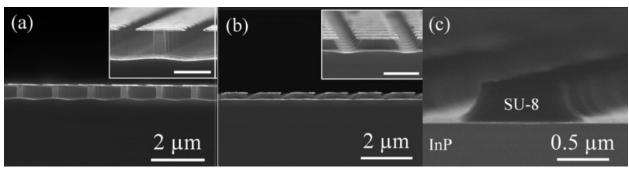

substrates in Figure 2.4(a) and 2.4(b), respectively. The Pt serves as a strong catalyst to assist chemical etching which is highly anisotropic with vertical sidewalls. Au has a higher barrier with InP such that fewer holes are generated, thus it is more dominated by chemical etching. Therefore, vertical sidewall is only obtained for a certain orientation (45° relative to the primary <110> flat) where etching is fastest in the lowest atomicdensity plan. We also have a control etching shown in Figure 2.4(c) that uses a photoresist SU8 as hard mask. There is no etching at all using the same etching solution as the ones with metal catalyst, which verifies that metals do serve as important catalysts to initiate the etching and direct the etching behaviors.

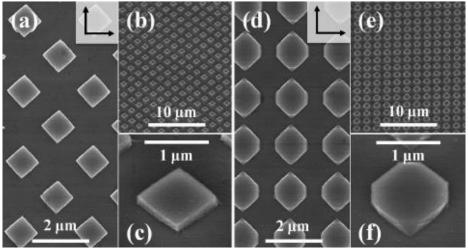

Figure 2.5 shows SEM images (after Au removal) obtained at plan-view (a,d), low-magnification 45° tilted-view (b,e) and high-magnification 45° tilted-view (c,f) of InP nanostructures formed by i-MacEtch using the two distinct pattern orientations indicated. Note that the pattern orientations shown in Figure 2.4 are the same as in Figure 2.5(d). It can be seen that vertical sidewalls on all four sides are achieved (Figure 2.4(c)), where the Au patterns are oriented at 45° relative to the wafer flat edge, so that the low-index {010} planes are the facets most exposed to the etching solutions. Conversely, when the Au patterns are oriented at 90° relative to the primary (110) flat edge (Figure 2.5f), in addition to the perpendicular {010} planes, as in the case of purely masked wet etching [62], sloped facets that are presumably the slow etch (211)A facets are also produced. Thus, only the 45° orientation of the metal patterns is suitable for the formation of perfectly vertical nanostructures having (100) sidewall facets, while a 90° oriented metal pattern leads to the formation of features having multifaceted geometries with high-index sidewall facets. Asoh et al. also noted crystal orientation-dependent anisotropic etching in their study of Pt-assisted InP etching [63].

Figure 2.3: InP nanostructures generated from i-MacEtch: (a) arrays of nanopillars generated from Pt square pads, (b) arrays of nanoscale fins from Au lines after Au removal, (c) the letters "UIUC" from Au pads with inset showing a high-magnification view of the outlined region (white box) corresponding to the letter "I", and (d) concentric InP microstructures generated from a set of Au rings, with inset showing the high-magnification view of the outlined region. The inset scale bars are 500 nm and metal catalyst layers were patterned by SL (a) and EBL (b–d). Reprinted with permission from [60].

Figure 2.4: Cross-sectional SEM images of InP pillar arrays formed by i-MacEtch with metal catalyst patterns (sitting on top) made of (a) 30 nm thick Pt and (b) 30 nm thick Au disks. (c) i-MacEtch control experiment: SEM shows no etching with SU-8 as a mask. Inset scale bars represent 1 µm. Reprinted with permission from [60].

Figure 2.5: SEM images of InP nanostructures etched for 10 min with  $\gamma$  = 24.5 at room temperature, where the square Au catalyst patterns (removed before SEM) were aligned at (a–c) 45° and (d–f) 90° relative to the (110) wafer flat edge (the two arrows in the top-view images indicate equivalent  $\langle 110 \rangle$  directions). (a,d) panels show plan-view images, while (b,c,e,f) were obtained at a 45° tilted angle. Reprinted with permission from [60].

# 2.3 Fabrication of high-aspect-ratio InP FinFET by MacEtch

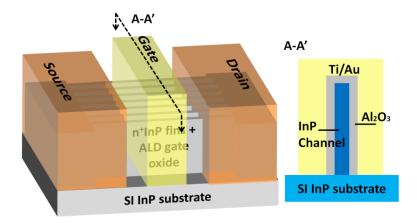

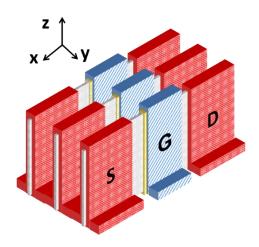

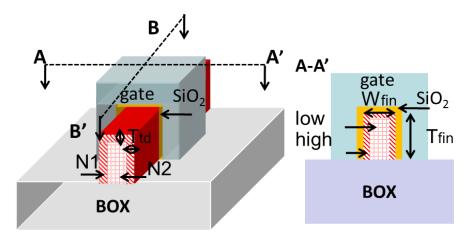

Figure 2.6: Schematic representation of the final device structure. The cross-sectional view of the InP JL-MOSFET is shown along the A-A' plane in the right-hand-side panel. Reprinted with reference [64].

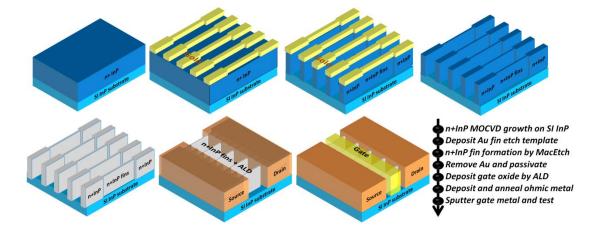

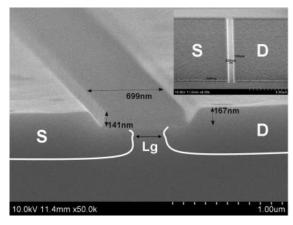

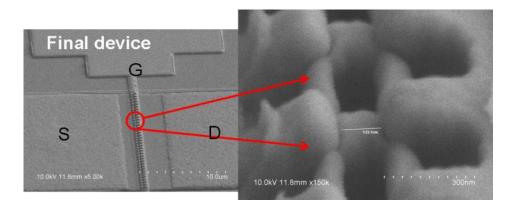

Figure 2.6 shows a schematic representation of the fabricated InP multigate JL-MOSFET structure. Figure 2.7 depicts the key fabrication steps. The InP FinFET channels were first defined by e-beam patterning on a 600 nm thick MOCVD grown Si-doped ( $8 \times 10^{17}$  cm<sup>-3</sup>) InP epitaxial layer on a semi-insulating InP substrate. After native oxide removal by diluted HF, the

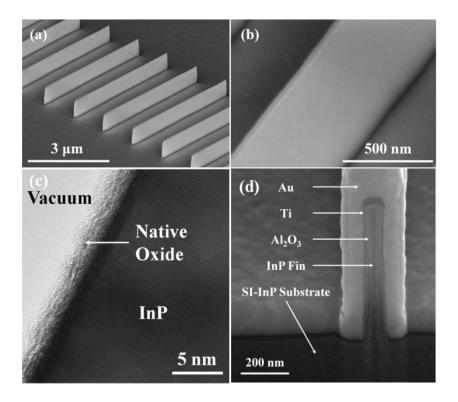

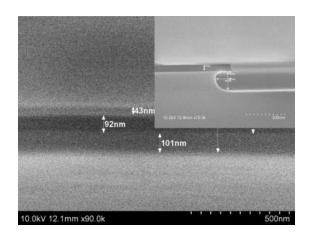

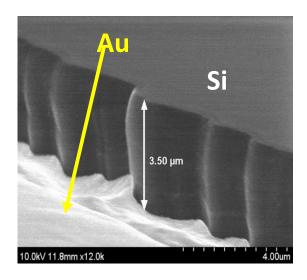

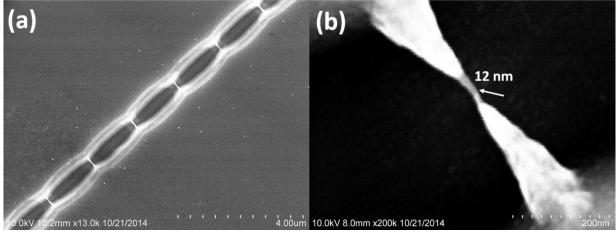

samples were loaded for Au evaporation (30 nm). This was followed by the newly developed inverse MacEtch (i-MacEtch) process, where Au serves as a catalyst to induce local electrochemical etching in a solution of H<sub>2</sub>O<sub>2</sub> and H<sub>2</sub>SO<sub>4</sub> at room temperature. After the desired aspect ratio was reached, Au was removed in commercially available Au etchant. Figure 2.8 (a)-(b) shows an array of InP fins that are ~20 nm wide and ~700 nm tall. Unique to i-MacEtch, the sidewall etching profile is remarkably smooth, independent of metal pattern edge roughness, and free of ion-induced damage. Figure 2.8 (c) shows a bright-field TEM image of the fin sidewall, which confirms its atomically smooth surface.

Figure 2.7: Schematic diagram and corresponding description of the process flow for the fabrication of an InP JL-MOSFET by i-MacEtch. The maximum annealing temperature is maintained below 500 °C throughout the whole process. Reprinted with permission from [65].

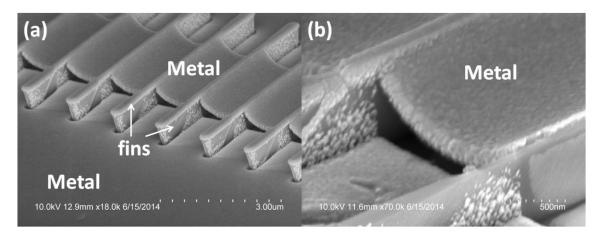

To fully isolate the fin channels, 700 nm tall fins were formed by intentionally overetching the 600 nm thick doped epi-layer. The samples were dipped into diluted HF 10:1 for 40s to remove the collapsed oxide generated by MacEtch. Then the samples were immersed into diluted 1:1 (NH<sub>4</sub>)<sub>2</sub>S: DI H<sub>2</sub>O for 10 min for surface passivation. Al<sub>2</sub>O<sub>3</sub> (~10 nm) was immediately deposited by ALD as the gate dielectric, followed by a 30 s RTA at 500 °C. In order to fully wrap the metal contacts over the high AR InP fins, tilted sputtering of Ge/Au/Ni/Au was employed for source/drain (S/D) pads and Ti/Au (10 nm/100 nm) for the gate metal. S/D

contacts were annealed by RTA in  $N_2$  at 400 °C for 30 s. Figure 2.8 (d) shows the cross-section of a single fin conformably covered by the gate stack. Fins with widths as narrow as 15 nm and AR > 50:1 were achieved. Figure 2.9 (a) and (b) show the top and tilted view of the fabricated device.

Figure 2.8: 60° tilted-view SEM images of (a) an array of InP fin nanostructures fabricated by i-MacEtch and (b) high-magnification view of the central region of a single fin. (c) HR-TEM image showing the sidewall of a single InP after i-MacEtch; (d) 52° tilted-view SEM image showing the cross-section at the center of a single metal-coated 14 nm wide InP fin with aspect ratio ~50:1. Reprinted with permission from [65].

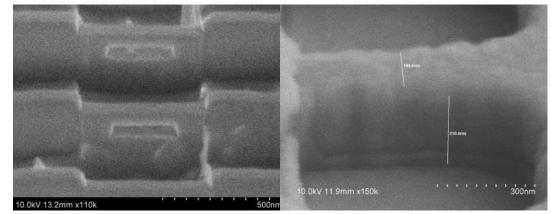

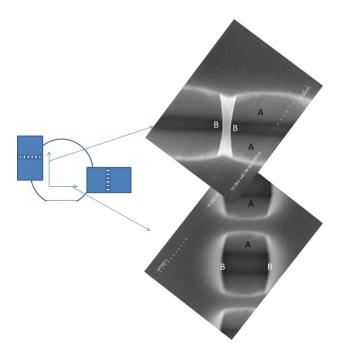

Note that the on-state performance, including transconductance  $g_m$  and drive current  $I_{on}$ , is reasonable for a long channel device with un-optimized parasitics (similar to a long channel Si junctionless transistor in [50]). We would also like to point out that the unprecedently high-aspect-ratio (50:1) fins used in this work for device farbication greatly raised the difficulty in processing. We indeed attempted to scale down the channel length. However, due to the extremely tall fins, the topological uneveness was so huge that it was difficult to do sub-100 nm

feature patterning in a university lab. We first spun thin e-beam resist PMMA (200 nm) on top of the fins for source/drain patterning. Disconituity of PMMA coverage of the fin sidewalls could easily occur due to the poor conformality of spin coating for these deep trenches. Therefore, after S/D metal sputtering and lift-off, metals could still be connected as shown in Figure 2.10 because there was no PMMA coating along the fin sidewall between source and drain where it should have been. For this reason, we had to significantly increase the thickness of PMMA to ~600 nm and raise the corresbonding dose and energy during e-beam lithography. The minimal feature size that can be written has been greatly increased due to the imposed extreme lithography condition. It is almost impossible to pattern sub-100 nm features using a 600 nm thick resist.

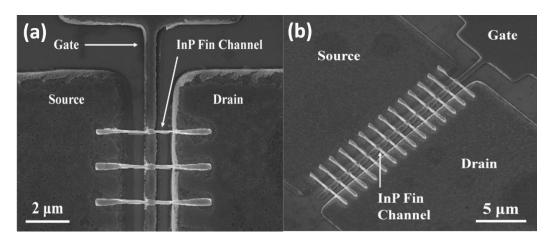

Figure 2.9: (a) Top-view and (b) tilted view SEM image showing the final JL-MOSFET structure. As shown, the gate is centrally aligned between the source and drain.

We do expect much better performance as long as a shorter channel length device can be fabricated by developing advaced 3D process technology, such as resist reflow [66], disperse coating [67], spray and electrodeposition [68], or directed self-assembly nanolithography [69]. The optimization could be achieved by many other ways, like lithography innovation (may be incorporated with CMP and other plannarize methods) and/or S/D regrowth to minimize the offset resistance. Those technology optimizations need to be explored extensively, but they are beyond the scope of this work. We emphasze that we have fabricated a FinFET with 50:1 aspect

ratio here, which definitely imposes a great barrier in 3D processing. On the other hand, FinFETs may not require such a high-aspect-ratio in the near future. Lower aspect ratio (e.g. 10 - 20 to 1) FinFETs, which can be controllably produced by our etching method, may not pose severe processing difficulty. We chose an ultra-high-aspect-ratio (50:1) structure in this work so that the ultimate potential of this method can be demonstrated. We sincerely hope that the significance of this demonstration still holds despite the processing challenge and resulting performance compromise.

Figure 2.10: Failure example showing metal lift-off above the tall fins patterned using a 200 nm thin e-beam resist. (a) SEM image after source/drain metal desposition and lift off using a thin PMMA layer (200 nm), when the original fin height is 700 nm, (b) zoomed view of the non-removed metals on top of gate region due to poor conformal PMMA coverage on the tall fin sidewalls.

#### 2.4 Device characterization and discussion

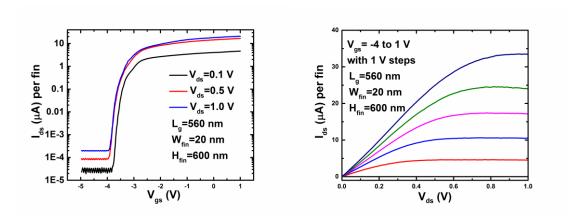

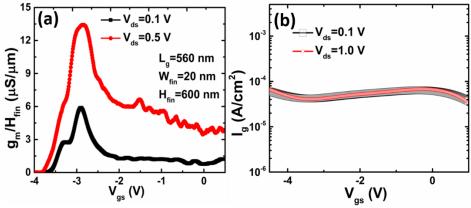

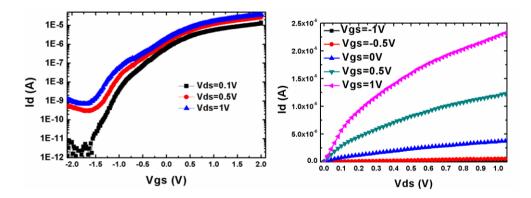

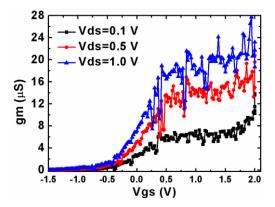

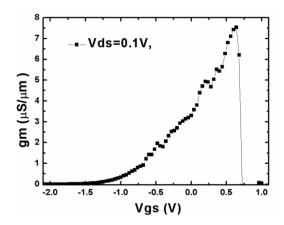

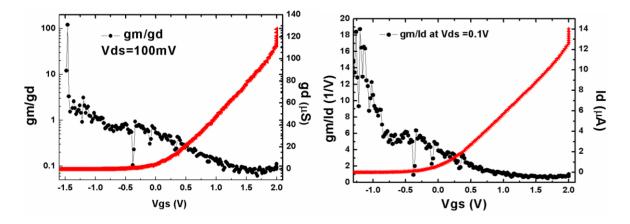

To reveal the superiority of MacEtch for device application, we have done the device characterization on Agilent4200. Figure 2.11 shows the electrical performance of a device with an array of 14 fins with gate length  $L_g = 560$  nm, fin width  $W_{fin} = 20(32)$  nm, and height  $H_{fin} = 600$  nm. The sub-threshold slope (SS) extracted from the transfer curves (Figure 2.11 (a), (b)) is  $\sim 70/80$  mV/dec, respectively. The device is sharply turning on/off, which is due to the enhanced gate electrostatic control over the extremely narrow fins with low interface states density [70]

fabricated by MacEtch. The on/off ratio reaches as high as  $5 \times 10^5$ , which is comparable with the state-of-the-art techniques [71]. There was no hysteresis when sweeping  $V_{gs}$  in opposite directions. These are direct indications of high interface quality with minimum mobile charges or traps between the etched fin surface and high-k dielectric. The high negative  $V_{th}$  is attributed to the low gate work function and fixed oxide charges, which was extracted by TCAD simulation to be on the order of  $7 \times 10^{12}$  cm<sup>-2</sup>. The drive current reaches  $52(160) \,\mu\text{A}/\mu\text{m}$  at  $V_{ds} = 1 \,\text{V}$  for the  $W_{fin} = 20/32 \,\text{nm}$  devices, respectively.

Figure 2.11: (a)  $I_{ds}$ - $V_{gs}$  semi-log curves and (b)  $I_{ds}$ - $V_{ds}$  curves of representative devices with  $W_{fin}$  = 20 nm, showing abrupt turn on in the subthreshold region. Reprinted with permission from [65].

Figure 2.12: (a) normalized  $g_m$ - $V_{gs}$  curves and (b)  $I_{gate}$ - $V_{gs}$  curves of representative devices with  $W_{fin} = 20$  nm.

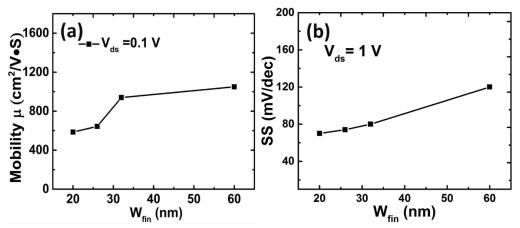

Note that the current is normalized by the fin height (not width). If we increase the aspect ratio of fins further, the current conducted by each fin will increase accordingly. The aspect ratio cannot be infinitely increased since it introduces difficulty in 3D nano-patterning process. The plots of the two terminal I-V curves prior to the gate metal deposition show total resistance of 0.8  $k\Omega$  and 2.8  $k\Omega$  respectively. We intentionally widen the S/D terminals by forming a dumbbellshaped metal catalyst pattern (Figure 2.9) to reduce the contact resistance. However, the contact separation is still large (2  $\mu m).$  Figure 2.12(a) shows the normalized transconductance  $g_m$  vs.  $V_{gs}.$ The relatively small g<sub>m</sub> is due to the large parasitic source/drain resistance. One of the key concerns is to reduce the source/drain contact distance to further improve the transistor performance by reducing the parasitic resistance. Much higher I<sub>on</sub> can be expected if the S/D region is optimized, either by employing advanced patterning methods to shrink the contact distance, epitaxial regrowth in S/D extension area, and/or increasing the channel doping concentration. Figure 2.12(b) shows the normalized gate leakage current at  $V_{\text{ds}} = 0.1$  and 1 V, which is extremely low (4e10<sup>-5</sup> A/cm<sup>2</sup>), results from good isolation of the gate from S/D. Therefore, the gate leakage is not contributing to the device leakage I<sub>off</sub> in this case. Since I<sub>off</sub> for devices with different W<sub>fin</sub> are nearly identical, the major device leakage conduction should come from the substrate instead of the device channels, as measured from the substrate. The gate stack can effectively turn off the narrow fin channel so that almost no leakage current flows through the fins. Substrate engineering is the only way to further reduce the on-current [72]. V<sub>th</sub> and the I<sub>on</sub>/I<sub>off</sub> ratio change gradually with W<sub>fin</sub>. Smaller W<sub>fin</sub> (below 30 nm) is beneficial for reducing V<sub>th</sub> while maintaining relatively large I<sub>on</sub>/I<sub>off</sub> ratio. Figure 2.13 (b) plots SS as a function of W<sub>fin</sub>. Due to the strong gate electrostatic control enabled by the high AR structure, even the widest fin width ( $W_{\text{fin}} = 60 \text{ nm}$ ) device shows a low SS (120 mV/dec) and DIBL (110 mV/V).

The extracted low field effective electron mobility approaches the bulk value as  $W_{fin}$  increases (Figure 2.13 (a)).

Figure 2.13 (a) The extracted low-field electron mobility  $\mu$  vs.  $W_{fin}$ . (b) Subthreshold slop Ss vs.  $W_{fin}$  for InP FinFETs with L<sub>g</sub>=560 nm, EOT= 3.9 nm and active fin height  $H_{fin}$  = 600 nm. Reprinted with permission from [65].

Although it is not easy to do an absolutely fair performance benchmarking since the on-state performance can be easily traded with other device metrics, such as much larger parasitic capacitance and/or worse off-state performance (Ss, I<sub>off</sub> etc.), we provide Table 2.1 for comparison of different FinFET structures including stacked nanowires for the same purpose of high current per unit surface area. Channel length L<sub>c</sub> is defined as the distance between metallurgical junction of S/D and channel in inversion mode transistor, while L<sub>c</sub> simply represents the S/D contact distance in a junctionless transistor. From Table 2.1, we can conclude that the absolute value of I<sub>on</sub> that a single fin can conduct in a low-aspect-ratio FinFET remains low [50], even if the channel length is aggressively scaled [73]. The stacked channel device either suffers from severe parasitic problem that leads to a low I<sub>on</sub> [74], or non-uniformity issue due to 3D process challenge that results in unacceptable leakage and Ss [75]. Our prototype ultra-high-aspect-ratio FinFET demonstrated here shows reasonably high current per fin due to the increased conducting volume and low off-state leakage. It does not suffer non-uniformity due

to the excellent etching control. Therefore, our method represents a big step towards super-high current density electronics.

Table 2.1: Comparison of figures of merit of different technologies

| Ref  | $L_{g}$ | Lc     | EOT    | $V_{DD}$ | Ion per   | Perimeter | I <sub>off</sub> per | Ss     | Type    |

|------|---------|--------|--------|----------|-----------|-----------|----------------------|--------|---------|

|      |         |        |        |          | fin/stack | per stack | fin/stack            |        |         |

| [50] | 1 μm    | N/A    | 10 nm  | 1 V      | 0.25 μΑ   | 70 nm     | 2 pA                 | 63     | FinFET  |

|      |         |        |        |          |           |           |                      | mV/dec |         |

| [74] | 250 nm  | N/A    | 4.3 nm | 1 V      | 20 μΑ     | 113 nm    | 1 pA                 | 62     | Stacked |

|      |         |        |        |          |           |           |                      | mV/dec | channel |

| [73] | 14 nm   | N/A    | N/A    | 0.8 V    | 33.7 μΑ   | 100 nm    | 4.2 nA               | 67     | FinFET  |

|      |         |        |        |          |           |           |                      | mV/dec |         |

| [75] | 1 μm    | 200 nm | 4.5 nm | 1 V      | 480 μΑ    | 480 nm    | N/A                  | 94     | Stacked |

|      |         |        |        |          |           |           |                      | mV/dec | channel |

| This | 560 nm  | 1.8 μm | 4.3 nm | 1 V      | 7.2 μΑ    | 1200 nm   | 0.1 nA               | 63     | FinFET  |

| work |         |        |        |          |           |           |                      | mV/dec |         |

A novel technique, i-MacEtch, has been developed for sculpting III-V materials with highly anisotropic, high-aspect-ratio profiles to replace the traditional dry etching method in the semiconductor device fabrication process. We implement it into the fabrication of InP JL-FETs with ultra-high ARs, without the need for dry etching, ion implantation, or high temperature annealing, which is the revolution to redefine the traditional FinFET fabrication. These are all crucial to maintain the quality of high-k/III-V material surfaces and interfaces. The fabricated devices with narrow fin widths exhibit excellent on-state performance and near-ideal SS. Because of the simplicity, scalability, and high compatibility, we believe the III-V i-MacEtch can be incorporated into III-V transistor fabrication for future III-V based circuit manufacturing.

#### 2.5 Theoretical investigation of the scaling behavior of high AR on JL FinFETs

The recently reported JL FinFETs showed very low on-state current ( $\sim 0.03 \,\mu A$  per fin at 1 V overdrive) [50], presumably due to the fairly low AR ( $< 1/3 \, \text{with W}_{fin} = 30 \, \text{nm}$  and  $H_{fin} = \sim 10 \, \text{nm}$ ) in addition to the low electron mobility of silicon. In comparison, the on-state current

measured from the high AR (> 30 for the active fin) InP FinFET is much higher, and it can be further increased if we continue to increase the fin AR by further etching. Preliminary simulation studies were carried out by TCAD simulation to investigate the ultimate scaling behavior and design rules for this type of high AR FinFETs using experimental, carefully calibrated TCAD model parameters.

#### 2.5.1 Device operating principle and optimization process

$$I_{on,flatband} = q\mu N \frac{H_{fin}W_{fin}}{L_c}V_{dd}$$

(2.1)

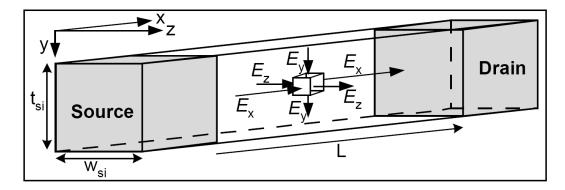

At flat-band condition, the drain current of JL FinFETs can be expressed as (2.1), where  $\mu$  is the mobility, N is the carrier concentration,  $L_c$  is the channel length,  $V_{DD}$  is the supply voltage,  $W_{fin}$  is the fin width and  $H_{fin}$  is the fin height.  $I_{on, flat \, band}$  can be simply increased by increasing N,  $W_{fin}$  or  $H_{fin}$  and reducing  $L_c$ . However, due to the limited bias swing of power supply,  $I_{on}$  usually cannot reach the flat band condition even at the highest bias  $V_{dd}$ .  $I_{on}$  can be simply denoted as:

$$I_{on} = \alpha (N, W_{fin}, C_{ox}) \times I_{on, flat band}$$

(2.2)

where  $\alpha$  (N, W<sub>fin</sub>, C<sub>ox</sub>) is the function of N, W<sub>fin</sub> and C<sub>ox</sub> for a specific technology node with known L<sub>c</sub> and V<sub>dd</sub>. It is expected that  $0 < \alpha < 1$  in a low power supply system. Larger C<sub>ox</sub>, smaller N and smaller W<sub>fin</sub> would increase  $\alpha$  because of the suppressed SCE. Therefore, both increased available conduction carriers and suppressed SCE are indispensable to maximizing the on-state current.

Traditional channel length  $L_c$  scaling requires increasing doping concentration and reducing  $W_{fin}$ , which is quite difficult to scale technically. Incredibly high N helps deliver more current. However,  $W_{fin}$  has to be aggressively scaled correspondingly ( $W_{fin}$ <5 nm when N is greater than  $1\times10^{20}$  cm<sup>-3</sup> [76]) for maintaining good electrostatic control. Such extreme values are impractical

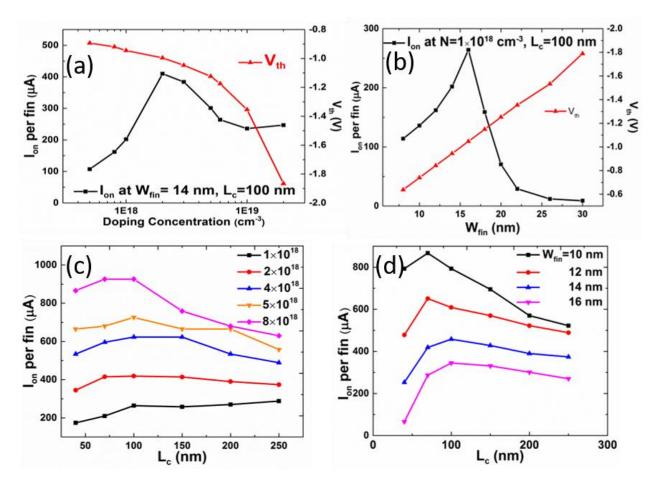

to achieve in experimental processing. There is unacceptable performance fluctuation among different devices. Therefore, channel doping concentration N and fin width  $W_{\rm fin}$  have to be considered comprehensively in order to get the highest performance at a particular channel length  $L_c$ . As shown in Figure 2.14 (a), at a fixed  $L_c$ =100 nm and N=1×10<sup>18</sup> cm<sup>-3</sup>, the maximum  $I_{\rm on}$  first increases with the increase of  $W_{\rm fin}$  because of the increased conduction area. After reaching a maximum point, the  $I_{\rm on}$  reduces due to the worse Ss results from a weaker gate electrostatic control. As shown in Figure 2.14 (b), for a fixed N (i.e.  $W_{\rm DM}$ ) and  $L_c$ , there is also an optimal  $W_{\rm fin}$  for the highest  $I_{\rm on}$ .  $I_{\rm on}$  increases with the reduction of  $W_{\rm fin}$  because of stronger electrostatic control. After reaching a maximum point, it reduces with further reduction of  $W_{\rm fin}$  because of the reduced current conduction volume where gate electrostatic control is already strong enough to yield a low Ss.

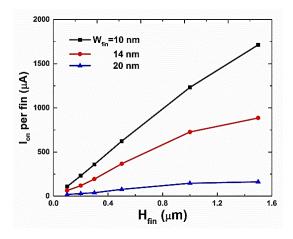

We plot the maximum  $I_{on}$  for each technology node for three different doping concentration levels as shown in Figure 2.14 (c). All devices simulated here have the same total area (500 nm × 500 nm), which means a shorter  $L_c$  has a larger S/D thus lower S/D resistance. Increasing N can improve  $I_{on}$  as expected for all  $L_c$ . Interestingly, for a fixed doping level,  $I_{on}$  has a non-monotonic relationship with  $L_c$ .  $I_{on}$  first increases with the reducing of  $L_c$  due to reduced S/D distance. After reaching a peak point, it decreases with further reducing  $L_c$  because of severe short-channel effects. The transition points move lower as N increases. When N is higher than 8e18 cm<sup>-3</sup>, the optimal  $W_{fin}$  requires below 10 nm which can be considered infeasible experimentally. Correspondently, we also plot the scaling behavior of  $L_c$  vs.  $I_{on}$  for three different  $W_{fin}$  as shown in Figure 2.14 (d). A similar phenomenon is observed that  $I_{on}$  first increases with the reduction of  $I_c$ . However, the slope of  $I_{on}$ - $I_c$  is small because higher N is chosen for longer  $I_c$  devices, which counteracts the effects of larger S/D resistance due to smaller S/D area. After reaching a

maximum point,  $I_{on}$  reduces due to more severe short-channel effects. Unlike ultra-thin body layer or low AR fins, the maximum allowable  $W_{fin}$  doubles theoretically in the high AR double-gate FinFETs, thus doubling the available conduction carriers per fin.

Figure 2.14: Simulated device performance. (a)  $I_{on}$  vs. doping concentration (N) for  $L_c=100$  nm,  $H_{fin}=700$  nm,  $W_{fin}=14$  nm; (b)  $I_{on}$  vs.  $W_{fin}$  for  $L_g=100$  nm,  $H_{fin}=700$  nm and  $N=1\times10^{18}$  cm<sup>-3</sup>; (c) the maximum  $I_{on}$  vs.  $L_g$  for different channel N from  $1\times10^{18}$  to  $8\times10^{18}$  cm<sup>-3</sup> and  $H_{fin}=700$  nm; (d) the maximum  $I_{on}$  vs.  $L_g$  for different fin width  $W_{fin}$  from 10 to 18 nm and  $H_{fin}=700$  nm;  $I_{on}$  were extracted at  $V_{gs}=V_{off, \, state}+V_{dd}$ ,  $V_{ds}=V_{dd}=0.8$  V, and  $V_{off, \, state}=V_{gs}$  at  $I_{ds}=100$  nA. EOT =1 nm for all simulated devices.

#### 2.5.2 Projections for the ultimate scaling performance

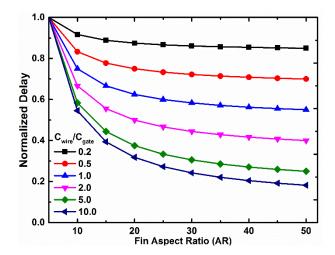

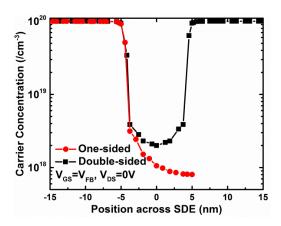

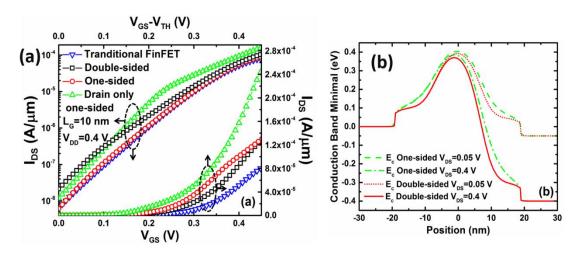

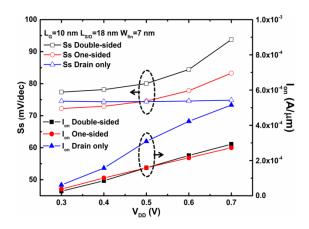

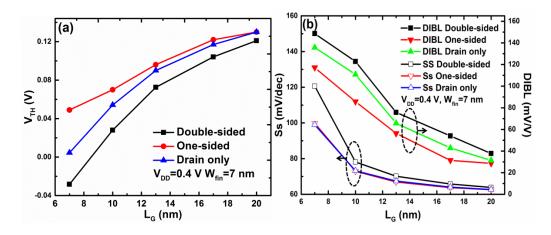

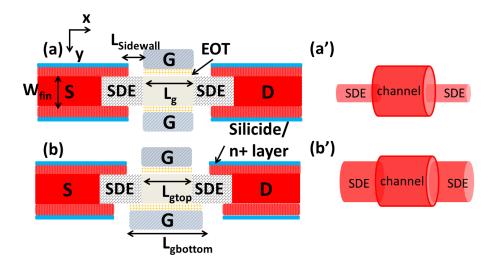

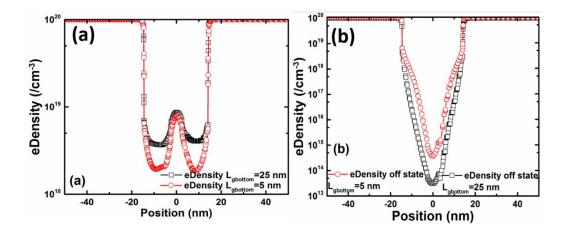

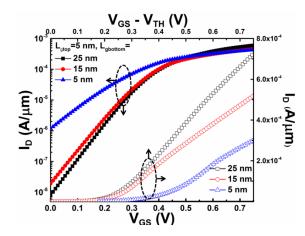

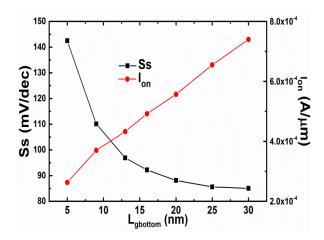

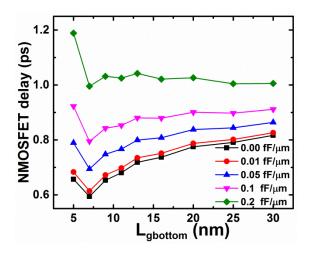

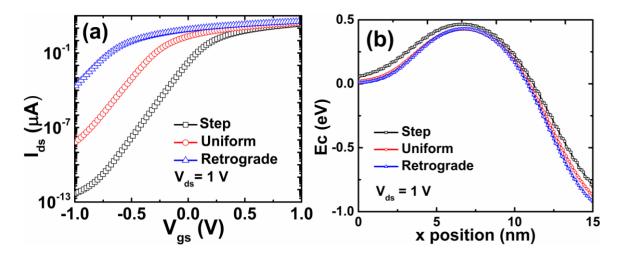

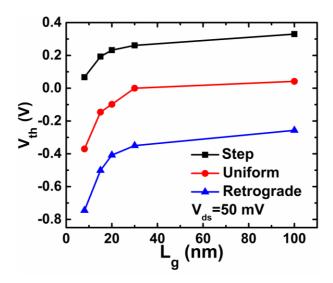

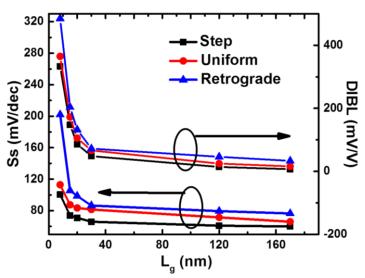

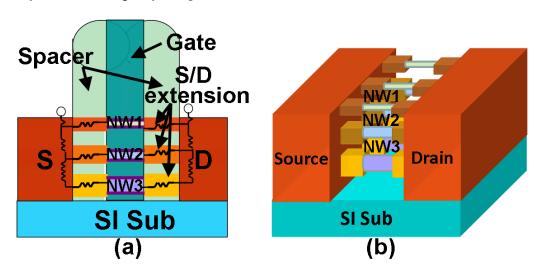

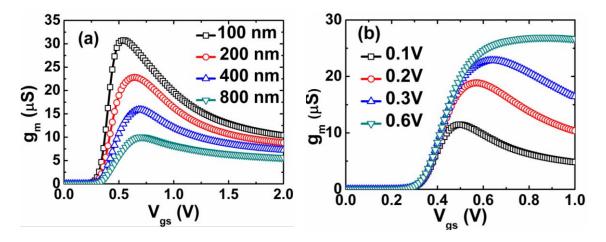

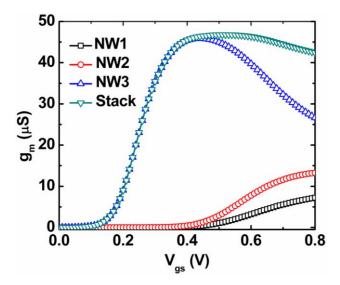

Figure 2.15: Modeled  $I_{on}$  vs.  $H_{fin}$  for a fixed  $L_c$ =100 nm,  $W_{fin}$  =10, 14 and 20 nm, EOT =1 nm and N is optimized for each  $W_{fin}$  and  $L_c$ ;  $I_{on}$  were extracted at  $V_{gs}$ = $V_{off, state}$ + $V_{dd}$ ,  $V_{ds}$ = $V_{dd}$ =0.8V, and  $V_{off, state}$ = $V_{gs}$  at  $I_{ds}$ =100 nA. All simulated devices have identical total area (500 nm  $\times$  500 nm).