© 2016 Bilal Gabula

#### MODULARIZING THE LDO TO OPTIMIZE PERFORMANCE BASED ON APPLICATION DESIGN CONSTRAINTS

BY

BILAL GABULA

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2016

Urbana, Illinois

Adviser:

Associate Professor Pavan Kumar Hanumolu

# ABSTRACT

This thesis aims to construct a modular low-dropout regulator that gives designers more freedom in building a highly efficient regulator that meets application demands. This modular design is able to separate DC regulation and high-frequency supply rejection while not compromising on either of the two. Flexibility is a key requirement during both design and post-design. The proposed regulator is able to achieve all the required goals with full spectrum power supply rejection. By splitting the pass device, this design is able to achieve the best of both internal pole dominant and external pole dominant linear regulators. To my parents, for their love and support.

# ACKNOWLEDGMENTS

I would like to thank my advisor, Dr. Pavan Kumar Hanumolu, for believing in me even when I didn't believe in myself and for pushing me to keep going. I am truly grateful for the opportunity to work with him. I also want to thank Mrunmay and Timir for helping me get started on this project. I would like to thank my Mom, Dad, Sana, Arham, Ivan, Rafat Masi, Mark, Istvan and Torin for always being there and supporting me through thick and thin. I would like to thank my friends, Achal, Asad, Estefany, Gerard, Kadur, Mahika, Nikhil, Reddy, Sid, Taj, Vinay, Vishwa and Vrishin, who have helped me blow off steam while pushing me to stay motivated the last few years. I would also like to acknowledge the contribution of the ECE department at UIUC. My undergraduate and graduate experience was largely defined by the courses and structure the department provides so effectively.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LIST OF ABBREVIATIONS                                                                                                                                                                                                                                                                                              |  |  |  |

| CHAPTER 1 INTRODUCTION 1                                                                                                                                                                                                                                                                                           |  |  |  |

| 1.1 Shunt Regulator                                                                                                                                                                                                                                                                                                |  |  |  |

| 1.2 Series Regulator                                                                                                                                                                                                                                                                                               |  |  |  |

| CHAPTER 2 LDO TERMINOLOGY                                                                                                                                                                                                                                                                                          |  |  |  |

| 2.1 Dropout Voltage                                                                                                                                                                                                                                                                                                |  |  |  |

| 2.2 Quiescent Current                                                                                                                                                                                                                                                                                              |  |  |  |

| 2.3 Line and Load Regulation                                                                                                                                                                                                                                                                                       |  |  |  |

| 2.4 Efficiency                                                                                                                                                                                                                                                                                                     |  |  |  |

| 2.5 Supply Rejection                                                                                                                                                                                                                                                                                               |  |  |  |

| CHAPTER 3 LITERATURE REVIEW                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                    |  |  |  |

| CHAPTER 4 MODULAR LDO DESIGN                                                                                                                                                                                                                                                                                       |  |  |  |

| 4.1 Supply Rejection                                                                                                                                                                                                                                                                                               |  |  |  |

| 4.2 Split Pass Transistor Approach and Sizing                                                                                                                                                                                                                                                                      |  |  |  |

|                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 3.1Feed Forward Noise Cancellation153.2Switch Based Transient Enhancement163.3Flipped Voltage Follower163.4Dynamic Biasing17HAPTER 4MODULAR LDO DESIGN184.1Supply Rejection184.2Split Pass Transistor Approach and Sizing194.3Buffer Design204.4Amplifier Choice204.5DC Regulation224.6Analysis25HAPTER 5RESULTS29 |  |  |  |

| CHAPTER 6 CONCLUSION                                                                                                                                                                                                                                                                                               |  |  |  |

| REFERENCES                                                                                                                                                                                                                                                                                                         |  |  |  |

# LIST OF FIGURES

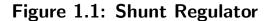

| 1.1 | Shunt Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

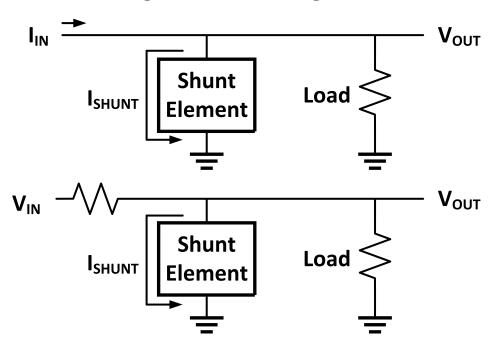

| 1.2 | Series Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3  |

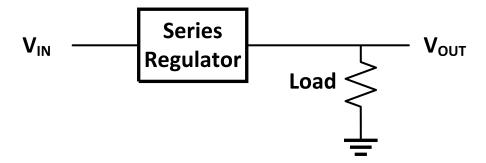

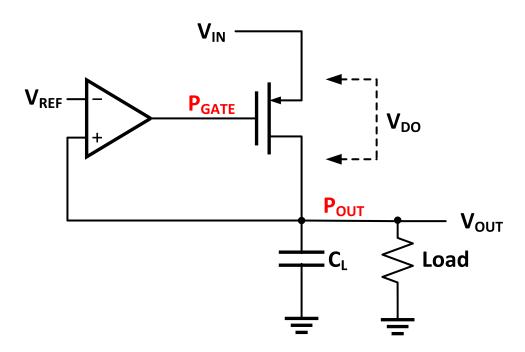

| 2.1 | LDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7  |

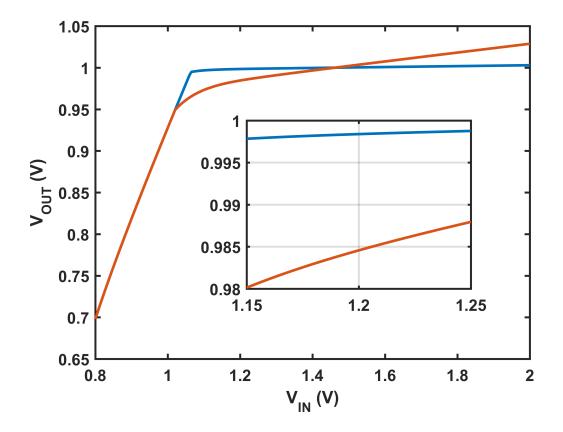

| 2.2 | Line Regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8  |

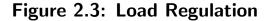

| 2.3 | Load Regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9  |

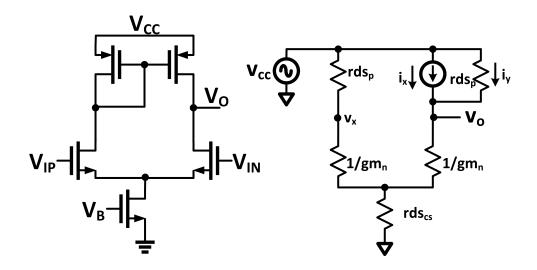

| 2.4 | NMOS Differential Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11 |

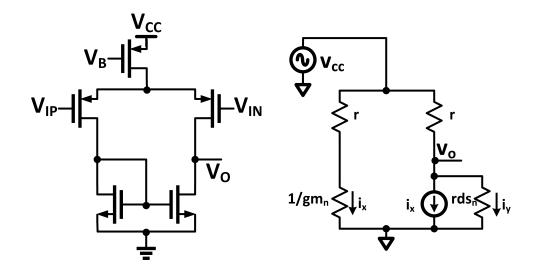

| 2.5 | PMOS Differential Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11 |

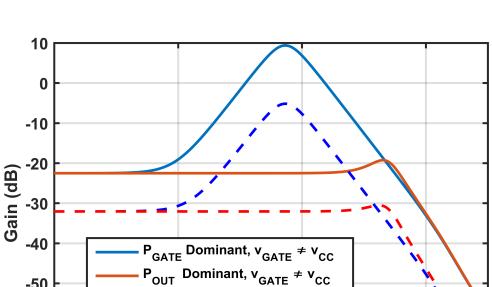

| 2.6 | PSR and Pole Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13 |

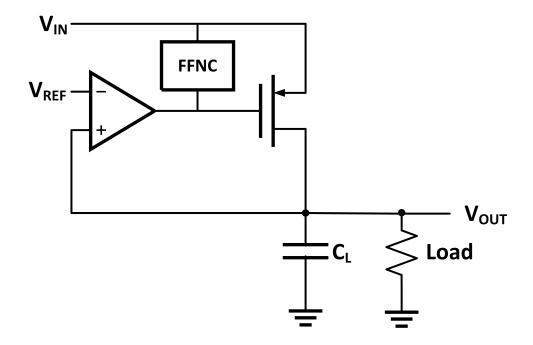

| 3.1 | Feed Forward Noise Cancellation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15 |

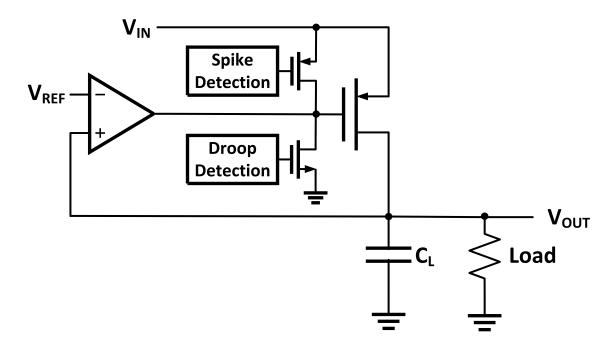

| 3.2 | Transient Enhancement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16 |

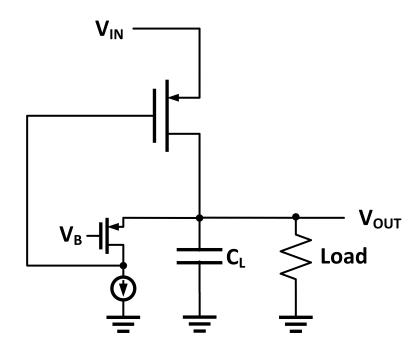

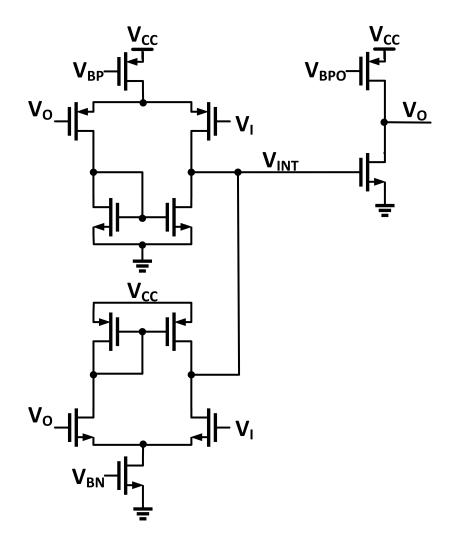

| 3.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17 |

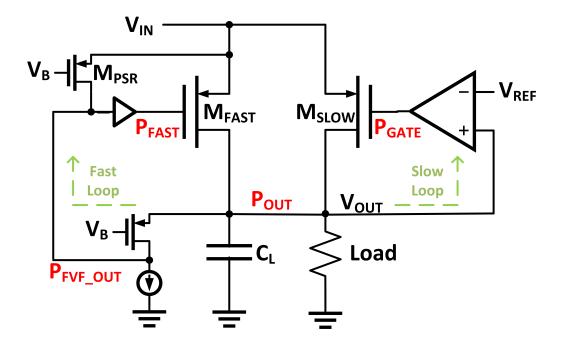

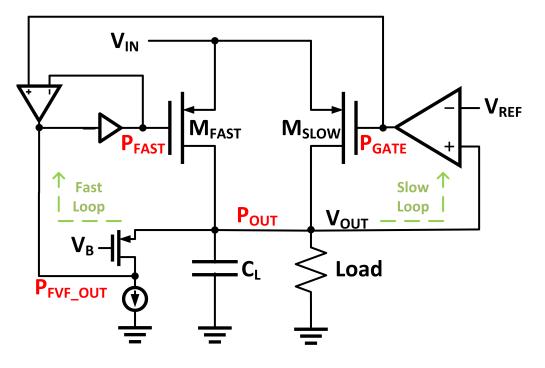

| 4.1 | Split Transistor LDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19 |

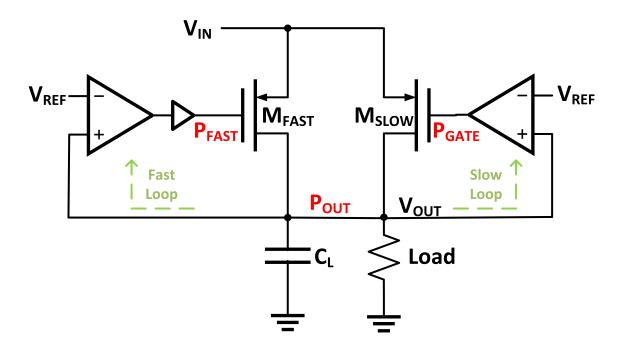

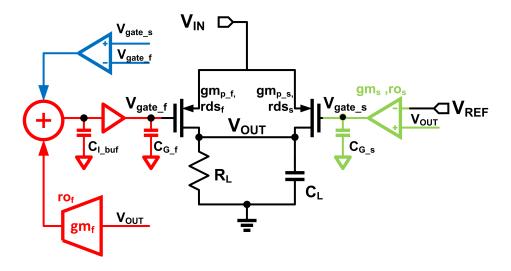

| 4.2 | Buffer Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21 |

| 4.3 | FVF Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23 |

| 4.4 | FVF with Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23 |

| 4.5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24 |

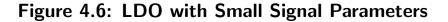

| 4.6 | LDO with Small Signal Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25 |

| 4.7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25 |

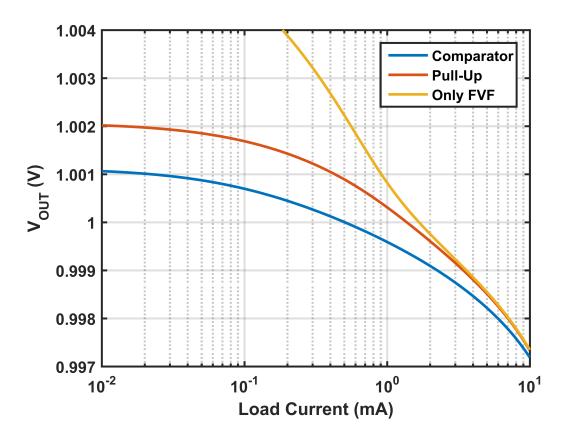

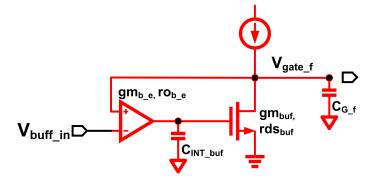

| 5.1 | Load Regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30 |

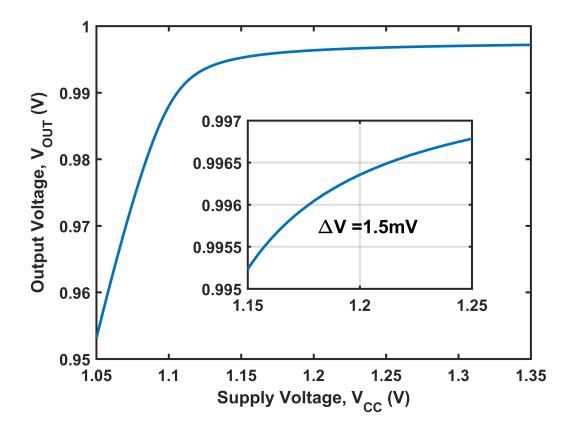

| 5.2 | Line Regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31 |

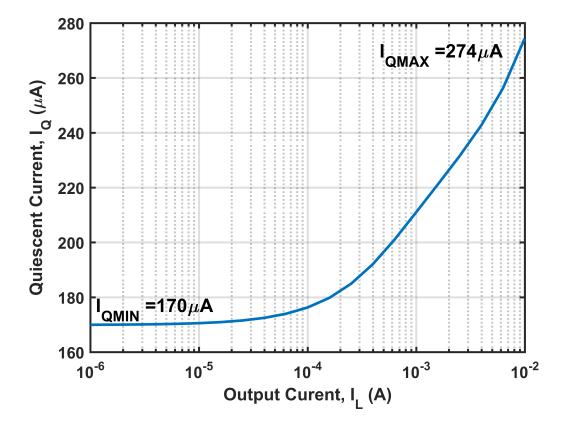

| 5.3 | Quiescent Current Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32 |

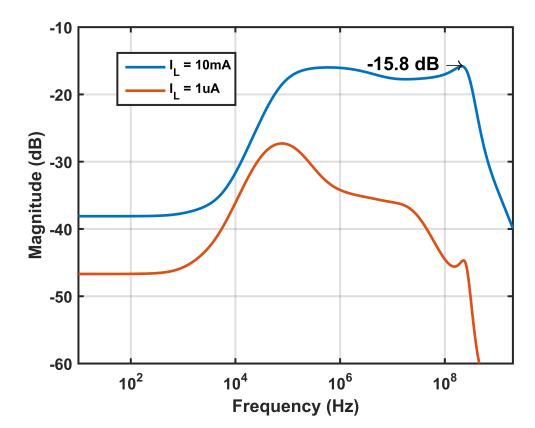

| 5.4 | Supply Rejection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33 |

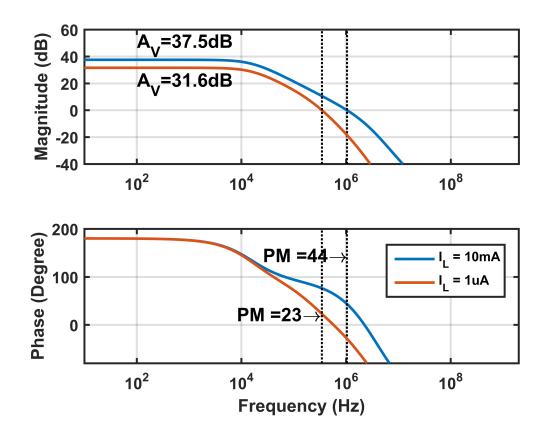

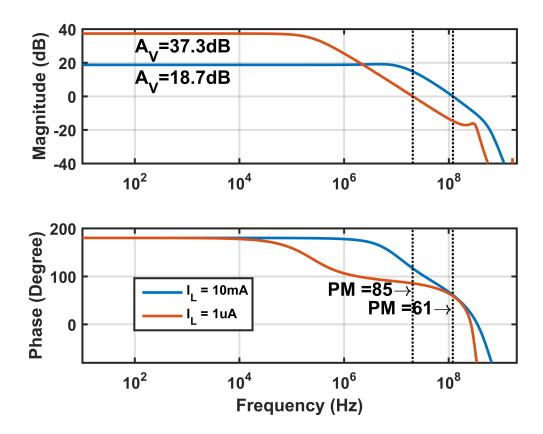

| 5.5 | Slow Loop Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

| 5.6 | Fast Loop Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35 |

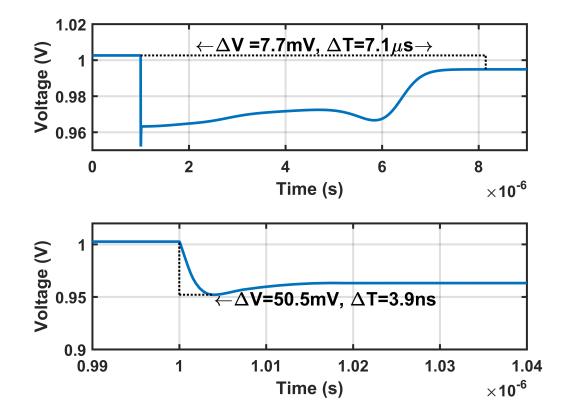

| 5.7 | $V_{\rm OUT}$ Response to a Load Step $\hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \ldots \hfill \ldots \hfill \hfi$ | 36 |

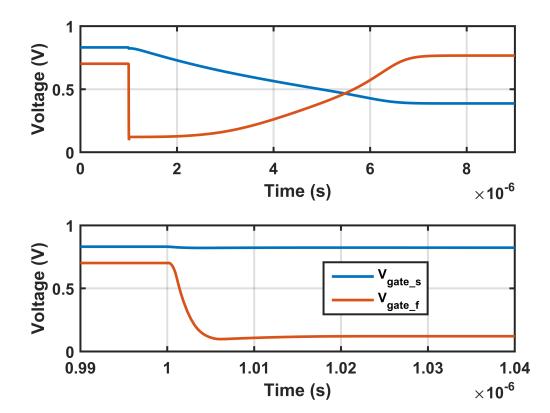

| 5.8 | Internal Nodes Response to a Load Step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37 |

# LIST OF ABBREVIATIONS

- BJT Bipolar Junction Transistor

- FOM Figure of Merit

- FFNC Feed Forward Noise Cancellation

- FVF Flipped Voltage Follower

- LDO Low-Dropout Regulator

- MOSFET Metal Oxide Semiconductor Field-Effect Transistor

- NMOS N-channel Metal Oxide Semiconductor Field-Effect Transistor

- PMOS P-channel Metal Oxide Semiconductor Field-Effect Transistor

- SMPS Switched Mode Power Supply

- VDO Dropout Voltage

# CHAPTER 1 INTRODUCTION

With advances in technology, the last decade has seen a significant rise in portable electronic products. These portable electronics are all battery powered and have increased the need for high-efficiency power management. This chapter discusses a current list of DC-DC converters some of which are very commonly used in portable electronics. Table 1.1 summarizes the different converters. Some of the important characteristics associated with these converters are power efficiency, supply rejection, transient response, load and line regulation. All of these terms will be explained in detail in Chapter 2.

|                    | Shunt Regulator |              | Series Regulator |              |

|--------------------|-----------------|--------------|------------------|--------------|

|                    | Passive         | Active       | Non-Linear       | Linear       |

| Power Efficiency   | ×               | ×            | $\checkmark$     | ×            |

| Supply Rejection   | ×               | $\checkmark$ | ×                | $\checkmark$ |

| Transient Response | ×               | ×            | ×                | $\checkmark$ |

| Load Regulation    | $\checkmark$    | $\checkmark$ | $\checkmark$     | $\checkmark$ |

| Line Regulation    | ×               | ×            | $\checkmark$     | $\checkmark$ |

Table 1.1: Comparison of DC-DC Converters

### 1.1 Shunt Regulator

This regulator works on the principle of shunting extra current. It therefore requires a current input. However, if the input is a voltage, a series pass element (such as a resistor) can be used. Figure 1.1, shows both current-in and voltage-in versions of the regulator. The shunt element in the regulator can be of two different types: active or passive. For example a Zener diode can be used as a passive shunt regulator, while an NMOS transistor could be used for an active version.

Supply rejection and load regulation of this type of regulator depends on the particular performance and type of shunt element used. A shunt element that can sink higher currents and respond faster would have better supply rejection and load regulation [1]. Line regulation, however, would be based on the series pass element. Equation 1.1 shows the efficiency<sup>1</sup> of a shunt regulator.

$$\eta = \frac{P_{\text{OUT}}}{P_{\text{IN}}} = \frac{V_{\text{OUT}} \times I_{\text{OUT}}}{V_{\text{IN}} \times I_{\text{IN}}} = \frac{V_{\text{OUT}} \times (I_{\text{IN}} - I_{\text{SHUNT}})}{V_{\text{IN}} \times I_{\text{IN}}}$$

(1.1)

$$\eta = \frac{V_{\rm OUT}}{V_{\rm IN}} \times \left(1 - \frac{I_{\rm SHUNT}}{I_{\rm IN}}\right) \tag{1.2}$$

In a current-in system,  $V_{\rm IN} = V_{\rm OUT}$ , which simplifies Equation 1.2 to Equation 1.3.

<sup>&</sup>lt;sup>1</sup>Note: All efficiency calculations in this section are based on the systems themselves and do not include amplifier/quiescent currents.

$$\eta = 1 - \frac{I_{\rm SHUNT}}{I_{\rm IN}} \tag{1.3}$$

The regulator needs a large  $I_{SHUNT}$  to have good supply rejection and load regulation. From Equation 1.3 it is clear that the shunt regulator is not very efficient.

#### 1.2 Series Regulator