© 2016 Philip B. Miller

# REDUCING SYNCHRONIZATION IN DISTRIBUTED PARALLEL PROGRAMS

ΒY

### PHILIP B. MILLER

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2016

Urbana, Illinois

Doctoral Committee:

Professor Laxmikant V. Kalé, Chair Dr. Anshu Dubey, Argonne National Laboratory Professor William D. Gropp Associate Professor Luke Olson

### Abstract

Developers of scalable libraries and applications for distributed-memory parallel systems face many challenges to attaining high performance. These challenges include communication latency, critical path delay, suboptimal scheduling, load imbalance, and system noise. These challenges are often defined and measured relative to points of broad synchronization in the program's execution. Given the way in which many algorithms are defined and systems are implemented, gauging the above challenges at synchronization points is not unreasonable. In this thesis, I attempt to demonstrate that in many cases, those synchronization points are themselves the core issue behind these challenges. In some cases, the synchronizing operations cause a program to incur the costs from these challenges. In other cases, the presence of synchronization potentially exacerbates these problems.

Through a simple performance model, I demonstrate that making synchronization less frequent can greatly mitigate performance issues. My work and several results in the literature show that many motifs and whole applications can be successfully redesigned to operate with asymptotically less synchronization than their naïve starting points. In exploring these issues, I have identified recurrent patterns across many applications and multiple environments that can guide future efforts more directly toward synchronizationavoiding designs. Thus, I attempt to offer developers the beginnings of a high-level play-book to follow rather than having to rediscover applicationspecific instances of the patterns. In memory of Daniel Harry Schreiber.

# Table of Contents

| Chapter 1  | Introduction                                                               |

|------------|----------------------------------------------------------------------------|

| -          | Modeling the Performance Impact of Desynchronizing<br>on                   |

| -          | Patterns for Reducing Synchronization in Distributed-<br>Parallel Programs |

| Chapter 4  | Atmospheric Data Input in ISAM                                             |

| Chapter 5  | Desynchronizing Parallel File Output                                       |

| Chapter 6  | Dense LU Factorization                                                     |

| Chapter 7  | Tree-Structured Adaptive Mesh Refinement                                   |

| -          | Desynchronizing and Optimizing the<br>o AMR Framework                      |

| Chapter 9  | Conclusion                                                                 |

| References |                                                                            |

## Chapter 1

### Introduction

Developers of scalable libraries and applications for distributed-memory parallel systems face many challenges to attaining high performance. These challenges include communication latency, critical path delay, suboptimal scheduling, load imbalance, and system noise. A wide range of tools and techniques have been developed to analyze and address these concerns.

Among the various responses, these problems are often defined and measured relative to points of broad synchronization in the program's execution. As many algorithms are defined and systems are implemented, this is not an unreasonable approach. In this thesis, I attempt to demonstrate that in many cases, those synchronization points are themselves the flip side of the coin behind these challenges. In some cases, the synchronizing operations themselves cause a program to incur the costs from these challenges. In other cases, the presence of synchronization potentially exacerbates these problems.

### 1.1 Load Imbalance

A great deal of work in the parallel computing literature references load imbalance to synchronization [1]. For an explicit instance, we find the definition "In the most general sense, a load imbalance in a parallel code is the difference in work on two or more processes between two of their synchronization points" [2]. In contrast, other areas of distributed computing use measures of load, such as time-averaged processor utilization or service response time, that do not reference coordinated activities between separate processes. This distinction is quite natural, since parallel computing of the kind under consideration is often applied to problems and solution methods that involve tightly coupled interactions among various parts of the computation. Measures of utilization and responsiveness thus do not capture the effects of load imbalance in this setting<sup>1</sup>.

In two limit cases, the time-averaged view and the synchronized view inherently coincide. In an embarrassingly parallel application, all processors work independently, but the job is incomplete until the last processor produces its final results; there is effectively synchronization at the very beginning and end of execution, but at no other points in between. The other case arises when examining load at the finest resolution between consecutive synchronization points with nothing intervening.

Over multiple points of global synchronization, aggregate utilization will equal a load measure from the bounding synchronization points if relative load among the processes is equal between each pair of consecutive synchronization points - i.e. if the load pattern repeats itself. If the load pattern varies, utilization less than 100% can reflect load imbalance even if the total work in each process is equal when summed between the two end points. Absent the intermediate synchronization, the processes would perform their equal work in equal time. Thus, we can say that the synchronization itself caused the program to incur a cost of load imbalance.

### 1.2 Noise

Petrini et al. related the impact of noise in an application with regular synchronization [3]. In that paper, they cited an earlier observation of noise in NAMD as a curiosity that did not impact performance as substantially [4], because at the time NAMD didn't have the global FFTs in PME for longrange force calculation that would impose global synchronization. Once that was added, noise became a much greater concern for NAMD, and usage has shifted toward leaving a processor core idle on most systems where interference cannot be avoided.

More recent work on modeling and simulating the impact of noise is specifically geared toward capturing the implementation details of heavilysynchronizing collective operations, because that is where noise is felt most severely [5].

<sup>&</sup>lt;sup>1</sup>At a suitable level of measurement, e.g. neglecting polling/spinning on communication, utilization level does capture many other performance effects.

### 1.3 Fault Recovery

Another problem facing large-scale parallel systems is efficiently addressing system faults. One way of tolerating faults is through message-logging protocols [6, 7]. These protocols replace expensive rollback of the entire system to a global checkpoint with local recovery and re-execution of just a single failure domain, such as a hardware node or group of nodes [8]. With sufficient information about applications' control flow and communication structure, they can run with low additional memory demands and minimal execution overhead [9, 10]. More sophisticated protocols can even omit re-execution of some tasks if the underlying environment can prove that their results have been fully communicated [11].

During recovery, unaffected processes can continue execution independent of the failed process(es) up to a point where they depend (possibly transitively) on re-executed work from the recovering process. The extent to which this is possible depends on both the application's point-to-point communication structure and the frequency with which it calls for global synchronizing operations. When live processes reach a point in their execution where they wait for the completion of such operations, they must idle until the failed process(es) catch up and fulfill those dependencies. Thus, looser synchronization can reduce the impact of faults.

### 1.4 Summary

The preceding observations have been previously offered to motivate the use of asynchronous and task-based programming and execution models. In as much as these models avoid creating inadvertent program-order dependencies among logically independent computations, they reduce instances of synchronization that are irrelevant to correct execution. This thesis focuses at a higher level, examining the synchronization presented by algorithms and applications themselves.

My work and several results in the literature show that many motifs and whole applications can be successfully redesigned to operate with asymptotically less synchronization than their naïve starting points. The adaptations I've contributed to include

• per-step input of atmospheric forcing data in the Integrated Science

Assessment Model (ISAM), used to study land-surface/atmosphere interactions (Chapter 4),

- parallel output of particle trajectories in NAMD and ChaNGa (Chapter 5),

- dense LU factorization (Chapter 6),

- unknown-count uses of the TRAM framework for streaming many-tomany communication, used in EpiSimdemics ([12, 13, 14], described in Chapter 3),

- a tree-structured AMR mini-application (Chapter 7), and

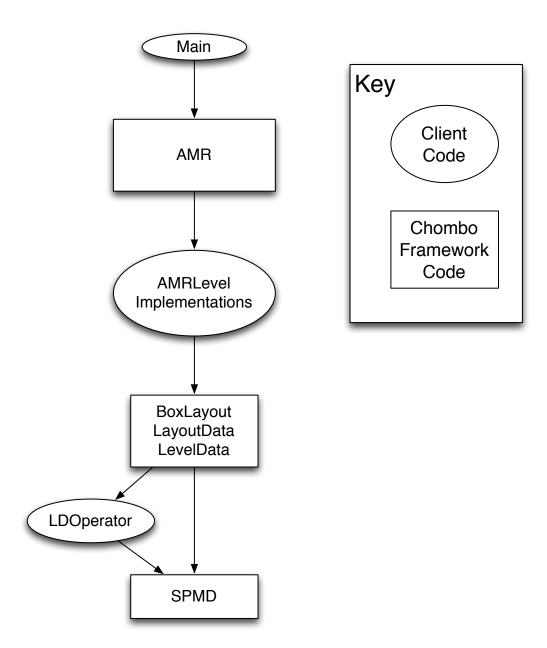

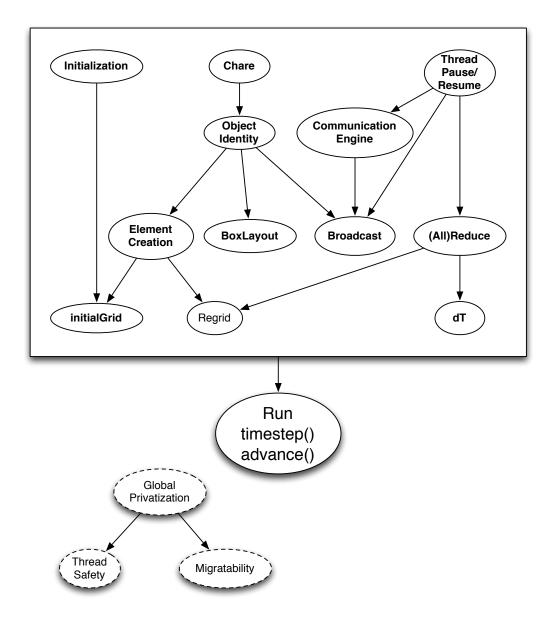

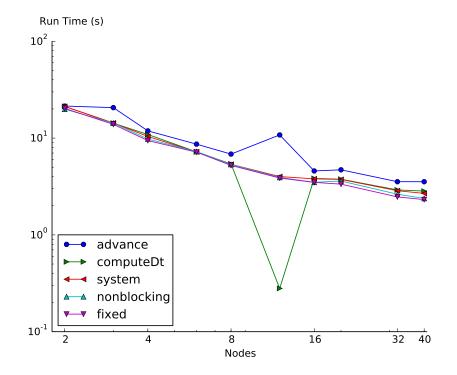

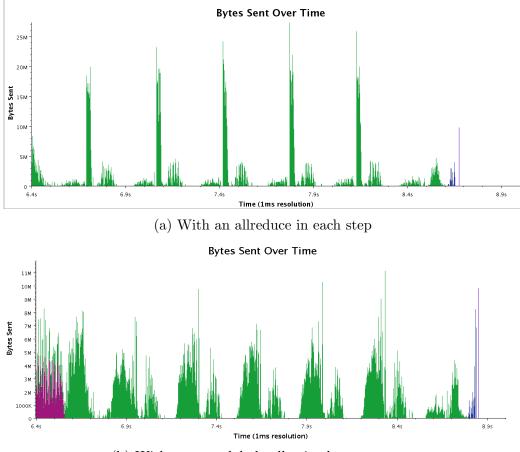

- the Chombo framework for patch-structured AMR (Chapter 8).

We see varying degrees of performance improvement from implementing these changes. We also see that in systematically reducing synchronization, a specifically asynchronous environment is neither necessary (Chapter 4) nor sufficient (Chapter 8).

In exploring these issues, I have identified recurrent patterns across many applications and multiple environments that can guide future efforts more directly toward synchronization-avoiding designs. These are described in Chapter 3. Thus, I attempt to offer developers the beginnings of a highlevel play-book to follow rather than having to rediscover application-specific instances of the patterns.

## Chapter 2

## Modeling the Performance Impact of Desynchronizing Execution

Motivated by the connection of synchronization to the costs of load imbalance, noise, and critical path delays, this chapter explores a simple performance model to demonstrate that less frequent synchronization can mitigate these problems.

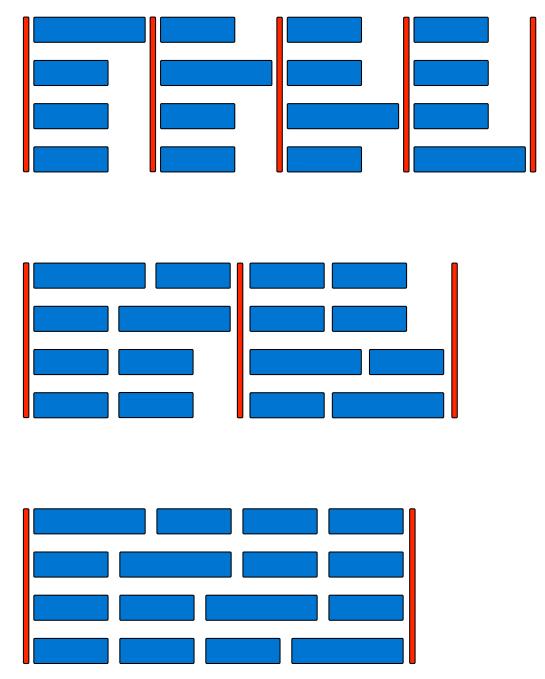

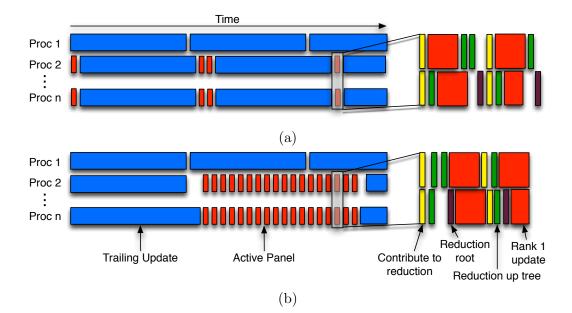

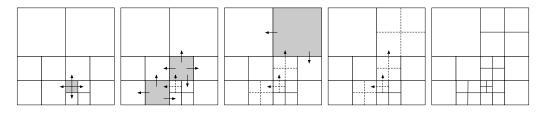

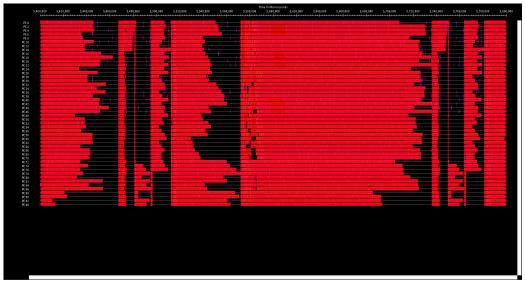

Consider an iterative parallel program running on p processors. In each step, every processor typically executes a basic work unit of length w. Some fraction f of the work units, evenly distributed across time and processors, take longer than w by a ratio  $r = 1 + \Delta > 1$ . The processors must synchronize their execution every k steps (e.g. in a convergence test, or the data distribution seen in ISAM in Chapter 4). Unlike Valiant's Bulk Synchronous Parallel model [15], the synchronizing operation itself is taken to be free, and communication cost is neglected. The application will run for s steps in total, which is assumed to be large. An intuitive illustration of this model, with varying k, can be seen in Figure 2.1.

In all cases, the total work is given by the expression

$$spw(1+f\Delta)$$

Given the uniform distribution of overload, the ideal execution time simply divides the work by the processor count:

$$T_{ideal} = sw(1 - f + fr) = sw(1 + f\Delta)$$

$$(2.1)$$

Since we are primarily concerned with large-scale parallel systems, assume that  $p \gg 1/f$ , so that some processor can be expected to experience an overload in each step.

Figure 2.1: An illustration of the intution behind this model's predictions that eliminating synchronization can mitigate performance impacts of load imbalance, noise, and other undesirable effects. The rows of blue boxes represent work on separate processors, and red bars represent points of global synchronization among them. As synchronization is eliminated, less time is lost.

In the case where the application synchronizes at every step, k = 1, the elapsed time per step is simply the maximum over all processors, wr, and so the total elapsed time is

$$T_{k=1} = swr = sw(1+\Delta) \tag{2.2}$$

Effectively, the program behaves as if f = 1 in Equation 2.1.

Next, we consider the case where synchronization is slightly less frequent: k = 2. In very unlucky windows, some processor will have two long steps back to back, making the window take 2wr time<sup>1</sup>. Except at processor counts that are large relative to  $f^2$ , the majority of windows can be expected to take time w(1+r) and thus the total elapsed time (with 2 steps in each window) is approximately

$$T_{k=2} = s \frac{w(1+r)}{2}$$

(2.3)

$$=sw\frac{1+(1+\Delta)}{2}\tag{2.4}$$

$$= sw\frac{2+\Delta}{2} \tag{2.5}$$

$$= sw\left(1 + \frac{\Delta}{2}\right) \tag{2.6}$$

We can see that just widening the synchronization window by one step nearly halves the effect of the overload, relative to Equation 2.2.

In the limit where k > s, every processor is expected to experience fs long steps of time wr and (1 - f)s steps of time w. Thus the total time to completion is given by

$$T_{k>s} = fswr + (1 - f)sw$$

(2.7)

$$= sw(1 - f + fr) \tag{2.8}$$

$$= sw(1 + f\Delta) \tag{2.9}$$

This matches the ideal time given by Equation 2.1. Entirely removing midrun synchronization thus fully mitigates any excess cost of the intermittent overload.

<sup>&</sup>lt;sup>1</sup>This probability may not be entirely negligible at k = 2, but it decreases geometrically as  $f^k$ , with larger k being of greater interest

More generally, we can compute the expected time for any value of k. The program will execute s/k synchronization windows each encompassing k steps. Of those,  $\lceil kf \rceil$  will be long, and the rest normal. Thus, the total time will be approximately

$$\frac{s}{k} \cdot \left( \lceil kf \rceil wr + (k - \lceil kf \rceil)w \right)$$

(2.10)

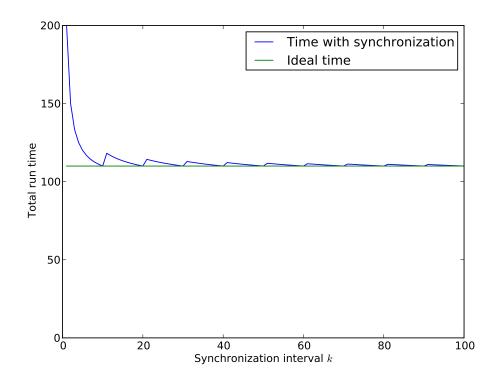

In the limit as k grows large in this equation, we can again see that it converges to the ideal time given in Equation 2.1. This formula as a function of k is plotted in Figure 2.2. As a speedup relative to k = 1, we find that

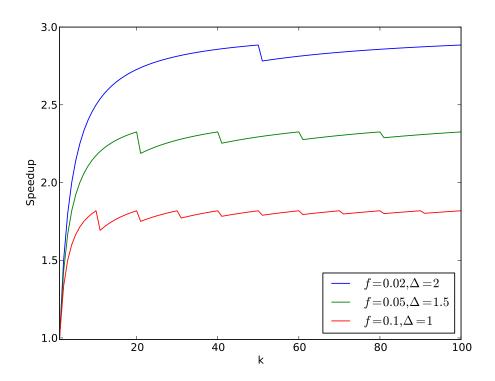

speedup<sub>*f*,

$$\Delta$$</sub>(*k*) =  $\frac{1 + \Delta}{1 + \frac{\lceil kf \rceil}{k}\Delta}$  (2.11)

This is illustrated in Figure 2.3.

The overall effect of fully eliminating synchronization in this model is to provide a maximum speedup of

speedup<sub>$$\Delta,k\geq s$$</sub> $(f) = \frac{1+\Delta}{1+f\Delta}$  (2.12)

Since noise is typically observed to occur in a time-dependent manner rather than a step-dependent manner, the model requires some adaptation<sup>2</sup>. Consider unsynchronized noise occuring with a period t and amplitude a. If  $t \leq w$ , then it is high enough frequency to affect essentially all processors equally from this model's perspective. Thus, f = 1 and  $\Delta = \frac{w}{t} \cdot a$ .

In the lower-frequency case, where t > w, then  $f \approx t/w$  and  $\Delta \approx a/w$ . These are approximate values, because the stretching of a step on one processor may delay others enough that they suffer noise as well, or noise may occur when the processor was idle waiting for a message to arrive [5].

The model as described above assumes that the relevant synchronization is global among all processors. When synchronization is not global, but involves only a subset, the model must be adjusted accordingly. The fraction of

<sup>&</sup>lt;sup>2</sup>Trace-based performance instrumentation with fixed output buffers is an exception to this. In CHARM++, event logs for the Projections tool get flushed to disk after a fixed number of entries. Since steps of execution typically generate similar numbers of events repeatedly, but in different volumes on different processors, flushing acts like step-based noise.

Figure 2.2: Predicted running time of a program of 100 steps, with  $\Delta = 1$  and f = 0.1 as a function of k. We can see that as the synchronization window k increases, the running time converges to the total workload.

Figure 2.3: Speedup provided by widening the synchronization window from k = 1. Essentially ideal speedup is reached when  $k \ge 1/f$ .

processors that synchronize at any given point can be used to scale the value f. This reflects that in any given synchronization group, a processor will be overloaded proportionately less often as in the entire system. This structure may be found in neighbor exchange operations, especially where each processor is responsible for more than one independent unit of computation.

Programs that exhibit 'phased' behavior within larger steps should approximately follow this model. This is observed, for instance, in the original version of Chombo, with updates to each level of refinement constituting a phase. At different levels, different processors are over- or under-loaded, but across phases they partially average out. As described in Section 8.2, desynchronizing those phases improved overall performance.

## Chapter 3

## Patterns for Reducing Synchronization in Distributed-Memory Parallel Programs

Looking at the applications described in this thesis and elsewhere, we can identify several common patters for weakening or eliminating synchronization in distributed-memory settings:

- Batch (blocking on / waiting for) collectives (§ 3.1)

- Communicate more with each collective, to reduce frequency (§ 3.2)

- Send and consume data expected from a collective incrementally (§ 3.3)

- Separate communication from coordination (§ 3.4)

- Replace synchronizing collectives with coordination schemes (§ 3.5)

- Replace synchronizing collectives with p2p messages that achieve the desired effect (§ 3.6)

- Semantic object naming (§ 3.7)

This chapter characterizes these patterns, and attempts to generalize and abstract them so that they can potentially be applied more broadly and consciously.

This effort is in the spirit of various design pattern and pattern language efforts, originating in the work of (building) architect Christopher Alexander [16], imported into computer science and software engineering by the 'Gang of Four' Gamma, Helm, Johnson, and Vlissides [17] and broadly explored in the 'Pattern Languages of Programs' (PLoP) conference, and specifically introduced to parallel programming by Tim Mattson et al. in a book [18] and the ParaPLoP workshop series.

A common characteristic in many parallel applications is that broad synchronization is typically associated with calls to collective operations. This is partially inherent in the natural dependences those operations express, such as in all-to-all communication patterns. It can also result from dependences introduced by the algorithms used in the implementation of those operations [5]. Thus, many of the patterns illustrated in this thesis involve modifying or replacing collective communication operations with various alternatives.

In some cases, an operation causing synchronization conveys additional semantic information relevant to the applications control flow beyond any direct payload of data that it transfers. In the limit of operations that carry no payload, such as MPI barriers and CHARM++ quiescence detection, the only purpose they can serve is to transfer this more abstract state across processes and objects. In those cases, if we wish to weaken or eliminate synchronization, we must find other ways to let applications draw the same conclusions.

At the level of implementation considerations, synchronization often conveys useful information that cannot be overlooked. At the point of the call, the posting of a send operation indicates several facts:

- 1. the payload data has been fully computed

- 2. the payload data is available in a specific designated buffer

- 3. the sender is willing and able to commit network resources to that transfer

Analogous versions of the latter two points also apply to explicit receive operations.

- 1. a specific designated buffer is available to receive the payload data

- 2. the receiver is willing and able to commit network resources to the transfer

Since collectives generally combine sending and receiving data, both sets of facts apply, among all participants in the collective. These facts are essential to the efficient execution of optimized collective algorithms that rely on cooperation of processes between the originator of some input data and its final recipient.

In one-sided operations, these necessary facts must be handled very differently, essentially with coordination schemes of various sorts. Readiness of data must be conveyed through synchronization separate from the communication operation, such as fences or barriers. Buffer addresses must be negotiated in advance or explicitly communicated. Network resource commitment, where taken into consideration, also requires explicit synchronization aside from the transfer.

Consider an MPI application that wants to ensure that all of a set of receives are posted before their corresponding sends, or vice versa, to ensure that it does not fail or suffer performance penalties due to implementation or hardware limits. This is a fundamental example of synchronization for coordination without any payload or higher-level semantic content. It's solved by posting a set of non-blocking operations all in one direction (e.g. all sends), calling for a barrier, and then posting all of the opposite operations (e.g. all receives).

In general, we informally consider synchronization as a third factor alongside communication and computation when analyzing the design and deployment of various parallel algorithms. An algorithm or configuration that can achieve its desired result by reducing one of these terms either without increasing the others or by limiting the increase to a reasonable tradeoff can be expected to offer better overall performance. Similarly, with increasing processor count or problem size, slower growth in the synchronization term will predict lower overall cost. Thus, although applicable in different contexts and applied in different forms, the patterns below all aim at reducing synchronization relative to other elements of a parallel program's execution.

### 3.1 Batch (Blocking On / Waiting For) Collectives

**AKA** Use synchronization from one collective to avoid incurring synchronization penalties from subsequent collectives.

**Applicability** There is a large interval between when data to be communicated is or can be ready to send, and when it must be available to consume. There is a large portion of available data whose communication can be shifted substantially earlier or later to be communicated in bulk. The synchronization associated with the unit collectives does not provide useful information to the rest of the application. **Description** Consider an application that performs several collective operations interspersed with its computation in each step. For instance, the application may execute in several delineated phases, with some of those phases calling collectives. If the result of those collectives isn't immediately needed to continue work within that phase, nor does the fact of their completion provide semantic information, then the synchronization those collectives impose may incur avoidable costs as described in Chapter 2.

To avoid those costs, it's preferable to rearrange execution (and potentially program structure, as necessary) so that as many collective operations as possible are performed back-to-back, rather than interspersed with computation. After one synchronizing operation, batching more in a 'convoy' avoids introducing opportunities for imbalanced load, noise, or extra critical path delays to intervene and delay completion of later operations. Even with nominally uniform work for every process to perform between synchronizing operations, increasingly variable processor clock speeds across individual chips and nodes means that any extraneous work will likely be imbalanced [19].

With non-blocking collectives, this pattern is still potentially relevant. Barring specialized hardware, interrupt-driven operation, or a dedicated thread, processor time must still be made available to allow non-blocking collectives to make progress. Batching uses the synchronization of one operation to guarantee the necessary resource availability for however many follow it in (ideally) quick succession.

#### Known Uses

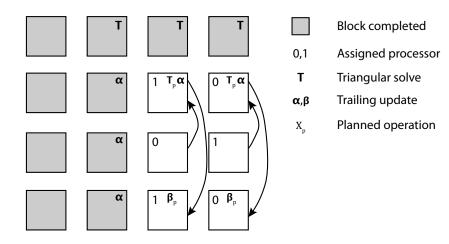

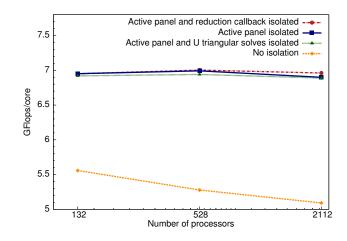

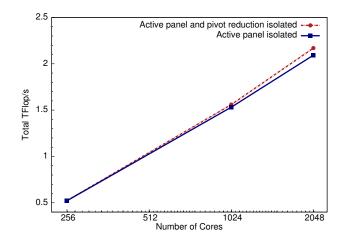

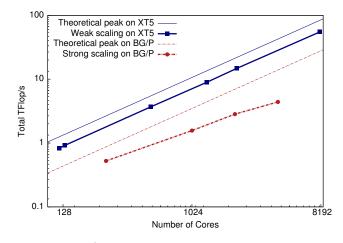

CHARMLU: The exclusive scheduling of active panel factorization updates and reductions ensured that other operations would not interfere with this highly-synchronous work on the critical path. Essentially, from the perspective of the active panel, the large-block DGEMMs in trailing updates acted as noise lasting several times the duration of each column's work. The optimization to batch up the synchronous active panel work is described in Sections 6.2.5 and 6.2.6.

CHOMBO: Though not its logical endpoint, the work on Chombo's stable timestep calculations described in Section 8.2 shows the effect of batching reductions. By doing all of a timestep's reductions at its end, and then combining them, we obtained better performance than running separate reductions between timestepping of each level of refinement. **Related Concepts** This pattern will tend to appear in concert with explicitly increased concurrency and parallelism in nearby portions of execution. In Chombo, application of this pattern exposed latent concurrency among computation on multiple levels of refinement.

### 3.2 Communicate More With Each Collective, To Reduce Frequency

#### **AKA** Condensing collectives

**Applicability** The same general conditions as in batched collectives apply. Additionally, the communication and computation to be performed must fit in a single defined operation.

**Description** Abstractly, the idea of this pattern is to rearrange communication, and possibly the computation to feed that communication, so that more communication occurs in association with each synchronizing operation. If that synchronization was not otherwise informative, then this rearrangement should lead to a proportionate decrease in how often synchronizing operations must occur.

One instance of this pattern would be replacing repeated gather or scatter operations over a common set of processes but with varying roots with fewer all-to-all or all-gather operations.

This pattern is something of an anomaly. Where other patterns suggest to replace or weaken collectives, this one proposes to strengthen them. The tradeoff is that a single heavy-weight operation may carry a great deal of synchronization (in the form of excess dependencies), but much of that synchronization can be overlapped within a single narrow window of execution, leaving a many times broader window of execution between synchronization.

#### Known Uses

A clear example of this pattern is seen in optimizations of the ISAM land surface modeling code, described in Chapter 4. In that setting, repeated scatter operations occurring every k steps were transformed to much rarer all-to-all operations every kp steps, whose period scales with the number of processors used in a given run. The total set of true dependences and which processor provided the data to satisfy them was unchanged by this transformation. However, all computational steps beyond the first one after the collective have their dependences satisfied much earlier.

Meanwhile, many false dependences between independent computational steps were broken apart. In this case, the frequent synchronization from scatter calls provided no extra information that the application itself actually needed. However, the coordination of network resource usage those synchronized collectives provided avoided creating network hotspots that would have appeared in a naïve use of one-sided operations instead. Using an all-to-all operation preserved the communication efficiency benefits of synchronized network resource allocation.

Ultimately, by applying the transformation from frequent iterated scatter operations to rare all-to-all operations, the synchronization window was drastically widened. As predicted by the model described earlier and observed in experiments, this had the effect of fully mitigating periodic load imbalance.

In the CHOMBO AMR framework, the time-advancing operation on each level is expected to globally reduce and return a stable timestep value usable for the following step. As described in Section 8.2, all of the per-level stable timestep reductions ultimately fed into a single reduction of the value to use across all levels of refinement. By forcing synchronization between the updates of separate levels, the framework incurred the costs of load imbalance and communication latency at every level. Moving all of these reductions to the end of each whole step eliminated that excess synchronization, and allowed all the reductions to be consolidated into a single operation.

CHARM++ has recently implemented a consolidated 'summary statistics' reduction operation. It takes multiple inputs, and computes all of the minimum, maximum, mean, and standard deviation. It is built on a more general tuple reduction design that would allow condensation of arbitrary related reductions, though that has not yet found other uses.

As described in Section 6.3, the 'tournament pivoting' algorithm used in Communication-Avoiding LU factorization also demonstrates this pattern.

**Related Concepts** As in the previous pattern, condensed collectives will tend to appear in concert with explicitly increased concurrency and parallelism in nearby portions of execution. Cause and effect in this relationship can flow in either direction, depending on details of the application. In ISAM, parallelization of the atmospheric input reading and pre-processing was necessary to subsequently make this pattern applicable.

Alternatives Non-blocking collectives are applicable in circumstances very similar to this pattern - a substantial time interval between availability of some data and the demand for it. When applied exactingly, they have the advantage of more precisely expressing the dependencies of related computation on the data they convey. They have the prospective disadvantage of increasing the necessary amount of control flow and volume and lifetime of state necessary to manage them. This contrast is particularly noticeable when the combined data grows with one of the application's scaling factors, such as processor or step count. This is the case in ISAM, which would call for up to  $\mathcal{O}(P)$  non-blocking scatters to be in flight at once. Non-blocking collectives also require an effort to ensure their progress, which may not be trivial if the application otherwise does little or no communication.

## 3.3 Avoid Collective Synchronization by Sending and Consuming Data Incrementally

**Applicability** The data to be communicated by a collective can be broken down into independent units, and the computation can incrementally generate and/or consume those units in coarse enough work grains to not suffer high relative overhead from fine-grained communication.

**Description** As noted by Hoefler et al. [5], various collective operations encode different dependency patterns among participating processes. By using a collective to communicate the data to fulfill those dependencies, an application is saying that *all* data to be sent depends on all preceding computation, and all subsequent computation depends on all data received. In some cases, such as transpose-based parallel FFT implementations [20], this is a very practical choice.

In many cases, however, each unit of data to send might be generated by an independent unit of computation, and each unit of data received may expose independent units of computation. This pattern suggests that the program should be structured to allow those computations to occur incrementally, with data tansfer interleaved. Thus, the program can avoid the strong synchronization entailed by using a collective to transfer it all at once.

#### Known Uses

CKIO, an implementation of parallel output in CHARM++, demonstrates this pattern [21]. As data fills a buffer representing a write stripe, the write operation can be initiated immediately, independent of any other data that may be expected. This is described further in Chapter 5.

CHARMLU also exhibits a variant of this pattern, as described starting in Section 6.2.1. Due to its memory scheduling, blocks of matrix data are not transferred in conventional multicast operations to be consumed at some point later. Rather, they're transferred when there is space set aside for them. Computation proceeds according to priority, and releases storage holding input blocks as the need for those blocks on a given process ends.

EPISIMDEMICS: Another CHARM++ application demonstrating this pattern is EPISIMDEMICS [14]. This is an agent-based code for simulation of contagion phenomena in semi-discrete time. Typical simulations focus on the spread of infectious diseases in day-long steps. The simulation is modeled by a bipartite graph of objects. The objects on one side of the graph represents groups of individual agents. The objects on the other side of the graph represent groups of locations where those agents may interact over the course of each simulated day. In each day, the agents dynamically generate a schedule of locations they will visit, and transmit the times they will be at each of those location to the location objects. When the location objects have received the full set of visits, they compute the interactions between agents who were present at overlapping times during that day, and send the interactions back to the agent objects. When the agents have received the full set of interactions they experienced during the day, they update their state (e.g. become infected) and prepare for the next simulated day.

The initial implementation of EPISIMDEMICS in MPI executed each day in a cycle of compute-communicate phases. Each communication was implemented as a variable all-to-all collective. For various reasons, this design encountered scaling limits at approximately 512 cores. Allowing for incremental communication and processing in the CHARM++ port (along with other changes) improved scalability to thousands of processors. Ultimately, subsequent optimizations enabled it to scale to hundreds of thousands of cores on Blue Waters and various Blue Gene Q installations.

CHOMBO: A mild example of this pattern can be seen in the MPI implementation of CHOMBO. Its standard communication pattern for blockto-block boundary exchange, interpolation, and down-sampling uses a loop of point-to-point nonblocking send and receive operations between processors holding neighboring or overlapping boxes, followed by waiting for all of those operations to complete. This behavior is precisely modeled by the neighborhood all-to-all operations added in the MPI-3 standard. However, by treating each message independently, receivers are able to do necessary processing on each one (e.g. copying from the communication buffer into its final location; accumulating the received values with existing data; interpolating the received data in time or space either alone or with existing data) as it arrives, rather than waiting for all of the messages expected by the collective that could nominally replace these individual operations.

A more fully elaborated form of this pattern appears in porting CHOMBO to CHARM++, described in Chapter 8. Each high-level communication operation in the original CHOMBO code was treated as a collective. In this design, computation on any box on a processor is made to wait on completing the communication for all other boxes also assigned to that processor. By running the control flow of CHOMBO for each box independently, we gain incremental processing of communicated data. As soon as each box's dependencies are satisfied, its computation proceeds.

An implementation of parallel sorting in CHARM++ by Solomonik [22] exhibits this pattern. Earlier implementations identify 'splitter' or 'separator' keys that would produce a sufficiently uniform distribution of values across processors, redistribute all of the data according to those distinguished keys in a bulk all-to-all operation, and only then rearrange the data locally on each process to its final sorted order. In the newer implementation, data is partitioned and transferred incrementally as acceptable splitter keys are identified, and each recipient starts merging partial results into locally sorted order as the rest of the data moves and the sorting process proceeds.

**Related Concepts** Streaming communication and computation is a more general idea that somewhat subsumes this one. The distinction is that incrementalizing a collective is based on having a pattern of communication that has inherent uniformity in what data is being communicated, and what entities are sending and receiving it. Streaming deals with data that would not have generally been transferred through collectives, except in artificial attempts to follow a bulk-synchronous design.

After all the individual units of data have been received and processed, there may be subsequent work dependent on the whole set. If the count of messages to be received is known *a priori*, then that computation can be locally triggered. If not, the next pattern is applicable as well.

### 3.4 Separate Communication from Coordination

**Applicability** The application gains useful semantic information from the communication operation beyond the content explicitly passed by the operation. That semantic information is not inherently necessary for efficient implementation of the communication itself.

More concretely, this patterns applies when there is uncertainty in the number or size of messages being sent and received. One example would be a scalar MPI\_Alltoall to form the receive counts and displacements arguments to a subsequent variable MPI\_Alltoallv. Another would be a reduce-scatter to indicate how many messages each process must wait to receive in a communication phase before moving on.

A more general scenario with uncertainty of both sends and receives is where receiving one message may lead to the generation of others. Thus, the program requires some consensus mechanism to ensure that each process can tell when it has received every message that has been or will be sent to it.

**Description** Send messages using elementary point-to-point mechanisms, or using optimized schemes such as routing and aggregation [13]. These can be fairly general, and non-specific to the application. Separately, identify the characteristics of the communication pattern or the algorithm it supports that need to be signalled. Implement or deploy a mechanism to detect that characteristic. If a more general mechanism doesn't entail an excess cost in efficiency, it is likely suitable.

#### Implementation Mechanisms

Nonblocking Barrier or Reduction: This simplest mechanism can be lightweight and very efficient, since it requires only a simple, bounded communication pattern to implement. However, it is limited in that it requires message senders to be identified before communication starts, and message senders to know idependently when they have sent all of their traffic. An implementation of this pattern, Dynamic Sparse Data Exchange [23], was offered as motivation to add non-blocking barrier collectives to the MPI standard.

Quiescence Detection (QD) is one of the most general mechanisms to fill this role. It detects when all messages sent within a parallel program have been received and processed, and no further messages remain in transit in the network or queued on any processor. Thus, it can support use cases with unpredictable senders, variable message counts, and dependent messages generated as a result of receiving previous messages. CHARM++ includes a highly efficient implementation [24]. A potential downside of its use, noted below, is that by detecting a global property, it conflicts with concurrent composition of multiple modules the idependently need to know when their own communication has finished, without regard to activity in the others.

Modular Quiescence Detection: 'Completion Detector' (CD) One means of providing this out-of-band coordination is the 'Completion Detector' library in CHARM++ [25]. This library uses waves of reductions and broadcasts over a spanning tree of the system to count senders finished and messages sent and received, signaling completion when all messages from all senders have been delivered. It is similar in design to CHARM++'s quiescence detection module, except that it has been made modular to not require that the rest of the program fall idle for it to make progress.

Parental Responsibility 'Termination Detection' (TD) is a design for recognizing the completion of 'diffusing computations' on a distributed system, originally developed by Djikstra [26]. It builds a spanning tree over processing elements that have sent messages, with responsibility for detecting the end of all activity within a subtree lying with its root. As processors receive messages, they send acknowledgments to the sender, except for the first message they receive which is not acknowledged until all messages they have sent get back acknowledgments.

#### Known Uses

EPISIMDEMICS ([14], also described in § 3.3) illustrates this pattern. Specifically, the number of messages each communication end-point will send or receive in a step is not known *a priori*, since it is entirely data dependent. As noted above, setup work can occur as messages are delivered, but each timestep cannot be processed by an object until it knows that it has received all of the messages sent to it for that step. In this case, each sender knows when it has sent all of its messages for a step. Thus, senders can potentially tell a coordination mechanism when they are done, and how many messages they sent.

As the communication pattern in EPISIMDEMICS is an instance of dynamic sparse data exchange [23], that design would have been applicable to the MPI implementation. The same design is possible in CHARM++, but with much greater syntactic and runtime overhead.

Quiescence detection worked well for this purpose in early versions of EPISIMDEMICS. However, its global nature was problematic when the application evolved to run multiple instances of the simulation within each job to allow dynamic scenario testing. At that point, QD coupled progress of the independent scenarios, and hence synchronized them. Substituting an instance of the Completion Detector for QD in each instance of the simulation resolved this difficulty.

Topological Routing and Aggregation of Messages (TRAM [13]): While the basic mechanisms of TRAM can convey the data in question from sender to receiver, both TRAM and the application need additional coordination information for correctness. TRAM needs to know when all messages generated by a step have been sent, so that it can start to flush its buffers. TRAM must also know when all messages at a given layer of its routing system have been received, so that that layer can proceed to flush its buffers to the next layer. Finally, the application needs to know when it has received all of the messages that were sent, so that it can proceed to compute on the entire set.

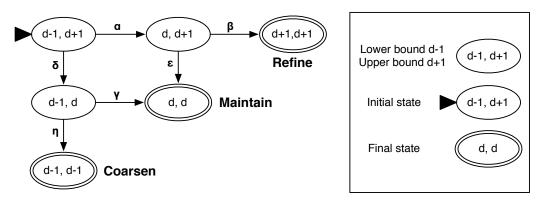

TREEAMR: In the TreeAMR code described in Chapter 7, we initially replaced global collective communication with point-to-point messages carrying all of the data, and a separate synchronization mechanisms to indicate when consensus on how to adjust the mesh was reached. This stage of evolution does not eliminate synchronization, but it weakens the dependencies carried by it, and enabled further adaptations that do eliminate broad synchronization. A second stage of evolution in TreeAMR carried this further: by carefully coordinating object insertions and subsequent control flow, one of two synchronizations at each regridding step was further eliminated.

DSDE: Another example can be seen in recent solutions to the 'dynamic sparse data exchange' problem [23] that helped justify the non-blocking barrier operation added to MPI-3. A naive implementation of this communication pattern uses a variable all-to-all operation (possibly preceded by a simple all-to-all to convey buffer sizes), with many send/receive counts set to zero. To replace the sparse all-to-all operations with lighter weight communication patterns, Hoefler et al. combined non-blocking synchronous sends with a non-blocking barrier used to indicate that all messages had been delivered, and so no process would need to wait on the chance that more would arrive.

**Related Concepts** Valiant's Bulk Synchronous Parallel model [15] assumes that all communication is uncoordinated, and uses separate global synchronization for receivers to know that messages have arrived. This pattern partially mimics BSP, with major caveats. Relative to BSP, the presumed ability of modern systems to process messages as they arrive offers substantial 'extra' expressive power within each superstep, since each received message can potentially generate subsequent dependent messages. Thus, more powerful mechanisms than barriers are necessary, but not necessarily any more costly.

Standalone communication without conveying broader coordination is likely to also be received incrementally, and hence available to process incrementally as well. Thus, this pattern is closely related to the pattern of replacing collectives with incremental communication and processing, described in Section 3.3.

### 3.5 Replace Synchronizing Collectives with Coordination Schemes

**Applicability** The application gains useful semantic information from the synchronizing operation beyond the content explicitly passed by the operation. That semantic information is not necessary for efficient implementation of the communication itself.

**Description** The semantic information provided by synchronization can be obtained by some other application-specific means, or the application can profitably be adapted to use a substitute for or alternative form of that information.

#### Known Uses

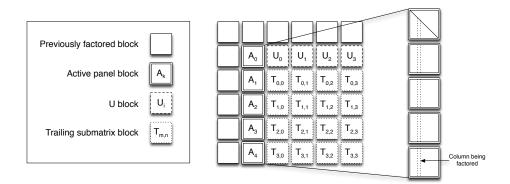

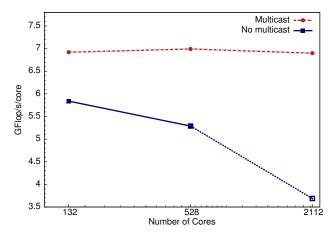

CHARMLU: HPL, the reference LINPACK implementation used for Top500 benchmarking [27], uses synchronized multicasts over rows and columns of a 'process grid' to transmit factored blocks for use in further computation. The synchronization in these broadcasts effectively coordinates two kinds of resources: communication bandwidth and progress, and available memory. CHARMLU (described in Chapter 6) does not use synchronized multicasts, and thus coordinates these resources through other means [28, 29, 30].

HPL has a configurable fixed 'lookahead depth' that controls how many steps ahead of computation data can be distributed. By doing so, it limits the memory footprint of remote data that each process holds as input for local computations. CHARMLU replaces the fixed lookahead depth with a dynamic per-process value based on actual available memory. Within the bounds of available memory, each processor sends explicit requests for blocks of data that it will need in the near future. How it does this, efficiently and without creating deadlock situations, is described in Section 6.2.2.

Because a given factored block is needed by all blocks beyond it in the factorization, the request scheme created hotspots of injection bandwidth on the nodes holding each block as many requests arrived in close succession. This revealed the value of coordinating network resource usage from the synchronized multicasts. Since the set of processors with a pending request at any given time is dynamic, we implemented a scheme to send the message via dynamic spanning trees by appending the destination list to the block

message to a few processors, and have them each forward the message to further subsets. This is described in more detail in Section 6.2.4.

CKIO also demonstrates this pattern. Collective output has been used to synchronize processes to ensure that the recipient of data to be written would be ready to handle it when provided. With message driven asynchronous execution, concurrent composition, and suitable coordination, the synchronization becomes unnecessary. The results of this work are described in Chapter 5.

**Related Concepts** Alpert and Philbin described an analog of this concept for a Bulk Synchronous Parallel setting, which they call 'Counting BSP' [31]. They observe that if receivers can anticipate the number of messages they will receive in a superstep and count them as they arrive, then no actual barrier to synchronize the end of the superstep is necessary.

## 3.6 Replace Synchronizing Collectives with Point-to-Point Messages That Achieve the Desired Effect

**Applicability** The application gains useful semantic information from the synchronizing operation beyond the content explicitly passed by the operation. That semantic information is not necessary for efficient implementation of the communication itself. Enough data is available locally in each process to form a substitute through targeted point-to-point messages.

**Description** When the coordination information drawn from synchronization is not necessarily global, individual processors can communicate directly with each other to synthesize a local substitute. This may imply changes in the higher-level algorithm's operation to use that local information rather than the global version previously available.

#### Known Uses

CHARMLU's use of directed request messages to indicate memory availability for specific blocks on particular processors demonstrates this pattern, as described in Section 3.5 and Section 6.2.2. In concert with 'separating communication from coordination' (Section 3.4), broad synchronization in the mesh evolution phase of TreeAMR ([32], Chapter 7) can be eliminated entirely. Both the first and last stages stages of optimizations to mesh evolution push the knowledge of general state from broadly interdependent collective operations about regions to be refined or coarsened, objects to be created or destroyed, and neighbors added or removed into local point-to-point messages with narrow dependencies. The first stage replaces collectives that described mesh evolution globally with locally consistent and stable mesh evolution marked by consensus detection. The last stage replaces globally detected and signaled consensus with locally provable consensus based on convergence of lower and upper bounds.

This pattern is potentially applicable to numerically stable time step calculation in any simulation of a system in which computed effects have finite propagation speed through the simulation domain. For instance, compressible fluid flows satisfy this, while incompressible models do not. They can achieve this by locally computing and applying stable time step lengths within each portion of the domain, and coordinating values at interfaces where the time step differs. The impact this approach would have over the prevalent global reduction method in CHOMBO is explored in Section 8.2.3. Implementation of this new design is on the roadmap for the ENZO-P AMR cosmology/astrophysics application using the CELLO framework [33].

### 3.7 Semantic Object Naming

AKA Unique global names, coordinate-based indexing

**Applicability** The application requires a *dynamically evolving* set of objects that must be generally reachable for communication. These objects are counted, numbered, sorted, placed, or located. The application is built to run in an environment that provides fully distributed and asynchronous location metadata lookup (e.g. Chare Arrays in CHARM++ [34]).

**Description** Every object to be created has its identifier constructed based on some inherent characteristic of its place or role in the application. How that identifier is formed may be very application-dependent. For instance:

- a spatial coordinate within the simulation domain,

- the path to or position of the object in some distributed structure representing the computation

- the object's unit of responsibility in a data decomposition

- how much progress the computation has made

This obviates the need for globally synchronizing steps to do things like counting the objects to create, scanning that count across processors, numbering the objects, sorting the object list, or mapping object-level neighbor lists to processor-level communication lists.

#### Known Uses

There are two implementations of tree-based structured AMR in CHARM++ that apply this pattern. Both implement bit-vector indices for boxes giving the path from the tree root to the named node, as described in Section 7.2.4 in the context of a tree AMR mini-application. The CELLO framework extends the scheme to a forest-of-trees structure, by prepending the top-level index of each box's containing tree to the bit-vector. A similar design is on the roadmap for CHANGA's Barnes-Hut tree.

In CHARMLU, matrix blocks are indexed by their position in the matrix. This enabled easy experimentation on their mapping [35], and would support the request-driven dynamic multicasts described in Section 6.2.4 even if blocks were dynamically relocated (such as for load balance) during execution.

The port of CHOMBO to CHARM++ partially implements this pattern. It encodes the generation and refinement level of each box into parts of their index, as described in Section 8.1.3. The final element of each box's index that's currently generated by global numbering could be replaced with coordinate-based indices to avoid global numbering and sorting.

Bock and Challacombe's implementation of *Sparse Approximate Matrix-Matrix Multiplication*, SpAMM [36], logically extends the 3D parallel matrixmultiplication of Agarwal et al. [37]. They use the sparsity structure to omit computing portions of the block-wise convolution space that will not make noticeable contributions to the final product. The basic 3D algorithm could be implemented to apply this pattern both in 2D to blocks of the input and output matrices, and in 3D to the intermediate blocks summed to form the product. SpAMM implements a recursive tree structure within these indices, representing subdivisions of the matrix that it will actually operate on.

Alternative: In applications with well-defined and smoothly-evolving neighborhood structure, process-local object numbering and distributed update protocols can similarly avoid global operations to name and connect objects (at least after initialization). AMR simulations can be made to fit this case, and can be implemented as such [38]. The challenge of this approach as opposed to pure semantic naming and distributed location lookup is that it requires more specialized application logic to implement. In both cases, each application must invent its own means to label relevant and potentially evolving entities. Without distributed lookup for unique global names, applications must also define its own algorithms for locating and connecting those objects, rather than relying on a common synchronization-avoiding infrastructure. Since a universal implementation of that infrastructure exists [34], it can be effectively used with this pattern in all but extraordinary cases.

## Chapter 4

## Atmospheric Data Input in ISAM

#### List of Patterns Illustrated:

3.1 Batch (blocking on / waiting for) collectives ( $\S$  4.1)

3.2 Communicate more with each collective, to reduce frequency  $(\S 4.3)$

The Integrated Science Assessment Model (ISAM) is a whole-Earth and single-site land surface model code used to study biogeophysical and biogeochemical phenomena and their interaction with the larger climate and ecosystem. It couples fluxes of carbon, nitrogen, water, and energy between the near-surface atmosphere, plant growth, and material accumulation above and below ground. ISAM has been used extensively in various modeling and synthesis studies.

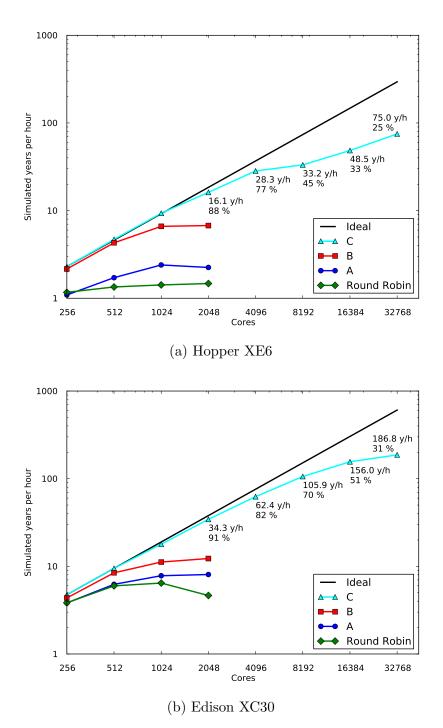

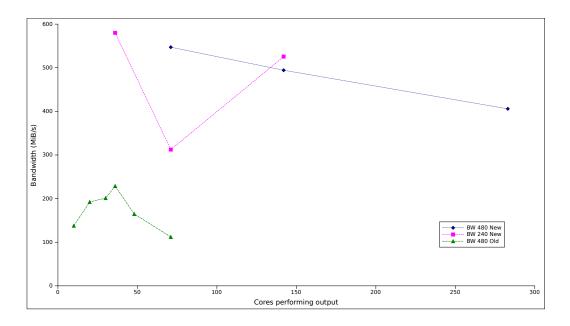

In previously published work in collaboration with Michael Robson [39]<sup>1</sup>, we adapted ISAM to substantially improve its performance and scalability on large supercomputers. Relative to the performance of a suitable baseline version of the code at its peak of 1k cores, we obtained a  $6.6 \times$  speedup on the Hopper Cray XE6 system and a  $2.8 \times$  speedup on the Edison Cray XC30 system, both hosted at NERSC. These same changes also enabled strong scaling up to 32k cores on each of these systems, with efficiency limited only by a documented serial bottleneck described by Amdahl's Law. This chapter reviews the portion of the previously published work relating to the model's atmospheric data input (also called the 'climate forcing'), describes the substantial excess synchronization that our improvements removed, and reanalyzes the results obtained in light of the model presented in Chapter 2.

<sup>&</sup>lt;sup>1</sup>The text and figures of this chapter are adapted from the cited paper with permission. ©2014 IEEE

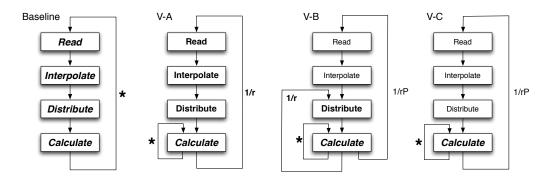

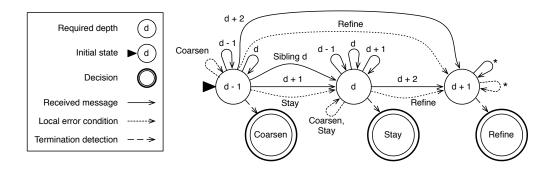

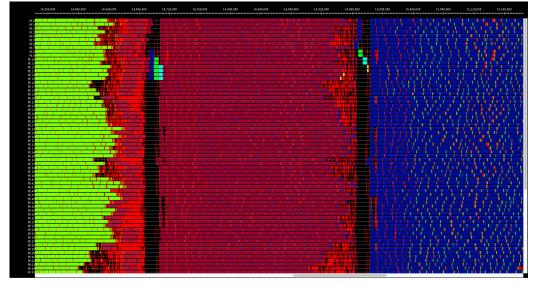

Figure 4.1: An illustration of the process by which various versions of ISAM acquire and consume atmospheric input data. Each flow chart represents one version of the code, with various optimizations implemented. The optimizations are described in the section corresponding to the label on each flow chart. In the baseline version, input is read, interpolated, and distributed in each step (shown by '\*' loops). Later versions reduce redundant work by a factor of  $3 \le r \le 12$ , the ratio of model time steps to atmospheric input time resolution (1/r loops). Finally, non-computational work is parallelized and desynchronized in two stages (1/rP loops).

The basic structure of the climate forcing data input procedure involves three steps. A process reads the appropriate point in the time series provided by the input files, using the NetCDF library [40, 41]. It then computes the spatial interpolation to the simulated land surface points. Finally, the interpolated data are distributed to the processes according to which grid points they are responsible for. The mapping of points to processors is done in a round-robin fashion to obtain rough load balance. This structure, and the changes to it described in this chapter, are illustrated in figure 4.1.

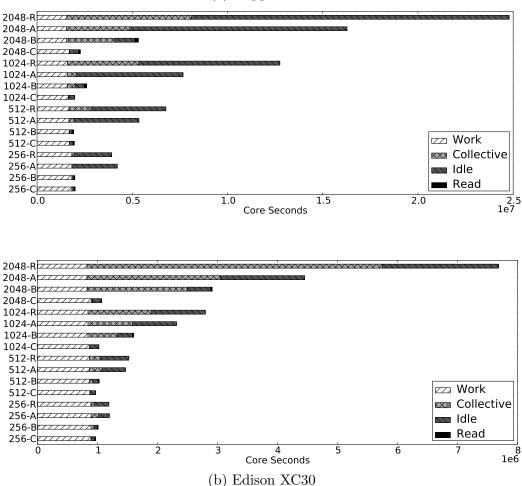

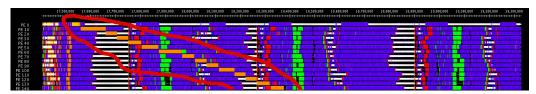

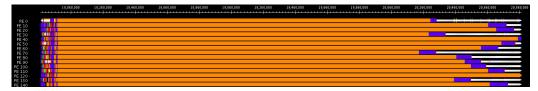

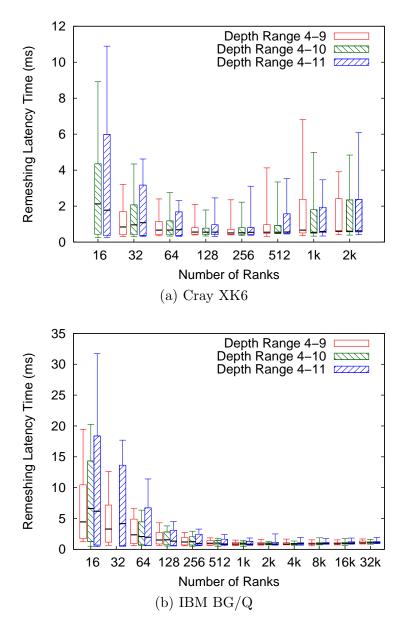

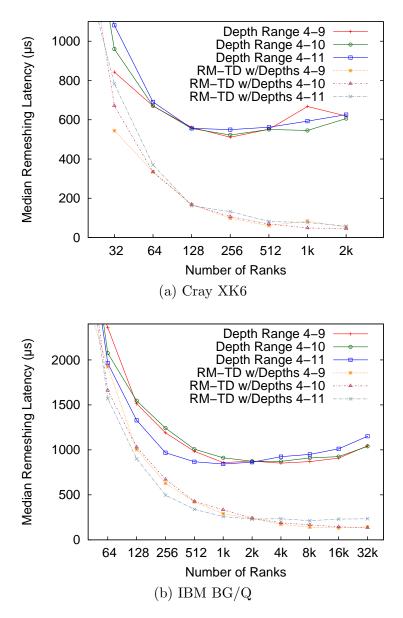

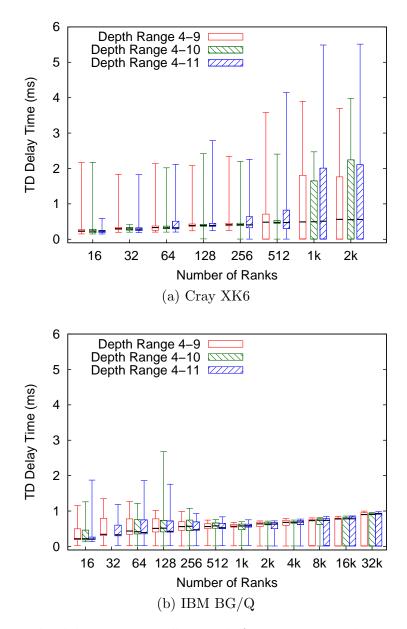

The initial design of this input presented many impediments to scalability. The remainder of this chapter discusses how these limitations have been largely eliminated. All data are shown in figures 4.2 and 4.3. The individual curves and bars are keyed 'A', 'B', and 'C' by the successive optimizations they depict, and 'R' denotes the baseline with no input optimizations, but with the round-robin mapping described in the original paper.

In collecting the data reported here, we coarsely separated time spent on collectives from idle time waiting at collectives. For each dynamic instance of a collective operation, we recorded the time elapsed from call to return in each process. We record the minimum observed time across all processes as the actual collective time of each instance, and the excess time beyond that minimum on each process as idle time. Given the approximate nature of this methodology, it may be more appropriate for present purposes to simply consider collective and idle time in combination, rather than independently.

## 4.1 Matching Atmospheric Timestep with Model Timestep

The ISAM model is typically run with a timestep of 30–60 minutes. The atmospheric data are provided at time intervals of 3–6 hours. In the initial implementation of ISAM developed by our collaborators, every step contained a call to the input procedure, which read the most recent atmospheric data from the source files on rank 0, interpolated it, and distributed it. Thus, the latency of filesystem access, interpolation, and MPI\_Scatterv was on the critical path of successive model timesteps. Given that the same data would be provided for 3–12 steps in a row, this repetition was both redundant and created excess synchronization.

By modifying ISAM to reuse already-prepared data, we improved performance by a factor of  $1.7 \times$  on 1024 ranks of Hopper and  $1.2 \times$  on 1024 ranks of Edison. This improvement comes from both reduced time spent performing collectives, and reduced imbalance time waiting on heavily-loaded cores to reach each collective.

On 1024 cores of Hopper, where the round-robin and present optimized versions of the code obtain their best performance, the optimized code spends 88% less CPU time performing collectives and 24% less CPU time idling. The decline in collective time accounts for 62% of the  $1.7 \times$  speedup and the decline in idle time accounts for a further 34% of the speedup.

On 1024 cores of Edison, where the round-robin and present optimized versions of the code also obtain their best performance, the optimized code spends 30% less CPU time performing collectives and 18% less CPU time idling. The decline in collective time accounts for 64% of the  $1.2 \times$  speedup and the decline in idle time accounts for a further 33% of the speedup.

In as much as the work of several collectives was consolidated in time into a single one, this can be seen as an instance of the 'batch collectives' pattern (§ 3.1). The effect on execution structure is precisely analogous: widening the window between synchronizing collectives.

Figure 4.2: Overall scaling of ISAM as successive optimizations are applied to the input process for the climate forcing data. The graphs show years of simulated time per hour of execution wall time. Higher is better. Runs were for 5 years of simulated time. Labeled points show precise performance values and parallel efficiency relative to the most optimized code version 'C' on 256 cores.

(a) Hopper XE6

Figure 4.3: Breakdown of core-seconds spent by ISAM on different activities, as a function of scale and applied optimizations of the climate forcing data input process. Runs were for 5 years of simulated time. Lower is better.

### 4.2 Parallel-In-Time Reading and Interpolation

With input data read from the filesystem every few steps, the time per step scales poorly due to an Amdahl's law bottleneck on the time to access the filesystem and interpolate the data. Additionally, contemporary supercomputers offer high-bandwidth parallel filesystems to support their computational capabilities. By reading input data using only a single rank, ISAM was limited to the bandwidth of a single node.

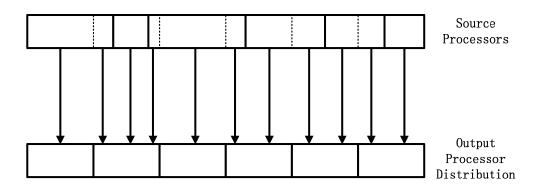

Thus, our next optimization to ISAM's input procedure is to read and interpolate many steps worth of input data in parallel. At model timesteps where data must be read, each process reads and interpolates data for a step computed by incrementing the current timestep by its rank. At each subsequent step, the responsibility for distributing data cycles across the ranks until every rank has served as the root once.

In theory, this can reduce the elapsed wall time spent on reading and interpolation by  $\mathcal{O}(P)$ , since P such steps are performed in parallel. This is potentially limited by available bandwidth both in accessing the file data from the filesystem and in interpolating it in memory. It also presents the potential for interference and contention between these processes or other jobs on resources such as the Lustre metadata server. At larger scales, we observe these effects as decreasing average bandwidth per core and node and increased variability, as described in the original paper.

Note that the memory load imposed by this adaptation scales with the number of ranks per node, rather than the number of ranks in the entire job. The code does not distinguish between rank 0 and all other ranks; thus they all have the capacity to read and interpolate input. In a setting where the total memory on a node is insufficient to buffer a step's input per rank, we could adjust the scheme to only read and interpolate on every kth rank instead. This simply adjusts the above theoretical impacts by a constant factor of k, without changing the conclusion of improved scalability.

The improvement provided by this optimization over that described in section 4.1 is  $2.76 \times$  on 1024 cores of Hopper and  $1.3 \times$  on 1024 cores of Edison. In both cases, the reduction in idle time accounts for the bulk of the improvement. On both systems, this optimization allows the code to continue to gain performance at scales up to 2k cores, with efficiencies of 39% and 34% respectively, relative to the 256 core baseline.

### 4.3 Simultaneous Distribution of Multiple Steps

Having minimized wasted CPU time by fully parallelizing the reading and interpolation steps, the largest non-work portion of the execution time at the scaling limit of the code from section 4.2 is spent in collectives. On 2048 cores, these consume 46% of CPU seconds on Hopper and 57% of CPU seconds on Edison. On both systems, the increases in collective times account for the bulk of increased time relative to runs on 1024 cores.

To overcome this impediment, we observe that at the first scatter operation after climate forcing data is read and interpolated, the P processors each have data available for an upcoming timestep. However, in each scatter, only the cyclically selected root processor actually provides it. This misses a substantial opportunity for increased parallelism in usage of network resources.

We take advantage of this opportunity by replacing the per-step calls to MPI\_Scatterv with an MPI\_Alltoallv operation performed every P time steps. Rather than spatially scattering data representing the climate forcing at a single point in time, we now transpose the data from its provided temporal distribution (each core sends a distinct timestep for every point) to a spatial distribution (each core receives the time series for the points it owns). Once this is done, each core can independently execute P time steps with no communication. Thus, we note that this transformation is an application of the 'do more with each collective operation' pattern described in Section 3.2.

At first glance, this pre-distribution of input data may seem to dramatically increase memory usage on every node. However, this is not the case. To see why, we first observe that the additional memory consumption is a constant, independent of P. Suppose there are n points in total, and each one requires bbytes of memory for a single time step's climate data. Each core is responsible for n/P of those points. The data each core reads from disk as in section 4.2 is bn. In the transposition, each core receives the bn/P bytes for one future time step from each of the P cores. Thus, the total received data is just bn– exactly as much as every core read from disk. For the NCEPQ climate data set, b = 24 and  $n = 192 \times 94 = 18,048$ , totaling 423 kilobytes. For the CRU\_NCEP data set, b = 32 and  $n = 720 \times 360 = 259,200$ , totaling 8 megabytes.

|     |                           | Lines | Lines   |       |

|-----|---------------------------|-------|---------|-------|

|     | Optimization              | added | deleted | Total |

| (A) | Matching input steps      | 53    | 35      | 88    |

| (B) | Parallel input            | 133   | 53      | 188   |

| (C) | Simultaneous distribution | 68    | 12      | 80    |

Table 4.1: Volume of code change required to implement each optimization

The effects of this optimization are striking. Where previously roughly half the execution time was spent in collectives at just 2k cores, this optimization reduces that time to less than 1% on both systems. Additionally, idle times also fell by over 50% on both systems, due to the longer period between synchronization points and greater opportunity for dynamic load variation to average out. Moreover, read times (though representing only a small proportion of execution) also fell substantially because of this optimization. We conjecture that this decrease is due to reduced contention when accessing the filesystem, since different cores can reach this phase across a wider timespan, as opposed to nearly simultaneously. Overall, this provides a  $2.4 \times$  speedup on 2k cores of Hopper, and a  $2.9 \times$  speedup on 2k cores of Edison. It also allows us to scale with continued speedups to 32k cores.

### 4.4 Summary

From our baseline code, we have obtained speedups of  $6.58 \times$  on 1024 cores of Hopper and  $2.78 \times$  on Edison. With all of the optimizations applied, we strong scale from 256 cores to 2048 process with an efficiency of 88% on Hopper and 91% on Edison. We accomplished this dramatic performance improvement through transformations that

- removed redundant collective calls (§ 4.1),

- parallelized input to use all processors instead of just one (§ 4.2), and

- exploited the parallel availability of much more input data to asymptotically reduce the frequency of calls to synchronizing collectives (§ 4.3).

In doing so, we also enabled essentially perfect strong scaling to more than an order of magnitude more processors than the code had previously been able to use.

# Chapter 5

# Desynchronizing Parallel File Output

#### List of Patterns Illustrated:

- 3.3 Send and consume data expected from a collective incrementally  $(\S 5.1)$

- 3.4 Separate communication from coordination (§ 5.1)

- 3.5 Replace synchronizing collectives with coordination schemes ( $\S$  5.3)

- 3.7 Semantic object naming  $(\S 5.2, 5.3)$

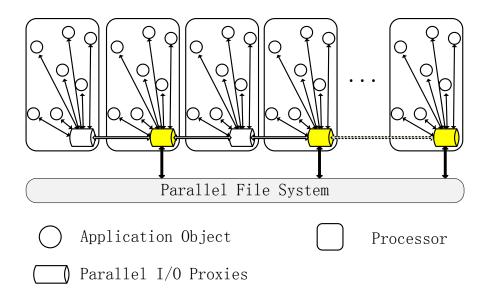

Parallel file systems, such as Lustre and GPFS, are common to large scale parallel computers. They offer very high write bandwidth to keep up with the data generation of applications running on those systems. To obtain good bandwidth, applications and their supporting libraries must arrange operations so that each 'stripe' unit of a file is only written to by a single processor, ideally in large, aligned block units. Typically, computations are not structured so that the resulting data will be arranged this way naturally. Thus, in line with the description in Chapter 3, the code must at a minimum

- 1. have a means to designate the block-processor mapping,

- 2. ensure buffers are allocated on each such processor to hold pending data, and

- 3. communicate that the writing processors are ready to receive the data from the processors generating it.

MPI collective write operations satisfy these needs through synchronized operation. For the cost of that synchronization, they offer very high performance in relocating the provided data and delivering it to the parallel file system.

The CkIO library was developed to provide CHARM++ applications with parallel filesystem support comparable to MPI-IO. This library has been through two full design generations to improve its performance and implementation flexibility. The later generation design is in production use in the CHANGA N-body particle simulation code used for cosmology and astrophysics. It is also in beta use for the NAMD classical molecular dynamics code for biomolecular research.

In the design progression of CkIO, we can see the incremental application of several patterns described in Chapter 3. In the first generation  $[21]^1$ , the library separated communication from coordination (§ 3.4) and processed data incrementally (§ 3.3). The second generation partially applied semantic naming (§ 3.7), but not to the extent that it could eliminate coordination through synchronized operations. After describing the two generations of CkIO that have been built so far, the final section of this chapter outlines a potential future design that fully applies these lessons to eliminate the need to synchronizing operations when performing parallel output.

### 5.1 Initial Design

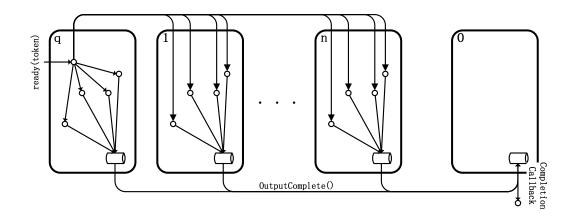

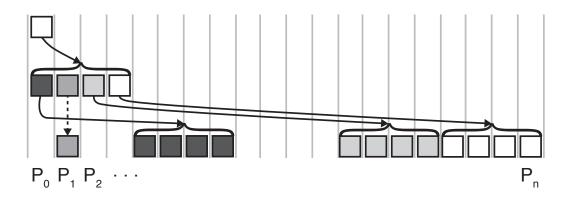

We have implemented an output forwarding layer for parallel applications written on top of the Charm++ parallel runtime system. As shown in Figure 5.1, the application's work is divided among several objects on each processor. The objects communicate with each other by asynchronous method invocation in an active-messaging scheme. Each processor can be executing work in one object while transmitting or receiving messages for others. This overlap of communication and computation is important for high performance.

Normal application development practices in Charm++ suggest the use of numbers of objects that correspond to a 'natural' decomposition of the problem being solved or the system being simulated, without direct regard for the number of processors in the system. The runtime can then map these objects

<sup>&</sup>lt;sup>1</sup>The text and figures describing this design in Section 5.1 are adapted from the cited paper with permission. O2011 IEEE

Figure 5.1: Architecture: Application objects communicate with local IO proxy objects, which exchange data amongst themselves and interact with the filesystem.

to optimize for load balance and communication patterns. However, for an I/O library, the many considerations of process- and node-level buffering, connection and contention limiting, and others drive toward an implementation that explicitly considers how many processors are available and how work is distributed among them.

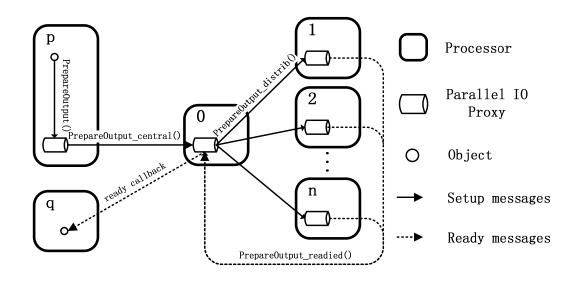

The central element of our implementation is a one-per-processor collection of objects (known as a *Chare Group* in Charm++) that we will interpose between application-level objects that own the data and the underlying parallel filesystem. Groups communicate by the same asynchronous mechanisms as other Charm++ objects, but are addressed by the processor on which they reside, rather than by an abstract index. The 'Parallel I/O Proxy' objects of Figure 5.1 are implemented as a chare group, instantiated at application startup. The interface to this group, including the message entry points and sequencing logic, can be seen in Figure 5.2. The corresponding implementation code can be seen in Figure 5.3.

When the application wants to perform output, it signals the chare group to prepare for that process (Manager::prepareOutout()). The group signals its readiness to the application through a callback (ready), through which it delivers an opaque handle that the application should pass in along with the data. That handle acts as a 'parallel file descriptor,' allowing the proxy

```

1

group Manager {

entry void prepareOutput_central(std::string name, size_t bytes,

CkCallback ready, CkCallback complete,

2

3

Options opts);

\frac{4}{5}

^7_8

entry void prepareOutput_readied(CkReductionMsg *m);

9

/// Serialize setting up each file, so that all PEs have the same sequence

entry void run() {

for (filesOpened = 0; true; filesOpened++) {

10

11

12

if (CkMyPe() == 0)

when prepareOutput_central(std::string name, size_t bytes,

CkCallback ready, CkCallback complete,

13

14

\frac{15}{16}

Options opts) atomic {

// Default setting and error checking omitted

17

18

19

nextReady = ready;

thisProxy.prepareOutput_distrib(nextHandle, name, bytes, opts);

files[nextHandle] = FileInfo(name, bytes, opts);

\frac{20}{21}

files[nextHandle].complete = complete;

21

22

23

24

3

when prepareOutput_distrib[filesOpened](int handle, std::string name,

23

25

26

27

size_t bytes, Options opts) atomic {

if (CkMyPe() != 0) {

files[handle] = FileInfo(name, bytes, opts);

}

28

29

30

31

// Open file if we're one of the active PEs

if ((CkMyPe() - opts.basePE) % opts.skipPEs == 0 &&

CkMyPe() < lastActivePE(opts)) {

int fd = open(name.c_str(),</pre>

32

33

\frac{34}{35}

O_WRONLY | O_CREAT, S_IRUSR | S_IWUSR);

if (-1 == fd)

36

CkAbort("Failed to open a file for parallel output");

37

38

files[handle].fd = fd;

}

39

\frac{40}{41}

\texttt{contribute(CkCallback(CkIndex_Manager::prepareOutput_readied(0),}

thisProxy[0]), filesOpened);

42

}

\frac{43}{44}

if (CkMyPe() == 0)

45

when prepareOutput_readied[filesOpened](CkReductionMsg *m) atomic {

\frac{46}{47}

delete m;

nextReady.send(nextHandle++);

48

}

\frac{49}{50}

}

};

51

52

53

\frac{54}{55}

entry void write_dataWritten(int handle, size_t bytes);

};

```

Figure 5.2: The interface definition and coordination code for the I/O proxy group

```

1

struct Options {

/// How much contiguous data (in bytes) should be assigned to each active PE

2

size_t peStripe;

/// How much contiguous data (in bytes) should a PE gather before writing it out

3

4

\mathbf{5}

size_t writeStripe;

/// How many PEs should participate in this activity

6

7

int activePEs;

8

/// Which PE should be the first to participate in this activity

9

int basePE:

/// How should active PEs be spaced out?

10

11

int skipPEs;

};

12

13

14

struct FileInfo {

std::string name;

Options opts;

15

16

17

size_t bytes, total_written;

18

int fd;

19

CkCallback complete;

20

}:

21

class Manager : public CBase_Manager {

/// Application-facing methods, invoked locally on the calling PE

void prepareOutput(const char *name, size_t bytes,

\frac{22}{23}

^{24}

\frac{25}{26}

CkCallback ready, CkCallback complete,

Options opts = Options()) {

27

thisProxy[0].prepareOutput_central(name, bytes, ready, complete, opts);

\frac{28}{29}

}

30

void write(int handle, const char *data, size_t bytes, size_t offset) {

Options &opts = files[handle].opts;

31

32

do {

33

size_t stripe = offset / opts.peStripe;

int pe = opts.basePE + stripe * opts.skipPEs;