© 2016 Dipanjan Das

#### VOLTAGE REGULATION OF A SERIES STACKED SYSTEM OF DIGITAL LOADS BY DIFFERENTIAL POWER PROCESSING

BY

DIPANJAN DAS

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2016

Urbana, Illinois

Adviser:

Professor Philip T. Krein

## ABSTRACT

A modern high-end multi-core microprocessor has very stringent power supply requirements. It can draw hundreds of amperes of current at supply voltages as low as 0.8 V. As the supply voltages keep decreasing, the power delivery to meet the supply requirements is becoming increasingly difficult and inefficient. However, the presence of multiple cores in the microprocessor offers us a way to power it at a higher voltage by series-stacking the cores. Differential power processing has been shown to be an efficient way to series-stack server loads. In this work we study the dynamics of the elementto-element DPP topology implemented with bi-directional buck-boost converters. Some of its dynamic drawbacks are pointed out and a topological modification to counter those drawbacks is proposed. We then develop a linear control to regulate processor core voltages in a series stack of 4 cores. A hysteretic control to accommodate light load modes in the bi-directional regulating converters is also discussed. Both the linear and the hysteretic controller are implemented successfully in hardware and efficiency improvement due to light-load modes is demonstrated.

To my parents, for their love and support.

## ACKNOWLEDGMENTS

I would like to thank my adviser, Professor Philip T. Krein, for giving me the opportunity to work under his guidance. He has always encouraged me and given me valuable insights and resources to solve problems. I would also like to thank Professor Robert Pilawa for providing me with valuable and enjoyable learning experiences in the last two years. I would also like to thank Srikanthan for motivating and providing me with energy during my first two years here.

I would like to thank the Strategic Research Initiative and Grainger Center for Electric Machinery and Electromechanics for funding this work.

Finally I would like to thank my family, who have always loved me and supported me unconditionally to pursue my goals.

# TABLE OF CONTENTS

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| CHAPTER 1THEORY AND LITERATURE SURVEY11.1Processor Power Delivery Requirements11.2Output Impedance of the Buck Converter21.3Transient Response Improvement, Efficiency Improvement111.4Series Connected Power Delivery and DPP15                                                                                                                                                                  |  |  |

| CHAPTER 2DPP FOR PROCESSOR POWER DELIVERY202.1Selection of Topology202.2The Element-to-Element Topology252.3Dynamics of the Element-to-Element Topology292.4Simulation Results on Dynamic Performance352.5Hierarchical Element-to Element topology382.6Motivation for Modified Topology382.7Simulation Results on Improvement in Dynamic Performance41                                            |  |  |

| CHAPTER 3 HARDWARE VERIFICATION433.1 DPP Converter board433.2 Transient Performance Tests473.3 Efficiency51                                                                                                                                                                                                                                                                                       |  |  |

| CHAPTER 4 IMPROVING EFFICIENCY AND DYNAMIC PER-<br>FORMANCE       53         4.1 Light-Load Modes in a Buck Converter       53         4.2 Switching Boundary Controllers       56         4.3 Voltage Mode Hysteretic Controllers       57         4.4 Extending Light Load Operation to Bi-directional DPP<br>Converters       60         4.5 Improved Voltage Regulation of the Stack       68 |  |  |

| CHAPTER 5 HARDWARE VERIFICATION OF HYSTERETIC<br>CONTROL                                                                                                                                                                                                                                                                                                                                          |  |  |

| CHAPTER 6 CONCLUSION AND FUTURE WORK 8                                         | 0 |

|--------------------------------------------------------------------------------|---|

| 6.1 Conclusion                                                                 | 0 |

| 6.2 Future Work                                                                | 0 |

| APPENDIX A SCHEMATICS, LAYOUT PICTURES AND BILL                                |   |

| OF MATERIALS                                                                   | 2 |

| APPENDIX B MICROCONTROLLER C CODES                                             | 6 |

| Mode Control                                                                   | 6 |

| B.2 C Code Used to Program the TMS320F28377S for Current<br>Hysteretic Control | 6 |

| REFERENCES                                                                     | 9 |

# LIST OF TABLES

| 3.1 | Averaged efficiency of the element-to-element topology, nom-<br>inal stack current = $5 \text{ A} \dots \dots$                              | 52 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1 | Averaged efficiency of the element-to-element topology, nom-<br>inal stack current = 5 A $\dots \dots $ | 76 |

|     | List of components used in the first PCB (linear controller)<br>List of components used in the second PCB (hysteretic                                                                                   | 83 |

|     | $controller)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                          | 89 |

# LIST OF FIGURES

| 1.1  | Buck converter with parasitic elements                       | • |   | 2  |

|------|--------------------------------------------------------------|---|---|----|

| 1.2  | Buck converter averaged model                                | • |   | 3  |

| 1.3  | Compensation of buck converter                               |   |   | 4  |

| 1.4  | Open loop and closed loop output impedance of buck con-      |   |   |    |

|      | verter under droop control                                   |   |   | 5  |

| 1.5  | Typical buck converter output filter structure with para-    |   |   |    |

|      | sitic components                                             |   |   | 6  |

| 1.6  | Typical impedance of a composite system of capacitors        |   |   | 8  |

| 1.7  | A distributed model approximation for evaluating capaci-     |   |   |    |

|      | tor impedance in $1.6$                                       |   |   | 9  |

| 1.8  | Intermediate bus architecture (IBA)                          |   |   | 10 |

| 1.9  | Multi-phase buck                                             |   |   | 12 |

| 1.10 | Transient repetition rate                                    |   |   | 13 |

| 1.11 | Coupled inductor 2-phase buck converter                      |   |   | 14 |

| 1.12 | Series-connected power delivery                              |   |   | 16 |

| 1.13 | IBA vs. series-connected power delivery                      | • | • | 17 |

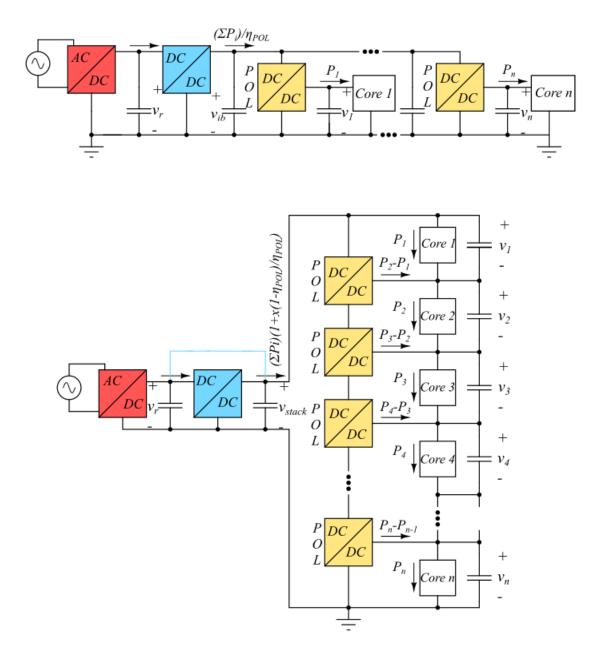

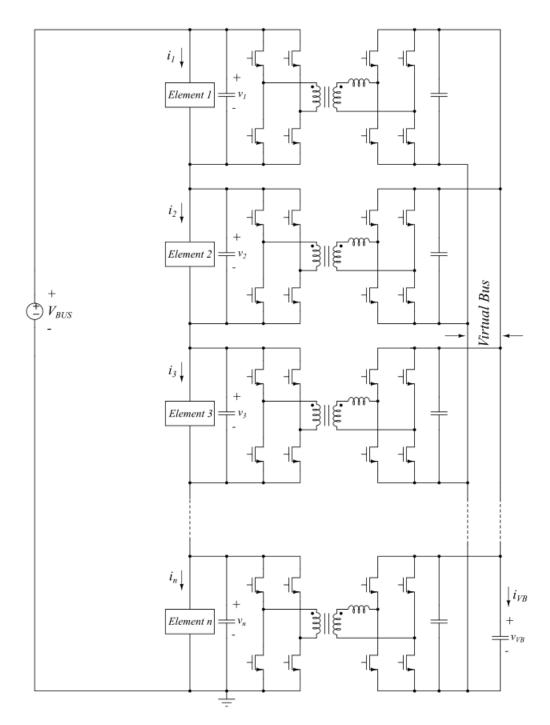

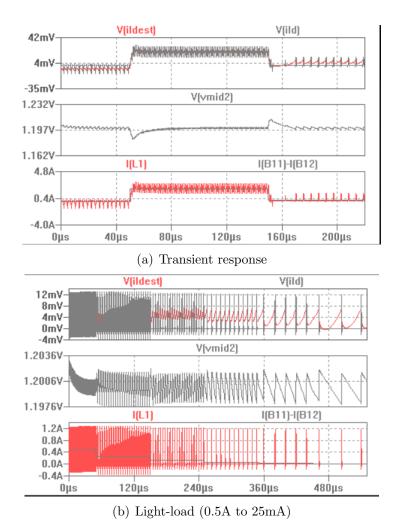

| 2.1  | The bus-to-element DPP topology                              | _ |   | 21 |

| 2.2  | Series Connected Bus to Element DPP using n isolated         | • | • |    |

|      | flyback converters                                           |   |   | 23 |

| 2.3  | Virtual bus-to-element topology using full bridge isolated   |   |   | -  |

|      | converters as DPP converters                                 |   |   | 24 |

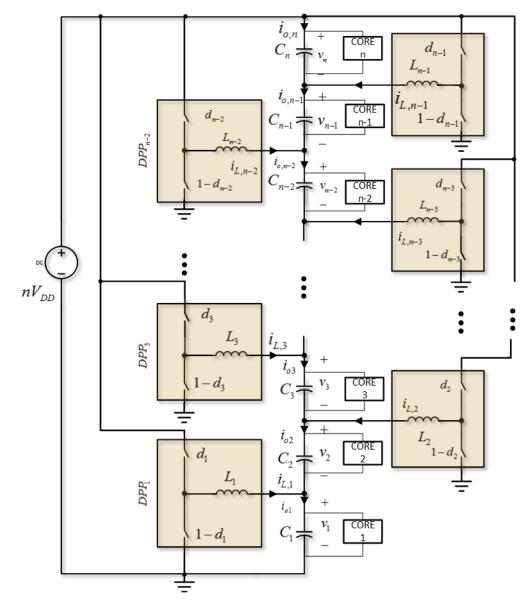

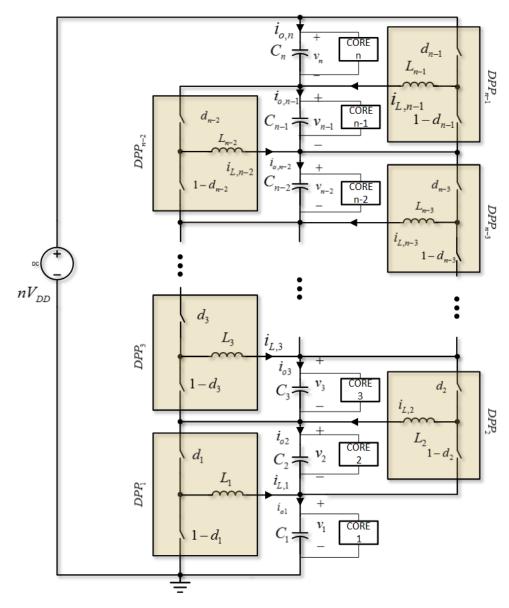

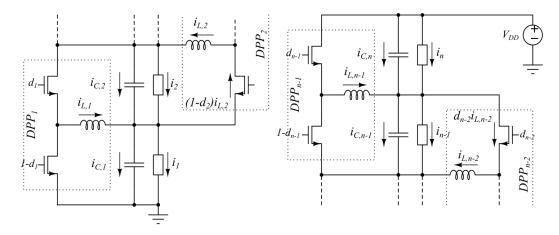

| 2.4  | Element-to-element topology                                  |   |   | 26 |

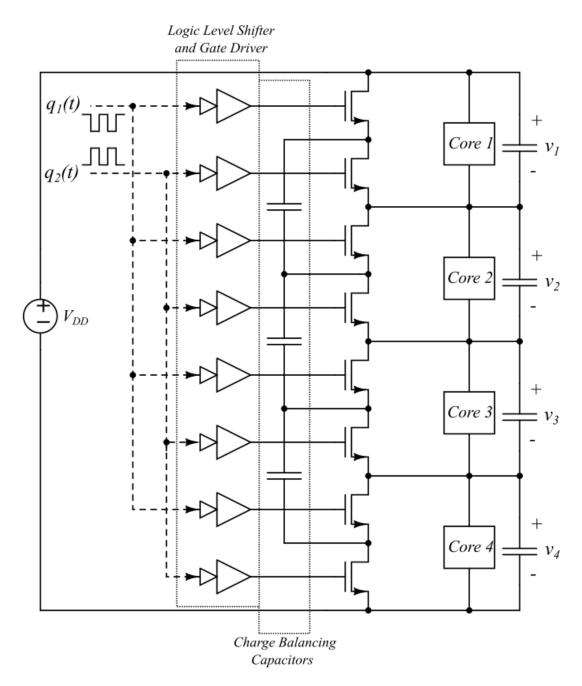

| 2.5  | Switched capacitor voltage balancing circuit                 |   |   | 28 |

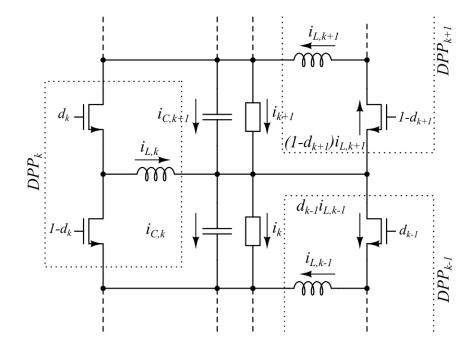

| 2.6  | A single DPP converter with adjacent converter elements .    |   |   | 29 |

| 2.7  | DPP converters at the extremities of the stack               |   |   | 30 |

| 2.8  | DPP converter module                                         |   |   | 33 |

| 2.9  | Frequency response of converters at the middle of the stack. |   |   |    |

|      | n = stack height                                             |   |   | 34 |

| 2.10 |                                                              |   |   | 36 |

| 2.11 | Simulated trend in settling times with increasing number     |   |   |    |

|      | of series-stacked elements                                   |   |   | 37 |

| 2.12 | Hierarchical element-to-element DPP                          |   |   | 39 |

| 2.13 | Balancing current path in element-to-element topology        |   |   | 40 |

|      |                                                              |   |   |    |

| 2.14       | Improvement in transient performance: (a) Element-to-<br>element DPP (b) Hierarchical element-to-element DPP                           | 42         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.1        | High-level schematic of the implemented hardware                                                                                       | 44         |

| 3.2        | DPP board with 3 converters                                                                                                            | 46         |

| 3.3        | Individual DPP converter                                                                                                               | 47         |

| 3.4        | Compensation                                                                                                                           | 48         |

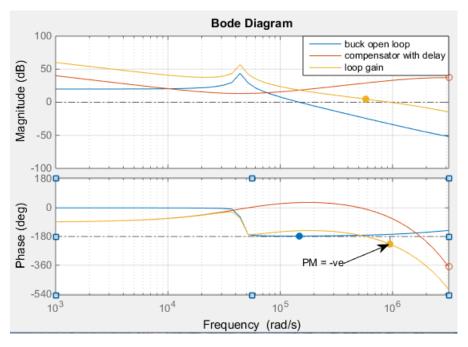

| 3.5        | Delay effect                                                                                                                           | 49         |

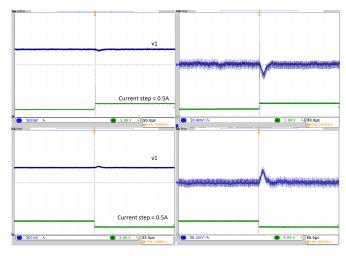

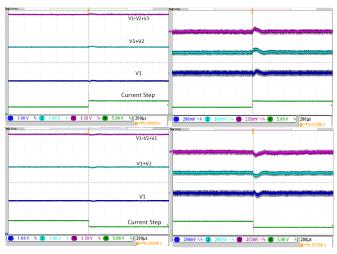

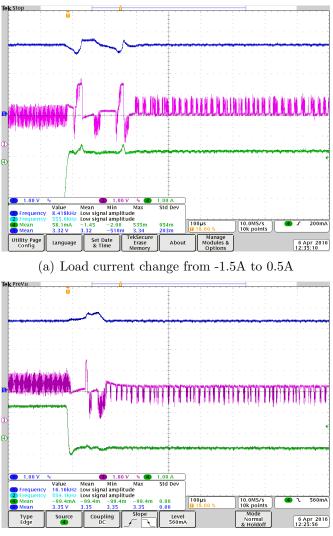

| 3.6        | Transient performance tests for the basic element-to-element topology                                                                  | 50         |

| 3.7        | Transient performance test for the hierarchical topology                                                                               | 50<br>51   |

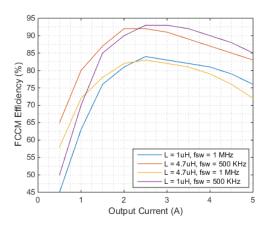

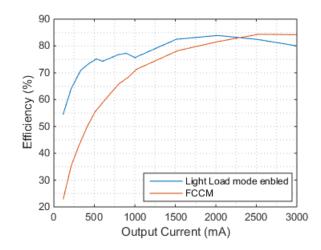

| 3.8        | Individual DPP converter efficiency plot                                                                                               | $51 \\ 51$ |

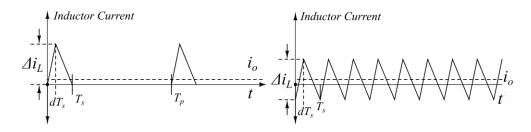

| 4.1        | Single pulse PFM mode (left) and FCCM mode (right)                                                                                     |            |

|            | inductor currents at same average output current                                                                                       | 54         |

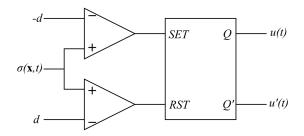

| 4.2        | Sliding mode switching signal generation                                                                                               | 57         |

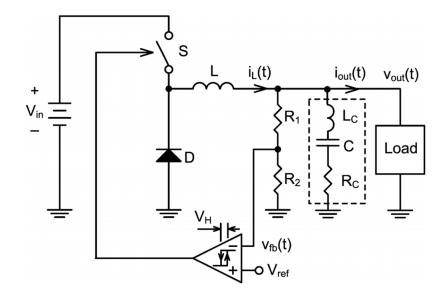

| 4.3        | A buck converter with hysteretic control                                                                                               | 58         |

| 4.4        | DC regulation of hysteretic buck                                                                                                       | 59         |

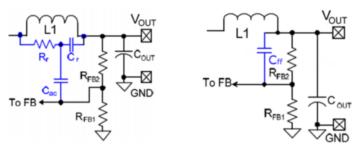

| 4.5        | Current and voltage ripple feedforward                                                                                                 | 59         |

| 4.6        | Droop control of hysteretic buck converter                                                                                             | 60         |

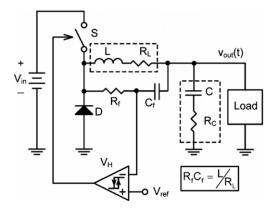

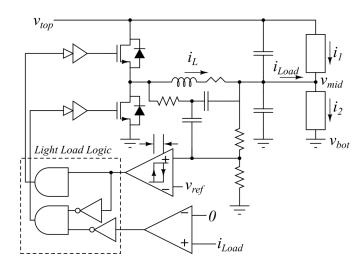

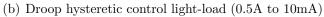

| 4.7        | Bidirectional DPP converter with hysteretic control                                                                                    | 61         |

| 4.8        | Load current estimation of DPP converters                                                                                              | 62         |

| 4.9        | Hysteretic control with load current sensing                                                                                           | 62         |

| 4.10       | Droop controlled DPP                                                                                                                   | 63         |

| 4.11       | Hysteretic droop control                                                                                                               | 64         |

|            | Current hysteretis controlled DPP                                                                                                      | 66         |

| 4.13       | Hysteretic current mode control                                                                                                        | 67         |

| 4.14       | Current hysteretis controlled stack                                                                                                    | 68         |

| 4.15       | Current hysteretis controlled stack - Proportional gain                                                                                | 70         |

| 4.16       | Current hysteretis controlled stack - PI controller                                                                                    | 71         |

| 4.17       | Current hysteretis controlled stack - bidirectional light-load                                                                         | 72         |

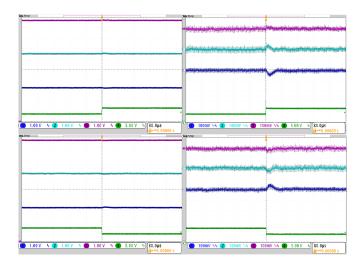

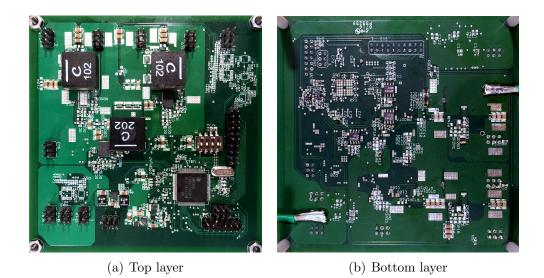

| 5.1<br>5.2 | Hysteretic current mode control hardware setup DPP board with 3 converters                                                             | 74<br>75   |

| 5.3        | Individual DPP converter efficiency plot in FCCM and with light-load mode enabled, $L = 1 \ \mu \text{H}$ , $f_{sw} = 500 \text{ kHz}$ | 76         |

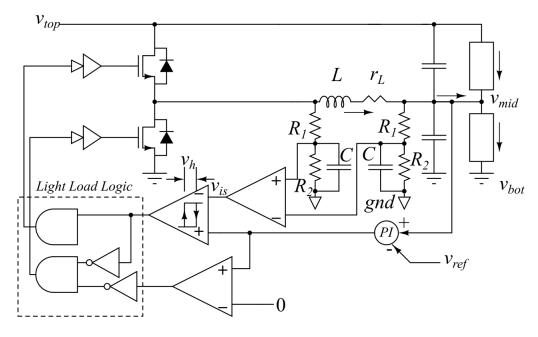

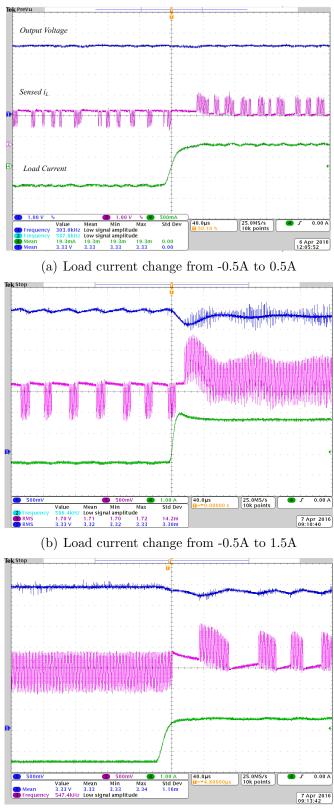

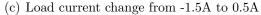

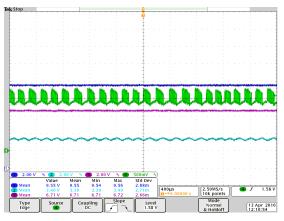

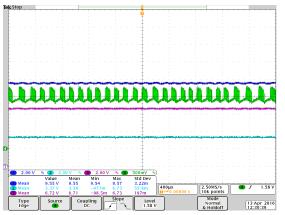

| 5.4        | Bidirectional light-load modes in a single DPP converter                                                                               | 77         |

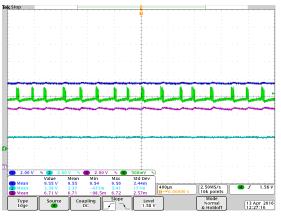

| 5.5        | Transient response of a single converter (bottommost) op-                                                                              | 70         |

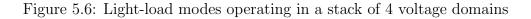

| 5.6        | erating in a stack of 4 voltage domains                                                                                                | 78<br>79   |

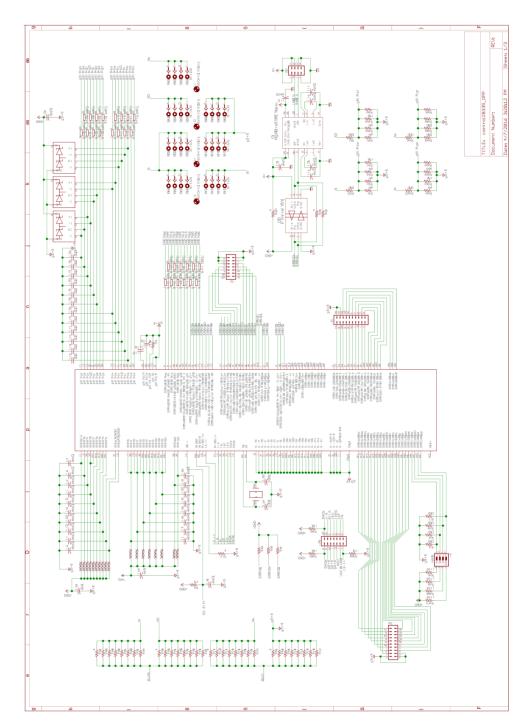

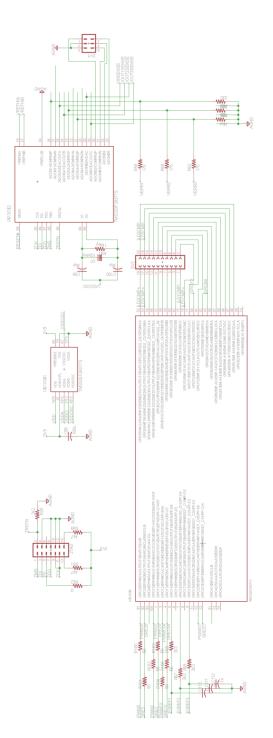

| A.1        | Linear control board for DPP schematic, microcontroller                                                                                | 84         |

| A.2        | Linear control board for DPP schematic, DPP converters                                                                                 | 85         |

| A.3        | Linear control board for DPP schematic, microcontroller supply                                                                         | 86         |

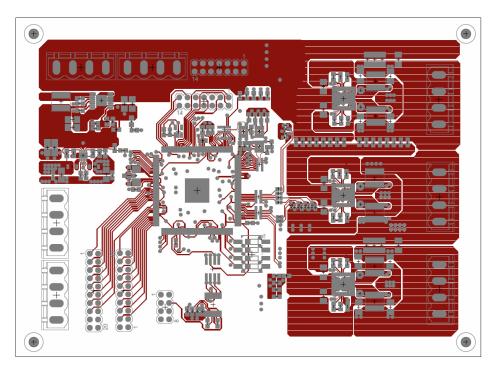

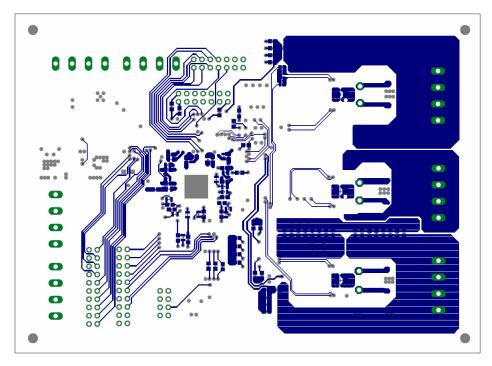

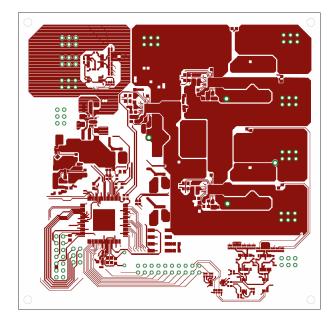

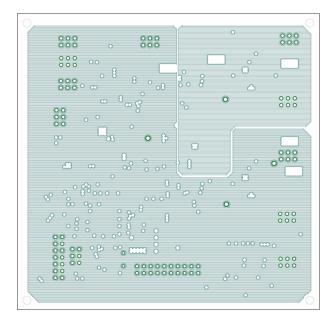

| A.4        | Linear control board for DPP layout, top layer                                                                                         | 87         |

|            | ÷ · • •                                                                                                                                |            |

| A.5  | Linear control board for DPP layout, bottom layer                                       | 87 |

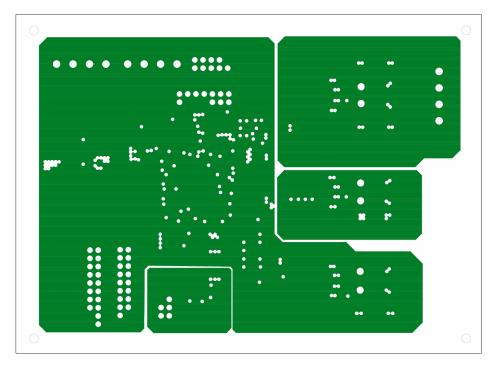

|------|-----------------------------------------------------------------------------------------|----|

| A.6  | Linear control board for DPP layout, layer 2 (gnd planes)                               | 88 |

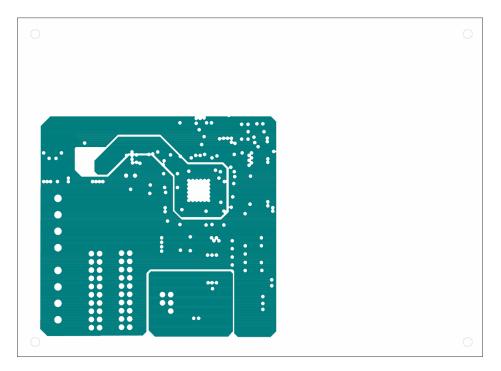

| A.7  | Linear control board for DPP layout, layer 3 (microcon-                                 |    |

|      | troller supply) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 88 |

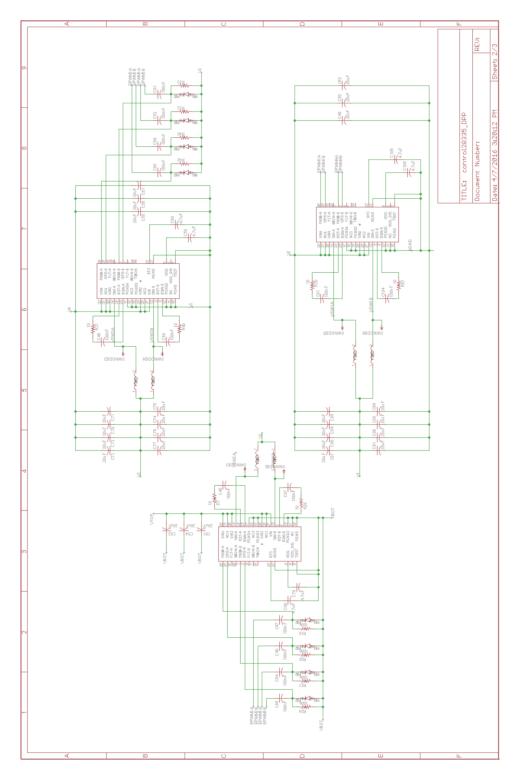

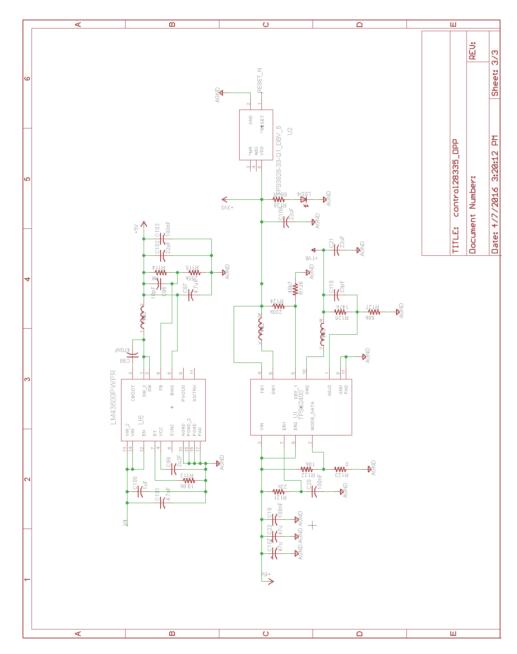

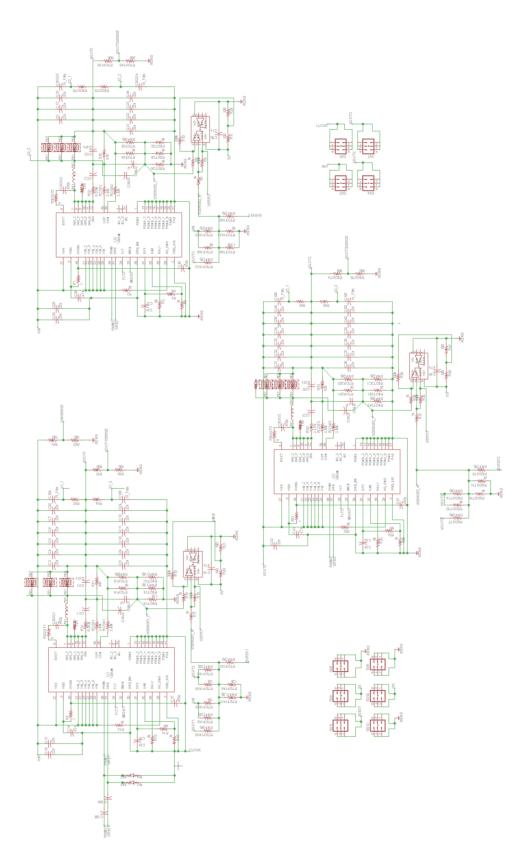

| A.8  | Hysteretic control board for DPP schematic, microcontroller .                           | 90 |

| A.9  | Hysteretic control board for DPP schematic, DPP converters .                            | 91 |

| A.10 | Hysteretic control board for DPP schematic, microcon-                                   |    |

|      | troller supply                                                                          | 92 |

| A.11 | Hysteretic control board for DPP schematic, microcon-                                   |    |

|      | troller supply                                                                          | 93 |

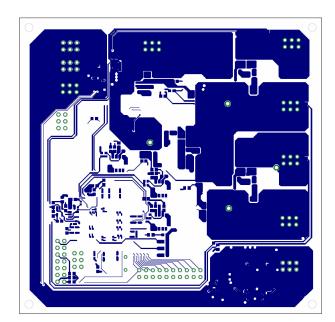

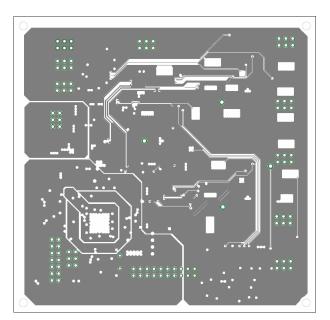

| A.12 | Hysteretic control board for DPP layout, top layer                                      | 94 |

| A.13 | Hysteretic control board for DPP layout, bottom layer                                   | 94 |

| A.14 | Hysteretic control board for DPP layout, layer 2 (gnd planes)                           | 95 |

| A.15 | Hysteretic control board for DPP layout, layer 3 (micro-                                |    |

|      | controller supply)                                                                      | 95 |

|      |                                                                                         |    |

## CHAPTER 1

## THEORY AND LITERATURE SURVEY

#### 1.1 Processor Power Delivery Requirements

Ever since the first integrated circuit was developed, transistors have been growing exponentially ever smaller in agreement with Moore's law. As a direct consequence, computational power of microprocessors has been steadily increasing due to more transistors fitting into the same area. Until the mid 2000s, along with computational power, electrical power consumption of processors had also been steadily increasing (due to operation at increased clock frequencies). Increased power consumption implied increased heat dissipation per unit area, which became a serious limiting factor (processors running at more than 4 GHz were reported but never made it to the market because of low reliability). Power consumption of microprocessors has since then stagnated at around 100 W. However, to continue increasing computational power (the official term is *performance per watt*) of computers, multi-core processors started coming into the picture. Today we have high-end processors for PCs which have 8 or even more cores.

Power consumption and maximum clock frequencies of processors may have stagnated, but scaling of transistors has not stopped. As transistors keep getting smaller, the supply voltages keep decreasing. As a result, power supplies that power today's processors often have to supply more than a 100 A of current at extremely low voltages (as low as 0.7 V). So far the industry has been able to meet supply specifications using multiphase buck converters. However, as the core voltages continue to decrease, power supply designers are approaching a limit where multi-phasing buck converters or multiplying output capacitor count will simply not be able to meet the low-voltage highcurrent requirements of a microprocessor. An alternate series-stacked power delivery architecture to overcome this problem has been proposed before

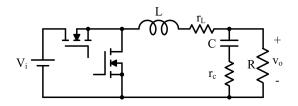

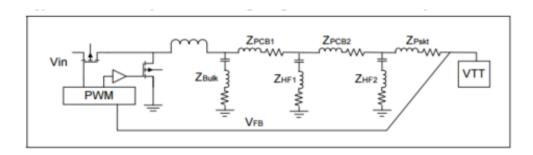

Figure 1.1: Buck converter with parasitic elements

[1]. Here, it has been shown how series-stacking processor cores has several advantages over the usual parallel connected core architecture. In this thesis we first consider the limitations of the parallel connected core architecture (in terms of its power supply requirements). Then we study the dynamics of a series-stacked architecture and develop a control for it, to improve its efficiency and transient performance.

### 1.2 Output Impedance of the Buck Converter

To design a power supply for a microprocessor load we have to take care that the output impedance of the supply is able to match the load. The load, i.e. the digital electronic circuit that forms the processor core, is usually considered to be resistive.<sup>1</sup>

As the voltage requirements of processors scale down while maintaining constant power consumption, the impedances of processor loads tend to go down by a factor of  $\frac{1}{V_{DD}^2}$ . To understand the corresponding impact on the design of power supplies let us take a look into a typical synchronous buck converter with parasitic impedances as shown in Figure 1.1.

The basic operation of the synchronous buck converter is simple [2]. The two switches alternately switch on and off to create a square wave at the

$$P_{dyn} = \alpha C_{dyn} f_{clk} V_{DD}^2 \tag{1.1}$$

The implication of this equation is that if clock frequency does not change during operation then ay CMOS digital circuit can be considered to be a resistive load (dependent on activity factor  $\alpha$ ) from a power supply designer's point of view. Modern processors modulate clock frequency as a function of activity factor so that processing does not slow down for heavy computational loads.

<sup>&</sup>lt;sup>1</sup>Equation 1.1 gives the dependence of Power Consumed by a CMOS digital circuit with activity factor  $\alpha$ , clock frequency  $f_{clk}$  and supply voltage  $V_{DD}$ .  $C_{dyn}$  is a fixed parameter dependent on the number of nodes in the CMOS circuit that undergoes switching during a particular clock cycle.

Figure 1.2: Buck converter averaged model

switching node  $N_{sw}$ . That square wave is filtered by the LC low-pass filter to provide a low-ripple dc voltage at the output terminal. The output voltage can be varied by varying the duty ratio of the square wave generated at the switching node. The output voltage generated if we assume lossless switches and inductor is given by

$$v_{out} = dv_{in} \tag{1.2}$$

This however only tells us about the static (or steady-state) behavior of the buck converter. A dynamical analysis has to be done to understand what the output voltage transients look like when there is a step (or ramp, etc.) change in output current or input voltage occurs. Averaged models are used to model the dc/dc converters as linear circuits [3]. One way to do the averaged modeling for the buck converter is to assume that the voltage at the switching node is  $dv_{in}$  (Figure 1.2).

If we neglect perturbations in the input voltage (i.e.  $v_{in} = V_{in}$ ) it can be easily seen using the impedance divider expression that the transfer function of the output voltage with respect to duty ratio is

$$G_{vd} = \frac{v_o(s)}{d(s)} = \frac{V_{in} \left(1 + Cr_c s + L_c C s^2\right)}{1 + C \left(r_c + r_l\right) s + \left(L + L_c\right) C s^2}$$

(1.3)

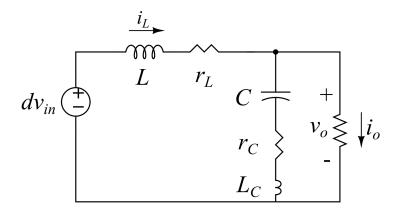

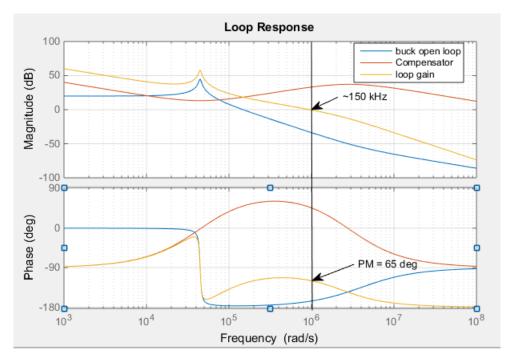

Now that we have a transfer function that defines the relation between output voltage and duty ratio variation we can do a closed loop control to regulate output voltage. Several types of controllers are used for closed loop control of buck converters. The most common among them is the 2pole, 2-zero compensator combined with an integrator. The 2-pole, 2-zero compensator is used to extend the bandwidth of the buck converter and stabilize it by improving its phase margin, while the integrator improves dcgain to remove any steady state error. A typical design using  $L = 5 \ \mu H$ , C = 50  $\mu F$  is shown in Figure 1.3.

Let us now try to find an expression for the output impedance of the buck converter. For simplicity first we find an expression for the open loop output impedance. Since it is open loop we can evaluate the output impedance simply by shorting the input  $(d(s)v_{in})$  at the switching node) and observing the output voltage variation with current injected at the output terminal as shown in Figure 1.2. Following this method and neglecting the series inductance of the capacitor, the output impedance expression turns out to be:

$$Z_{out,ol} = Z_L ||Z_C = \frac{(Ls + r_l)(1 + Cr_c s)}{1 + C(r_l + r_c)s + LCs^2}$$

(1.4)

We can use superposition to find an expression for the closed loop output impedance now. Assume that the feedback law is  $dv_{in} = -H(s)v_o$  which is typical for a voltage mode controller with input voltage feed-forward (an alternative to current mode control for dealing with input voltage transients). With some algebraic manipulations the closed loop output impedance can be shown to be

$$Z_{out,cl} = \frac{Z_{out,ol}}{1 + G(s)H(s)} \tag{1.5}$$

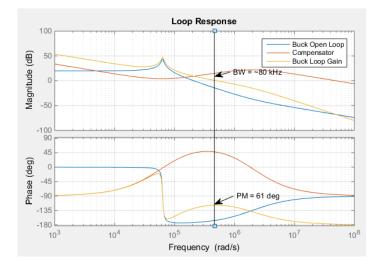

Figure 1.3: Compensation of buck converter

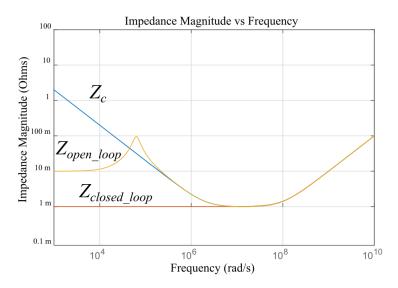

Figure 1.4: Open loop and closed loop output impedance of buck converter under droop control

In this expression the term in the denominator G(s)H(s) is also called the loop-gain in control theory, and typically this term is what determines the bandwidth of the buck converter. At frequencies near and above the crossover frequency of the converter the output impedance of the converter can be approximated to be equal to the impedance of the paralleled capacitor network (Figure 1.4). Below the crossover frequency the output impedance is governed by the loop transfer function. Usually we see that below the crossover frequency, the output impedance decreases with decreasing frequency (with integral control), but controller design such that the output impedance remains constant below the crossover frequency is also considered desirable in certain cases [4], [5]. This type of design is also known as droop control and offers constant output impedance at frequencies lower than the crossover frequency. The magnitude of the constant output impedance determines the deviation of the output voltage from the reference voltage at steady state with load current. This type of control is known as droop control.

Our motive is to decrease closed loop output impedance of the converter without affecting its bandwidth (loop gain crossover frequency- $\omega_{co}$ ). To accomplish that, first we have to make a few simplifying assumptions.

• Consider droop control, i.e. minimum output impedance in closed loop occurs at and below the crossover frequency. This simplifies calculations of output impedance. At the crossover frequency  $\omega_{co}$ , the closed

loop output impedance equals the open-loop output impedance. So we only have to figure out a way to reduce output impedance at the crossover frequency.

- $\frac{1}{\sqrt{LC}} = k\omega_{co}$ , i.e. the frequency of the double pole of the buck converter is a fixed fraction of the loop-bandwidth

- $\frac{\omega_{co}L}{r_l} = Q_L$ , i.e. the quality factor of the inductor at the crossover frequency is fixed, and paralleling of the same component does not affect the quality factor

- $\frac{1}{\omega_{co}Cr_c} = Q_c$ , i.e. the quality factor of the output capacitor is fixed at the crossover frequency

Manipulating the open-loop output impedance expression at the crossover frequency using these simplifying constraints,

$$|Z_{out,ol}| = \frac{1}{C\omega_{co}} \sqrt{\frac{\left(1 + \frac{1}{Q_L^2}\right)\left(1 + \frac{1}{Q_c^2}\right)}{\left(1 - k^2\right)^2 + \left(\frac{k^2}{Q_c} + \frac{1}{Q_L}\right)^2}}$$

(1.6)

So from here we see that the output impedance of a buck converter scales with output capacitance as  $\frac{1}{C}$ . We have already seen before that the output impedance requirement scales with output voltage as  $\frac{1}{V_{DD}^2}$ . So projecting, the output capacitance requirement of a buck converter supplying a processor load will increase with decreasing output voltage; i.e., theoretically if the processor voltage scales down from  $V_{DD}$  to  $\frac{1}{2}V_{DD}$ , then the output capacitance of the buck converter has to be increased to 4 times its original value.

Figure 1.5: Typical buck converter output filter structure with parasitic components [5]

This however is a very optimistic evaluation. In effect an actual power supply supplying the processor load looks like the circuit shown in Figure 1.5. The buck converter is directly connected to some bulk capacitance (usually OSCON type capacitors having relatively high series resistance and inductance compared to ceramic capacitors). The power supply unit is connected to the microprocessor board where ceramic decoupling capacitors  $(Z_{HF1})$  are provided to stabilize any instability present in the output of the power supply unit. We have to keep in mind that the very high currents and extremely low voltages make the drops across the PCB path parasitics  $Z_{PCB1}$ ,  $Z_{PCB2}$ very real issues. After encountering the decoupling capacitors, the power goes to the separate supply voltage pins of the microprocessor. Each of the supply pins (or small clusters of supply voltage pins) has separate ceramic capacitors connected very close to it. These ceramic capacitors (called cavity capacitors) form the final filtering/stabilizing stage  $(Z_{HF2})$ . The impedance  $Z_{Pskt}$  is the effective impedance between the cavity capacitors and the supply pins of the microprocessors. To reduce the impact of this impedance, today's processors often have half or more of their total pin count dedicated to supply and grounding. The large degree of paralleling due to this helps keep the socket impedance in check.

Any practical capacitor will have parasitic resistances and inductances (effective series resistance and inductance) and are modeled as a series connection of a resistor, capacitor and inductor. So in essence a capacitor will behave like a capacitor only below the resonant frequency of the LCR series circuit. Above that, it will behave like an inductor. Paralleling of the same types of capacitors will not change the resonant frequency. It will only reduce the values of impedances at all frequencies. The frequency at which a capacitor or combination of capacitors start behaving like an inductor is known as the breakaway point.

OSCON capacitors are very energy dense in the sense that they can have large capacitances packed into small areas. But they also have significantly large ESR and ESL compared to ceramics. Therefore, OSCON capacitors tend to breakaway (start behaving like inductors) at significantly lower frequencies than ceramic capacitors (at least one decade below ceramics). One possible way obtain large capacitances and still maintain a high breakaway frequency is to connect ceramic capacitors in parallel with OSCON capacitors. (Special care has to be taken to set the ratio of the OSCON capacitor to the ceramic capacitor correctly. Otherwise the paralleling may not prove to be effective at all.)

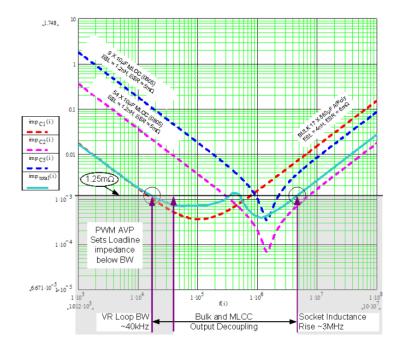

The effective impedances of a particular combination of bulk, decoupling and socket capacitors are plotted in Figure 1.6. The capacitor network impedance with the series parasitic elements  $(Z_{PCB1}, Z_{PCB2}, Z_{Pskt})$  is shown in Figure 1.6 as well.

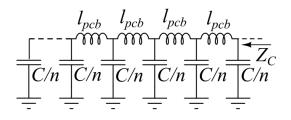

The effect of the series PCB impedance components is to offset the capacitor impedance curves to higher minimum values by adding double zeroes at multiple resonant frequencies near the breakaway frequencies of each types of capacitors (Figure 1.6). To compensate for this increase in output impedance, capacitor values have to be increased further. The impact of these parasitic series impedances is crippling. As more decoupling capacitors are added in parallel to each other in order to reduce the ESR, the effective capacitance network moves closer to a distributed model which can be simplistically represented as in Figure 1.7

It can be shown analytically that the impedance of the network shown in Figure 1.7 approaches a minimum value of  $\sqrt{\frac{L}{C}}$ . So in effect output impedance  $z_{out}$  of the power supply line scales as  $\frac{1}{\sqrt{C}}$  instead of  $\frac{1}{C}$ . This

Figure 1.6: Typical impedance of a composite system of capacitors (bulk electrolytic, MLCC decoupling and MLCC cavity capacitors) - [5]

Figure 1.7: A distributed model approximation for evaluating capacitor impedance in 1.6

implies that the output capacitance requirement varies with supply voltage as  $C \propto \frac{1}{V_{DD}^4}$ . Empirically the capacitance requirement varies with output voltage as a function of  $\frac{1}{V_{DD}^5}$  instead of  $\frac{1}{V_{DD}^4}$  due to capacitance derating effects at lower voltages.<sup>2</sup>

The point of this exercise was to show that supplying microprocessor loads with buck converters as supply voltages decrease (keeping power constant) becomes impractical. The PCB impedances pose a limiting value to the obtainable output impedance from a power supply and after some point increasing output capacitances (or even decreasing the impedance of the inductive network  $Z_L$  by multi-phasing techniques, which we will see later in this chapter) will simply not be able to handle the output impedance requirements. As we have pushed towards lower supply voltages (supply at sub-threshold voltages less than 0.4 V may also become a possibility in the future) the number of supply pins has increased drastically (in order to reduce effective PCB impedance by achieving a high degree of paralleling).

To counter the PCB impedance effects at low voltages and high currents, most microprocessor manufacturers have now started to integrate buck converters inside the chip itself. This way the processor can be supplied at a relatively high voltage (hence reducing the output impedance requirement of the converter that supplies power to it) and the core voltage can be internally generated by high-frequency integrated buck converters. The logic behind integrating the buck converters on chip is that the output impedance requirement of the integrated converters is significantly lower because there are multiple converters that supply different cores. This architecture of power

$<sup>{}^{2}</sup>C \propto \frac{1}{V_{DD}^{5}}$  is an overly pessimistic estimation which is approached when an impractical number of decoupling capacitors are paralleled in an attempt to reduce the effective ESR of the network. The actual factor at which capacitance requirement decreases with supply voltage is somewhere between  $\frac{1}{V_{DD}^{5}}$  and  $\frac{1}{V_{DD}^{3}}$

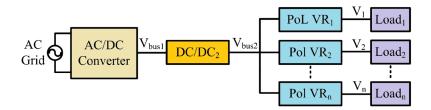

Figure 1.8: Intermediate bus architecture (IBA)

delivery is known as the intermediate bus architecture (IBA), shown in Figure 1.8.

Several other advantages of this IBA power delivery are evident. It has been shown that system-level energy/efficiency optimization is possible by regulating the core voltage as a function of activity factor of each core. If a certain core is operating at a low activity factor then its supply voltage can be reduced and operated at a lower frequency than other cores. This reduces the power consumption of that core without compromising throughput. This is called dynamic voltage scaling (DVS). Modern microprocessors use DVS very frequently. Processors usually identify the activity factor and appropriately adjust their clock frequency (low clock frequency when activity factor is low and vice versa) to maintain a constant throughput. Then they send out voltage identification (VID) bits to the voltage regulator modules to appropriately increase or decrease the supply voltage. With IBA power delivery the voltage levels of different cores can be adjusted independently of each other. This has been proven to be very useful for power consumption optimization. However, efficiency of integrated converters tends to be low because of high frequency switching. So, while we are saving power by DVS we are also losing power because of lower overall efficiency. So the benefits of this architecture are limited.

What we should take away from this development is that supplying power to the chip at higher voltages is always more desirable than supplying lower voltages (and correspondingly higher current). This motivates us to think about the possible gains that we may see if we connect processor cores in series instead of in parallel as is the usual practice. We will discuss the possibilities of series connection in more detail in section 1.3.

Now, let us take a look into the losses in buck converters. Consider the same simple model of the buck converter as in Figure 1.1. Conduction losses

during steady state operation are incurred mainly in the inductor and the two switches. Neglecting inductor current ripple,

$$P_{cond} = < i_l >^2 (r_L + r_{sw}) \tag{1.7}$$

Usually as the voltage scales down and current scales up, to avoid inductor saturation phases are added in the buck converter (Figure 1.9)

As a consequence of paralleling several buck converters, the effective  $r_L$ and  $r_{sw}$  scale down linearly with voltage (increase in current output implies more phases in the multi-phase buck converter). But since the conduction losses are dependent on  $i_L^2$ , the conduction losses in the converter increase as a function of  $\frac{1}{v_o}$ . The switching losses in the converter increase linearly with the number of phases because of additional switches. That is also a linear function of  $\frac{1}{v_o}$ , so losses in the converter increase as a function of  $\frac{1}{v_o}$ . Therefore, the efficiency of power converters will decrease with decreasing output voltage. However, better switching devices and inductor core materials are becoming readily available day by day and as such decreasing efficiency is not as big a limitation as the capacitor requirement for down-scaling of output voltage. Multi-phasing of buck converters also has a few other significant advantages that will be discussed in the next section.

Now suppose we have multiple PoL converters supplying different cores from the output of the multi-phase buck as seen in the IBA. The net efficiency of this combination will mainly be governed by the most inefficient of the power conversion stages (usually the PoL conversion stage because of its high frequency). We will see later in section 1.4 why the series connection of cores has a clear advantage here.

## 1.3 Transient Response Improvement, Efficiency Improvement

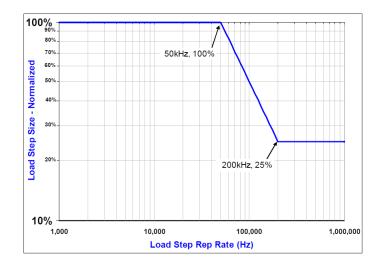

With processors now incorporating various power saving modes and voltage scaling, output impedance is not the only area requiring improvement for power supplies. According to the latest Intel VRM specifications [5] a power supply designer can now expect step load changes from 0 to full load current at a repetition rate of 50 kHz (Figure 1.10).

Figure 1.9: Multi-phase buck

The implication here is that the output voltage should stabilize within the very short periods (20  $\mu s$  for a transition between 10% to 100% of full load) as specified by the repetition rates in the plot. The settling time of a buck converter is governed by the closed-loop bandwidth of the voltage regulator. Usually the obtainable closed-loop bandwidth for buck converters using a 2-pole, 2-zero compensator is a fraction (1/5 or less) of the switching frequency. The best transient response (bandwidth) that linear control can provide has been effectively studied by many researchers. One such instance is [6], although parameter variation plays a big role as we try to increase bandwidth using this approach. Also estimating/sensing capacitor current and utilizing it in feedback control have proven to be effective in improving bandwidth [7].

Linear control of power supplies in general does not give us optimal response times for transients and designers often end up overusing capacitors to keep transient voltages within limits. Time-optimal response of a buck converter (or bang-bang control) has been studied and targeted for many years. The effective bandwidth achieved with time-optimal response is nearly equal to the switching frequency of the converter while the bandwidth usually obtained using linear control is only a fraction of the switching frequency. Current Mode control by using carefully matched or adaptive ramp compensation can provide near optimal results. Nonlinear control methods have been tried out successfully and are very useful as they provide uniform and predictable transient response to all kinds of load steps. A geometric method for obtaining near null (optimal) and null response (i.e. total negation of output voltage transient with load current stepping) has also been tested in the past [8], [9]. The latter method providing null response requires augmentation that makes the converter inefficient during transients. In a converter that is supplying fast varying loads such as microprocessors these are not very practical to implement.

Improving the efficiency of microprocessor power supplies has been studied mainly in the form of improving light-load efficiency. Microprocessor power supplies are almost exclusively made of multiphase buck converters (Figure 1.9). While all the phases available need to be operational at high current load to avoid inductor saturation, at lighter loads the multiple phases only cause increased switching losses. To improve light load efficiency, usually phases are shut down (phase-shedding) at lighter loads. Switching signals to the n phases of the multiphase buck converter can be interleaved so that the current ripples in the individual phases are complemented and lowered (or even eliminated) when they add up at the output capacitor. This helps in significantly lowering the switching noise in the output of the buck converter.

Figure 1.10: Transient repetition rate [5]

Figure 1.11: Coupled inductor 2-phase buck converter

At lighter loads, when multiple phases have been shed the output switching voltage noise increases, which may or may not be tolerated by the VRM restrictions [10]. Transient behavior due to shedding of a phase also has to be taken into account. Another slightly different and more effective approach to light load efficiency improvement in multiphase buck converters has been studied in [11]. However, this variation is more suitable for lower power applications where current sharing is not the primary reason for using a multiphase converter. A similar technique more suitable for higher power has been proposed in [12].

Improving transient response of power supplies has proven to be significantly more challenging with increasing step load requirements. The path to improving settling times of buck converters in general is to increase the number of phases so that individual phases have to handle smaller step currents. Decreasing the inductance value to improve settling times of converters is not a good solution since the inductors will saturate at lower average currents. An interesting solution to this problem was developed by coupling the output inductances as shown in Figure 1.11. Initially proposed for two phase converters with mutually coupled inductances [13], the coupling action enables the inductor current to slew at a rate inversely proportional to the leakage inductance of the coupled inductors (when the two phases are not interleaved) while rejecting current ripple proportionally to its magnetizing inductance when the phases are separated by  $180^{\circ}$ . A number *n* of these two phase coupled units can be paralleled and interleaved to form a 2n phase solution for a modern VRM. The idea has been extended to more than two phase converters by use of multi-phase coupled inductors with ladder type cores and has been shown to provide exceptional transient performance [14]. This modified multiphase buck converter is less prone to inductor current mismatches and the inductor also saturates at a higher average current due to lower ripple. Also, increased ripple rejection suggests that the switching frequency of the phases can be reduced to an large extent to improve efficiency substantially as has been mentioned in [14].

#### 1.4 Series Connected Power Delivery and DPP

From the discussion on output impedance of buck converters, we can infer that maintaining constant power delivery at lower and lower voltages becomes exponentially difficult owing mainly to PCB impedances and parasitic inductances and resistances of capacitors. As supply voltages are expected to fall lower (even sub-threshold operation at supply voltages as low as 0.4V is becoming more probable in the near future) we expect to see output impedance of converters to approach an asymptotic limit when increasing capacitance and number of supply pins may still not be enough to cope with the output impedance requirements of new processors. However, as supply voltages decrease and as we become able to multiply transistor count in upcoming processors, we have seen an increase in core count of processors and we can expect to see processors with more cores (16 or more) in the future. Since clock speeds have reached a certain limit, increasing core count is now the way to improve processing power (performance per watt) of processors. This opens up the possibility of connecting processor cores in series rather than in parallel.

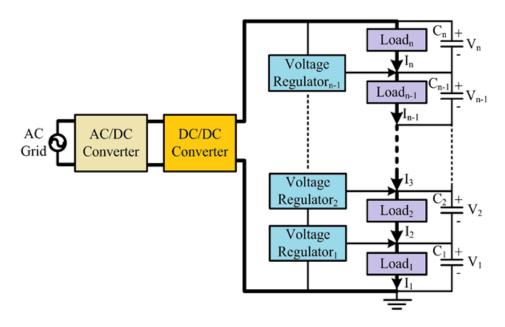

Since we want to independently control the supply voltages of each core, we have to use additional power converters that supply the difference in currents between adjacent cores at each node (Figure 1.12). One may argue that the total converter count remains the same as the IBA architecture of Figure 1.8, but a closer look explains why the series architecture is better than the IBA architecture in terms of power delivery efficiency. The intermediate dc-dc buck converters of both the architectures have nearly the same efficiencies. And the PoL converters that regulate the core voltages also have

Figure 1.12: Series-connected power delivery

the same efficiency, but the PoL converters that regulate the stack voltages only process a small fraction of the net power of the CPU in the case of the series architecture. In the IBA architecture the PoL converters process the entire power of the CPU as demonstrated in Figure 1.13.

CPU core activity balancing has been a software focus of major processor and operating system researchers since the advent of multicore CPUs. If we take advantage of that fact and assume that at any time the PoL converters are not going to have to process more than x percent of the net processor power, then the minimum efficiency of the power delivery will be given by  $\eta_{DPP} = \frac{\eta_{rect}\eta_{mpb}\eta_{int}}{x+(1-x)\eta_{int}}$ . Compared to the IBA, whose efficiency can be written as  $\eta_{IBA} = \eta_{rect}\eta_{mpb}\eta_{int}$ , this is a very significant improvement. This expression validates the fact that if the activity factors of all the cores are matched exactly, then the relatively lower efficiency of the final PoL stage will not be a factor in the net power delivery efficiency of the system.

Our original motivation, managing output impedance without having to increase capacitances unreasonably, is also addressed under certain reasonable assumptions. The capacitance requirements at each node are mainly defined by the current consumption of each core. Under the assumption that core count increases proportionally with decrease in voltage, we see that net capacitor requirement will also increase proportionally  $\left(\frac{1}{V_{DD}}\right)$  with decrease

Figure 1.13: IBA vs. series-connected power delivery: The architecture shown at the top is the integrated bus architecture (IBA) and the lower one is a high level diagram of the series-connected power delivery architecture.

ing voltage unlike the discussion in section 1.2 where capacitance requirement was shown to increase at least as a function of  $\frac{1}{V_{DD}^2}$ . An additional advantage of using series connected power delivery is that dynamic voltage scaling of processor cores is implicitly possible.

Series connection or stacking is not a new concept. Differential power processing (DPP) is an efficient way to implement series stacking and also has been studied in the past under different names (partial power processing, charge recycling etc.). Series connection of solar panels using DC optimizers [15] is a popular solution for MPPT tracking for a series connection of a stack of photovoltaic panels. The series-connected solution with DPP [16] however, has been shown to be more efficient than the DC optimizer solution. The concept of DPP was also used for voltage balancing of battery systems. An example of this is the series connected battery charger proposed by Brainard [17]. Here a cascade of inverting buck-boost converters were used to equalize the voltages of a series battery string while charging the batteries. This circuit is the basis of the circuit we later use as voltage regulators for processor core voltage regulation. A switched capacitor method for charge balancing of a series connected string of batteries, which also relates well with the concept of DPP, was proposed by Pascual and Krein [18].

Series connected power delivery for digital loads is a much more recent concept and so far it has shown a lot of promise. The main applications have come up in the area of power delivery to data centers. In one application [19], the load balancing has been done entirely in software so that the external converters that process the differential powers between adjacent servers are not needed at all. Although this is what we should be targeting, it is somewhat unrealistic in general. Distributing the huge amount of computational load equally among all servers itself is a significant challenge. However, we still can achieve relatively small mismatches by following a less stringent computational load distribution and allowing the differential power processing converters to process a small amount of power. The results obtained here [20] confirm that extreme efficiencies can be achieved by this series power delivery scheme.

Compared to series-connected power delivery for server systems, research on series power delivery in processor cores has been much more limited due to the apparent difficulty in setting up test systems. Deciding on the level (motherboard level or digital circuit level) at which series stacking is to be done is a challenge since processors are not the only components on the board and the voltage levels of all units have to be compatible. An early result using multipliers as digital loads and low dropout regulators (LDOs) as the DPP voltage regulators has shown that series power delivery is indeed possible and can meet necessary voltage regulation specifications [21]. As seen here, LDOs seem to be a good choice for the DPP converters because of their excellent bandwidth and input-to-output noise rejection but they tend to be inefficient. Typically if the supply voltage of each core is to be equalized then the LDOs will be only 50% efficient (ideally). This makes LDOs not suitable for high power processor cores where small relative computational mismatches can lead to significant amounts of injected currents at each node. A more efficient solution can be achieved by replacing LDOs with switchmode power converters. As always there is an efficiency-bandwidth trade-off here. In [22] several architectures have been proposed that can be used to successfully achieve voltage regulation of a series stack of processor cores.

A more recent development in this area is the use of switched capacitor converters for voltage regulation [23]. Since the power processing requirement of the DPP converters is quite small, switched capacitor converters can be easily used for voltage regulation of the intermediate nodes. Improving power processing capability and efficiency of power conversion by using soft charging [24] can serve to improve both the power processing capacity and efficiency of power delivery. However, switched capacitor power delivery only proves effective if voltage equalization is our goal (and voltage droop is acceptable). More research has to done on switched capacitor DPP topologies before the advantages of voltage scaling are not compromised when using switched capacitor circuits for stack voltage regulation.

## CHAPTER 2

## DPP FOR PROCESSOR POWER DELIVERY

### 2.1 Selection of Topology

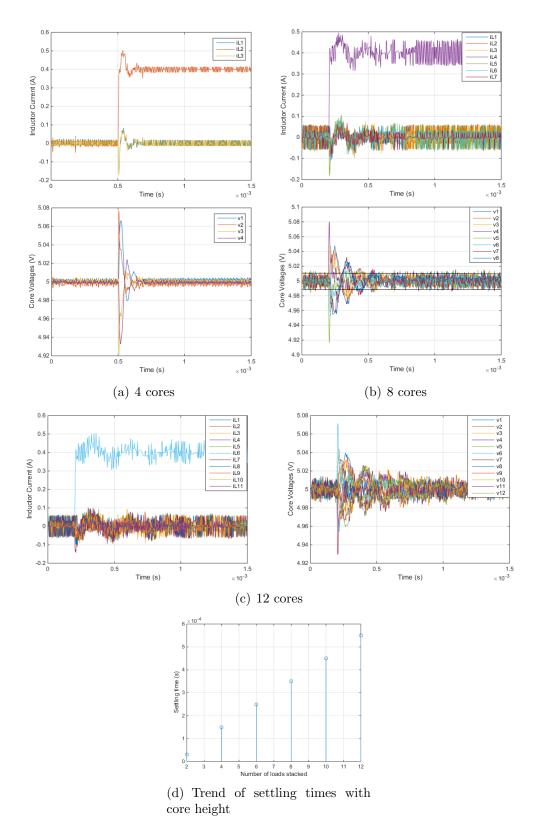

The general structure for series-connected power delivery has been shown in Figure 1.12. However, there are several different topologies that can be used for actually implementing the voltage regulators that process differential current between the different loads. All these topologies are fundamentally different in the way they transfer power to the load. Selecting the topology for a particular series-connected application depends on which parameter we are looking to optimize. First we look into the bus-to-element connected topology. Then we will look into the element-to-element topology which is less intuitive compared to the former. After that we will discuss the motivation for selection of the element-to-element topology for our processor core voltage regulation application.

#### 2.1.1 The Bus-to-Element topology

The bus-to-element architecture transfers energy between the series elements and the main bus. A virtual bus or other storage element could also be used instead of the main bus. Various topologies and control strategies can be implemented with this architecture. The main benefit of this architecture is in the independence of converter states. A disadvantage is that the components have to be rated for the entire bus voltage. It is possible to have n or n-1 bus-to-element differential converters depending on converter topology and system objectives. One implementation of the bus-to-element architecture is shown in Figure 2.1. The average current provided by the differential converters can be determined by applying KCL at the intermediate voltage nodes.

The relation between the domain voltages and the duty ratios of the converters can be evaluated as

$$D_1V_{stack} = V_1$$

$$D_2V_{stack} = V_1 + V_2$$

$$D_3V_{stack} = V_1 + V_2 + V_3$$

$$\vdots$$

$$D_{n-1}V_{stack} = V_1 + V_2 + V_3 + \dots + V_{n-1}$$

where

$$V_{stack} = V_1 + V_2 + V_3 + \dots + V_n \tag{2.1}$$

With the bus-to-element converters, the steady state current equation for series load elements is simply

$$I_{L,k} = I_{o,k} - I_{o,k+1} \tag{2.2}$$

As we see the duty ratios of the individual converters in general decrease from high values at the top to low values at the bottom of the stack. If the stack has a large number of elements, the converters have to be designed with different values of inductances and output capacitances to maintain the same bandwidth at each node. Component sizing to ensure the same bandwidth of each converter becomes a problem as the number of elements in the stack increases.

To get around this particular disadvantage (i.e. to improve modularity and hence increase scalability) two particular modifications to this topology have been suggested. A very promising architecture uses n flyback converters (Figure 2.2), as suggested in [25]. Another similar topology that is derived from this topology is the virtual bus-to-element topology shown in Figure 2.3 [26]. Both of these topologies use n balancing converters as opposed to n-1, which may suggest that efficiency is compromised with respect to the original bus-to-load topology. However, a careful analysis done in [25] and [26] proves that the converters themselves are prone to process less differential power in the two isolated topologies.

Figure 2.2: Series connected bus-to-element DPP using n isolated flyback converters [25]

Figure 2.3: Virtual bus-to-element topology using full bridge isolated converters as DPP converters

### 2.2 The Element-to-Element Topology

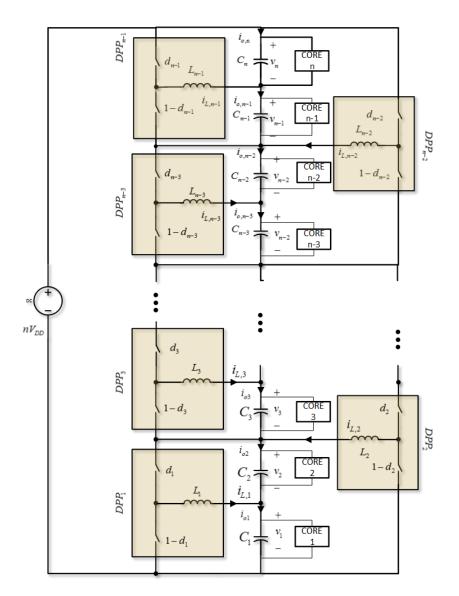

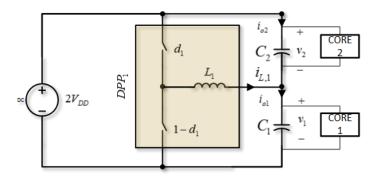

A slightly different topology for voltage regulation of a series stack is the element-to-element topology shown in Figure 2.4.

The element-to-element architecture focuses on local converters that transfer energy between neighboring nodes. This architecture shown in Figure 2.4 has its differential converters in a buck-boost topology. The advantage of this approach is that the differential converters can be locally controlled and component voltage ratings can be comparatively low. The drawback is that the converter states are not independent. The inductor current of one DPP converter is dependent on the inductor currents flowing in the adjacent converters. By applying KCL at each node The steady state inductor currents and mismatch currents are observed to be related by

$$\begin{bmatrix} 1 & -(1-D_2) & 0 & \dots & 0 & 0 \\ -D_1 & 1 & -(1-D_3) & \ddots & \vdots & \vdots \\ 0 & \ddots & \ddots & \ddots & 0 & 0 \\ \vdots & \ddots & -D_{n-3} & 1 & -(1-D_{n-1}) & 0 \\ 0 & \dots & 0 & -D_{n-2} & 1 & 0 \\ 0 & \dots & 0 & -D_{n-1} & 1 \end{bmatrix} \begin{bmatrix} I_{L,1} \\ I_{L,2} \\ \vdots \\ I_{L,n-2} \\ I_{L,n-1} \\ I_n \end{bmatrix} = \begin{bmatrix} I_1 - I_2 \\ I_2 - I_3 \\ \vdots \\ I_{n-2} - I_{n-1} \\ I_{n-1} - I_n \\ I_n \end{bmatrix}$$

$$(2.3)$$

The converters can be interchangeably considered to behave as buck converters (stepping down  $v_{k+1} + v_k$  to  $v_k$ ) or boost converters (converse of the buck) or buck-boost converters (converting  $v_{k+1}$  to  $v_k$ ). The relation between the duty ratios and the domain voltages can also be expressed as follows:

$$\begin{aligned} \frac{v_1}{v_2} &= \frac{D_1}{1 - D_1} \\ \frac{v_2}{v_3} &= \frac{D_2}{1 - D_2} \\ \frac{v_3}{v_4} &= \frac{D_3}{1 - D_3} \\ \vdots \\ \frac{v_{n-1}}{v_n} &= \frac{D_{n-1}}{1 - D_{n-1}} \end{aligned}$$

Although the coupling of inductor currents poses a challenge in implement-

Figure 2.4: Element-to-element topology

ing closed loop control (as we are going to see later on in this chapter) the lower voltage ratings of the converter switches give this topology an advantage over the bus-to-element topology. The lower voltage ratings enable us to switch at high frequencies, lowering the inductor requirement for each DPP converter and improving bandwidth of the DPPs.

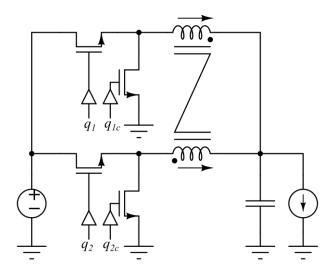

As we have mentioned before, selection of topology is largely application dependent. For example differential power processing for optimizing energy output of a series-connected array of solar panels calls for the element-toelement topology. The wide area over which panels are distributed makes it impractical to use the bus-to-element topology. Topology selection also depends on the level at which we want to do differential power processing. If we are connecting a rack of server loads in series, the power supply and the differential voltage regulation circuitry cannot be limited to a single board. Also, the comparatively large load and voltages suggest that we have to use a topology in which the DPPs process minimum power for a given degree of mismatch. A comparative analysis of the power processed by different topologies given a limit on the amount of mismatches between consecutive elements of the stack has been done in [25]. This shows that the isolated busto-load topology has a clear advantage in the amount of power processed. So isolated bus-to-load (or virtual bus-to-load) architectures find their application in rack level voltage regulation by DPP. For board-level applications like ours, the motive is to achieve fast transient responses and maintain very stringent voltage regulation. High-frequency on-chip DPP converters would be an ideal solution for our case. The element-to-element topology with buck-boost converters is a good choice for board-level DPP because of lower switch voltages. A switched capacitor equivalent of the element-to-element topology is also possible. Figure 2.5 shows a switched capacitor circuit that can be used for voltage balancing of a series stack. This topology is a variant of the series stacked battery charge balancing circuit proposed in [27] and shares the advantages of the element-to-element topology with buckboost converters in terms of modularity and scalability. However, it is only suitable for low-power processor stacks because of its voltage droop characteristics (or cases where droop is a requirement). Further research is needed before the switched capacitor topology becomes an attractive solution for regulating supply voltages of a series stack of processor cores. A successful attempt to improve power density and efficiency of the switched capacitor

Figure 2.5: Switched capacitor voltage balancing circuit

ladder so that higher mismatch currents can be processed has been made by using a resonant ladder converter in [28]. The resonant switched capacitor ladder was used to regulate voltages of a series stack of 4 BeagleBone Black servers.

However, to implement a system of DPP converters for voltage regulation of a series stack of processor cores we have to study the system in more detail. Conventional multi-phase buck converters that supply modern processors have been modeled quite rigorously in the past. Averaged models of buck converters have been studied and methods to design linear control to improve their bandwidth have been researched since the advent of the first CPUs. To properly realize the benefits and consider the feasibility of using DPP to regulate core voltages, we have to study the dynamics of the element-toelement topology supplying a series string of processor loads [29].

## 2.3 Dynamics of the Element-to-Element Topology

To study the dynamics of the system, first we have to make a few simplifying assumptions. For simplicity we are going to assume that the core voltages

Figure 2.6: A single DPP converter with adjacent converter elements

are to be equalized. Although during actual operation we want the core voltages to be independently controlled according to the activity level of the core, this assumption has its validity. During actual operation usually the computational load of the processor is more or less equally distributed across all cores, so the voltage requirements of all cores rise or fall in close correlation with each other. Therefore, when we connect cores in parallel we expect the stack voltage to go down during low computational load and the differential power processing units will simply operate to equalize the core voltages. Now with voltage equalization in mind let us try to model the DPP system. Figure 2.6 shows a part of the entire stack from Figure 2.4.

Writing down the KCL equation at node N, we have

$$i_{c,k+1} + i_{k+1} - d_{k-1}i_{L,k-1} + i_{L,k} - (1 - d_{k+1})i_{L,k+1} - i_k - i_{c,k} = 0 \qquad (2.4)$$

Now recollecting  $C\frac{dv_c}{dt} = i_c$  as the relation between capacitor voltage and current for an ideal capacitor and substituting  $\Delta v_k = v_{k+1} - v_k$ , we have

$$C\frac{d}{dt}\Delta v_k = d_{k-1}i_{L,k-1} - i_{L,k} + (1 - d_{k+1})i_{L,k+1} - (i_{k+1} - i_k)$$

(2.5)

This equation is valid for all nodes except those at the two extremities of the stack. As seen from Figure 2.7, for the bottommost and topmost nodes we have respectively

Figure 2.7: DPP converters at the extremities of the stack

$$C\frac{d}{dt}\Delta v_{1} = -i_{L,1} + (1 - d_{2})i_{L,2} - (i_{2} - i_{1})$$

$$C\frac{d}{dt}\Delta v_{n-1} = d_{n-2}i_{L,n-2} - i_{L,n-1} - (i_{n} - i_{n-1})$$

(2.6)

This complete set of n-1 equations can now be linearized about operating points  $i_{L,k} = I_{L,k} + \hat{i}_{L,k}$ ,  $d_k = D_k + \hat{d}_k$  and  $\Delta v_k = \Delta V_k + \Delta v_k$ . Also if we neglect perturbations in the mismatch currents  $(i_{k+1} - i_k)$ , then the above set of Equations 2.5 and 2.6 are simplified as

$$C\frac{d}{dt}\hat{\Delta v_{1}} = -i_{L,1} + (1 - D_{2})i_{L,2} - \hat{d_{2}}I_{L,2}$$

$$C\frac{d}{dt}\hat{\Delta v_{k}} = D_{k-1}i_{L,k-1} - i_{L,k} + (1 - D_{k+1})i_{L,k+1} + \hat{d_{k-1}}I_{L,k-1} - \hat{d_{k+1}}I_{L,k+1}$$

$$C\frac{d}{dt}\hat{\Delta v_{n-1}} = D_{n-2}i_{L,n-2} - i_{L,n-1} + \hat{d_{n-2}}I_{L,n-2}$$

(2.7)

Apart from this set of equations there is another set of equations that define the inductor current dynamics in terms of duty ratios and domain voltages. Writing down those equations from Figure 2.6 we have

$$L\frac{di_{L,k}}{dt} = d_k v_{k+1} - (1 - d_k)v_k \tag{2.8}$$

As described before, we have a simplifying assumption that voltage equalization is our objective. Because of that we have the nominal operating point of the duty ratio of the DPP converters at  $D_k = \frac{1}{2}$  (for loss-less converters). Under this assumption, the above nonlinear set of equations reduces to

$$L\frac{d\hat{i}_{L,k}}{dt} = \frac{1}{2}\hat{\Delta v}_k + \hat{d}_k \left(V_{k+1} + V_k\right)$$

(2.9)

We can now write the complete set of 2(n-1) equations in state space form as

$$\dot{\mathbf{x}} = A\mathbf{x} + B\mathbf{u} \tag{2.10}$$

where the state and input matrices A and B are given by

$$\mathbf{x} = \begin{bmatrix} \Delta \hat{v}_1 & \Delta \hat{v}_2 & \dots & \Delta \hat{v}_{n-1} & | & \hat{i}_{L,1} & \hat{i}_{L,2} & \dots & \hat{i}_{L,n-1} \end{bmatrix}'$$

$$\mathbf{u} = \begin{bmatrix} \hat{d}_1 & \hat{d}_2 & \hat{d}_3 & \dots & \hat{d}_{n-1} \end{bmatrix}'$$

$$A = \begin{bmatrix} 0 & 0 & \dots & 0 & | & -\frac{1}{C} & \frac{1}{2C} & 0 & \dots & 0 \\ 0 & 0 & \dots & 0 & | & \frac{1}{2C} & -\frac{1}{C} & \frac{1}{2C} & \dots & 0 \\ 0 & 0 & \dots & 0 & | & 0 & \frac{1}{2C} & -\frac{1}{C} & \dots & 0 \\ \vdots & \vdots & \ddots & \vdots & | & \vdots & \vdots & \ddots & \ddots & \frac{1}{2C} \\ 0 & 0 & \dots & 0 & | & 0 & 0 & 0 & \frac{1}{2C} & -\frac{1}{C} \\ \hline & & & & & & & & & & \\ -\frac{1}{2L} & 0 & \dots & 0 & | & 0 & 0 & 0 & \dots & 0 \\ 0 & \frac{1}{2L} & \dots & 0 & | & 0 & 0 & 0 & \dots & 0 \\ \vdots & \vdots & \ddots & \vdots & | & \vdots & \vdots & \ddots & \ddots & \vdots \\ 0 & 0 & \dots & \frac{1}{2L} & | & 0 & 0 & 0 & \dots & 0 \end{bmatrix}$$

(2.11)

$$B = \begin{bmatrix} 0 & -\frac{I_{L,2}}{C} & 0 & \dots & 0\\ \frac{I_{L,1}}{C} & 0 & -\frac{I_{L,3}}{C} & \dots & 0\\ 0 & \frac{I_{L,2}}{C} & 0 & \dots & 0\\ \vdots & \vdots & \ddots & \ddots & -\frac{I_{L,n-1}}{C}\\ 0 & 0 & 0 & \frac{I_{L,n-2}}{C} & 0\\ -- & -- & -- & --\\ \frac{V_1 + V_2}{L} & 0 & 0 & \dots & 0\\ 0 & \frac{V_2 + V_3}{L} & 0 & \dots & 0\\ \vdots & \vdots & \ddots & \ddots & 0\\ 0 & 0 & 0 & \dots & \frac{V_{n-1} + V_n}{L} \end{bmatrix}$$

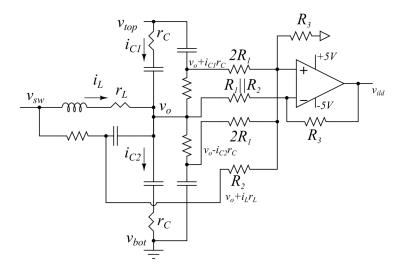

Figure 2.8: DPP converter module

The relationships between the voltage difference perturbations,  $\Delta v_i$ , and the duty ratio perturbations,  $\hat{d}_i$ , are described by the above matrix equations. However it is still a bit unclear how the system behaves because of the cross terms in the top half of the *B* matrix. To maintain modularity, our motive is to develop a control for each DPP module that independently equalizes the voltages of the two domains it is attached to. This means that the controller for one DPP will only take in  $\Delta v_i$  as input and provide  $d_i$  as the output. The control design will have serious limitations if the voltage differences are also largely affected by the duty ratios of the adjacent DPP converters. The obvious way to decouple the adjacent DPP units is to increase the domain capacitances *C*.

Evaluating  $(sI - A)^{-1}B$  with these matrices will give us an  $(n-1) \times (n-1)$ matrix of transfer functions between **x** and **u**. We are only concerned about the direct terms of that matrix since we are targeting a modular design. To observe the behavior of the direct terms of the transfer function matrix we are going to evaluate the transfer functions in MATLAB with varying number of stacked elements. For a 2 element stack (Figure 2.8) the transfer function  $\frac{x_1(s)}{d_1(s)}$  is easy to derive

$$\frac{x_1(s)}{d_1(s)} = \frac{1}{1 + 2LCs^2} \tag{2.12}$$

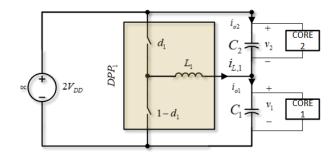

Moving on to stacks containing more elements, we can see that the Bode plots of the transfer functions are as shown in Figure 2.9. The plots have been made in MATLAB using  $L = 1 \ \mu \text{H}$  and  $C = 100 \ \mu \text{F}$ , a small inductance ESR of 10  $m\Omega$  was also incorporated for damping. The effect of non-zero average inductor currents was neglected here since those effects can easily be desensitized (added zeros can be shifted to very high frequencies) by using sufficiently large values of domain capacitances. The obtained Bode plots, even as the stack height (number of elements in the stack) increases, closely resemble the bode plot for the 2-domain case.

This suggests that the same transfer function of Equation 2.12 can be used to design closed loop control for the individual DPPs.

#### 2.3.1 Closed Loop Control

The frequency response of transfer functions obtained suggests that modular design of converters with local control is possible. Each DPP converter can be modeled as a buck converter with 2  $V_{DD}$  input and output  $V_{DD}$  as shown in Figure 2.9. The transfer function between duty ratio and voltage difference between the two domains is given by

$$G_{\Delta v d,i} = \frac{\Delta v_i}{d_i} = \frac{2V_{DD} \left(1 + 2r_c Cs\right)}{1 + \left(r_c + r_L\right) Cs + LCs^2}$$

(2.13)

Figure 2.9: Frequency response of converters at the middle of the stack. n = stack height

Based on this model a 2-pole, 2-zero compensator of the form

$$C(s) = K \frac{(\omega_{z_1} + s)(\omega_{z_2} + s)}{s(\omega_{p_1} + s)(\omega_{p_2} + s)}$$

(2.14)

can be implemented to regulate the voltage difference to zero. To ensure that the controller is able to equalize the domain voltages as expected, let us simulate a few cases.

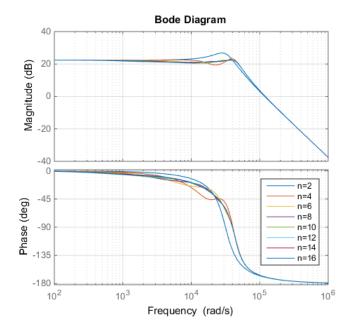

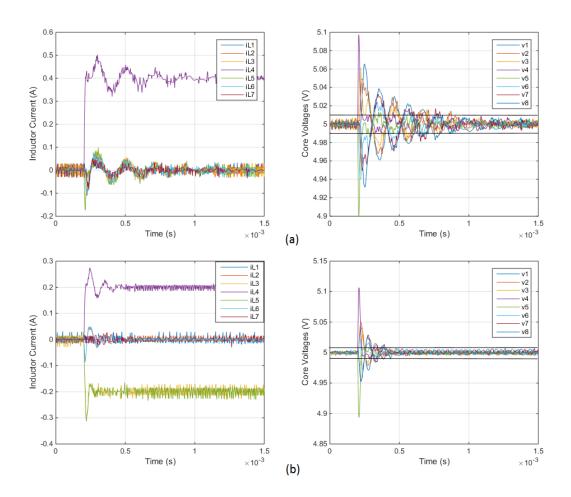

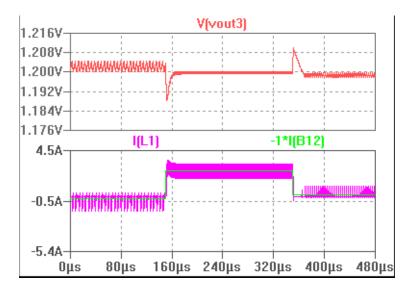

#### 2.4 Simulation Results on Dynamic Performance

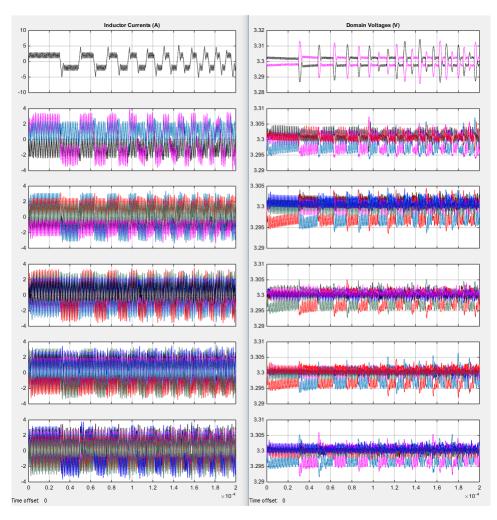

A test converter with  $L = 5 \ \mu \text{H}$ ,  $C = 20 \ \mu \text{F}$  was considered with appropriate series resistances of 10 m $\Omega$  on both components and the compensator was designed so that we obtain 60 degree phase margin at a 100 kHz bandwidth. The regulated domain voltages are to be 5 V and transients of 0.5 A are considered. The simulation results for the 2-core case in Figure 2.10 verify that the closed loop control is effective in voltage equalization and reaches steady state in 20  $\mu$ s which complies with the calculated bandwidth.

To see the impact of increasing the stack height, transient simulations with more cores in the stack have been carried out and the results are shown in Figure 2.11.

As we see from the simulations, the settling times of the voltages get severely degraded as the number of cores in the stack increases. So in effect to meet the performance specifications (bandwidth requirements) of processor cores, the switching frequency of the DPP converters has to be increased proportionally so that the degradation of bandwidth is compensated. This is undesirable as we are not getting the most bandwidth out of the designed converters and is one major disadvantage of this topology. It has been shown however that with global control and including inductor current information into our control design, improvement in performance can be achieved [30]. However, this will compromise our goal of achieving a modular design and the method will require large processing power for large core count. Instead, a topological modification to counter this problem of decreasing transient performance is proposed in the next section.

Figure 2.10: Load current step response, 2-core case

Figure 2.11: Simulated trend in settling times with increasing number of series-stacked elements

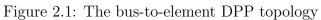

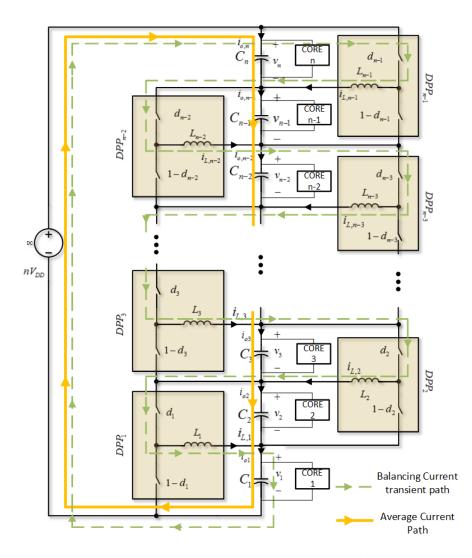

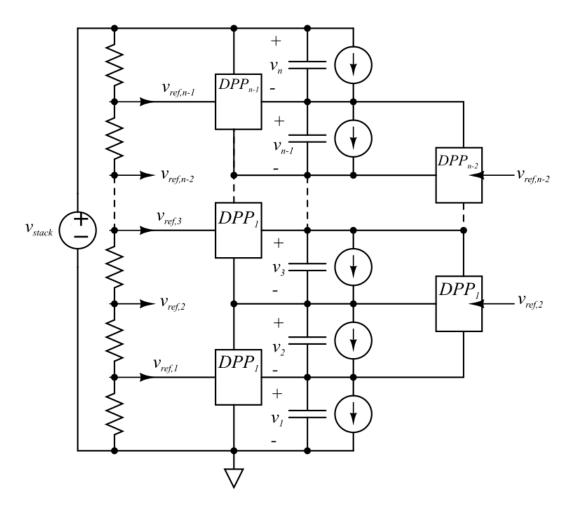

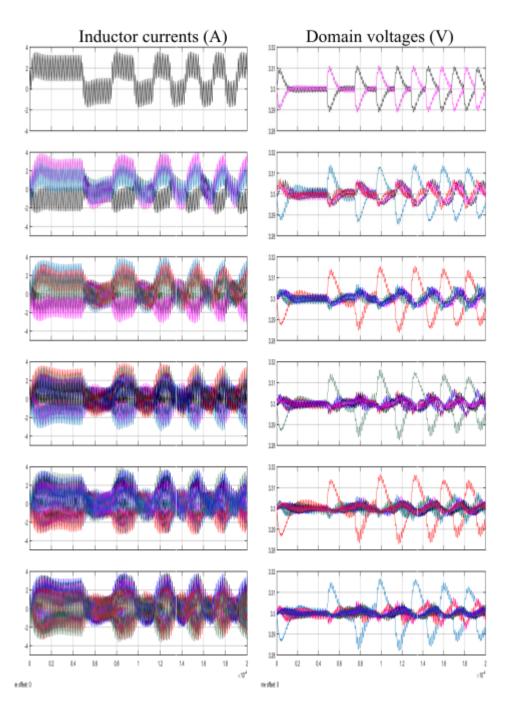

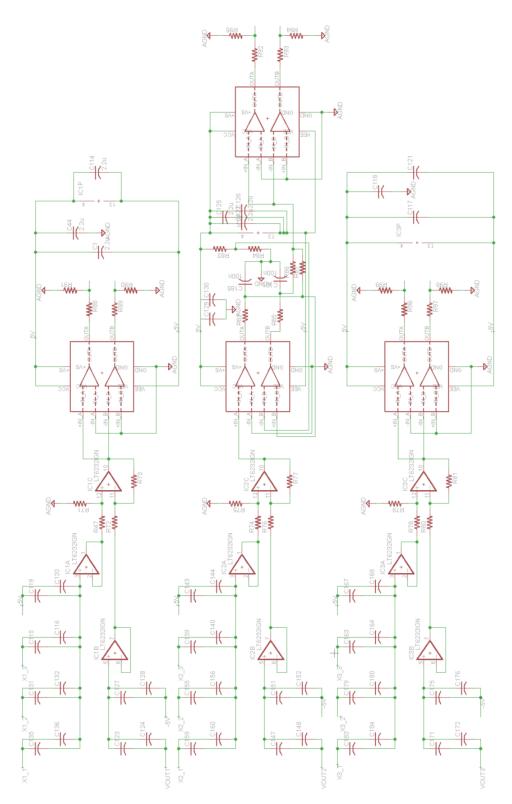

#### 2.5 Hierarchical Element-to Element topology

A hierarchical element-to-element topology is now proposed that significantly improves transient performance for larger core counts. The topology, shown in Figure 2.12, is a direct implementation of the hybrid/nested topology suggested in [22]. In this topology, alternate DPP converters have been set to balance the voltages of two consecutive domains instead of 1. We can divide the DPP converters on the system into two categories: the inner DPP converters which regulate adjacent domain voltages and outer converters that regulate the voltages taken two domains at a time. The advantage that we obtain from this is that the inner converters are now completely decoupled from each other.

#### 2.6 Motivation for Modified Topology

To understand why this topology was selected for improvement in transient performance we need to properly understand why the element-to-element topology performed worse with increasing core count. The bandwidth deterioration arises because of inductor current coupling exhibited in the capacitor charge balance equations. To maintain capacitor voltages at the set-points, the inductor currents of each DPP cannot change independently of the adjacent inductor currents. To look at the situation more intuitively, let us consider the path of the balancing current that must flow for voltage regulation (Figure 2.13). For an *n* element stack there are n - 1 inductors in the balancing current path. The rate at which the average balancing current can increase in the event of a transient gets limited as we increase the number of DPP converters in the stack. This explanation also validates the linear increase in settling times that we observe in Figure 2.11 (d). The bus-to-load topology is not prone to the same problem.

The hierarchical element-to-element topology can be used to improve settling times for a large number of stacked loads. The difference between this topology and the original element-to-element topology is that this one has half the converters running in an outer loop  $(DPP_2, DPP_5..., DPP_{n-2})$ . This reduces the number of inductors in the balancing current path to half the number that was present in the original element-to-element topology. So in

Figure 2.12: Hierarchical element-to-element DPP

Figure 2.13: Balancing current path in element-to-element topology

effect a two-level (one inner loop and one outer loop) hierarchical elementto-element topology can be used to double the number of voltage domains in series without degrading transient performance. If even more cores need to be stacked, then the number of hierarchies in the topology can be increased.

One obvious disadvantage of the hierarchical topology is the higher switch voltages on the outer-loop converters. This implies that we will have higher switching losses in the outer-loop converters if the switching frequencies of the inner loop converters are kept equal. This is essential because the bandwidths of the outer loop converters define the bandwidth of the series-connected system. So the efficiency of the hierarchical topology will be slightly lower than that of the original element-to-element topology. This limitation is not very serious since the converters process very little power and the impact of DPP converter efficiency on net efficiency is negligible for small mismatches.

## 2.7 Simulation Results on Improvement in Dynamic Performance

To validate improvement in dynamics we have to ensure that the bandwidths of the outer converters are the same as that of the inner loop converters. Since the input voltages of the outer converters have been doubled, the inductors in those converters have to be doubled as well. Matching bandwidths of inner loop converters and outer loop converters is not a necessity in an actual implementation. However, here we want to demonstrate that the improved transient response is a consequence of the modification of the topology only and not a consequence of improved DPP converter bandwidth. The simulation results for 8 stacked domains for the element-to-element and the hierarchical topologies are shown in Figure 2.14.

Figure 2.14: Improvement in transient performance:

- (a) Element-to-element DPP

- (b) Hierarchical element-to-element DPP

## CHAPTER 3

## HARDWARE VERIFICATION

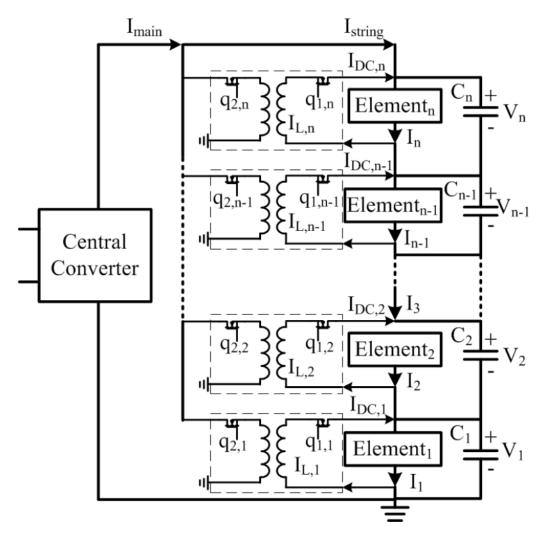

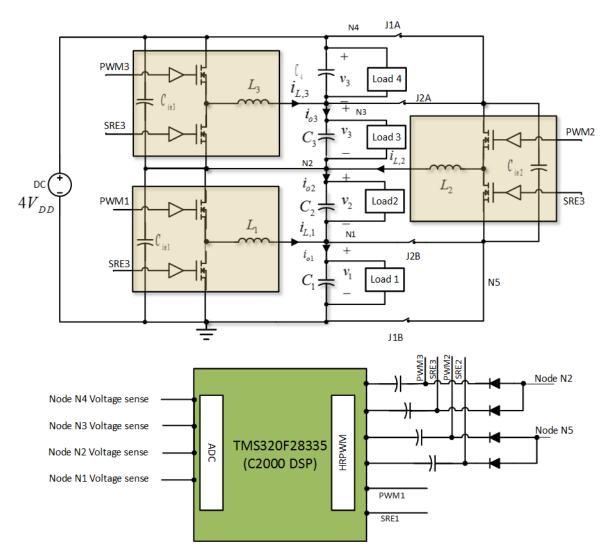

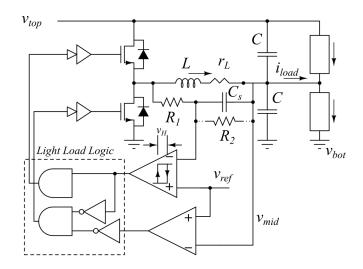

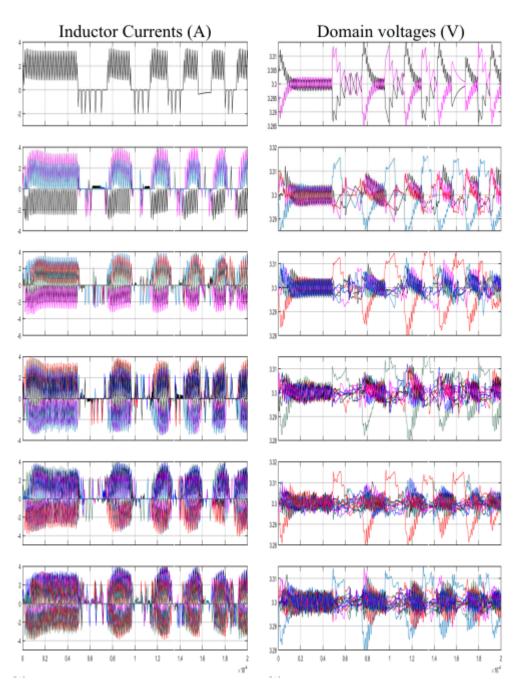

A hardware setup with 4 series-connected voltage domains was prepared to test our theoretical results. The hardware was initially set up for powering a stack of 4 Beaglebone Black boards. So the converter was optimized for 3.3 V - 5 V output and a few (less than 10 W) of output power. However the Beaglebone Black boards do not consume nearly as much power for the switched inductor converter to be effective. The converter is bidirectional and the mismatch currents are too low. Effective efficiency evaluation with small Beaglebone loads would require setting a very high switching frequency (several MHz) and relatively large inductor value (since voltage is high, and following from our previous discussion on scaling). So for verification 4 electronic loads (HP 6060B) were connected to form a series stack. The hardware was set up such that both the original element-to-element and the hierarchical element-to-element topologies can be tested on the same board.

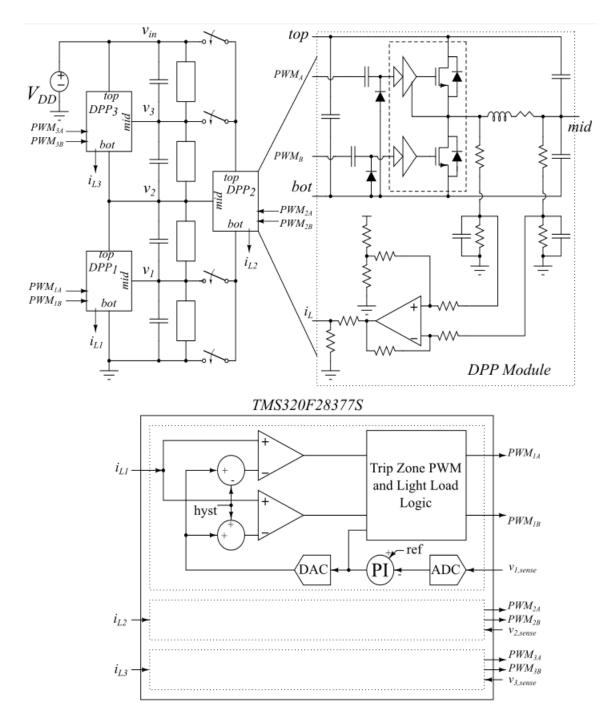

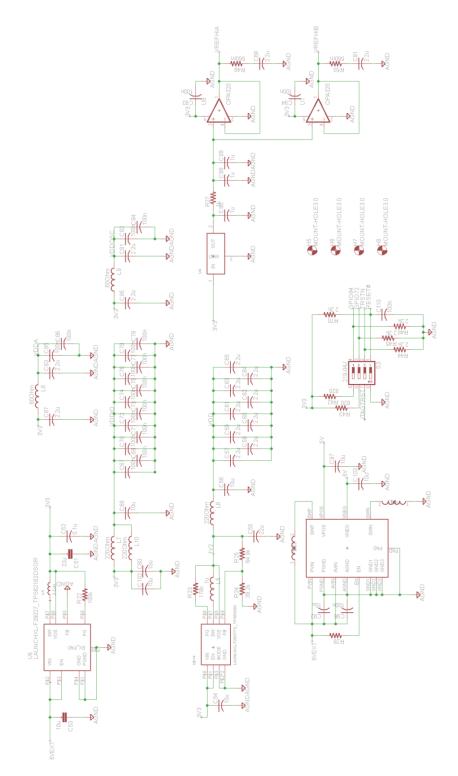

## 3.1 DPP Converter board

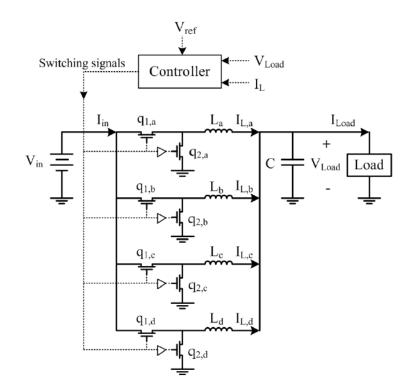

A high-level schematic of the board is shown in Figure 3.1. Each individual DPP unit has a 2-phase buck converter with integrated drivers. Both phases are not required considering that the power processed by the converters is expected to be low. This enables us to have 2 different values of inductors in the converter at the middle of the stack, one the same as the other two DPPs and another that is double of the other two. The switches J1A, J2A, J1B, and J2B enable us to switch between the element-to-element topology and the hierarchical element-to-element topologies and has been incorporated with an array of shorting resistors. This way, the number of wire connections external to the board has been kept minimal. Only connections to the individual loads and no additional connections to configure the board into the required

Figure 3.1: High-level schematic of the implemented hardware

topologies are necessary.