## TOWARD REALIZING POWER SCALABLE AND ENERGY PROPORTIONAL HIGH-SPEED WIRELINE LINKS

#### BY

#### TEJASVI ANAND

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2015

#### Urbana, Illinois

#### Doctoral Committee:

Associate Professor Pavan Kumar Hanumolu, Chair Associate Professor Rakesh Kumar Professor Elyse Rosenbaum Professor Naresh R. Shanbhag

## ABSTRACT

Growing computational demand and proliferation of cloud computing has placed high-speed serial links at the center stage. Due to saturating energy efficiency improvements over the last five years, increasing the data throughput comes at the cost of power consumption. Conventionally, serial link power can be reduced by optimizing individual building blocks such as output drivers, receiver, or clock generation and distribution. However, this approach yields very limited efficiency improvement. This dissertation takes an alternative approach toward reducing the serial link power. Instead of optimizing the power of individual building blocks, power of the entire serial link is reduced by exploiting serial link usage by the applications.

It has been demonstrated that serial links in servers are underutilized. On average, they are used only 15% of the time, i.e. these links are idle for approximately 85% of the time. Conventional links consume power during idle periods to maintain synchronization between the transmitter and the receiver. However, by powering-off the link when idle and powering it back when needed, power consumption of the serial link can be scaled proportionally to its utilization. This approach of rapid power state transitioning is known as the rapid-on/off approach. For the rapid-on/off to be effective, ideally the power-on time, off-state power, and power state transition energy must all be close to zero. However, in practice, it is very difficult to achieve these ideal conditions. Work presented in this dissertation addresses these challenges.

When this research work was started (2011-12), there were only a couple of research papers available in the area of rapid-on/off links. Systematic study or design of a rapid power state transitioning in serial links was not available in the literature. Since rapid-on/off with nanoseconds granularity is not a standard in any wireline communication, even the popular test equipment does not support testing any such feature, neither any formal measurement

methodology was available. All these circumstances made the beginning difficult. However, these challenges provided a unique opportunity to explore new architectural techniques and identify trade-offs. The key contributions of this dissertation are as follows.

The first and foremost contribution is understanding the underlying limitations of saturating energy efficiency improvements in serial links and why there is a compelling need to find alternative ways to reduce the serial link power.

The second contribution is to identify potential power saving techniques and evaluate the challenges they pose and the opportunities they present.

The third contribution is the design of a 5Gb/s transmitter with a rapid-on/off feature. The transmitter achieves rapid-on/off capability in voltage mode output driver by using a fast-digital regulator, and in the clock multiplier by accurate frequency pre-setting and periodic reference insertion. To ease timing requirements, an improved edge replacement logic circuit for the clock multiplier is proposed. Mathematical modeling of power-on time as a function of various circuit parameters is also discussed. The proposed transmitter demonstrates energy proportional operation over wide variations of link utilization, and is, therefore, suitable for energy efficient links. Fabricated in 90nm CMOS technology, the voltage mode driver, and the clock multiplier achieve power-on-time of only 2ns and 10ns, respectively. This dissertation highlights key trade-off in the clock multiplier architecture, to achieve fast power-on-lock capability at the cost of jitter performance.

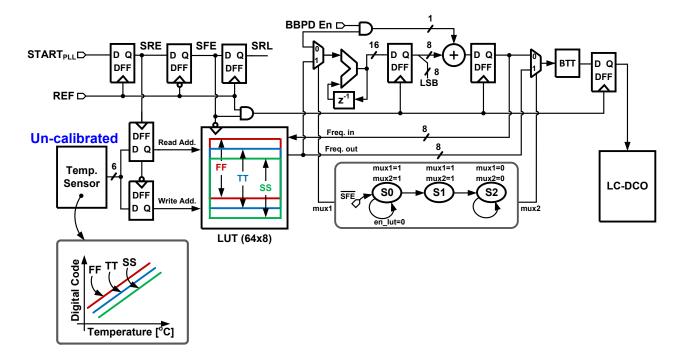

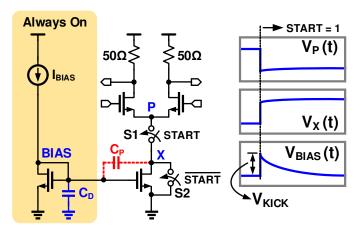

The fourth contribution is the design of a 7GHz rapid-on/off LC-PLL based clock multiplier. The phase locked loop (PLL) based multiplier was developed to overcome the limitations of the MDLL based approach. Proposed temperature compensated LC-PLL achieves power-on-lock in 1ns.

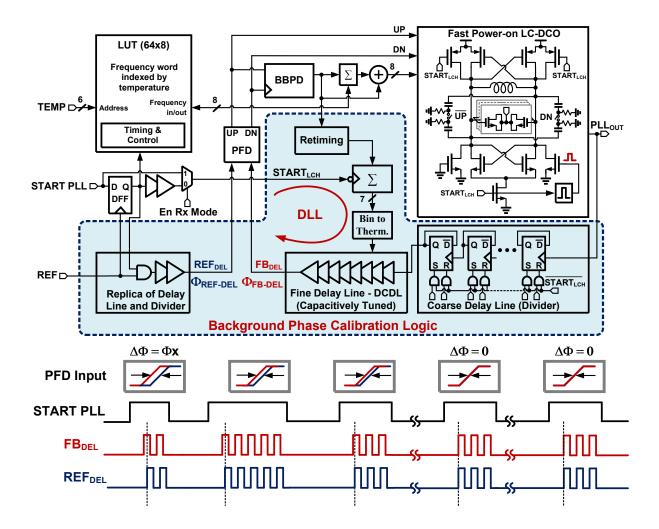

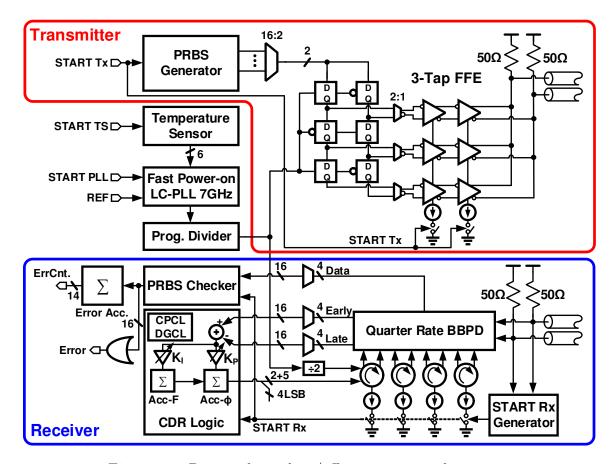

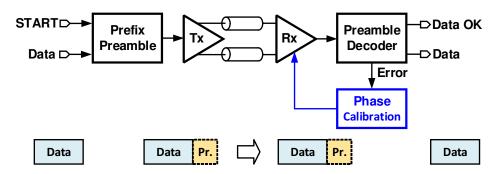

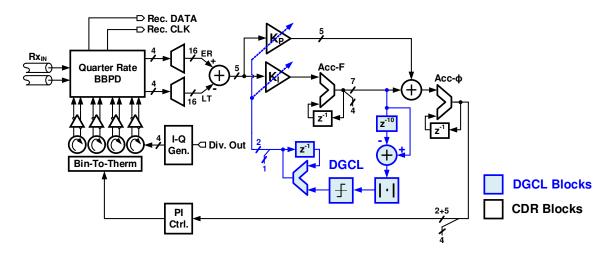

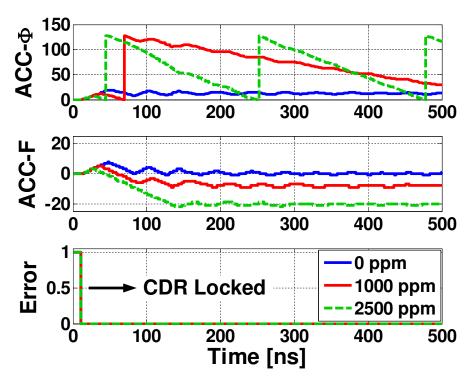

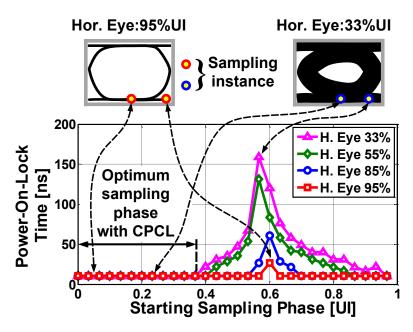

The fifth and biggest contribution of this dissertation is the design of a 7Gb/s embedded clock transceiver, which achieves rapid-on/off capability in LC-PLL, current-mode transmitter and receiver. It was the first reported design of a complete transceiver, with an embedded clock architecture, having rapid-on/off capability. Background phase calibration technique in PLL and CDR phase calibration logic in the receiver enable instantaneous lock on power-on. The proposed transceiver demonstrates power scalability with a wide range of link utilization and, therefore, helps in improving overall system efficiency. Fabricated in 65nm CMOS

technology, the 7Gb/s transceiver achieves power-on-lock in less than 20ns. The transceiver achieves power scaling by 44x (63.7mW-to-1.43mW) and energy efficiency degradation by only 2.2x (9.1pJ/bit-to-20.5pJ/bit), when the effective data rate (link utilization) changes by 100x (7Gb/s-to-70Mb/s).

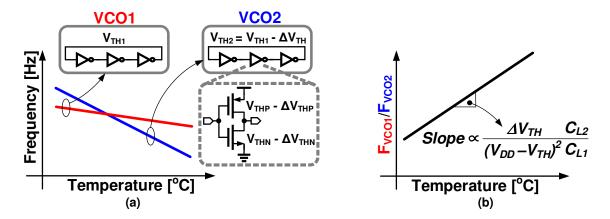

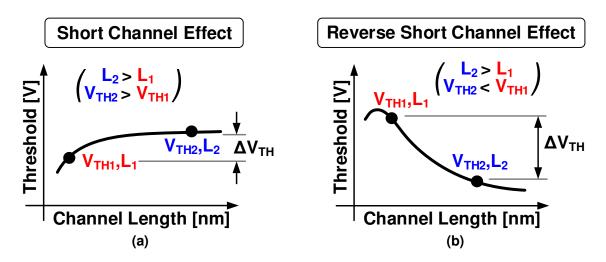

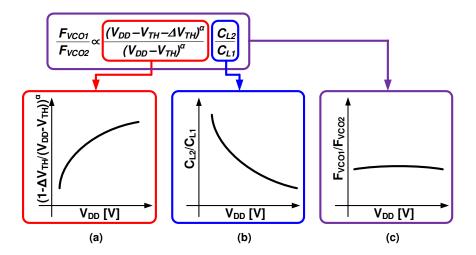

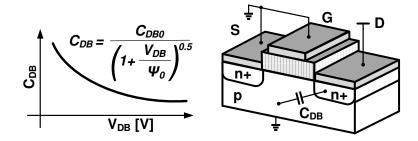

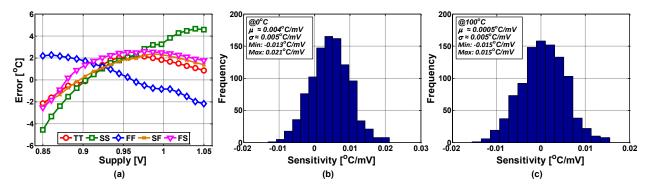

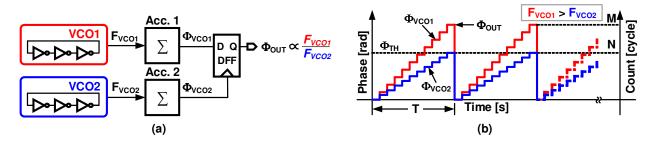

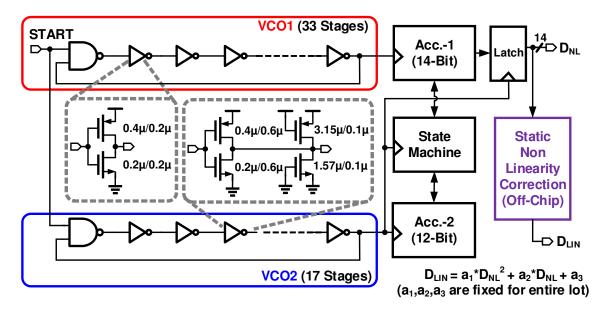

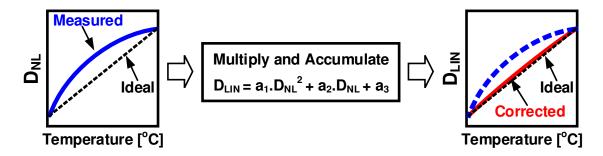

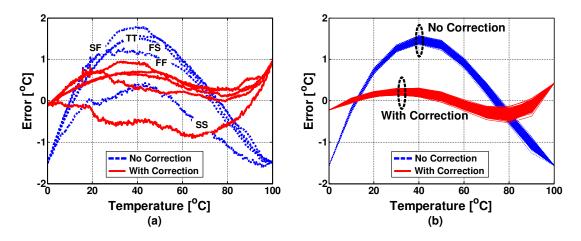

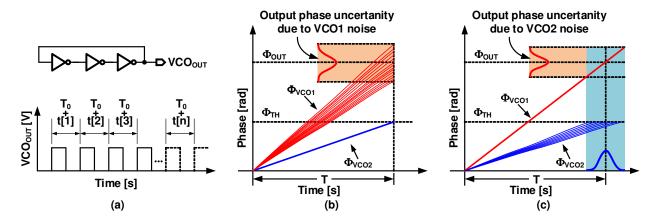

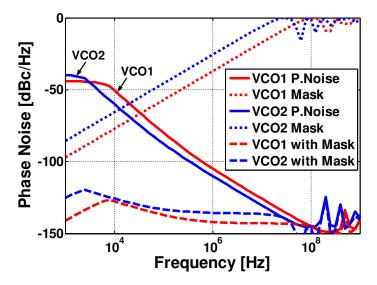

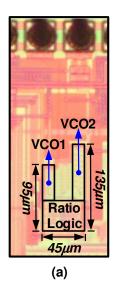

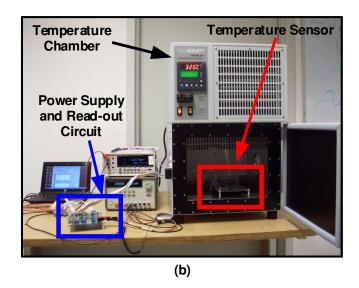

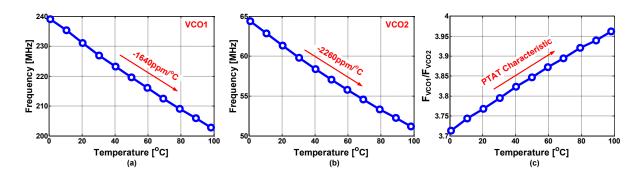

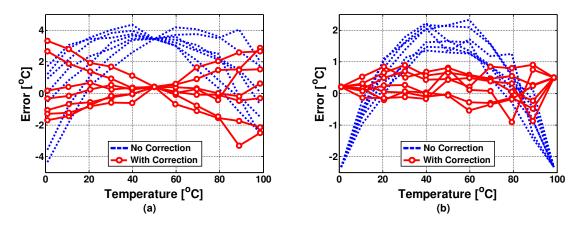

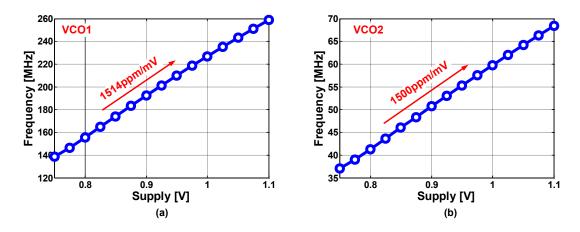

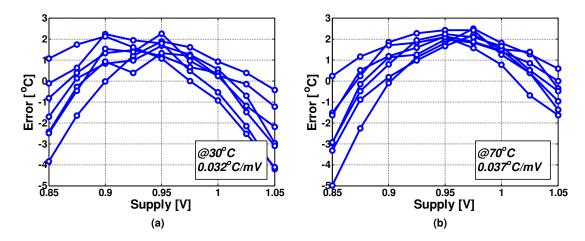

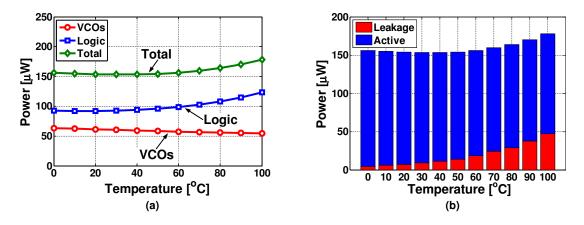

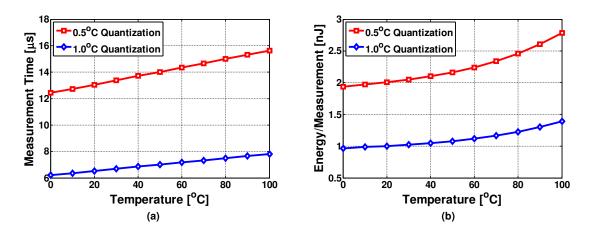

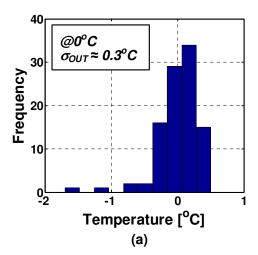

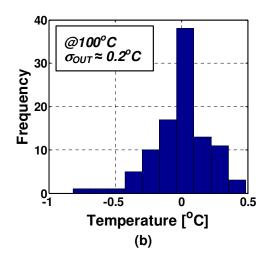

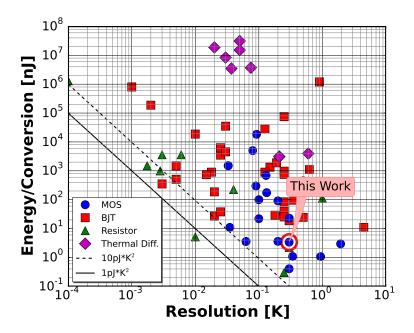

The sixth and final contribution is the design of a temperature sensor to compensate the frequency drifts due to temperature variations, during long power-off periods, in the fast power-on-lock LC-PLL. The proposed self-referenced VCO-based temperature sensor is designed with all digital logic gates and achieves low supply sensitivity. This sensor is suitable for integration in processor and DRAM environments. The proposed sensor works on the principle of directly converting temperature information to frequency and finally to digital bits. A novel sensing technique is proposed in which temperature information is acquired by creating a threshold voltage difference between the transistors used in the oscillators. Reduced supply sensitivity is achieved by employing junction capacitance, and the overhead of voltage regulators and an external ideal reference frequency is avoided. The effect of VCO phase noise on the sensor resolution is mathematically evaluated. Fabricated in the 65nm CMOS process, the prototype can operate with a supply ranging from 0.85V to 1.1V, and it achieves a supply sensitivity of  $0.034^{\circ}$ C/mV and an inaccuracy of  $\pm 0.9^{\circ}$ C and  $\pm 2.3^{\circ}$ C from 0-100°C after 2-point calibration, with and without static nonlinearity correction, respectively. It achieves a resolution of 0.3°C, resolution FoM of 0.3(nJ/conv)res<sup>2</sup>, and measurement (conversion) time of  $6.5\mu s$ .

To my parents and almighty God, for their love and support.

🕉 भूर्भुव: स्व: तत्सिवतुर्वरेन्यं । भर्गो देवस्य धीमहि, धीयो यो न: प्रचोदयात् ॥

Oh God! Thou art the Giver of Life,

Remover of pain and sorrow,

The Bestower of happiness,

Oh! Creator of the Universe,

May we receive thy supreme sin-destroying light,

May Thou guide our intellect in the right direction.

Gayatri Mantra

## ACKNOWLEDGMENTS

I am grateful to several people for the successful completion of this dissertation and my graduate studies. Without their help and support, this dissertation would not have seen the light of the day. First, I would like to express my sincere gratitude to my advisor Professor Pavan Kumar Hanumolu for his inspiring guidance and constant support throughout my Ph.D. His vast knowledge and strong technical expertise helped me to get a good understanding of phase locked loops and high-speed serial links.

I would like to thank Professor Naresh R. Shanbhag for serving on my dissertation committee, and for his inspiring and thought provoking discussions. I would also like to thank Professor Elyse Rosenbaum and Professor Rakesh Kumar for serving on my dissertation committee and for providing valuable comments and suggestions.

I greatly benefited from the fruitful research collaboration with Professor Kofi Makinwa at the Delft University of Technology, Netherlands. His deep understanding and love for temperature sensors has helped me to make contributions in the world of sensors.

Special thanks go to Dr. Daniel Friedman and Dr. Alberto Valdes Garcia at the IBM T.J. Watson Research Center, Yorktown Heights for providing me an opportunity to be a part of their team and gain valuable research experience. In particular, I would like to thank Dr. Mark Ferriss, Dr. Bodhisatwa Sadhu and Dr. Wooram Lee for being excellent mentors and friends. I miss the wonderful discussions we use to have during lunch.

My heartfelt thanks and regards goes to my previous mentors Professor Bharadwaj Amrutur and Principal Scientist Kuruvilla Varghese at the Indian Institute of Science, Bangalore, India for their encouragement and motivation.

Much needed financial support by Intel Labs, SRC, Analog Devices, and NSF is gratefully acknowledged.

I would like to express my warmest appreciation for Seong Joong Kim, member of our research group, who generously helped me with soldering the QFN package on several occasions. His hands-on expertise on PCB is unrivaled at UIUC. I would like to thank Dr. Brian Young, former member of our research group, for his help during my tape-out. His invaluable experience and critical feedback helped me to become a better designer. I would also like to thank Dr. Amr Elshazly, former member of our research group, for his timely help and constructive feedback during my tape-out.

I would also like to acknowledge the current and former members of our research group for their help and support: Dr. Rajesh Inti, Dr. Karthikeyan Reddy, Woo-Seok Choi, Mrunmay Talegaonkar, Dr. Saurabh Saxena, Ahmed Elkholy, Romesh Kumar Nandwana, Guanghua Shu, Da Wei, Timir Nandi, Ahmed Elmallah, Dongwook Kim, Charlie Zhu, Danyang Wang, and Mostafa Ahmed. Apart from my group members, I would like to thank faculty members and my friends in other research groups: Dr. Chandrasekhar Radhakrishnan, Dr. Min-Sun Keel, Mingu Kang, Yingyan Lin and Pourya Assem, to name a few.

My heartfelt thanks to my friends Jivesh, Vikas, Pratul, Rajneesh, Venu, Viveka, Vikram, Abhishek, Ajay, Sachin, Arun, Pramod, Sameer, Anshul, Pratap, Col. Sandeep, Chaitanya, Surbhi, Kannan, Syam, Rajashekhar, Shrikant and many others for their trust and friendship.

Words are not enough to express my gratitude to my family members and to the almighty God for their unwavering support in my good and bad times.

## TABLE OF CONTENTS

| CHAPT | FER 1 MOTIVATION                                            | 1  |

|-------|-------------------------------------------------------------|----|

| 1.1   | Why Serial Link Power Consumption Is a Matter of Concern    | 3  |

| 1.2   | Power Reduction Methodology                                 | 6  |

| CHAPT | TER 2 POWER SCALING AND ENERGY PROPORTIONAL OPERATION       |    |

| TEO   | CHNIQUES                                                    | 9  |

| 2.1   | Serial Link Architecture and Simulation Model               | 1  |

| 2.2   | Serial Link Power Scaling with DVFS                         | 13 |

| 2.3   | Serial Link Power Scaling with Rapid-On/Off                 | 15 |

| 2.4   | DVFS versus Rapid-On/Off                                    | 20 |

| 2.5   |                                                             | 21 |

| CHAPT | TER 3 A 5Gb/s TRANSMITTER FOR ENERGY PROPORTIONAL LINKS     |    |

| (EP   | L)                                                          | 22 |

| 3.1   | 1 /                                                         | 23 |

| 3.2   | Proposed Fast Power-On Transmitter Architecture             | 25 |

| 3.3   | 0                                                           | 31 |

| 3.4   | 1 0                                                         | 35 |

| 3.5   |                                                             | 10 |

| 3.6   | Conclusion                                                  | 50 |

| CHAPT | TER 4 A 7GHz FAST POWER-ON-LOCK PLL FOR ENERGY PROPORTIONAL | L  |

| LIN   |                                                             | 53 |

| 4.1   |                                                             | 53 |

| 4.2   |                                                             | 55 |

| 4.3   | 1                                                           | 59 |

| 4.4   |                                                             | 52 |

| 4.5   | 1                                                           | 35 |

| 4.6   |                                                             | 66 |

| 4.7   | Conclusion                                                  | 72 |

|       | TER 5 A 7Gb/s EMBEDDED CLOCK TRANSCEIVER FOR ENERGY         |    |

| PRO   | DPORTIONAL LINKS                                            | 74 |

| 5.1   | Transceiver Architecture                                    | 74 |

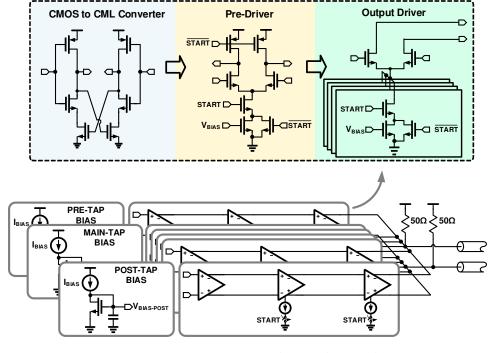

| 5.2   | Transmitter                                                 | 76 |

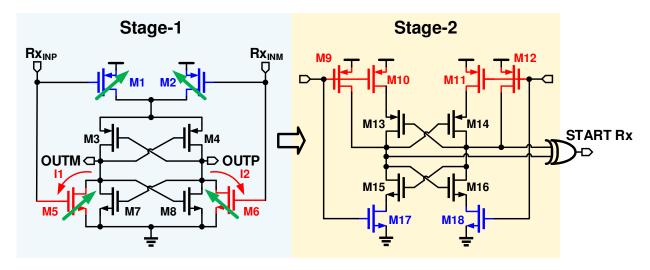

| 5.3   | Receiver                                                  |

|-------|-----------------------------------------------------------|

| 5.4   | Measurement Results                                       |

| 5.5   | Conclusion                                                |

|       | TER 6 A HIGHLY DIGITAL TEMPERATURE-TO-FREQUENCY-TO-       |

| DIG   | ITAL BASED TEMPERATURE SENSOR 9                           |

| 6.1   | Temperature Sensor Concept                                |

| 6.2   | Making Sensor Less Sensitive to Supply Voltage Variations |

| 6.3   | Temperature Sensor Architecture                           |

| 6.4   | Effect of Phase Noise on Sensor Resolution                |

| 6.5   | Measurement Results                                       |

| 6.6   | Conclusion                                                |

| CHAPT | TER 7 CONCLUSION                                          |

| APPEN | NDIX A LIST OF SERIAL LINK PAPERS SURVEYED                |

| REFER | ENCES                                                     |

## CHAPTER 1

## **MOTIVATION**

Low cost and reliable data communication is key in enabling technologies such as cloud computing, big-data, parallel processing, and video streaming applications. High-speed wireline communication is one of the most critical fabric in the present communication infrastructure. Electronic gadgets such as smartphones, tablets, laptops, servers and even smart watches contain several wireline links. Wireline links, also known as serial links, can be categorized into various standards, as shown in Table 1.1.

Table 1.1: Wireline Link Standard and Data Rates

| Standard Name | Data Rates          |

|---------------|---------------------|

| DDR4          | $3.2 \mathrm{Gb/s}$ |

| MIPI-M PHY    | $5\mathrm{Gb/s}$    |

| QPI           | 8Gb/s               |

| USB 3.1       | $10 \mathrm{Gb/s}$  |

| PCIe 3.0      | 8Gb/s               |

| HDMI 2.0      | $18\mathrm{Gb/s}$   |

| IEEE 802.3bj  | $25\mathrm{Gb/s}$   |

| InfiniBand    | $25\mathrm{Gb/s}$   |

|               |                     |

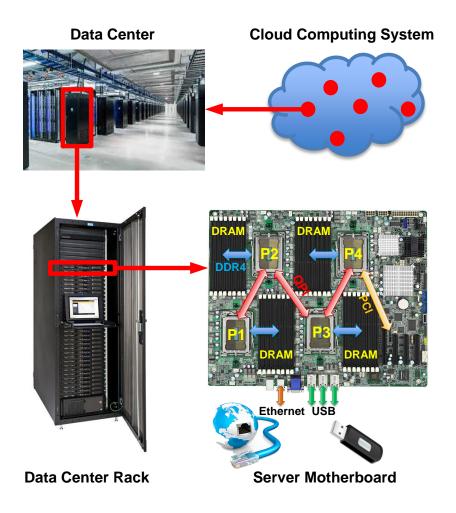

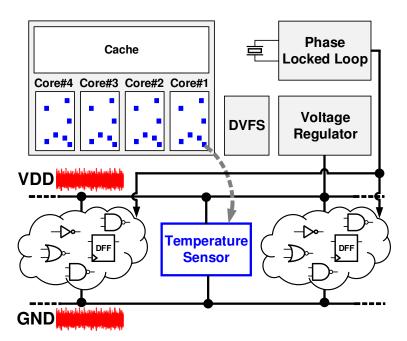

An example of serial links present on a server motherboard, which forms a part of cloud infrastructure, is shown in Fig. 1.1. The motherboard has four processor slots, which can be identified as P1, P2, P3, and P4. An interface between a processor and a DRAM module is known as double data rate (DDR) interface. Processor-to-processor interface is known as QuickPath Interconnect (QPI) or HyperTransport (HT) interface, and it is often used in parallel processing. An interface between a processor and other peripherals is known

Figure 1.1: High-speed wireline links in a server motherboard and server as part of a cloud infrastructure.

as peripheral component interconnect (PCI), and a universal serial bus (USB) interface. Finally, an interface to router or switch is known as an Ethernet interface.

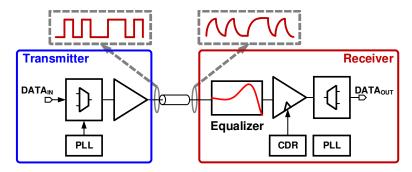

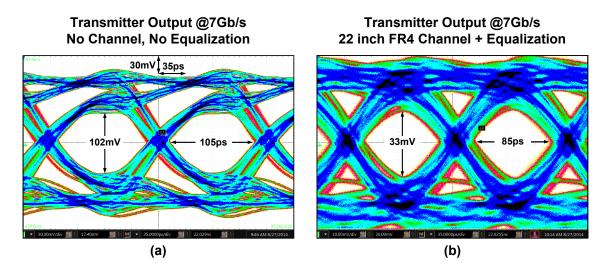

Basic building blocks of a serial link is shown in Fig. 1.2. It consists of three components, a transmitter, channel, and receiver. The transmitter includes a serializer and an output driver. The channel is made up of copper trace on FR4, twisted copper wire or a shielded cable. The receiver consists of a sampler and a deserializer. Channel loss results in intersymbol interference (ISI), which closes the data eye at the receiver input. To compensate for the channel loss, equalization is provided in the receiver and sometimes on the transmitter end. As the channel length increases, for the same data rate, the loss also increases, and, therefore, more equalization is needed to compensate for the loss. Equalization increases

Figure 1.2: Architecture of a serial link.

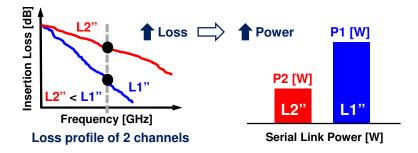

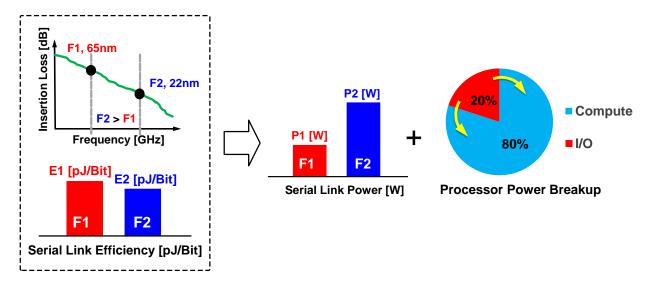

Figure 1.3: Effect of channel loss on power consumption.

the power consumption of serial links, as shown in Fig. 1.3. In server class processors, serial links today consume approximately 20% of power [1,2]. Despite consuming only a fraction of processor power, serial link power consumption is becoming a matter of concern.

## 1.1 Why Serial Link Power Consumption Is a Matter of Concern

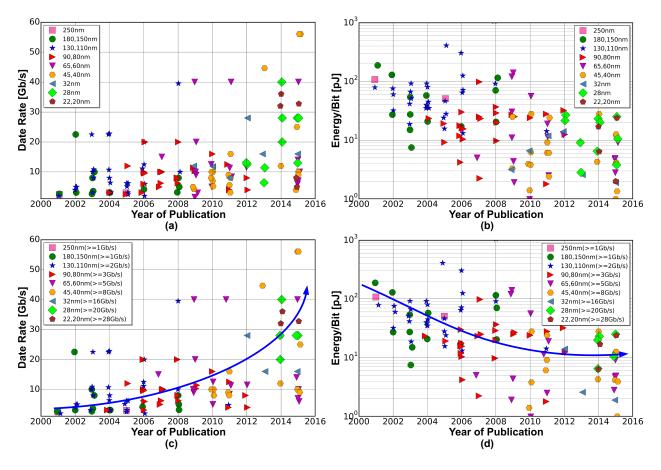

Growing appetite for high-performance computing has resulted in a consistent increase in the number of processing cores every year [3]. Consequently, this has resulted in an increase in the demand of off-chip I/O bandwidth. For example, IBM's Power-7 with eight cores has 4.7Tb/s off-chip bandwidth. While the IBM Power-8 with twelve cores has a 7.6Tb/s off-chip bandwidth [4]. The processor's package is typically constrained by the number of I/O pins, and, therefore, bandwidth demand is usually met by increasing the per-pin data rate or per-pin bandwidth, as shown in Fig. 1.4(a). It can be observed that serial links are keeping up with the bandwidth demand. Figure 1.4(b) plots the energy-per-bit versus year

<sup>&</sup>lt;sup>1</sup>The data plotted in Fig. 1.4(a), (b), (c) and (d) was collected from over 129 papers published in leading conferences. Details of the serial link data used in Fig. 1.4 are available in Appendix A.

Figure 1.4: Serial link trends. (a) Data rate versus year of publication of off-chip links. (b) Energy efficiency versus year of publication. (c) Data rate versus year of publication filtered by the data rate for a given technology node. (d) Energy efficiency versus year of publication filtered by the data rate for a given technology node.

of publication. It can be observed that the energy efficiency improvement of these links has started to taper-off in recent years.

Voltage and process scaling have been the biggest contributors in improving energy efficiency over the last 15 years. However, as the supply voltage scaling has saturated in finer technology nodes, the energy efficiency improvement due to voltage scaling has diminished. Porting a serial link, which was designed at a fixed data rate, to a finer process node helps in improving energy efficiency. However, if the data rate requirement of a serial link increases while moving to a fine process node, then it can be observed from Fig. 1.4(d) that there is no net efficiency improvement beyond 65nm. This behavior is explained as follows: Over the last several years, the channel length of serial links has stayed more or less fixed. Channel

Figure 1.5: Reason for saturating energy efficiency in fine process nodes and its effect on the I/O power component in a processor.

lengths did not change because changing channels incurs a high cost, while the data rates continued to increase. This has resulted in increased channel loss at Nyquist frequencies, and consequently more equalization is required to offset the loss, which translates to increased power consumption. Therefore, energy efficiency improvements provided by process scaling is offset by the energy needed to compensate for channel loss. As a result, energy efficiency improvement in finer process nodes is not significant [5].

The combined effect of increasing bandwidth and saturating energy efficiency would eventually result in increased power consumption of serial links. Today, serial links consume approximately 20% of processor power, but if the above-mentioned trend continues, this portion will increase in the future, as shown in Fig. 1.5. The trend of increasing serial link power share is catalyzed by the fact that the logic power would continue to reduce with every new technology node until it hit the minimum power limits [6]. Once the logic power hits the minimum power limit or when the rate of power reduction in the logic core gets slower than the rate of increase in the serial links power, at that point, due to thermal constraints of the processor package, increasing serial link power could potentially constrain the power budget allocated for the computational cores. Consequently, increasing a processor's computational capacity in the future would be challenging, and serial link power will become the bottleneck. Therefore, a paradigm shift in reducing serial link power is needed.

Figure 1.6: (a) Instantaneous bandwidth versus time in a conventional serial link. (b) Energy efficiency and power versus link utilization.

## 1.2 Power Reduction Methodology

Conventionally, both system and circuit designers have attempted to solve the power problem in their best possible ways. System designers optimize the design parameters such as data rate, the number of I/O lanes, communication medium, supply voltage, or the technology node used. Circuit designers optimize individual circuit blocks such as phase locked loop (PLL) power, or analog to digital converter's (ADC) figure of merit. The combined effort of both these groups results in a serial link system whose energy efficiency is optimized at its peak performance level. However, there is a problem with this design approach. This design approach fails to account for the usage pattern of applications that utilize these serial links.

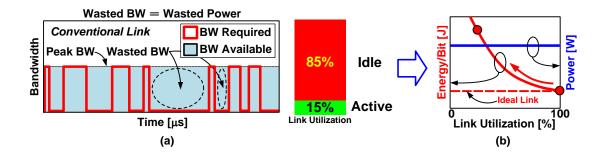

In practical systems, serial links are only sporadically used. They are used whenever there is a miss in the last level of a cache, and then the processor fetches data from DRAM, or if there is a request to download a web page, and the request packet is sent to the server. Figure 1.6(a) shows the instantaneous bandwidth demand versus time in a conventional serial link. Even though almost peak bandwidth is available all the time, approximately 85% of the time, this bandwidth is not being used [7,8]. This wastage of bandwidth, when the serial link is idle, results in idle power consumption. In a conventional serial link, this idle power is necessary to maintain synchronization between the transmitter and the receiver. Even if serial links are designed and optimized for the best energy efficiency at their peak performance level, due to idle power consumption, energy efficiency of links degrades as the link utilization is reduced, as shown in Fig. 1.6(b). Ideally, constant energy-per-bit across

all utilization levels is desirable.

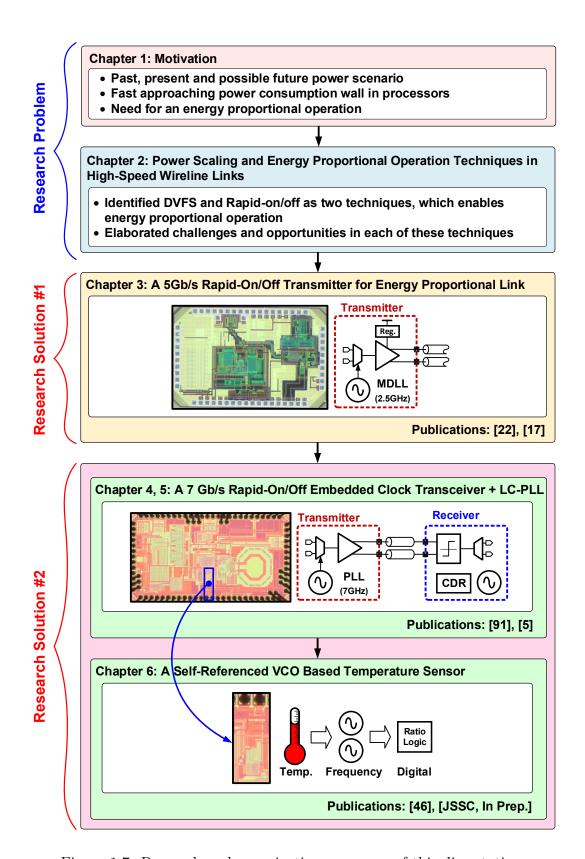

One possible way to overcome drawbacks of a conventional design approach is to cooptimize both the system and circuit designs. Instead of optimizing links efficiency at their

peak performance, the energy efficiency of serial links must be optimized at their average

utilization levels. The focus of this dissertation is to develop circuit and system architectures

that are optimized to leverage the usage pattern of applications in order to save power. A

summary of research presented in this dissertation and its organization is illustrated in

Fig. 1.7.

Figure 1.7: Research and organization summary of this dissertation.

## CHAPTER 2

# POWER SCALING AND ENERGY PROPORTIONAL OPERATION TECHNIQUES

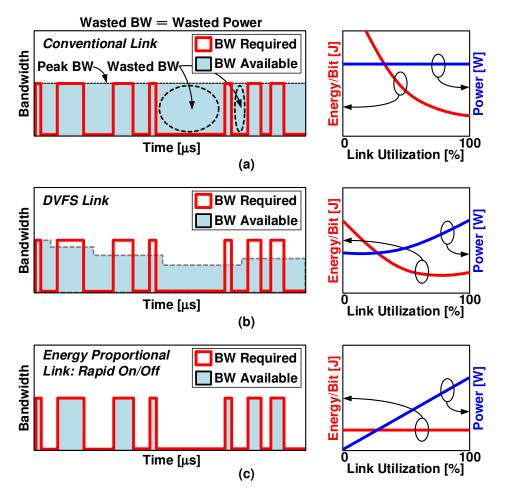

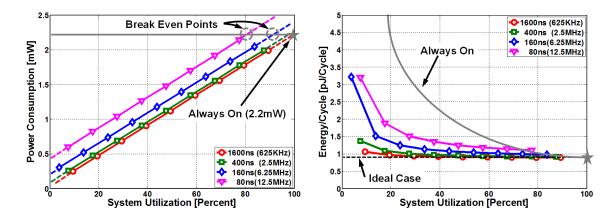

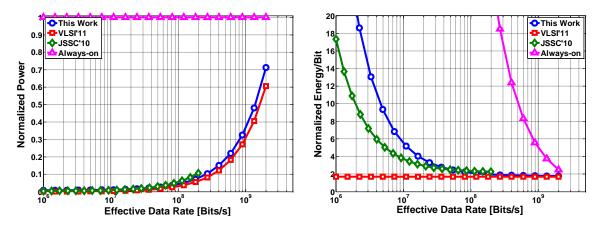

In a system, serial links can be treated as a resource to accomplish either a computational or a processing task. In a practical scenario, these serial links are utilized sporadically by the applications that run on a processor. Therefore, instantaneous bandwidth demand (utilization) of the serial links varies over time. As shown in Fig. 2.1(a), when a conventional serial link is idle, it consumes idle power to maintain synchronization between transmitter and receiver. As a result, energy efficiency of such a link, as quantified by the energy-per-bit metric, degrades at lower link utilization levels.

The impact of degradation in energy efficiency is perceivable in data centers where approximately 7% of data center power is spent in off-chip serial links [1,2,9], which include both the memory and data networks. It is estimated that by 2016, data centers in North America are expected to consume approximately 13,250MW of power [10]. With an average server utilization of 15% [7], these data centers could potentially save 1,420MW as idle link power (assuming power usage effectiveness (PUE)<sup>1</sup> of 1.8). Using a nationwide average electricity rate of \$0.07/kWh for an industrial complex, this amounts to saving approximately \$870M annually.

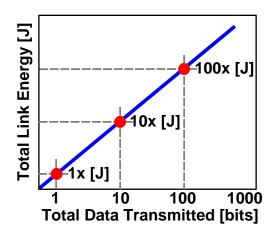

By scaling the serial link power to match its utilization, idle power wastage could be eliminated. The elimination of wasted power will ensure that the link will maintain a constant energy-per-bit across all utilization levels. Such a mode of operation of the serial link is also known as the energy proportional operation [8]. Figure 2.2 shows the energy proportionality

$$PUE = \frac{Total\ Facility\ Energy}{IT\ Equipment\ Energy} \tag{2.1}$$

This ratio remains constant for a data center. For example, if IT equipment energy consumption increases, this results in overall increase in data center energy consumption by a factor of PUE.

<sup>&</sup>lt;sup>1</sup>Power usage effectiveness (PUE) is a measure of how efficiently a data center uses energy.

Figure 2.1: Instantaneous bandwidth versus time demand along with power consumption and energy-per-bit of (a) conventional serial link, (b) dynamic voltage and frequency scaling (DVFS) based link, and (c) rapid-on/off approach based link.

concept in serial links. If x amount of energy is required to transfer 1 bit of data across the channel, then to transfer 10bits, 10x energy would be needed, irrespective of link utilization, i.e., energy is proportional to the amount of data transmitted and is independent of link utilization.

Dynamic voltage and frequency scaling (DVFS) and rapid-on/off approach are two known techniques to achieve the energy proportionality goal. In DVFS, the supply voltage and link rate are adaptively scaled based on the bandwidth demand [11–13], as shown in Fig. 2.1(b). Note that in DVFS technique, while the instantaneous bandwidth demand exceeds the available bandwidth, the average bandwidth available in serial link matches with the average bandwidth demand, i.e. average area under the red curve and shaded region are equal. Fig-

Figure 2.2: Concept of energy proportional operation in serial links.

ure 2.1(c) shows the energy proportional behavior of an ideal rapid-on/off communication scheme. In this technique, the link is powered down when idle and powered up instantaneously when the data is ready to be transferred [14–18], resulting in the most energy-efficient use of link bandwidth. In such systems, power consumption scales linearly with link utilization, resulting in energy consumption to become proportional to the transferred data.

DVFS and rapid-on/off operation have their own merits and challenges to achieve the desired power scalability and energy proportionality objective. This chapter presents a comparative study of both these techniques by pointing out their limitations and enumerates key challenges. The comparison is done with the help of a Matlab simulation of an abstract serial link model. The rest of the chapter is organized as follows. Section 2.1 describes the serial link architecture and model used for simulation. Section 2.2 discusses the DVFS theory, challenges, and simulation results. Section 2.3 presents the rapid-on/off non-idealities, simulation results, and key challenges. Section 2.4 presents comparative analysis with DVFS. Section 2.5 concludes this chapter.

## 2.1 Serial Link Architecture and Simulation Model

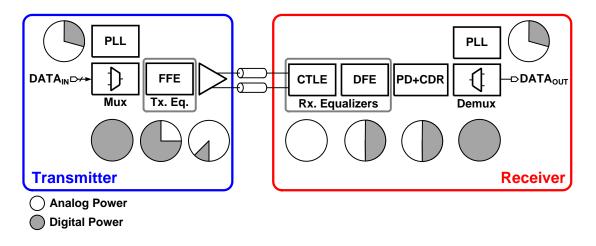

Figure 2.3 shows the block diagram of a high-speed serial link with embedded clock architecture and its approximate power break down. The transmitter consists of a phase locked loop

Figure 2.3: Embedded clock serial link architecture, and an approximate power break down of each block into analog and digital component.

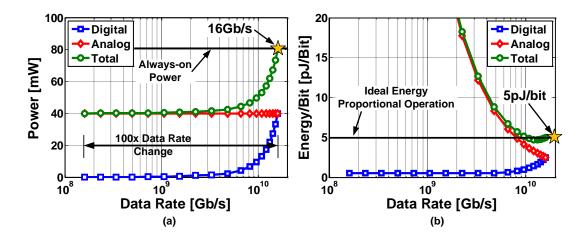

(PLL) as a clock multiplier, serializing multiplexer (Mux), feed forward equalizer (FFE), and an output driver. The receiver consists of continuous time linear equalizer (CTLE), decision feedback equalizer (DFE), phase detector (PD), clock and data recovery loop (CDR), de-multiplexer block (Demux), and PLL. Mux and Demux blocks consist mostly of digital logic gates. The transmitter output driver, which can be either current mode logic (CML) or voltage mode based, has a majority of its power attributed to the analog component. The CTLE is a pure analog block and the current mode logic based DFE has both analog and digital components. It is difficult to scale power in analog circuits because voltage scaling is limited by the available bias margins and signal swing. Therefore, in the analysis, it is assumed that the analog power does not scale with the supply voltage or the data rate. Hence, understanding the composition of a serial link power in terms of its analog and digital components is essential to understand the efficacy of DVFS. For the modeling purpose, a serial link with digital and analog power component of 50% each is assumed. The simulation model consists of a serial link operating at 16Gb/s with an energy efficiency of 5pJ/bit.

## 2.2 Serial Link Power Scaling with DVFS

In the DVFS mode of operation, during periods of low bandwidth demand, the link data rate is reduced and digital supply voltage is scaled so as to barely meet the timing requirements. Section 2.2 presents a mathematical model of a serial link for DVFS and points out the challenges in using DVFS approach.

#### 2.2.1 Mathematical Modeling and Simulation

Maximum achievable data rate in a serial link is inversely proportional to the delay through the CMOS logic, which can be expressed as

$$DataRate(V_{DD}) \propto \frac{\beta}{2} \frac{(V_{DD} - V_{TH})^{\alpha}}{V_{DD}C_L}$$

(2.2)

where  $\beta$  is a function of mobility, device size, and capacitance,  $V_{DD}$  is the instantaneous supply voltage of the link,  $V_{TH}$  is the threshold voltage,  $C_L$  is the load capacitance, and  $\alpha$  is a constant close to 1.3 for short channel devices [19].  $V_{DD}$  is scaled from  $V_{DDmax}$  of 1V to  $V_{DDmin}$  which is 0.45V (1.5 $V_{TH}$ ). Below  $V_{DDmin}$ , the supply voltage is kept constant, and only the data rate is scaled so as to reduce power at lower link utilization.

To eliminate the device size and technology constants from the analysis, the data rate is normalized for a given  $V_{DD}$ , which is written as

$$DataRate_{norm}[Gb/s] = 16. \frac{DataRate(V_{DD})}{DataRate(V_{DDmax})}$$

(2.3)

where a factor of 16 is for the 16Gb/s link. The digital component of the serial link power at a given  $V_{DD}$  is written as

$$P_{DIG} = \left(\frac{V_{DD}}{V_{DDmax}}\right)^2 \frac{P_{LINK}.DataRate_{norm}}{2}$$

(2.4)

where  $P_{LINK}$  is serial link power at peak data rate, the factor or 2 in the denominator corresponds to 50% digital power. The analog component of link power remains constant irrespective of voltage scaling or data rate changes and is expressed as  $P_{ANA} = 0.5P_{LINK}$ .

Figure 2.4: Matlab simulation of DVFS. (a) Power versus effective data rate. (b) Energy-per-bit versus effective data rate.

By using (2.3) and (2.4), energy-per-bit of the serial link is written as

$$\frac{Energy}{Bit} = \frac{P_{DIG} + P_{ANA}}{DataRate_{norm}} \tag{2.5}$$

Figure 2.4(a) and (b) show a plot of serial link power versus effective data rate and energy-per-bit versus effective data rate respectively. At high effective data rates, link power scales down rapidly as the digital component reduces. However, at very low data rates the link power stays constant and consequently energy-per-bit increases, thereby deviating from ideal energy proportional operation.

## 2.2.2 Challenges and Opportunities in DVFS

It can be observed from Fig. 2.4 that analog power in a serial link is the biggest bottleneck in achieving energy proportionality with DVFS technique. At low data rates (1Gb/s-to-2Gb/s), low-loss short channels, and fine technology nodes, the majority of serial link power is attributed to digital power due to the absence of equalization and termination requirements. Therefore, DVFS is more suitable for links, which are mostly digital.

Time needed for voltage regulators and PLLs to settle supply voltage and frequency to a new value could be of the order of hundreds of nanoseconds or a couple of microseconds. During this time, the link sits idle and consumes power, which further degrades the energy-per-bit. The voltage regulator and PLL settling time result in performance penalty because the processor has to wait for the serial link to stabilize before it can begin moving data. The processor continues to be clocked and consume power during this wait period. Consequently, the overall system energy efficiency is reduced. The energy analysis of DVFS presented in the Section 2.2.1 did not account for the loss in processor performance.

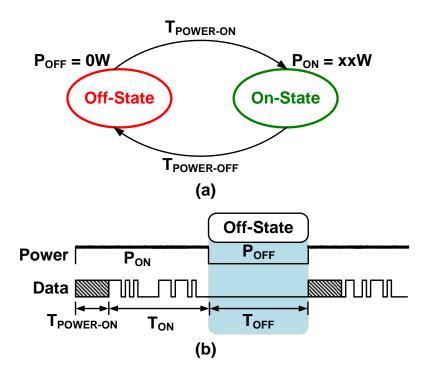

## 2.3 Serial Link Power Scaling with Rapid-On/Off

In rapid-on/off mode of operation, the serial link has two power states, namely on-state and off-state, as shown in Fig. 2.5(a). The link is powered-off when idle and powered-on instantaneously when there is data to be transferred, as shown in Fig. 2.5(b). The on/off transition time must be of the order of nanoseconds so that the link can be powered-on/off with very fine granularity. In this way, the power consumption scales linearly with link utilization (see Fig. 2.1(c)), resulting in energy consumption to become proportional to the transferred data, and the serial link, therefore, achieves energy proportional operation.

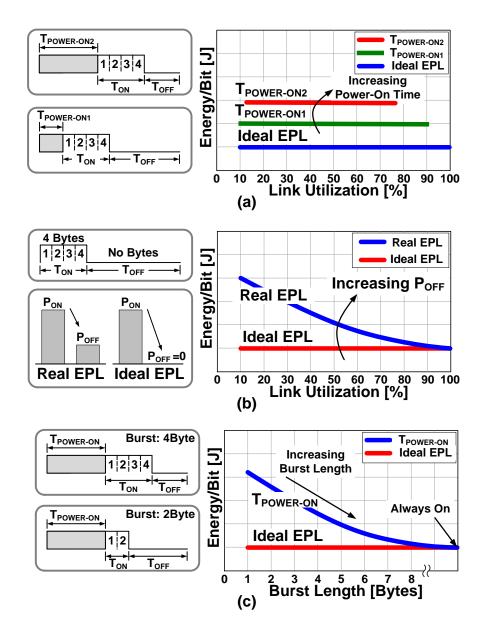

## 2.3.1 Effect of Non-Idealities on Rapid-On/Off Links

Practical serial links have finite power-on time, non-zero off-state power, and finite power-cycling energy. The effect of these parameters on the link's energy efficiency (energy-per-bit) can be mathematically captured as:

$$\frac{Energy}{Bit} = \frac{P_{ON}T_{ON} + P_{ON}T_{POWER-ON} + P_{OFF}T_{OFF} + E_{ON-OFF}}{Total\ number\ of\ bits\ transmitted}$$

(2.6)

where  $P_{ON}$  is the on-state power,  $P_{OFF}$  is the off-state power,  $T_{ON}$  is the on-state time,  $T_{OFF}$  is the off-state time,  $T_{POWER-ON}$  is the power-on time and  $E_{ON-OFF}$  is the energy consumed during on/off transition.

Finite power-on time is due to the time required to charge/discharge bias nodes, and time needed for the clock multiplier to achieve frequency and phase lock. Energy wasted

Figure 2.5: (a) Power states in rapid-on/off mode of operation. (b) Timing diagram in rapid-on/off mode of operation.

during power-on time degrades the energy proportional behavior of the link. Assuming the link consumes approximately peak power during the power-on transition, this wasted energy equates to  $P_{ON}T_{POWER-ON}$ . The effect of power-on time on link efficiency is shown in Fig. 2.6(a). For a constant burst length, power-on energy  $(P_{ON}T_{POWER-ON})$  increases the energy-per-bit by a fixed amount across all link utilization values.

Finite off-state power in the link is mainly due to current biases that were left powered-on to reduce power-on time and leakage in logic gates. Figure 2.6(b) illustrates the effect of static off-state power on link energy-efficiency. At lower link utilization  $(T_{OFF} >> T_{ON})$ , even with a small off-state power  $(P_{OFF})$ , the off-state energy  $(P_{OFF}T_{OFF})$  starts to dominate link energy-efficiency. Therefore, the off-state power must be close to zero to achieve constant energy-per-bit at extremely low data rates.

Power-cycling energy is the energy consumed in charging/discharging nodes in each power cycle or data burst event. Therefore, more frequent data bursts incur larger energy penalty. Figure 2.6(c) shows the effect of burst length on energy-per-bit for a fixed effective data

Figure 2.6: Effect of non-ideal behavior of rapid-on/off links. (a) Effect of power-on time on link energy efficiency. (b) Effect of static off-state power on link energy efficiency. (c) Effect of data burst length on link energy efficiency.

rate. When the data is transferred in smaller bursts, energy spent in powering-on the link  $(P_{ON}T_{POWER-ON})$  and power cycling energy  $(E_{ON-OFF})$  becomes comparable to the onstate energy  $(P_{ON}T_{ON})$  and consequently leads to increased energy-per-bit.

The plot of energy-per-bit versus utilization captures essential features of power scalable or energy proportional links. With the help of energy-per-bit versus utilization plot, energy

Figure 2.7: Matlab simulation of burst mode operation. (a) Energy-per-bit versus effective data rate for various power-on time. (b) Energy-per-bit versus effective data rate for various off-state power values. (c) Energy-per-bit versus effective data rate for various data burst lengths.

consumption estimates can be made for a given link usage scenario of an application. Thus, it forms one of the important metrics to characterize and compare such links.

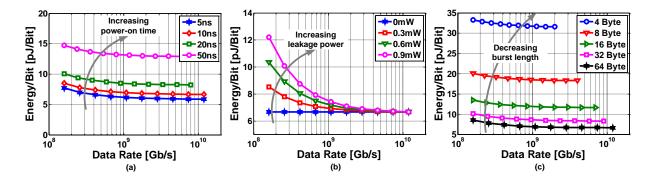

For simulating non-idealities in rapid-on/off mode, a serial link operating at 16Gb/s with an energy efficiency of 5pJ/bit is used. This serial link consumes 80mW of power in the on-state. Figure 2.7 shows the simulated results in the presence of non-idealities.  $P_{OFF}$  of  $300\mu$ W, burst length of 64 bytes,  $T_{POWER-ON}$  of 10ns and  $E_{ON-OFF}$  of 50pJ are used in these simulations unless otherwise stated. The effect of power-on time from 5ns to 50ns on the link's energy-per-bit is shown in Fig. 2.7(a). The effect of off-state power from  $0\mu$ W to  $900\mu$ W on the link's energy-per-bit is shown in Fig. 2.7(b). The effect of data burst length from 4 bytes to 64 bytes on the link's energy-per-bit is shown in Fig. 2.7(c).

### 2.3.2 Challenges and Opportunities in Rapid-On/Off Operation

Voltage mode output drivers, though more efficient than current mode logic based drivers, require a voltage regulator to set the output swing. However, this regulator cannot be powered-on/off instantaneously. Even if we keep the regulator powered-on during the off-state at the expense of small power penalty, voltage droop caused due to the limited load transient response reduces the eye margin on the samplers at the receiver end. Current mode output drivers are immune to supply noise variation. However, the bias current needed to

Figure 2.8: Energy-per-bit versus effective data rate for the various percentages of time long off-periods could occur.

bias the output driver must be powered-on instantaneously, which is difficult to achieve in practice.

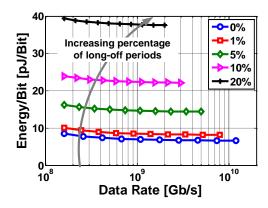

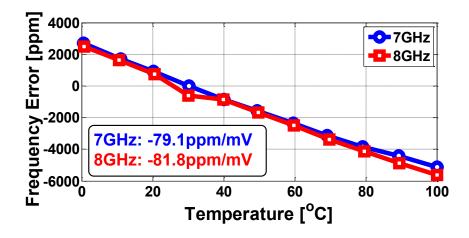

During the long off-periods, due to change in temperature, the oscillator frequency could drift from the locked position. Limited load transient response of the voltage regulator could also change the oscillator frequency during power-on. Therefore, during the power-on period, both frequency and phase of the oscillator must be locked to the reference. Phase and frequency settling in the phase locked loop are governed by the loop bandwidth, which is limited to one-tenth of the reference frequency due to stability reasons [20]. Consequently, PLLs could take several hundred nanoseconds to achieve the phase and frequency lock. The effect of long frequency locking time due to temperature drift on the link's energy efficiency is simulated for various percentages of time such an event could happen, and the results are shown in Fig. 2.8. Frequency locking time of  $1\mu$ s is assumed in this simulation. For applications where long off periods could happen 20% of the time, the energy efficiency degrades by almost 7x at high data rates.

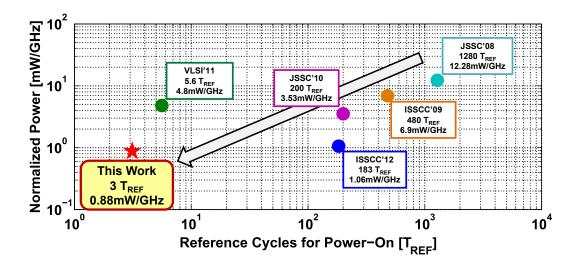

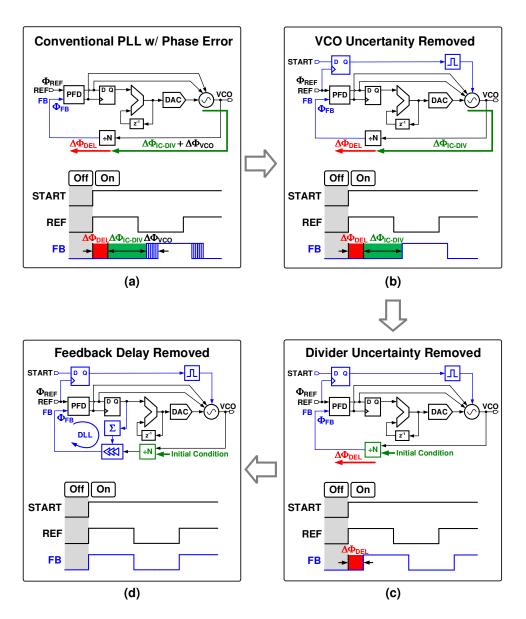

Recently, PLL with 100ns of phase lock time has been demonstrated [21]. However, it is not sufficient to achieve the energy proportional objective. Multiplying delay locked loop (MDLL) [22] and multiplying injection locked oscillator (MILO) [14] have also demonstrated phase locking in 10ns ( $\approx 3T_{REF}$ ) and less. However, performing fast frequency locking in PLL, MDLL and MILO remains a challenging research problem.

Figure 2.9: Comparison of DVFS and rapid-on/off operation. (a) Power versus effective data rate. (b) Energy-per-bit versus effective data rate.

On the receiver end, detecting a start of transition and powering-up the receiver in a few nanoseconds is a non-trivial design problem. Powering up the equalization chain and synchronizing the clock and data recovery loop with the incoming data remains unaddressed in the literature.

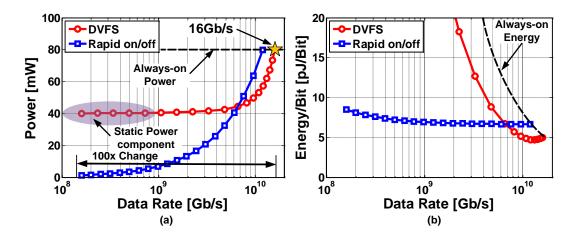

## 2.4 DVFS versus Rapid-On/Off

Comparison of DVFS with the rapid-on/off based link is made with the help of an abstract model presented in Section 2.1, and the results are shown in Fig. 2.9. It can be observed that, for a 100x change in data rate (16Gb/s - 160Mb/s), the energy-per-bit for the DVFS is increased by 50x (5pJ-250pJ), while for the burst mode it is increased by only 1.7x (5pJ-8.5pJ). For the data rates between 8Gb/s-16Gb/s, DVFS seems to perform better than the burst mode. This is due to the fact that the digital power in DVFS scales down rapidly. However, at lower data rates, the component of analog power dominates the serial link power and results in energy efficiency degradation in DVFS. Consequently, for a broad range of link utilizations, rapid-on/off performs better than DVFS.

### 2.5 Conclusion

DVFS and rapid-on/off operation are two key techniques to achieve power scalability and energy proportional operation in the serial links. In this chapter, an abstract model of a serial link was presented, and comparative study of DVFS and rapid-on/off operation was done. DVFS was found to be limited by the analog component of serial link power and is, therefore, useful for all-digital short-channel serial links. Rapid-on/off operation is an attractive way to achieve energy proportional operation as both the analog power and digital power can be scaled depending on the utilization. Therefore, the rapid-on/off approach can be effectively used for high-speed serial links.

In this dissertation, the rapid-on/off approach is used to achieve power scalability and energy proportional operation. The focus of the next chapters is on addressing non-idealities in rapid-on/off based serial links by designing novel architectures.

## CHAPTER 3

# A 5Gb/s TRANSMITTER FOR ENERGY PROPORTIONAL LINKS (EPL)

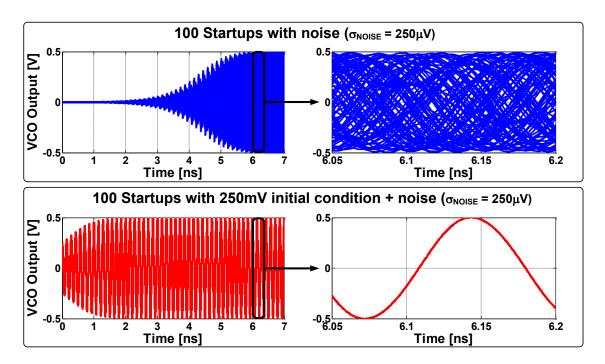

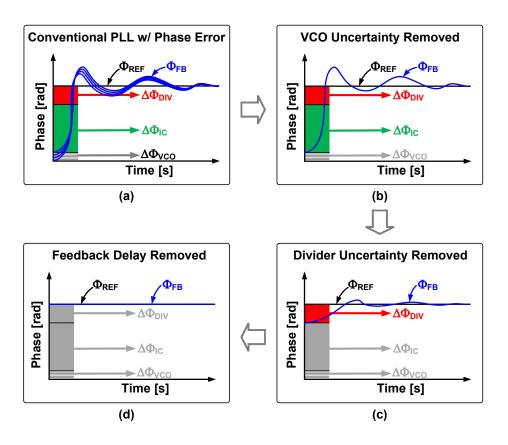

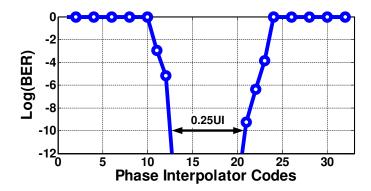

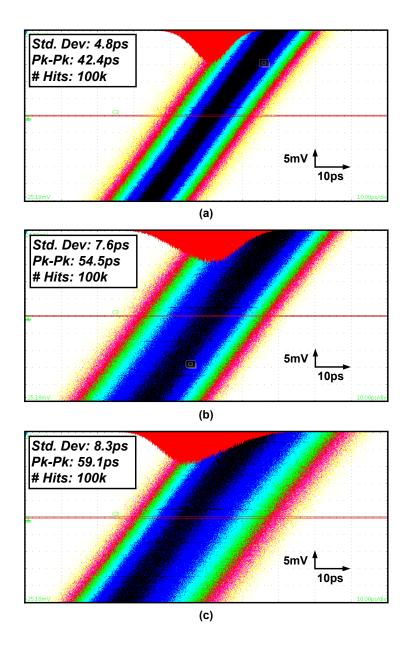

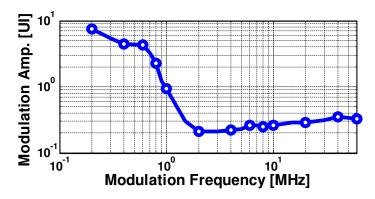

In this chapter, we present a rapid-on/off transmitter consisting of a voltage mode driver and a clock multiplier. Fabricated in 90nm CMOS process, the prototype transmitter achieves 100x effective data rate range (5Gb/s-0.048Gb/s) while scaling the power by 50x(4.8mW-0.095mW) and energy efficiency by only 2x(1-2pJ/Bit). Such energy proportional operation is achieved by using a fast power-on voltage mode driver and fast power-on lock multiplying delay locked loop (MDLL) based digital clock multiplier. In this work, wide effective data rate range is achieved by duty cycling the transmitter at a fixed data rate of 5Gb/s and not by changing active data rate. By adopting a digital voltage regulator, the prototype voltage mode driver achieves 2ns power-on time, less than  $11\mu$ W off-state power, 32pJ energy overhead for on/off transition, and 2.6mW on-state power at 5Gb/s output data rate. By employing a highly scalable digital architecture with accurate frequency presetting and instantaneous phase acquisition, the prototype 8x/16x clock multiplier achieves 10ns (3 reference cycles) power-on time,  $2ps_{rms}$  long-term absolute jitter, less than  $25\mu$ W off-state power, 12pJ energy overhead for on/off transition, and 2.2mW on-state power at 2.5GHz output frequency [22].

The rest of the chapter is organized as follows. Section 3.1 discusses the building blocks of a conventional transmitter and their limitations for rapid-on/off application. Section 3.2 introduces the proposed transmitter architecture. A mathematical modeling of MDLL power-on transient is presented in Section 3.3. Circuit details of the clock multiplier are discussed in Section 3.4. Section 3.5 presents the measured results. Section 3.6 concludes the chapter.

## 3.1 Limitations of Conventional Transmitter for Rapid-On/Off Links

#### 3.1.1 Output Driver

Voltage-mode (VM) drivers dissipate a quarter of the power as compared to the current-mode logic (CML) output drivers [23]. However, voltage regulators required to set output swing and termination impedance cannot be powered-on instantaneously. Keeping these regulators always-on, severely impacts energy-per-bit at lower data rates [15]. Digital voltage regulators [24,25], provide a means to power-on/off rapidly while consuming no static power in the off-state. The pass transistor in the digital regulator also helps in power-gating the logic, resulting in low leakage power in the off-state. For these reasons, digital regulators are employed in the proposed VM driver.

#### 3.1.2 Clock Multiplier

The long locking time of conventional clock multipliers implemented using phase locked loops (PLLs) presents the biggest bottleneck in achieving energy proportional operation. Increasing the PLL bandwidth reduces the locking time. However, to ensure loop stability, loop bandwidth cannot exceed one-tenth the reference frequency [20]. As a result, even if the VCO frequency is precisely set digitally, the sluggish phase acquisition limits the phase locking time to at best a few hundred nanoseconds [15,26]. Techniques such as dynamic phase error compensation [27], edge-missing compensation [28], and hybrid PLLs [29] improve the phase acquisition time. By calibrating the phase of the feedback clock, the best power-on time of forty reference cycles has also been reported [21]. However, such improvements are inadequate to achieve the energy proportional operation goal.

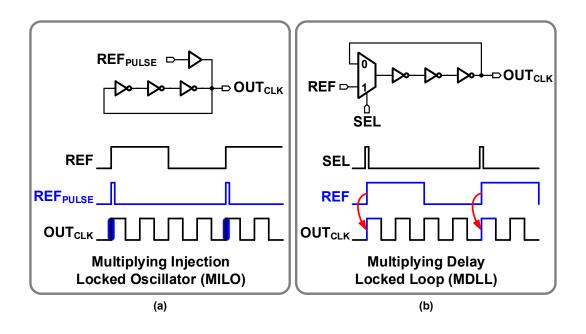

The multiplying injection locked oscillator (MILO) provides a means to reduce poweron time. Figure 3.1(a) shows an MILO, which is phase locked to four times the reference frequency. A pulse train generated at the reference frequency is injected into the oscillator to achieve fast phase locking. The spectrum of this pulse train is rich in frequency components

Figure 3.1: (a) Simplified schematic and timing diagram of a multiplying injection locked oscillator (MILO). (b) Simplified schematic and timing diagram of a multiplying delay locked loop (MDLL).

at reference, and its harmonics and these harmonics appear as spurs at the output. By increasing MILO's bandwidth with stronger injection strength, locking time can be reduced. However, wide bandwidth results in large spurs at the injection frequency [30]. Filtering of MILO's output with a second injection locked oscillator (ILO) could reduce these spurs. However, it comes at the cost of extra power [31]. This trade-off, which compromises the lock time, limits the use of MILOs for fast power-on applications.

Multiplying delay locked loop (MDLL) provides a means to overcome the drawbacks of MILOs. Figure 3.1(b) shows an MDLL, which is phase locked to four times the reference frequency. In MDLL, every  $N^{th}$  VCO edge is replaced by the clean reference edge by opening up the ring oscillator for a brief period using a narrow pulse [32–34]. This edge replacement results in instantaneous phase locking, which is independent of the bandwidth. Inserting a clean reference edge every reference cycle resets all accumulated jitter in the VCO and results in superior jitter performance [35, 36]. A perfect edge replacement results in no reference spurs at the output. These features make MDLL a suitable candidate for fast power-on applications.

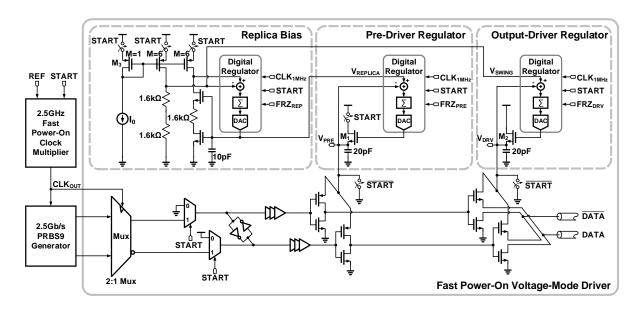

Figure 3.2: Schematic diagram of the proposed fast power-on transmitter.

## 3.2 Proposed Fast Power-On Transmitter Architecture

Figure 3.2 shows the block diagram of the proposed transmitter. It consists of a fast power-on lock clock multiplier, a 2:1 latch based multiplexer, and a voltage mode driver output stage. The clock multiplier, implemented using a digital multiplying delay-locked loop (MDLL), generates a 2.5GHz output from a 312.5MHz reference clock. The PRBS9 generator outputs data at 2.5Gb/s, which is serialized to get a valid PRBS9 pattern and transmitted at 5Gb/s with 250mV differential peak-to-peak output swing.

The proposed voltage mode driver consists of a replica bias, pre-driver, and an output driver. The replica bias circuit generates reference voltages  $V_{REPLICA}$  and  $V_{SWING}$  for the pre-driver and output driver regulators, respectively.  $V_{REPLICA}$  needed to create 50 ohm output impedance is generated by enclosing a replica of the output driver [37], which is  $1/16^{th}$  the original size, in a closed loop.  $V_{SWING}$  sets the differential output driver swing. Pre-driver and output driver regulators use the replica bias output to generate virtual supply voltages for the pre-driver ( $V_{PRE}$ ) and output driver ( $V_{DRV}$ ), respectively. These regulators are implemented using digital feedback loops, which help in storing states during the power-off event and in restoring states during power-on.

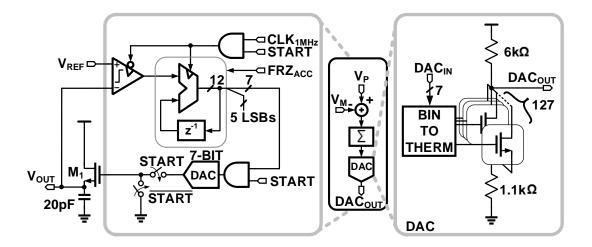

Figure 3.3 shows the schematic of the proposed digital voltage regulator. It consists of

Figure 3.3: Schematic diagram of the proposed digital voltage regulator.

a clocked comparator, an accumulator, and a resistive DAC.  $V_{OUT}$  is compared with  $V_{REF}$ , and the output is fed to the 12-bit accumulator. The accumulated output drives a 7-bit resistive DAC to minimize the error between  $V_{REF}$  and  $V_{OUT}$ . The lower 5LSBs of the accumulator output are ignored to reduce voltage ripple due to loop delay. The DAC uses high  $V_{th}$  transistors to avoid leakage in the off-state. A 1.1k ohm resistor at the bottom of the DAC provides desired voltage offset. A 20pF decoupling capacitor at the output of transistor  $M_1$  helps in suppressing noise on the output voltage. A large capacitor helps in suppressing more noise, but it increases the power-on time and the energy consumed during power-on/off cycle.

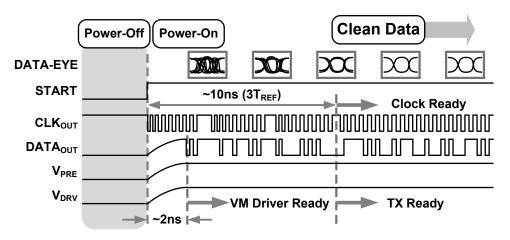

### 3.2.1 Power-On Transient Response of the Transmitter

Figure 3.4 shows the transient response of the transmitter. When the START signal is de-asserted, the pre-driver and output driver regulators output  $V_{PRE}$  and  $V_{DRV}$  nodes are discharged to ground. The gates of transistors  $M_1$  and  $M_2$  are pulled low (see Fig. 3.2), the clock to all comparators is gated, and bias current of the replica bias block is turned off. In this state, only the leakage current in digital logic contributes to off-state power consumption. During the off-state, regulator states are saved in their respective accumulators.

When the START signal is asserted, the DACs rapidly restore the accumulator's state

Figure 3.4: Transient response of the proposed fast power-on lock transmitter.

and set the gate voltages of transistors  $M_1$  and  $M_2$ , which quickly bring  $V_{PRE}$  and  $V_{DRV}$  to the desired value. The 20pF decoupling capacitor charges up in 2ns, after which the driver is ready for transmitting data. The MDLL based clock multiplier limits the transmitter start-up time, which takes around 10ns (three reference cycles) to start.

During the power-on state, the PMOS diode (M<sub>3</sub>) in the replica bias settles slowly with a large time constant. This results in a slow settling of  $V_{REPLICA}$  and  $V_{SWING}$  nodes after power-on. To avoid the effect of these variations on the regulator output ( $V_{PRE}$  and  $V_{DRV}$ ), the accumulators of pre-driver and output driver regulators are frozen using  $FRZ_{PRE}$  and  $FRZ_{DRV}$  signals. Once the  $V_{REPLICA}$  and  $V_{SWING}$  nodes settle, the  $FRZ_{PRE}$  and  $FRZ_{DRV}$  signals are de-asserted, and the regulators go back in closed-loop operation.

#### 3.2.2 Effect of Power Supply Droop on Output Driver

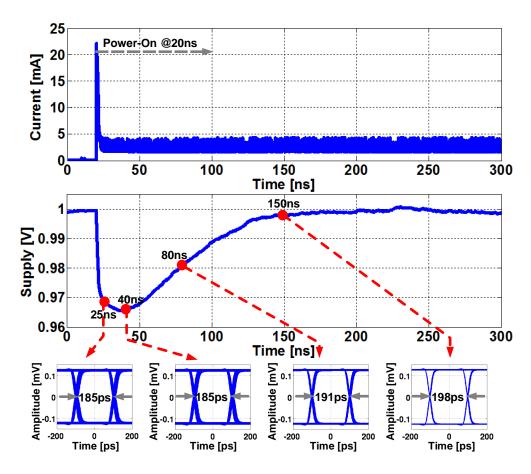

Burst mode operation requires fast load transient response linear regulators [38–40] to power the transmitter. When the output driver is powered-on, the output of the regulator droops momentarily before regaining its original value. The amount of droop and transient response time are a function of loop dynamics of an external regulator and current step. To capture this effect, the output driver including the multiplexer is simulated with a fast load transient response regulator. Figure 3.5 shows the current step, power supply droop and the output eye diagram at various time instants. Droop in the power supply increases output jitter,

Figure 3.5: Simulated power supply droop on the output driver.

which will eventually reduce the sampling margin on the receiver.

# 3.2.3 Fast Power-On Clock Multiplier

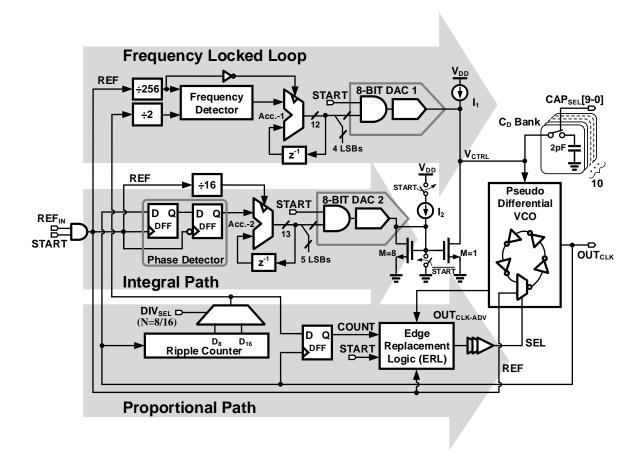

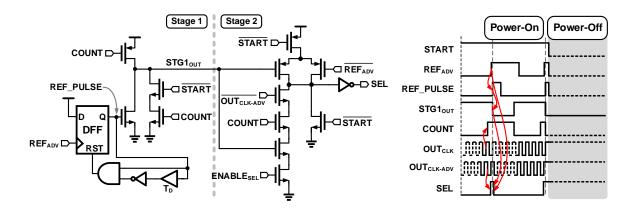

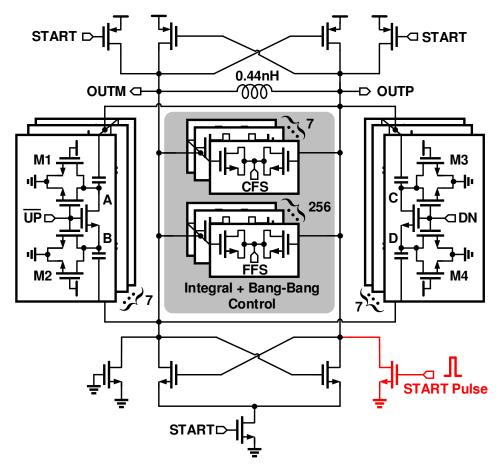

Figure 3.6 shows the block diagram of the proposed MDLL based digital clock multiplier. It employs a split tuned architecture in which a frequency locked loop (FLL) drives the ring oscillator close to the frequency lock, and an integral control that brings the oscillator frequency to the desired output frequency. The proportional path ensures stability by periodically resetting the oscillator output phase with the input reference clock phase using edge replacement logic (ERL). Frequency locked loop consists of a frequency detector, 12-bit accumulator clocked at  $F_{REF}/256$ , fast settling DAC and a constant current source  $I_1$ . Integral path uses a bang-bang phase detector, 13-bit accumulator, and 8-bit DAC. The phase

Figure 3.6: Schematic diagram of the proposed fast power-on MDLL based digital clock multiplier.

detector consisting of two D flip-flops, clocked at the reference frequency, produces lead/lag phase information with a 1-bit output. The accumulator clocked at  $F_{REF}/16$  integrates the sub-sampled bang-bang phase detector output. Sub-sampling has no adverse effect on the jitter performance because the accumulated sub-sampled output is used only to track frequency drifts due to voltage and temperature changes during normal operation that are slower than  $F_{REF}/16$ .

The proportional path consists of a programmable divider and edge replacement logic (ERL). The edge replacement logic generates a narrow SEL signal pulse, which opens up the ring oscillator momentarily and passes the clean reference edge. To have a perfect edge replacement, care is taken to generate the SEL signal with sharp rise and fall times.

The digital accumulators store the frequency information of the oscillator in the digital

form during the power-off state. They are synthesized with high  $V_{th}$  devices to reduce leakage. Four LSBs from the frequency locked loop accumulator and five LSBs from the fine integral path accumulator are ignored to avoid ripple on control voltage node,  $V_{CTRL}$ , due to loop delay. To reduce the power-on time penalty caused by slow settling transients, the DAC bias circuitry is not turned-off in the power-off state. The bias voltages are maintained at the expense of a small power penalty during the off-state. When the MDLL is powered-on, the frequency information is rapidly restored to the oscillator using fast Nyquist-rate DACs, thus bringing the oscillator to frequency lock quickly. Once frequency lock is achieved, the rising edge of the reference replaces the  $N^{th}$  oscillator edge thus achieving instantaneous phase lock.

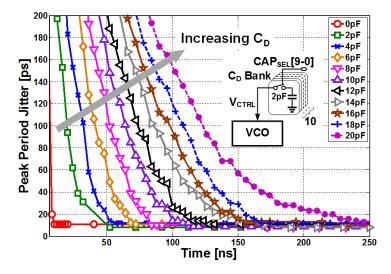

Periodic edge replacement results in current being drawn periodically from  $V_{CTRL}$ , thereby causing a supply ripple at the reference frequency and its harmonics. Despite the pseudo differential nature of VCO, current drawn by VCO is not constant, which causes a ripple on  $V_{CTRL}$ . Deterministic jitter (DJ) resulting from  $V_{CTRL}$  ripple can be reduced with a decoupling capacitor. However, a large decoupling capacitor increases the time constant on the  $V_{CTRL}$  node, thereby increasing the time it takes for the frequency to settle to the right value, which eventually increases power-on lock time. To quantify this trade-off between DJ and power-on lock time, a bank of programmable decoupling capacitor ( $C_D$  bank) is added on the  $V_{CTRL}$  node and the measured results are presented in Section 3.5.

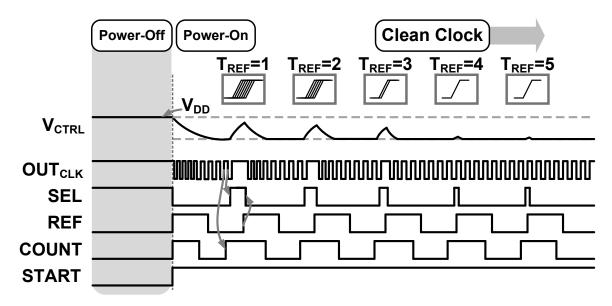

#### 3.2.4 Power-On Transient Response of the Clock Multiplier

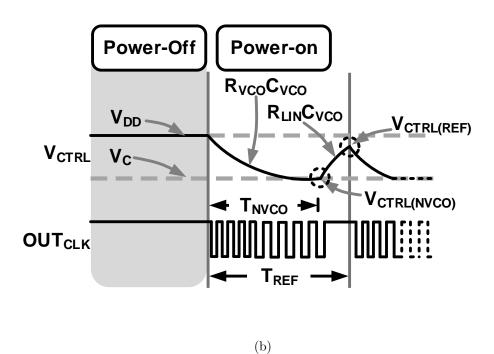

Figure 3.7 shows the power-on transient response of the proposed clock multiplier. When the multiplier is powered-off, REF signal is gated, SEL signal is asserted high, and the VCO stops oscillating. Once the VCO is open, it no longer sinks current. This causes the  $V_{CTRL}$  node to charge up to  $V_{DD}$ , which eventually shuts down current source  $I_1$ . When the multiplier is powered-on, the SEL signal is de-asserted, and the VCO starts to oscillate. The  $V_{CTRL}$  node then settles to the desired value with a finite time constant. During the time when the  $V_{CTRL}$  node is settling, the VCO oscillates at a higher frequency, which causes the rising edge of the divider output COUNT signal to appear earlier than desired. On the

Figure 3.7: Transient response of the proposed fast power-on clock multiplier.

rising edge of the COUNT signal, the SEL signal is asserted high, and the VCO opens up and waits for the rising edge of the REF signal to pass through. During this waiting period, VCO stops, and the  $V_{CTRL}$  node again rises toward  $V_{DD}$ . On the subsequent rising edge of the reference, the SEL signal is de-asserted, and the VCO begins to oscillate again. In the second reference cycle, the  $V_{CTRL}$  node again settles to the desired value but the initial high oscillation frequency again causes a rising edge of the divider output COUNT signal to appear earlier than desired. However, this time it appears closer to the rising edge of the reference signal, which causes smaller disturbance on the  $V_{CTRL}$  node. This results in smaller oscillator frequency variation as compared to the first reference cycle. In the third reference cycle, the disturbance on the  $V_{CTRL}$  node is even smaller, and the multiplier is close to achieving frequency and phase lock. Thus, in the proposed MDLL architecture, the power-on time is mainly limited by the time constant on the  $V_{CTRL}$  node.

# 3.3 Power-On Transient Modeling of MDLL

MDLL in the locked state satisfies the following relationship:  $N.T_{VCO} = T_{REF}$ , where N is the multiplication ratio,  $T_{VCO}$  is the VCO's time period, and  $T_{REF}$  is the reference clock time period. However, while acquiring a lock, the  $V_{CTRL}$  node varies, and  $T_{VCO}$  does not

remain constant for all N VCO cycles (see Fig. 3.7). Consequently N VCO cycles finish earlier than expected. The accumulated jitter,  $T_j$ , during N VCO cycles can be written as

$$T_j = T_{REF} - T_{NVCO} \tag{3.1}$$

where  $T_{NVCO}$  is the time required to complete N VCO cycles and can be written as

$$T_{NVCO} = \sum_{i=1}^{N} T_{VCOi} \tag{3.2}$$

where  $T_{VCOi}$  is the VCO's time period in the  $i^{th}$  VCO cycle. The MDLL is considered completely powered-on when  $T_j$  is below the desired value.

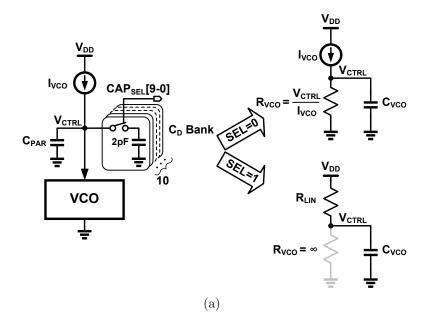

A simplified schematic diagram of VCO, for two SEL signal conditions, is shown in Fig. 3.8(a). The DAC and current source  $I_1$  are together shown as one current source  $I_{VCO}$ . The capacitors  $C_{PAR}$  and  $C_D$  are together shown as one capacitor,  $C_{VCO}$ , on the  $V_{CTRL}$  node. When the SEL signal is low, VCO is replaced with an equivalent resistor  $R_{VCO}$ , which sinks current  $I_{VCO}$ . When the SEL signal is high, the VCO no longer sinks current, and the  $V_{CTRL}$  node starts to settle toward  $V_{DD}$ . This causes the current source  $I_{VCO}$  transistor to operate in the linear region and is modeled as resistor  $R_{LIN}$ . The time constants on the  $V_{CTRL}$  node are  $R_{VCO}C_{VCO}$  and  $R_{LIN}C_{VCO}$  when the SEL signal is asserted low and high, respectively.

Figure 3.8(b) shows magnified startup transient during the first reference cycle. When the multiplier is powered-on, the instantaneous VCO's oscillation frequency is equal to

$$f_{VCO}(t) = K_V V_C + K_V (V_{DD} - V_C) e^{-t/\tau}$$

(3.3)

where  $K_V$  is the VCO's gain in Hz/V,  $V_C$  is the steady-state  $V_{CTRL}$  value and  $\tau = R_{VCO}C_{VCO}$  forms the VCO's time constant. Integrating (3.3) from 0 to  $T_{NVCO}$  gives

$$\int_{0}^{T_{NVCO}} f_{VCO}(t)dt = \int_{0}^{T_{NVCO}} K_{V}(V_{C} + (V_{DD} - V_{C})e^{-t/\tau})dt$$

(3.4)

$$\Rightarrow N = K_V(V_C T_{NVCO} + \tau (V_{DD} - V_C)(1 - e^{-T_{NVCO}/\tau}))$$

(3.5)

Figure 3.8: (a) Simplified schematic diagram of oscillator for modeling power-on transient. (b) Power-on transient of VCO during the first reference cycle.

For a given  $N, K_V, V_C, V_{DD}$  and  $\tau$ , equation (3.5) can be solved numerically for  $T_{NVCO}$ .  $T_j$  is obtained by substituting  $T_{NVCO}$  in (3.1). If  $T_j \neq 0$  then during time  $T_j$ , the  $V_{CTRL}$  rises toward  $V_{DD}$  with the time constant of  $R_{LIN}C_{VCO}$ . The voltage at  $V_{CTRL}$  at the end of the

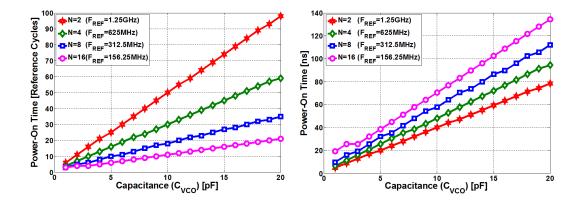

Figure 3.9: Modeling result of settling time in terms of reference cycles and absolute time versus  $C_{VCO}$  for various values of N (settled  $T_j$ ; 10ps).  $F_{VCO} = 2.5 \mathrm{GHz}$ ,  $V_C = 0.8 \mathrm{V}$ ,  $R_{VCO} = 1 \mathrm{K}$  ohm,  $K_V = 3.125 \mathrm{GHz/V}$ ,  $R_{LIN} = 4 \mathrm{k}$  ohm, and  $V_{DD} = 1.1 \mathrm{V}$ .

first reference cycle is given as

$$V_{CTRL(REF)} = V_{DD} - (V_{DD} - V_{CTRL(NVCO)})e^{-T_j/R_{LIN}C_{VCO}}$$

(3.6)

where  $V_{CTRL(NVCO)}$  is  $V_{CTRL}$  at the end of first N VCO cycles and is written as

$$V_{CTRL(NVCO)} = V_C + (V_{DD} - V_C)e^{-T_{NVCO}/\tau}$$

(3.7)

In the second reference cycle,  $V_{CTRL}$  settles toward  $V_C$  starting from  $V_{CTRL(REF)}$ . By using (3.1) and (3.5) and replacing  $V_{DD}$  with  $V_{CTRL(REF)}$ ,  $T_j$  is calculated for the second reference cycle. This process is continued until  $T_j$  reaches below the desired value.

Equations (3.1)-(3.7) were coded in Matlab, and the plot of power-on time in terms of reference cycles and absolute time as a function of  $C_{VCO}$  for various multiplication ratios N is shown in Fig. 3.9. The settling time increases linearly with  $C_{VCO}$ . For small values of  $C_{VCO}$  (smaller time constant  $R_{VCO}C_{VCO}$ ), the  $V_{CTRL}$  settles to  $V_C$  before completing N VCO cycles. As a result, the value of  $T_j$  at the end of first few reference cycle stays independent of the multiplication factor N. Hence, for small time constants and a fixed VCO frequency, the number of reference cycles to power-on the MDLL is independent of the multiplication factor N.

For large values of  $C_{VCO}$  and small multiplication factor N, VCO's time constant  $\tau$

Figure 3.10: Schematic diagram of the voltage controlled oscillator.

$(R_{VCO}C_{VCO})$  becomes comparable to the reference time period  $T_{REF}$ . Consequently, for initial few reference cycles, the  $V_{CTRL}$  node does not settle all the way to  $V_C$  at the end of N VCO cycles. As a result, in this case, the value of  $T_j$  depends on the multiplication factor N. Smaller N will have large  $T_j$  at the end of first few reference cycle. Therefore, an MDLL with a smaller multiplication factor N takes a few more reference cycles to power-on. However, in terms of absolute settling time, for a fixed VCO frequency, a smaller multiplication factor N corrects the MDLL's output phase more often and results in smaller power-on time.

# 3.4 Clock Multiplier Building Blocks

# 3.4.1 Voltage Controlled Oscillator (VCO)

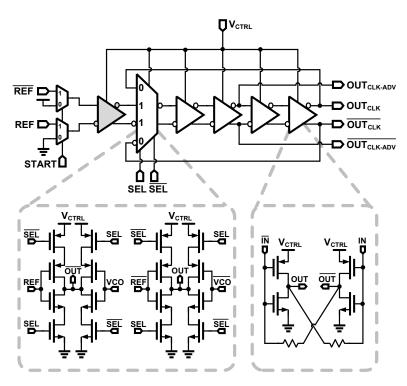

A schematic diagram of VCO is shown in Fig. 3.10. It consists of five stages connected in a ring configuration. One of these five stages is an inverting multiplexer and the other four are cross-coupled inverters. The  $OUT_{CLK-ADV}$  signal is tapped from the middle of the VCO.

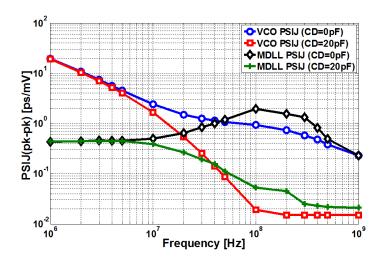

Figure 3.11: Simulated power supply induced jitter (PSIJ) of VCO (including DAC) and MDLL.

This signal is used to meet timing requirements in the edge replacement logic. The REF signal to the multiplexer is driven by a VCO delay cell, shown as a shaded cell in Fig. 3.10. Passing the REF signal through the VCO buffer matches the rise time of the REF edge with the  $OUT_{CLK}$  edge resulting in a lower reference spur at the output. The choice of five stages in the oscillator was made carefully to achieve sharp rise and fall times, which helps in reducing deterministic jitter caused due to imperfect reference edge replacement. Resistive cross coupling on the multiplexer was avoided to reduce noise coupling from the  $OUT_{CLK}$  edge to the clean REF edge during the edge replacement operation. The choice of pseudo-differential stages was made to achieve a smaller self-induced ripple on the  $V_{CTRL}$  node, resulting in better jitter performance with a smaller decoupling capacitor. When simulated at  $2.5 \,\text{GHz}$ , the VCO consumes approximately  $550 \mu\text{A}$  from a  $1.1 \,\text{V}$  supply.

Power supply induced jitter (PSIJ) of the VCO (including DACs) and MDLL are a strong function of decoupling capacitor  $C_D$  on the  $V_{CTRL}$  node. The simulated  $PSIJ_{pk-pk}$  value for  $C_D = 0$ pF and 20pF is shown in Fig. 3.11. At 100MHz sinusoidal supply disturbance, simulated  $PSIJ_{pk-pk}$  of MDLL for  $C_D = 0$ pF and 20pF is 2ps/mV and 0.053ps/mV, respectively. At 1MHz sinusoidal supply disturbance, simulated  $PSIJ_{pk-pk}$  of MDLL for  $C_D = 0$ pF and 20pF is 0.43ps/mV.

Figure 3.12: Schematic and timing diagram of the proposed edge replacement logic (ERL).

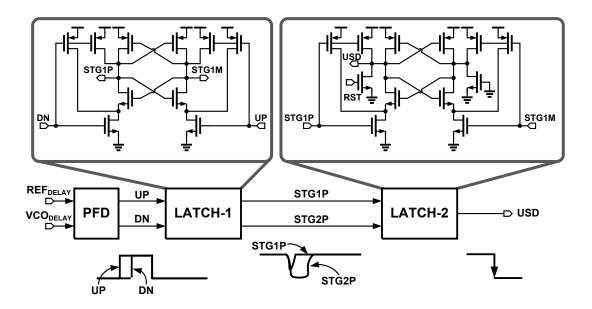

#### 3.4.2 Edge Replacement Logic (ERL)

Edge replacement logic is responsible for generating a narrow pulse to pass the clean reference edge every  $N^{th}$  VCO cycle. The width of this pulse is typically  $T_{VCO}/2$ . Conventional select logic requires synchronous thermometric counter running at VCO frequency to generate periodic pulses of one VCO period width [32]. However, running a synchronous counter at VCO frequency results in large power dissipation. Moreover, the initial VCO frequency is required to be higher than  $N*F_{REF}$ , which limits this circuit [32] to be used for fast power-on applications where the VCO frequency is very close to  $N*F_{REF}$  during power-on. During normal operation, the SEL signal must be de-asserted after the rising edge of REF signal and before the falling edge of the VCO output, and within time  $T_{VCO}/4$  in the best case. The select logic in [36] avoids thermometric counter but suffers from  $T_{REF\uparrow-SEL\downarrow}$  timing constraint, which is difficult to meet at higher VCO frequencies. In this work, the proposed ERL employ ripple counter to reduce power consumption and uses advanced reference signal to overcome the  $T_{REF\uparrow-SEL\downarrow}$  timing constraint.

Figure 3.12 shows the schematic and timing diagram of the proposed ERL circuit. When the COUNT signal is low, the output of the first stage,  $STG1_{OUT}$  is pre-charged to logic high. After the completion of N VCO cycles, the COUNT signal is asserted high. The SEL signal is asserted high on the falling edge of  $OUT_{CLK-ADV}$ . The SEL signal opens up the oscillator and waits for the REF rising edge to pass. The  $REF_{ADV}$  signal is generated by tapping the REF signal before the delayed REF goes into the VCO. On the rising edge of

Figure 3.13: Schematic and timing diagram of the Nyquist-rate DAC.

the  $REF_{ADV}$ , the output of Stage 1 is discharged, and the SEL signal is de-asserted. The timing by which the  $REF_{ADV}$  signal must be advanced with respect to the REF signal is given by the following equation:

$$T_{REFADV\uparrow -REF\uparrow} = T_{REFADV\uparrow -SEL\downarrow} - T_{VCO/4}$$

(3.8)

where  $T_{REFADV\uparrow-SEL\downarrow}$  is the time between the  $REF_{ADV}$  rising edge to the SEL falling edge.

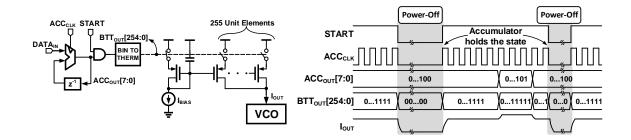

#### 3.4.3 DAC

Delta-sigma DACs followed by post filter offer a compact way to achieve high-resolution frequency control of the VCOs. However, a large time constant of the post-filter increases the frequency settling time. The proposed Nyquist-rate DAC and its timing diagram is shown in Fig. 3.13. The DAC is implemented using thermometer-coded current-mode architecture to ensure monotonicity and fast settling. Single-ended source switched PMOS current elements are used to minimize area. By employing current mode Nyquist-rate DACs, use of low bandwidth post filter is avoided, thereby achieving high bandwidth to rapidly set VCO frequency during power-on/off events. When the system is powered-off, the clock to the accumulator is gated, and the accumulator holds its state. De-asserting the START signal causes the output of binary to thermometric logic to go down to zero, which shuts down the DAC. When the system is powered-on, the previous state of the DAC is restored, and  $I_{OUT}$  quickly reaches the desired value.

The choice of DAC's resolution and frequency tuning range is governed by tolerable fre-

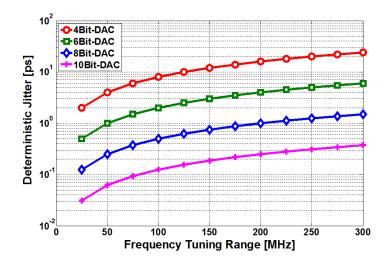

Figure 3.14: Simulated deterministic jitter as a function of frequency tuning range for N=8 and  $F_{VCO}=2.5\mathrm{GHz}$ .

quency quantization error. Frequency quantization error results in the accumulation of VCO phase for one reference cycle, which results in deterministic jitter and consequently reference spurs. For a given DAC resolution and frequency tuning range, deterministic jitter  $\phi_{DJ}$  can be estimated mathematically as follows:

$$\phi_{DJ} = \frac{F_{TUNE}.N.T_{VCO}}{2^{DAC-BIT}.F_{VCO}} \tag{3.9}$$

where  $F_{TUNE}$  is the frequency tuning range, N is the frequency multiplication factor, DAC-BIT is the size of DAC,  $F_{VCO}$  is the VCO frequency, and  $T_{VCO}$  is the VCO period. Using (3.9), the plot of deterministic jitter as a function of frequency tuning range for various DAC sizes is shown in Fig. 3.14. Increasing the DAC resolution on the one hand reduces the frequency quantization error, and on the other hand it increases the area and parasitic capacitance on the  $V_{CTRL}$  (virtual supply node of VCO), which eventually increases the power-on time of MDLL. Design of fast power-on MDLL with wide frequency tuning range VCO remains a challenging problem. In the proposed architecture, an 8 bit integral path DAC provides up to 125MHz of tuning range.

Figure 3.15: Die micrograph of the proposed transmitter.

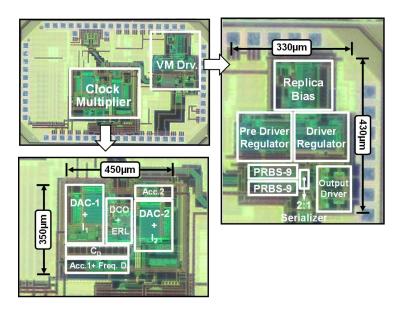

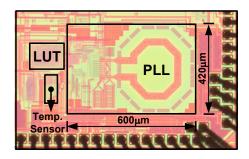

#### 3.5 Measurement Results

The die micrograph of the prototype transmitter, implemented in a 90nm CMOS process, is shown Fig. 3.15. It occupies an active area of  $0.3\text{mm}^2$  of which the voltage mode driver occupies  $0.14\text{mm}^2$  (330 $\mu$ m x 430 $\mu$ m) and the MDLL occupies  $0.16\text{mm}^2$  (450 $\mu$ m x 350 $\mu$ m). The chip is packaged in a 48-pin QFN plastic package.

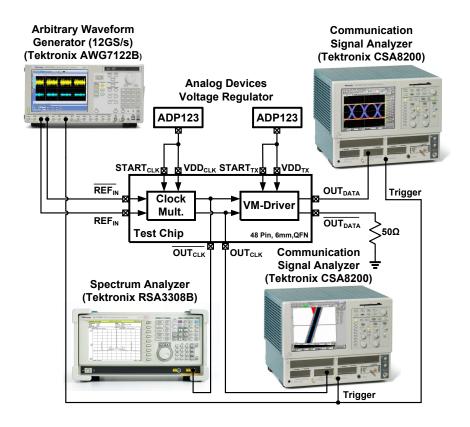

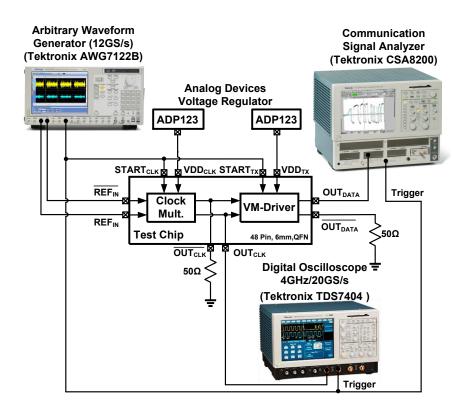

Measurement setups to measure the transmitter in an always-on, and in rapid-on/off mode are shown in Fig. 3.16 and Fig. 3.17, respectively. The reference clock for the clock multiplier is generated from an arbitrary waveform generator (Tektronix AWG7122B), and the output spectrum and jitter of the MDLL is measured on a spectrum analyzer (Tektronix RSA3308B) and communication signal analyzer (Tektronix CSA8200), respectively. Reference is used as a trigger signal for Tektronix CSA8200. The transmitter output eye is measured on Tektronix CSA8200 with reference as a trigger signal. The transmitter is powered using a set of linear voltage regulators manufactured by the Analog Devices (part# ADP123).

In the case of rapid-on/off measurements, the transmitter is power cycled using a START signal, which is generated from the AWG7122B, and the same START signal is used as a trigger to capture the output transient of the transmitter on a communication signal analyzer (Tektronix CSA8200). The MDLL's settling behavior (in this case, period jitter) is measured

Figure 3.16: Measurement setup for always-on measurements.

by capturing the  $OUT_{CLK}$  signal on an oscilloscope (Tektronix TDS7404).

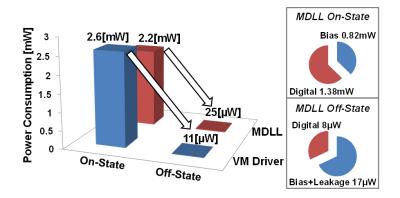

A wide range of measurements were conducted to quantify the trade-offs between performance and power-on time. For all the measurements, a multiplication ratio of 8, the reference frequency of 312.5MHz and a 0pF decoupling capacitor ( $C_D$ ) for MDLL were used, unless otherwise stated. At 5Gb/s, the transmitter consumes 4.8mW (excluding PRBS generators) with the voltage mode driver consuming 2.6mW from a 1V supply and the MDLL consuming 2.2mW from a 1.1V supply. Figure 3.18 shows the on-state and off-state power break-up of the transmitter. In the power-off state the transmitter consumes  $33\mu$ W of which  $11\mu$ W is consumed by the voltage mode driver and  $25\mu$ W by the MDLL. Off-state power in the voltage mode driver is largely due to leakage in digital circuits such as accumulators and multiplexers. In MDLL, out of the measured 2.2mW on-state power, 1.38mW is consumed in the digital logic, and the remaining 0.82mW is consumed in the DACs and the oscillator. In the off-state, out of measured  $25\mu$ W,  $17\mu$ W is consumed in bias circuits and leakage in

Figure 3.17: Measurement setup for on/off measurements.

Figure 3.18: Measured power breakup of the proposed transmitter.

DAC's decoder logic, and  $8\mu W$  is due to leakage in the rest of logic circuits.

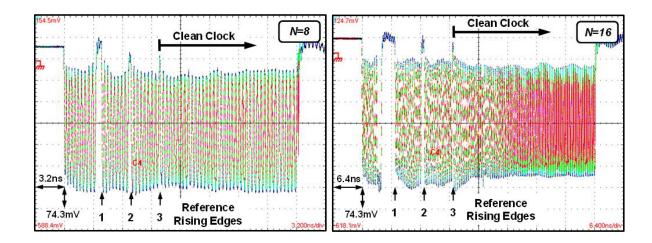

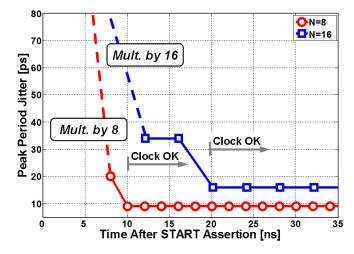

Figure 3.19 shows the captured transient of 2.5GHz clock waveform, while power cycling the MDLL for a multiplication factor of 8(312.5MHz reference) and 16(156.25MHz reference). Figure 3.20 plots the measured peak period jitter versus power-on time. In both cases,

Figure 3.19: Measured power-on/off transient of the proposed MDLL for multiplication factors of 8 and 16.

Figure 3.20: Measured period jitter of the proposed MDLL for multiplication factors of 8 and 16.

the MDLL locks in approximately three reference cycles. Mathematically, it was shown in Section 3.3 that a small time constant on the  $V_{CTRL}$  node makes settling time, in terms of reference cycles, to be independent of the multiplication factor N.

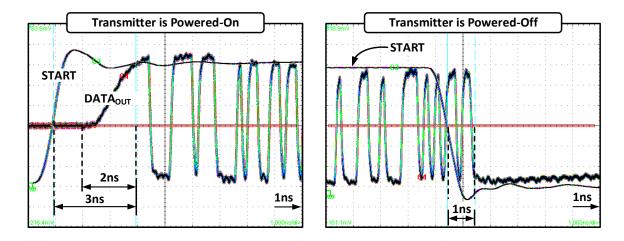

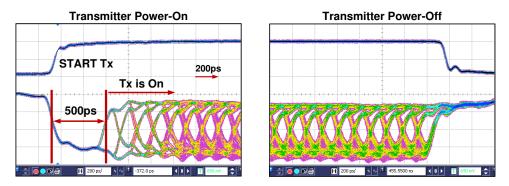

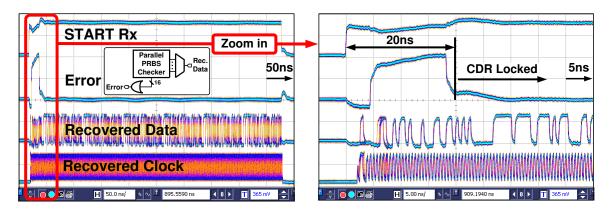

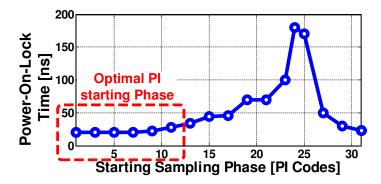

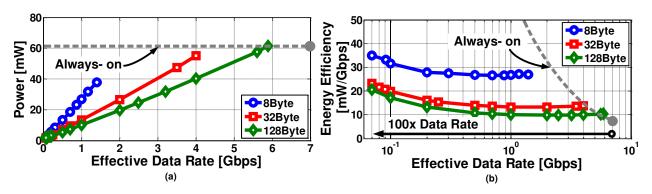

Figure 3.21 shows the captured  $DATA_{OUT}$  and START signals while power cycling the transmitter. The delay difference between the START signal captured on the CSA8200 and the one which goes inside the chip is 1ns, as seen in the power-off event. The measured power-on time of the voltage mode driver is around 2ns and is dominated by the time needed to charge 20pF decoupling capacitors of the output driver and per-driver regulators. The

Figure 3.21: Measured power-on/off transient of the proposed transmitter.

Figure 3.22: Measured power consumption and energy-per-bit of the proposed transmitter as a function of effective data rate for various burst lengths in bytes.

voltage mode driver thus does not limit the power-on time of the whole transmitter. The power-on time is limited by the MDLL's power-on time, which is 10ns. The measured energy overhead of power cycling is 44pJ of which 32pJ is consumed in the voltage mode driver and the remaining 12pJ in the MDLL. Charging and discharging of capacitors on  $V_{DRV}$  and  $V_{PRE}$  nodes (see Fig. 3.2) are the major contributors to this overhead.

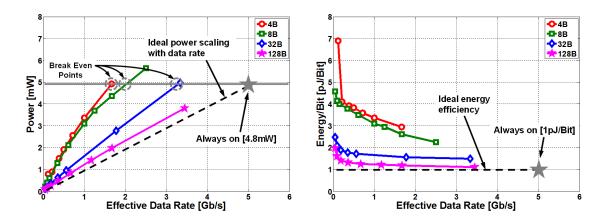

Figure 3.22 plots the power consumption and energy efficiency of the transmitter versus effective data rate for different data burst lengths (in bytes). Ideally, the power consumption must scale linearly with the data rate, as shown by dashed line in the power consumption versus effective data rate plot. However, the power overhead due to power cycling and finite

Figure 3.23: Measured eye diagram of the proposed transmitter at 5Gb/s with PRBS9 output data.

power-on time increases the slope of the power versus the effective data rate curve at smaller burst lengths (4 bytes). For longer burst lengths, the power overhead due to power cycling is a smaller portion of the total power consumed during data transmission. Therefore, energy proportional behavior, which is closer to the ideal case, is achieved. For 128 byte packet size, the power consumption varies from 4.8mW to 0.095mW (50x change) and the energy efficiency varies from 1pJ to 2pJ (2x change) when the effective data rate varies from 5Gb/s to 48Mb/s (100x change). The 32 byte packet size data burst reaches the break-even power point at 3.33Gb/s, and any increase in the bandwidth demand beyond this point must be met by keeping the transmitter in an always-on state.

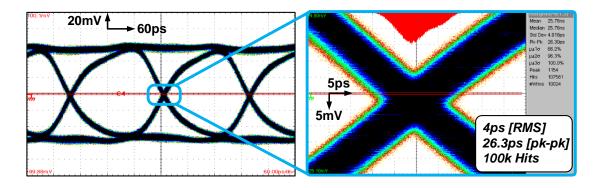

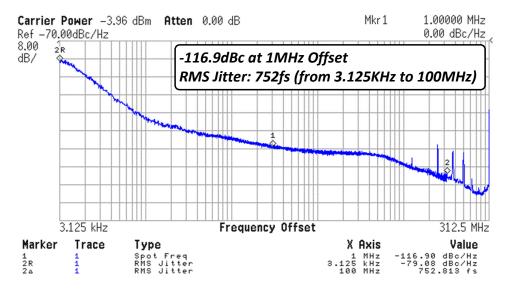

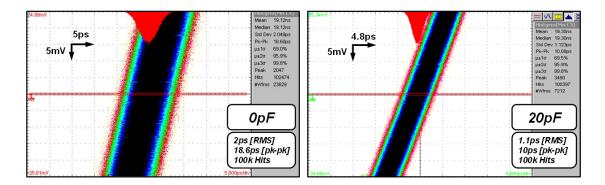

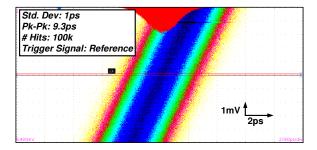

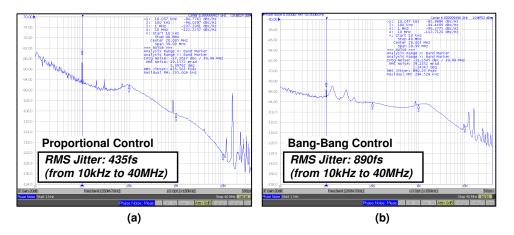

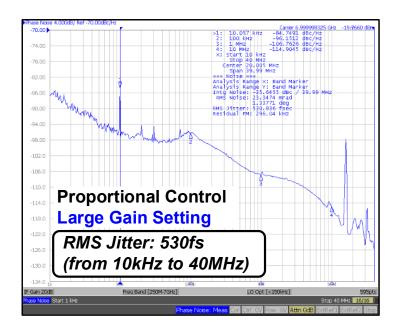

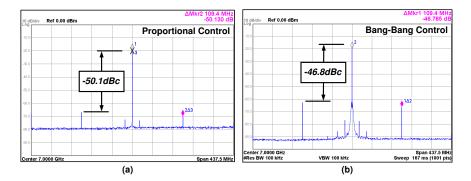

Figure 3.23 shows the captured transmitter output eye diagram with the PRBS9 data. The differential output swing is  $250mV_{ppd}$ , and the measured long-term jitter is  $4ps_{rms}$  and  $26.3ps_{pk-pk}$  with 100k hits. Figure 3.24 shows the MDLL output phase noise plot at 2.5GHz. The measured phase noise at 1MHz offset is -116.9dBc/Hz and the jitter obtained by integrating phase noise from 3.125KHz to 100MHz is 752fs.

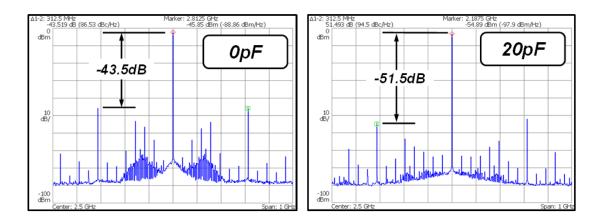

The trade-off between power-on time and jitter performance is measured using programmable capacitor bank  $C_D$  (see Fig. 3.6). Figure 3.25 shows the measured period jitter for different decoupling capacitor values. These measurements were conducted by enabling the capacitors one at a time while the MDLL is power cycled. As expected, a big decoupling capacitor increases the power-on time by increasing the time for the control voltage  $V_{CTRL}$  to settle. The measured settling time is 256ns for a 20pF capacitor and 10ns for 0pF capacitor.

Figure 3.24: Measured phase noise spectrum of the proposed MDLL at 2.5GHz output frequency.

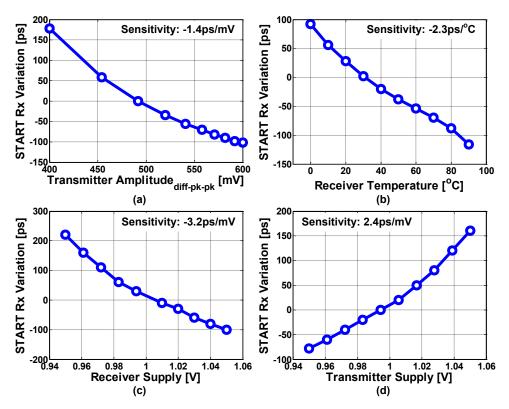

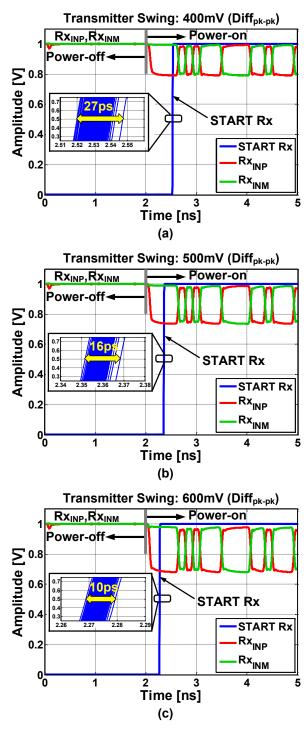

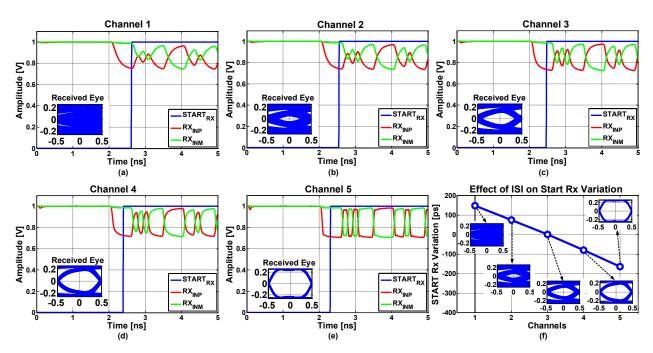

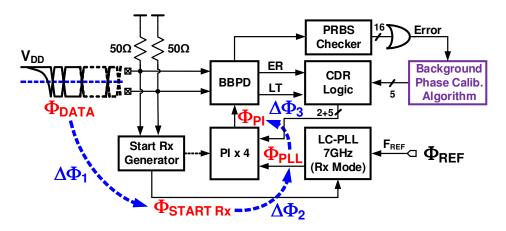

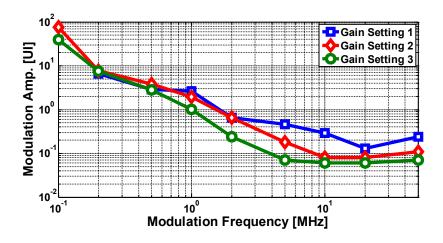

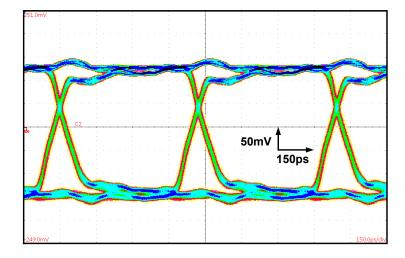

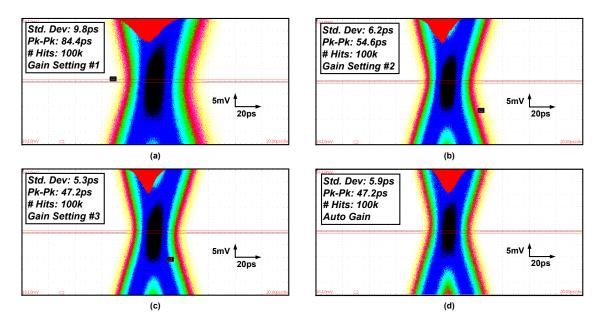

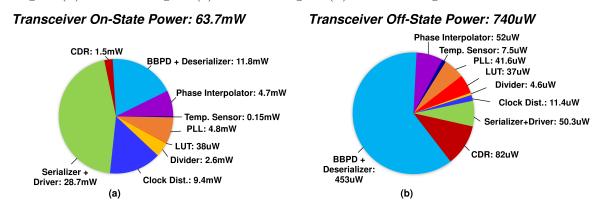

Figure 3.25: Measured peak period jitter as a function of time for different decoupling capacitor  $(C_D)$  settings.