# ARCHITECTURAL & CIRCUIT LEVEL TECHNIQUES TO IMPROVE ENERGY EFFICIENCY OF HIGH SPEED SERIAL LINKS

#### BY

#### SAURABH SAXENA

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2015

Urbana, Illinois

#### Doctoral Committee:

Associate Professor Pavan Kumar Hanumolu, Chair Professor Jose E. Schutt-Aine Professor Naresh R. Shanbhag Professor Pramod Viswanath

## Abstract

High performance computing and communication are two key aspects of all information processing systems. With aggressive scaling of silicon technology enabling integration of a large number of transistors in a small area, managing power and thermal reliability has become very challenging. While lowering the power needed for performing computation has been the prime focus for decades, energy consumed for data transfer has recently become a major bottleneck especially in high performance applications. The focus of this thesis is on improving energy efficiency of communication links by exploring design techniques at both the architectural and circuit levels.

In the first part of this work, we propose a time-based equalization scheme to implement transmit de-emphasis in voltage-mode output drivers. Using two-level pulse-width modulation, it overcomes the tradeoff between impedance matching, output swing, and de-emphasis resolution in conventional voltage-mode drivers. A prototype PWM-based  $5\,\mathrm{Gb/s}$  voltage-mode transmitter was implemented in a  $90\,\mathrm{nm}$  CMOS process and characterized across different channels and output swings to demonstrate the effectiveness of proposed techniques. The horizontal/vertical eye openings (BER= $10^{-12}$ ) at the ends of  $60\,\mathrm{inch}$  and  $96\,\mathrm{inch}$  stripline channels are  $78\,\mathrm{mV/0.6\,UI}$  and  $8\,\mathrm{mV/0.3\,UI}$ , respectively. This transmitter achieves an energy efficiency of  $3.1\,\mathrm{mW/Gb/s}$  while compensating for  $16\text{-}28\,\mathrm{dB}$  channel loss, which compares favorably with the state-of-the-art.

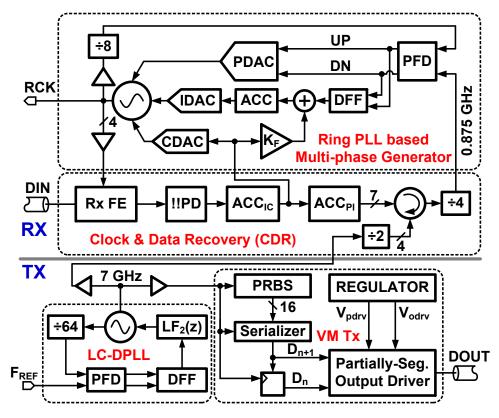

In the second part, techniques to improve energy efficiency of a complete transceiver are presented. The transmitter employs a novel partially segmented voltage-mode output driver to lower power consumption in pre-drivers during 2-tap FIR equalization. The receiver implements a low power half-rate clock and data recovery with the proposed ring PLL based multi-phase sampling clock generation in CDR loop and charge-based sampling and descri-

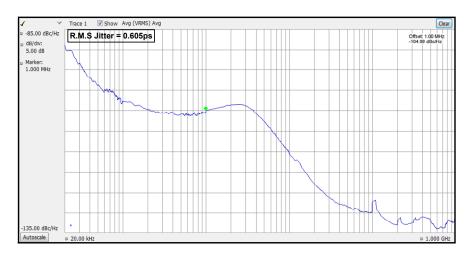

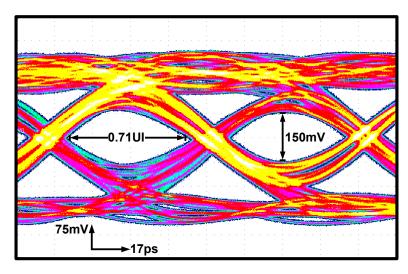

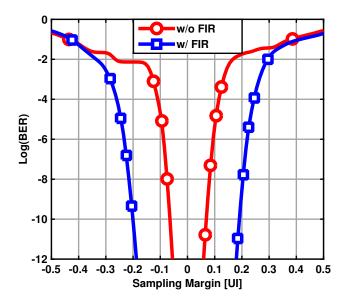

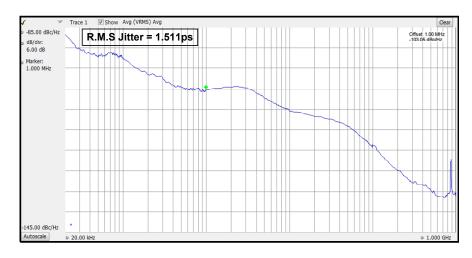

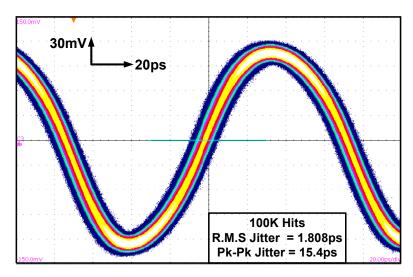

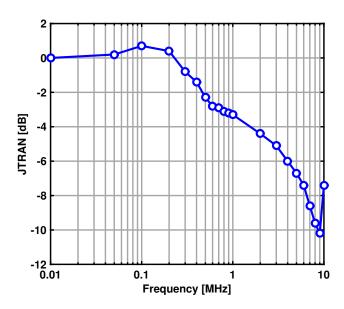

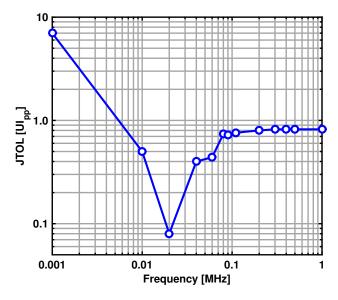

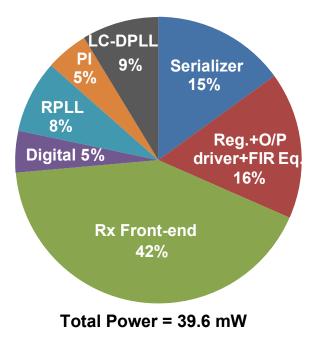

alization. These techniques are verified using the measured results obtained from a 14Gb/s transceiver prototype. Transmitter achieves an energy efficiency of  $0.89\,\mathrm{mW/Gb/s}$  while securing a  $0.36\,\mathrm{UI}$  sampling time margin with BER =  $10^{-12}$  at the end of the channel with 11 dB loss at Nyquist frequency. The receiver recovers sampling clock with  $1.8\,\mathrm{ps_{rms}}$  long term absolute jitter while recovering 14 Gb/s data at BER =  $10^{-12}$ . The receiver achieves an energy efficiency of  $1.69\,\mathrm{mW/Gb/s}$ . Transmitter and receiver share an LC PLL, which achieves  $0.605\,\mathrm{ps_{rms}}$  integrated jitter at 7 GHz output with an energy efficiency of  $0.5\,\mathrm{mW/GHz}$ . The transceiver as a whole achieves an energy efficiency of  $2.8\,\mathrm{mW/Gb/s}$ .

## Acknowledgments

I thank Professor Pavan Hanumolu, my research advisor, for walking with me on this wonderful journey of research spread over six short years. I am grateful for the opportunity and freedom he has given me to explore and crystallize my research interests during the Ph.D. As a curious colleague and an enlightened advisor, he kept me inspired through all the seasons of learning. For a circuit designer, nothing could be more troubling than a dysfunctional chip designed over a long year, but rarely does any circuit work well at the first shot. In such awful moments of a non-working chip, he could easily pull me out with his insightful debugging schemes and focus on learning even with a failing chip. Learning from Professor Hanumolu seems a never ending curve whether it is research, teaching, writing, or presentation. According to him, my current drawings have improved 1000X over my first drawing, but there is a scope of 1000X more improvement. I hope I learn that too someday.

I still remember the first day of my graduate school and meeting with Professor Kartikeya Mayaram. The first thing he inquired was about my well being and settling in a new country. I would like to thank Professor Mayaram and Professor Terri Fiez for exposing me to different research fields and for the opportunity to work in their research group at Oregon State University. I am grateful to my professors for their invaluable suggestions and support, helping me pursue research in the field of my choice.

One thing which I should confess during my Ph.D. is my addiction to coffee with friends. Space and time were the only variables and friends for coffee seemed the rescue for every problem, personal or professional. I would like to elaborate on the coffee with friends because coffee trips deeply involved discussions of all kinds. In coffee trips, day-long problems could get solved, a new idea might spring from single discussion, a far-fetched idea could be materialized with inputs from everyone around, and round-the-globe information maintained

the sanity. I dare to confess the names of all accomplices for my coffee addiction and they include Romesh, Mrunmay, Woo-Seok, Guanghua, Seong-Joong, Ahmed, Charlie, Sachin, Reddy, Hariprasath, and Manideep. I would like to thank Brian for insightful discussions in the early morning hours and Tejasvi for sharing his research experience during health-conscious lunches. Apart from friends in my research group, I would like to thank Ankita and Deepak for being like family members throughout my Ph.D. Thank you all my friends for making my stay at school to be ever cherished in my life.

I would like to express my deepest gratitude to my parents, brother, and sister for their sacrifice, love, and support throughout this endeavor. Though I moved from a small town in India to a faraway place in United States for my Ph.D., my brother and sister-in-law residing in the US did not leave me feeling away from home. I would like to thank them for their love and friendship.

# Table of Contents

| List of 7 | Tables                                                              | vii     |

|-----------|---------------------------------------------------------------------|---------|

| List of F | Figures                                                             | iii     |

| _         | 1 Introduction                                                      | 1       |

| 1.1       | Basics of a Serial Link                                             | 4       |

| 1.2       | Channel                                                             | 7       |

| 1.3       | Serial Link Performance Metrics                                     | 7       |

| 1.4       | Research Trends in Serial Links                                     | 8       |

| Chapter   | 2 Overview of Serial Links                                          | 13      |

| 2.1       | Transmitter                                                         | 13      |

| 2.2       | Receiver                                                            | 18      |

| Chapter   | 3 An Energy-Efficient Voltage-Mode Tx Using PWM-Based De-Emphasis . | 23      |

| 3.1       |                                                                     | -<br>23 |

| 3.2       |                                                                     | -<br>30 |

| 3.3       | <u>.</u>                                                            | 37      |

| 3.4       |                                                                     | 43      |

| Chapter   | 4 A 14 Gb/s Wireline Transceiver                                    | 45      |

| 4.1       |                                                                     | 47      |

| 4.2       | V                                                                   | 54      |

| 4.3       |                                                                     | 65      |

| 4.4       |                                                                     | 68      |

| 4.5       | - '                                                                 | 73      |

| 4.6       |                                                                     | 78      |

| Chapter   | 5 Conclusion                                                        | 80      |

| 5.1       |                                                                     | 80      |

| 5.2       |                                                                     | 81      |

| Referenc  |                                                                     | 82      |

# List of Tables

| 3.1 | Power summary of 5 Gb/s VM Tx                                        | 42  |

|-----|----------------------------------------------------------------------|-----|

| 3.2 | Performance summary for 5 Gb/s VM Tx and comparison to the state-of- |     |

|     | the-art                                                              | 43  |

| 4.1 | Performance summary for 14 Gb/s XCVR and comparison to the state-of- |     |

|     | the-art                                                              | -79 |

# List of Figures

| 1.1  | Energy efficiency of world's top 500 supercomputers versus their compu-     |    |

|------|-----------------------------------------------------------------------------|----|

|      | tational capability.                                                        | 2  |

| 1.2  | Goal for ubiquitous energy-efficient operation                              | 3  |

| 1.3  | Power break down in a hypothetical exascale system [1]                      | 3  |

| 1.4  | Simplified block diagram of a serial link                                   | 4  |

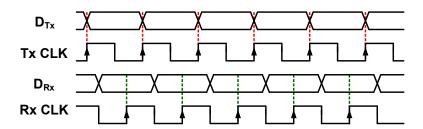

| 1.5  | Data and clock signal waveforms in a serial link                            | 4  |

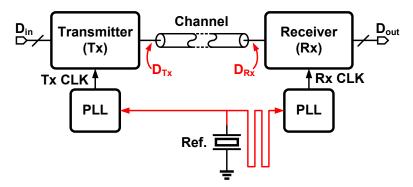

| 1.6  | Block diagram of a serial link with common I/O clocking                     | 5  |

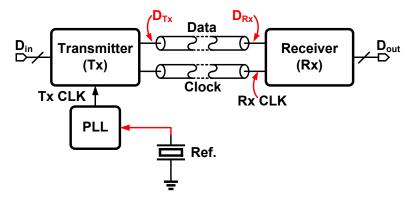

| 1.7  | Block diagram of a serial link with forwarded clocking                      | 6  |

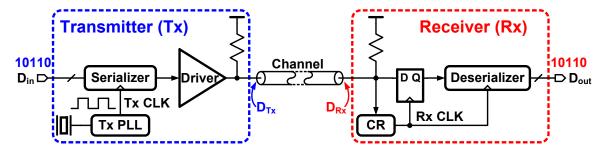

| 1.8  | Block diagram of a serial link with embedded clocking                       | 6  |

| 1.9  | Eye diagrams at the input and output of a lossy channel                     | 7  |

| 1.10 | Data rate for serial link versus year of publication                        | S  |

| 1.11 | Data rate for serial link versus CMOS technology node                       | S  |

| 1.12 | Energy efficiency for serial link versus year of publication                | 10 |

| 1.13 | Energy efficiency versus data rate for serial links                         | 11 |

| 1.14 | Energy efficiency versus channel loss for serial links                      | 11 |

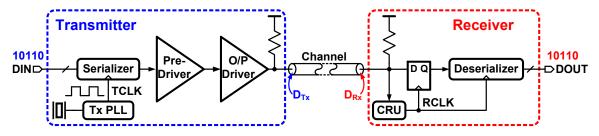

| 2.1  | Block diagram of a serial link with embedded clocking                       | 13 |

| 2.2  | Block diagram of a transmitter                                              | 14 |

| 2.3  | Current mode logic (CML) based output driver                                | 15 |

| 2.4  | CML driver with de-emphasis                                                 | 15 |

| 2.5  | (a) Voltage mode O/P driver. (b) Equivalent model of an ideal VM O/P        |    |

|      | driver                                                                      | 16 |

| 2.6  | (a) Conventional VM driver with de-emphasis, and (b) VM driver in [2]       | 17 |

| 2.7  | Typical eye diagram of a received signal                                    | 19 |

| 2.8  | Block diagram of a clock recovery unit (CRU)                                | 19 |

| 2.9  | (a) Block diagram of Hogge (Linear) phase detector. (b) Signal waveforms    |    |

|      | in Hogge phase detector                                                     | 21 |

| 2.10 | (a) Block diagram of Alexander (bang-bang) phase detector. Signal wave-     |    |

|      | forms for sampling with (b) early clock, and (c) late clock                 | 22 |

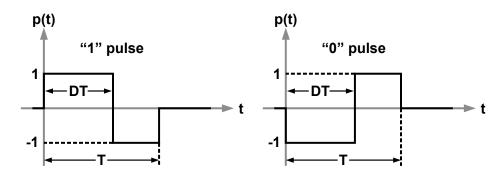

| 3.1  | Representation of data bits "1" and "0" using PWM pulses with duty cycle D. | 23 |

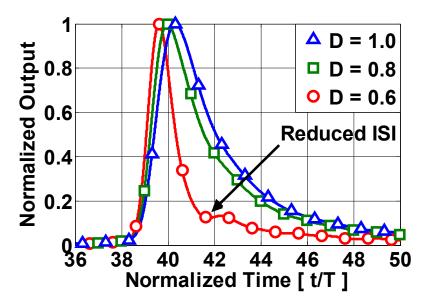

| 3.2  | Normalized time domain response of a channel to PWM pulses                  | 24 |

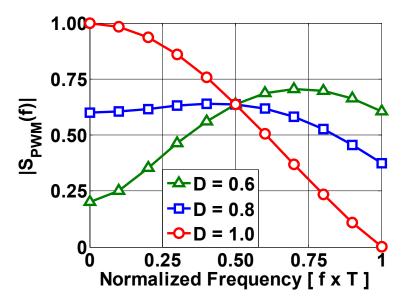

| 3.3  | Power spectral density of PWM pulses with different duty cycles             | 25 |

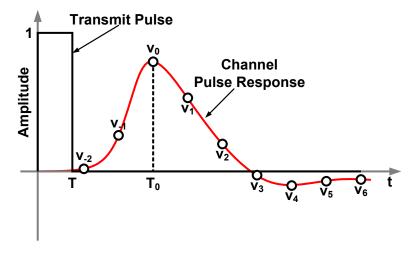

| 3.4  | Pulse response of a channel for NRZ input pulse                             | 25 |

| 3.5  | Worst case vertical eye opening with peak distortion analysis of PWM-          |    |

|------|--------------------------------------------------------------------------------|----|

|      | based de-emphasis for two different channels                                   | 26 |

| 3.6  | Worst case horizontal eye opening with peak distortion analysis of PWM-        |    |

|      | based de-emphasis for two different channels                                   | 27 |

| 3.7  | Worst case received eye opening vs r.m.s jitter amplitude                      | 29 |

| 3.8  | Simplified block diagram of the proposed transmitter                           | 30 |

| 3.9  | Simplified block diagram of encoder                                            | 31 |

| 3.10 | (a) Schematic of current controlled delay cell. (b) Tuning characteristic of   |    |

|      | the delay cell (output delay vs. tuning current)                               | 32 |

| 3.11 | Pseudo-differential fully symmetric XOR gate                                   | 32 |

| 3.12 | Eye diagram at the output of the encoder: (a) with bandlimited CMOS            |    |

|      | XOR gate (b) after optimizing transistor sizes and layout                      | 33 |

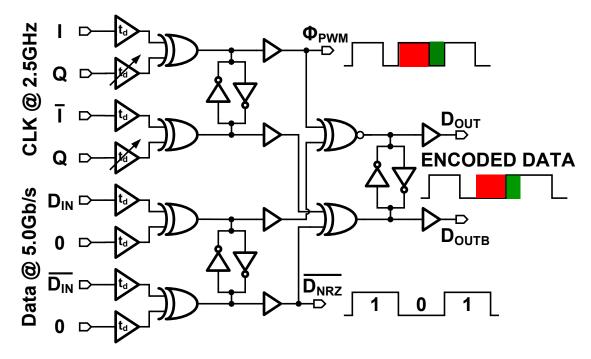

| 3.13 | Complete block diagram of the pseudo-differential encoder                      | 34 |

| 3.14 | Schematic of voltage mode output driver                                        | 35 |

| 3.15 | Digital phase-locked loop (DPLL) block diagram                                 | 36 |

| 3.16 | Die photo of the proposed transmitter                                          | 37 |

|      | Measured frequency response of FR4 stripline channels                          | 38 |

|      | (a) TX eye diagram at the input of channel with 16 dB loss, and (b)            |    |

|      | received eye diagram at the output of the channel                              | 38 |

| 3.19 | (a) TX eye diagram at the input of channel with 28 dB loss, and (b)            |    |

|      | received eye diagram at the output of the channel                              | 39 |

| 3.20 | Received eye opening at the end of channel with 28 dB loss                     | 40 |

|      | Bathtub plots for different channel loss                                       | 40 |

|      | Horizontal eye opening vs. peak-to-peak transmit amplitude                     | 41 |

|      | DPLL jitter histogram at 2.5 GHz output.                                       | 41 |

|      | Simulated differential return loss (S11) for the TX                            | 42 |

|      | (6-2)                                                                          |    |

| 4.1  | Block diagram of a serial link with embedded clocking                          | 45 |

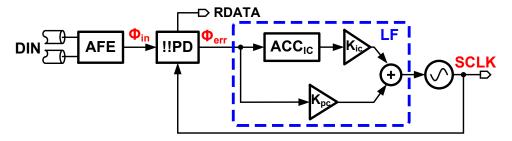

| 4.2  | Block diagram of a conventional digital CDR                                    | 47 |

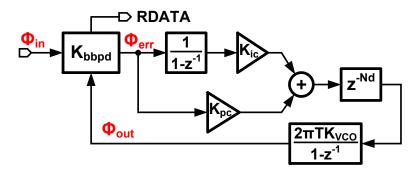

| 4.3  | Linearized small signal model of a conventional digital CDR                    | 48 |

| 4.4  | Block diagram of half-rate phase interpolator based digital CDR                | 49 |

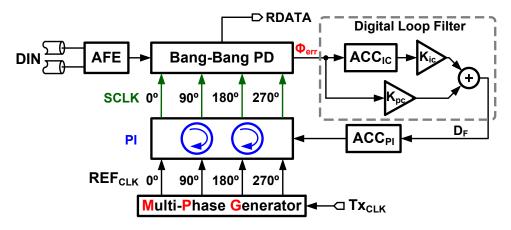

| 4.5  | Block diagram of proposed ring PLL based multi-phase clock generation          |    |

|      | in CDR loop                                                                    | 50 |

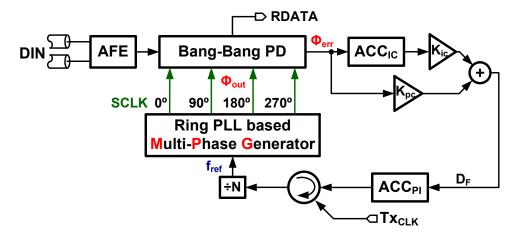

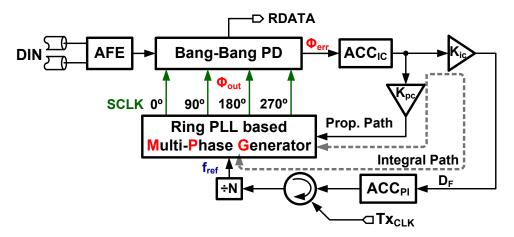

| 4.6  | Block diagram of proposed clock and data recovery                              | 51 |

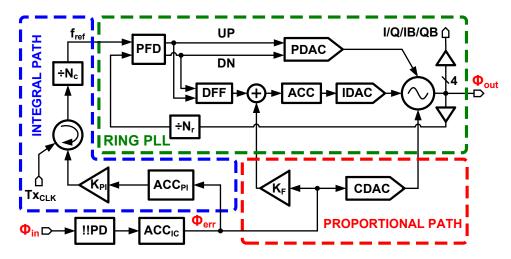

| 4.7  | Block diagram for CDR proportional and integral path controls through          |    |

|      | ring PLL                                                                       | 52 |

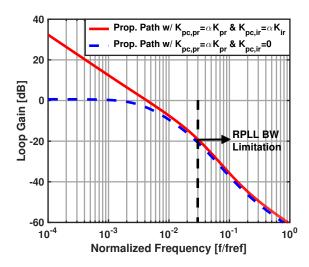

| 4.8  | Open loop gains for CDR proportional path with and without integral            |    |

|      | path control in ring PLL                                                       | 53 |

| 4.9  | Simplified block diagram of a digital clock and data recovery                  | 55 |

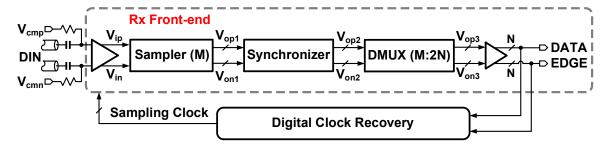

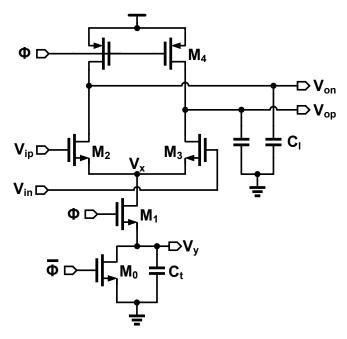

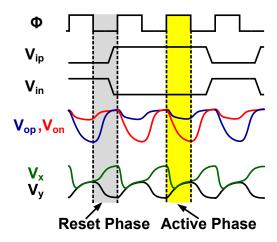

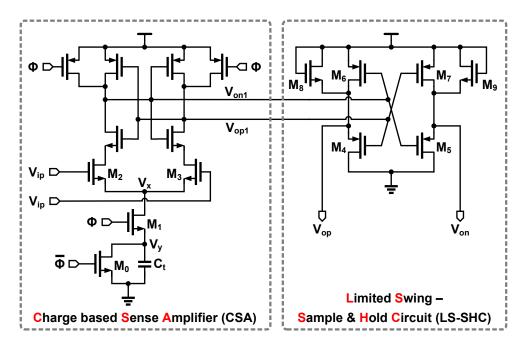

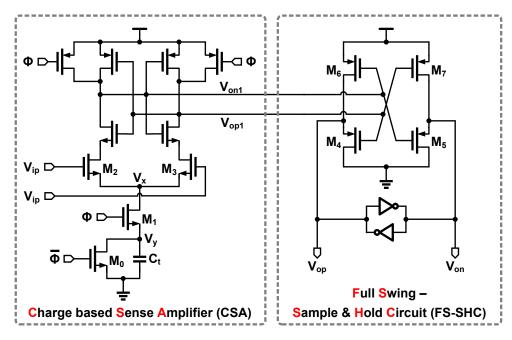

| 4.10 |                                                                                | 56 |

|      | Transient signal waveforms in CbA                                              | 57 |

|      | Schematic diagram of a charge-based NRZ latch in [3]                           | 57 |

|      | Schematic diagram of a proposed limited-swing charge-based flip-flop (LS-CFF). |    |

|      | Transient signal waveforms in LS-CFF                                           | 59 |

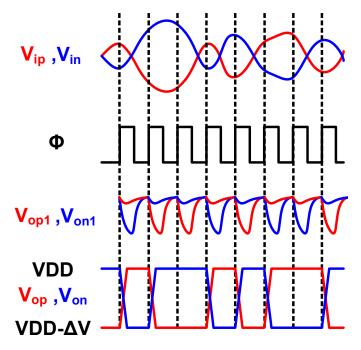

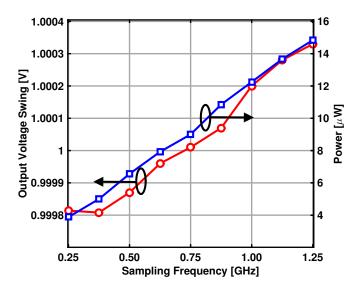

| 4.15 | (a) Differential output voltage swing vs. input voltage for LS-CFF clocked |    |

|------|----------------------------------------------------------------------------|----|

|      | at 7 GHz. (b) Output voltage swing and power consumption vs. sampling      |    |

|      | frequency for LS-CFF                                                       | 60 |

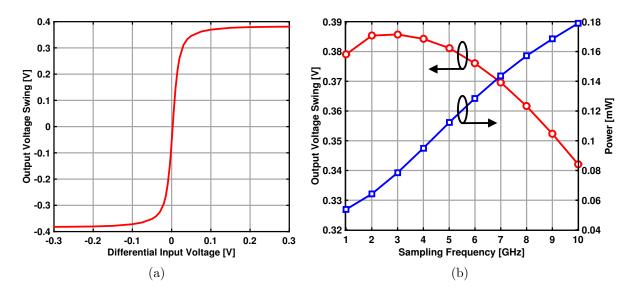

| 4.16 | (a) Output voltage swing vs. frequency, and (b) power consumption vs.      |    |

|      | frequency for optimized LS-CFF                                             | 61 |

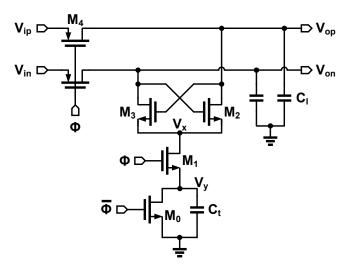

| 4.17 | Schematic diagram of a full-swing charge-based flip-flop (FS-CFF)          | 62 |

| 4.18 | Output voltage swing and power consumption vs. sampling frequency for      |    |

|      | FS-CFF                                                                     | 63 |

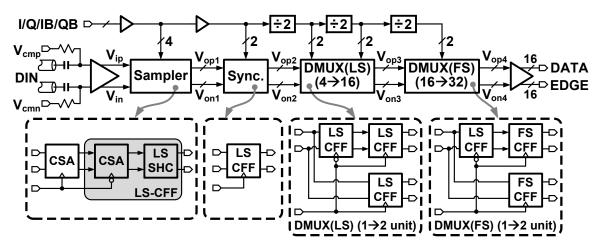

| 4.19 | Detailed block diagram of the Rx front-end                                 | 63 |

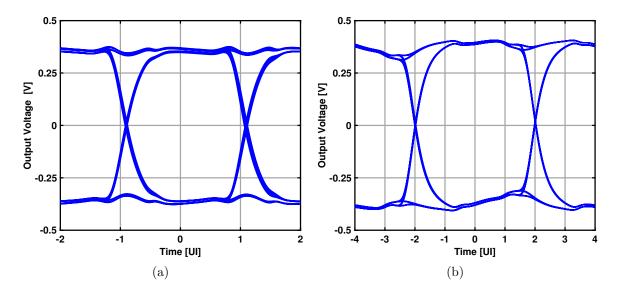

| 4.20 | (a) Eye diagram at the output of front-end sampler. (b) Eye diagram at     |    |

|      | the output of first descrialization stage                                  | 64 |

| 4.21 | Block diagram of clock divider with tunable delay                          | 65 |

| 4.22 | (a) Schematic diagram of single side of a uniformly segmented differen-    |    |

|      | tial VM O/P driver. (b) Simplified schematic of VM O/P driver with         |    |

|      | embedded equalization                                                      | 65 |

| 4.23 | Block diagram of proposed partially segmented VM Tx w/ embedded de-        |    |

|      | emphasis                                                                   | 67 |

| 4.24 | Block diagram of proposed 14 Gb/s transceiver                              | 69 |

| 4.25 | Block diagram of LC oscillator based digital PLL                           | 70 |

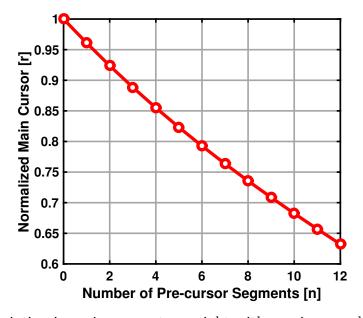

|      | Block diagram of proposed voltage mode transmitter                         | 71 |

|      | Variation in main cursor tap weight with varying equalizer tap weight      | 72 |

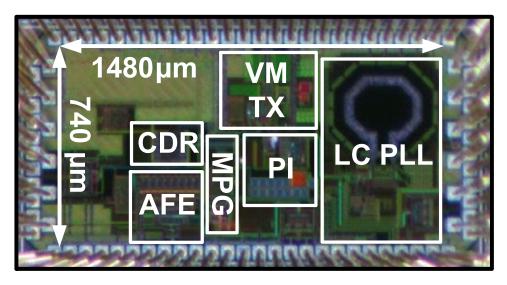

|      | Die photo of the transceiver prototype                                     | 73 |

|      | Phase noise spectrum of LC-DPLL locked at 7 GHz                            | 73 |

|      | Differential transmit eye diagram at 14 Gb/s                               | 74 |

|      | Bathtub plots at the output of channel w/ and w/o FIR equalization         | 75 |

|      | Phase noise spectrum of ring PLL output locked at 7 GHz                    | 75 |

|      | Recovered clock waveform                                                   | 76 |

|      | JTRAN curve for the proposed CDR locked at 14 Gb/s                         | 77 |

|      | JTOL plot measured with stressed data input                                | 77 |

| 4.36 | Power breakdown in 14 Gb/s serial link                                     | 78 |

## Chapter 1

#### Introduction

Computation and communication are fundamental functions in all modern day information processing systems. On one end, supercomputers which serve the high-end scientific community directly or large scale data centers which cater to the needs of millions of people worldwide, must possess enormous capability for computation and communication. On the other end of the performance spectrum, portable devices like laptops, mobile phones, etc., must provide adequate computing and communication performance with extreme power constraints. For several reasons, improved performance of all these devices at a lower and affordable cost is not only desirable but also the need of the hour to meet the growing demands of computation and communication. The primary bottleneck in improving performance of these devices is the power dissipation. As an example, it is worthwhile to examine the energy efficiency of the world's most powerful supercomputers.

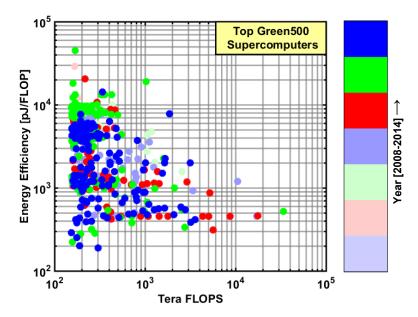

Figure 1.1 shows the energy efficiency of the world's top supercomputers introduced over last seven years and which make it to the list of the top 500 Green Supercomputers [4]. Energy efficiency of a supercomputer is measured as energy spent in executing one floating point operation as shown along the y-axis. The computational capability of a supercomputer is measured as the number of floating-point operations per second (FLOPS) and shown along the x-axis. The plot illustrates three important things. First, computational capacity of supercomputers has increased over the years. Secondly, energy efficiency of supercomputers has become better over time. Last but not the least, large computational capability and low energy consumption is still a challenge as the highest performing supercomputers are not the most energy-efficient.

Roughly a decade back, when the petaFLOP supercomputer was introduced, it was estimated that one would need 1000X performance in the future, and efforts were made to

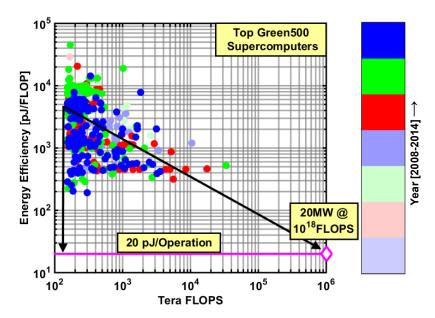

figure out what it would take to achieve a 1000X performance improvement [1]. To this end, the goal for high performance computing was set to achieve ExaFLOP operation with 20 MW power consumption, which leads to an energy efficiency of 20 pJ/FLOP as projected in Fig. 1.2. In a further step, advanced hardware and software techniques developed to achieve 20 pJ/FLOP energy efficiency would not be constrained to a single computational capability but energy efficiency should percolate up/down to benefit a wide range of energy-efficient operation. Figure 1.2 captures this wide range of energy-efficient operation which is the goal for exascale computing. Also, the energy-efficient operation should extend to a range of other applications not shown in the plot.

Figure 1.1: Energy efficiency of world's top 500 supercomputers versus their computational capability.

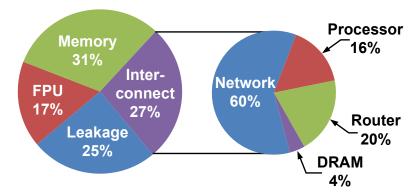

A feasibility study of such an exascale system was done after considering many technological advancements on both the hardware and software fronts [1]. Figure 1.3 shows the power breakdown of a hypothetical exascale system. The pie chart on the left shows that leakage power is going to be significant, amounting to 25% of the overall power consumption due to smaller dimensions in fine technology. FPU is the core computational floating point unit, which executes floating point operations and consumes 17% of the total power. A large memory is needed in such systems and it consumes 31% of the system power. A total of 31% memory power is distributed in L1 cache, L2/L3 cache, DRAM, disk, and register

Figure 1.2: Goal for ubiquitous energy-efficient operation.

files with 39%, 16%, 3%, 14%, and 28%, respectively. The information or data which is to be processed is generated, stored, and used at different locations in a system. This data is transferred from one point to another through an interconnect. Depending on the location of source and destination, power dissipation in the data interconnect varies. In total, inter-

Figure 1.3: Power break down in a hypothetical exascale system [1].

connect power dissipation is expected to be 27% of total system power. Further breakdown of the interconnect power is shown in the pie chart on the right. It consists of power spent in data transfer on processor itself (16%), router (20%), DRAM (4%), and moving data from one rack to the other in a network. Here, the network includes data transfer between racks and has a dominant power consumption of 60% of the overall interconnect power. A data

interconnect is often called 'Serial Link' or 'SerDes' (serializer/deserializer). The focus of this work is on improving the interconnect energy-efficiency.

#### 1.1 Basics of a Serial Link

Figure 1.4: Simplified block diagram of a serial link.

Figure 1.5: Data and clock signal waveforms in a serial link.

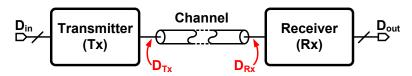

Figure 1.4 shows a simplified block diagram of a conventional serial link (data link). It consists of a transmitter (Tx) that modulates digital bits  $D_{in}$  with a pulse waveform into an analog signal  $D_{Tx}$  and couples it to the channel. The channel is a medium of transmission, which can be a metal trace, copper wire, an optical fiber, etc. On the other end of the channel is a receiver (Rx) block that samples the incoming signal  $D_{Rx}$  and recovers transmitted bits, ideally error-free. Figure 1.5 shows data/clock signal waveforms for the serial link. The transmitted data  $D_{Tx}$  is aligned with transmitter clock Tx CLK, and the receiver samples the received signal  $D_{Rx}$  in the center of each bit using clock Rx CLK. While the transmitter uses a local clock to send bits periodically, the receiver should know the data rate at which bits are transmitted, so that it can sample the received signal correctly. The clocking scheme on the Tx and Rx side in serial links distinguishes them from others in their usage.

Based on the clocking scheme on the Tx and Rx side, serial links can be classified into three categories: common clock I/O architecture, forwarded clock I/O architecture, and embedded clock I/O architecture. These clocking architectures are discussed in detail below.

#### 1.1.1 Common Clock I/O Architecture

In common clock I/O architecture, Rx can use the same reference clock source for sampling as used during the transmission [5]. Figure 1.6 shows a block diagram of a common I/O clocking scheme. A single crystal is used as a reference for clock generation with phase locked loops (PLL) on both transmitter and receiver sides. A problem arises when on-chip and off-chip delays need to be matched for clock (Tx CLK/Rx CLK) and data paths ( $D_{Tx}/D_{Rx}$ ) and it gets more critical for multi-Gb/s data interconnect. This scheme is limited to a few 100 Mb/s of data rate. Common I/O clocking has a problem in finding an optimum sampling clock phase on the Rx side given the mismatch in clock and data paths. It can be resolved if the clock used for transmitting data is also sent to Rx, which together formulate a forwarded clock architecture as discussed next.

Figure 1.6: Block diagram of a serial link with common I/O clocking.

#### 1.1.2 Forwarded Clock I/O Architecture

Figure 1.7 shows a block diagram of a transceiver with forwarded clock architecture that incorporates a dedicated channel to pass Tx CLK from Tx to Rx. The received clock is de-skewed adaptively to sample the received bit at an optimum location. The architecture comes with 3 an extra cost of added channel for clock. However, this cost is negligible when amortized over multiple links operating in parallel at the same data rate. The forwarded clock technique is commonly used in processor-memory interfaces and multi-processor communication [6]. Forwarded clock architecture is limited to relatively low data rate short-reach

Figure 1.7: Block diagram of a serial link with forwarded clocking.

links like chip-to-chip communication on the same board. For long-reach links, embedded clocking is used as discussed next.

#### 1.1.3 Embedded Clock I/O Architecture

Figure 1.8: Block diagram of a serial link with embedded clocking.

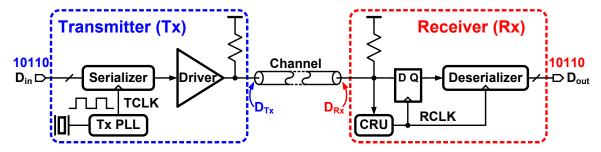

Figure 1.8 shows a block diagram of a serial link with embedded clocking. Here, Tx uses a local clock generated by a phase locked loop (Tx PLL) to serialize parallel input bit streams ( $D_{in}$ ) to a single high speed bit stream ( $D_{Tx}$ ). On the Rx side, the sampling clock Rx CLK is recovered from the received data using a clock recovery (CR) loop, and the recovered clock samples the received signal  $D_{Rx}$  to recover transmitted bits correctly. The sampled data can be later describilized for further use. The clock recovery loop needs extra power, but it recovers frequency and phase of the received data without any prior information and any additional channel. Embedded clocking is used in high speed mobile I/O (M-PHY), lossy backplane channels, optical fibers, etc.

#### 1.2 Channel

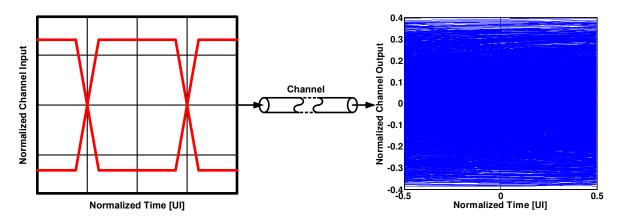

Figure 1.9: Eye diagrams at the input and output of a lossy channel.

It is not unfair to say that power consumption and complexity in serial links are very much dictated by the kind of channel. Starting from the transmitter output, everything which comes in the signal path till the Rx sampler input constitutes the channel. It includes bond wire, package parasitics,  $\mu$ -stripline or stripline metal traces, SMA connectors, connecting cables, etc. A lossy channel attenuates, disperses, and distorts transmitted signal and makes it indistinguishable at the receiver end. Figure 1.9 shows typical eye diagrams at input and output of a lossy channel. A large channel loss leaves little or no timing margin to sample and recover data bits correctly. So, both Tx and Rx incorporate equalizers such as FFE (feed forward equalizer), CTLE (continuous time linear equalizer), and DFE (decision feedback equalizer) to compensate for channel anomalies.

#### 1.3 Serial Link Performance Metrics

At the very top level, performance of serial links is compared with the following three metrics:

- 1. Data rate: Defined as number of bits transmitted/received per second.

- 2. Energy Efficiency: Defined as power consumed in Tx/Rx per unit data rate.

- 3. Channel Loss: Defined as power loss at Nyquist frequency. Though it is defined at a single frequency, channel characteristics throughout the transmit signal band are

important.

A high data rate per link or pin is beneficial to reduce board space. A lower power consumption per unit data transfer improves overall energy efficiency and enables more links in parallel for the same power budget. Channel loss plays a spoiler for high data rate and low energy efficiency. Since channel loss results in signal attenuation, distortion, and dispersion of transmitted signal, it demands additional energy to recover data bits in an error-free manner at the receiver.

Contrary to requirement, an abundant energy source for high data rate transmission across a lossy channel is not a solution. This is because thermal losses for interconnects become unbearable with the famous 'Power Wall' [7]. Rise in temperature is more detrimental for lower technology nodes, which are otherwise faster compared to slower and older technologies. One can try to dissipate heat at static processing centers with an unaffordable cost of cooling, but portable devices do not have that luxury either. Low power consumption per unit data rate (mW/Gb/s) is the only way forward to enhance computation and communication performance while keeping thermal dissipation within acceptable limits. Lower power consumption for higher data rate while compensating for higher loss has been a guiding factor for research in serial links in the past and will remain so in the future. The next section will review research in serial links over the last 15 years.

#### 1.4 Research Trends in Serial Links

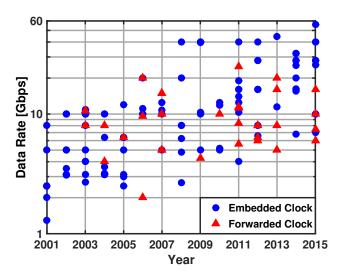

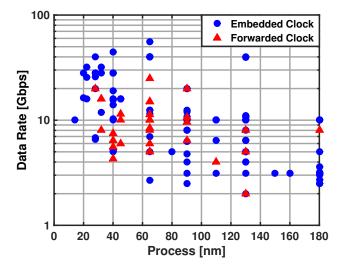

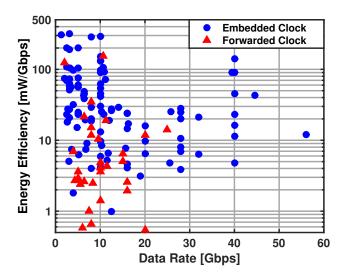

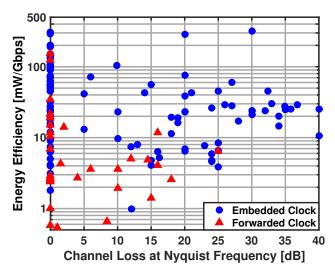

A research survey was carried out for serial link transceivers published by industry and academia in circuit conferences and journals. The survey includes 140 publications over the last 15 years. Figure 1.10 shows the data rate for transceivers with year of publication. In the last 15 years, data rates have steadily increased for both forwarded and embedded clock architectures. Advancement in silicon technology with finer dimensions is one big reason for the increase in data rates [8]. Figure 1.11 shows data rate versus CMOS process node. The figure shows a clear trend of increasing data rate over lower process nodes.

It is to be noted that the same peak data rate (e.g. data rate = 40Gb/s) in serial links is

Figure 1.10: Data rate for serial link versus year of publication.

Figure 1.11: Data rate for serial link versus CMOS technology node.

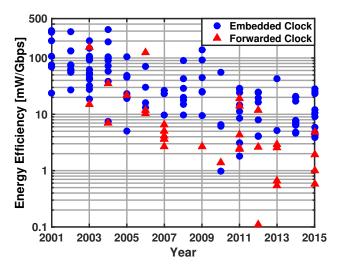

Figure 1.12: Energy efficiency for serial link versus year of publication.

demonstrated in different process nodes. This observation indicates that technology itself is not the limiting factor to achieve high data rate. And the differences between the two designs lie in the energy efficiency of such transceivers which benefit from architectural or circuit level innovations, finer technology, or lower channel loss. Figure 1.12 depicts energy efficiency of serial links versus year of publication. A clear trend of decreasing energy efficiency over the years is due to the combined effort at architecture and circuit level innovations and technological advancement. An important observation is that the energy efficiency of forwarded clock architectures is generally lower than that of embedded clock architectures. This is because of the difficulty in extracting clock from random data transmitted across lossy channels in embedded architectures.

Since the goal of research in serial links is to facilitate higher data rate and lower energy consumption, it is worthwhile to look at energy efficiency versus data rate as shown in Fig. 1.13. Data rates for forwarded clock architecture are limited, and the architecture achieves lower energy efficiency compared to embedded links. For embedded architectures, a roughly constant energy efficiency in the range of 4-30 pJ/bit, or energy efficiency increasing with data rates, is due to added power penalty for systems operating at high data rates with increased channel loss. Figure 1.14 shows energy efficiency for serial links versus channel loss at Nyquist frequency. Energy efficiency markers at 0 dB channel loss are publications reporting channel loss that is either negligible or unavailable. Most of the forwarded link

Figure 1.13: Energy efficiency versus data rate for serial links.

architectures stand out with low energy efficiency at a given channel loss when compared to embedded links because of easier data recovery with forwarded clock. Embedded links exhibit high energy efficiency at higher data rate with increased channel loss. While silicon technology is going to hit the limit of scaling soon, innovations at the architecture and circuit levels is the only way forward to improve energy efficiency at higher data rates.

Figure 1.14: Energy efficiency versus channel loss for serial links.

The trends described above make a compelling case for research in embedded serial links to increase data rates and reduce energy consumption even in the presence of increased channel loss. This work focuses on innovating at the architectural and circuit levels to improve energy efficiency of high speed serial links that employ embedded clock architectures. This thesis is organized as follows: In Chapter 2, basic building blocks of a serial link are reviewed, and potential problems and avenues for improving link energy efficiency are identified. In Chapter 3, a 5 Gb/s voltage-mode transmitter embedded with time-based de-emphasis is implemented in 90 nm CMOS process. Time-based de-emphasis overcomes the tradeoff between impedance matching, output swing, and de-emphasis resolution in conventional voltage-based de-emphasis. In Chapter 4, a 14 Gb/s transceiver prototype is implemented in a 65 nm CMOS process. The transmitter employs a novel partially segmented 2-tap FIR voltage-mode output driver to lower power consumption. The receiver implements a low power half-rate clock and data recovery using the proposed ring PLL based multi-phase sampling clock generation and charge-based sampling and deserialization. In Chapter 5, the above serial link projects are summarized and the thesis is concluded.

## Chapter 2

## Overview of Serial Links

Figure 2.1: Block diagram of a serial link with embedded clocking.

Figure 2.1 shows block diagram of a serial link with embedded clocking. On the Tx side, a locally generated clock from Tx PLL is used to serialize N parallel low frequency bit streams ( $D_{in}$ ) to full-rate data through serializer. An output driver performs equalization and couples full-rate data  $D_{Tx}$  to the channel. On the Rx side, the sampling clock is recovered from the received signal through a clock recovery unit (CRU) and data is recovered by sampling the received signal using the recovered clock RCLK. The recovered data is deserialized to N parallel low rate bit streams,  $D_{out}$ . Different building blocks of a conventional serial link are discussed below.

### 2.1 Transmitter

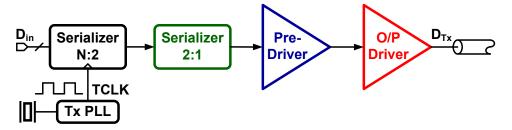

Figure 2.2 shows a simplified block diagram of a transmitter. It consists of a serializer, predriver, output (O/P) driver, and Tx PLL. The output driver, pre-driver, and last stage of the serializer process data signals at maximum speed and are power hungry blocks on Tx side. O/P driver consumes significant power which is proportional to channel loss in the serial link. Power dissipation in pre-drivers depends on O/P driver topology and can be

Figure 2.2: Block diagram of a transmitter.

a significant portion. Jitter requirements on the clock used for serialization guide Tx PLL design, and it can be sufficiently low power consuming compared to other blocks. In the end, it is the output driver design with embedded equalization which determines Tx design for energy-efficient operation. Characteristics of different output drivers are discussed below.

#### 2.1.1 Transmitter Output Driver

The Tx output driver should possess three main features. First, it should have a fixed output impedance that is matched to the channel characteristic impedance to guarantee signal integrity. Impedance matching ideally should be independent of output signal swing. Second, output drivers must be amenable for embedding de-emphasis-based equalization without altering their output impedance. Finally, it is important to have control over the magnitude of output swing to optimize signaling power as a function of channel loss. Conventionally, output drivers can be categorized into current mode logic (CML) based output drivers and voltage mode (VM) output drivers. CML-based and VM O/P drivers are discussed in detail below.

#### 2.1.1.1 Current Mode Logic (CML) based Output Driver

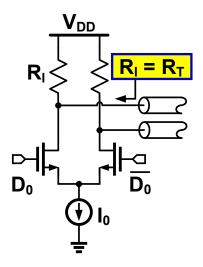

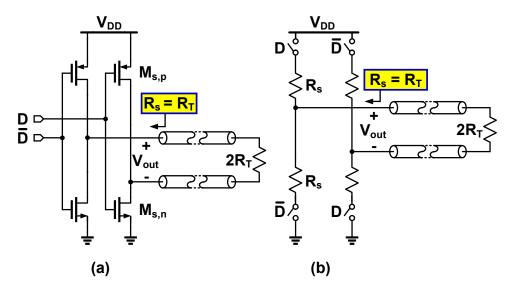

A current mode logic (CML) based output driver shown in Fig. 2.3 has all the desirable features as mentioned before. The output impedance is equal to  $R_l$ , which can be chosen to match the channel characteristic impedance,  $R_T$ . Large output impedance of the input pair makes impedance matching nearly independent of output signal swing. It is straightforward to control the output swing by varying the tail current source  $I_0$ . For feedforward

Figure 2.3: Current mode logic (CML) based output driver.

equalization, de-emphasis can be implemented by simply splitting the main current source according to equalizer weights as shown in Fig. 2.4. A major disadvantage of the CML driver is its large current consumption, which is equal to  $V_{d,pp}/R_T$ , where  $V_{d,pp}$  is the peak-to-peak differential output swing. In contrast, voltage mode output drivers result in energy-efficient operation as discussed next.

Figure 2.4: CML driver with de-emphasis.

Figure 2.5: (a) Voltage mode O/P driver. (b) Equivalent model of an ideal VM O/P driver.

#### 2.1.1.2 Voltage Mode (VM) Output Driver

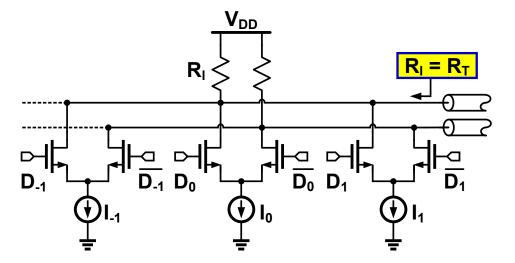

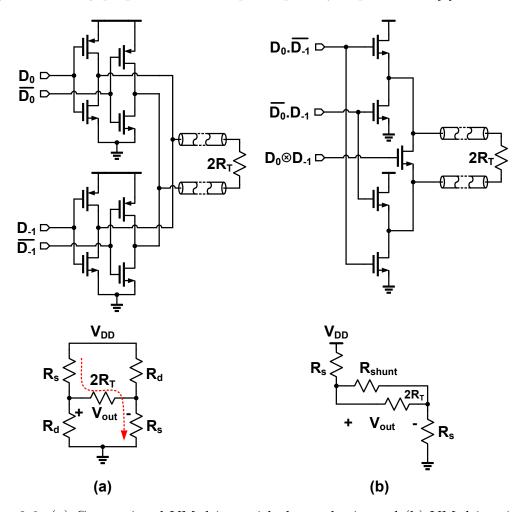

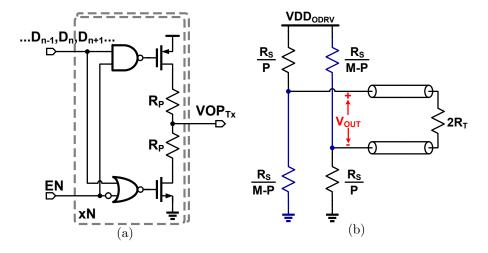

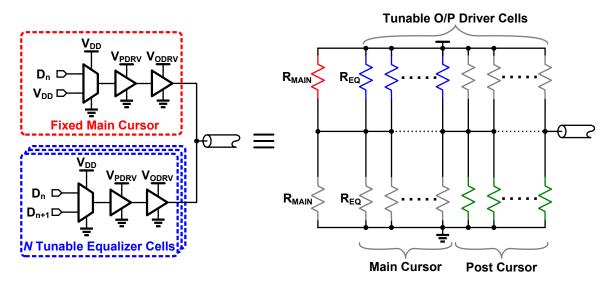

A voltage mode (VM) output driver shown in Fig. 2.5(a) is an attractive alternative to the CML driver because it can be ideally 4X more power efficient [9]. A model of the VM O/P driver is shown in Fig. 2.5(b), where  $R_s$  models the ON state resistance of the driver switches,  $M_{s,p}/M_{s,n}$ . Transistors  $M_{s,p}/M_{s,n}$  are biased and sized to match the channel characteristic impedance,  $R_T$ . Output swing is controlled by the driver supply voltage  $V_{DD}$  and it consumes current  $V_{d,pp}/4R_T$  for differential peak-to-peak swing,  $V_{d,pp}$ . While the power efficiency benefit of the VM driver is appealing, it is not particularly suited for de-emphasis.

Figure 2.6(a) shows a conventional differential VM driver in which de-emphasis is implemented by changing the output voltage level using a resistive divider [10]. A resistive voltage division is created by switching resistors in branches  $R_s$  and  $R_d$  such that the modified driver output impedance,  $R_s||R_d$ , is equal to the channel characteristic impedance  $R_T$ . While resistive divider provides variable voltage for equalization, the current consumption increases  $(\geq V_{DD}/4R_T)$  due to low impedance path from supply to ground. Furthermore, the current consumption also depends on output swing and is maximum  $(V_{d,pp}/2R_T)$  at minimum output swing. In [11], the signaling current is held constant at  $V_{DD}/4R_T$  by using a shunt resistance  $R_{shunt}$  (realized using transistor,  $M_{shunt}$ ) across the differential output port, as shown in Fig. 2.6(a). However, if the resolution of equalization were not to be compromised,

the non-linear dependence of resistors  $R_s$ ,  $R_d$ , and  $R_{shunt}$  on the output voltage incurs large power penalty in pre-drivers.

Combining the signaling power efficiency of the previous scheme with direct tuning of the driver output impedance [12], authors in [2] introduced a VM driver shown in Fig. 2.6(b). Here, the output driver impedance is tuned by controlling the gate voltage of the driver switches. A 2-tap equalization is implemented by switching  $R_s$  and  $R_{shunt}$  based on precoded data  $(D_0, D_{-1})$ . The signaling power scales up with the output swing unlike the previous architectures and it is minimum for minimum output swing. Nevertheless, in all the above cases, the output driver impedance realized by switching MOSFET is tightly coupled with the output voltage swing and the amount of de-emphasis. And the resolution of de-emphasis tap weight is inversely proportional to the power penalty in pre-drivers [2].

Figure 2.6: (a) Conventional VM driver with de-emphasis, and (b) VM driver in [2].

In view of the above conflicting tradeoffs, we seek to use time-based techniques to decouple de-emphasis from impedance control and output swing. To this end, we propose to drive a conventional VM driver with a two-level pulse width modulated (PWM) data stream to achieve de-emphasis without compromising the VM driver power efficiency. An overview of PWM-based de-emphasis is presented first in Chapter 3 and the impact of clock jitter with multiple transition edges during equalization is carefully analyzed. Later in the chapter, we implement a time-based 5 Gb/s voltage mode transmitter equalizing for channel loss > 15 dB.

#### 2.2 Receiver

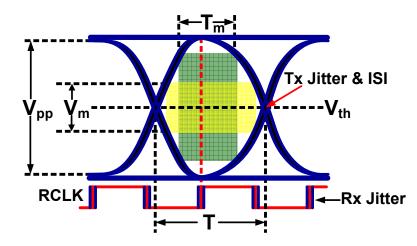

A receiver recovers data bits by sampling the received signal D<sub>Rx</sub> using recovered clock RCLK (Fig. 2.1). The received signal is attenuated and distorted due to channel loss along the transmission path. Figure 2.7 shows typical eye diagram of a received signal  $D_{Rx}$ . Here, a non-return-to-zero (NRZ) pulse waveform is used to modulate transmit bits. The peak-topeak received signal swing is  $V_{pp}$  and each bit is T period wide. A sampler in the Rx frontend compares the received signal with an ideal threshold voltage  $V_{th} = 0 V$ , for differential signals, and detects 1/0 for transmitted bits. However, any real comparator circuit has a lower limit on the minimum voltage level to be detected, which is defined as the sensitivity of the receiver. High sensitivity to received input at the Rx front-end enables lower transmit swing and less power consumption on the Tx side. The sampling circuit often suffers from process dependent statistical mismatch in differential paths, which adds a fixed voltage offset to the threshold level. Therefore, the effective voltage sampling margin of the sampler is reduced by  $V_m$  near the ideal threshold level. Voltage offset is usually compensated for in samplers but at the expense of increased power. Sensitivity of a sampler can be improved by using a high gain regenerative sense-amplifier based flip-flop [13]. Power consumption in data samplers is significant as they operate at maximum speed.

For sampling data, the recovered clock *RCLK* has to be aligned ideally with the center of the received signal, which has maximum voltage margin during sampling. Zero crossing variation (timing jitter) in received signal and sampling clock both reduce the sampling time

Figure 2.7: Typical eye diagram of a received signal.

Figure 2.8: Block diagram of a clock recovery unit (CRU).

margin to  $T_m \leq T$ . Time domain jitter on RCLK and voltage sensitivity of the sampler decide correctness of detected bits. The correctness of sampled data is measured in terms of bit error rate (BER) and it requires a BER $< 10^{-12}$  for most serial link applications. Assuming a white Gaussian voltage noise  $(N(0,\sigma_{\text{vnoise}}))$  added to received voltage swing before sampling, a BER =  $10^{-12}$  requires an additional voltage margin of  $\pm 7\sigma_{\text{vnoise}}$  at the input of sampler. Similarly, it requires a sampling time margin of  $\pm 7\sigma_{\text{jitter}}$  for timing uncertainty  $\sigma_{\text{jitter}}$  in the sampling clock.

Sampling gets complicated when transitions in the received signal vary due to jitter on Tx side and intersymbol interference (ISI) introduced by channel. Hence, it is required that sampling clock *RCLK* should track the received signal in frequency and phase and this is referred to as clock recovery on the Rx side. Basics of clock recovery are discussed next.

#### 2.2.1 Rx Clock Recovery

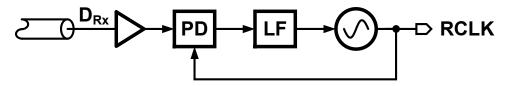

Figure 2.8 shows a block diagram of a typical clock recovery unit on the Rx side. It consists of phase error detector (PD), loop filter (LF), and an oscillator. PD detects phase error or

timing error between transitions in sampling clock and received data. Phase error,  $\Phi_{\rm err}$ , is filtered using analog or digital loop filter, LF. Loop filter output tunes the oscillator, thereby controlling the sampling phase and frequency. Analog or digital processing in the loop mostly depends on the phase error detector, whose output is analog or digital. Two commonly used phase detection methods between sampling clock and random data are: (a) linear (Hogge) phase detector, and (b) bang-bang (Alexander) phase detector. The two phase detection methods are discussed below in more detail.

#### 2.2.1.1 Hogge (linear) Phase Detector

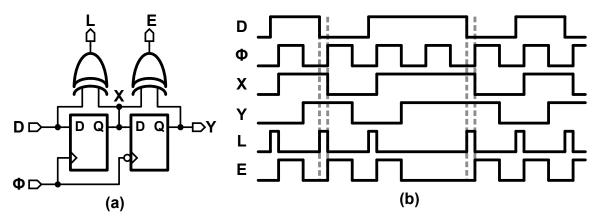

Figure 2.9(a) shows a block diagram of a Hogge phase detector. It consists of two D flip-flops (DFF) and two XOR gates. First DFF samples random data D at rising edge of clock  $\Phi$ as shown in Fig. 2.9(b). Phase difference between data and clock is encoded as pulse width (PW) of XOR output, Late(L). The second DFF generates a pulse (Early(E)) of half the clock period every time data makes a transition. The difference between pulse widths of two modulated signals,  $PW_L - PW_E$  is the phase error between sampling clock and received data. In Fig. 2.9(b), the clock sampling edge is left of center w.r.t. random data. Hence, pulse width difference  $PW_E - PW_L > 0$  and signifies that the sampling clock is early w.r.t. its ideal sampling location at the center. Similar phase detector operation holds for the sampling clock located right of center with  $PW_L - PW_E < 0$ . The evaluated phase error is later used to change the sampling clock phase in a feedback loop. Ideally, linear phase detectors quantify phase error exactly. However, they have a few drawbacks. At high data rates, the data bit period becomes comparable to circuit delays, and any delay mismatch in signal paths, like  $D \to L$  and  $X \to L$ , is a cause of unintended phase error. Secondly, XOR gates suffer from limited circuit bandwidth while generating pulse width modulated output higher than data rates. In addition, the phase detector output is an analog signal and cannot benefit from low power and smaller area digital filtering in the feedback loop. A digital phase detector overcomes some of these issues as discussed next.

Figure 2.9: (a) Block diagram of Hogge (Linear) phase detector. (b) Signal waveforms in Hogge phase detector.

#### 2.2.1.2 Alexander (bang-bang) Phase Detector (!!PD)

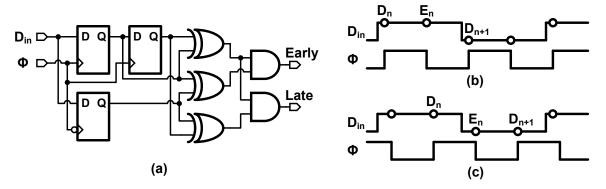

Unlike linear phase detectors, an Alexander phase detector (Fig. 2.10(a)) detects sign of phase error. The phase detector samples at both positive edge (data sample,  $D_n$ ) and negative edge (edge sample,  $E_n$ ) of clock. These data and edge samples are combined by a combinational logic to detect early or late. Figure 2.10(b) shows sampling waveforms with clock rising edge occurring earlier than the center of the data bit. Here,  $D_n$  and  $D_{n+1}$  are different but  $D_n$  and  $E_n$  are the same. After the combinational logic, Early signal evaluates HIGH and Late signal will be zero. Early and Late signals will be vice-versa for clock sampling edge placed to the right of the center of the data bit (Figure 2.10(c)). The phase detector outputs Early/Late are both zero for no data transitions. The signed output (HIGH/LOW) of the phase error detector is later processed digitally to correct sampling phase in a feedback loop. Bang-bang phase detectors are easy to use at high data rates and are not limited by pulses narrower than a bit period. However, !!PD output has a quantization error unlike the linear phase error detector.

In !!PD, data and edge samplers operate at maximum speed and consume a lot of power. Cascaded sense-amplifier based flip-flops with large non-linear gain and high voltage sensitivity are used for data/edge sampling. Power consumption in these samplers is dynamic in nature and scales linearly with data rate. Charge sharing based front-end sampling in [3] consumes lesser power compared to sense-amplifier based flip-flop. Chapter 4 elaborates on already existing sampler designs and introduces a novel energy-efficient charge-based Rx

Figure 2.10: (a) Block diagram of Alexander (bang-bang) phase detector. Signal waveforms for sampling with (b) early clock, and (c) late clock.

#### front-end.

It is to be noted that the underlying principle of phase error detection is sampling each bit at bit rate in linear phase detectors and twice the bit rate in bang-bang phase detectors. Since power consumption in CMOS circuits is directly proportional to frequency of operation, sub-rate phase detector architectures operating at lower frequencies have often been used. The basic idea of sub-rate architectures is to sample input with multiple phases of a lower frequency clock in place of using a single-phase high-frequency clock. The number of samplers increases in proportion to additional clock phases. Reducing the clock speed and using subrate phase detectors is not always a winning option for two reasons. First, the speed of samplers is reduced but the number of samplers has increased. The total power consumption for more samplers operating at sub-rate may not be always less than that for fewer samplers operating at full-rate clock. Secondly, generating and routing more sampling clock phases at lower rate can be more power hungry than doing the same for a full-rate clock. Generating low jitter clock and tracking multiple clock phases for sampling are two different problems in clock and data recovery (CDR) loop. Based on the application, a low jitter clock and its sampling phases are generated and tracked in different kinds of clock and data recovery loops. Chapter 4 discusses power consumption in conventional clock and data recovery loops in more detail. Later in the chapter, we propose a low power and low jitter clock and data recovery loop for half-rate CDR architecture.

## Chapter 3

## An Energy-Efficient Voltage-Mode Tx Using PWM-Based De-Emphasis

In this chapter, we propose a time-based equalization technique to implement de-emphasis in voltage-mode drivers. In section 3.1, a time-based equalization scheme is examined analytically while compensating for loss in backplane channels. In Section 3.2, incorporating the time-based de-emphasis, a 5 Gb/s voltage-mode transmitter is implemented. Section 3.3 shows the efficacy of PWM-based equalization with measurement results for implemented VM Tx prototype. Finally, this project is concluded in Section 3.4.

#### 3.1 Pulse Width Modulation Based De-emphasis

Figure 3.1: Representation of data bits "1" and "0" using PWM pulses with duty cycle D.

A pulse width modulated pulse (PWM) waveform (Fig. 3.1) with duty cycle, D, can be expressed as:

$$p_{pwm}(t) = u(t) - 2u(t - DT) + u(t - T)$$

(3.1)

where T is the bit period,  $0.5 \le D \le 1$  is the duty cycle of the pulse waveform, and u(t) is a step function. The PWM pulse takes on only two discrete output levels  $\pm 1$  and reduces to a non-return-to-zero (NRZ) pulse and a Manchester encoded pulse when D=1 and D=0.5,

respectively.

It was shown in [14] that intersymbol interference (ISI) caused by channel loss can be suppressed by choosing D between 0.5 and 1 appropriately when PWM pulse is transmitted. The impact of duty cycle of the PWM pulse on ISI can be visualized both in the time and frequency domains. In time domain, consider the normalized channel response to a PWM pulse, shown in Fig. 3.2 for three different duty cycle conditions. The channel loss at Nyquist frequency is about 28 dB. Compared to D=1 (unequalized NRZ), D=0.6 pulse response exhibits significantly less ISI, thus illustrating that ISI can be minimized by choosing D optimally.

Figure 3.2: Normalized time domain response of a channel to PWM pulses.

This behavior can also be viewed in frequency domain. The power spectral density of the PWM pulse is calculated to be:

$$|S_{PWM}(f)| = \frac{1}{\pi f} \sqrt{1 + \cos(\pi f T) \left[\cos(\pi f T) - 2\cos((2D - 1)\pi f T)\right]}$$

(3.2)

Plotting the power spectral density  $|S_{PWM}(f)|$  for different duty ratios, as shown in Fig. 3.3, illustrates frequency de-emphasis. Interestingly, the de-emphasis extends beyond the Nyquist frequency in contrast to a conventional n-tap finite impulse response (FIR) filter approach, which de-emphasizes frequencies only below the Nyquist frequency. As a result, PWM-

Figure 3.3: Power spectral density of PWM pulses with different duty cycles.

based de-emphasis exhibits superior ISI suppression. The equalization effectiveness can be quantified by evaluating its response to a bit sequence that generates the largest amount of ISI. The maximum distortion to a received pulse can be evaluated from a single pulse response with peak distortion analysis as discussed below.

#### 3.1.1 Peak Distortion Analysis for PWM-based Equalization

Figure 3.4: Pulse response of a channel for NRZ input pulse.

Figure 3.4 shows a typical pulse response of a channel for an NRZ input pulse. Sampling

instant  $t=T_0$  with peak sampled voltage value  $v_0$  is an ideal sampling location for the bit detection. Voltage values  $v_n$  sampled at  $t=T_0+nT$  where  $n\in Z$  and  $n\neq 0$ , contribute to ISI. These samples can collectively reduce the peak sampled value with a bit sequence for the worst case ISI [15]. Similarly, for each time instant  $t=T_0+\Delta$  of one bit period where  $-T/2 \leq \Delta < T/2$ , the worst case bit sequence leads to the minimum horizontal eye opening due to ISI. The worst case vertical and horizontal eye openings serve as a metric for effectiveness in canceling ISI.

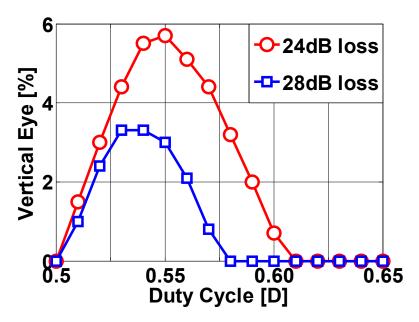

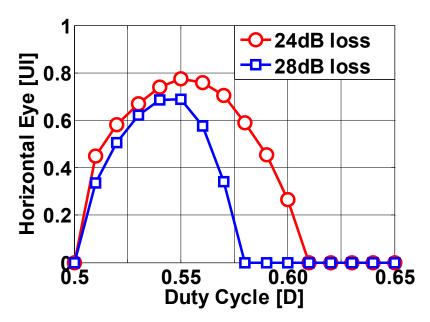

The worst case vertical and horizontal eye openings are calculated with PWM-based equalization for two different channel loss profiles having 24 dB and 28 dB loss at Nyquist frequency, respectively. Figure 3.5 and Figure 3.6 show the worst vertical and horizontal eye openings with varying duty cycle ratio for the two channels, respectively. It is to be noted that the eye was completely closed without de-emphasis (D=1). With an optimum duty cycle ratio, maximum vertical/horizontal eye openings of 5.9%/0.83 UI and 3.4%/0.69 UI can be obtained with channel losses of 24 dB and 28 dB, respectively.

Figure 3.5: Worst case vertical eye opening with peak distortion analysis of PWM-based de-emphasis for two different channels.

These plots also illustrate a duty cycle tuning range to cover the desired channel loss. An optimum duty cycle for PWM-based equalization depends on the channel loss profile. As channel loss decreases, the duty cycle increases, which results in narrower pulses. This

Figure 3.6: Worst case horizontal eye opening with peak distortion analysis of PWM-based de-emphasis for two different channels.

aggravates the pulse generation problem for higher data rates and low-loss channels. Effectiveness of PWM equalization at higher data rates will be technology limited due to the need for generating narrow pulses.

Unlike conventional voltage-based equalization where output voltage swing varies with the number of equalizer taps [16], PWM-based equalization transmits only two voltage levels ( $\pm 1$ ), making it ideally suited for implementing de-emphasis in a voltage mode driver. Specifically, PWM-based de-emphasis offers the following advantages. First, it eliminates the non-linear dependence of driver output impedance on varying output swing present in voltage-mode de-emphasis. Second, it decouples termination impedance from both the amount of de-emphasis and output swing. In other words, driver output impedance can be set to match the channel characteristic impedance, independent of de-emphasis magnitude and resolution.

However, clock jitter has a detrimental impact on transmitter performance regardless of the signaling format (NRZ or PWM). Channel attenuation further exacerbates this due to the so-called jitter amplification effect [17]. To quantify the sensitivity to clock jitter, peak distortion analysis of PWM-based de-emphasis in the presence of jitter is performed in the next section.

## 3.1.2 PWM-based De-emphasis in presence of Jitter

The PWM pulse modulates the input bit sequence  $...b_{k-1}, b_k, b_{k+1}, ...$  to transmit a signal given by

$$y(t) = \sum_{k} (b_k + b_{k-1})u(t - kT) - 2\sum_{m} b_m u(t - \overline{m} + \overline{D}T)$$

(3.3)

There are two edge transitions every bit period and jitter affects both edges corrupting the final duty cycle D. In the presence of jitter j(kT) at bit transition edge and  $j(\overline{m+D}T)$  at duty cycled edge, the jittered transmit signal is  $y_j(t)$  (eq (3.4)). Under Taylor series expansion and approximation  $|j(kT)| \ll T$  and  $|j(\overline{m+D}T)| \ll T$ ,  $y_j(t)$  can be simplified as

$$y_{j}(t) = \sum_{k} (b_{k} + b_{k-1})u(t - kT + j(kT)) - 2\sum_{m} b_{m}u(t - \overline{m} + \overline{D}T + j(\overline{m} + \overline{D}T))$$

$$\approx y(t) + \sum_{k} (b_{k} + b_{k-1})j(kT)\delta(t - kT) - 2\sum_{m} b_{m}j(\overline{m} + \overline{D}T)\delta(t - \overline{m} + \overline{D}T)$$

(3.4)

where  $\delta(t) = 1$  for t = 0 and  $\delta(t) = 0$  for  $t \neq 0$ . The last two expressions in the above equation show the effect of jitter induced ISI in the transmit signal. The performance of PWM-based equalization in the presence of jitter with Gaussian distribution can be estimated with Matlab in the following manner [17]:

- 1. Evaluate the worst case bit sequence  $(d_k)$  for the channel in the presence of ISI and absence of jitter [15].

- 2. Construct the worst case transmit signal using the worst case bit sequence and eq. 3.4 with Gaussian distribution for jitter.

- 3. Convolve the worst case transmit signal with estimated channel impulse response h(t) to measure the received eye in the presence of jitter.

- 4. It is to be noted that the number of jitter samples used above depends on the length of the worst case bit sequence  $(l_{wc})$ . So, the above steps are repeated n times with a

different seed for Gaussian jitter distribution each time to collect large enough jitter samples  $(n \times l_{wc})$  in the end. Finally, the worst case received eye in the presence of jitter is obtained by superimposing received eye diagram for each noise seed.

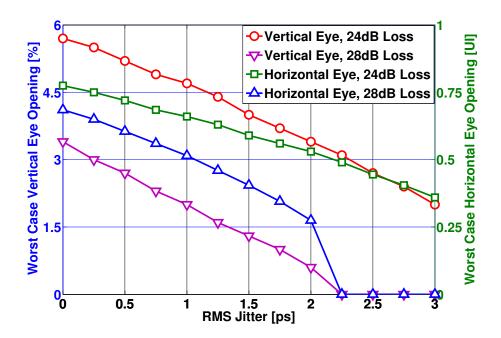

When jitter j(kT) and  $j(\overline{m+DT})$  are independent and identically distributed Gaussian random variables, the worst case vertical and horizontal eye openings obtained from the above algorithm are shown in Fig. 3.7. The worst case eye opening degrades with jitter for two different channel losses. For a channel with 28 dB loss at Nyquist frequency, RMS jitter

Figure 3.7: Worst case received eye opening vs r.m.s jitter amplitude.

in excess of 2 ps together with the worst case bit sequence can close the received eye opening completely. This is a very pessimistic upper bound of the jitter as it assumes worst case jitter and ISI to occur at the same time, but nevertheless provides a guideline for the target jitter specification for the design of clock generation.

Next we implement a voltage mode transmitter incorporating PWM-based equalization to reap the benefits of decoupled impedance matching, equalization, and output swing control.

# 3.2 Voltage-Mode Transmitter with PWM-based De-emphasis

An energy-efficient voltage mode (VM) transmitter has been realized while compensating for large channel loss with PWM-based equalization. PWM-based equalization helps in eliminating tradeoffs between impedance matching, high channel loss compensation, and variable output voltage swing in VM transmitters.

Figure 3.8: Simplified block diagram of the proposed transmitter.

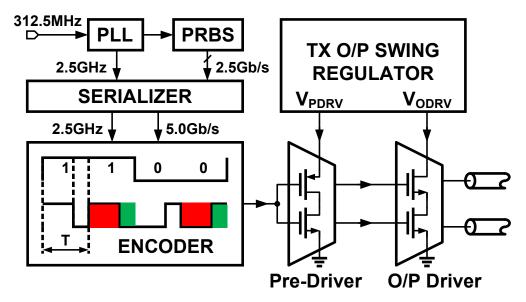

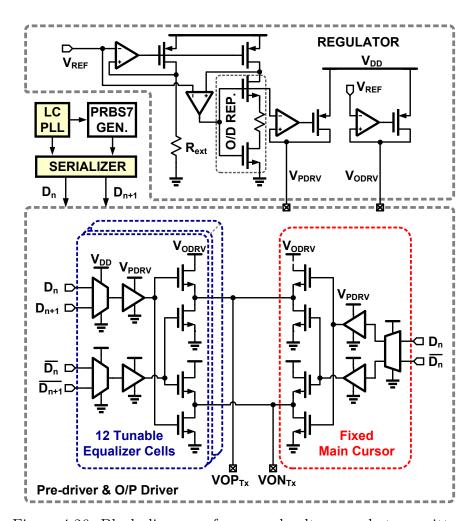

Figure 3.8 shows the proposed voltage mode transmitter architecture. A digital PLL generates 2.5 GHz clock used to serialize half rate  $(2.5 \,\mathrm{Gb/s})$  PRBS data to  $5 \,\mathrm{Gb/s}$  NRZ data stream. At the heart of the TX is the ENCODER that converts  $5 \,\mathrm{Gb/s}$  NRZ data into pulse width modulated data. The duty cycle of the PWM output signal is adjusted in the encoder in accordance with the channel loss. The encoder output is buffered using a predriver and transmitted using a conventional N-over-N voltage mode driver. Driver output swing and impedance are independently controlled by properly setting supply voltage of the main driver  $(V_{\mathrm{ODRV}})$  and pre-driver  $(V_{\mathrm{PDRV}})$ , respectively. On-chip low dropout regulators are used to generate  $V_{\mathrm{ODRV}}$  and  $V_{\mathrm{PDRV}}$ . Implementation details of the key building blocks of the transmitter are discussed below.

#### 3.2.1 Encoder

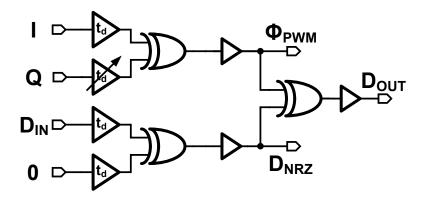

Figure 3.9: Simplified block diagram of encoder.

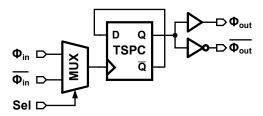

The simplified block diagram of the encoder is shown in Fig. 3.9. Using quadrature phases (I/Q) of a 2.5 GHz clock and 5 Gb/s non-return-to-zero data ( $D_{IN}$ ), the encoder generates a pulse-width modulated output data stream,  $D_{OUT}$ . The top half of the encoder circuit operates on I/Q phases and generates a 5 GHz clock ( $\Phi_{PWM}$ ) with variable duty cycle. When all of the I/Q phases are delayed by the same amount,  $t_d$ , the output duty cycle is equal to 50%. By varying the delay of phase Q with respect to phase I, the duty cycle can be varied both above and below the nominal value of 50%. Because the delay can be tuned precisely, the de-emphasis resolution can be as high as desired. The bottom half of the encoder circuit is used to maintain the phase relationship between the I/Q phases and  $D_{IN}$  at the output. To this end,  $D_{IN}$  is passed through a delay path that is matched to that of the I/Q phases. The output 5 Gb/s PWM data is generated by XORing  $\Phi_{PWM}$  with  $D_{NRZ}$  as depicted in the final stage in Fig. 3.9. The delay cells and CMOS XOR gate in the encoder are crucial to PWM-based equalization and are discussed next.

# 3.2.1.1 Current Controlled Delay Cell

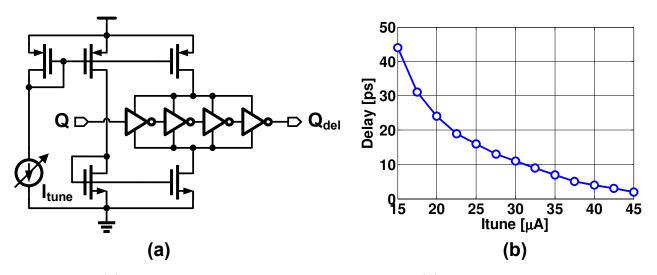

The programmable delay is implemented by a cascade of current-starved inverters (delay cells) as shown in Fig. 3.10(a). An even number of delay cells are used to minimize duty cycle distortion otherwise caused by both asymmetric and unequal number of high-to-low and low-to-high transitions for odd number of cells. The delay is controlled using an external

Figure 3.10: (a) Schematic of current controlled delay cell. (b) Tuning characteristic of the delay cell (output delay vs. tuning current).

current source ( $I_{tune}$ ). The simulated transfer characteristic of a delay cell, including its parasitics extracted from the layout, is shown in Fig. 3.10(b). The output delay is offset from the nominal delay at  $I_{tune}$ =50  $\mu$ A. A total delay tuning range in excess of 30 ps is achieved, which is adequate to compensate for channel loss ranging from 16 dB to 28 dB.

## 3.2.1.2 XOR-based Pulse Width Modulation

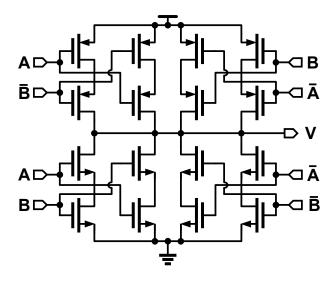

Figure 3.11: Pseudo-differential fully symmetric XOR gate.

The performance of the last stage CMOS XOR gate is critical to maintaining high fidelity

of the PWM output. Limited bandwidth of the static CMOS logic data causes intersymbol interference, which degrades equalization performance. Even an order of few fF of parasitic capacitance at internal nodes of the XOR gate (Fig. 3.11) can cause significant ISI.

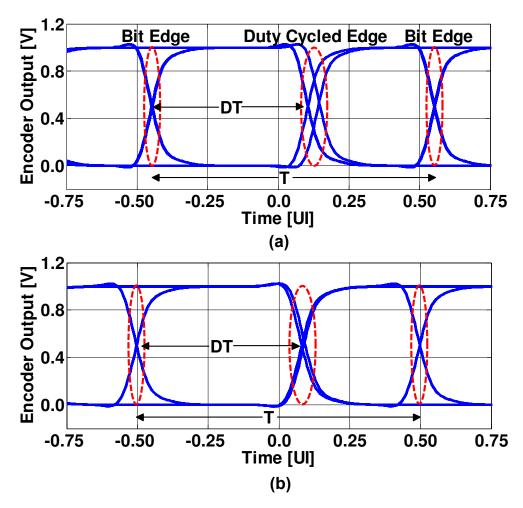

Figure 3.12: Eye diagram at the output of the encoder: (a) with bandlimited CMOS XOR gate (b) after optimizing transistor sizes and layout.

This ISI effect could be observed in the simulated output eye diagram shown in Fig. 3.12(a). The figure shows two transitions every bit period. 'Bit Edge' marks the beginning and end of each bit period. 'Duty Cycled Edge' marks the intermediate transition edge reflecting the duty cycle of the bit waveform. Bit edge has less jitter whereas the duty cycled edge shows two distinct streaks of jitter. This is due to two different kinds of transitions at the duty cycled edge: (i) a transition at the duty cycled edge for consecutive identical bits, and (ii) a transition at the duty cycle edge just after the bit transition 1-to-0 or vice versa.

This data-dependent jitter degrades the effectiveness of PWM equalization by corrupting the duty cycle ratio. For this reason, the CMOS XOR gate is optimized for minimal parasitic capacitance at all internal nodes. Figure 3.12(b) shows the simulated output of the encoder with extracted parasitic capacitance. The typical peak-to-peak jitter is about 4.2 ps. The XOR output is buffered to drive the output drivers. XOR gates used for just passing the data to emulate the delay in the clock modulation path are independently optimized as they operate with static inputs (either 1 or 0).

Figure 3.13: Complete block diagram of the pseudo-differential encoder.

The complete block diagram of the pseudo-differential encoder is shown in Fig. 3.13. The duty cycle modulated 5 GHz clock signal,  $\Phi_{\rm PWM}$ , and its compliment  $\overline{\Phi}_{\rm PWM}$  are generated by XORing I with Q and  $\overline{\rm I}$  with Q, respectively.  $D_{\rm NRZ}$  and its compliment  $\overline{D}_{\rm NRZ}$  are generated in a similar fashion. Differential PWM outputs are generated by XNORing  $\Phi_{\rm PWM}$  with  $D_{\rm NRZ}$  and XORing  $\overline{\Phi}_{\rm PWM}$  with  $\overline{D}_{\rm NRZ}$ . Cross-coupled inverters are inserted to maintain the differential nature of all the pseudo-differential signals.

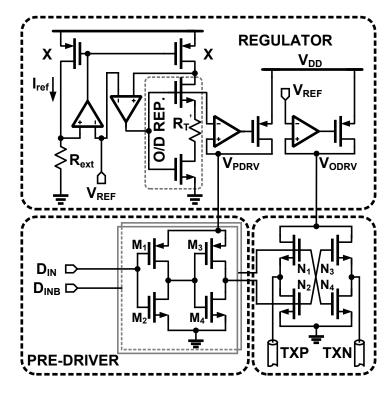

Figure 3.14: Schematic of voltage mode output driver.

## 3.2.2 Voltage Mode Output Driver

The block diagram of the voltage mode output driver is shown in Fig. 3.14. The output stage consisting of NMOS transistors N1-N4 operates with a regulated supply voltage of  $V_{ODRV}$ . A low dropout regulator sets  $V_{ODRV}$  to be equal to an external reference voltage  $V_{REF}$ , which makes the peak-to-peak differential output voltage swing also equal to  $V_{ODRV} = V_{REF}$  and current consumption equal to  $V_{REF}/4R_T$ . Transistors N1-N4 are driven by a CMOS inverter based pre-driver, whose supply voltage is  $V_{PDRV}$  [18]. A bias circuit consisting of a replica of the output driver and a low dropout regulator generates  $V_{PDRV}$  so that the output impedance of the replica driver is matched to the reference resistor,  $R_{ext}$ . This replica-biasing ensures that the main driver output impedance is matched to the channel characteristic impedance. To save power in the replica biasing circuit,  $R'_T$  is scaled up by a factor of 8X and the output driver replica is scaled down by the same factor in comparison to the main output driver. Here, the output driver has minimum number of internal nodes as compared to the internal nodes in digitally controlled and segmented output drivers [9] or in output drivers with analog impedance control through transmission gate [19]. This helps to

suppress data dependent ISI while transmitting sub-bit rate pulses. The pre-driver consists of two inverters implemented using transistors M1/M2 and M3/M4 (Fig. 3.14). It acts as a level-shifting buffer and converts rail-to-rail swing encoder output to the lower swing input signals of the output drivers. The two inverters are separately optimized to minimize duty cycle distortion.

### 3.2.3 Digital Phase Locked Loop

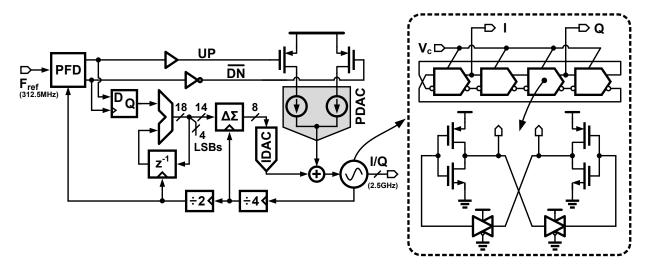

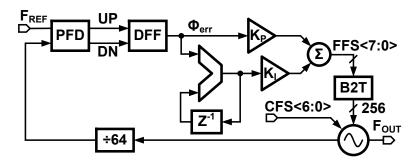

Figure 3.15: Digital phase-locked loop (DPLL) block diagram.

Low jitter I/Q clock phases at 2.5 GHz are generated from a 312.5 MHz reference clock using a type-II digital phase locked loop (DPLL) shown in Fig. 3.15 [20]. It consists of a linear proportional path, a digital integral path, a current controlled ring oscillator (CCO) with quadrature outputs, and a feedback divider. Proportional control is implemented by driving the CCO with the linear phase frequency detector (PFD) output through a three-level current DAC (PDAC). Because the pulse width of the PFD output is proportional to the input phase error, no quantization error is introduced into the loop. Integral control is implemented by accumulating the sign of the PFD output, measured using a bang-bang phase detector. The quantization error introduced by the bang-bang phase detector is suppressed by the 18 bit digital accumulator in the integral path. The lower 4 LSBs of the accumulator output are ignored to suppress the jitter caused by limit cycles and the rest

of the 14 MSBs are truncated to 8 bits using a second-order digital delta sigma modulator (DSM). The DSM output controls the oscillator through an 8 bit thermometer coded DAC (IDAC). The DSM is clocked at twice the frequency of the incoming digital input to reduce inband quantization error. The current controlled oscillator is implemented using a cascade of 4 pseudo-differential CMOS inverters coupled in a feedforward manner using transmission gates (see Fig. 3.15).

## 3.3 Measurement Results

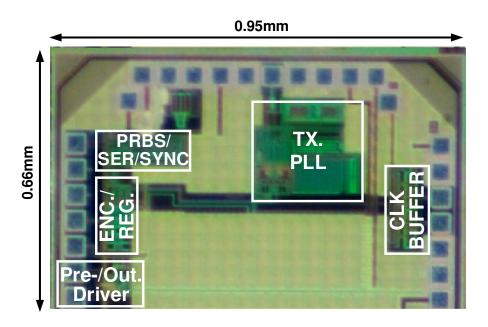

Figure 3.16: Die photo of the proposed transmitter.

The proposed transmitter was implemented in a 90 nm CMOS process and packaged in 60 pin QFN package. The transmitter occupies an active area of 0.13 mm<sup>2</sup> (Fig. 3.16).

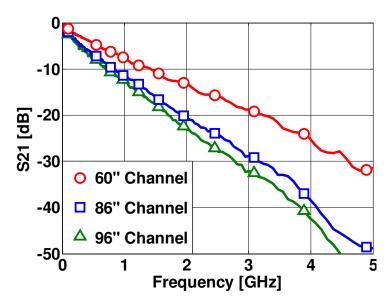

The performance of the transmitter is characterized across three stripline channels of varying length (and loss) fabricated on a FR4 PCB board. Figure 3.17 shows the measured frequency response (S21) of the three channels, which indicates a loss of 16 dB (60 inch), 24 dB (86 inch), and 28 dB (96 inch) at the Nyquist frequency of 2.5 GHz. In addition to the stripline trace, the channel includes bondwires, package parasitics, 1.5 inch on-board microstrip line, SMA connectors, and SMA cables.

Figure 3.17: Measured frequency response of FR4 stripline channels.

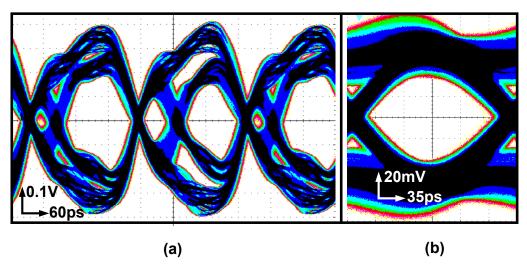

Figure 3.18: (a) TX eye diagram at the input of channel with 16 dB loss, and (b) received eye diagram at the output of the channel.

The differential output eye diagram when transmitting PRBS7 data across a 60 inch channel is shown in Fig. 3.18(a). An asymmetry between the odd and even bits is caused by duty cycle distortion of the clock phases. Loading mismatch on clock phases generated and routed on-chip resulted in the clock duty cycle distortion. The differential eye diagram at the output of the channel, shown in Fig. 3.18(b), indicates a vertical eye opening of 78 mV and horizontal eye opening of 0.6 UI. The duty cycle of the PWM signal to achieve this eye opening is roughly equal to 65%.

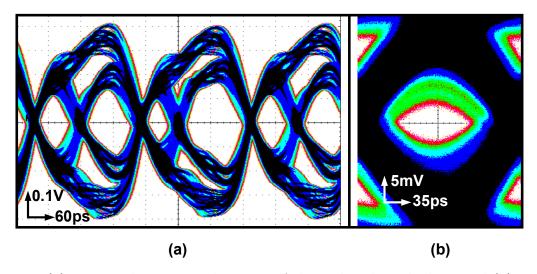

Figure 3.19: (a) TX eye diagram at the input of channel with 28 dB loss, and (b) received eye diagram at the output of the channel.

The experiment was repeated with a 96 inch channel and the resulting differential eye diagrams are shown in Fig. 3.19. Due to higher loss compared to the 60 inch channel, the optimal duty cycle of the PWM signal in this case is close to 58%. It can also be observed that the duty cycle distortion of clock phases has a greater impact on the received eye.

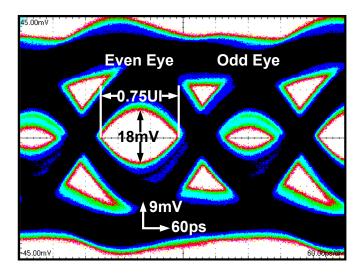

Figure 3.20 depicts that the vertical/horizontal eye openings of the odd and even bits are  $8\,\mathrm{mV}/0.3\,\mathrm{UI}$  and  $18\,\mathrm{mV}/0.75\,\mathrm{UI}$ , respectively. The wider eye opening of the even bits indicates that the performance can be further improved by correcting the clock duty cycle distortion.

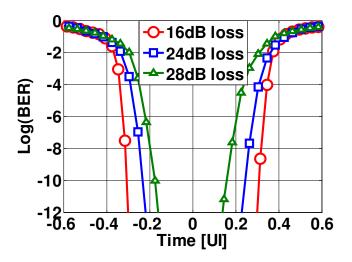

The transmitter performance is also measured in terms of BER at the RX end. To this end, bathtub curves are measured using 80SJNB BER analysis software and Tektronix DSA8200 sampling oscilloscope and plotted in Fig. 3.21. The transmitter achieves BER  $< 10^{-12}$  with

Figure 3.20: Received eye opening at the end of channel with 28 dB loss.

Figure 3.21: Bathtub plots for different channel loss.

a timing margin of 0.6 UI and 0.3 UI for channel loss of 16 dB and 28 dB, respectively.

Figure 3.22: Horizontal eye opening vs. peak-to-peak transmit amplitude.

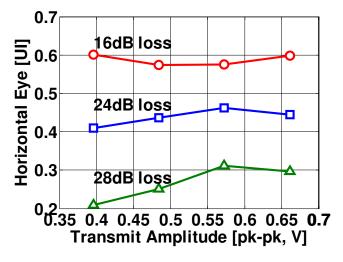

The performance of the transmitter was also evaluated across a range of amplitudes of the transmitted signal. The measured horizontal eye opening for BER =  $10^{-12}$  with various output amplitudes shown in Fig. 3.22 illustrates that the horizontal eye opening remains fairly constant for the 16 dB loss channel and varies by about 0.1 UI with higher loss channels.

Figure 3.23: DPLL jitter histogram at 2.5 GHz output.

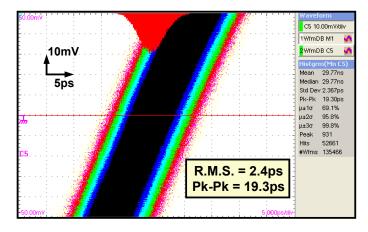

The measured long-term absolute jitter of the digital PLL at 2.5 GHz output frequency is shown in Fig. 3.23. It achieves 2.4 ps r.m.s. and 19.3 ps peak-to-peak jitter.

The taxonomy of the total power dissipated in the transmitter at 0.66 V output swing is provided in Table 3.1. The total power is 15.6 mW, which translates to a power efficiency of 3.1 mW/Gb/s. Increased frequency operation for pre-driver and output drivers while

Table 3.1: Power summary of 5 Gb/s VM Tx.

|               | Power [mW] |

|---------------|------------|

| Serializer    | 0.84       |

| Encoder       | 4.32       |

| PLL           | 2.55       |

| Pre-driver    | 1.31       |

| Output driver | 2.61       |

| Regulator     | 3.92       |

| Total Power   | 15.6       |

transmitting sub-bit rate pulses increases the power consumption compared to conventional NRZ-based pre-/output drivers. However, the power of the transmitter as a whole compares favorably while compensating for high channel loss (28dB). The performance of the transmitter is compared with other state-of-the-art transmitters in Table 3.2. This work achieves 7.1 times better power efficiency (mW/Gb/s) compared to [14]. A simple FOM1=mW/Gb/s does not signify the effort in equalizing the channel loss. So, a modified FOM2 defined below is also used to make the comparison [19].

$$FOM2 = DR(Gb/s) \times 10^{(Channel loss/10)} / Power(mW)$$

(3.5)

where 'DR' is the data rate, and channel loss is in 'dB'. Larger FOM2 indicates better performance. This work achieves a maximum FOM2 of 202 which is 2.2X better than [14].

Figure 3.24: Simulated differential return loss (S11) for the TX.

Table 3.2: Performance summary for 5 Gb/s VM Tx and comparison to the state-of-the-art.

|                     | JSSC06 [14] | ISSCC08 [19] | JSSC13 [2] | This Work    |      | k    |

|---------------------|-------------|--------------|------------|--------------|------|------|

| Technology [nm]     | 90          | 90           | 65         | 90           |      |      |

| Supply Voltage [V]  | 1.2         | 1.2          | 1.2        | 1.0/1.1/1.25 |      |      |

| Data Rate [Gb/s]    | 5           | 8            | 10         | 5            |      |      |

| Channel Loss [dB]   | 33          | 37           | 13         | 16           | 24   | 28   |

| Equalization Scheme | PWM         | FFE-5/       | FFE-2      | PWM          | PWM  | PWM  |

|                     | (CML)       | DFE-2/CTLE   | (VM)       | (VM)         | (VM) | (VM) |

| Vertical Eye [mV]   | 15          | -            | 200        | 78           | 18   | 8    |

| Horizontal Eye [UI] | 0.75        | 0.11         | 0.78       | 0.60         | 0.45 | 0.30 |

| Power [mW]          | 110         | 232*         | 11         | 15.1         | 15.6 | 15.6 |

| On chip PLL         | NO          | YES          | NO         | YES          |      |      |

| FOM1 [mW/Gb/s]      | 22          | 29           | 1.1        | 3.0          | 3.1  | 3.1  |

| FOM2                | 91          | 165          | 18.1       | 13.3         | 80.0 | 202  |

<sup>\*</sup> Total power for TX and RX.

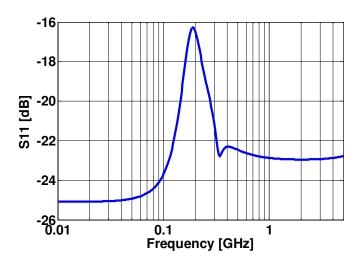

Figure 3.24 shows the simulated differential return loss measurement for the TX including the parasitics extracted from the layout. Here, the TX is biased for  $0.65\,\mathrm{V}$  peak-to-peak differential output swing. The differential return loss is  $\leq$ -16 dB over a frequency range 0-5 GHz.

# 3.4 Summary