## TUTORIAL ON DESIGNING AND SIMULATING A TRUNCATION SPURS-FREE DIRECT DIGITAL SYNTHESIZER (DDS) ON A FIELD-PROGRAMMABLE GATE ARRAY (FPGA)

$\mathbf{B}\mathbf{Y}$

SHUO LI

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2015

Urbana, Illinois

Adviser:

Professor José E. Schutt-Ainé

## Abstract

Direct digital synthesis is a technique for using digital data processing blocks as a means to generate a frequency and phase tunable output signal referenced to a fixed-frequency precision clock source. Many telecommunication applications require such a high-speed switching, fine-tuning and superior quality signal source for their components. This thesis will introduce the direct digital synthesizer (DDS) and investigate the signal integrity issues associated with the DDS design.

In order to minimize the size of the lookup table to save hardware and lower the power consumption, we normally truncate the phase word output from the phase accumulator in the standard approach of designing DDS. However, this process will generate spurious frequencies (spurs), which degrade the quality of the output signals. It is considered one of the main signal integrity issues in the DDS design.

Previous research introduces a novel spurs-free truncation method for compressing the lookup table to avoid using phase truncation without significant hardware change. This thesis aims to implement this DDS with novel truncation spurs-free structure and test it in a practical environment. It does so by providing a tutorial on designing, implementing and simulating the DDS on an Altera DE2-115 FPGA using Altera Quartus II FPGA design software and ModelSim Simulator. The Verilog hardware description language is used as the development language. This thesis will describe entire designs of both DDS with traditional structure and DDS with novel truncation spurs-free structure. By comparing the outputs, it also examines the corresponding simulation results and verifies the improvement of the signal quality.

To my family, professors and friends for their love and support.

## Acknowledgments

First of all, I would like to give my sincere gratitude to my graduate thesis advisor, Professor José E. Schutt-Ainé, for all his kind help, support, encouragement and guidance on my graduate study. He is a very kind and knowledgeable professor who is always willing to help the students when they are in need. I feel blessed that I have had the opportunity to learn from and work with my brilliant advisor and his research group in the past year.

Second, I would like to thank all my colleagues in Professor José E. Schutt-Ainé's research group. They are not only excellent researchers, but also great friends who are always very generous and helpful. The happy hours spent with them are really enjoyable. I would like to give my special thanks to my good friends in graduate school: Mujing Wang, Tao Yang, Xinying Wang, Jin Lei, Xu Chen, Xiao Ma, Albert Zaichen Chen, Mao Li, Linyang Zhang, Xinyang Song and Liang Zhang for all the inspirational talks and sweet memories we have together.

Thanks to Mr. Karan Bhagat and Mr. Yuanwang Yang who started this project and provided a detailed tutorial for me to carry on. Thanks to all the ECE staff, especially for Ms. Jen Carlson and Ms. Laurie Fisher who offered me great help during my graduate study at the University of Illinois at Urbana-Champaign.

Last but not least, I would like to give my sincere thanks to my parents, grandparents, girlfriend and sister for their continuous support, trust, understanding and love.

# Contents

| Chapter 1. INTRODUCTION                                                      |

|------------------------------------------------------------------------------|

| 1.1 Motivation1                                                              |

| 1.2 Outline                                                                  |

| Chapter 2. THEORETICAL ANALYSIS OF DDS                                       |

| 2.1 Theoretical Analysis of DDS with Traditional Structure                   |

| 2.2 Types of Spurs in DDS                                                    |

| 2.3 Theoretical Analysis of DDS with a Novel Truncation Spurs-Free Structure |

| Chapter 3. INTRODUCTION TO VERILOG                                           |

| 3.1 Resources                                                                |

| 3.2 Verilog Design Examples                                                  |

| Chapter 4. FPGA DESIGN FLOW                                                  |

| 4.1 Introduction to FPGA                                                     |

| 4.2 Design Flow                                                              |

| Chapter 5. FPGA DESIGN TUTORIAL IN QUARTUS II                                |

| 5.1 Project Setup                                                            |

| 5.2 HDL Coding                                                               |

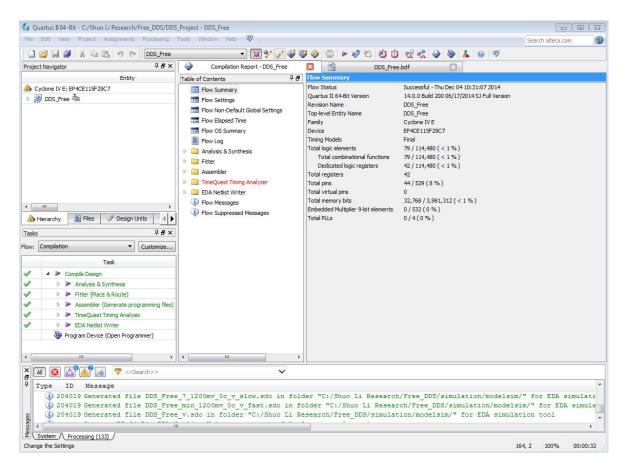

| 5.3 Compilation                                                              |

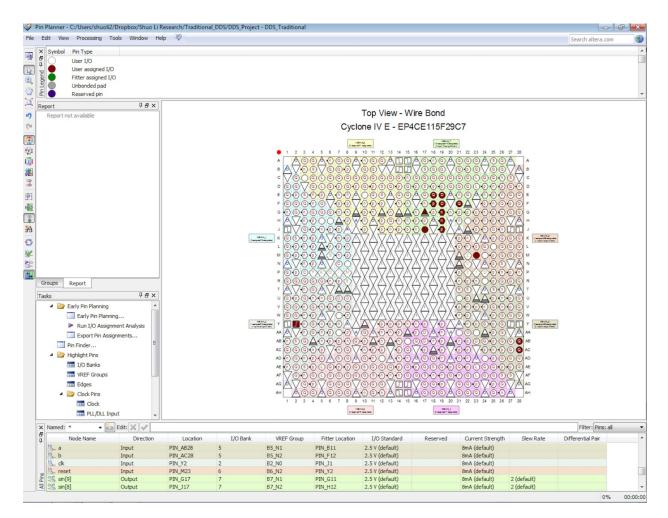

| 5.4 FPGA Configuration and Programming                                       |

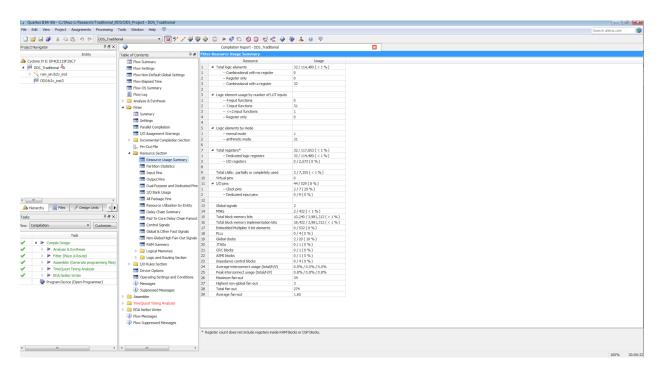

| 5.5 Design Resources and Statistics                                          |

| 5.6 Instructions on Writing Testbench55                                      |

| 5.7 Behavioral/Gate Level Simulation in Altera-ModelSim56                    |

| Chapter 6. DDS MEASUREMENTS                                                  |

| 6.1 Measurements of DDS with Traditional Structure59                         |

| 6.2 Measurements of DDS with Truncation Spurs-Free Structure                 |

| Chapter 7. CONCLUSION                                                        |

| 7.1 Summary64                                                                |

| 7.2 Future Work                                                              |

| Appendix A: SETTING UP MODELSIM | 65 |

|---------------------------------|----|

| Appendix B: VERILOG MODULES     | 68 |

| References                      | 76 |

# **Chapter 1. INTRODUCTION**

## **1.1 Motivation**

A direct digital synthesizer (DDS) is a type of frequency synthesizer used for generating arbitrary waveforms referenced to a single, fixed-frequency clock. Nowadays, the cost-competitive, high-performance, functionality-integrated and small package-sized DDS products are widely used in the field of telecommunications and are becoming an alternative to some traditional analog synthesizer solutions. The applications of DDS include signal generation, local oscillators, function generators, mixers, modulators, and sound synthesizers.

The advantages of DDS are the following [1]:

1. Precise tuning resolution in micro-hertz and sub-degree phase tuning capability.

**Application example:** Because the DDS is able to generate signals at very precise frequencies, it is useful for the applications that require phase continuous frequency sweeping such as filter characterization [2].

2. High speed tuning while keeping the phase continuous with no overshoots or undershoots.

Application example: Function generators.

3. Digital architecture ensures no need for manual tuning or tweaking associated with component aging and temperature drift in an analog synthesizer solution.

Application examples: Local oscillator for digital phase-locked loop (PLL)

4. Digital control interface enables the system to be remotely controlled, minutely optimized and under processor control.

With the above advantages over the traditional analog frequency synthesis technologies, it seems obvious that direct digital synthesis technology should be able to dominate the frequency synthesis area. However, the signal integrity problems mainly caused by the spurs have limited its usage in many high-demand applications. Among them, the truncation spurs generated from the phase truncation in the standard DDS design process are the primary problem and have become a major signal integrity issue in the DDS design.

By investigating and understanding the sources of the spurs, previous research has come up with a truncation spurs-free method for compressing the look-up table to avoid phase truncation without significant increase of hardware usage [3]. The motivation of this thesis is to design such a DDS with truncation spurs-free structure and verify the improvement of the signal quality. Since it is a preliminary research work, the DDS will be designed and implemented in Verilog codes that are synthesizable on an FPGA. FPGA is widely used in digital circuit design for its flexibility, accuracy and effectiveness. The most significant advantage of using an FPGA is that designs can be created and changed in a very short period. Instead, with application specific integrated circuits (ASIC), the designers will have to wait months for the circuits to be fabricated [4]. In this thesis, we aim to investigate the truncation spurs-free method; therefore, we will adjust the design and parameters along the way, so it is more feasible for us to use the FPGA design approach. However, on the other hand, the FPGA will limit the highest frequency we can reach. In this thesis work, the fixed reference clock frequency is 50MHz, which is the maximum FPGA on-board clock.

#### 1.2 Outline

This thesis will serve as a complete tutorial on the background knowledge of DDS with traditional structure and DDS with truncation spurs-free structure as well as how to design and implement them in Verilog that are synthesizable on FPGA and simulate them with ModelSim.

- 1. Chapter 2 provides an overview of the structure and operation of the DDS with both traditional and truncation spurs-free structures. Additionally, it introduces which types of spurs that may exist, the reason why they exist and the method for eliminating the truncation spurs.

- 2. Chapter 3 serves as an introduction to Verilog HDL. It addresses the necessary knowledge that we should have about Verilog for completing this project by providing examples of some major blocks in digital circuit design.

- 3. Chapter 4 introduces the background knowledge of FPGA and the FPGA design flow

- 4. Chapter 5 presents a detailed and complete step-by-step tutorial on designing, implementing and simulating both DDS with traditional structure and DDS with truncation spurs-free structure on FPGA in Altera Quartus FPGA development software.

- 5. Chapter 6 presents the simulation results from the different structures of DDS and some theoretical analysis of the results.

- 6. Chapter 7 concludes this thesis with a summary and potential topics for further research.

## **Chapter 2. THEORETICAL ANALYSIS OF DDS**

#### 2.1 Theoretical Analysis of DDS with Traditional Structure

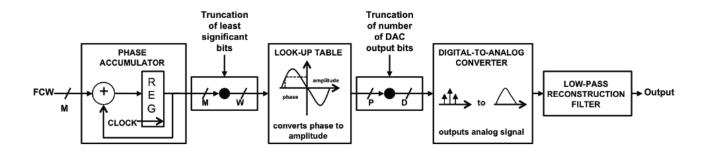

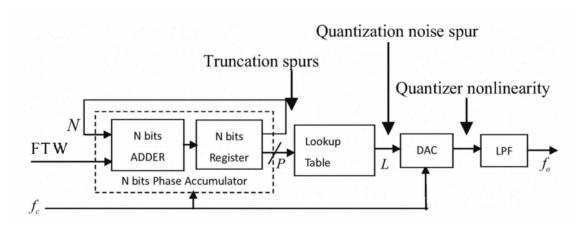

The traditional direct digital synthesizer (DDS) mainly consists of four primary components. The first one is the phase accumulator (PA), which determines the frequency range and accuracy of the output signal. The second component is the lookup table (LUT), which is used to store the amplitude information of the quantized and discrete sine wave. The third component is the digital to analog converter (DAC), which generates analog signal. The fourth component is the low pass filter (LPF), which is used to smoothen the output signal [5],[6]. The traditional structure of DDS is shown in Figure 2.1 [4].

Figure 2.1: Traditional Structure of DDS

The operation of the DDS starts with applying a frequency control/tuning word (FCW/FTW) to the PA. With referencing a fixed input clock, the PA will increment by the M-bit FCW (M = 32) in our design) once in each clock cycle and the result value is stored in an inbuilt register. The output of the register will loop back to be accumulated with input FCW in the next clock cycle. The output of the PA is then truncated from M-bit to W-bit (W<M) and fed into the input of LUT. The process of truncation is simply elimination of the lower order bits. The LUT will take the W-bit word (W = 8 in our design) as the phase of the sine wave and generate the amplitude. Therefore, the LUT is also called a phase to amplitude converter. The quantized version of the sine wave is then fed into the DAC, which generates the analog output signal. Generally, the bit width of the DAC input is always limited. Therefore, the output of the LUT is truncated again before being fed into the DAC. After converting the digital signal to analog signal, the output of DAC is then fed into the LPF, which reduces the noise and eliminates the spikes of the signal [1],[4]. The main consideration is that PA and DAC should operate on the same reference clock. Even though the PA is clocked, it still operates very fast; however, the speed of DAC and LPF is relatively low due to their design architecture [7]. Now, we will look into the details in each component and understand the background theory on how exactly the DDS works.

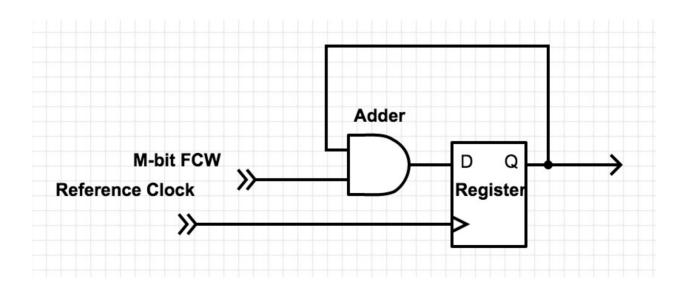

#### Phase Accumulator (PA):

The PA is constructed by an adder and a built-in register. In each clock cycle, we can realize the accumulation by adding the output of the register from last clock cycle back to the input of the adder. Then, the M-bit output of PA will increment by FCW. The structure of the PA is shown in Figure 2.2.

Figure 2.2: Structure of Phase Accumulator

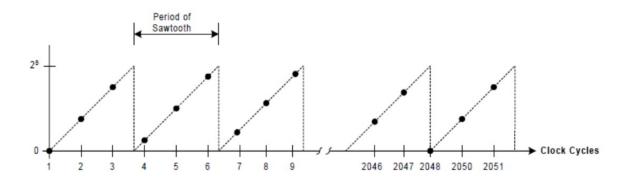

The output of PA forms a quantized saw-tooth waveform as shown in Figure 2.3 [1],[4]. Each dot on the saw-tooth waveform is the actual value of PA output.

Figure 2.3: Behavior of Truncation Words

In Figure 2.2, we name the reference clock frequency of DDS system as  $f_{clock}$ . DDS conducts frequency accumulation from the "Phase" concept. As we mentioned above, the PA is constructed by an adder and a register. For each coming clock impulse, the adder will add FCW with the output of the PA from the last clock cycle, then send the sum back to the output of the PA to realize accumulation. In this way, PA will increment by FCW once at each coming clock impulse. The output data is the phase of the synthesized signal. The overflow frequency of the PA is the frequency of the DDS output signal.

PA is the core of DDS system that generates phase information of the signal increment. For the sine wave, instant amplitude completely depends on instant phase according to Equation 2.1

$$\omega = \frac{\mathrm{d}\phi(t)}{\mathrm{d}t} \tag{2.1}$$

Therefore, the faster the phase change, the higher the signal frequency.

The PA applies the overflow feature of M-bit binary adder to simulate  $2\pi$  phase cycle of the ideal sine wave. The output of the PA can be considered as the phase signal of the ideal sine wave while the output of LUT can be considered as the clock sampling of the time-domain waveform.

Let M be the word length of the PA and  $f_{clock}$  as the reference clock frequency; then the clock cycle is shown as Equation 2.2.

$$T_c = \frac{1}{f_{clock}} \tag{2.2}$$

Then, the PA has 2<sup>M</sup> possible values. FCW is the frequency control word. During the working process of the system, the increment of the PA in each clock cycle is

$$\Delta \phi = FCW \times \frac{2\pi}{2^M} \tag{2.3}$$

The corresponding angular frequency would be

$$\omega = \frac{\Delta \Phi}{\Delta t} = \frac{\Delta \Phi}{T_c} = FCW \times \frac{2\pi f_{clock}}{2^M}$$

(2.4)

Therefore, the output frequency of the DDS is

$$f_{DDS} = \frac{\omega}{2\pi} = FCW \times \frac{f_{clock}}{2^M}$$

(2.5)

From Equation 2.5, we know that the larger the FCW, the faster the PA jumps, which leads to a higher frequency at the output. The resolution of the DDS output signal or the step interval of the  $f_{DDS}$  is

$$\Delta f_{DDS} = \frac{f_{clock}}{2^M} \tag{2.6}$$

Since the output signal of the DDS is the sampling synthesis of the sine wave, it is very important to fulfill the Nyquist theorem requirement. The Nyquist theorem states: "If a function x(t) contains no frequencies higher than B Hz, it is completely determined by giving its ordinates at a series of points spaced 1/(2B) seconds apart," [4],[8],[9]. Equation 2.5 is conditional, given that Equation 2.7 is true [9].

$$f_{DDS} = \frac{f_{clock}}{2} \tag{2.7}$$

Thus,

$$FCW \le 2^{M-1} \tag{2.8}$$

According to the characteristic requirement of the spectrum, we normally choose [1]

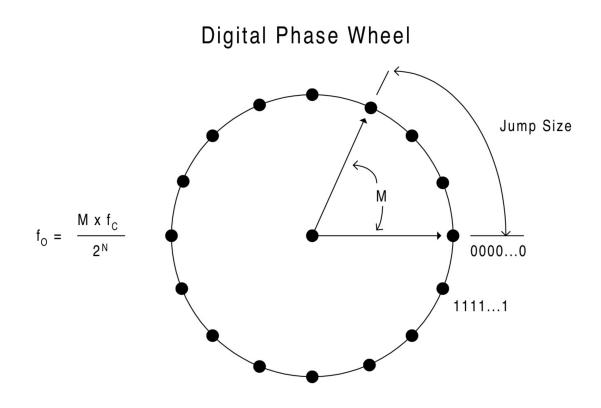

$$f_{DDS} \le 0.4 f_{clock} \tag{2.9}$$

For a more straightforward explanation, the function of PA performs as a "phase wheel." Shown as Figure 2.4, the sine wave oscillation is considered as a vector rotation around a phase circle. Each designated point on the phase wheel corresponds to an equivalent point on a full cycle of a sine wave. As the vector rotates, the corresponding output sine wave is being generated. When the vector finishes rotating the whole phase wheel at a constant speed, it means that a complete cycle of sine wave is outputted. The contents of the PA correspond to the points on the cycle of the sine wave. The number of discrete phase points on the phase wheel depends on the resolution of the PA, which is  $f_{clock}/2^{M}$  in this thesis design. The larger the M, the larger number of discrete phase points we have on the phase wheel (the number is  $2^{M}$ ). However, the output of the PA is linear, so it cannot be used to generate a sine wave directly; it is the reason that the DDS system includes a LUT [1].

Figure 2.4: Digital Phase Wheel

#### Lookup Table (LUT):

The lookup table (LUT) serves as a phase-to-amplitude converter, which is used to convert a truncated version of the PA's instantaneous output value into the discrete sine wave amplitude information that is presented to the D/A converter [1]. It consists of a read only memory (ROM). By using the output data of the PA as the phase sampling address, we can get waveform sampling data (binary code) stored in the LUT, then complete the phase-to-amplitude conversion. To keep the LUT reasonably sized, we truncate the bits from the PA and only feed the higher order bits to the input of LUT to save the hardware resources and power.

The LUT contains unique values of a sine wave over one period; however, most DDS architectures will exploit the symmetrical nature of a sine wave and utilize mapping logic to synthesize a complete sine wave cycle from a quarter cycle of data from the PA. The LUT will generate the all the necessary data by reading forward and backward through the LUT [1],[10].

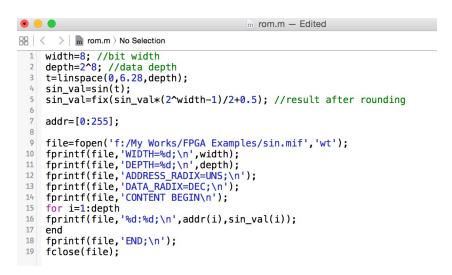

In the FPGA design, one will need a Memory Initialization File [.mif] containing the values of the LUT. We use MATLAB to generate this file with the file extension as ".mif". This file will be added to the ROM [4]. For details, please refer to **Section 5.2-6**.

#### **Digital to Analog Converter (DAC)**

The digital to analog converter (DAC) is applied to create an analog waveform from the digital discretized sine wave. Since the bit width of the DAC is generally limited, we will need to apply a second truncation process to the output of the LUT to get a word with appropriate number of bits and then feed it to the DAC input. An important fact is that the DAC plays a big role for limiting the design's maximum attainable frequency because the PA and DAC need to work with same reference clock. In this thesis, we design and implement the DDS completely in HDL, and perform the behavioral and post map & route simulations with ModelSim, so we don't need an actual DAC. Also, DAC will bring other sources of spurs, which may influence the results. Further potential research directions in this topic may need to have an actual DAC or even involve designing DAC. Please refer to **Section 7.2** for details.

#### Low Pass Filter (LPF):

In the DDS design, the LPF performs as a reconstruction filter, which reduces the noise and eliminates the spikes of the input signal that come from the DAC. Since we do not want any aliases of the fundamental frequency, the LPF also performs as an antialiasing filter; therefore, it limits us to the Nyquist frequency. Due to the sharp frequency response characteristics, a Chebyshev filter is typically used on this stage [1]. Same with the DAC, we don't need an actual LPF in this thesis work.

## 2.2 Types of Spurs in DDS

The direct digital synthesis (DDS) technology has several advantages over the traditional analog frequency synthesis technologies in terms of high-frequency resolution, high-speed frequency tuning, continuous phase and so on. However, the signal quality issues primarily caused by the spurs limit the usage of DDS technology in many high-demand applications. The three major sources of spurs are shown as Figure 2.5:

Figure 2.5: Three Major Sources of Spurs

#### **Phase Truncation Spurs:**

In order to obtain high-frequency resolution at the DDS output, the bit width of the phase accumulator must be sufficiently wide, typically 24-48 bits [1],[3]. However, in order to design a smaller sized lookup table (LUT) that only needs a reasonable amount of hardware and consumes less power, we eliminate some of the least significant bits (LSBs) of the 32-bit word from the phase accumulator output because it is relatively easy to reduce the size of the LUT and truncate the phase word at its input [1]. Unfortunately, this truncation of bits will lead to the spectral impurity to the output signal known as the phase truncation spurs and it is the biggest source of noise and spikes in the DDS system. We will provide detailed further explanation in **Section 2.3**. Many algorithms can be implemented and added into this digital design to reduce the phase truncation spurs. In this thesis project, we will design and implement a DDS with novel truncation spurs-free structure on FPGA to eliminate the truncation spurs.

#### **Quantization Noise Spurs:**

The bit width of a digital to analog converter (DAC) is always limited. Generally, the bit width of the DAC is even narrower than that of the LUT [1]. In this project, we truncate the output of the LUT even further and then give it to the DAC. The discrete amplitude values of the sine signal are quantized and stored in the LUT. The DAC will accept signed binary number with a certain precision. To achieve this, the input bits are further rounded. This quantization will generate spurs at the output frequency spectrum of the DDS.

#### **Quantization Nonlinearity Spurs:**

Due to the DAC's inherent design and non-ideal transfer function behavior, it is impossible to design a perfect DAC. Every input will have few errors associated with it, so we cannot get an ideal output. These errors, caused by nonlinear behavior of the DAC, lead to the quantization nonlinearity spurs. This type of spur can further exacerbate the truncation and quantization spurs noise spurs and is very hard to evaluate [11]. The spurs caused by the nonlinear behavior of DAC can only be reduced by increasing the precision of the DAC; however, the elimination will improve the quality of output signal significantly [3].

## 2.3 Theoretical Analysis of DDS with a Novel Truncation Spurs-Free Structure

In the previous sections, we mentioned that the truncation spurs caused by truncating the lower order bits of PA output are the primary signal integrity issue of DDS system, which limits the usage of DDS in many high-demand applications. In this section, we will introduce a truncation spurs-free method to compress the LUT size without phase truncation and a significant change of hardware usage [3].

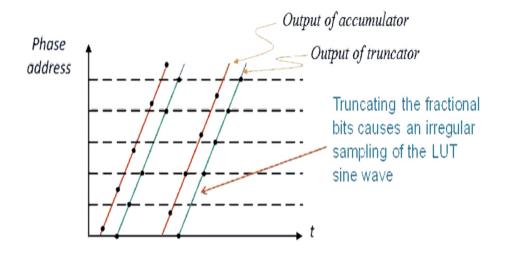

First of all, we need to understand exactly what happens behind the phase truncation that leads to the truncation spurs. In Figure 2.6, the red line represents the output of the PA; the green line represents the output of the truncator; the y-axis represents the phase address in LUT and the x-axis represents the time. The input of the LUT is actually the output of the truncator, which serves as the phase address. In the truncating process, the irregular sampling of the LUT sine wave may occur as the red arrow pointed out in Figure 2.6.

Figure 2.6: Effects on Phase Truncation

In Figure 2.5, N is the bit-width of PA input and P is the bit-width of the LUT input. We know that if N = P, then there is no phase truncation. The truncation spurs existed because N-P bits are discarded. We call these N-P bits fractional bits. As we mentioned in Section 2.1, there is a fact that the bit-width of DAC input is always limited, generally much smaller than that of PA. Thus, we will have to perform truncation on the LUT output before feeding it to DAC anyway.

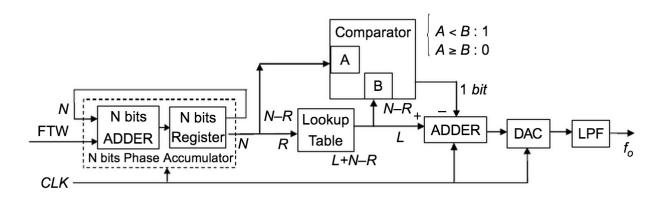

L is the bit-width of DAC input (L<<N); thus there are only  $2^{L}$  possible data values at the DAC input. Consequently, there are only  $2^{L}$  corresponding phase points referred to as the key phase points stored in LUT. These key phase points will divide one complete cycle of sine wave into  $2^{L}$ -1 key spans. If we can find which key span corresponds to which PA outputs, an accurate amplitude value stored in LUT can be determined and sent to the DAC. In this way, we can eliminate the truncation spurs. Now, the question is how can we actually determine which key span corresponds to which PA outputs. To solve this problem, we come up with a truncation spurs-free structure of DDS by introducing a comparator and an adder to the traditional structure of DDS. The truncation spurs-free structure of DDS is shown in Figure 2.7.

Figure 2.7: Truncation Spurs-Free Structure of DDS

As we mentioned above, there are 2<sup>L</sup> key phase points stored in the LUT. The comparator will compare the outputs of PA to each key phase point and generate an accurate amplitude value in one clock cycle. The main difference is that the lower (N-R) bits from output of PA are not simply discarded. Instead, they will be compared with the lower (N-R) bits of the key phase points stored in the LUT. If the lower (N-R) bits of PA output correspond to a larger value, then the amplitude value will be sent to DAC directly. Otherwise, the amplitude value is sent after subtracting 1. The output of LUT is adjusted by an adder. The irregular sampling of the sine wave will not happen again as we shown in Figure 2.6.

The size of the new LUT would be  $(2^R \times (L+N-R))$  instead of  $2^R \times L$ . We can see that the size of ROM increases linearly instead of exponentially.

# **Chapter 3. INTRODUCTION TO VERILOG**

Verilog is a hardware description language (HDL) standardized as IEEE 1364-1995. It can be used to model digital systems at algorithm level, gate level and transistor level. It is most commonly used in the design and verification of digital circuits at the register-transistor level (RTL) of abstraction. It is also used in the verification of analog circuits and mixed-signal circuits.

Verilog is very simple, straightforward and efficient. Since Verilog is not only a machinereadable language, but also a human readable language, it can support hardware design verification, synthesis, and testing. Nowadays, Verilog has become the top choice in digital systems design and the foundations for synthesis, verification, and layout technology.

Verilog includes plenty of built-in primitives, including logic gates, user-defined primitives, transistors and line logic. It also has the function to check the timing related problems between device pins. Generally speaking, Verilog has two data types to support its mixed abstraction levels. These two types are net and variable. For continuous assignment, variable and net are able to assign the data to net continuously. Verilog provides a basic structural modeling method. For procedural assignment, the calculation results of net and variable can be stored in variable. Verilog provides a behavioral modeling method.

A project developed in Verilog consists of several modules. Each module will include an I/O and a function description. The function description of a module can be structural level, behavioral level or mixed level. Then we connect these modules together with nets. A complete Verilog design module includes four main parts: port definition, I/O statement, signal type statement, and function description.

Compared with another common hardware description language, VHDL (very high speed integrated circuit HDL), Verilog is a weakly typed HDL, is easier to learn and more concise with efficient notations. The syntax is more C-like. On the other hand, VHDL as a strong typed HDL is more verbose than Verilog. Consequently, designs in VHDL are considered self-documenting. Engineers working with VHDL need to do extra coding; however, they often catch errors missed by Verilog. Verilog is good at hardware modeling but lacks higher level constructs, while VHDL has many programming constructs but lacks the low level modeling capabilities. Although Verilog is more popular in industry today, VHDL is still being used in some top companies like National Instruments due to its features. In this thesis design, we will choose Verilog as the hardware design language.

## **3.1 Resources**

- From my own learning experience, I would say that the "World of ASIC" website

(www.asic-world.com) is one of the best resources to learn digital design in Verilog

It provides detailed tutorials, design examples, and suggestions on tools and

reference books for Verilog beginner. It also provides instructions for other HDLs as

well as a scripting language used in digital design and verification such as VHDL,

SystemVerilog, SystemC, and Perl.

- 2. Besides the references books recommended on the "World of ASIC" website, two junior-level undergraduate courses at UIUC are good resources on learning digital design, especially the skills that you will use in this tutorial [13],[14]. One is ECE 385 Digital Systems Laboratory, which gives you hands-on experiences on designing complex digital systems from scratch. You will learn how to implement circuits on a breadboard, design digital systems in HDL and synthesize your circuits on an FPGA for testing and verification. Another is CS 233 Computer Architecture, which teaches fundamentals on computer architecture in a practical approach by providing excellent machine problems. You will need to use Verilog and C++ to finish these assignments.

## **3.2 Verilog Design Examples**

Some design examples that will be necessary to use when designing the DDS are given below: **Note:** These are not actual codes for this project. For major modules, please check **Appendix B**.

First of all, we will need to define a module in Verilog, which includes defining a module name, ports as well as vector ports and ports directions. The design example is shown in Figure 3.1.

```

module dds(

1

2

clk,

reset,

3

FCW,

4

5

dataout);

6

input clk;

7

input reset;

8

input [31:0] FCW;

9

output data2dac;

10

11

12

//Add entire design and instantiations.

13

endmodule

14

```

Hardware has two kinds of drivers (data type which can drive a load). The first one is called reg in Verilog while the other is called wire. The data type example is shown in Figure 3.2.

```

reg register_name; //a single bit register

wire wire_name; //a single wire

reg [31:0] register_name; //a 32-bit register

wire [31:0] wire_name; //a 32-bit wide bus

```

Figure 3.2: Example for Data Type Assignment

For the operators, they are almost the same thing in the other programming languages such as C programming language. Now, we will introduce some useful control statements and variable assignments by providing design examples for some required sub-modules in DDS design.

#### **Register:**

```

module register (

1

2

in,

3

clk,

4

reset,

5

out

);

6

7

input in, clk, reset;

8

9

output out;

10

reg out; //Internal variables

11

12

always @ (posedge clk)

13

if (~reset) begin

14

out <= 1'b0;

15

end

16

17

else begin

out <= in;

18

end

19

20

endmodule

21

```

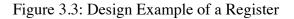

In the Figure 3.3, the design example of the register includes an if-else statement, which is to check a condition to decide whether or not to execute a portion of code. If the condition is satisfied, the code is executed. If not, it runs the other portion of code. In the above example, it checks if reset is 1. If this condition is satisfied, then it will output 0; if not, it will output the input.

## **Counter:**

```

module counter (

1

2

clk,

3

reset,

enable,

4

5

count

);

6

7

input clk, reset, enable;

8

output [3:0] count;

9

10

reg [3:0] count;

11

12

always @ (posedge clk or posedge reset)

13

if (reset) begin

14

count <= 0;</pre>

15

end

16

else begin

17

while (enable) begin

18

count <= count + 1;</pre>

19

end

20

21

end

22

23

endmodule

```

Figure 3.4: Design Example of a Counter

In the Figure 3.4, the design example of the counter includes a while statement, which executes the code within it repeatedly if the condition returns true. In the above example, the count keeps increment by 1 if the enable is checked to be true.

n-bit Full Adder:

```

1

module n_adder (

2

in a,

in_b,

3

cin,

4

5

cout,

6

sum

7

);

8

9

parameter size = n;

10

input [size-1:0] in_a;

11

input [size-1:0] in_b;

12

input cin;

13

output [size-1:0] sum;

14

output cout;

15

16

assign {cout,sum} = in_a + in_b + cin;

17

18

endmodule

19

```

Figure 3.5: Design example of n-bit full adder

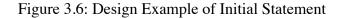

In digital design, there are two types of elements, combinational and sequential. In Verilog, there are two approaches to model combinational elements, one is using an "assign" statement; the other one is using an "always" statement. However, there is only one way to model sequential elements, which is using "always" statement. In the Figure 3.5, we use "assign" statement to output cout and sum because it is a combinational logic. Besides "assign" and "always", there is a third statement called initial statement, which is only used in designing test benches in Verilog. It is executed at the beginning of simulation. An example is shown in Figure 3.6

```

initial begin

clk = 0;

enable = 1;

FCW = 1048576; // 2^20 = 1048576

end

```

**Comparator:**

```

module comparator (

1

2

a,

3

b,

G,

4

5

Ε,

6

L

7

);

input [7:0] a, b;

8

output G, E, L;

9

10

wire G, E, L;

11

12

assign G = (a>b);

13

assign E = (a==b);

14

assign L = (a<b);</pre>

15

16

endmodule

17

```

```

module comparator (

19

20

a,

21

b,

22

G,

23

Ε,

24

L

25

);

26

input a0,a1,b0,b1;

27

output G,E,L;

28

29

reg G,E,L;

30

31

always@(a0 or a1 or b0 or b1)

32

begin

33

G <= {a1,a0}>{b1,b0};

34

E <= {a1,a0}=={b1,b0};</pre>

35

L <= {a1,a0}<{b1,b0};

36

37

end

38

endmodule

39

```

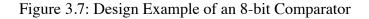

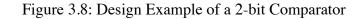

In Figure 3.7 and Figure 3.8, we use two different approaches to design the comparator. One uses an "assign" statement; the other one uses an "always" statement. In this thesis work, we will use an "assign" statement to design the comparator because it is relatively simpler.

#### **Finite State Machine (FSM):**

```

module FSM (

1

2

clock,

reset,

3

4

sig_1,

5

sig_2,

6

a,

7

b

8

);

9

input clock, reset;

10

output a, b;

11

12

13

wire clock, reset, sig_1, sig_2;

reg a, b;

14

15

parameter size = 2;

16

parameter IDLE = 2'b00, A = 2'b01, B = 2'b10;

17

18

19

reg [size-1:0] state;

reg [size-1:0] next_state;

20

//combinational logic

21

always @ (clock or sig_1 or sig_2)

22

begin : FSM_COMBO

23

next_state = 2'b00;

24

case(state)

25

IDLE : if (sig_1 == 1'b1) begin

26

next_state = A;

27

end else if (sig_2 == 1'b1) begin

28

next_state = B;

29

end else begin

30

31

next_state = IDLE;

end

32

33

A : if (sig_2 == 1'b1) begin

34

next_state = B;

35

end else begin

36

next_state = A;

37

38

end

39

next_state = IDLE;

B:

40

41

default : next_state = IDLE;

42

endcase

43

end

44

```

Figure 3.9: Design Example of the FSM

```

//sequential logic

45

always @ (posedge clock)

46

begin : FSM_SEQ

47

if (reset == 1'b1) begin

48

state <= IDLE;</pre>

49

end else begin

50

state <= next_state;</pre>

51

52

end

end

53

//output logic

54

always @ (posedge clock)

55

begin : FSM_OUTPUT

56

if (reset == 1'b1) begin

57

a <= 1'b0;

58

b <= 1'b0;

59

end else begin

60

case(state)

61

IDLE : begin

62

a <= 1'b0;

63

b <= 1'b0;

64

end

65

66

A : begin

67

a <= 1'b0;

68

b <= 1'b1;

69

70

end

71

B : begin

72

a <= 1'b1;

73

b <= 1'b1;

74

end

75

default : begin

77

a <= 1'b0;

78

b <= 1'b0;

79

80

end

endcase

81

end

82

end

83

endmodule

84

```

Figure 3.9: Continued

In the Figure 3.9, the design example of the FSM includes the case statements, which are used when we have one variable that needs to be checked for multiple values. In the above example, we use case statement to check the state status. It is important to note that that it is better to include a default case with a return to idle every time we use case statement to make the code safe because if the Verilog machine enters to a non-covered state, it will hang there. Also, when you use the case statement, if you don't cover all the cases and you are trying to write a combinational logic, the synthesis tool will infer latch.

From all the examples and descriptions above, you may see the "always" statement several times. In the following, I will introduce this important block in Verilog design.

From the name we can imagine that the "always" statement executes always instead of executing once like the initial statement. It includes a sensitive list or a delay associated with it. There are two types of sensitive lists, one is level sensitive for combinational logic; one is edge sensitive for flip-flops. In the FSM example, "sig\_1" and "sig\_2" included in "always" in the combinational logic block are level sensitive lists. The "clock" included in "always" in the sequential logic block is an edge sensitive list. If a change happens in any of the sensitive lists, the always statement will be triggered.

We can have an "always" statement without a sensitive list in the case where we have a delay, as shown in Figure 3.10.

21 always begin

22 #1 clk = ~clk

23 end

Figure 3.10: Example of "Always" Statement Without a Sensitive List

Finally, if you look into the codes above, you will see two different types of assignment operators. One is "=", which is used in the combinational logic; the other one is "<=", which is used in the sequential logic. "=" is called blocking assignment and "<=" is called non-blocking assignment. The blocking assignment executes codes sequentially while the non-blocking one executes codes in parallel. This is very important because misuse of these two assignments will totally disrupt the codes. Also, begin and end constructs are only necessary when multiple operations.

Hardware coding is different from software coding. Sometimes you should think like real hardware and solve issues associated with real hardware to make a good design.

# **Chapter 4. FPGA DESIGN FLOW**

## 4.1 Introduction to FPGA

FPGA is an integrated circuit designed to be configured by a customer or a designer after manufacturing. The FPGA configuration is generally specified using HDL. From a research standpoint, we will use the FPGA instead of the ASIC approach to build the DDS in this thesis, because the designs on FPGA can be easily modified and tested on board.

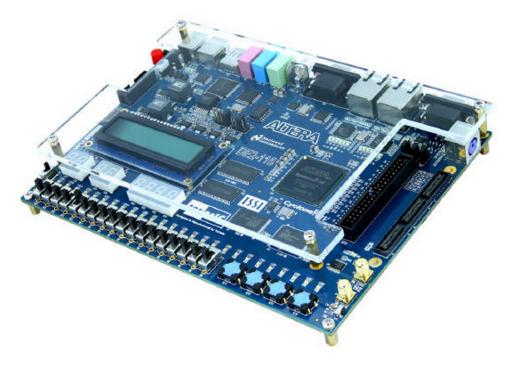

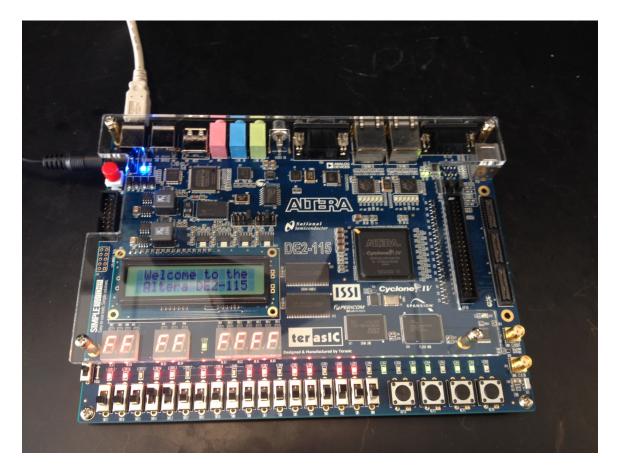

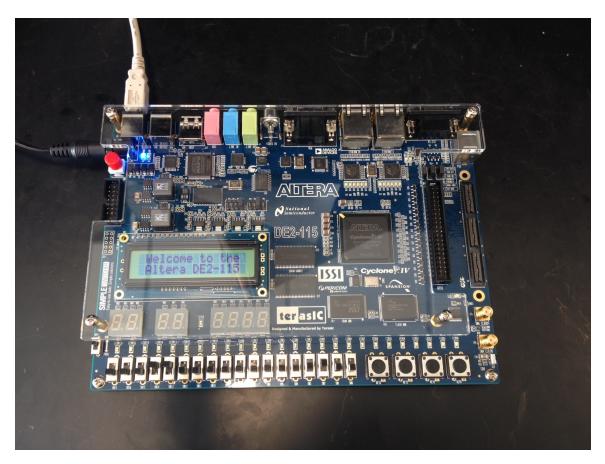

As shown in Figure 4.1, the FPGA we choose is Altera DE2-115 development and education board, which is an ideal teaching platform [15].

**DE2-115 Development and Education Board**

Figure 4.1: DE2-115 Development and Education Board

There are plenty of switches and ports, 128M on-board memory and enough hardware resources for us to use. The on board clock frequency is 50MHz.

## 4.2 Design Flow

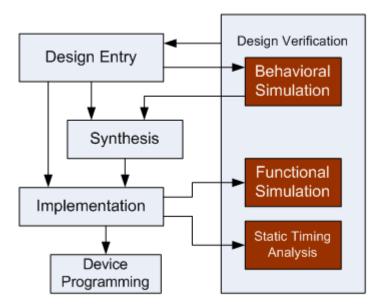

The FPGA design flow is shown as Figure 4.2 [16],[17].

Figure 4.2: FPGA Design Flow

**Note:** Design Entry includes **Functional/Device Specification** and **HDL Coding** and Implementation includes **Mapping** and **Placement and Route**.

## **Functional/Device Specification:**

On this stage, the designers need to set up the configuration (make/model/speed/class/device family) of the FPGA. After that, the designing software will conduct some preliminary setup for the particular FPGA device's intellectual properties (IPs), designs and components [4],[17],[18].

## HDL Coding:

On this stage, the designers write HDL codes to model the entire digital designs. The designers can also use a schematic approach to model the entire circuits. We will show both approaches in **Chapter 5.2**; however, since we need to implement an algorithm in this thesis, the HDL coding approach is preferred [4],[17],[18].

#### Logic Synthesis:

Synthesis is a process that converts the HDL codes to the gate-level netlist, which describes the different types of components, elements, and interconnections between the components and other details like area occupied and temperature of operation, etc. Also, synthesis will help check the syntax of the HDL codes and map the design to a particular FPGA family [4],[17],[18].

## Mapping:

In this stage, the software maps the generic logic design to the logic technology contained in the selected FPGA device [4],[17],[18].

## Placement and Route (PAR):

This stage is one of the most important steps in the entire implementation. Placement decides where the components should be placed on the FPGA while routing is responsible for the connections between different components. PAR is crucial because it is related with the timing and area constraints of the design. A bad placement will result in problematic routing, which leads to design violations [4],[19].

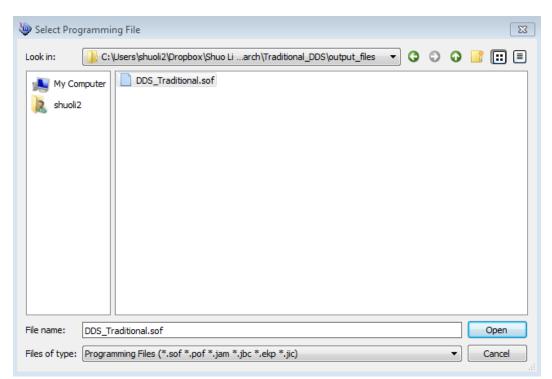

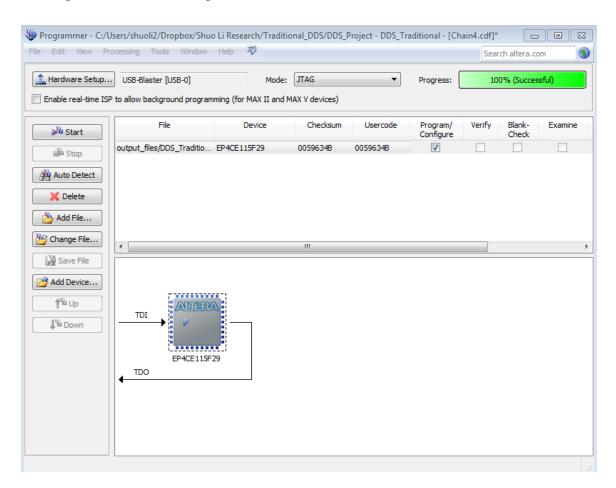

## **FPGA Configuration and Programming:**

The last step of the FPGA design flow is to program the designs on the FPGA and test the circuit. On this stage, the software converts the entire design to a "bitstream" file, which is loaded on the FPGA board. After that, the FPGA is ready to run the digital design [4],[19].

## **Design Verification:**

It is extremely important for every design to meet certain standards and satisfy certain conditions. After each design step, the designers need to check if their circuits meet various constraints such as timing, area and functional logic [19].

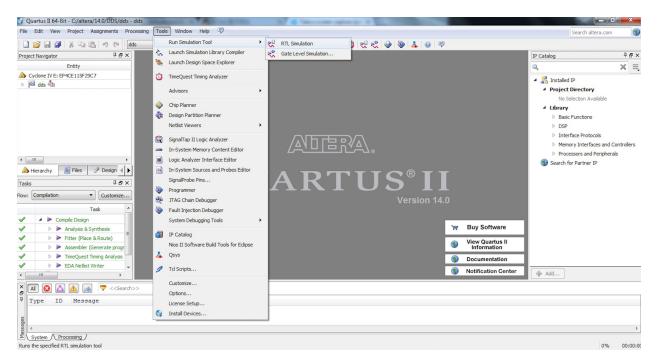

In this thesis, we will use ModelSim as the simulation tool for design verification. The descriptions of each testing stage are given below:

- 1. Behavioral Simulation: This task is to verify the functionality of the HDL codes.

- 2. **Gate-Level Simulation:** The gate-level netlist is generated after the completion of synthesis. This task is to test the timing and gate-level functionality of the design.

- 3. **Static Timing Analysis (STA):** STA comes out after the completion of PAR. The designer will analyze some important issues related with the design of the circuit such as setup and hold times, critical path and clock skews. The STA will examine every possible path in the circuit and help debugging glitches and slow paths [4].

- 4. **Post-PAR Timing Simulation:** This task provides a comprehensive timing summary of the circuit.

## Chapter 5. FPGA DESIGN TUTORIAL IN QUARTUS II

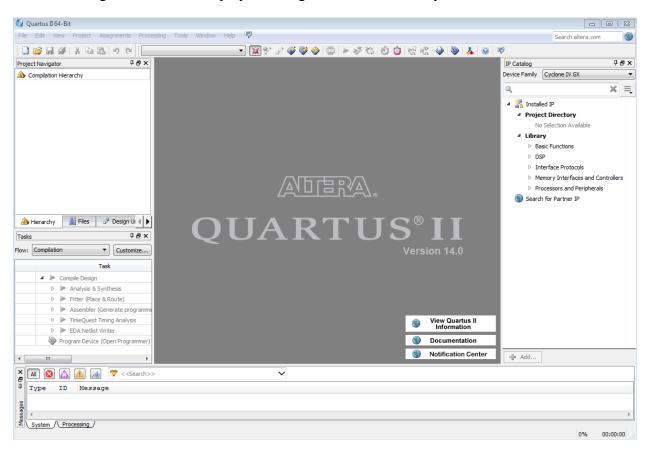

In this thesis project, we will use Quartus II Web Edition FPGA design software. It is a software tool produced by Altera for analysis and synthesis of HDL designs, which enables the developers to compile their designs, perform timing analysis, examine RTL diagrams, simulate a design's reaction to different stimuli, and configure the target device with the programmer.

First of all, we should download the software from Altera's official website, <u>http://www.altera.com/products/software/quartus-ii/web-edition/qts-we-index.html</u>. We may just select to download the Quartus II Web Edition v14.0, which is free and should be good enough for our project. The Quartus II FPGA design software is only workable on Windows XP, 7 or 8 or Linux so far. For Mac users, it is not very convenient, so they may need to install a Windows based operating system (Window7 for this project) by installing Parallels first on their Macs. There may be some other better ways to do this; however, from my own working experience, I highly recommend you just choose a workstation with Windows based OS to avoid any further problems in your design and simulation.

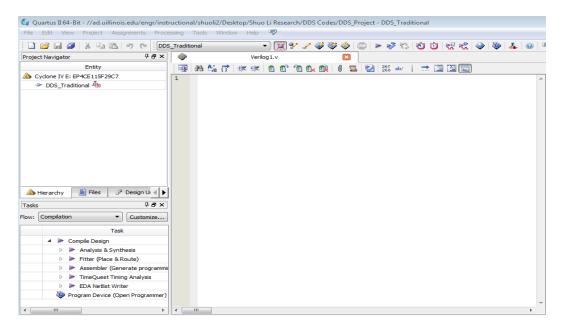

After installing your Altera Quartus II, you can open your software by clicking the shortcut icon on the desktop or Start Manu  $\Rightarrow$  All Programs  $\Rightarrow$  Altera 14.0 directory  $\Rightarrow$  Quartus II 14.0 directory  $\Rightarrow$  Quartus II 14.0. After opening Altera Quartus II software, Figure 5.1 will display.

| QUARTUS' II                                                                 | Getting Started<br>With Quartus <sup>®</sup> II Software                                                         |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Start Designing<br>Designing with Quartus II software<br>requires a project | <b>Start Learning</b> The audio/video interactive tutorial teaches you the basic features of Quartus II software |

| Create a New Project<br>(New Project Wizard)<br>Open Existing Project       | Open Interactive Tutorial                                                                                        |

|                                                                             |                                                                                                                  |

| Literature Training O                                                       | Online Demos Support                                                                                             |

Figure 5.1: Opening Display

Then the design console will display as in Figure 5.2 automatically.

Figure 5.2: Design Console

## **5.1 Project Setup**

1. To create a new project, from the **File** menu or opening display in Figure 5.1, select **New Project Wizard**. Click **Next** to go through the introduction screen if it appears. Then, the Figure 5.3 will appear. Fill in the fields in Figure 5.3 (make sure there are no spaces in any of your entries). The program will ask you if it should create the specified directory if it does not exist; choose **yes**.

| 💱 New Project Wizard                                                                                                                                     | × |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Directory, Name, Top-Level Entity [page 1 of 5]                                                                                                          |   |

| What is the working directory for this project?                                                                                                          |   |

| //ad.uillinois.edu/engr/instructional/shuoli2/Desktop/Shuo Li Research/DDS Codes                                                                         |   |

| What is the name of this project?                                                                                                                        |   |

| DDS_Project                                                                                                                                              |   |

| What is the name of the top-level design entity for this project? This name is case sensitive and must exactly match the entity name in the design file. |   |

| DDS_Traditional                                                                                                                                          |   |

| Use Existing Project Settings                                                                                                                            |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

|                                                                                                                                                          |   |

| < Back Next > Finish Cancel Help                                                                                                                         | > |

Figure 5.3: New Project Wizard

Select Next on page 2 without adding any files. On page 3, select Cyclone IV for the device family, make sure the second option under target device is selected, and choose EP4CE115F29C7 in the available devices list according to Figure 5.4. Then click Next to page 4.

| o determine the v                                                                                                                                                                                       | ersion of the Quartus                                                                        | s II soltwal                                                                                     | e in which your ta                                                        | rget device is suppor                                                                                                 |                                                                    |                           |                                                                                   |                                                                            |   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------|---|--|

| Device family                                                                                                                                                                                           |                                                                                              |                                                                                                  |                                                                           |                                                                                                                       | Show in 'Available de                                              |                           |                                                                                   |                                                                            |   |  |

| Family: Cydone IV E                                                                                                                                                                                     |                                                                                              |                                                                                                  |                                                                           |                                                                                                                       | Package:                                                           | Any                       |                                                                                   |                                                                            | • |  |

| Devices: [All -                                                                                                                                                                                         |                                                                                              |                                                                                                  |                                                                           |                                                                                                                       |                                                                    |                           |                                                                                   | <b>▼</b>                                                                   |   |  |

|                                                                                                                                                                                                         |                                                                                              |                                                                                                  |                                                                           |                                                                                                                       | Pin count:                                                         | Any                       |                                                                                   |                                                                            |   |  |

| Target device                                                                                                                                                                                           |                                                                                              |                                                                                                  |                                                                           |                                                                                                                       | Core Speed grade:                                                  | Any                       |                                                                                   |                                                                            | • |  |

| -                                                                                                                                                                                                       |                                                                                              |                                                                                                  |                                                                           |                                                                                                                       | Name filter:                                                       |                           |                                                                                   |                                                                            | - |  |

| O Auto device :                                                                                                                                                                                         | selected by the Fitter                                                                       |                                                                                                  |                                                                           |                                                                                                                       | Name filter:                                                       |                           |                                                                                   |                                                                            |   |  |

| Other: n/a                                                                                                                                                                                              |                                                                                              |                                                                                                  |                                                                           |                                                                                                                       |                                                                    |                           |                                                                                   |                                                                            |   |  |

|                                                                                                                                                                                                         | -                                                                                            |                                                                                                  |                                                                           |                                                                                                                       |                                                                    |                           |                                                                                   |                                                                            |   |  |

| Name                                                                                                                                                                                                    | Core Voltage                                                                                 | LEs                                                                                              | User I/Os                                                                 | Memory Bits                                                                                                           | Embedded n                                                         | nultiplier 9-bit elements | PLL                                                                               | Global Clocks                                                              |   |  |

|                                                                                                                                                                                                         | Core Voltage<br>1.0V                                                                         | LEs<br>114480                                                                                    | User I/Os<br>529                                                          | Memory Bits<br>3981312                                                                                                | Embedded n<br>532                                                  | nultiplier 9-bit elements | <b>PLL</b> 4                                                                      | Global Clocks                                                              | 0 |  |

| EP4CE115F29I8L                                                                                                                                                                                          |                                                                                              |                                                                                                  |                                                                           |                                                                                                                       |                                                                    | nultiplier 9-bit elements |                                                                                   |                                                                            | 0 |  |

| P4CE115F29I8L<br>P4CE115F29I7                                                                                                                                                                           | 1.0V<br>1.2V                                                                                 | 114480                                                                                           | 529                                                                       | 3981312                                                                                                               | 532                                                                | nultiplier 9-bit elements | 4                                                                                 | 20                                                                         | 0 |  |

| EP4CE115F29I8L<br>EP4CE115F29I7<br>EP4CE115F29C9L                                                                                                                                                       | 1.0V<br>1.2V<br>1.0V                                                                         | 114480<br>114480                                                                                 | 529<br>529                                                                | 3981312<br>3981312                                                                                                    | 532<br>532                                                         | nultiplier 9-bit elements | 4                                                                                 | 20<br>20                                                                   |   |  |

| EP4CE115F29I8L<br>EP4CE115F29I7<br>EP4CE115F29C9L<br>EP4CE115F29C8L                                                                                                                                     | 1.0V<br>1.2V<br>1.0V                                                                         | 114480<br>114480<br>114480                                                                       | 529<br>529<br>529                                                         | 3981312<br>3981312<br>3981312                                                                                         | 532<br>532<br>532                                                  | nultiplier 9-bit elements | 4<br>4<br>4                                                                       | 20<br>20<br>20                                                             |   |  |

| EP4CE115F29I8L<br>EP4CE115F29I7<br>EP4CE115F29C9L<br>EP4CE115F29C8L<br>EP4CE115F29C8                                                                                                                    | 1.0V<br>1.2V<br>1.0V<br>1.0V<br>1.2V                                                         | 114480<br>114480<br>114480<br>114480                                                             | 529<br>529<br>529<br>529<br>529                                           | 3981312<br>3981312<br>3981312<br>3981312<br>3981312                                                                   | 532<br>532<br>532<br>532<br>532                                    | nultiplier 9-bit elements | 4<br>4<br>4<br>4<br>4                                                             | 20<br>20<br>20<br>20<br>20                                                 |   |  |

| EP4CE115F29I8L<br>EP4CE115F29I7<br>EP4CE115F29C9L<br>EP4CE115F29C8L<br>EP4CE115F29C8<br>EP4CE115F29C7                                                                                                   | 1.0V<br>1.2V<br>1.0V<br>1.0V<br>1.2V<br>1.2V                                                 | 114480<br>114480<br>114480<br>114480<br>114480<br>114480                                         | 529<br>529<br>529<br>529<br>529<br>529<br>529                             | 3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312                                                        | 532<br>532<br>532<br>532<br>532<br>532                             | nultiplier 9-bit elements | 4<br>4<br>4<br>4<br>4<br>4                                                        | 20<br>20<br>20<br>20<br>20<br>20<br>20<br>20                               |   |  |

| P4CE 115F 29I8L<br>P4CE 115F 29I7<br>P4CE 115F 29C9L<br>P4CE 115F 29C8L<br>P4CE 115F 29C8<br>P4CE 115F 29C8<br>P4CE 115F 29C7<br>P4CE 115F 23I8L                                                        | 1.0V<br>1.2V<br>1.0V<br>1.0V<br>1.2V<br>1.2V                                                 | 114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480                               | 529<br>529<br>529<br>529<br>529<br>529<br>529<br>529                      | 3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312                                             | 532<br>532<br>532<br>532<br>532<br>532<br>532<br>532               | nultiplier 9-bit elements | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4                                              | 20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20                         |   |  |

| P4CE 115F 2918L<br>P4CE 115F 2917<br>P4CE 115F 29C9L<br>P4CE 115F 29C9L<br>P4CE 115F 29C8L<br>P4CE 115F 29C8<br>P4CE 115F 29C7<br>P4CE 115F 2318L<br>P4CE 115F 2317                                     | 1.0V<br>1.2V<br>1.0V<br>1.0V<br>1.2V<br>1.2V<br>1.2V<br>1.0V<br>1.2V                         | 114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480                     | 529<br>529<br>529<br>529<br>529<br>529<br>529<br>529<br>281               | 3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312                                  | 532<br>532<br>532<br>532<br>532<br>532<br>532<br>532<br>532        | nultiplier 9-bit elements | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4                                    | 20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20                         |   |  |

| P4CE115F2918L<br>P4CE115F2917<br>P4CE115F29C9L<br>P4CE115F29C8L<br>P4CE115F29C8<br>P4CE115F29C8<br>P4CE115F29C7<br>P4CE115F2318L<br>P4CE115F2317<br>P4CE115F2317                                        | 1.0V<br>1.2V<br>1.0V<br>1.0V<br>1.2V<br>1.2V<br>1.2V<br>1.0V<br>1.2V<br>1.0V                 | 114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480                     | 529<br>529<br>529<br>529<br>529<br>529<br>529<br>529<br>281<br>281        | 3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312                       | 532<br>532<br>532<br>532<br>532<br>532<br>532<br>532<br>532<br>532 | nultiplier 9-bit elements | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4                          | 20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20             |   |  |

| P4CE 115F 2918L<br>P4CE 115F 2917<br>P4CE 115F 2917<br>P4CE 115F 29C8L<br>P4CE 115F 29C8L<br>P4CE 115F 29C8<br>P4CE 115F 29C7<br>P4CE 115F 2317<br>P4CE 115F 2317<br>P4CE 115F 23C9L<br>P4CE 115F 23C8L | 1.0V<br>1.2V<br>1.0V<br>1.0V<br>1.2V<br>1.2V<br>1.2V<br>1.0V<br>1.2V<br>1.0V                 | 114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480           | 529<br>529<br>529<br>529<br>529<br>529<br>529<br>281<br>281<br>281        | 3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312            | 532<br>532<br>532<br>532<br>532<br>532<br>532<br>532<br>532<br>532 | nultiplier 9-bit elements | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4           | 20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20             |   |  |

| P4CE 115F 2918L<br>P4CE 115F 2917<br>P4CE 115F 2917<br>P4CE 115F 29C8L<br>P4CE 115F 29C8L<br>P4CE 115F 29C8<br>P4CE 115F 29C7<br>P4CE 115F 2317<br>P4CE 115F 2317<br>P4CE 115F 23C9L<br>P4CE 115F 23C8L | 1.0V<br>1.2V<br>1.0V<br>1.0V<br>1.2V<br>1.2V<br>1.2V<br>1.2V<br>1.2V<br>1.0V<br>1.0V<br>1.0V | 114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480<br>114480 | 529<br>529<br>529<br>529<br>529<br>529<br>529<br>281<br>281<br>281<br>281 | 3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312<br>3981312 | 532<br>532<br>532<br>532<br>532<br>532<br>532<br>532<br>532<br>532 | nultiplier 9-bit elements | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 | 20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20 |   |  |

Figure 5.4: Device Specifications

3. Select **ModelSim-Altera** as the simulation tool name, and **Verilog HDL** as the simulation format, then click **Next**. See Figure 5.5.

| New Project Wizard       |                  |               |         |                                                                 |

|--------------------------|------------------|---------------|---------|-----------------------------------------------------------------|

| EDA Tool Setti           | ngs [page 4 of   | 5]            |         |                                                                 |

| Specify the other EDA to |                  | -             | vour pr | piect.                                                          |

| EDA tools:               | <b>-</b>         |               | /       |                                                                 |

| Tool Type                | Tool Name        | Format(s)     |         | Run Tool Automatically                                          |

| Design Entry/Synthesis   | <none></none>    | <none></none> | -       | Run this tool automatically to synthesize the current design    |

| Simulation               | ModelSim-Altera  | ▼ Verilog HDL | -       | Run gate-level simulation automatically after compilation       |

| Formal Verification      | <none></none>    | •             |         |                                                                 |

| Board-Level              | Timing           | <none></none> | •       |                                                                 |

|                          | Symbol           | <none></none> | -       |                                                                 |

|                          | Signal Integrity | <none></none> | •       |                                                                 |

|                          | Boundary Scan    | <none></none> | -       |                                                                 |

|                          |                  |               |         |                                                                 |

|                          |                  |               |         |                                                                 |

|                          |                  |               |         | < <u>Back</u> <u>N</u> ext > <u>E</u> inish Cancel <u>H</u> elp |

Figure 5.5: EDA Tool Settings

4. Click **Finish** on page 5. Now you should be able to have an entry for the project in the Project Navigator window. It should display as in Figure 5.6.

| Project Navigator                         | ₽₽×          |  |  |  |  |  |

|-------------------------------------------|--------------|--|--|--|--|--|

| Entity                                    |              |  |  |  |  |  |

| Cyclone IV E: EP4CE115F29C7               |              |  |  |  |  |  |

| DDS_Traditional <sup>4</sup> <sup>™</sup> |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

|                                           |              |  |  |  |  |  |

| 🚵 Hierarchy 📄 Files 🗗 De                  | esign Ui 🚽 🕨 |  |  |  |  |  |

Figure 5.6: Project Navigator

# 5.2 HDL Coding

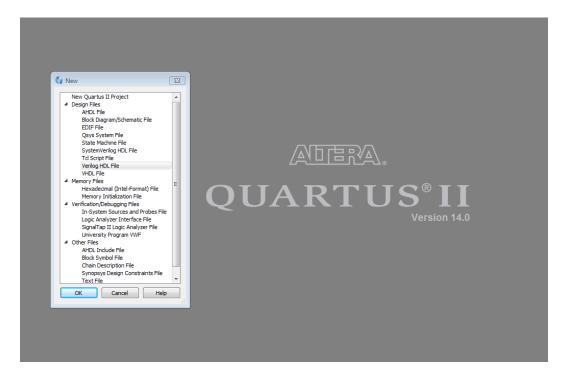

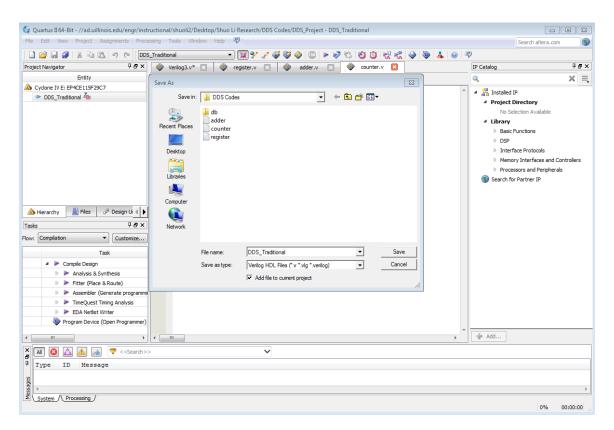

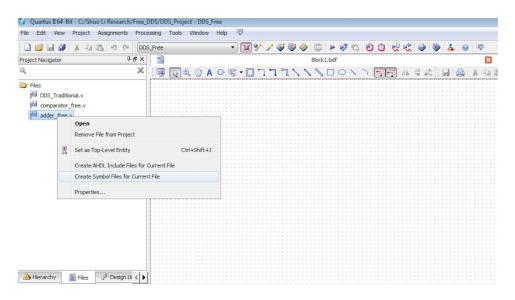

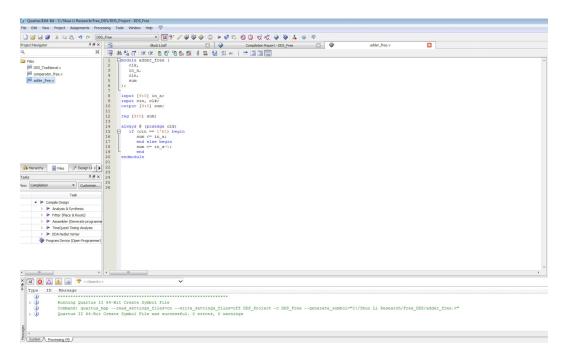

To create the top-level module (DDS\_Traditional.v), go to File → New or click on the icon in the top left corner. A panel will display as in Figure 5.7. Under the Design Files, select Verilog HDL File. Click OK. Now we have a blank Verilog file shown as in Figure 5.8.

Figure 5.7: New Panel

Figure 5.8: Blank Verilog File

2. After generating several blank Verilog files, we will need to name them, include them into the project and set up a top level file, which has to be the **DDS\_Traditional.v**. As shown in Figure 5.9, we name one of the blank files DDS\_Traditional.v, then click **Save**. Remember to check the **Add file to current project**.

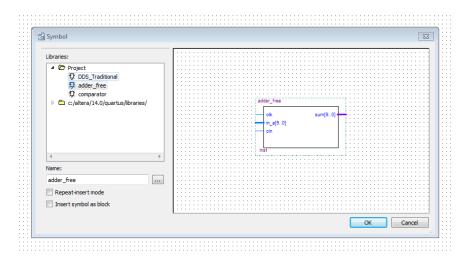

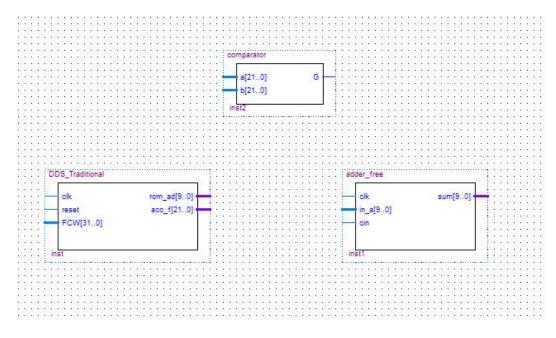

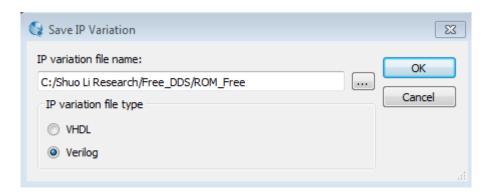

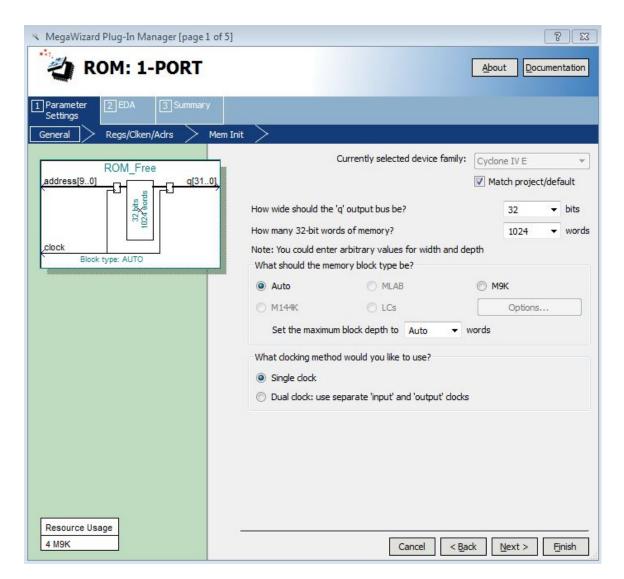

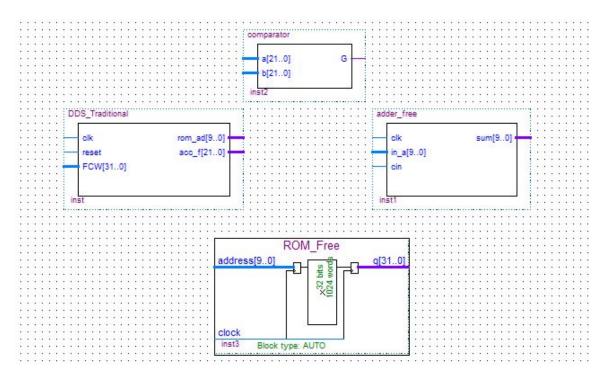

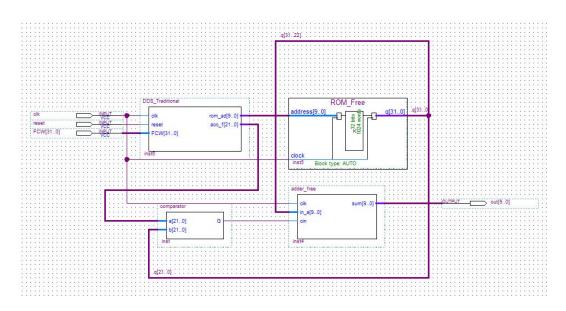

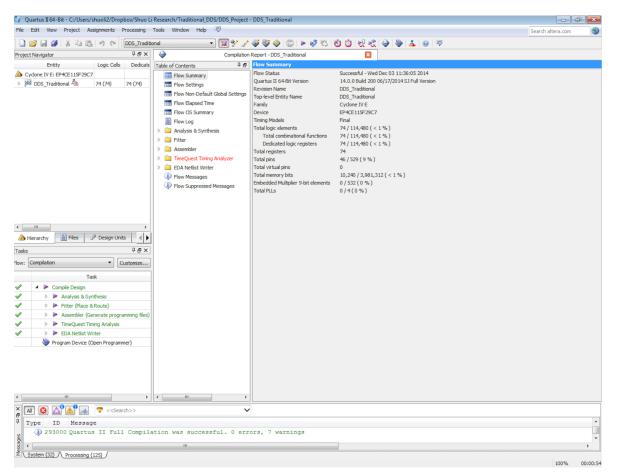

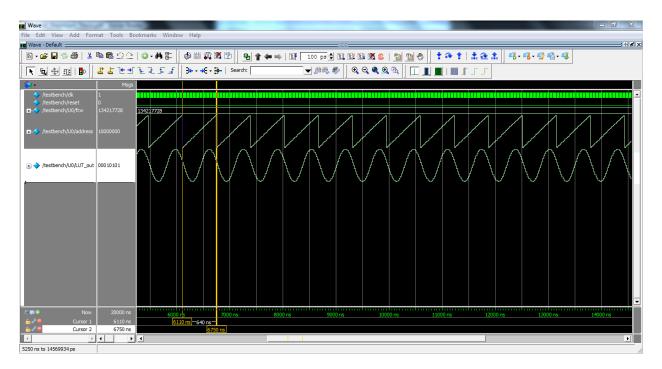

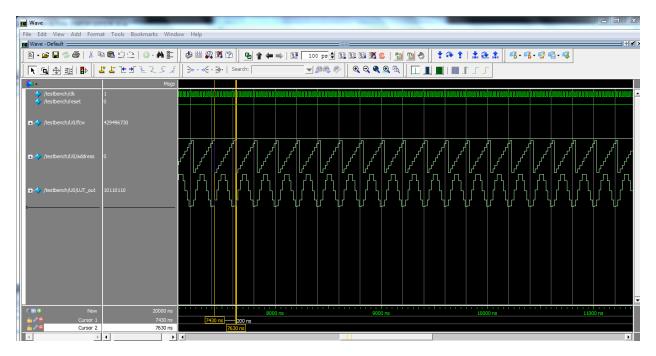

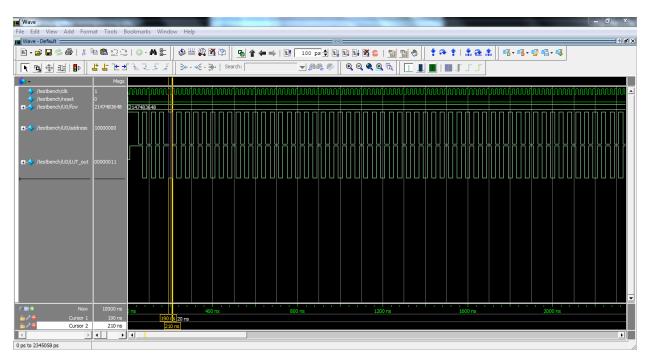

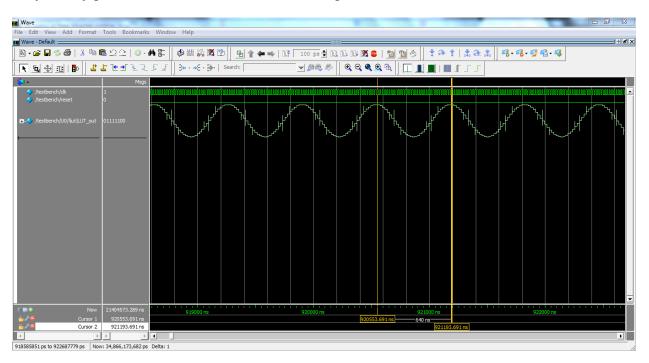

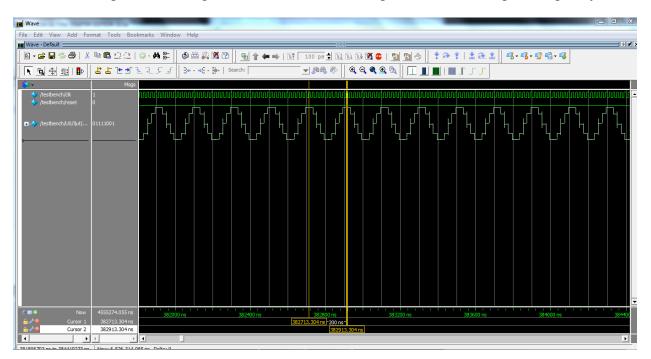

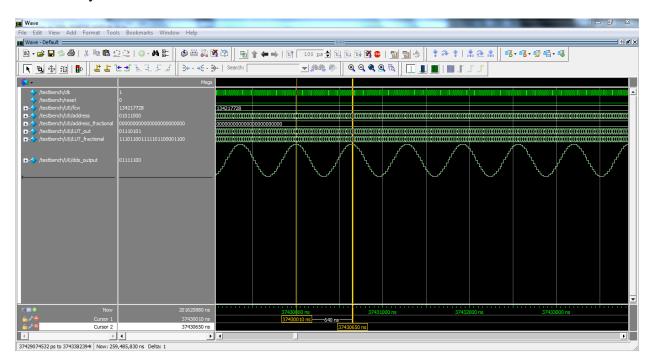

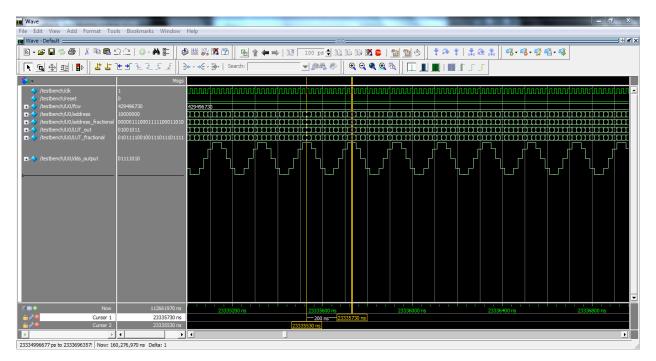

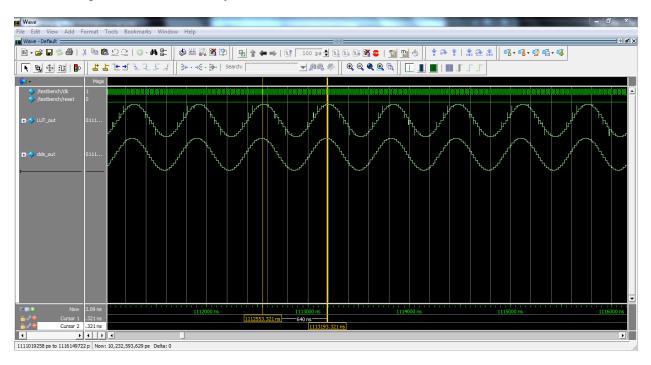

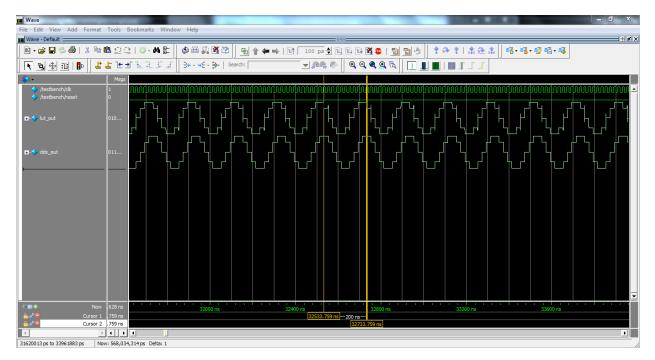

Figure 5.9: Naming the Blank Verilog File