## Next Generation Data Processing for Future X-ray Observatories

Dissertation

der Mathematisch-Naturwissenschaftlichen Fakultät der Eberhard Karls Universität Tübingen zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften (Dr. rer. nat.)

vorgelegt von

#### Henning Wende

aus Hann. Münden

Tübingen 2015

Gedruckt mit Genehmigung der Mathematisch-Naturwissenschaftlichen Fakultät der Eberhard Karls Universität Tübingen.

| Tag der mündlichen Qualifikation: | 23.07.2015                    |

|-----------------------------------|-------------------------------|

| Dekan:                            | Prof. Dr. Wolfgang Rosenstiel |

| 1. Berichterstatter:              | Prof. Dott. Andrea Santangelo |

| 2. Berichterstatter:              | Prof. Dr. Klaus Werner        |

"Design is an iterative process. The necessary number of iterations is one more than the number you have done. This is true at any point in time."

Akin's Law of Spacecraft Design #3

## Abstract

During the last two decades space-based X-ray observatories have been used to study the most energetic sources in the Universe and to investigate the physics and characteristics of matter under extreme conditions. Detectors sensitive to X-ray photons have been significantly improved, their area has increased, their energy resolution has reached the Fano limit (120 eV @ 6 keV), and the detection time during which the detector is inactive (dead-time) has been reduced to nanoseconds.

These technological advancements have enabled X-ray observations with very high time resolution. Time resolved spectra in the range from 1 keV to 80 keV with good energy resolution open up a new field of X-ray astronomy since several types of X-ray sources, e.g. rotating neutron stars and black holes, show flux and spectral variations in time in the order of milliseconds and below. These variations can only be observed if an instrument is sensitive enough to detect single photons and if the read-out is fast enough to determine the energy of the photon and thus produce an event before the next photon arrives.

Concepts of instruments capable of producing spectra or single events with high time resolution are the High Time Resolution Spectrometer (HTRS) aboard the International X-Ray Observatory (IXO) and the Large Area Detector (LAD) aboard the Large Observatory for X-ray Timing (LOFT). While the detectors of these instruments can detect every single photon coming from an X-ray source, the subsequent data processing electronics have to deal with unprecedented bandwidths. Depending on the brightness of the source and the available telemetry bandwidth from the satellite to the ground station the need for data compression and even reduction arises.

In this thesis I present the work that was done in the context of the development of two instruments for X-ray observatories at the Institute for Astronomy and Astrophysics in Tübingen (IAAT). From 2010 to 2014 our institute participated in the development of the Data Processing Unit (DPU) for the HTRS aboard the International X-Ray Observatory and in the development of several components for the data handling chain of the LAD instrument aboard the Large Observatory for X-ray Timing, in particular the Panel-Back-End-Electronics (PBEE).

#### HTRS DPU

The first project was the definition and development of the HTRS DPU prototype. The configurable spectrum generation and detector handling that is part of the DPU was designed in VHDL and implemented into a Spartan 3 FPGA. To enable the use of the bzip2 compression algorithm in the DPU the VHDL model of the LEON3 microcontroller was integrated into the same FPGA and a custom designed system software was written in C using the RTEMS framework. The functionality of the DPU has been demonstrated and the required performance and efficiency of the bzip2 compression has been validated.

#### LAD PBEE

The second project was the design and development of the LAD PBEE prototype and the interface components used for communication between the Module-Back-End-Electronics (MBEE) and the PBEE. The custom interface and the data handling procedures of the PBEE are implemented in VHDL using a special VHDL design technique, the Two Process Method. For the PBEE prototype a PCB was designed, built, and equipped with a Virtex 4 and a Spartan 3 FPGA. The interface was implemented in the MBEE and the PBEE, and a communication test-bench with both prototypes additional MBEE simulators demonstrated the full functionality of the design as well as the required interface performance.

#### Structure of the Thesis

The first part of this thesis introduces X-ray astronomy (Chapter 1), explains the impact of the programmatic mission context on hardware design (Chapter 2), and gives an overview of the processes by which a proposed mission is selected for implementation.

The second part starting with Chapter 3 gives an overview of the basic hardware components that are used for data handling and processing, and illustrates the choices made for the HTRS and LAD equipment. Details on the software and programming techniques used during the development of the prototypes are given in Chapter 4.

The third part finally presents the two missions, IXO in Chapter 5, and LOFT in Chapter 6. The instruments are introduced with the main focus on the Data Processing Unit (IXO) and the Panel-Back-End-Electronics (LOFT), their functionality, and the results of the prototype validation. A summary of the work is given in Chapter 7 including an outlook on possible studies that might be conducted with the current or future prototypes.

Additionally the appendix of this work contains detailed step-by-step instructions on how to implement the LEON3 microcontroller design in an FPGA development board. This process was not very well documented before and it might be useful for other studies with the LEON3 to refer to this comprehensive guide on how to setup and configure a working system.

## Deutsche Zusammenfassung

In den letzten zwei Jahrzehnten wurden eine Reihe von Röntgensatelliten entwickelt, gebaut und schließlich genutzt, um hochenergetische Röntgenquellen zu untersuchen, sowie die Eigenschaften und das Verhalten von Materie unter extremen Bedingungen zu studieren. Besondere Fortschritte wurden dabei auf dem Gebiet der Detektortechnik gemacht. Die für Röntgenstrahlen sensitive Fläche wurde vergrößert, die Energieauflösung der Detektoren konnte bis an das Fano-Limit herangebracht werden und die Zeit, die für eine Detektion notwendig ist und während der ein Teil des Detektors vorübergehen inaktiv bleibt (Totzeit), wurde auf wenige Nanosekunden reduziert.

Die technologische Entwicklung der Detektoren und der Ausleseelektronik ermöglicht heute Beobachtungen mit hoher Zeitauflösung und guter Energieauflösung von Röntgenstrahlen im Bereich von 1 keV bis 80 keV. So wurde ein neues Feld der Röntgenastronomie erschlossen, denn viele in diesem Licht sichtbare Quellen zeigen eine Variabilität im zeitlichen Verhalten ihrer Leuchtkraft und der spektralen Zusammensetzung, die im Bereich von Millisekunden und darunter liegt. Zu diesen Quellen gehören zum Beispiel rotierende Neutronensterne sowie rotierende Schwarze Löcher. Allerdings können die hier vorhandenen zeitlichen Variationen nur dann aufgelöst werden, wenn der Detektor über eine entsprechend kurze Totzeit verfügt und die auslesende und verarbeitende Elektronik die Detektordaten auch mit ausreichend hohem Durchsatz verarbeiten kann.

Im Besonderen sind zwei geplante Instrumente in der Lage, die benötigte Zeitauflösung bei guter Energieauflösung zu liefern. Das High Time Resolution Spectrometer (HTRS) des International X-ray Observatory (IXO) und der Large Area Detector (LAD) auf dem Röntgensatelliten Large Observatory for X-ray Timing (LOFT).

In der vorliegenden Arbeit stelle ich zwei funktionsfähige Prototypen vor, an deren Entwicklung das Institut für Astronomie und Astrophysik Tübingen (IAAT) in den Jahren von 2010 bis 2014 beteiligt war. Im Rahmen meiner Tätigkeit wurde die Data Procecssing Unit (DPU) des HTRS Instruments als Teil des IXO Observatoriums entwickelt und die Panel-Back-End-Electronic (PBEE) des Large Area Detectors der LOFT Mission gebaut. Beide Prototypen wurden sowohl in Simulationen wie auch in einem Laboraufbau auf ihre korrekte Funktionalität und vorgesehene Leistungsfähigkeit hin untersucht. In beiden Fällen kann diese Arbeit über die positiven Ergebnisse berichten.

#### HTRS DPU

Zu den Aufgaben der DPU gehören die Steuerung des Detektors und das Erzeugen von konfigurierbaren Spektren aus Einzelereignissen zur Datenreduktion. Diese Funktionalität wurde in VHDL entwickelt und in einem Spartan 3 FPGA implementiert. Eine besonders wichtige Aufgabe der DPU ist die Datenkompression mit dem bzip2 Algorithmus. Die Kompression wurde in der Programmiersprache C implementiert und unter Verwendung des VHDL-Modells des LEON3 Mikroprozessors ebenfalls in den FPGA integriert. Die Funktionalität der DPU und die erwartete Leistung der bzip2 Kompression konnten in einem Laboraufbau demonstriert werden.

#### LAD PBEE

Die Arbeit am zweiten Projekt beinhaltete die Definition und die Entwicklung eines PBEE Prototypen und einer neuartigen Schnittstelle für die Kommunikation zwischen Module-Back-End-Electronic (MBEE) und PBEE. Sowohl die Schnittstelle wie auch die gesamte Logik der PBEE wurden in VHDL entwickelt. Dabei wurde eine spezielle Methode der VHDL Entwicklung, die Two Process Method, verwendet. Ein Platinenlayout des Prototyps wurde erstellt, gefertigt und bestückt. Dabei kamen Trägermodule mit einem Virtex 4 und einem Spartan 3 FPGA zum Einsatz. In einem Laboraufbau aus einem MBEE Prototypen, dem PBEE Prototypen und zwei weiteren MBEE Simulatoren, die auf der PBEE Platine untergebracht sind, konnte die geforderte Datenübertragungsrate der Schnittstelle und Funktionalität der PBEE gezeigt werden.

#### Struktur der vorliegenden Arbeit

Nach einer Einführung in die Röntgenastronomie in Kapitel 1 wird der Einfluss des programmatischen Kontextes einer Mission auf die Entwicklung der Hardware (Kapitel 2) erläutert.

Kapitel 3 präsentiert einen Überblick der zur Verfügung stehenden Hardware für die Datenverarbeitung und begründet auch die getroffene Auswahl für die entwickelten Prototypen. Im Anschluss daran gibt Kapitel 4 einen Einblick in die verwendete Software und erklärt insbesondere die Vorteile der verwendeten VHDL Entwicklungstechnik in Abschnitt 4.2.

Im dritten Teil der Arbeit werden die Missionen IXO (Kapitel 5) und LOFT (Kapitel 6) vorgestellt und die genannten Instrumente detailliert beschrieben. Diese Kapitel gehen auch detailliert auf die entwickelten Komponenten (HTRS DPU und LAD PBEE) ein und stellen die Entwicklung der Prototypen bzw. die Ergebnisse der Labortests vor. Abschließend fasst Kapitel 7 die Arbeiten und Ergebnisse noch einmal zusammen und gibt auch einen Ausblick auf Weiterentwicklungen der Prototypen und mögliche weiterführende Studien.

Im Anhang der Arbeit finden sich eine Reihe detaillierter Anleitungen wie der LEON3 Mikrocontroller auf einem FPGA-Entwicklungsboard in Betrieb genommen wird.

## Contents

| I  | X-   | ray As   | stronomy                        | 1    |

|----|------|----------|---------------------------------|------|

| 1  | X-ra | ay Astro | onomy                           | 3    |

|    | 1.1  | -        | ef History of X-ray Astronomy   | . 3  |

|    | 1.2  |          | ncements in Instrumentation     |      |

|    |      | 1.2.1    | First Rocket Experiments        |      |

|    |      | 1.2.2    | Uhuru                           |      |

|    |      | 1.2.3    | Einstein                        |      |

|    |      | 1.2.4    | EXOSAT                          |      |

|    |      | 1.2.5    | ROSAT                           |      |

|    |      | 1.2.6    | ASCA                            |      |

|    |      | 1.2.7    | RXTE                            |      |

|    |      | 1.2.8    | BeppoSAX                        |      |

|    |      | 1.2.9    | Chandra                         |      |

|    |      |          | ) XMM                           |      |

|    |      |          |                                 |      |

| 2  |      | -        | sion Context                    | 13   |

|    | 2.1  |          | SA Cosmic Vision Program        |      |

|    |      |          | ESA Cosmic Vision Timeline      |      |

|    | 2.2  | The N    | IASA Astro2010 Decadal Survey   | . 16 |

| II | Da   | ita Pro  | ocessing Elements               | 19   |

| 3  | Har  | dware    | Layer                           | 21   |

|    | 3.1  | Micro    | processors                      | . 21 |

|    | 3.2  |          | n-on-a-Chip                     |      |

|    |      | 3.2.1    | Traditional SoC Design          | . 24 |

|    |      | 3.2.2    | Reconfigurable SoC Design       |      |

|    | 3.3  | Field-   | Programmable-Gate-Array         |      |

|    |      | 3.3.1    | Advantages over Microprocessors |      |

|    |      | 3.3.2    | Advantages over ASICs           |      |

|    |      | 3.3.3    | FPGA Hardware Parallelism       |      |

|    |      | 3.3.4    | FPGAs @ IAAT                    | . 30 |

|   | 3.4  | Mass Memory                    | 31 |

|---|------|--------------------------------|----|

| 4 | Soft | tware Layer                    | 35 |

|   | 4.1  | VHDL                           | 36 |

|   |      | 4.1.1 General Structure        | 36 |

|   |      | 4.1.2 Design Implementation    | 38 |

|   | 4.2  | The Two Process Method         | 38 |

|   |      | 4.2.1 Two Processes per Entity | 40 |

|   |      | 4.2.2 Using Records            | 41 |

|   |      | C C                            | 42 |

|   |      | 4.2.4 Summary                  | 42 |

|   | 4.3  | •                              | 43 |

|   |      |                                | 43 |

|   |      |                                | 45 |

|   | 4.4  |                                | 46 |

|   |      | 4.4.1 SpaceWire                | 46 |

|   |      | 4.4.2 CAN                      |    |

### III Implementation

| 5 | IXO |        |                                                             | 53 |

|---|-----|--------|-------------------------------------------------------------|----|

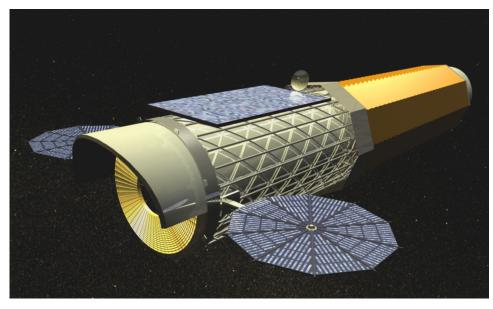

|   | 5.1 | Missic | on Overview                                                 | 54 |

|   | 5.2 | Optics | s and Payload                                               | 57 |

|   | 5.3 | Progra | ammatic Background                                          | 63 |

|   | 5.4 |        | cientific Requirements                                      | 64 |

|   |     | 5.4.1  | Co-Evolution of Galaxies and their Supermassive Black Holes | 64 |

|   |     | 5.4.2  | Large-Scale Structure and the Creation of Chemical Elements | 64 |

|   |     | 5.4.3  | Matter under Extreme Conditions                             | 65 |

|   |     | 5.4.4  | Life Cycles of Matter and Energy in the Universe            | 66 |

|   | 5.5 | HTRS   | Instrument and Detector                                     | 68 |

|   |     | 5.5.1  | HTRS Detector Chip                                          | 68 |

|   |     | 5.5.2  | HTRS Detector Electronics                                   | 68 |

|   |     | 5.5.3  | HTRS Detector Readout                                       | 70 |

|   | 5.6 | HTRS   | Data Processing Unit                                        | 71 |

|   |     | 5.6.1  | Data Rate Reduction                                         | 72 |

|   |     | 5.6.2  | Channel-Bit-Width                                           | 73 |

|   |     | 5.6.3  | DPU Prototype                                               | 75 |

|   |     | 5.6.4  | HTRS Conclusions                                            | 78 |

|   | 5.7 | From   | IXO to ATHENA                                               | 78 |

| 6   | LOF            | Г                                            | 81  |

|-----|----------------|----------------------------------------------|-----|

|     | 6.1            | Introduction                                 | 81  |

|     | 6.2            | Scientific Background                        | 83  |

|     | 6.3            | LOFT Scientific Requirements                 | 83  |

|     | 6.4            | LOFT Engineering Requirements                | 85  |

|     |                | 6.4.1 Effective Area                         | 85  |

|     |                | 6.4.2 Spectral Resolution                    | 86  |

|     |                | 6.4.3 Sensitivity                            | 86  |

|     |                | 6.4.4 Monitoring of Transient Sources        | 87  |

|     |                | 6.4.5 Mission Duration                       | 88  |

|     | 6.5            | Wide Field Monitor                           | 89  |

|     | 6.6            | Large Area Detector                          | 92  |

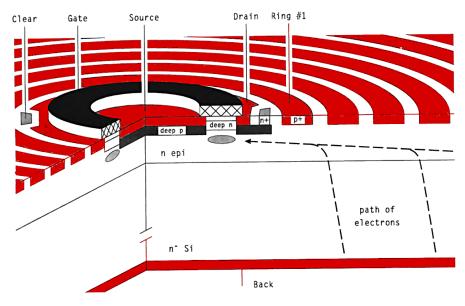

|     |                | 6.6.1 Silicon Drift Detectors                | 94  |

|     |                | 6.6.2 ASICs                                  | 95  |

|     |                | 6.6.3 Collimator                             | 96  |

|     |                | 6.6.4 MBEE                                   | 98  |

|     |                | 6.6.5 PBEE                                   | 102 |

|     |                | 6.6.6 DHU                                    | 102 |

|     | 6.7            | PBEE Prototype Board                         | 104 |

|     |                | 6.7.1 Interfaces                             | 104 |

|     |                | 6.7.2 Event Processing                       | 110 |

|     | 6.8            | LAD @ IAAT                                   | 111 |

|     |                | 6.8.1 MBEE Prototype                         | 111 |

|     |                | 6.8.2 PBEE Prototype                         | 114 |

|     |                | 6.8.3 Test Setup and Verification            | 120 |

| 7   | Sum            | imary & Outlook                              | 123 |

| IV  | Ар             | pendix                                       | 125 |

| A١  | lew F          | Project in Xilinx ISE                        | 129 |

| Us  | ing i <b>l</b> | MPACT to Configure a Target Device           | 135 |

| Us  | ing IS         | SE Design Suite to Configure a Target Device | 139 |

| Cre | eatin          | g a PROM File for the BPI Flash              | 143 |

| Wr  | iting          | a PROM File to the BPI Flash                 | 147 |

| Im  | plem           | enting the LEON3 Design                      | 151 |

| Executing LEON3 Programs using GRMON | 157 |

|--------------------------------------|-----|

| Configuring HTerm for Use with LEON3 | 161 |

| Using the Terminal Application       | 165 |

| Bibliography                         | 173 |

# Part I

# X-ray Astronomy

## Chapter 1

## X-ray Astronomy

### 1.1 A Brief History of X-ray Astronomy

The reason why X-ray astronomy was not available to astronomers during most of the history of mankind is, that the Earth's atmosphere is nontransparent to X-rays. This is because X-ray photons carry more energy than visible photons and are able to ionize oxygen and nitrogen atoms in the atmosphere. The process is called photo-electric absorption since the X-ray photon is absorbed by the atom, while a free electron is produced.

When the first X-ray detectors were invented, it immediately became clear that the Sun was an intense source of X-rays. The question arose if there were more X-ray sources in our Galaxy. But even in a starry night with clear skies, no X-rays reach the ground. X-ray detectors therefore had to be lifted into the upper atmosphere. The first rocket flight that carried an X-ray detector and successfully detected a cosmic source of X-ray emission was launched in 1962 by a group at American Science and Engineering (AS&E). The very bright source found by Riccardo Giacconi, Herbert Gursky, Frank R. Paolini, and Bruno B. Rossi was named Scorpius X-1 (Giacconi et al. 1962).

The launch of the first dedicated X-ray satellite Uhuru (Chapter 1.2.2) in 1970 marked the beginning of an era of space-based X-ray astronomy. With the detection of more extrasolar sources, e.g. Cen X-3 and Her X-1 by Uhuru (Krishnaswamy 1996), scientists had to think of mechanisms in which stars, or their remainders, could produce X-rays. When pulsations in the X-ray flux in the order of seconds were discovered, it became clear that rotating neutron stars had to be the natural sources of the emission. Variations in the pulse period due to Doppler shifting indicated that the neutron star was moving in an orbit. The hypothesis that the neutron star was part of a binary system with a normal star companion proved correct. Since then X-ray binaries are studied by scientists all over the world because they feature conditions (density, temperature) that are unique amongst a large spectrum of astronomical objects (Ramadevi 2007). The binary nature of the star system allows astronomers to determine the masses of the neutron star and its companion. For some of these systems, the mass of the X-ray emitting object was found to be hundreds or thousands of solar masses, but the mass of a neutron star is limited to less than three solar masses, otherwise the star would collapse. The findings thus supported the idea of the existence of black holes.

The pulsations found in some X-ray emissions led to the understanding of the accretion mechanism. In a binary system the neutron star accumulates matter from the companion star. Since the neutron star has a magnetic field and is spinning rapidly, the falling matter forms a disk around the star, the accretion disk. When the matter reaches the surface of the neutron star it becomes very hot and the emitted radiation can only escape along the magnetic axis of the neutron star. Since the axis of rotation and the magnetic field are not aligned the emission beam shows precession. This can be seen as the pulsation of the X-ray emission.

Some sources were found to suddenly appear in the sky, remain bright for several days to a few weeks, and then slowly fade again until no longer observable. Interestingly the progress of the decay of the emission is related to the absolute brightness of the source. Most of these sources, called X-ray transient sources, were understood to be supernova explosions (Mazzali et al. 2007).

The inner regions of some galaxies were also found to emit X-rays. The X-ray emission from these active galactic nuclei is believed to originate from ultra-relativistic gas near very massive black holes at the Galaxy's center (Kraft et al. 2007). And finally a diffuse X-ray mission was found originating from all over the sky. As of today the source of this emission is not clearly identified (Snowden 2011).

### 1.2 Advancements in Instrumentation

### 1.2.1 First Rocket Experiments

The first cosmic X-ray source, Scorpius X-1 and the cosmic X-ray background were discovered simultaneously in 1962 with a rocket experiment of the National Aeronautics and Space Administration (NASA), which was equipped with a Geiger-Müller counter with the aim of detecting X-rays reflected from the Moon (Giacconi et al. 1962).

### 1.2.2 Uhuru

On 12 December 1970 NASA launched its first dedicated X-ray satellite Uhuru from the San Marco platform near Malindi, Kenya. The satellite is also known as Small

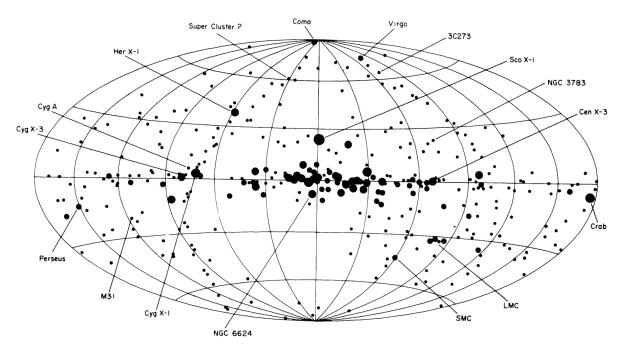

Figure 1.1

The sources from the Fourth Uhuru Catalogue displayed in galactic coordinates. The size of each symbol representing a source is proportional to the logarithm of the peak intensity. Source: Forman et al. (1978).

Astronomical Satellite 1 (SAS-1) but was renamed after launch to "Uhuru", which is Swahili for "freedom", to honour its launch date, the seventh anniversary of Kenya's independence. Uhuru carried two sets of proportional counters with a total effective area of 0.084 m<sup>2</sup> covering an energy range from 2 keV to 20 keV (Santangelo and Madonia 2014).

The science payload, at 64 kg, weighed no more than a typical rocket experiment at the time. The two sets of conventional proportional counters with simple honeycomb collimators were used to undertake the first X-ray survey of the sky. The spacecraft was spin stabilized at 12 minutes per revolution. One detector had a field of view of 1 degree x 10 degrees, so it viewed each source for 2 s during each scan. A second detector had a field of view of 10 x 10 degrees and spent 20 seconds on sources during each scan. Uhuru scanned sky regions several times (typically about 60 passes per 24 hour period) thereby greatly increasing its sensitivity to weak sources. The net result of this was that Uhuru was able to detect X-ray sources 10 times fainter than the faintest detectable sources during earlier rocket flights down to a limiting sensitivity of about 0.001 of the intensity of the Crab Nebula. Although not uniform in sensitivity, 95% of the sky was scanned during the 2.5 year lifetime of the mission. Finally the Uhuru catalogue was issued, containing 339 objects as shown in Figure 1.1.

#### 1.2.3 Einstein

NASA's second of three High Energy Astrophysical Observatories, HEAO-2, renamed Einstein after it became operational, was launched 13 November 1978 and was the first satellite mission that used X-ray telescopes with mirrors. This was made possible when in 1951 the physicist Hans Wolter at the University of Kiel developed a mirror configuration consisting of paraboloid and hyperbolic mirrors mounted confocally and coaxially that was able to focus X-ray light. These Wolter telescopes had already been used on Skylab in the early 1970's to investigate the corona of the Sun (Underwood et al. 1977).

The Einstein observatory however was the first imaging X-ray telescope put into space that was pointed at the sky. The few arcsecond angular resolution, the field-of-view of tens of arcminutes, and a sensitivity several 100 times greater than any mission before it provided, for the first time, the capability to image extended objects, diffuse emission, and to detect faint sources. It made the first X-ray images of shock waves from exploded stars, and images of hot gas in galaxies and clusters of galaxies. Einstein also located accurately over 7000 X-ray sources and detected X-ray jets from Cen A and M87 aligned with radio jets.

### 1.2.4 EXOSAT

The European Space Agency's EXOSAT (European X-Ray Observatory Satellite), was operational from May 1983 to April 1986. Similar to the Einstein Observatory it carried two Wolter telescopes and two proportional counters of which one had a total effective area 3 times larger than anything flown before. During its lifetime, EXOSAT made 1780 observations of a wide variety of objects, including active galactic nuclei, stellar coronae, cataclysmic variables, white dwarfs, X-ray binaries, clusters of galaxies, and supernova remnants. It also discovered Quasi Period Oscillations in LMXRB and X-ray Pulsars and measured the iron line in galactic and extra galactic sources (Taylor et al. 1981; White and Peacock 1988). Natural decay of the orbit caused the satellite to enter the atmosphere on 6 May 1986.

### 1.2.5 ROSAT

The Roentgensatellite or ROSAT, a joint venture between Germany, the United Kingdom and the United States, carried even larger X-ray telescopes into orbit on 1 June 1990. The two imaging telescopes operating in the soft X-ray (0.1 keV to 2.4 keV) and EUV (0.06 keV to 0.2 keV) ranges consisted of four / three nested Wolter type I-mirrors. For the manufacturing of the X-ray mirrors - the largest and most accurate ones at that time - Zerodur, a ceramics with zero thermal expansion and an extremely low surface roughness, was used for the first time. The telescopes focused X-rays on two position sensitive proportional counters (PSPC) with a spatial resolution of 20 arcsec and one high resolution imager (HRI) with a spatial resolution of 5 arcsec. The satellite and the X-ray telescopes had been designed, built and operated by Germany while NASA provided the Delta launch and the high resolution imager and the UK built and operated the EUV telescope.

ROSAT has expanded the number of known X-ray sources to more than 60000 and has proved to be especially valuable for investigating the multi-million degree hot gas present in the upper atmospheres of many stars. ROSAT also performed the first all sky survey with imaging telescopes leading to the discovery of 125000 X-ray and 479 EUV sources (Trümper 1984; Voges et al. 1999). In addition the diffuse galactic X-ray emission was mapped with unprecedented angular resolution (< 1 arcmin).

#### 1.2.6 ASCA

After the great successes of satellites with imaging X-ray telescopes ASCA (Advanced Satellite for Cosmology and Astrophysics) was designed to study the detailed distribution of X-rays with energy. Therefore ASCA carried four large-area X-ray telescopes, each composed of 120 nested gold-coated aluminum foil surfaces. At the focus of two of the telescopes located was a Gas Imaging Spectrometer (GIS), while a Solid-state Imaging Spectrometer (SIS) was operated at the focus of the other two. The sensitivity of ASCA's instruments allowed for the first detailed, broad-band spectra of distant quasars to be derived. In addition, ASCA's suite of instruments provided the best opportunity at the time for identifying the sources whose combined emission makes up the cosmic X-ray background. ASCA was launched on 20 February 1993 and operated successfully till 15 July 2000 when it was transferred into a safe-hold mode. The satellite re-entered on 2 March 2001 after 7 and half years of scientific observations.

### 1.2.7 RXTE

Although RXTE did not have focusing X-ray mirrors, it had the unique capability to study rapid time variability in the emission of X-ray sources over a wide range of X-ray energies. The Rossi X-ray Timing Explorer was launched on 30 December 1995 from NASA's Kennedy Space Center. Originally designed for a required lifetime of two years with a goal of five, RXTE surpassed that goal and completed 16 years of observations before being decommissioned on 5 January 2012. The mission carried two pointed instruments, the Proportional Counter Array (PCA) to cover the lower part of the energy range (2 keV - 60 keV), and the High Energy X-ray Timing Experiment

(HEXTE) covering the upper energy range (15 keV to 250 keV). These instruments used collimators to limit their field of view to 1° which did not provide any imaging capabilities but allowed for a timing resolution of 1  $\mu$ s (Gruber et al. 1996; Rothschild 1996). In addition, RXTE carried an All-Sky Monitor (ASM) that scans about 80 % of the sky every orbit, allowing monitoring at time scales of 90 minutes or longer.

### 1.2.8 BeppoSAX

BeppoSAX was a program of the Italian Space Agency with participation of the Netherlands Agency for Aerospace Programs. It was launched on April 30, 1996 from Cape Canaveral, and was the first X-ray mission with a scientific payload covering more than three decades of energy - from 0.1 keV to 300 keV, with moderate imaging capability. BeppoSAX proved to be useful for X-ray imaging sources associated with Gamma-ray bursts, determining their positions with unprecedented precision, and monitoring the X-ray afterglow (Boella et al. 1997; Piro 1997). All in-orbit operations of the BeppoSAX mission ended in April, 2002. In April 2003, the spacecraft re-entered Earth's atmosphere and splashed down in the Pacific Ocean.

### 1.2.9 Chandra

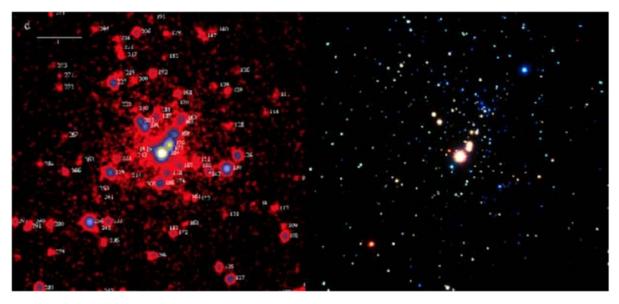

One of the most important X-ray astronomy mission of the present decade is NASA's Chandra X-ray Observatory, which was launched on July 23, 1999. The unique feature of the Chandra observatory is the High Resolution Mirror Assembly, a Wolter 1 type X-ray telescope with a focal length of 10 m and an effective area of 400 cm<sup>2</sup> @ 5 keV. Chandra uses three instruments of which one is the High Resolution Camera (HRC) that can achieve a spatial resolution of 0.4 arcsec with a pointing uncertainty of less than 0.1 arcsec (Garmire et al. 2003; Weisskopf et al. 2000). The result of this very high angular resolution is impressively shown in Figure 1.2.

The optical elements used in Chandra's mirror have four paraboloid-hyperboloid pairs resulting in the ten meter focal length. The mirror shells are made from Zerodur because of its low coefficient of thermal expansion and because Zerodur permits extremely smooth polished surfaces to the degree of a roughness of only a few atoms. The mirror surface is also coated with iridium, a material more reflective than gold (Weisskopf 2011).

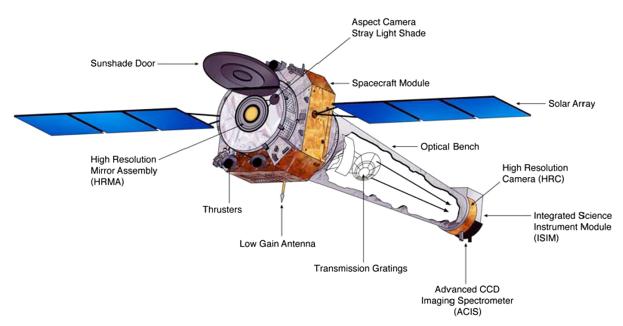

Figure 1.3 shows the design of the observatory.

#### Figure 1.2

Left: X-ray image obtained by ROSAT shows 75 X-ray sources in the Orion star cluster. Right: The same region observed by Chandra resolves 1500 sources. Source: Weisskopf (2011).

#### Figure 1.3

Chandra has two focal plane instruments. One is a High Resolution Camera (HRC). This camera while similar to the HRI carried by ROSAT and Einstein has significantly smaller pore size of the MCP and a larger microchannel plate (MCP), lower background, charged particle anticoincidence mechanisms, and energy resolution. It is used for high resolution imaging, fast timing measurements, and for observations requiring a combination of both. The second instrument, the Advanced CCD Imaging Spectrometer (ACIS), is an array of charged coupled devices (CCDs) that can be used simultaneously for imaging and spectroscopy. Images of extended objects can be obtained along with spectral information from the observed sources. Source: Weisskopf (2011) and Schwartz (2004).

#### 1.2.10 XMM

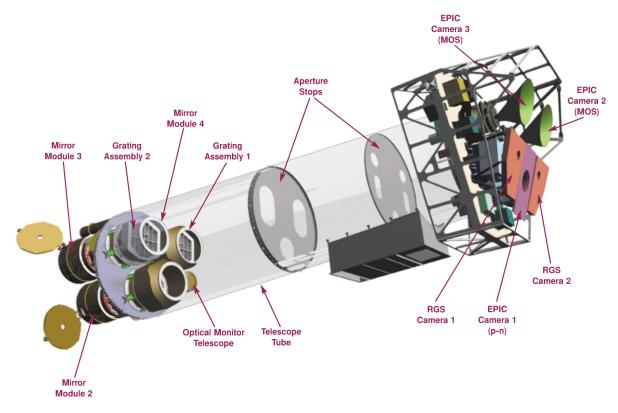

ESA's XMM (X-ray Multi-Mirror Mission) is one of the most successful missions launched by the European Space Agency. The telescope was launched on December 10, 1999. It utilizes three mirror modules, each is a Wolter 1 type grazing incidence telescope with a focal length of 7.5 m and a spatial resolution of 15 arcsec. The three telescopes are equipped with imaging cameras and spectrometers that operate simultaneously, together with a coaligned optical telescope. An overview of the telescopes design including mirrors and instruments is show in Figure 1.4 (Bagnasco et al. 1999; Lumb, Schartel, and Jansen 2012).

#### Figure 1.4

The X-ray Multi-Mirror Mission (XMM). The main components are the three Wolter 1 type grazing incident telescopes, two of them equipped with Reflection Grating Spectrometer assemblies (RGS). The three instruments are the two RGS cameras used for spectroscopy, the two EPIC MOS (metal-oxide) CCD cameras and another EPIC p-n CCD camera used for imaging. Source: Bagnasco et al. (1999).

## Chapter 2

## X-ray Mission Context

The programmatic context in which design and development of any space mission are carried out is an important part of the overall project. This context might be a national space agency with limited budget or a large consortium pooling the resources of several countries. While the latter obviously allows for more elaborate (i.e. expensive) mission concepts, the decision processes in such a context are much more complex and time consuming. Usually some sort of competition between several mission types, concepts, and designs is implemented.

Nevertheless, even the very first ESA mission entirely devoted to the study of X-rays, the EXOSAT mission (mission details in Chapter 1.2.4) launched in 1983, was developed and built by a multi-national European consortium including the United Kingdom, the Netherlands, Germany, and Italy. The ESA share of the satellites costs (development, integration, and testing) amounted to 52 million euros, while the construction of the instruments and satellite bus were contributions by the consortium. The ESA context in which the selection and management of missions takes place is explained in this chapter. A similar mechanism used by NASA is also discussed briefly in Chapter 2.2.

### 2.1 The ESA Cosmic Vision Program

Currently ESA has 20 member states (see Table 2.1) and one associated member (Canada). In a context of different national interests in space-based astrophysics it is difficult to decide which mission to develop, build, and launch next. Therefore, ESA has developed a mechanism that allows for a reasonable selection of important scientific themes of common interest in the European scientific community. The most important cornerstone for the long-term planning, selection, and execution of missions is currently the Cosmic Vision 2015-2025 program (Bignami et al. 2005).

This program is the successor to the previous definition of important questions to be addressed by space-based telescopes and observatories "Horizon 2000" (Longdon

1984). The Horizon 2000 program proved to be a great success when in 2005 the probe Huygens descended through Titan's atmosphere onto the moons surface. Development and execution of this mission took 23 years, from the submission of the proposal in 1982 through the production, integration, and validation phase (1988-1997) and a launch in 1997 to the arrival in 2005. This enormous effort was enabled by the Horizon 2000 program originally presented in 1984.

To provide a solid and scientifically justified base for decisions regarding the selection of suitable space missions ESA defines four main Cosmic Vision 2015-2025 Science Objectives. These are considered the most important themes of astronomical research across Europe:

- 1. What are the conditions for planet formation and the emergence of life?

- 2. How does the Solar System work?

- 3. What are the fundamental physical laws of the Universe?

- 4. How did the Universe originate and what is it made of?

These questions establish the scientific context in which ESA then issues several "Call for Missions" for ideas of next-generation observatories and experiments. Scientists from ESA member states (Table 2.1) can submit their ideas and selected missions will receive funding from national space agencies to be studied and refined in more detail. After a second selection only a few missions remain and receive further funding to conduct a Phase A study. While further refined at scientific facilities the mission is also evaluated by industry partners for a possible realization. One - rarely two - missions are selected after the assessment phase for a possible launch and the development and assembly of prototypes begins, eventually resulting in the production and testing of flight hardware and finally the launch.

### 2.1.1 ESA Cosmic Vision Timeline

This section summarizes important events related to the Cosmic Vision 2015-2025 program. It is compiled from several ESA press releases.

The first Call for Mission for the current Cosmic Vision 2015-2025 program was issued in March 2007, targeting two missions: one medium (M-class) and one large (L-class), for launch in 2017 and 2018. From 50 proposals received, four M-class candidates (Euclid, PLATO, Marco Polo, and Cross Scale), a mission of opportunity (SPICA, led by JAXA) and three L-class candidates (IXO, Laplace and TandEM) were selected for assessment. The LISA mission, carried over from the predecessor of the Cosmic Vision program "Horizon 2000 Plus", was included as an L-class candidate.

| Table 2.1                                                             |

|-----------------------------------------------------------------------|

| Left: The 10 ESA founding members.                                    |

| Right: 10 more countries joined the European Space Agency since then. |

| 1.  | Belgium        | 11. Austria        |

|-----|----------------|--------------------|

| 2.  | Denmark        | 12. Czech Republic |

| 3.  | France         | 13. Finland        |

| 4.  | Germany        | 14. Greece         |

| 5.  | Italy          | 15. Ireland        |

| 6.  | Netherlands    | 16. Luxembourg     |

| 7.  | Spain          | 17. Norway         |

| 8.  | Sweden         | 18. Poland         |

| 9.  | Switzerland    | 19. Portugal       |

| 10. | United Kingdom | 20. Romania        |

In 2009, the Cosmic Vision program was updated to reflect the overall funding availability, the technical progress of the studies, the situation of the mission technology readiness, and the availability of international partners. The two launch slots in 2017 and 2018 were confirmed, but were both designated as M (M1 and M2) missions. Solar Orbiter was reclassified as a sixth M-class mission candidate for M1/M2. The Laplace mission to the Jupiter system was selected as the outer planet candidate L-class mission. IXO, Laplace and LISA were maintained in the plan as candidates for the L1 launch opportunity, with a large involvement of international partners (NASA and JAXA), and targeting a launch year in 2020, subject to partnership consolidation.

The second call for Cosmic Vision missions was released in July 2010 with the goal of selecting a third M-class mission (M3) with a targeted launch date of 2024. From the 47 proposals submitted, four were recommended by the ESA Advisory Structure and selected for assessment. These missions (EChO, LOFT, MarcoPolo-R, and STE-QUEST) were joined by PLATO and became candidates for the M3 launch opportunity. In February 2014 the planet hunter PLATO was selected as medium-class science mission.

In 2011, ESA imposed major requirement changes on all three L-class mission candidates to take account of developments with ESA's international partners, namely NASA withdrawing from the L-class mission. During the reformulation exercise IXO became ATHENA and Laplace became JUICE. After the selection of JUICE (Jupiter Icy Moons Explorer) as current L1 mission by ESA in 2012 ATHENA was again revised to become a candidate for the 2013 selection of a science theme for an L2 or L3 mission.

A call for a small (S-class) missions in the science program was issued in March 2012, advertising a single launch opportunity in 2017. The CHEOPS mission was later selected for implementation from a total of 26 proposals.

In March 2013, a Call for White Papers was issued asking the science community to propose science themes and associated questions that could be addressed by the next two large (L-class) missions, L2 and L3, which are currently planned for launch 2028 and 2034.

In September 2013 "The Hot and Energetic Universe" was in fact selected as science theme for an L2 mission with a possible launch in 2028. ATHENA was the only candidate for this mission slot. A mission proposal was submitted to ESA in April 2014 (Nandra 2014).

### 2.2 The NASA Astro2010 Decadal Survey

To define the most important astronomical and astrophysical themes the National Research Council of the National Academy of Sciences releases the Astronomy and Astrophysics Decadal Survey every ten years. The current survey "New Worlds, New Horizons in Astronomy and Astrophysics" was released in August 2010 and recommends priorities for the most important scientific and technical activities of the decade 2010-2020. Recommendations for scientific questions to be answered include:

- How did the Universe begin?

- What were the first objects to light up the Universe and when did they do it?

- How do cosmic structures form and evolve?

- What are the connections between dark and luminous matter?

- How do stars and black holes form?

- How do circumstellar disks evolve and form planetary systems?

- Why is the Universe accelerating?

- What is dark matter?

- What are the properties of the neutrinos?

- What controls the masses, spins and radii of compact stellar remnants?

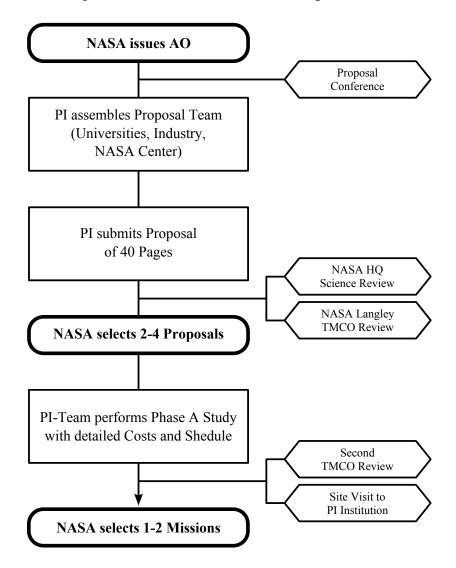

While this definition of important questions to be answered by the science community is very similar to ESA's Cosmic Vision program, NASA uses a different process to select and finance suitable space missions that is shown in Figure 2.1.

#### Figure 2.1

Overview of the NASA Mission Selection Process.

After the Announcement of Opportunity (AO) the PI-Team submits a proposal for a mission concept. Scientifically relevant concepts are selected on which a detailed Phase A study is performed. Finally a technical, management, cost and other program factors (TMCO) panel assesses the feasibility of the mission implementation approach. Once selected by the TMCO and after at least one more formal confirmation review the mission is ready for realization. Derivative work; original figure: National Research Council (2006).

# Part II

# **Data Processing Elements**

## Chapter 3

## Hardware Layer

Usually the first choice to be made during the development of data processing equipment is the selection of the actual hardware that will be used to perform data handling tasks. Several types of processing hardware are available, each with its own performance, complexity, and costs. The selection is usually based on a trade between costs and performance on one side and complexity, weight, and power consumption on the other. Another aspect is the implementation of the desired functionality in software, e.g. by using a programming language like C for a microcontroller or using a hardware description language for an FPGA. While this chapter deals with the different hardware options, Chapter 4 provides insights into the software layer.

### 3.1 Microprocessors

The basic component of most data processing units is the Central Processing Unit (CPU) or microprocessor. Early uses of microprocessors in space include e.g. the General Electric 18-bit word TTL. It was used on the Voyager satellites launched in 1976, included 4096 bytes of RAM and could execute 25000 instructions per second (Tomayko 1988). A modern example is the Dual BAE RAD750, a radiation-hardened version of the IBM PowerPC 750, running at 200 MHz with access to 256 megabytes of DRAM that is used e.g. by the Kepler Observatory (Yra et al. 2010).

Many different CPUs have been used aboard space missions. Such CPUs must be highly reliable and very durable since the temperatures in space, even with heaters, can vary widely and the radiation that a system is exposed to can be immense (up to 20 Gy/year). Therefore microprocessors used in space environment have to be designed and built including techniques like error checking and correcting memory (ECC RAM), radiation-hardened components, and hardware redundancies. They also have to be especially qualified for the use in the given environment. This qualification process represents the verification that a particular component's design, fabrication,

workmanship, and application are suitable and adequate to assure the operation and survivability under the required conditions (Kayali 2007).

Unfortunately such a qualification process is rather expensive, in terms of costs as in terms of time and can easily take five to ten years. This significantly reduces the number of available components in comparison to the availability of processors for ground-based applications. Table 3.1 shows a list of space missions and the CPU(s) used.

When a microprocessor for space applications has been designed from suitable, space qualified components, the whole system is tested and validated extensively. If all components are already qualified, a simpler but still time consuming process is conducted on all flight hardware equipment. The time and work invested into the qualification of the whole system can be further reduced by selecting one of two possible approaches explained in detail in the next two chapters.

One approach is to use a System-on-a-Chip where many different components are already integrated into one complex system that is then thoroughly tested and qualified for the use in space (Chapter 3.2). Another approach is to implement the whole processing unit as a VHDL (Chapter 4.1) design into an FPGA (Chapter 3.3). FPGAs are available in space qualified versions and VHDL designs can be tested and verified for the most part in a software environment.

Table 3.1

CPUs used in space missions throughout the years. Source: John Culver (2014; via e-mail).

| Mission         | CPU                       |

|-----------------|---------------------------|

| Cassini         | 1750A                     |

| Cluster (ESA)   | 1750A                     |

| MSTI-1,2        | 1750A                     |

| Rosetta (ESA)   | 1750A                     |

| EOS Terra       | 1750A                     |

| EOS Aqua        | 1750A & 8051              |

| EOS Aura        | 1750A & 8051              |

| Clementine      | 1750A, 32 bit RISC        |

| MSTI-3          | 1750A, R-3000             |

| Pluto Express   | 32 bit RISC               |

| Sampex          | 80386, 80387              |

| SMEX            | 80386, 80387              |

| SWAS            | 80386, 80387              |

| TRACE           | 80386, 80387              |

| WIRE            | 80386, 80387              |

| FUSE            | 80386, 80387, 68000       |

| Surrey MicroSat | 80386EX                   |

| FAST            | 8085                      |

| Galileo AACS    | ATAC (bit slice) and 1802 |

| SPOT-4          | F9450                     |

| EO-1/WARP       | Mongoose V                |

| IceSat Glas     | Mongoose V                |

| MAP             | Mongoose V, UTMC 69R000   |

| CGRO            | NSSC-1                    |

| Topex/Poseidon  | NSSC-1                    |

| UARS            | NSSC-1                    |

| EUVE            | NSSC-1, 1750A             |

| HST             | NSSC-1/386, DF-224-486    |

| Coriolis        | RAD6000                   |

| Deep Space-1    | RAD6000                   |

| Gravity Probe B | RAD6000                   |

| HESS            | RAD6000                   |

| MARS 98         | RAD6000                   |

| SIRTF           | RAD6000                   |

| SMEX-Lite       | RAD6000                   |

| Swift           | RAD6000                   |

| Triana          | RAD6000                   |

### 3.2 System-on-a-Chip

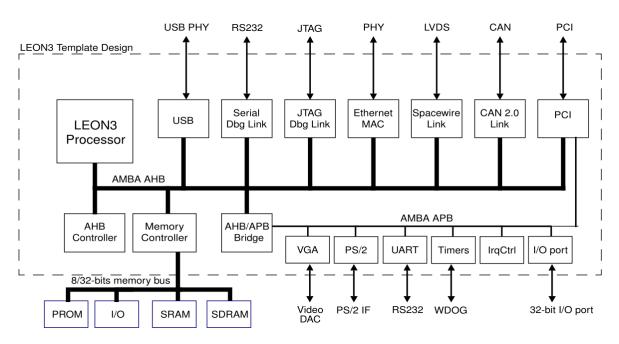

The high-level operations of satellite systems are usually handled by a System-ona-Chip (SoC). Its tasks include command and control of the instrument, relaying commands to distributed sub-units, handling the telemetry (not necessarily directly to the ground station but to the satellite bus), collecting and processing housekeeping data, and applying lossy or lossless compression algorithms to the collected data to reduce its size

A SoC is an integrated circuit (IC) that – very similar to a microcontroller – includes a central processing unit (CPU). It also includes additional advanced hardware components such as memory (RAM), timing sources and counters, peripheral components like USB, Ethernet, and SpaceWire interfaces, analog-digital-converters (ADCs), and different kinds of specialized components (audio, video, compression).

For reasons explained in Section 3.1 future missions will tend to replace SoCs by microcontrollers designed in a synthesizable hardware description language (e.g. VHDL) and implemented in an FPGA. While additional components can also be implemented in the FPGA creating a SoC like structure, some FPGA parts may still contain parallel logic providing the benefits described in Section 3.3.3.

### 3.2.1 Traditional SoC Design

In the traditional design, different data sources (i.e. scientific space instruments) are equipped with stand-alone data processing units (DPUs) using radiation-hardened parts. Present available radiation-hardened processors (e.g. ERC32, TSC21020 or AT697) offer low to medium processing performance and therefore are typically used for control and sequencing tasks only (Fiethe et al. 2007). To handle the high data rates of modern instruments, DPUs need to include some dedicated hardware for offline processing via mass storage or online processing, e.g. data compression. Such classical systems show clear disadvantages in resource allocation (low integration density and moderate performance). The state-of-the-art solution could be a complete SoC system implemented within a radiation-hardened ASIC. But this approach has the drawback of a long development time and low adaptability to changes in mission requirements due to the fact that the implementations have to be fixed to a simplified scheme, which needs to be frozen in an early project phase.

Commercial off-the-shelf (COTS) DPU hardware uses standard components and plastic encapsulation. This approach combines good performance with small outline lightweight packages and the intrinsic high reliability of high volume production (Fiethe et al. 2007). Usually plastic encapsulation and failure rates of COTS parts are acceptable or can be made acceptable for a space environment by additional measures. This allows very compact DPU designs (Fiethe et al. 2003; Gliem and Gerlach 2001). The big disadvantage of using COTS parts is that every part has to be tested for radiation resistance and its correct operation has to be verified under space-like environmental conditions. This needs a lot of preparatory work and due to the short availability time of commercial parts, such components need to be selected and fixed in a very early phase of the project or they might otherwise not be available later on.

# 3.2.2 Reconfigurable SoC Design

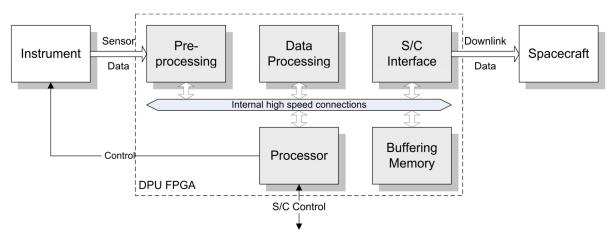

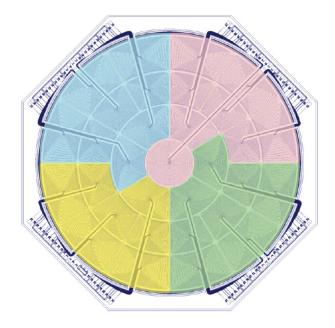

The availability of radiation tolerant FPGAs and processor technology enable new approaches to the instrument system architecture. An advanced SoC design integrates special functions (e.g. data compression or formatting/coding (Michalik et al. 2006)) together with the processor system in a single FPGA. Figure 3.1 shows the general architecture of such an advanced DPU/SoC design.

### Figure 3.1

SoC architecture using an FPGA. The SoC design integrates specialized functions (like data processing) together with the main processor (CPU) in a single FPGA. Interfaces to the spacecraft (S/C) are included. Source: Fiethe et al. (2007).

# 3.3 Field-Programmable-Gate-Array

A Field-Programmable-Gate-Array (FPGA) is a silicon chip that can be re-programmed even when already in use (field-programmable). The chip contains a number of components that are grouped into functional units – so called "slices" – inside a semiconductor device. Slices on the chip are connected via programmable interconnects and form "logic blocks". Modern FPGA devices contain large numbers ( $\gg 10000$ ) of blocks enabling them to provide the capability to implement huge and complex circuits.

Using a hardware description language (HDL) engineers can realize arbitrary circuit designs in an FPGA. The work done in the context of this thesis, implementing a LEON3 microprocessor in a Spartan FPGA (see Chapter 5, IXO), and developing the LOFT LAD PBEE and implementing it in a Virtex FPGA (Chapter 6, LOFT), was done using VHDL.<sup>1</sup> The description of an FPGA design has some similarities to the use of a programming language, such as a certain syntax, modularity, conditional constructs and loops, data types. But it is also different by not using sequentially processed commands but parallel executed statements instead.

FPGAs can be considered "becoming" any circuit design by a chain of processes that is described in detail in Chapter 4.1.2 - Design Implementation on page 38 and visualized in Figure 4.2 on page 39. Due to their high flexibility, and the ability to be re-programmed repeatedly, FPGAs are used especially in the development of new hardware designs. They can also be used very cost efficiently when only a small number of rather complex processing units is needed and the initial development of an ASIC is too expensive and longsome. Both cases are certainly true for developing and operating a space-based telescope. But also in the commercial satellite business in general the use of FPGA based hardware solutions is increasing (Habinc 2002).

# 3.3.1 Advantages over Microprocessors

One simple argument for the superiority of FPGAs over microprocessors is the fact that the LEON3 microprocessor can be implemented in an FPGA, thus the FPGA becomes the microprocessor. A more serious advantage is the fact, that FPGAs are inherently capable of real hardware-parallelism. All functional units (logic blocks) inside an FPGA are operating in parallel. All operations on input signals are done on the e.g. rising edge of a clock signal, sequential operations on internal data have to be implemented manually (which can be done, see Chapter 4.2). The parallel execution can make the implementation of complex algorithms very difficult since sequentially

<sup>&</sup>lt;sup>1</sup> The "V" in VHDL is short for VHSIC, which itself is the acronym for Very-High-Speed-Integrated-Circuit.

written code will not produce sequential operations. This is a very basic and important characteristic in the description of an FPGA design and is therefore explained in more detail in Section 3.3.3.

There are however applications for microprocessors that can not simply be implemented in an FPGA. A microcontroller loads its instructions entirely from external memory, even though this memory might be integrated in a SoC design. It can, when given enough memory, which nowadays is rarely a limiting factor, process an arbitrary long sequence of operations and therefore perform almost arbitrary complex calculations. Since the equivalent to the microcontroller's instructions is hardwired in the FPGA's logic blocks there is a natural limit to the design size. A fundamental advantage of microcontrollers are their significantly lower prices. FPGAs are easily a factor of 10 more expensive than modern microprocessors.

# 3.3.2 Advantages over ASICs

When a digital circuit has been designed, assembled from single parts, and tested, it is eventually produced as an integrated circuit (IC). Whenever large numbers of ICs are used in a complex design, the final assembly is implemented in one single complex part, the Application-Specific Integrated Circuit (ASIC). The major difference in comparison to an FPGA is that the ASIC can not be modified after production. The development process of an ASIC however is very similar to the development of an FPGA design, the hardware description language VHDL can be used in both cases.

The final production of an ASIC is much cheaper than the production of the extremely complex structure of an FPGA, since only the final circuit is realized. On the other hand, the costs of the initial development of the required photomasks, and the assembly of a production line are very high, reaching up to several hundred thousand euros. One reason for this is the need for an extremely high quality of the masks, since every error is passed onto the final product.

# 3.3.3 FPGA Hardware Parallelism

This section explains in detail the consequences of the real hardware parallelism of statements in an FPGA design written in e.g. VHDL. Note that a CPU is not capable of real hardware parallelism.<sup>2</sup> A CPU always executes instructions sequentially. A user may have the impression that a CPU can work on several tasks at the same time because it switches between the execution of different processes very quickly (more than hundred times per second) when running at up to 3 GHz.

The VHDL source code shown in Code Example 3.1 describes one functional entity (hence the keyword entity). Many of such entities of different size and complexity are used to build the final design in a modular way. The entity shown is supposed to take an 8-bit value on a parallel bus as input and to process this value to produce an 8-bit result on a parallel bus as output.

The section starting with "main: process (clk)" contains the logic that is to be applied to the input signals on the rising edge of a clock signal. This is achieved by using the if-statement with "rising\_edge(clk)". Two different things are specified to happen:

- 1. The 8-bit value in the register "input" is transferred into a local register "A".

- 2. The value in the local register "A" is mathematically added as a binary number with the value in register "input" and the result is placed in the register "output".

The code is written in sequential statements. A CPU would process these statements sequentially and the result would be the addition of the input value with itself which is placed on the output bus. This result would be equal to the multiplication by 2 of the input value. That is not what's going to happen!

The reason for the very different behavior lies within the parallelism of the statements. Those statements are not interpreted as commands being processed by a CPU but instead they create and connect flip-flops, adders and other simple logic blocks. Those logic blocks are wired to the clock signal and are activated at the same time, the rising edge of the clock. Therefore while the input value is transferred into the local register "A", the current value (the old one) of register "A" is added with the (new) input signal!

Result: If the input value changes, on the next rising edge of the clock the old value of the input (which is still located in "A") is added with the new value of input and the result is placed in the output register. Only after another clock cycle and with a constant input the result would in fact be equal to the multiplication by 2.

<sup>&</sup>lt;sup>2</sup> While the introduction of multi-core CPUs enabled small-scale hardware parallelism (a few processes running at the same time), the technical details like inter-process-communication, and uniform / non-uniform memory access still remain very challenging.

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

-- ENTITY

entity Surprise is

port(

clk : in std_logic;

input : in std_logic_vector(7 downto 0);

clk

output : out std_logic_vector(7 downto 0)

);

end entity;

-- A B C H T T F C T U B F

architecture Behavioral of Surprise is

signal A : std_logic_vector(7 downto 0);

begin

main: process (clk)

begin

if rising edge(clk) then

A <= input;

output <= input + A;</pre>

end if:

end process;

end architecture;

```

#### Code Example 3.1

This entity demonstrates the important concept of real hardware prallelism in FPGAs. The VHDL design is split into the declarative entity header and the functional architecture body. A process is defined that contains the logic of the module.

The clock synchroneous process (activated on "rising edge") reads an 8-bit input value into the local register "A". *At the same time* the (old) value "A" is added with the (new) input value and written to the output regsiter. The result does not equal the multiplication by 2 of the input value, but rather the addition of the current input value with the last one. The written order of the statements has no effect.

While hardware parallelism allows for very fast data processing, it can make understanding the functionality of an unknown entity very difficult.

# 3.3.4 FPGAs @ IAAT

Because of the advantages that FPGAs can have over microprocessors and ASICs (presented in the previous sections 3.3.1 and 3.3.2) different FPGAs are used for the prototype boards developed in the context of this thesis. Both applications are described in-depth in Chapters 5 and 6.

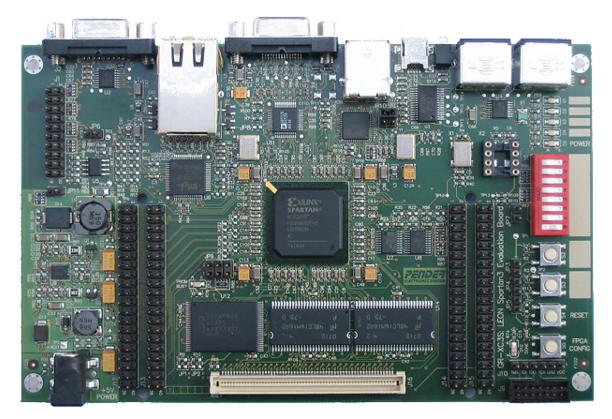

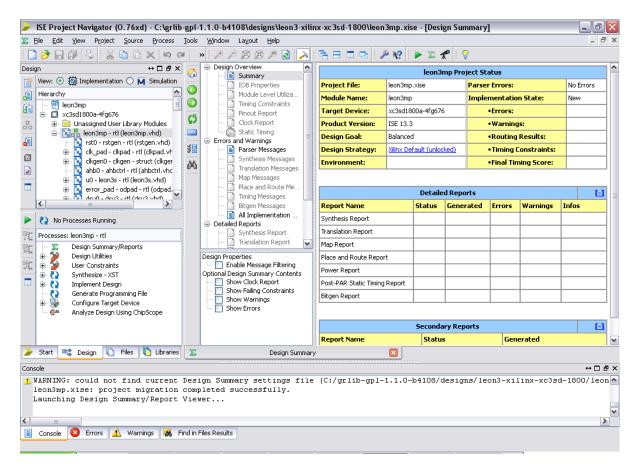

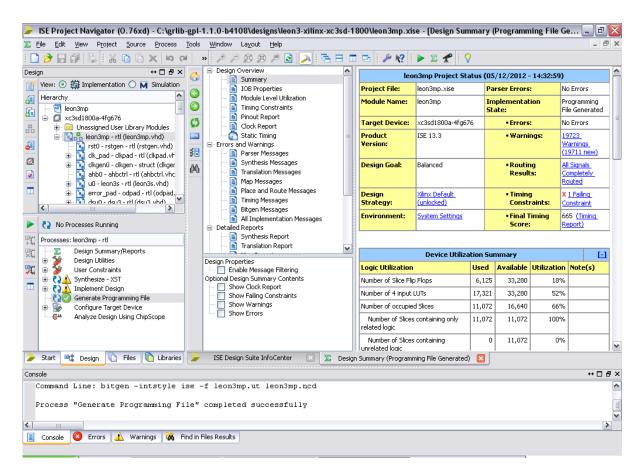

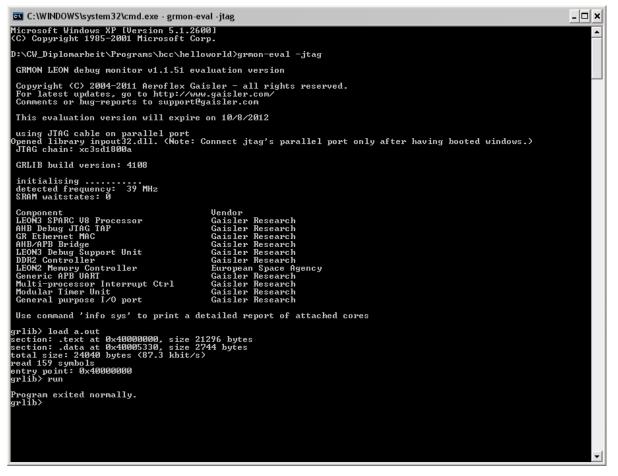

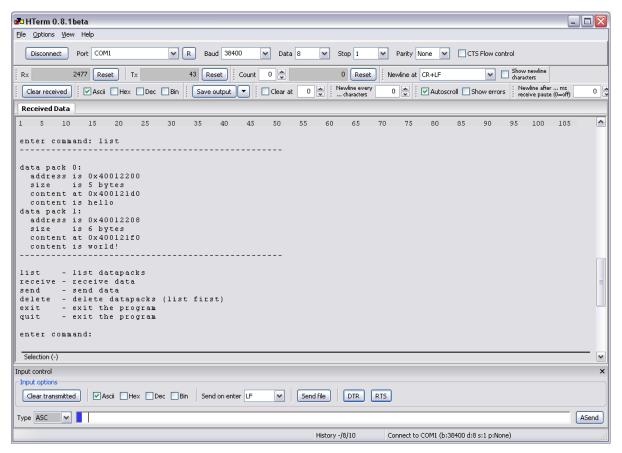

### HTRS DPU

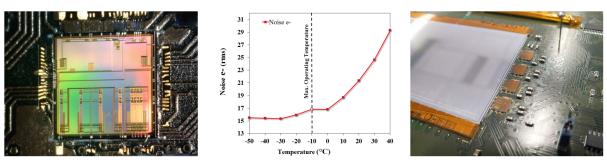

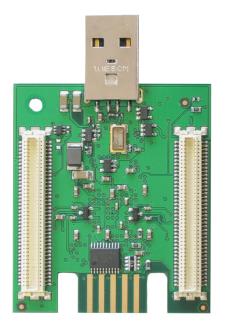

For the Data Processing Unit (DPU) of the High Time Resolution Spectrometer (HTRS), an instrument aboard the International X-ray Observatory (presented in Chapter 5.5), a Xilinx Spartan 3 XC3S on a Pender GR-X3CS development board was used to build the DPU prototype. The Spartan 3 was chosen since a similar FPGA, the Virtex 4, is available as radiation-hardened version qualified for the use in space. The board manufactured by Pender Electronic Design is shown in Figure 3.2.

Both FPGAs – when used to implement a LEON3 microcontroller – offer better performance (processing speed) as already available, space qualified, off-the-shelf microcontrollers. The LEON3 microcontroller (which is discussed in more detail in Chapter 4.3 is chosen for implementation because the Data Processing Unit of the HTRS has to execute complex compression algorithms which require the use of the programming language C to implement the desired functionality.

Additionally the DPU is required to process the data from multiple independent sources in parallel and therefore this part of the functionality is implemented directly in the FPGA to make use of the parallel processing capabilities discussed in 3.3.3. It is correct to say that in a way the DPU prototype uses the best of both worlds.

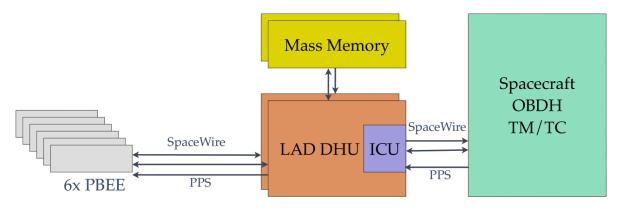

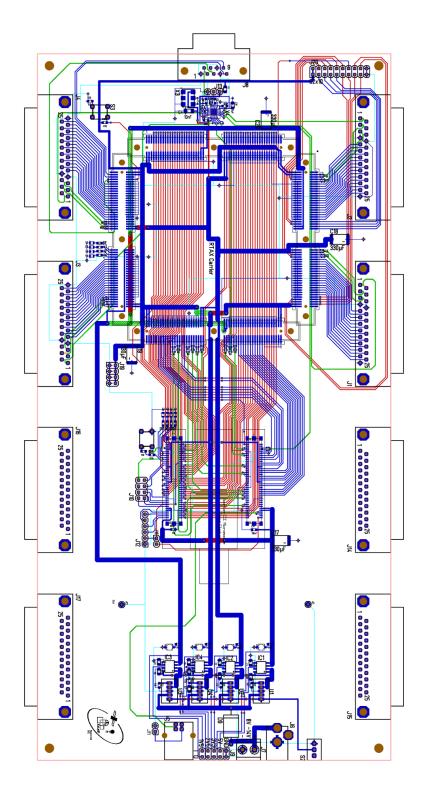

### LAD PBEE

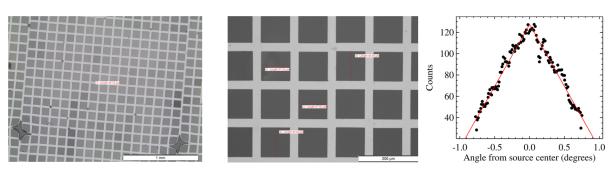

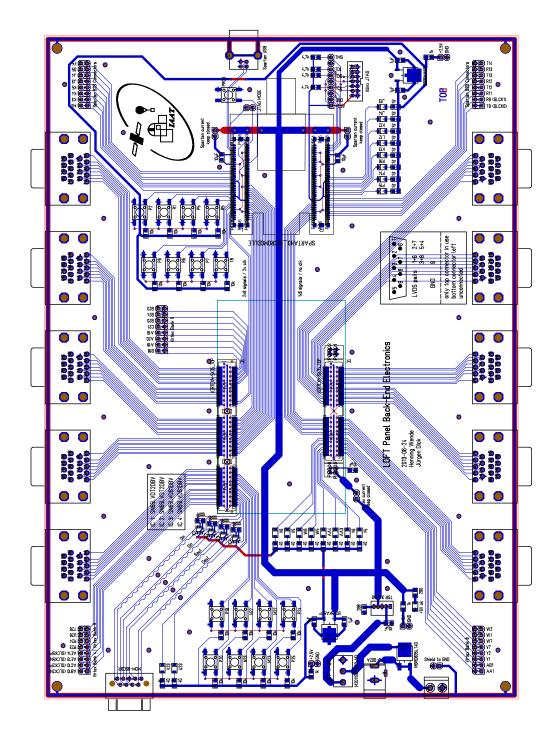

The second prototype, the Panel-Back-End-Electronics (PBEE) of the Large Area Detector (LAD), the main instrument of the Large Observatory for X-ray Timing (presented in Chapter 6.6), uses a Xilinx Virtex 4 on a custom designed printed circuit board (PCB) shown in Figure 3.3.

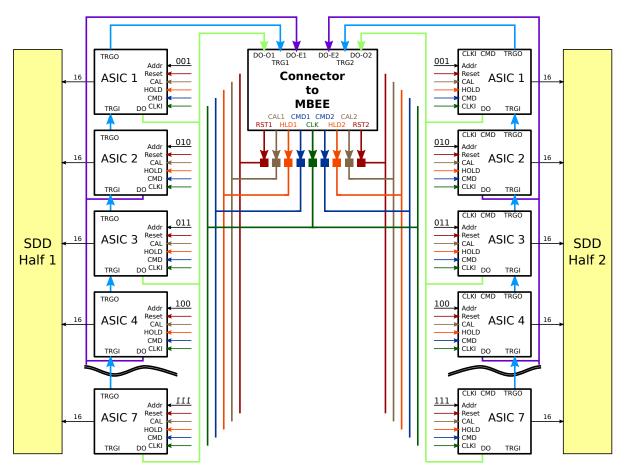

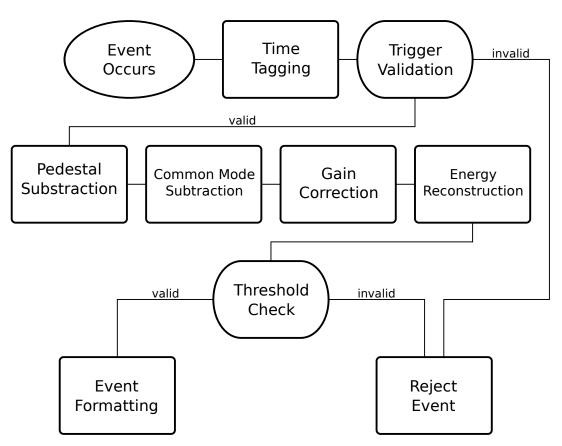

The PBEE implements 21 custom interfaces operated in parallel to communicate with and receive events from the Module-Back-End-Electronics (MBEE). The event data received from the 21 interfaces is at some point serialized and sent through a single space-wire link to the LAD instrument computer. This is a prime example of the hardware parallelism that only FPGAs are capable of providing.

The prototype board also contains an additional Xilinx Spartan 3 FPGA that is used to simulate two MBEE interfaces. This FPGA can be connected via USB to a PC to receive simulation data that is then sent to the PBEE. It can also be used to simulate the interface from the PBEE to the Data Handling Unit (DHU), albeit this connection does not use a SpaceWire interface.

# 3.4 Mass Memory

The design of mass memory as well as the design for all other systems used for space applications must take into account the difficult conditions in a space environment. A large number of effects like ionizing radiation (especially important for the storage of data), thermal conditions (e.g. between development/operation on ground and in space), and mechanical stresses (particularly during launch) have to be considered. The usual approach to this problem is the development of dedicated, space qualified, radiation-hardened hardware components, such as ASICs and FPGAs. The obvious drawbacks are very high costs due to the small number of units needed for a mission and the time consuming development process itself.

A better solution is the adaptation of already available (off-the-shelf) hardware to the given environment. Mass memory is well-suited for this approach since the components used are usually rather simple, compared to the complex structure of processing or interface and communication hardware. The development over the past years in this area, and particularly the advancements in miniaturization, have lead to a rapid growth in the storage capacity of mass memory components. The introduction of solid-state mass memories has created storage solutions which are easily competitive with tape recorders due to higher reliability, comparable density, and better performances. Solid-state mass memories have no moving parts and their operational flexibility has made them suitable for many applications, space missions being one of them.

### Figure 3.2

A Xilinx Spartan 3 FPGA on a Pender GR-XC3S development board. This board was used for the development of the Data Processing Unit of the High Time Resolution Spectrometer aboard the International X-ray Observatory.

A microcontroller design (LEON3) written in VHDL can be implemented in the Spartan 3 FPGA. The board features on-board RAM, an Ethernet controller, two USB controller, VGA video output, and two RS232 interfaces.

The FPGA is connected to an on-board 50 MHz oscillator and can be programmed via the Ethernet, serial, or an additional JTAG interface. Source: Pender Electronic Design GmbH, Switzerland.

### Figure 3.3

The custom designed prototype board for the Panel-Back-End-Electronics (PBEE) of the Large Area Detector (LAD) aboard the Large Observatory for X-ray Timing (LOFT). The board features 20 connectors for the custom designed interface to the Module-Back-End-Electronics.

While the primary FPGA, a Xilinx Virtex 4, is located at the center of the board, an additional FPGA, a Xilinx Spartan 3, was also integrated into the design (right side). This second FPGA has two on-board MBEE interface connections to the PBEE and thus can be used to simulate two MBEEs.

A full test run using two simulated MBEEs via the second FPGA and one prototype MBEE board was used to validate the parallel interface communication by sending commands and receiving simulation data.

# Chapter 4

# Software Layer

During the early design phase of any astrophysical mission appropriate hardware components have to be selected based on the required performance and the different characteristics as discussed in Chapter 3. After the hardware has been selected a suitable software layer has to be chosen to implement the desired functionality. While the operation of microprocessors usually require the use of a programming language, the development of an FPGA design is done using a hardware description language (HDL).

In the context of this thesis two different FPGA models were used to develop and operate prototype boards. For both models the design was written in the hardware description language VHDL.<sup>1</sup> Therefore Chapter 4.1 presents this hardware description language in more detail and also explains how a HDL design is implemented in an FPGA (4.1.2).

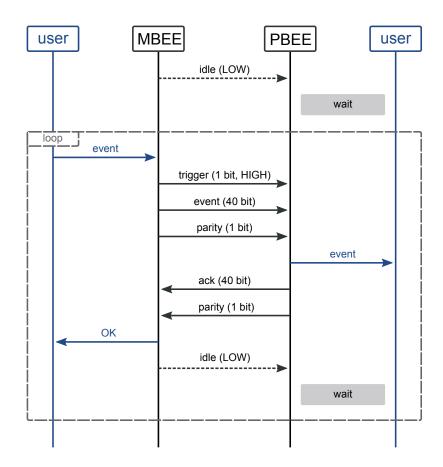

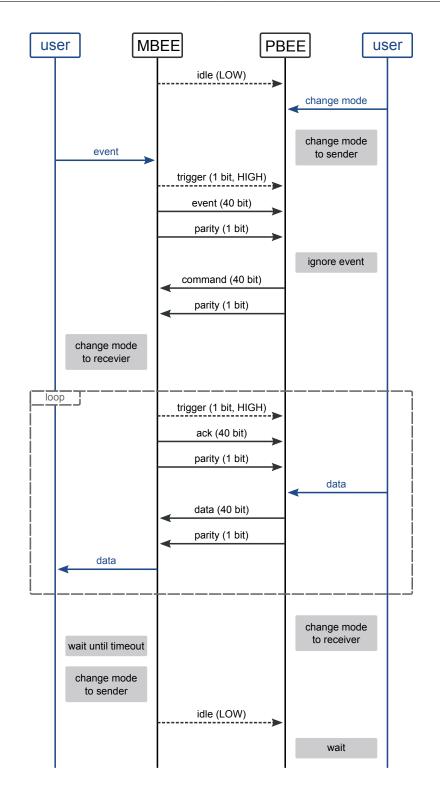

The custom designed interface used for the communication between several components of the LOFT observatory was implemented in VHDL using the *Two Process Method*, which is a special technique of writing VHDL code. Since the entire design of one of the two prototypes developed (LAD PBEE) was also written using the *Two Process Method*, Chapter 4.2 is devoted to a detailed explanation of this technique.

The other prototype design (HTRS DPU) includes a LEON3, a microcontroller design written in VHDL to be implemented in an FPGA. The functionality of this prototype was implemented in the LEON3 core using the programming language C. Additional data processing capabilities were also implemented in VHDL in the same FPGA. Chapter 4.3 is devoted to the LEON3.

Finally Chapter 4.4 deals with the different interfaces used between the components of modern data processing systems aboard space missions.

<sup>&</sup>lt;sup>1</sup> VHDL is short for VHSIC Hardware Description Language.

VHSIC stands for Very High Speed Integrated Circuit.

# 4.1 VHDL

As explained in Chapter 3.3 an FPGA differs in several ways from a microcontroller. There is no CPU that processes program instructions stored in binary machine code. Instead an FPGA is configured to reproduce a given circuit design by mapping it into the FPGA hardware structure. The mapping can be changed very late in the design cycle, even after the end product has been deployed in the field.

The configuration/design of the internal FPGA structure is specified using a hardware description language (HDL). The two most common languages are Verilog and VHDL.

### 4.1.1 General Structure

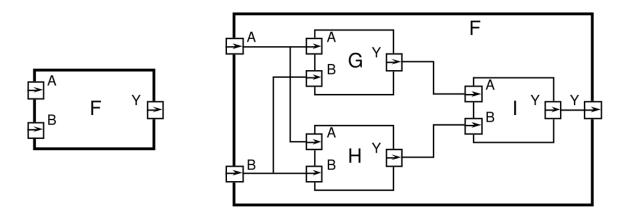

A digital circuit designed for an FPGA by the means of VHDL is usually composed of a number of modules called "entities" with in- and outputs. The outputs of an entity are functions of the inputs and sometimes of time given by any number of clock signal transitions. The left unit in Figure 4.1, the entity denoted F, is a function Y(A, B).

One way of describing the inner structure of an entity is by assembling it from a number of subsequently less complex sub-entities, whose ports are connected by signals specified in the containing entity. This technique is visualized in the right part of Figure 4.1.

This method is called the "structural description" of an entity. Another way of describing the functionality is by using the "behavioral description". This can easily be illustrated by a simple example:

Assume the entity shown in Figure 4.1 should simply realize an OR connection of the two input signals *A* and *B*. The one important line of code would then be:

$$Y = \bar{A}.B + A.\bar{B}$$

The final source code would have a few more lines, e.g. to specify the ports and types of signals used, but this single line would define the behavior of the entity.

**Figure 4.1** Structure of a VHDL entity. Source: Ashden (1990).

To describe the functionality of an entity using the behavioral description the designer can use VHDL language elements very similar to constructs used in programming languages. These include:

- temporary variables

- numbers and constants defined in central, project-wide locations

- strings and other non-trivial data types

- assignments

- if cases

- do, while, and for-loops

- switch-case procedures

- functions

However, there are significant differences when writing VHDL code compared to the source code of any programming language. The reason for this is that FPGAs do not execute commands (like microprocessors), instead VHDL describes the internal, parallel processing structure of the device. This true hardware parallelism is the subject of Chapter 3.3.3 - FPGA Hardware Parallelism (p. 28).

# 4.1.2 Design Implementation

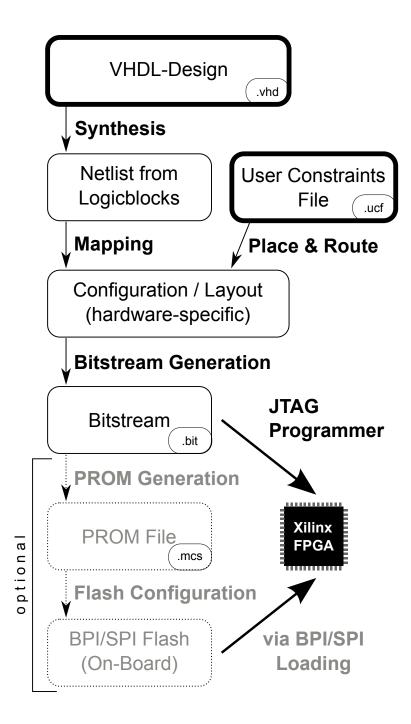

Several steps lead from the first idea of an VHDL design to the final bitstream that can be used to implement the design into hardware<sup>2</sup>. The VHDL source code can not simply be compiled but rather has to be synthesized into a netlist. During this process every entity is translated into a structure that uses the FPGA's elementary units, the logic cells or slices, to realize the desired function Y(A, B) (see Figure 4.1), e.g. by using look-up-tables. During this process dedicated components inside the FPGA might be allocated, e.g. block-RAM, digital clock manager, and FIFOs.

The next important step is routing the design through the FPGA. At this stage interconnections between entities are generated and the physical location is fixed. The position of the used input and output ports (to the device) is specified at this point in a user constraints file and has a significant effect on the process. The routing of the clock distribution network through the design usually determines the available clock frequency at this point, since clock skew for a given frequency has to be avoided.

Finally a bitstream is generated from the design that contains information about the process of implementing the design into the target FPGA. The bitstream can also be converted to a PROM file that is written into the devices flash memory and allows the FPGA to reconfigure itself upon the power-on sequence. Without a PROM file the FPGA will be "blank" after turning the power off.

The whole process is visualized in Figure 4.2.

# 4.2 The Two Process Method

The most commonly used design style for synthesizable VHDL models is what can be called the "dataflow" style. A larger number of concurrent VHDL statements and small processes connected through signals are used to implement the desired functionality. Reading and understanding dataflow VHDL code can be very difficult since the concurrent statements and processes do not execute in the order they are written, but when any of their input signals change value. It is not uncommon that when extracting the functionality of dataflow code, a block diagram has to be drawn to identify the dataflow and dependencies between the statements. The readability of dataflow VHDL code can be compared to an ordinary schematic where the wires connecting the various blocks have been removed, and the block inputs and outputs are labeled with signal names!

<sup>&</sup>lt;sup>2</sup> Note that the implementation of a VHDL design into an FPGA is not done by merely transferring data into the device but by a complex configuration process performed by dedicated hardware.

#### Figure 4.2

Schematic view of the implementation of a VHDL design. The user has to specify at least two files, shown with bold margin. The .vhd file contains the VHDL source code and the .ucf file contains the physical locations of input and output ports of the device.

A problem with the dataflow method is also the low abstraction level. The functionality is coded with simple constructs typically consisting of multiplexers, bit-wise operators and conditional assignments (if-then-else). The overall algorithm might be very difficult to recognize and debug. Yet another issue is simulation time: the assignment of a signal takes approximately 100 times longer than assigning a variable in a VHDL process. This is because the various signal attributes must be updated, and the driving event added to the event queue. With many concurrent statements and processes, a larger proportion of the simulator time will be spent managing signals and scheduling of processes and concurrent statements.

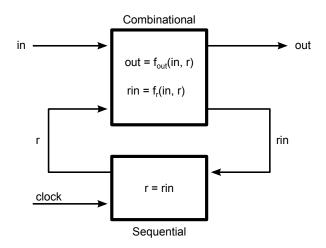

A solution to this situation is to use variables instead of signals in a sequential process and a second, combinatorial process to write an "input" record used in the sequential process with the system clock into a "registered" record. All the entity logic then lies within the sequentially written and executed first process. This technique called the "Two Process Method" was developed by Jiri Gaisler in 1997. The method was adopted by the author of this work for the development of the PBEE of the LAD instrument (see Chapter 6.6) and also used for the interface described in Chapter 6.7.1. This chapter is based on the work of Jiri Gaisler presented in (Gaisler 1996).

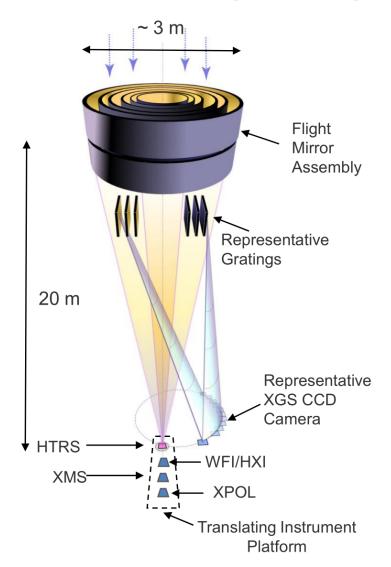

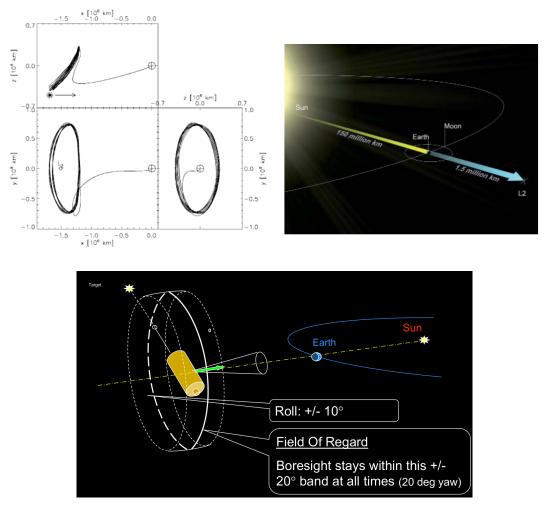

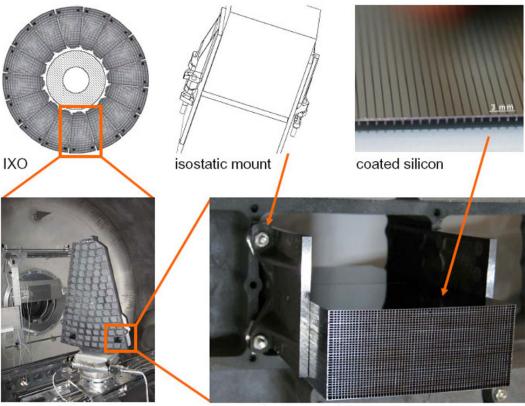

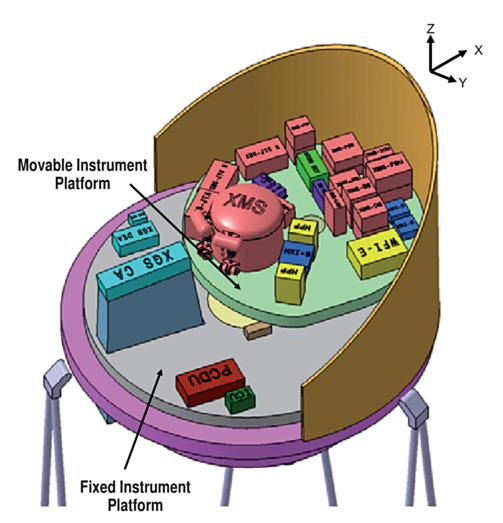

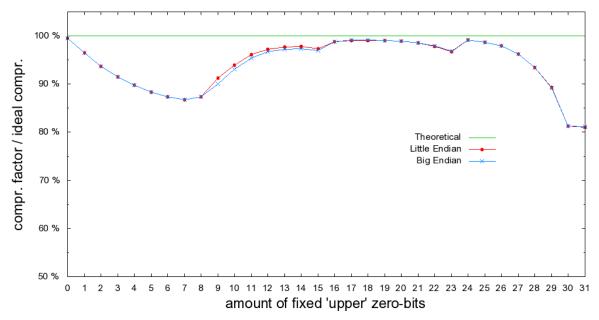

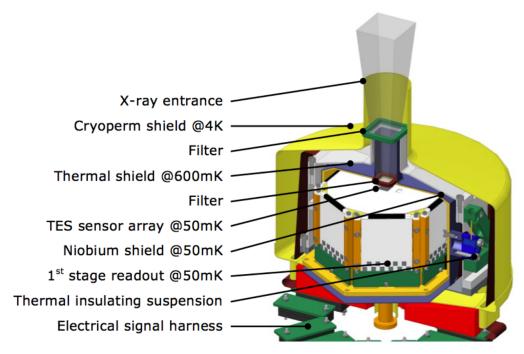

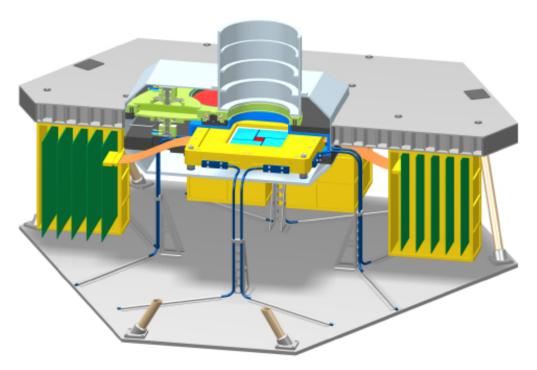

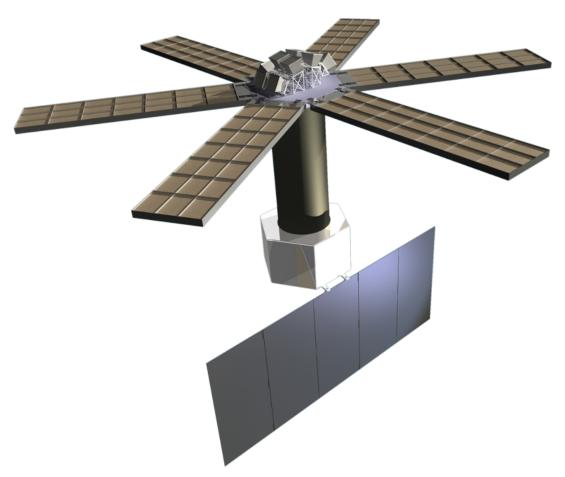

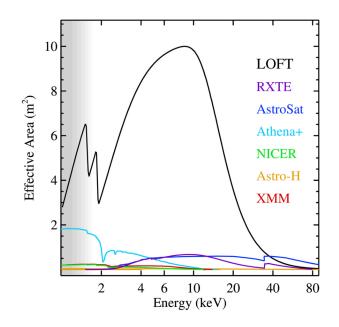

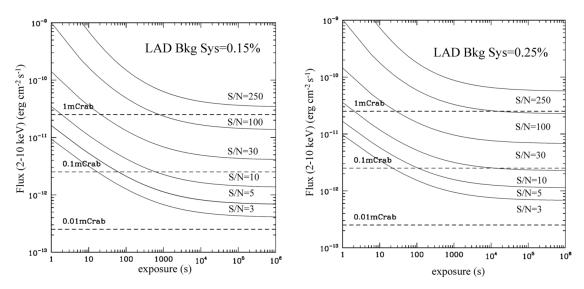

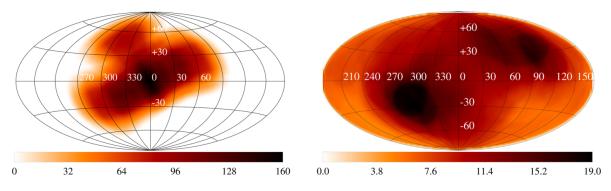

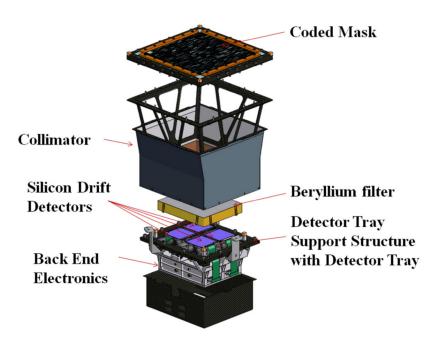

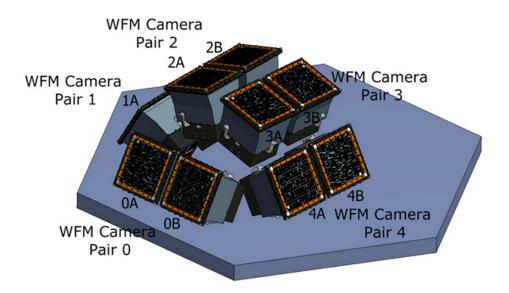

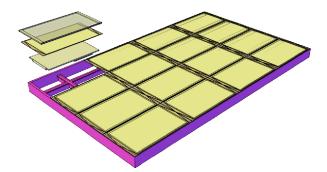

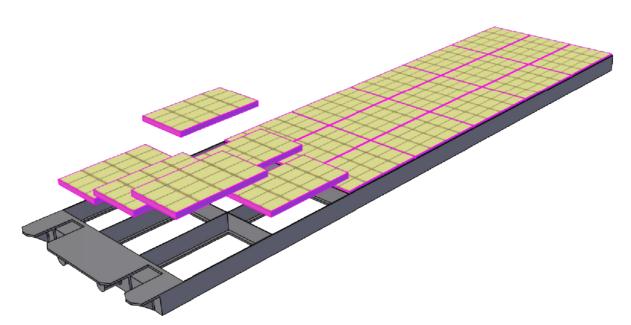

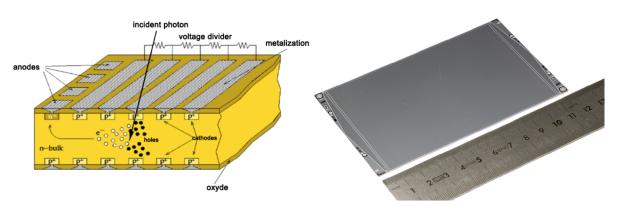

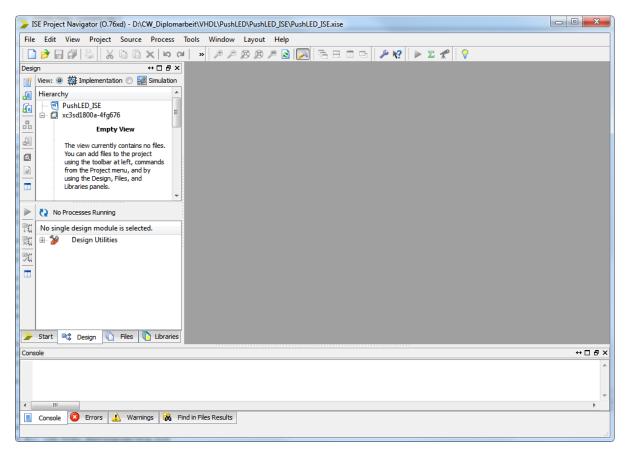

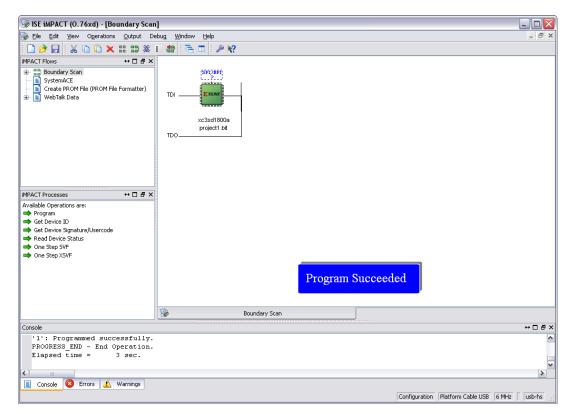

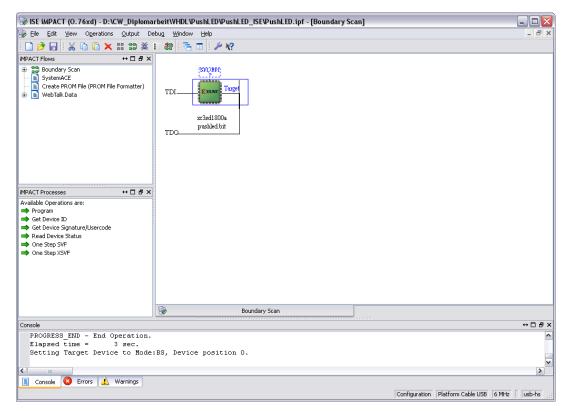

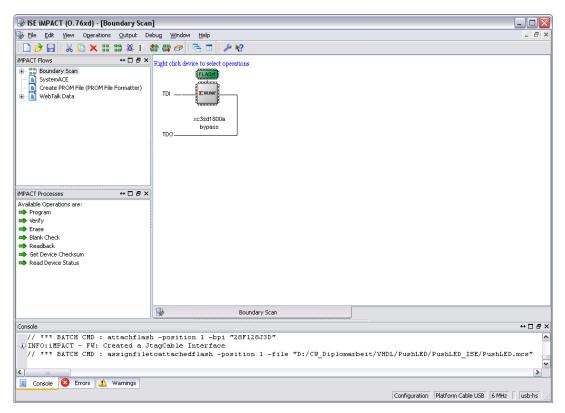

# 4.2.1 Two Processes per Entity