# Development of low power readout electronics for micro channel plate detectors with cross strip anodes for UV space observatories

### Dissertation

der Mathematisch-Naturwissenschaftlichen Fakultät der Eberhard Karls Universität Tübingen zur Erlangung des Grades eines Doktors der Naturwissenschaften (Dr. rer. nat.)

vorgelegt von

Marc Friedrich Pfeifer

geboren in Crailsheim

Tübingen 2014

Tag der mündlichen Qualifikation: 09.12.2014

Dekan: Prof. Dr. Wolfgang Rosenstiel

Berichterstatter: Prof. Dr. Klaus Werner

Berichterstatter: Prof. Dr. Josef Jochum

### Zusammenfassung

Der wissenschaftliche Fortschritt in der Astrophysik wird maßgeblich unterstützt durch Beobachtungen im ultravioletten (UV) Wellenlängenbereich des elektromagnetischen Spektrums. Die Erkenntnis über spezielle Eigenschaften astrophysikalischer Objekte ist allein durch Beobachtungen im UV möglich. Am Institut für Astronomie und Astrophysik in Tübingen (IAAT) werden neuartige, photonenzählende Mikrokanalplatten (MCP)-Detektoren entwickelt, um die wissenschaftliche Arbeit im ultravioletten Spektralbereich deutlich zu verbessern. Zusätzlich sind diese Detektoren unempfindlich im optischen Spektralbereich. Für den Einsatz der Detektoren in wissenschaftlichen Satelliten sind eine höhere Empfindlichkeit, eine längere Lebensdauer und eine geringe Leistungsaufnahme entscheidende Eigenschaften. Diese sind im Fokus der Arbeit am IAAT.

Im Rahmen dieser Dissertation wurde ein neuartiges Konzept für eine Elektronik zur Auslese der MCP-Detektoren untersucht und realisiert. Das Konzept ermöglicht die Erhöhung der Lebensdauer bei gleichzeitig geringer elektrischer Leistungsaufnahme. Die Schlüsselkomponente zur Realisierung des Konzeptes ist der Beetle Vorverstärker-Chip, welcher am Max-Planck-Institut für Kernphysik in Heidelberg für das LHCb-Experiment am CERN entwickelt wurde. Zur Steuerung und Auslese des Beetle Chip und weiterer elektronischer Komponenten wurde eine entsprechende Einheit in einem field-programmable gate array (FPGA) umgesetzt. Des weiteren wurde Steuer- und Analysesoftware implementiert. Für Tests der Ausleseelektronik wurden ein Gerät zur Ladungseinkopplung und ein Laboraufbau realisiert.

Die akkurate Verarbeitung von Signalen ähnlich denjenigen eines MCP-Detektors wurde durchgeführt. Komponenten, welche eine weitere Verbesserung der Ausleseelektronik hinsichtlich ihrer wissenschaftlichen Zielsetzung ermöglichen, wurden in Betrieb genommen.

Die korrekte Funktion einer weltraumtauglich realisierbaren Ausleseelektronik mit geringer Leistungsaufnahme wurde in dieser Arbeit gezeigt. Damit können MCP-Detektoren für zukünftige UV-Missionen gebaut werden, die einen bisher unerreichte Lebensdauer und Dynamik besitzen.

### Abstract

Scientific progress in astrophysics is strongly supported by observations in the ultraviolet (UV) wavelength regime of the electromagnetic spectrum. Insight into unique features of astrophysical objects is only possible in the UV. At the Institute for Astronomy and Astrophysics in Tübingen (IAAT), novel solar blind and photon counting micro channel plate (MCP) UV detectors are developed to improve scientific work in the UV significantly. For the application of the detectors in satellite observatories, enhanced sensitivity, longer lifetime and low power dissipation are crucial properties. These are at the focus of the work at IAAT.

In this thesis, a novel concept of low power readout electronics for the MCP detectors has been investigated and realized. The concept furthermore allows for an enhanced lifetime of the detectors. The Beetle pre-amplifier chip which was developed at Max-Planck-Institute for Nuclear Physics in Heidelberg for LHCb at CERN is the key component to realize the concept. To control and readout the Beetle chip and further electronic components, a corresponding unit was implemented in a field-programmable gate array (FPGA). Control and analysis software was furthermore implemented. For tests of the readout electronics, a charge injector device and a readout electronics laboratory setup were manufactured.

The accurate readout of signals that are comparable to signals from an actual MCP detector was performed. The commissioning of components to further improve the electronics setup in terms of the scientific constraints was carried out.

The proper function of a low power readout front-end electronics for MCP detectors that can be implemented space-qualified was shown in this work. It allows to build MCP detectors for future UV missions that have a so far unrivaled lifetime and performance.

# **Contents**

| Lis | st of | Figures                                                    | V          |

|-----|-------|------------------------------------------------------------|------------|

| Lis | st of | Tables                                                     | ix         |

| Int | trodu | ction                                                      | хi         |

| 1.  | Astr  | onomy in the ultraviolet spectral band                     | 1          |

|     | 1.1.  | Scientific topics and methods                              | 2          |

|     | 1.2.  | History and status of UV instruments and missions          | 10         |

|     | 1.3.  | Observational UV astronomy in the next decade              | 17         |

| 2.  | Mic   | ro channel plate UV detectors                              | 23         |

|     | 2.1.  | Overview of UV detection technology                        | 24         |

|     |       | 2.1.1. Micro channel plate based photoemissive detectors . | 26         |

|     |       | 2.1.2. CCDs: Photoconductive detectors for the UV?         | 40         |

|     | 2.2.  | ±                                                          | 44         |

|     |       | 2.2.1. ORFEUS-SPAS II wedge and strip anode detectors .    | 44         |

|     |       | 2.2.2. FUSE helical double delay line detectors            | 45         |

|     |       | 2.2.3. XSA MCP detector development at SSL Berkeley        | 46         |

| 3.  | IAA   | T cross strip anode MCP detector development               | 49         |

|     | 3.1.  | Detector concept                                           | 49         |

|     | 3.2.  | UHV facility                                               | 53         |

| 4.  | MCI   | P detector readout electronics                             | 63         |

|     | 4.1.  | Readout electronics concept                                | 64         |

|     | 4.2.  | The Beetle pre-amplifier chip                              | 68         |

|     | 4.3.  | Readout electronics setup                                  | 76         |

|     |       | 4.3.1. Beetle chip ceramics hybrid carrier board           | <b>7</b> 6 |

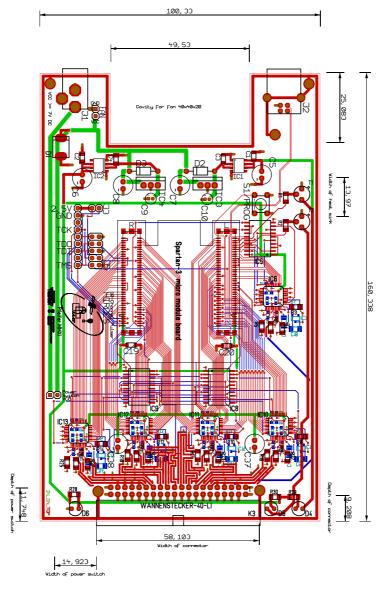

|     |       | 4.3.2. Front-end electronics FPGA board                    | 80         |

|     | 4.4.  | Virtex-4 FPGA VHDL firmware design                         | 87         |

|     | 4.5.  | Control and first-level analysis software                  | 94         |

### Contents

| 5.  | Read   | dout electronics tests and characterization                   | <b>103</b> |

|-----|--------|---------------------------------------------------------------|------------|

|     | 5.1.   | Test setups                                                   | 104        |

|     |        | 5.1.1. Description of the readout electronics setups $\dots$  | 104        |

|     |        | 5.1.2. Charge injector                                        | 108        |

|     |        | 5.1.3. Setup in the vacuum chamber                            | 117        |

|     | 5.2.   | Tests and characterization of the readout electronics $\dots$ | 118        |

|     |        | 5.2.1. Direct charge injection into a Beetle chip             | 120        |

|     |        | 5.2.2. Charge injection onto a wedge and strip anode          | 125        |

|     |        | 5.2.3. Simulations of the charge injection onto anodes        | 135        |

|     |        | 5.2.4. UV illumination of the vacuum chamber setup            | 139        |

|     |        | 5.2.5. Commissioning of XSAs and a Beetle CHC board .         | 147        |

|     |        | 5.2.6. Power consumption of the readout electronics setup     | 147        |

|     |        | 5.2.7. Discussion                                             | 148        |

| 6.  | Con    | clusion                                                       | 151        |

| Α.  | Tech   | nnical documentation                                          | 153        |

|     |        | MCP detector readout electronics                              |            |

|     |        | A.1.1. Virtex-4 FPGA board pin assignment                     |            |

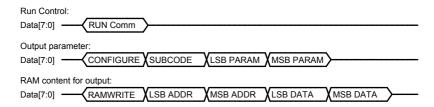

|     |        | A.1.2. Readout electronics commands and packet structure      |            |

|     | A.2.   | Charge injector                                               |            |

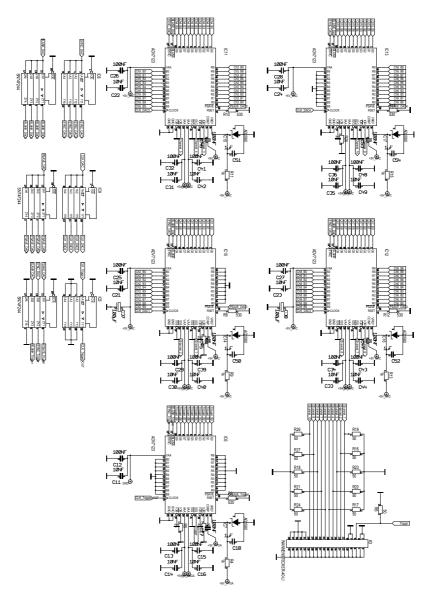

|     |        | A.2.1. Charge injector: schematics and PCB layout             |            |

|     |        | A.2.2. Charge injector: command encoding                      |            |

|     |        | A.2.3. Charge injector: event file structure                  |            |

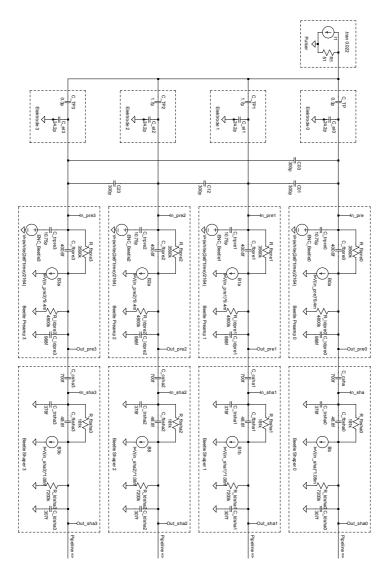

|     | A.3.   | SPICE Simulation Schematics                                   |            |

| Lis | t of   | Abbreviations and Glossary                                    | 179        |

| Bil | oliogr | raphy                                                         | 187        |

| Da  | nksa   | gung                                                          | 199        |

| Ве  | sond   | erer Dank                                                     | 201        |

# List of Figures

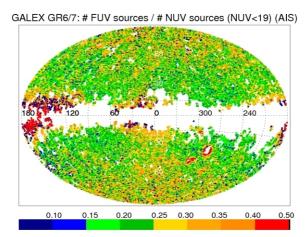

| 1.1.  | Distribution of bright and faint UV sources in the sky           | 3  |

|-------|------------------------------------------------------------------|----|

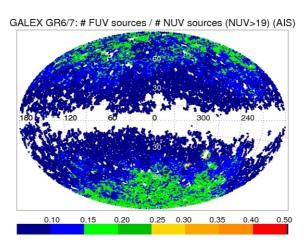

| 1.2.  | Time series of UV spectra of SAO 244 567                         | 7  |

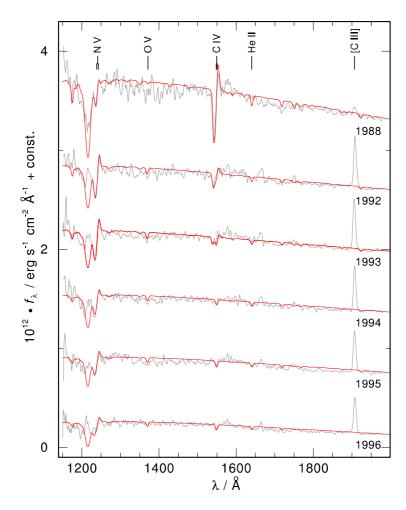

| 1.3.  | The Stingray Nebula                                              | 8  |

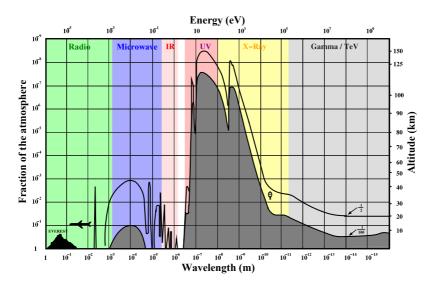

| 1.4.  | Atmospheric transmission of electromagnetic radiation            | 11 |

| 1.5.  | ORFEUS-SPAS II at the arm of the orbiter of STS-80               | 15 |

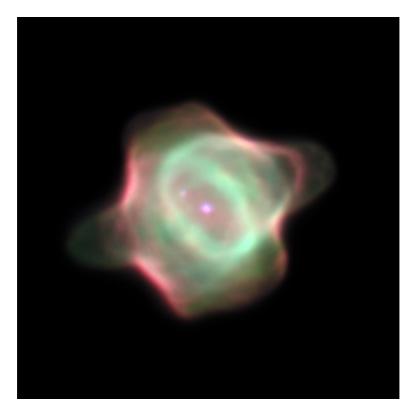

| 1.6.  | Model of the WSO-UV observatory satellite                        | 20 |

| 2.1.  | Architecture and operating principle of an MCP detector $$ .     | 27 |

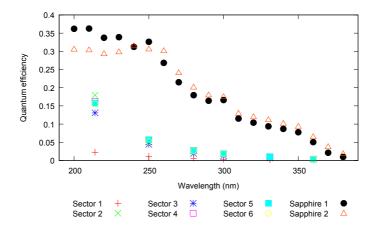

| 2.2.  | Quantum efficiency of alkali halide photocathodes                | 30 |

| 2.3.  | Quantum efficiency of diamond photocathodes                      | 32 |

| 2.4.  | Quantum efficiency of GaN photocathodes                          | 33 |

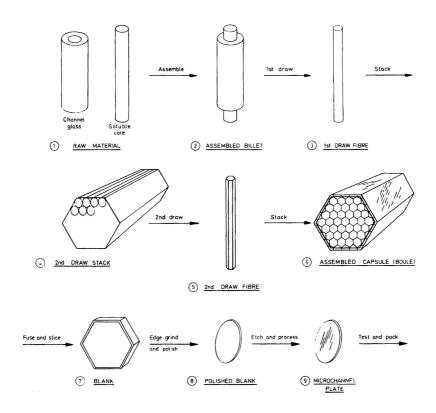

| 2.5.  | Micro channel plate manufacturing process                        | 35 |

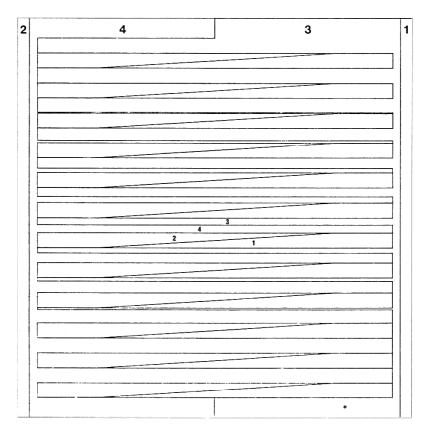

| 2.6.  | Wedge and strip anode                                            | 37 |

| 2.7.  | Helical double delay line anode                                  | 38 |

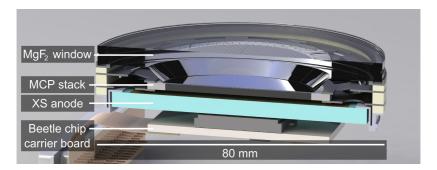

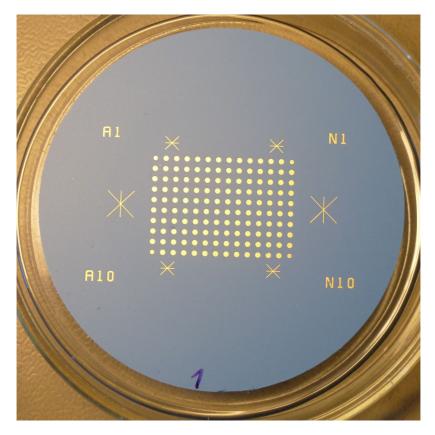

| 3.1.  | IAAT sealed tube detector design                                 | 50 |

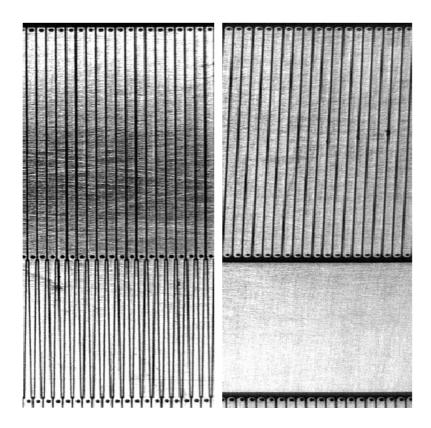

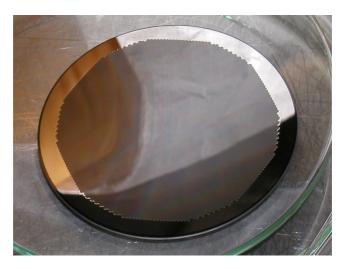

| 3.2.  | Micro channel plate                                              | 52 |

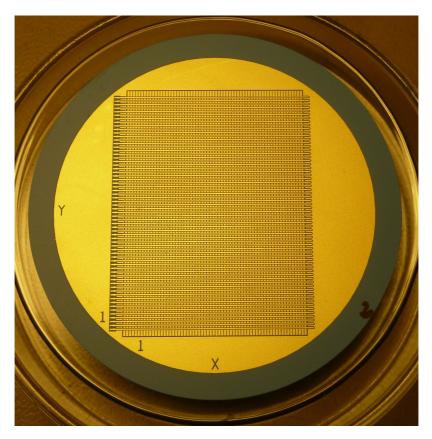

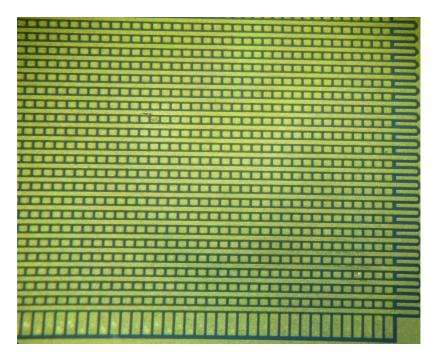

| 3.3.  | Cross strip anode: front view                                    | 54 |

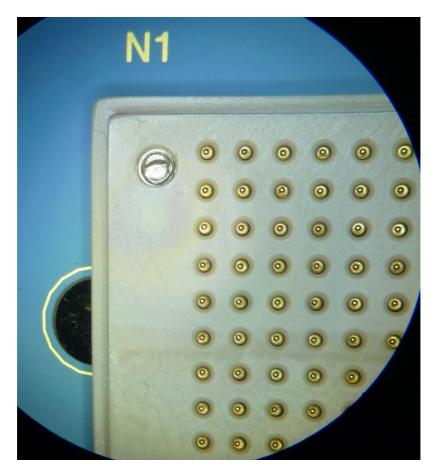

| 3.4.  | Cross strip anode: detail view                                   | 55 |

| 3.5.  | Cross strip anode: back view                                     | 56 |

| 3.6.  | Double-sided spring-loaded contact connector                     | 57 |

| 3.7.  | UHV facility: cross section                                      | 58 |

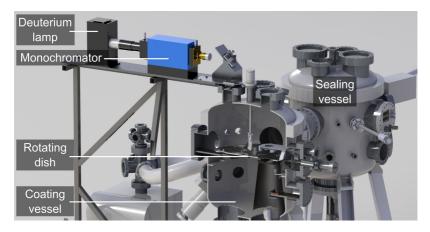

| 3.8.  | UHV facility: monochromator                                      | 59 |

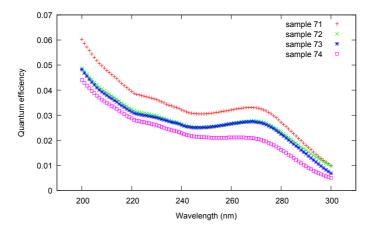

| 3.9.  | Quantum efficiency of CsTe photocathodes                         | 60 |

| 3.10. | Sealed diode body                                                | 62 |

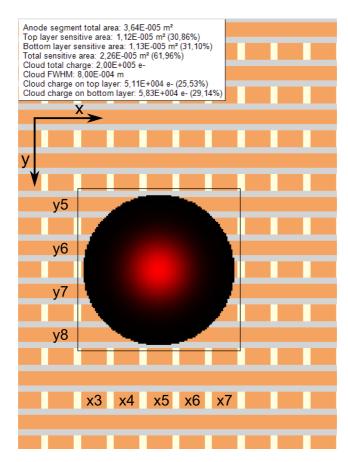

| 4.1.  | Illustration of an assumed charge cloud on an XSA                | 65 |

| 4.2.  | Charge distribution in the assumed cloud and on an XSA .         | 66 |

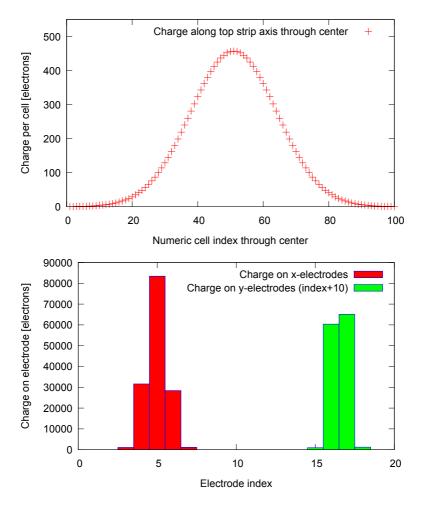

| 4.3.  | MCP detector readout electronics concept                         | 67 |

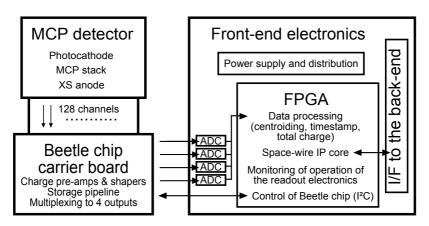

| 4.4.  | Functional schematic of the Beetle chip                          | 70 |

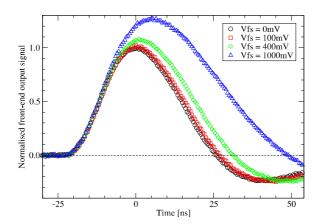

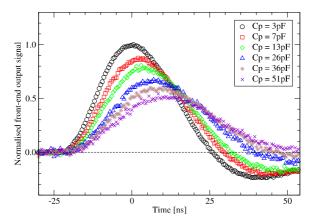

| 4.5.  | Beetle front-end output for different settings of $\mathit{Vfs}$ | 71 |

| 4.6.  | Beetle front-end output for different values of $C_p$            | 71 |

# List of Figures

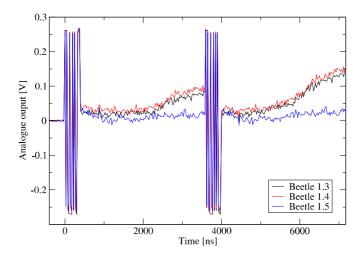

| 4.7.  | Baseline behavior for different Beetle chip versions 74                       |

|-------|-------------------------------------------------------------------------------|

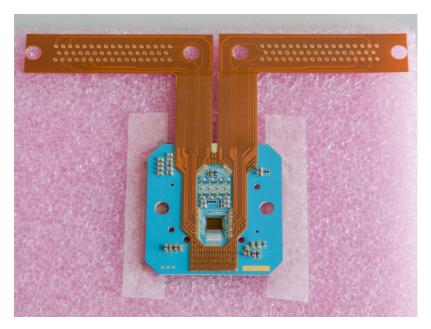

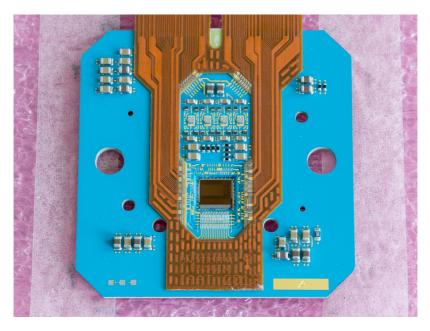

| 4.8.  | Beetle CHC board: overall view                                                |

| 4.9.  | Beetle CHC board: close up view 78                                            |

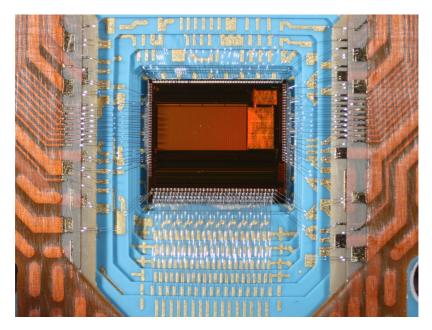

| 4.10. | Beetle CHC board: detail view                                                 |

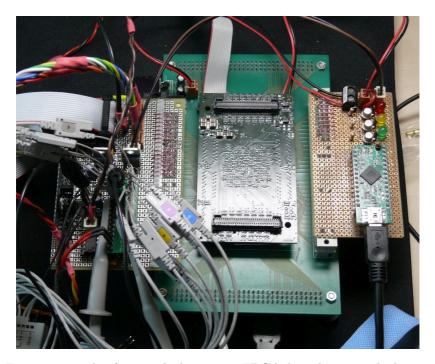

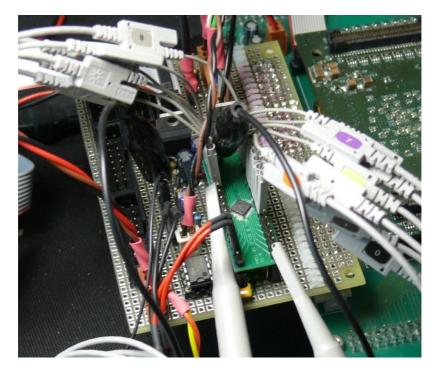

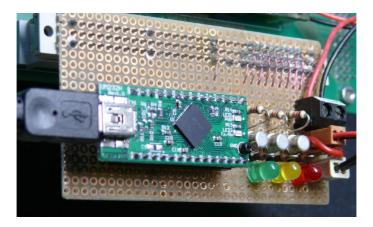

| 4.11. | Front-end electronics FPGA board setup 81                                     |

| 4.12. | FPGA micro module                                                             |

| 4.13. | Beetle interface and AD9649 ADC board                                         |

| 4.14. | USB interface board                                                           |

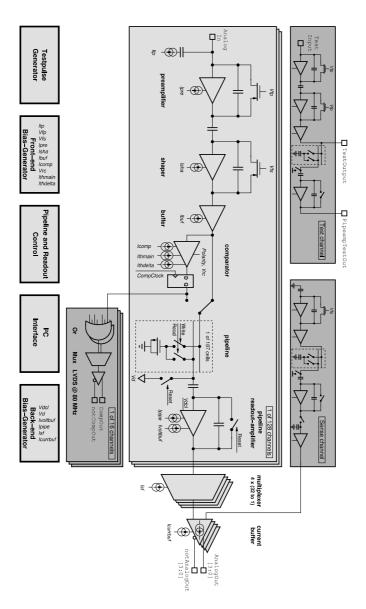

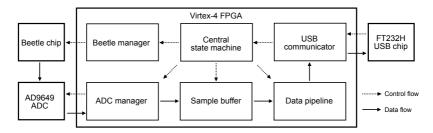

| 4.15. | $\tt Virtex-4\ VHDL$ firmware design: data and control flow $88$              |

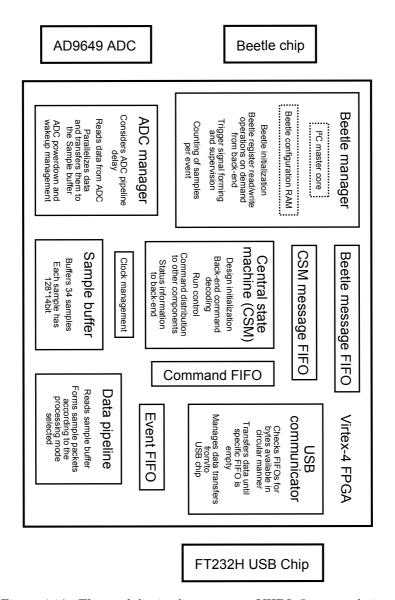

| 4.16. | $\label{limitex-4} \mbox{ Virtex-4 VHDL firmware design: module overview 90}$ |

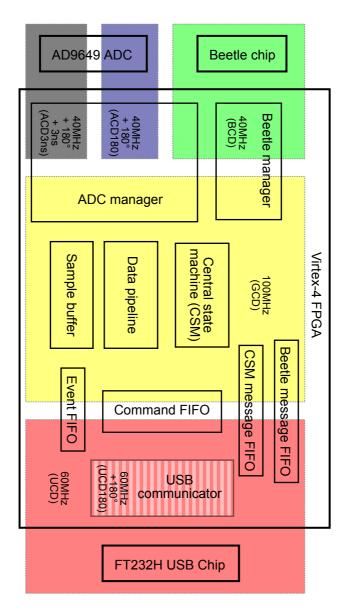

|       | $\tt Virtex-4$ VHDL firmware design: clock domain overview $$ . $93$          |

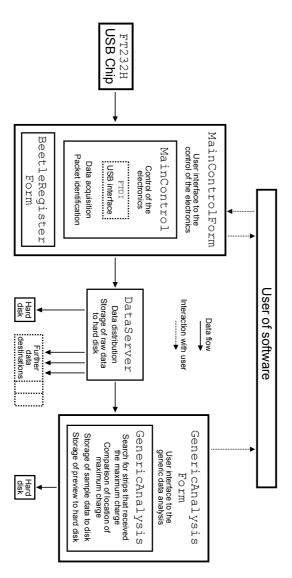

|       | Structure of the control and first-level analysis software $$ 96              |

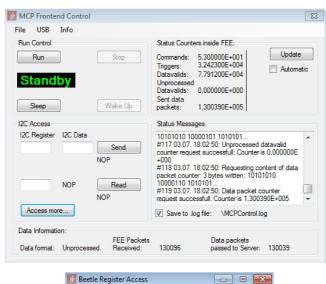

| 4.19. | Control software GUI                                                          |

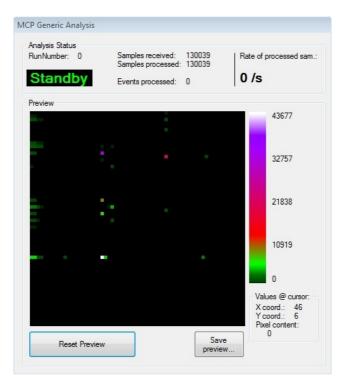

| 4.20. | First-level analysis software GUI $\ \ldots \ \ldots \ \ldots \ \ldots \ 101$ |

|       |                                                                               |

| 5.1.  | Initial readout setup                                                         |

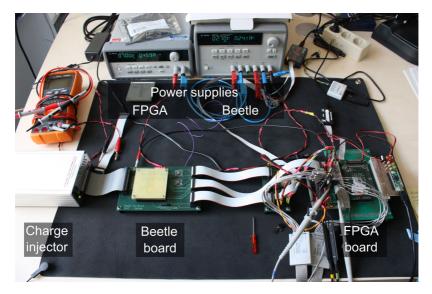

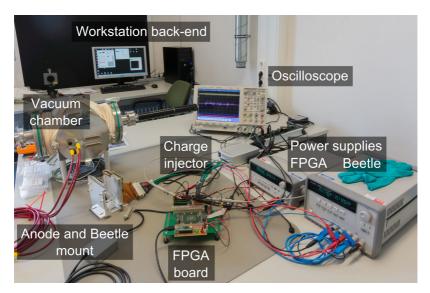

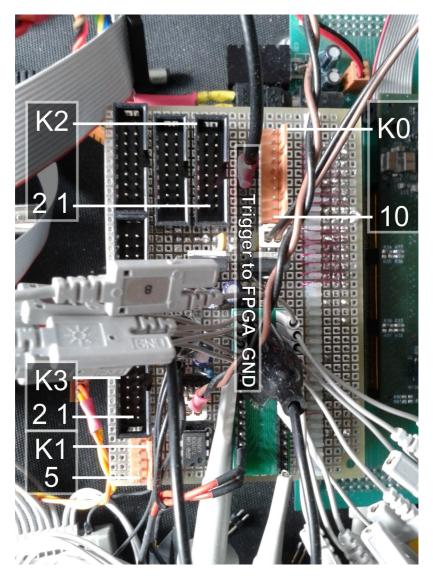

| 5.2.  | Readout electronics laboratory setup                                          |

| 5.3.  | Charge injector: overall view                                                 |

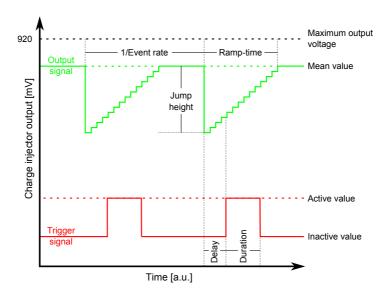

| 5.4.  | Charge injector: output shape and parameters $\dots \dots 112$                |

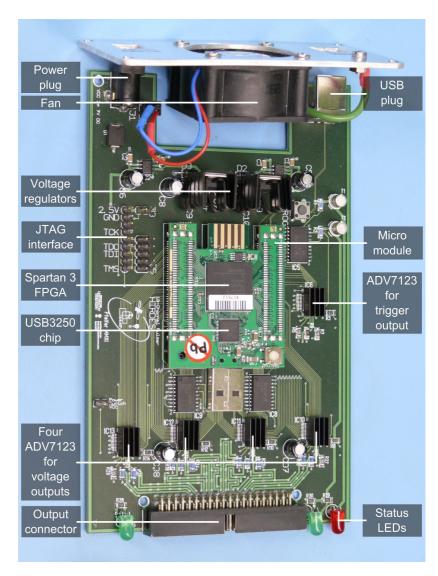

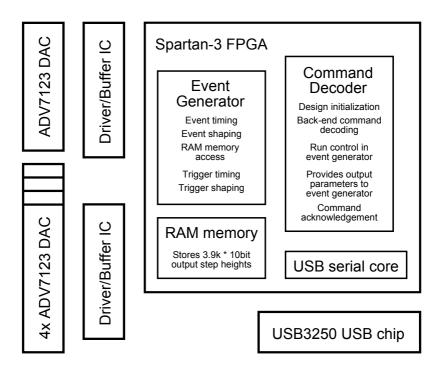

| 5.5.  | Spartan-3 VHDL firmware design: module overview $113$                         |

| 5.6.  | Charge injector control software GUI                                          |

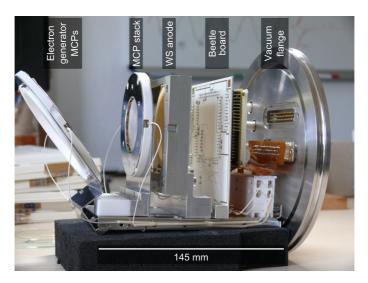

| 5.7.  | Setup in the vacuum chamber                                                   |

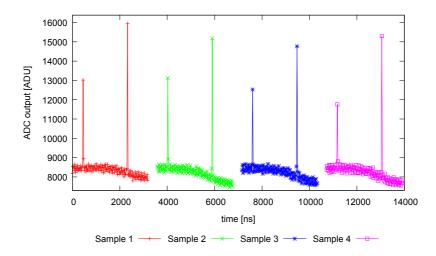

| 5.8.  | Initial setup: Beetle 1.3 readout sequence121                                 |

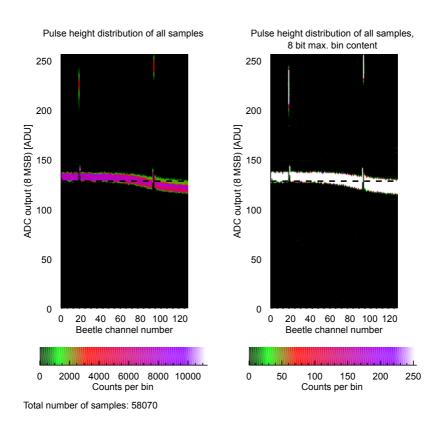

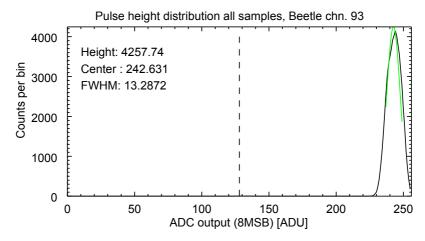

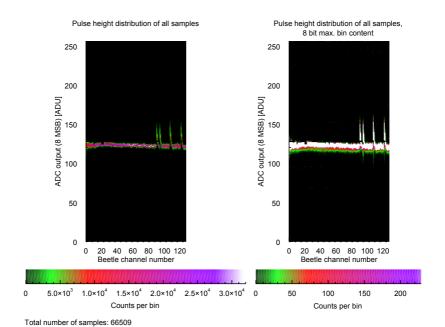

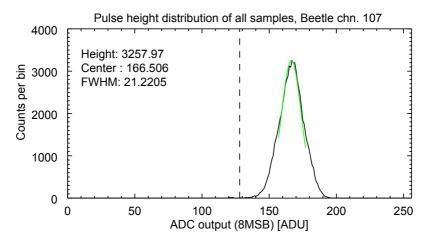

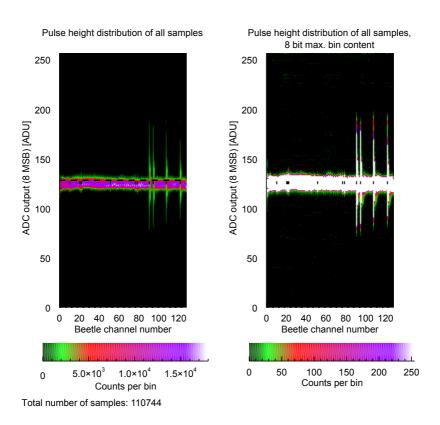

| 5.9.  | Initial setup: pulse height distribution (PHD), all channels . $122$          |

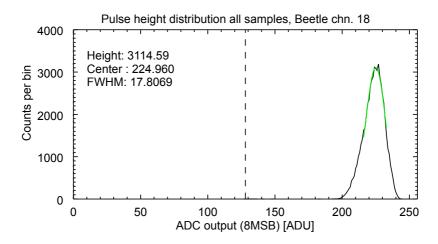

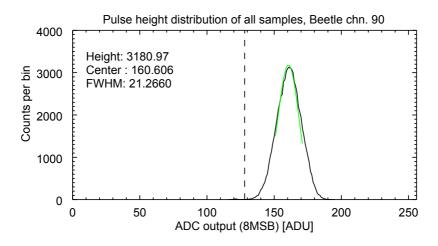

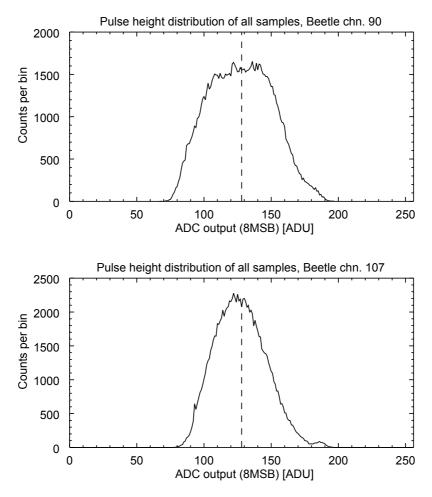

|       | Initial setup: PHD, two channels                                              |

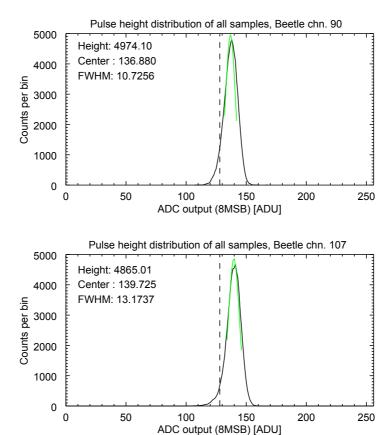

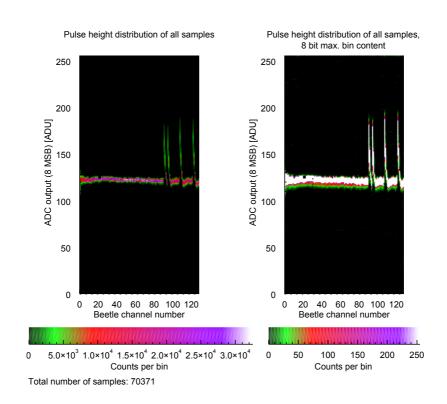

|       | $\mathrm{CI}(45)$ at WSA: PHD, all channels                                   |

|       | CI(45) at WSA: PHD, two channels                                              |

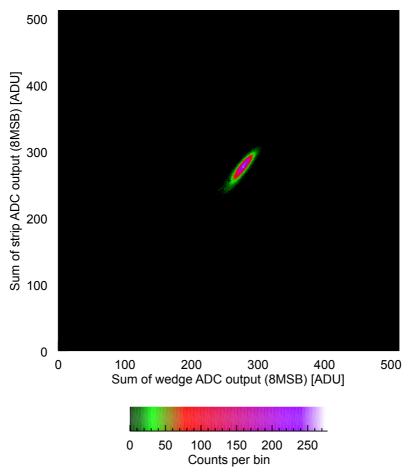

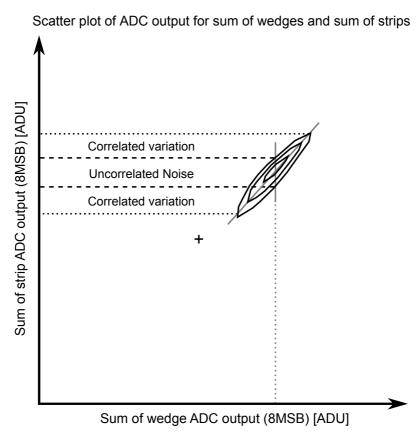

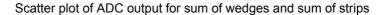

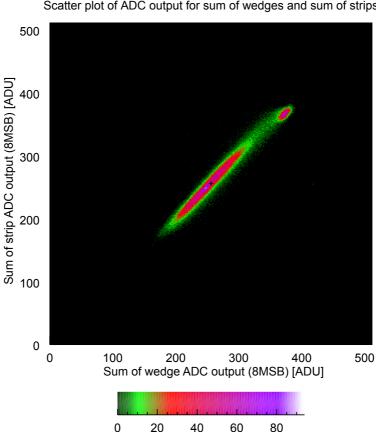

|       | CI(45) at WSA: scatter plot                                                   |

|       | Illustration of the distribution in the scatter plots $131$                   |

|       | CI(120) at WSA: PHD, all channels                                             |

|       | CI(120) at WSA: PHD, two channels                                             |

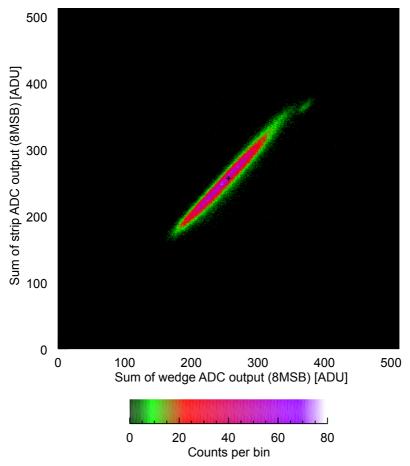

|       | CI(120) at WSA: scatter plot                                                  |

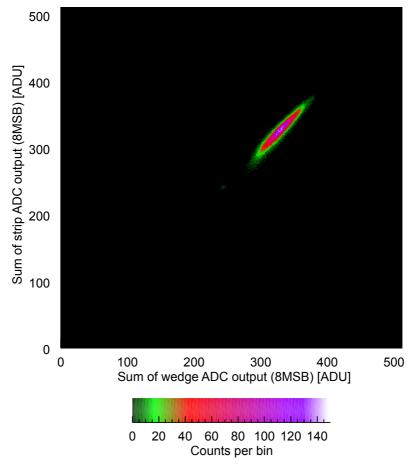

|       | SPICE simulation: charge injected in WSA $\dots \dots 136$                    |

|       | SPICE simulation: charge injected in one WSA electrode $$ . 137               |

|       | SPICE simulation: charge injected in one XSA electrode $138$                  |

|       | Schematic for the trigger generation from the HV $139$                        |

| 5.22. | MCP stack and WSA: PHD, all channels, UV Lamp on $$ 141                       |

| 5.23. | MCP stack and WSA: PHD, two channels, UV Lamp on 142                          |

# List of Figures

| 5.24. MCP stack and WSA: scatter plot, UV Lamp on               | . 143 |

|-----------------------------------------------------------------|-------|

| 5.25. MCP stack and WSA: PHD, all channels, UV Lamp off .       | . 144 |

| 5.26. MCP stack and WSA: PHD, two channels, UV Lamp off .       | . 145 |

| 5.27. MCP stack and WSA: scatter plot, UV Lamp off              | . 146 |

|                                                                 |       |

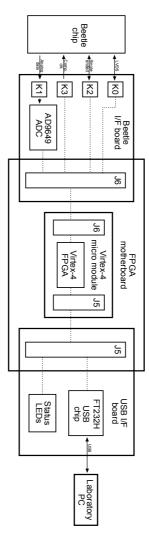

| A.1. Connection of the readout electronics boards               |       |

| A.2. Pin numbers of the $Beetle$ interface and $AD9649$ board . | . 155 |

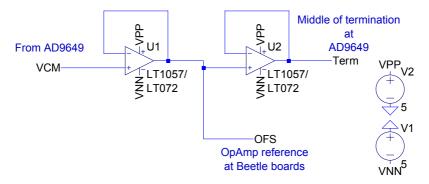

| A.3. Schematic of the AD9649 VCM OpAmp circuit                  | . 158 |

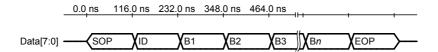

| A.4. Readout electronics packet structure                       | . 160 |

| A.5. Charge injector: connection scheme I                       | . 168 |

| A.6. Charge injector: connection scheme II                      | . 169 |

| A.7. Charge injector: PCB layout                                | . 170 |

| A.8. Charge injector: communication packet structure            | . 171 |

| A.9. Charge injector: event file structure                      |       |

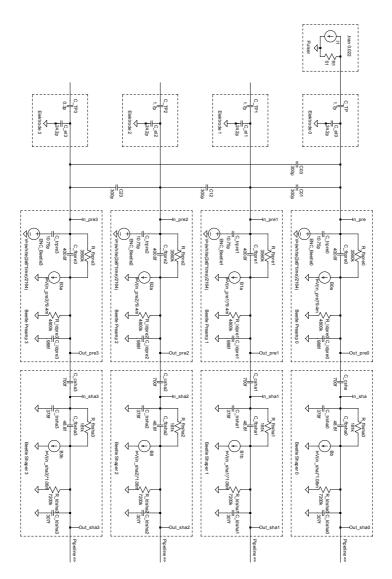

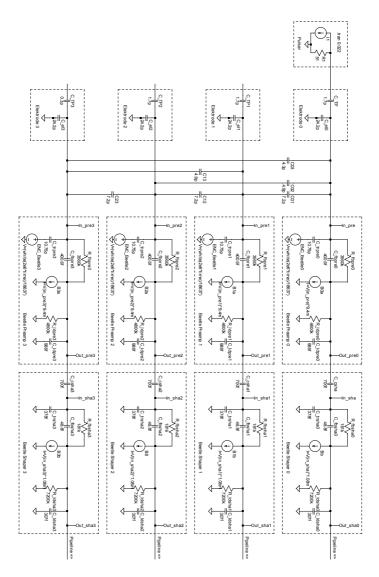

| A.10. SPICE schematic: CI at WSA at Beetle                      | . 176 |

| A.11. SPICE schematic: CI at one WSA electrode at Beetle .      |       |

| A.12. SPICE schematic: CI at one XSA electrode at Beetle .      |       |

# **List of Tables**

| 2.1. | UV detector performance comparison                       |

|------|----------------------------------------------------------|

| 4.1. | Virtex-4 FPGA resource utilization and timing 95         |

| 5.1. | Charge injector: output specifications                   |

| 5.2. | Parameters of the WSA test pulse electrodes 125          |

| 5.3. | Charge injected onto the WSA electrodes                  |

| 5.4. | Power consumption of the readout electronics             |

|      |                                                          |

|      | Beetle and trigger interface pin assignment              |

| A.2. | AD9649 ADC interface pin assignment                      |

| A.3. | AD9649 VCM OpAmp interface pin assignment 158            |

| A.4. | FT232H USB interface and status LED pin assignment $159$ |

| A.5. | Readout electronics commands: host to electronics 160    |

| A.6. | Readout electronics commands: electronics to host 162    |

| A.7. | Charge injector: commands                                |

| A.8. | Charge injector: configuration parameters 172            |

### Introduction

Astronomy is one of the oldest natural sciences. Ancient civilizations studied the motion of celestial objects and, despite the fact that the motivations were essentially religious or mythological, astronomical observations already have been used to establish calendars and to improve navigation. Astronomy as a mathematical science was established among the Babylonians however and was advanced in ancient Greece by the motivation to find physical explanations for celestial phenomena.

Astronomy today is the quantitative science of celestial observations and the underlying physical laws. The origin, physical properties, and the evolution of celestial objects in the Cosmos is at the focus of it.

The probes of astronomy are the particles and the radiation that stem from inside or the environment of celestial objects. Telescopes equipped with instruments like spectrographs, photometers, and imaging cameras are the experimental tools. Simulation of the physical conditions that are observed is the theoretical approach.

Astronomical observations of electromagnetic radiation from the Universe is possible in a wide energy range from below  $10^{-4}\,\mathrm{eV}$  in the radio band to above  $10^9\,\mathrm{eV}$  in the gamma regime. The ultraviolet (UV) spans the energy range from  $5\,\mathrm{eV}$  to  $100\,\mathrm{eV}$  which is usually expressed as a wavelength range of  $91.2\,\mathrm{nm}$  to  $300\,\mathrm{nm}$ .

UV astronomy covers a wide range of topics like the evolution of the Universe and its baryonic content, the physics of accretion and outflow in celestial objects, and the astrochemistry in the presence of strong radiation fields. UV observations are the only way to explore specific features of astronomical objects as resonance lines of the most important atoms and ions are located in the UV.

UV observations started in the late 1940s when unstabilized sounding rockets have been used to escape the atmosphere of Earth which blocks the UV radiation from the Universe. Spin-stabilization of the rockets and cold-gas reaction systems allowed for the observation of specific targets. However, the observation time was limited to a few hundred seconds. Satellites are used nowadays as platforms to observe the Universe in UV

### Introduction

light. They enable a longer observation time per target and a large number of targets that can be observed by the same instrument.

A variety of technologies were used on board of recent satellite observatory missions to acquire UV data. Progress was made during the last decades in the fields of detector efficiency, throughput, and lifetime of UV instruments. The progress was enabled by new gratings and coatings, novel detector configurations, and efficient readout electronics. Improved detector technology for UV observations is mandatory to expand the frontiers of scientific perception. For an application of detectors on future UV observatories, enhanced sensitivity, longer lifetime, and low power dissipation are crucial properties.

The development of novel photon counting, solar blind, and photon noise limited micro channel plate (MCP) detectors at the Institute for Astronomy and Astrophysics in Tübingen (IAAT) is a contribution to future astronomical UV space missions. The investigation of improved photocathode materials and a novel readout anode geometry are at the focus of research. The low power MCP detector readout electronics concept which was realized and tested in this work is a part of this development project at IAAT. It will allow to build MCP detectors for future UV missions that have a so far unmatched lifetime.

This doctoral thesis is organized as follows:

An overview of the questions that are addressed by observations in the ultraviolet spectral band is given in Chapter 1. Past and future instruments which are engaged by astronomers to answer these questions are described as well.

Chapter 2 gives an overview of technology that is available for UV observations with a focus on the micro channel plate detector concept and the components that have been applied in past and present realizations of MCP detectors. In Chapter 3, an MCP detector design that is investigated at the IAAT is described and its individual components are introduced. Details on an ultra-high vacuum facility for the production of photocathodes and the sealing of detector tubes are given.

The general readout electronics concept for this work is described in Chapter 4. The realized laboratory readout electronics and its components are introduced. Details on the specific function of the components are given. The Beetle chip and its architecture and function are discussed as well as details on the control and readout unit in the field-programmable gate array (FPGA). At the end of Chapter 4, the control and first-level analysis software is introduced.

Chapter 5 shows details on setups to test the readout electronics. In particular, a charge injector device and a setup in a vacuum chamber are introduced. Selected measurement runs and analyzed data to prove the proper function of the laboratory readout electronics are presented.

After a conclusion, the thesis ends with the Appendix where technical details in the form of schematics and pin tables of the readout electronics setup are given.

The motivation to perform astronomy in the ultraviolet (UV) wavelength band of the electromagnetic spectrum, is the fact that UV radiation interacts with matter in many physical conditions. Most of the resonance lines of atoms are excited in this energy domain. Simple ions have fluorescent transitions in this wavelength domain as well. Most molecules and atoms are photo-ionized or even photo-dissociated by ultraviolet radiation. Hence, as the UV radiation can be observed by astronomers, its interaction with the matter in the Universe and by this the properties of the matter itself can be investigated (Brosch et al., 2006).

Here we follow a convention stated by Werner (2010) for the limits of the ultraviolet spectral band: The UV band spans the wavelength range from 91.2 nm to 300 nm. The lower limit is the hydrogen Lyman absorption edge that shows up in observed spectra at 91.2 nm. Below this edge, the extreme ultraviolet (EUV) reaches down to 10 nm. Radiation that has wavelengths above 300 nm is accessible by ground-based telescopes while observations below 300 nm have to be performed outside the atmosphere of the Earth. This is the case because UV radiation is blocked by the ozone layer in Earth's atmosphere and hence a natural upper limit for the UV band is given. The UV band can be further divided into the far-UV (FUV) that spans from 90 nm to 200 nm, and the near-UV (NUV) between 200 nm and 300 nm. The wavelength range of the FUV and EUV below 200 nm down to 10 nm is often referred to as the vacuum-UV (VUV).

The work on the development of novel micro channel plate UV detectors at the Institute for Astronomy and Astrophysics in Tübingen is intended as a contribution to the improvement of the observation technology that will be used in the future to expand the scientific frontiers of UV astronomy. The development has been started with the aim to deliver detectors for the WSO-UV satellite observatory project which is discussed below.

This chapter gives an overview of the questions that are addressed by UV astronomy. The instruments utilized to answer these questions are described as well.

The following sections start with an introduction to the scientific topics

that modern UV astronomy is faced with and the methods that are used to deal with specific problems. In the second part of this chapter, an overview of the history and current status of UV missions and their instruments is given. The chapter ends with an outlook on the future of observational astronomy in the ultraviolet wavelength regime.

### 1.1. Scientific topics and methods

This section gives an overview of the scientific topics that modern UV astronomy deals with. Methods to answer the physical questions are introduced. The section presents a concrete example of the UV spectroscopic investigation of the central star in the Stingray Planetary Nebula and the modeling of its physical properties at IAAT. As far as not stated specifically, general information in this section is taken from the articles in Dopita et al. (2006).

Due to the fact that UV radiation interacts with matter in nearly every state, a huge amount of objects from different classes (see Figure 1.1) can be observed in the UV and hence a lot of phenomena can be explored in this spectral band. Gómez de Castro et al. (2006a) present three key fields of modern astronomy which are also key scientific issues to be addressed by the upcoming WSO-UV satellite observatory (see Section 1.3) (Gómez de Castro et al., 2009):

- The chemical evolution of the Universe and the diffuse baryonic content in the Universe

- The physics of accretion and outflow in astronomical objects

- The atmospheres of extrasolar planets and the astrochemistry in the presence of strong UV radiation fields

Further fields and classes of objects are stated by Gómez de Castro et al. (2006a) in addition to the key fields that are listed above:

• The Solar System. Data that are acquired in the UV and data that are acquired in other bands as well as the combination of these data sets is essential to understand the nature of the celestial bodies in our neighborhood and hence the evolution of the overall Solar System.

Figure 1.1.: Fraction of sources in the FUV (134.4 nm-178.6 nm) and NUV (177.1 nm-283.1 nm) bands from the all-sky imaging survey (AIS) by GALEX (Section 1.2). Top: sources brighter than  $m_{\rm AB}=19\,{\rm mag}$ , bottom: sources fainter than 19 mag in the NUV band. Brighter sources are dominated by hot stars in the Milky Way, fainter ones are extragalactic. Taken from Bianchi (2014), see also Bianchi et al. (2014).

- Star and stellar system formation. Most (65%) of the volume of the interstellar medium (ISM) is filled with diffuse gas at temperatures between 3000 K and 300 000 K. This gas is best observed in the UV. Absorption spectroscopy is the best tool to study the properties of circumstellar gas and the atmospheres of planets close to the central star that transit the stellar disk.

- Cool stars. The UV is unique to study their atmospheres.

- Massive stars. As the maximum of their spectral energy distribution is in the UV, it is the optimal spectral window to explore massive stars.

- White dwarfs, their structure and evolution as well as their interaction with the ISM. Far-UV spectra in the wavelength region between 122 nm and 200 nm are essential to determine the composition of white dwarfs and the evolution of their atmospheres. Imaging of the sky yields complementary information and is an important way to discover binary systems (Barstow and Werner, 2006).

- Interacting binaries in general. A large part of the interaction energy is released by radiation in the UV regime.

- Active galaxies have their maximum flux in the UV.

- Starbursts. The existence of one ore more initial mass functions (IMF)<sup>1</sup> and the form of the IMF, the possible modes of the star formation, and the interaction between massive stars and the ISM and intergalactic matter (IGM) can be explored.

- Supernovae.

In the following, details on selected key fields are given. Though they are mentioned as separate fields of research, they are strongly related and insight is most promising when they are all taken into account.

<sup>&</sup>lt;sup>1</sup>A function that describes the distribution of the initial masses in a population of stars.

The chemical evolution of the Universe. The chemical evolution of the Universe is driven by its enrichment of heavier elements that are produced in stars and released in supernova explosions at the end of their life time, distributed by stellar winds, or when planetary nebulae form at the end of the life of their solar-type progenitors. Hence, it is crucial to understand the life cycle of these stars to be able to comprehend the chemical evolution of the baryonic matter in the Universe. Simulations of the magneto-hydrodynamic turbulence in stellar atmospheres combined with data that are acquired in the UV are used to understand the thermal and dynamical evolution of the stars and diffuse gas in the Universe (Gómez de Castro et al., 2006a).

The interstellar matter is the raw material for star formation and the outcome of the star evolution process is the enrichment of the intergalactic matter with chemical elements heavier than those produced during the formation of the Universe. The warm gas of the ISM is best observed by the absorption of UV radiation in resonance lines of the elements in the gas. Many issues raise in this context that require attention. The structure of warm interstellar gas clouds and the consequences of the interaction of interstellar gas clouds are at the focus of discussion. Furthermore, it has to be determined in which way the ISM is influenced if star bursts occur in the proximity of the clouds. The theory of galaxy formation can be rechecked when one determines the portion of material in the local ISM that has its origin in a foreign region of the Galaxy (Linsky, 2009).

As the interstellar and intergalactic matter is the raw material for star formation, the mechanisms that cycle the gas from the ISM and IGM to feed the star and galaxy formation, respectively, have to be understood. The star formation rate is impacted by the efficiency of the gas transport mechanisms from and between the matter reservoirs. To track the overall evolution of the ISM and IGM, one has to establish a connection between the nearby and the early Universe. The early Universe can be observed in red-shifted UV wavelengths even via ground based telescopes. SNIa supernovae are consulted as standard candles to measure cosmic distances. The observation of more distant SNIa is necessary to determine distances in the even more early epochs of the Universe. It is only possible to identify Type I supernovae and distinguish them from Type II supernovae when taking their UV spectral distribution into account (Wamsteker et al., 2006).

The physics of accretion and outflow. Active Galactic Nuclei, white dwarfs that accrete matter, and T Tauri stars are examples for objects that transform energy of various form into corresponding other forms when they accrete matter from their surrounding. These energy forms can be potential energy, thermal energy, radiation, and magnetic energy for example. Furthermore, angular momentum has to be conserved and for example magnetic flux is built up during gravitational contraction (Gómez de Castro et al., 2006b, 2009).

The identification of the several possible interaction regions is the key to understand the phenomenon of accretion (Gómez de Castro et al., 2006a):

- In Active Galactic Nuclei and microquasars, FUV radiation is produced by an accretion disk.

- Where white dwarfs accrete matter, UV radiation is produced in the atmosphere of the accretion disk and the atmosphere of the white dwarf itself.

- In addition, UV radiation in T Tauri objects is produced in an extended magnetosphere.

Non-relativistic objects provide the best opportunity to study the accretion and outflow of matter in cosmic engines. To distinguish accretion and outflow in observations, the UV line profiles are the best footprint that is visible in the spectra.

For example, Figure 1.2 shows the time evolution of the UV spectrum of the central star of the so-called Stingray Planetary Nebula (SAO 244 567, Figure 1.3). The N v and C IV resonance lines display P Cygni profiles that are characteristic for a strong stellar wind. These lines almost vanished during one decade. By comparison with synthetic spectra which have been computed with appropriate stellar atmosphere models it could be shown that the mass-loss rate strongly decreased within this decade. This fact indicates an unusually fast evolutionary rate of the star that was probably caused by a re-ignition of helium-fusion in the white dwarf progenitor star (Reindl et al., 2014).

As the understanding of the underlying physics in accretion and outflow phenomena improves, new observations that employ instruments which are more sensitive and provide a better spatial and spectral resolution compared to current instruments are required (Gómez de Castro et al., 2006a,b).

Figure 1.2.: Time series of UV spectra of the central star of the Stingray Nebula (black lines) compared to model atmosphere spectra (red lines). The decreasing strengths of the N v and C IV resonance lines indicate a decreasing stellar wind mass-loss rate. The observations were obtained with IUE (Section 1.2). Taken from Reindl et al. (2014).

Figure 1.3.: Image of the Stingray Planetary Nebula (Hen-1357). The image was taken by the Wide Field and Planetary Camera 2 on board the Hubble Space Telescope. A bright central star (SAO 244 567) can be seen in the center of the image. The time evolution of its UV spectrum is shown in Figure 1.2. Gas bubbles expand to the lower left and upper right of the green ring. The red contours represent hot gas which is heated when the wind of the central star hits the walls of the bubbles. The colors indicate nitrogen (red), oxygen (green), and hydrogen (blue). The Stingray Nebula is the youngest known planetary nebula (Space Telescope Science Institute, 2014c).

Extrasolar planetary atmospheres and astrochemistry. In recent years, the field of exoplanetary research gained a large popularity among experts as well as the public. The reason for this is the fact that more and more planets in foreign star systems could be identified with increasingly powerful instruments. The research in this field revealed a large diversity in orbit-parameters, masses, atmospheric composition, and other planetary parameters. UV astronomy can contribute to this field of research as it provides powerful tools to astronomers. In particular, the footprint of absorption lines in the spectra of exoplanets that transit their host star are a powerful tool to explore the atmospheres of exoplanets and protoplanetary disks. In this context, insight into the shaping of planets and the impact of UV irradiation emitted by young stars onto the protoplanetary disks can be gained (Gómez de Castro et al., 2006a).

The process of planet formation in particular can not be investigated apart from other fields as for example the physics of the ISM and the physics of processes as accretion and outflow (Gómez de Castro et al., 2006b).

UV studies of the Solar System. The UV can also support the exploration of our cosmic vicinity. This field of science helped to understand the mechanisms that formed and still influence our home planet Earth. Studies of the atmospheres of Venus and Mars helped to understand the greenhouse effect and the consequences of the release of anthropogenic gases of which  ${\rm CO_2}$  is the most famous one. The strong greenhouse effect on Venus caused by  ${\rm CO_2}$  led to surface temperatures of up to 490 °C whereas a lack of a greenhouse effect on Mars has cooled its atmosphere to temperatures far below zero.

The composition of other planetary atmospheres in the Solar System besides the atmosphere of Earth indicates the origin of the planets, their unique evolution, and furthermore the evolution of the complete Solar System. The study of local atmospheric phenomena and the interaction of the atmospheres with the magnetic environment are further fields of interest.

Also the smaller bodies in the Solar System can be explored using UV radiation. In comets that originate from the outskirts of the Solar System, water dissociation products can be observed while the composition of the solid nucleus of comets is of further interest. In this context, the influx of

interstellar material into the Solar System may be important for planetary evolution in general.

Finally, planetary surfaces, the nuclei of the giant planets and the rings of planets can be explored by planetary mineralogy. This field can be expanded to the UV when it is supported by laboratory programs that characterize the possible minerals in the UV spectral region. As the transport of condensable gases is controlled by seasonable effects, a facility to monitor for example the rings of the giant planets in the UV could be installed (Brosch et al., 2006).

### 1.2. History and status of UV instruments and missions

This section shows the historic development of UV observations. An overview of past end present observatory missions is given and the instruments employed are introduced. As the UV radiation that is emitted from the various classes of sources in the Universe is blocked in the upper layers of Earth's atmosphere, UV observations were only possible as soon as technology to leave Earth's atmosphere was available (see Figure 1.4).

Rockets have been used as platforms that carried UV instruments to high altitudes in the beginning of observational UV astronomy in the late 1940s. A few hundred seconds of observational time were possible in this way. As the technology of satellites evolved afterward, longer observational periods per target were possible and far more targets could be observed with each instrument. Nowadays, satellites are the platforms that enable instruments to observe over years while rockets are used seldom and rather as a technology qualification platform.

At the time of this thesis, only a small number of UV instruments is in operation with limited observing capability or an only small remaining lifetime of the satellite that carries the instrument in the order of few years. New observatories and improved instruments are necessary to ensure that observational UV astronomy can contribute to deepen our understanding of the Universe in the future.

This section gives a brief overview of the history of scientific observations in the UV spectral band. An overview of the status of current instruments in orbit that are capable of UV observations is given. The last section of this chapter gives an outlook on candidates for future UV observatories.

Figure 1.4.: Transmission of electromagnetic radiation of different wavelength bands in the atmosphere of the Earth. The Figure shows 50% and 1% transmission curves depending on the wavelength (energy) and the height above sea level (remaining fraction of Earth's atmosphere). More then 50% of the original UV light from the Universe can be observed only at altitudes of more then 150 km above sea level. Reproduced by T. Schanz from Giacconi et al. (1968).

### History of observational UV astronomy

**Sounding rockets.** In the late 1940s, first UV observations have been performed outside the atmosphere of Earth. The instruments had been installed on sounding rockets that did not have any guidance and stabilization and for this had a pure ballistic trajectory with a pointing that was arbitrary. The first UV instrument was flown by Hulburt und Tousey from the American Naval Research Laboratory on a German V2 rocket. The observations that have been performed in the following years were UV photometric programs (Tousey, 1967; Wilson and Boksenberg, 1969).

The first spectrophotometric observations in the UV band have been performed by Stecher and Milligan (1962). They used a spectrometer that scanned the sky and was flown in a spin-stabilized but unguided Aerobee rocket. The peak altitude of the flight trajectory was 172 km. Scientific data was acquired in the wavelength range from 160 nm to 400 nm. The data suffered from an instrument anomaly during the first flight that was then absent in the following flights.

To be able to perform observations of specific regions of the sky and single objects, Morton and Spitzer (1966) used a cold-gas jet reaction system to orient the Aerobee rocket. Furthermore, they added a fine stabilization system which made an instrument stability of  $\pm~20''$  and a spectral resolution of about 0.1 nm possible.

**First satellites.** To overcome the problem of a limited observation time and a small number of targets that could be observed per flight, the installation of UV instruments on satellites as soon as these were available was the logical consequence. The first UV instrument on board of a satellite was a photometer used by Smith (1967) in the unstabilized US satellite 1964 83C.

The most important breakthrough in the technology to support scientific observations in the UV was a series of stabilized satellites of which Orbiting Astronomical Observatory-2 (OAO-2) Stargazer was the first successful one. Watts (1969) and Code et al. (1970) published first results from the experimental packages on board of OAO-2. First high-resolution UV-spectra were acquired on-board of OAO-3 Copernicus via the 80 cm primary mirror of the Princeton Experiment Package with a spectral resolution of  $5 \times 10^{-3}$  nm in the range between 95 nm and 145 nm (Rogerson et al., 1973; Snow, 1975).

**IUE.** The International Ultraviolet Explorer (IUE) was an astronomical satellite that was launched in 1978 and was a joint venture of ESA, NASA and UK. It provided the opportunity for guest observers to make real time observations which made IUE the first observatory type satellite in the current sense. IUE had an extraordinarily long operational time until 1996. During this 18 years of lifetime it returned more than 30 000 spectra of more than 9000 targets with a brightness range that spanned 10 orders of magnitudes. Two echelle spectrographs recorded spectra that have a resolution  $R = \lambda/\Delta\lambda$  of up to  $1.8 \times 10^4$  in the wavelength range between 115 nm and 320 nm. They were served by a 45 cm mirror (European Space Agency, 2014).

ORFEUS. Kappelmann et al. (1990) introduced the science that would be possible with the Orbiting Retrievable Far and Extreme Ultraviolet Spectrometers (ORFEUS) (Grewing et al., 1998; Space Telescope Science Institute, 2014d). This project was a follow-on project to a German/US collaboration where a 1 m telescope was flown on an American ARIES rocket (Grewing et al., 1981). Mandel et al. (1994) presented the first results of the ORFEUS instruments which have been a US Rowland and a German Echelle spectrograph. They were served by a 1 m telescope. The telescope and instruments were manufactured by Kayser-Threde GmbH (now: OHB System AG). The instruments were integrated into the retrievable free-flying platform ASTRO-SPAS. ASTRO-SPAS was built by Messerschmitt-Bölkow-Blohm (now a part of EADS) and was managed by the DARA (Deutsche Agentur für Raumfahrtangelegenheiten, today: DLR, German for: German Aerospace Center). It was launched into orbit four times, of which ORFEUS was on-board for two flights.

On each flight, ASTRO-SPAS was transported into its orbit by the Orbiter of the Space Shuttle Transport System (STS)<sup>2</sup> and then deployed into space via the robotic arm of the Orbiter. After a free flight mission phase of up to 14 days, it was retrieved by the shuttle crew and brought back to the Earth. The free-flight of ORFEUS mission I in the year 1993 (STS mission 51) lasted 6 days. During this flight, ORFEUS recorded more than 100 stellar spectra in the range 39 nm-120 nm via the US

<sup>&</sup>lt;sup>2</sup>Also known as NASA's manned Space Shuttle Program. It lasted from 1981 to 2011. The Space Shuttle Orbiter could carry four to seven astronauts and launched vertically attached to an external tank and solid boosters. 135 missions have been flown of which two have been lost in 1986 and 2003.

spectrometers. The second flight of ORFEUS was part of Space Shuttle Orbiter Columbia's mission STS-80 in 1996 and the free-flight phase of ORFEUS-SPAS II lasted 14 days (Figure 1.5). The spectral range of the German FUV Tübingen Echelle Spectrograph was  $90 \, \mathrm{nm}$ -140 nm with a resolution R of better than  $10 \, 000$  during the second flight (Barnstedt et al., 1999). See Section 2.2.1 for details on the wedge and strip anode micro channel plate detectors that have been designed and built in Tübingen for the FUV channel of ORFEUS.

**FUSE.** Following ORFEUS, among others, Far Ultraviolet Spectroscopic Explorer (FUSE) was a further scientific satellite that was on a permanent orbit. FUSE acquired high-resolution ( $R=20\,000$ ) spectra in the far-UV band from 91 nm to 118 nm. It used four mirror segments instead of one where two mirrors each were coated to operate in a defined bandpass. Siegmund et al. (1994, 1997) at the Space Science Laboratory of the University of California in Berkeley developed the delay line micro channel plate detectors that had been used in the spectrographs on board of FUSE (see Section 2.2.2 for details on the detectors). After the launch of the satellite in 1999, FUSE performed more than 6000 observations. FUSE was decommissioned in 2007 after the failure of the pointing-system of the satellite bus (Moos et al., 2000; Kaiser and Kruk, 2009; Space Telescope Science Institute, 2014a).

**GALEX.** Launched in April 2003 on a Pegasus rocket, the Galaxy Evolution Explorer (GALEX) was a sky survey satellite that performed the first UV all-sky survey beyond our Galaxy in two bands (135 nm-175 nm and 175 nm-275 nm) with a primary mirror of 50 cm. The surveys of GALEX were different in the amount of sky coverage and exposure time for a single pointing. The latter one included also the focusing on single nearby galaxies. During the baseline mission as well as during the legacy surveys that have been performed after the extension of the mission lifetime in 2006, low-resolution (R=100-200) spectroscopic surveys have been performed besides the imaging surveys as well. Figure 1.1 in the previous section shows the distribution of UV sources that have been identified by GALEX. GALEX was decommissioned in June 2013 (Martin et al., 2005; Morrissey et al., 2005; GALEX science team at California Institute of Technology, 2014).

Figure 1.5.: ORFEUS-SPAS II at the arm of the orbiter of STS-80. The Tübingen Echelle Spectrometer is attached to the 1 m ORFEUS telescope in the center of the platform ASTRO-SPAS. On the right side of the platform, the Interstellar Matter Absorption Profile Spectrograph (IMAPS) of the Princeton University is mounted. Photograph from IAAT archive.

### Current instruments that perform observations in the UV

The Hubble Space Telescope (HST) is a joint mission of ESA and NASA. Its primary mirror has a diameter of 2.4 m. In April 1990, HST was deployed by the crew of the Space Shuttle Mission STS-31. It was maintained by the crews of five further Space Shuttle servicing missions in the years from 1993 to 2003. Currently, HST carries six scientific instruments whose observation capability spans a wavelength range from the UV to the infrared. These instruments are three spectrographs, two imaging cameras and the fine guidance sensors that can be used for astrometry as well. The Space Telescope Imaging Spectrograph (STIS) is able to perform two-dimensional spectroscopy in the range from 105 nm to 1000 nm and has a camera mode furthermore. It was installed on the 10day second servicing mission (STS-82) in 1997. In 2004, the power supply of STIS failed and there was no UV instrument available at all until a third servicing mission in 2009 when STIS was repaired. During this mission (STS-125), the Cosmic Origins Spectrograph (COS) was installed on HST as an additional instrument. Its purpose are spectrographic observations of faint objects that are possible due to the high sensitivity of COS. COS can perform moderate and low-resolution spectroscopy in the range from 115 to 320 nm (Space Telescope Science Institute, 2014b).

**OM und UVOT.** Besides the instruments on HST there are, at the moment, only two more, though very similar, space-based instruments in operation that have the capability to perform UV observations: the Optical and UV Monitor (OM) on-board the XMM-Newton X-ray observatory (Mason et al., 2001; Talavera, 2009) and the Ultra-Violet/Optical Telescope (UVOT) on-board the Swift Gamma-Ray Burst Mission (Roming et al., 2005; Roming et al., 2009). Both telescopes have a 30 cm aperture and a spectral response from 180 nm to 600 nm and 160 nm to 800 nm, respectively. However, OM has a higher spatial resolution while UVOT has a higher throughput. Due to the fact that these instruments are co-aligned to the main instruments of their host observatory, their purpose is in general to expand the wavelength coverage of the observations that are performed by the particular main instrument. Hence, they are no true alternative to the instruments that are installed on space observatories that are intended for observations in the UV range specifically. In addition, they have a small aperture and a missing capability to cover the FUV.

### 1.3. Observational UV astronomy in the next decade

After a shutdown of the HST around the year 2020 at the latest, new UV space astronomy missions are required urgently. In any case, the community of UV astronomers is facing years and possibly even decades where no adequate scientific instruments for observations in the UV wavelength band are available. In this section, an overview of the general requirements for future UV observatories that have been expressed by several members of the UV community is given. A brief look on the applicability of alternatives to UV satellite observatories is also taken. After that, a selection of proposed future UV observatories is illustrated. Finally, the World Space Observatory UltraViolet (WSO-UV) is described in more detail as one of the most promising candidates for a future access to observations in the UV with a launch scheduled for 2019 (Sachkov et al., 2014a, Talk at conference).

### Requirements for future UV instruments and missions

Throughput is the most important technology driver for observational astronomy and for UV astronomy in particular to raise the signal statistics of observations. This implies improvements in the fields of detector area, optical components and and their coatings as well as in the development of big light-weight mirrors (Kappelmann and Barnstedt, 2006).

Solar blind detectors and solar blind imaging systems in general are required to reduce the huge background in the optical wavelengths that are emitted by many astronomical objects. See Section 2.1 for more details on UV sensors and photocathodes.

Requirements for the performance of future space-borne instruments depend on the specific science case. Kappelmann and Barnstedt (2006) summarize that most of the current science questions can be faced by a 3 m-4 m class telescope and two types of spectrographs with high throughput. These two spectrograph types are:

- 1. A spectrograph with high spectral resolution of  $R = \lambda/\Delta\lambda$  between 50 000 and 100 000 in the wavelength range of 90 nm to 350 nm

- 2. A spectrograph with medium spectral resolution ( $R \sim 1000$  to 5000) that is capable to perform integral field spectroscopy with a spatial resolution of  $\sim 0.01''$  and a wavelength coverage of 90 nm to 450 nm

### Alternative approaches to space UV observatories

Modern astronomy requires space-borne instruments to meet scientific requirements. These observatories are rather expensive and require long phases of design and planning. There are several suggestions of UV observational locations different than the low Earth orbit that is usual for UV satellite observatories. On this locations, observatories could possibly be realized significantly cheaper on the first glance. Brosch (2009) analyzed Antarctic astronomy, balloon-borne UV astronomy, and moon-based UV observations. He concluded that there is no true alternative to space observatories in the future.

### UV space observatories announced for the near future

Only a small number of missions is proposed at the moment that will be capable to perform observations in the UV during the next decade. After a failure of HST, the community of UV astronomers might face an age of observational darkness if the international community will not be successful to initiate a further mission. Two selected proposals for future UV observatories are presented in the following as examples. Though, the only UV satellite that is in the implementation phase at all is the Russian-led WSO-UV mission. It is discussed in more detail in the next section.

ASTROSAT is the first satellite of India's Space Research Organization (ISRO) that is dedicated to astronomy. It will carry several payloads. The UltraViolet Imaging Telescope (UVIT) is one of them. It is a twin 38 cm-aperture UV instrument and will perform simultaneous imaging in the range from 130 nm to 300 nm in two ultraviolet channels and one optical channel in the wavelength range from 320 nm to 530 nm with an angular resolution of up to 1.8". The launch of ASTROSAT is scheduled for 2015 (Inter-University Centre for Astronomy and Astrophysics, 2012; Hindu, 2014).

The Canadian Space Agency (CSA) proposed a UV/optical space telescope that is called CASTOR. The 1 m primary mirror of CASTOR would provide nearly diffraction-limited imaging in a field of view that is a factor 200 larger than that of ACS or WFC3 on HST. The focal plane is divided into three sections for a broad UV band from 150 to 300 nm and two blue-optical bands (Côte et al., 2012; Côte and Scott, 2014).

## The World Space Observatory-Ultraviolet (WSO-UV)

The World Space Observatory-Ultraviolet is the most promising candidate for a 2 m-class space UV telescope in the next decade (Sachkov et al., 2014b; INASAN, 2014)

WSO-UV is a cooperation of an international consortium that is led by the Federal Space Agency of Russia (ROSCOSMOS). The mission and scientific operations will be coordinated by Russia and Spain. The science program is planned to comprise a core scientific program, an open program for projects from the international community, and a funding bodies program for the partners in the project consortium. The nominal lifetime is planned to be 5 years with an optional extension to 10 years.

The satellite bus is the Russian NAVIGATOR platform that was used already for the radio satellite Spektrum-R<sup>3</sup> and will be used for Spektrum-RG<sup>4</sup>, a high-energy astrophysics observatory satellite, as well. The satellite bus of WSO-UV will carry a 1.7 m-aperture telescope (see the model in Figure 1.6) and instruments to carry out high resolution and long-slit low resolution spectroscopy as well as imaging. WSO-UV will be launched from Baikonur (Kazakhstan) in 2019 (Sachkov et al., 2014a, Talk at conference).

WSO-UV will carry three scientific instruments:

- A far UV high resolution echelle spectrograph with a resolution of  $R\sim 50\,000$  in the range between 115 nm and 176 nm

- A near UV high resolution echelle spectrograph with a resolution of  $R\sim50\,000$  in the range between  $174\,\mathrm{nm}$  and  $310\,\mathrm{nm}$

- A long slit spectrograph to perform long slit spectroscopy with a low resolution of  $R\sim10\,000$  in the 115 nm-305 nm band and a spatial resolution of 0.5''

The original design for the spectrographs was performed by Kappelmann et al. (1995, 2006); Kappelmann et al. (2009); Hermanutz et al. (2012). This design, called the High Resolution Double Echelle Spectrograph

<sup>&</sup>lt;sup>3</sup>Also called Radioastron. Russian satellite observatory to perform observations for radio astronomy. It was launched in July 2011 (RadioAstron Science and Technical Operations Group, 2014).

<sup>&</sup>lt;sup>4</sup>International high-energy astrophysics satellite under Russian leadership. The launch is scheduled currently for 2016.

## 1. Astronomy in the ultraviolet spectral band

Figure 1.6.: A model of the WSO-UV telescope exhibited during "Space Week" in Madrid (Kolotilov, 2011).

## 1.3. Observational UV astronomy in the next decade

(HIRDES), incorporated micro channel plate detectors (see next chapter) manufactured at IAAT in the instrument. Meanwhile, it is planned to equip the spectrographs on WSO-UV with cooled CCDs (Shugarov et al., 2014).

The imagers are a multi-purpose instrument to carry out imaging and slitless spectroscopy. This instrument will be equipped with two micro channel plate detectors that employ CsI and CsTe photocathodes (see 2.1).

After a look onto UV astronomy in general as well as on the history and status of UV instruments, this chapter focuses on certain UV detector technologies that are applied in the scientific instruments.

In a scientific instrument, the detector determines the feasibility of certain astronomical research projects for a given aperture. The improvement of existing technologies and the establishment of new detector techniques is the main focus of hardware research in UV astronomy.

A variety of detector types and technology is available to detect UV radiation. It's goal is to convert the UV radiation into electrical signals that are processed, stored, and sent to ground for further scientific exploration. Each detector type consists of a specific combination of certain technologies. This chapter will give a brief overview of advantages and disadvantages of certain UV technologies.

At the Institute for Astronomy and Astrophysics Tübingen (IAAT), research on one detector type, called a micro channel plate (MCP) UV detector, in combination with a cross strip anode readout, is conducted. MCP UV detectors have a history of successful applications in several observatory programs in the past. The research on MCP detectors at the IAAT is based on the heritage from detector contributions to missions on ARIES rockets and in the German instrument of ORFEUS. Photocathodes are at the focus of research as a means to raise the efficiency of the photon detection process. A cross strip anode readout is an innovation to raise the spatial resolution and the lifetime of a micro channel plate detector.

An overview of the UV detection technology that is available is given in the first section of this chapter. Examples where MCP detectors have been applied successfully in the past as well as details on the development of a cross strip anode MCP detector which inspired the current development at IAAT are given in the second section of this chapter. The next chapter describes the current research on MCP detectors at the IAAT.

## 2.1. Overview of UV detection technology

As far as not stated otherwise, the general information in this section is taken from Joseph (1995, 2000).

#### General characteristics of UV detectors

A detector that is intended to be used in a UV instrument has to be composed carefully. Usually, a compromise between several properties is necessary in the context of the scientific requirements that are defined for the overall instrument configuration. In general, there are five properties that a UV detector should have (Joseph, 1995):

- The detector should be solar blind

- High detective quantum efficiency (DQE)

- High local dynamic range (LDR) or global dynamic range (GDR) depending on the specific scene that is recorded

- Low intrinsic background and an insensitivity to external background sources

- Large multiplexing capability (i.e. a large number of pixels) to realize a sufficient spatial resolution for imaging applications or a sufficient spectral resolution in spectroscopy

Solar blindness is the property that the detector should not be sensitive to photons at optical wavelengths that are emitted from many astronomical objects besides the UV radiation. Often, astronomical sources of interest for UV astronomy radiate more of their flux in the optical wavelength range than they do in the UV. Hence, if the detector would be sensitive in the optical, this would cause a huge background in the scientific data and bring the detector operational point closer to the limits of its dynamic range.

The **detective quantum efficiency** means the total photon detection efficiency of a detector system. This includes for example the losses due to absorption of the UV radiation in an entrance window or losses due to the dead-time of a readout electronics.

The **local dynamic range** is defined as the maximum flux level in a narrow area of a detector minus the faintest level that is three standard

deviations above the background in acceptable integration times (Joseph, 1995).

In most astronomical imaging applications the light is concentrated in a few pixels on a detector or the sources are generally faint. Hence, the **global dynamic range** is less important for these applications. The GDR which is the maximum flux rate spread over the whole detector area is of greater interest in the cases where for example echelle spectra of bright hot stars are observed.

Detector **background sources** create events in the detector besides the radiation from the object that is observed. The background sources include internal detector dark events (e.g. caused by radioactive contaminations) and external background sources (e.g. Cherenkov radiation produced by cosmic rays).

#### Classes of UV detection devices

The detection devices that are of interest for astronomical observations in the UV can be sorted into two classes:

- Photoemissive devices: a photon releases an electron from the device's material. Photoemissive devices are for this photon counting. Examples are micro channel plate detectors or electron-bombarded CCDs (see below). The energy to release an electron is a few eV. Hence, photoemissive devices are natural UV detectors and are inherently solar blind. They have negligible background rates at room temperatures below 0.1 counts/cm²/s. However, an amplification mechanism to multiply a single photoelectron to a charge amount that is sufficient for further processing is usually necessary.

- Photoconductive devices: a photon causes an electron to transit into

the conduction band of the material of the device. Silicon-based

CCDs are an example for these devices. In general, they are integrating photon events except for X-ray applications. The excitation

energy is in the order of one eV. Photoconductive devices are for

this natural detectors for optical and near-infrared radiation and

are obviously not solar blind. Furthermore, usual photoconductive

devices are sensitive to thermally induced backgrounds and require

cooling.

### 2.1.1. Micro channel plate based photoemissive detectors

Micro channel plate (MCP) based detectors are the most successful type of UV detectors. A subtype that employs a cross strip anode (XSA) readout is of special interest here. This section presents details on the operation principle of MCP detectors. Micro channel plates, photocathodes, and readout schemes are introduced as well. Three examples for the realization of the MCP detector principle are described in Section 2.2 of this chapter. Chapter 3 shows the design of a cross strip anode MCP detector that is realized in Tübingen.

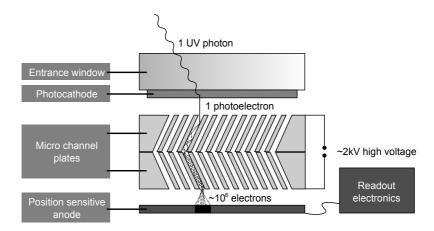

**Operation principle.** A micro channel plate detector consists of several components that act as a system to multiply an electron that is released by an incoming photon due to the photoelectric effect (see Figure 2.1).

The central element in the detector is the MCP that is a thin disk made in most cases of lead-oxide glass which contains hundreds of microscopic channels with a diameter and a distance of several micrometers (see Figure 3.2 for a photograph of the MCPs used at IAAT). The multiplication is performed in the channels of the micro channel plate where several electrons are released by each electron that hits one of the walls of the channels. Usually, a stack of two or more MCPs is used to realize a certain gain. A high voltage in the order of 1 kV for each MCP in the stack is applied from one face of the MCP stack to the rear side of the stack to accelerate the electrons in the channels. An electron avalanche leaves the MCPs.

The original electron usually is released by the incoming photon in a photocathode that is either deposited directly on top of the MCP stack or on the back side of a window in front of the MCPs. The photocathode is deposited to raise the probability of the photo effect but is not crucial for the operation of a MCP detector since electrons can be released off the surface of MCPs as well. The quantum efficiency for this process is small (2% at  $120\,\mathrm{nm}$  and  $10^{-9}$  at  $260\,\mathrm{nm}$  (Paresce, 1975)) nevertheless.

The electron cloud that leaves the MCP stack at its rear side can be deposited either onto an anode configuration or a solid state device to detect it. A readout electronics has to detect the charge information that is determined in this way.

A further digital processing in the electronics usually has the task to determine the center of mass of the charge distribution and hence the

Figure 2.1.: The architecture and operational principle of a micro channel plate detector.

center of the cloud. The cloud center corresponds to the position where the original photon hit the detector's active area in certain limits which are given by the channel bias angle and spacing, or distortions of the electric field of the high voltage at the edges of the MCPs.

In the following, several possible realization examples for photocathodes, micro channel plates, and readout anodes as well as their properties are described briefly.

#### **Photocathodes**

Photocathodes are used to convert photons into electrons. Different materials are used depending on the specific application (HAMAMATSU, 1997, Chapter 4). The bandgap of the photocathode material is the key parameter that determines the spectral range where the cathode operates most efficient. Usually, the operating spectral range has a sharp sensitivity cutoff (see the Figures 2.2, 2.3, and 2.4 below). In addition to an appropriate bandgap of the material, it should allow for a good electron transport to the emission surface and furthermore have a low or negative electron affinity to allow the electron that is released in the conversion process to escape from the photocathode material (Tremsin and Siegmund, 2005).

For astronomical applications, the out-of-bandpass rejection is yet another important parameter of the photocathode material. This means that the quantum efficiency should be as low as possible in the region below and above the spectral band for which the photocathode is intended. Especially the rejection of visible light is very important for instruments on satellites. For the example of UV instrumentation, stray-light from the sun is not easy to suppress. In scenarios where the intensity of the incident radiation is quite high, e.g. when performing observations of the Sun, the stability of the photocathode under intense radiation is more important than a good conversion efficiency.

Most of the photocathode materials require an operation in high vacuum conditions since their efficiency degrades substantially even under short atmospheric exposure. This implies some issues on production of the cathodes and handling during their integration into the detector assembly when selecting the proper material for the photocathode. In some photon counting applications, thermionic electron emission may be a final parameter that requires active cooling of the cathode to reduce the dark noise contribution of the cathode.

**Photon conversion process.** The process that ejects an electron from the photocathode surface when a photon is absorbed can be described as follows. The photon is absorbed in the photocathode and excites an electron, referred to as photoelectron, into the conduction band. For this, the energy of the photon must be larger then the bandgap energy of the photocathode material. The photoelectron produced in the inner volume of the material must be able to travel to the emission surface without being reabsorbed. The electron transport properties depend on the specific material structure and on the presence of impurities and defects that act as absorption centers and should be reduced to a minimum during the manufacturing process. When the photoelectron finally reaches the surface of the material, it must have more energy than electrons in the vacuum have. This negative electron affinity has often to be established by a treatment of the surface of the photocathode material to activate it. Usually, a doping of the material via Cs on top of a photocathode lowers the escape energy for photoelectrons off the surface.

In addition to the photon absorption and electron transport properties as well as the surface states of the photocathode material, the thickness of the cathode film on a carrier substrate is another important parameter that contributes to the conversion efficiency of a photocathode. The photon absorption probability increases with the photocathode film thickness while the probability of the transport of the electron to the emission surface decreases for a given wavelength of the photon to be converted. The optimum thickness for a given photocathode thus also has to be adjusted to the expected wavelength of the incoming photons.

The conversion efficiency of a photocathode usually is higher in the opaque mode where photons and electrons enter and leave at the same face of the photocathode than in the semitransparent mode where the electrons leave the photocathode at the opposite face of the cathode with respect to the incident photons. Despite this fact, when selecting a photocathode configuration, the semitransparent mode has to be favored for a given combination of a photocathode material and a carrier substrate. This is because since some cathode materials require high substrate temperature during their fabrication they can for example not been grown directly onto the surface of glass MCPs or other electron multiplying elements that are not rated for high temperatures.

Alkali halide photocathodes. Several alkali halide photocathodes have successfully been flown in space based instruments. The materials of this photocathode family are for example KBr, CsI, CsTe, and others. They are used due to their high efficiency that has its origin in good electron transport and surface emission properties, but also because their manufacturing is relatively easy. These photocathodes are typically manufactured by evaporation of high-purity powder under vacuum conditions. The result is a polycrystalline film that has sub-micrometer granular structure. The high bandgap of these materials makes them solar blind. KBr becomes sensitive to these wavelengths under prolonged exposure to high-intensity UV radiation which is restored after a short exposure to only visible light.

The quantum efficiency of alkali halide photocathodes (Figure 2.2) is different for example in the case of CsI and CsTe (Tremsin and Siegmund, 2005; Siegmund et al., 2008). The long-wavelength cut-off of CsI is at about 180 nm while it reaches an efficiency of about 40 % at 100 nm. For the case of CsTe, the peak quantum efficiency of below 20 % is located at 200 nm and drops to zero at  $\approx 300\,\mathrm{nm}$ .

Alkali halide photocathodes are stable only under short air exposure.

Figure 2.2.: Quantum efficiency of selected alkali halide photocathodes plotted against the wavelength of the incident photons. The photocathodes are deposited on MCPs. Data from Tremsin and Siegmund (2005).

The degradation of the performance under air conditions is caused by the sensitivity of the photocathodes to moisture. In the case of alkali halide photocathodes, the moisture is absorbed and forms a solution of the photocathode material. In extreme cases, when the water evaporates again, the film becomes completely discontinuous and leaves large crystal clusters on the surface of the substrate. CsI for example is, in contrary, not very hygroscopic and thus can sustain moderate exposures to air in the order of 10 minutes when it is transferred and installed into the final detection device. KBr can even withstand exposures up to 1 hour.

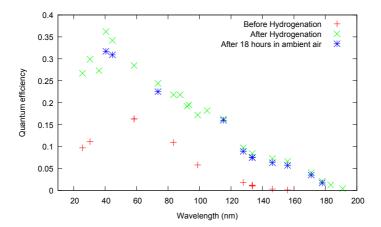

**Diamond photocathodes.** Despite the fact that diamond photocathodes are less efficient than other photocathode materials, diamond films have some features in favor of other cathode films. These features are radiation hardness, the chemical and mechanical stability under harsh environmental conditions and a very efficient heat dissipation. Diamond is thus attractive where efficiency can be sacrificed to stability. Diamond photocathodes are solar blind.

Chemical vapor deposition is applied to grow thin films of diamond. Other deposition techniques allow to grow diamond films on non-diamond substrates in a polycrystalline form and even on structured substrates as for example MCPs.

After the deposition of the diamond film, a surface treatment, often in form of a cesiation, is performed to achieve the smallest electron affinity and hence the best quantum efficiency. To avoid the necessity of the cathode processing under vacuum conditions for the case of surface activation by cesiation, other forms of surface treatment can be used. These are for example the activation by hydrogen in a hydrogen microwave plasma or the deposition of quasi monolithic layers of LiF. Hydrogenated diamond surfaces can withstand air exposures of several hours without much degradation (cf. Figure 2.3). Furthermore, the efficiency of these surfaces can be restored by moderate heating in vacuum after the exposition to water vapor.

The quantum efficiency of diamond in the opaque mode has its peak value in the order of  $20\,\%$  at around  $50\,\mathrm{nm}$  with a long wavelength drop at around  $150\,\mathrm{nm}$  or at  $200\,\mathrm{nm}$  when the surface is hydrogenated.

GaN photocathodes. The efficiency and bandwidth of the spectral sensitivity of GaN is better than that of the other materials mentioned above. The long wavelength cutoff furthermore can be tuned for GaN. GaN photocathodes are grown for example by molecular beam epitaxy on substrates that have a matching lattice as for example sapphire or silicon carbide. When the lattice of the substrate is not matching that of GaN, the quantum efficiency is typically reduced about a factor of 10 % though still significant and in particular higher than for CsI at wavelengths above 150 nm. GaN has to be processed and activated by Cs and oxygen under very high vacuum conditions. Nevertheless, after the exposure to air or nitrogen, the QE of GaN can be mostly recovered by vacuum bake out and fully restored by a subsequent cesiation of the cathode if necessary. The long term stability over several years in an evacuated sealed tube was shown (Siegmund et al., 2008).

In contrary to the other cathode materials, the spectral response of GaN is very broad expanding from the FUV up to a steep drop at around 380 nm. Opaque GaN photocathode configurations have shown quantum efficiencies of up to  $70\,\%$  at  $120\,\mathrm{nm}$ , though efficiencies of semitransparent

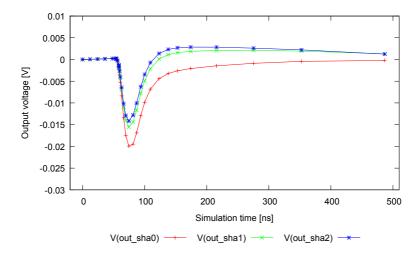

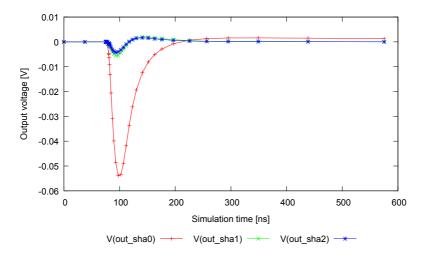

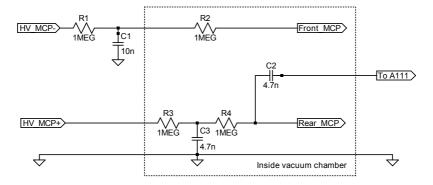

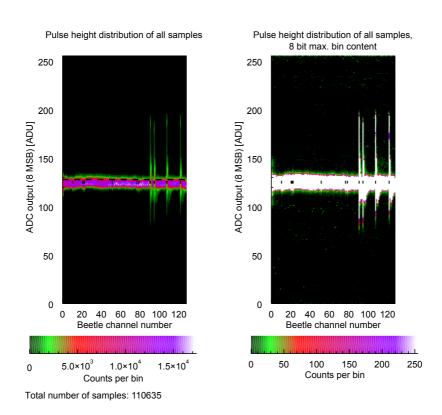

Figure 2.3.: Quantum efficiency of diamond photocathodes plotted against the wavelength of the incident photons, before and after the activation via hydrogen as well as after 18 hours exposed to air. Normal incidence on a planar Si substrate. Data from Tremsin and Siegmund (2005).