#### A TESTBED FOR EMBEDDED SYSTEMS

### **Peter Burgess**

### A Thesis Submitted for the Degree of PhD at the University of St Andrews

1994

Full metadata for this item is available in St Andrews Research Repository at:

http://research-repository.st-andrews.ac.uk/

Please use this identifier to cite or link to this item: <a href="http://hdl.handle.net/10023/13457">http://hdl.handle.net/10023/13457</a>

This item is protected by original copyright

## A Testbed for Embedded Systems

Peter Burgess

PhD Thesis

University of St Andrews

Division of Computer Science

Department of Mathematical and Computational Sciences

University of St Andrews

St Andrews, Fife, KY16 9SS

June 17, 1994

ProQuest Number: 10167224

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10167224

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346 m B582

#### Abstract

Testing and Debugging are often the most difficult phase of software development. This is especially true of embedded systems which are usually concurrent, have real-time performance and correctness constraints and which execute in the field in an environment which may not permit internal scrutiny of the software behaviour. Although good software engineering practices help, they will never eliminate the need for testing and debugging. This is because failings in the specification and design are often only discovered through testing and understanding these failings and how to correct them comes from debugging. These observations suggest that embedded software should be designed in a way which makes testing and debugging easier and that tools which support these activities are required. Due to the often hostile environment in which the finished embedded system will function, it is necessary to have a platform which allows the software to be developed and tested "in vitro".

The Testbed system achieves these goals by providing dynamic modification and process migration facilities for use during development as well as powerful monitoring and background debugging support. These facilities are built on a basic run-time harness supporting an event-driven programming model with a global communication mechanism. This programming model is well suited to the reactive nature of embedded systems. The main research contributions of this work are in the areas of finding deadlock-free, path-optimal routings for networks and of dynamic modification with automated conversion of data which may include pointers.

(i) I, Peter Burgess, hereby certify that this thesis, which is approximately 60,000 words in length, has been written by me, that it is the record of work carried out by me and that it has not been submitted in any previous application for a higher degree.

date 6/5/94 signature of candidate

(ii) I was admitted as a research student under Ordinance No. 12 in November, 1990 and as a candidate for the degree of PhD in November, 1990; the higher study for which this is a record was carried out in the University of St Andrews between 1990 and 1994.

date 6/9/94 signature of candidate

(iii) I hereby certify that the candidate has fulfilled the conditions of the Resolution and Regulations appropriate for the degree of PhD in the University of St Andrews and that the candidate is qualified to submit this thesis in application for that degree.

date 6/5/94 signature of supervisor

In submitting this thesis to the University of St Andrews I understand that I am giving permission for it to be made available for use in accordance with the regulations of the University Library for the time being in force, subject to any copyright vested in the work not being affected thereby. I also understand that the title and abstract will be published, and that a copy of the work may be made and supplied to any bona fide library or research worker.

date 6/5/94 signature of candidate

#### Acknowledgements

I would like to thank, primarily my supervisor Mike Livesey for suggesting I come to St Andrews to do a PhD in the first place, for his initial motivation and numerous suggestions and guidance along the way and for sharing the invaluable insights he gained from his work with the original ROV project. I would also like to give special mention to the following people:

Colin Allison, who often provided practical comments during the many Testbed design sessions based on his experience in the systems field and who read the first draft of this thesis at extremely short notice and gave many helpful suggestions for improvement.

Gerald Ostheimer, who has had to share an office with me for three years and whose revolutionary work on abstract architectures for parallel processing provided much inspiration for the Testbed programming model. I am also indebted to him for sharing his hypertext bibliographic database system, for reading and providing very useful criticism of an early version of the dynamic modification chapter and for broadening my knowledge of Computer Science considerably through numerous discussions.

Duncan Matthew, for providing me with source code and very thorough documentation of his hexapod walking robot, enabling me to implement it using the Testbed and so gain confidence in the programming model.

Tony Reynolds, for supervising a short term research fellowship at BT which provided early insight into the use of real-time clocks in distributed testing.

Finally, I would like to thank my brother, Richard, for getting me into computing in the first place.

# **Contents**

| 1 | Intro | duction                                                       | 1  |

|---|-------|---------------------------------------------------------------|----|

|   | 1.1   | Example of an Embedded System: The ROV                        | 2  |

|   | 1.2   | Approaches To Embedded System Construction                    | 4  |

|   | 1.3   | Goals of the Testbed                                          | 6  |

|   | 1.4   | System Overview                                               | 7  |

|   | 1.5   | Related Work                                                  | 8  |

|   |       | 1.5.1 Embedded Systems Development Environments               | 8  |

|   |       | 1.5.2 Concurrent Debugging                                    | 9  |

|   |       | 1.5.3 Interactive Debuggers                                   | 10 |

|   |       | 1.5.4 Replay                                                  | 10 |

|   |       | 1.5.5 Static Debugging                                        | 11 |

|   | 1.6   | Thesis Structure                                              | 11 |

|   | 1.7   | Original Contribution                                         | 12 |

| 2 | The F | Programming Model                                             | 13 |

|   | 2.1   | Introduction                                                  | 13 |

|   |       | 2.1.1 Platform and Language Issues                            | 14 |

|   | 2.2   | Action Semantics                                              | 15 |

|   | 2.3   | Message Semantics                                             | 15 |

|   | 2.4   | Devices                                                       | 17 |

|   | 2.5   | System Library                                                | 17 |

|   | 2.6   | Initializing Applications for Testing                         | 18 |

|   | 2.7   | Programming Interface to Data and Types                       | 19 |

|   | 2.8   | Dynamic Memory Allocation                                     | 20 |

|   | 2.9   | Development Support Environment                               | 20 |

|   |       | 2.9.1 Simulating Hardware and Environment                     | 21 |

|   |       | 2.9.2 Using Separate Processors to Reduce Monitoring Overhead | 21 |

|   |       | 2.9.3 Using Extra Routing Nodes to Avoid Interference         | 21 |

|   | 2.10  |                                                               | 22 |

|   |       |                                                               | 22 |

|   |           | 2.10.2  | HIGH_CONTROL                               | 22 |

|---|-----------|---------|--------------------------------------------|----|

|   |           | 2.10.3  | LOW_CONTROL                                | 26 |

|   |           | 2.10.4  | FEEDBACK                                   | 29 |

|   |           | 2.10.5  | Notes                                      | 30 |

|   |           | 2.10.6  | Testing the ROV                            | 31 |

|   | 2.11      | Related | i Work                                     | 33 |

|   | 2.12      | Conclu  | sions                                      | 35 |

|   |           | 2.12.1  | Reasons for Choosing this Model            | 35 |

|   |           | 2.12.2  | Trade-offs                                 | 37 |

| 3 | The T     | estbed  | System                                     | 38 |

|   | 3.1       |         | iction                                     | 38 |

|   | 3.2       |         | ot                                         | 38 |

|   |           | 3.2.1   | Accessing the Slot's System Data           | 40 |

|   | 3.3       | Slot St | ructure                                    | 41 |

|   |           | 3.3.1   | Slot Tables                                | 41 |

|   |           | 3.3.2   | Access to System Data from Applications    | 42 |

|   |           | 3.3.3   | Library Functions and Application State    | 42 |

|   |           | 3.3.4   | System Ports and Actions                   | 43 |

|   |           | 3.3.5   | Heap Implementation Details                | 43 |

|   | 3.4       | Loadin  | g Modules                                  | 43 |

|   |           | 3.4.1   | Construction of Object Module Descriptions | 44 |

|   | 3.5       | Special | l Slots                                    | 44 |

|   |           | 3.5.1   | The Centre                                 | 44 |

|   |           | 3.5.2   | The Host Server Slot                       | 45 |

|   | 3.6       | Host S  | ervices                                    | 45 |

|   |           | 3.6.1   | User Interface                             | 45 |

|   | 3.7       | Bootin  | g the Development System                   | 46 |

|   | 3.8       | Custon  | nizing the User Interface                  | 46 |

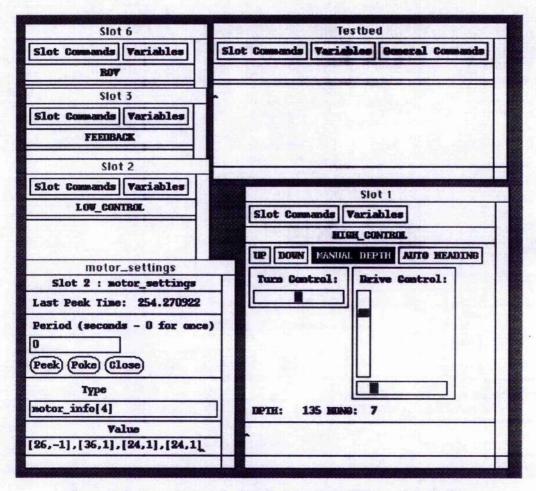

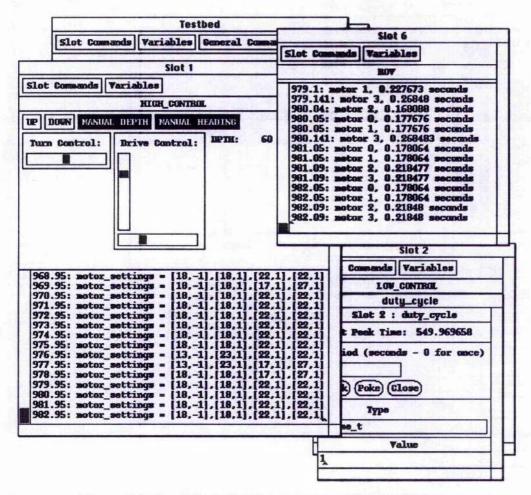

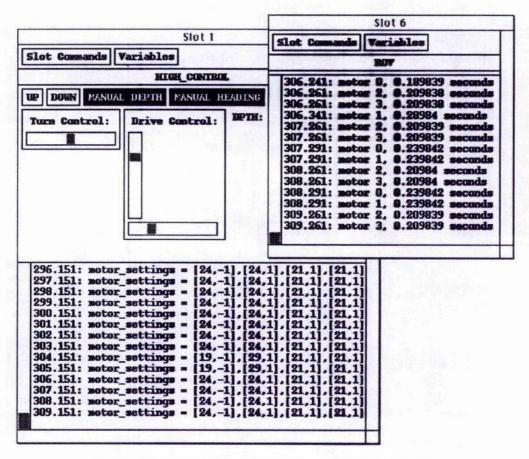

|   |           | 3.8.1   | Example: The ROV Control Panel             | 47 |

|   | 3.9       | Conclu  | sions                                      | 47 |

| 4 | The I     | Kernel  |                                            | 49 |

|   | 4.1       | Introdu | action                                     | 49 |

|   | 4.2       |         | l Work                                     |    |

|   | 0.4000350 | 4.2.1   | Commercial Real-Time Kernels               |    |

|   |           | 4.2.2   | Review of Real-Time Scheduling             |    |

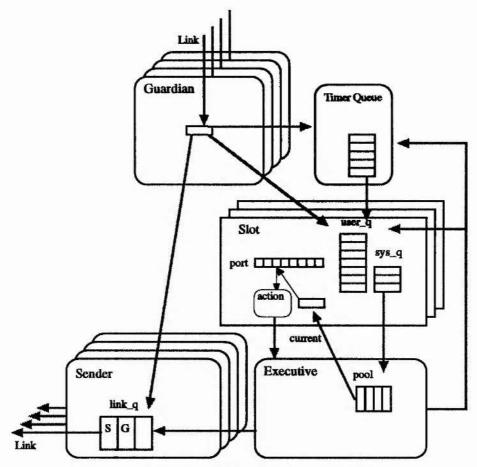

|   | 4.3       | Messas  | ge Flow Through The Node                   |    |

|   | 11        | 8.0     | oling Data Structures                      | 56 |

|   | 4.5  | Kernel Th    | reads        |           |       |      | * * | ٠            | <br>٠   |     |       | •             |            | ٠  | 56 |

|---|------|--------------|--------------|-----------|-------|------|-----|--------------|---------|-----|-------|---------------|------------|----|----|

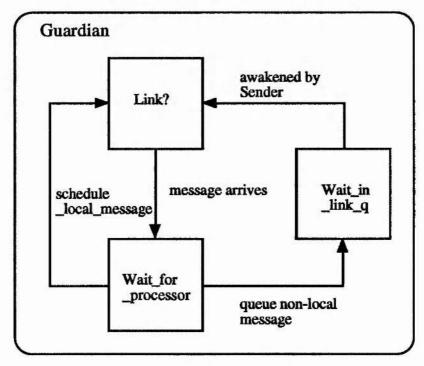

|   |      | 4.5.1 Th     | e Guardian   |           |       |      |     | ٠            | <br>٠   | •   | <br>• | •             | <br>       | ٠  | 56 |

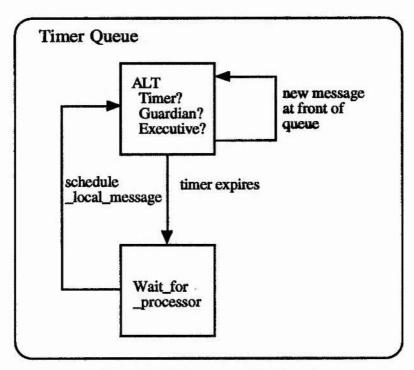

|   |      | 4.5.2 Th     | e Timer Qu   | ieue      |       |      |     |              | <br>٠   |     |       | 3.8%          | <br>       | •  | 58 |

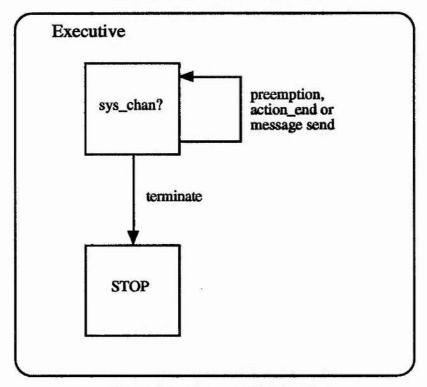

|   |      | 4.5.3 Th     | e Executive  | э         |       |      |     | •            | <br>•   |     | <br>٠ | •             | <br>       | ¥  | 59 |

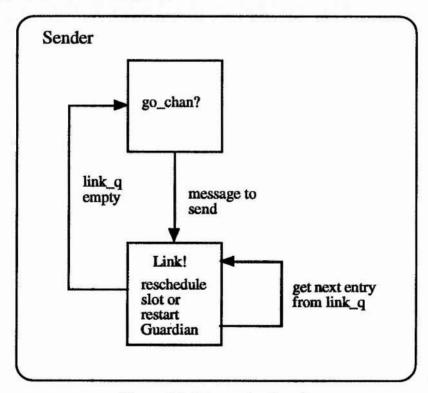

|   |      | 4.5.4 Th     | e Sender     |           |       |      |     | S <b>*</b> 0 | <br>•   | * : | <br>• |               | <br>       |    | 62 |

|   |      | 4.5.5 De     | evices       |           |       |      |     |              | <br>1.6 |     |       | •             | <br>       |    | 63 |

|   | 4.6  | Schedulin    | g in Testbed | 1         |       |      |     |              | <br>•   |     |       | 3. <b>*</b> 3 |            | *: | 64 |

|   |      | 4.6.1 Bo     | unded Dela   | ays       |       |      |     | ٠            | <br>٠   |     |       |               | <br>       |    | 64 |

|   |      | 4.6.2 In     | plementatio  | on of Pre | empt  | ion  |     |              |         |     |       |               |            | •  | 65 |

|   | 4.7  | Initializati | on           |           |       |      |     |              | <br>•   |     |       |               | <br>       | ¥  | 67 |

|   |      | 4.7.1 CI     | ock Synchr   | onization | n     |      |     |              |         |     |       | S*3.          | <br>       |    | 67 |

|   | 4.8  | Conclusio    | ns           |           |       | •    |     | ٠            | <br>    | ٠   |       |               | <br>       |    | 68 |

| 5 | Rout | ing          |              |           |       |      |     |              |         |     |       |               |            |    | 70 |

|   | 5.1  | Introduction | on           |           |       |      |     |              |         |     |       |               | <br>       | *  | 70 |

|   |      | 5.1.1 Fi     | nding the R  | outing .  |       |      |     |              | <br>٠   |     | <br>٠ |               | <br>       |    | 71 |

|   |      | 5.1.2 Re     | lated Work   |           |       |      |     |              |         |     |       |               |            |    | 72 |

|   | 5.2  |              | ed Network   |           |       |      |     |              |         |     |       |               |            |    | 73 |

|   |      | 5.2.1 W      | ormhole Ro   | uting .   |       |      |     | •            |         |     |       | *             | <br>       |    | 74 |

|   |      | 5.2.2 Pr     | operties of  | Testbed 1 | Netwo | orks | ١.  |              |         |     | <br>٠ |               | <br>       |    | 74 |

|   |      | 5.2.3 Br     | oadcast .    |           |       |      |     |              |         |     | <br>٠ |               | <br>       |    | 75 |

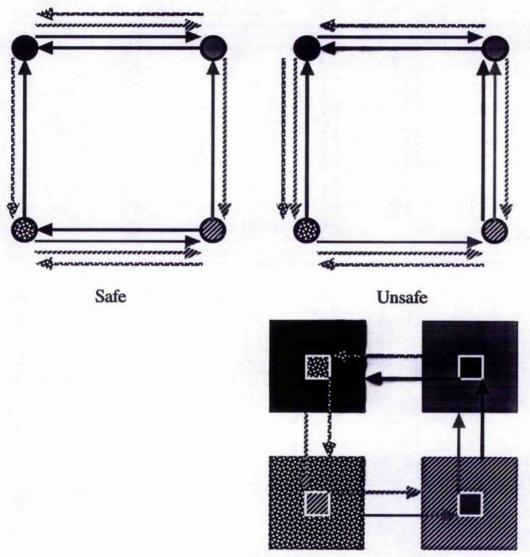

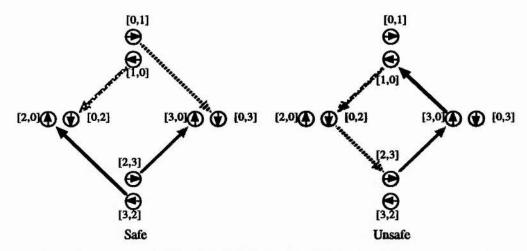

|   | 5.3  | Deadlock-    | Free Routin  | ng Functi | ions  |      |     |              |         |     |       | •             | <br>       |    | 75 |

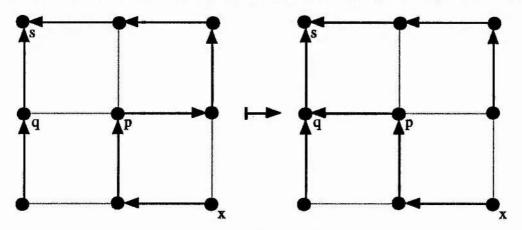

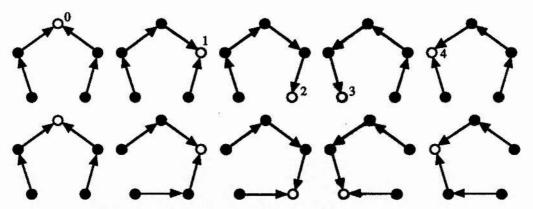

|   |      | 5.3.1 De     | ependency (  | Graph .   |       |      |     | •            |         |     | <br>  |               | <br>. 3983 |    | 77 |

|   | 5.4  | Optimality   |              |           |       |      |     |              |         |     |       | 3 <b>4</b> 5  | <br>       |    | 78 |

|   |      | 5.4.1 Ro     | outing Optin | nization  |       |      |     |              |         |     |       | y. <b>.</b>   |            |    | 81 |

|   |      | 5.4.2 Lo     | cal Minima   | 1         |       |      |     |              | <br>٠   |     |       |               | <br>       | *  | 82 |

|   |      | 5.4.3 Im     | plementation | on        |       |      |     |              |         |     |       |               | <br>       |    | 82 |

|   | 5.5  |              | Deadlock I   |           |       |      |     |              |         |     |       |               |            |    |    |

|   |      | 5.5.1 Co     | mbination    | Routings  | s     |      |     | •            | <br>•   |     |       |               | <br>       |    | 85 |

|   |      | 5.5.2 Fi     | xed Link Va  | lency N   | etwor | ks   |     |              |         |     |       |               | <br>0.02   |    | 89 |

|   | 5.6  | Application  | n to Comm    | on Netw   | ork C | lass | ses |              |         |     |       |               |            |    | 90 |

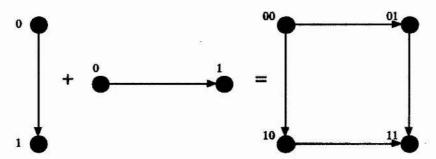

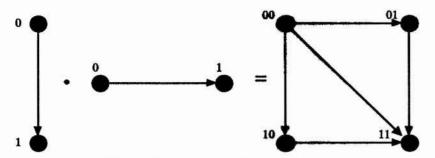

|   |      | 5.6.1 Gr     | ids and Hy   | percubes  |       |      |     | ٠            | <br>•   |     |       |               | <br>. 1961 |    | 90 |

|   |      | 5.6.2 Si     | mple Cycle   | s         |       |      |     |              |         |     |       |               | <br>       |    | 91 |

|   |      |              | e Torus .    |           |       |      |     |              |         |     |       |               |            |    | 91 |

|   | 5.7  | Conclusio    | ns           |           |       |      | ٠.  | ٠            |         | •   | <br>• | ٠             | <br>       | ٠  | 91 |

| 6 | Mon  | itoring and  | Backgrou     | nd Debu   | gging | 5    |     |              |         |     |       |               |            |    | 92 |

|   | 6.1  |              | on           |           |       |      |     | •            | <br>٠   |     |       | •             |            | •  | 92 |

|   | 6.2  | Related W    |              |           |       |      |     |              |         |     |       |               |            |    |    |

|   |      | 6.2.1   | Monitoring .        |          |      |       |      |            |         |       |       |   | : <b>.</b> . |     |               |   | • | •0 | 93  |

|---|------|---------|---------------------|----------|------|-------|------|------------|---------|-------|-------|---|--------------|-----|---------------|---|---|----|-----|

|   |      | 6.2.2   | Background l        | Debugg   | ging | Ι.    |      | ٠          |         |       |       | ٠ | •            |     |               |   | ٠ | •  | 94  |

|   | 6.3  | Testing | and Debuggin        | ng       |      |       |      | ٠          | *       |       |       |   | •            | ٠   |               |   | • | ٠  | 96  |

|   |      | 6.3.1   | Capture             |          |      |       |      | •          | •       |       |       |   | ٠            | •   |               |   | ٠ |    | 96  |

|   | 6.4  | Monito  | ring                |          |      |       |      | . •        |         |       | •     |   |              | ٠   | . ,           |   | ٠ | •: | 97  |

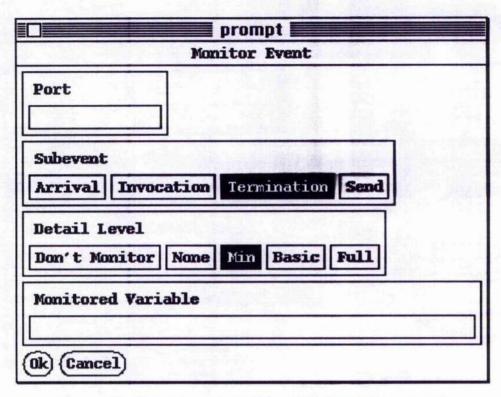

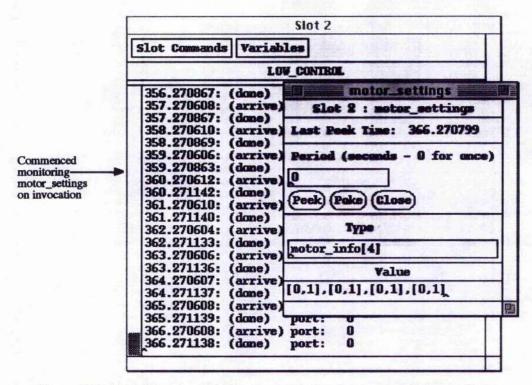

|   |      | 6.4.1   | <b>Event Monito</b> | ring .   |      |       |      | •          |         | <br>٠ |       |   |              | ÷   |               |   | • | •  | 98  |

|   |      | 6.4.2   | State Monitor       | ing      |      |       |      | •          | •       |       |       |   | ė            | ٠   | ٠.            | ٠ | ٠ | ٠  | 99  |

|   |      | 6.4.3   | Implementati        | on       |      |       |      | ( <b>)</b> |         |       |       |   |              |     |               |   | • | ٠  | 99  |

|   |      | 6.4.4   | User Interfac       | e to Mo  | onit | ori   | ıg . | ٠          | •       |       |       |   | •            | •   |               |   | • | •  | 100 |

|   | 6.5  | Avoidir | ng Interference     |          |      |       |      | ٠          |         |       | • •   |   |              |     |               |   | ٠ | ٠  | 102 |

|   |      | 6.5.1   | Example             |          |      |       |      | ٠          | ٠       | <br>٠ |       |   | ٠            | •   | •             |   | ٠ | ٠  | 103 |

|   | 6.6  | Backgr  | ound Debuggi        | ng       |      |       |      |            |         | <br>٠ |       |   | •            | *   |               |   | • | ٠  | 107 |

|   |      | 6.6.1   | Where to Place      | ce the S | Sun  | roga  | ate  |            | •       |       |       | ٠ | ٠            | ě   | •             | • | ٠ | •  | 108 |

|   |      | 6.6.2   | Example             |          |      |       |      | •          |         |       |       |   |              | ٠   |               |   | ٠ | •  | 109 |

|   | 6.7  | Conclu  | sions               |          |      | ٠.    |      | ٠          | ٠       | <br>٠ |       | • | ٠            | ٠   | •             |   | ٠ | ٠  | 110 |

| 7 | Demo | i-Ma    | dification          |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    | 112 |

| , | 7.1  |         | ction               |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

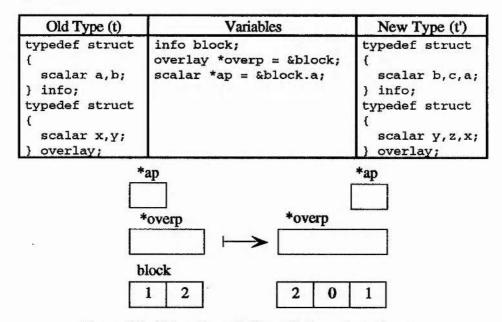

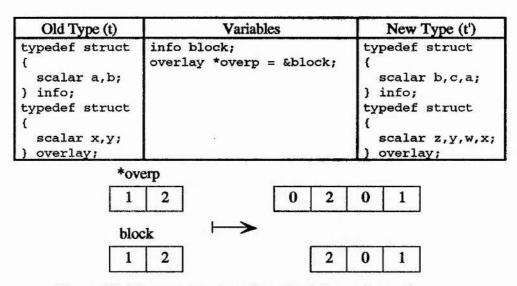

|   | 7.1  |         | ta Conversion       |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 7.3  |         | ing Aliases .       |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 1.5  |         | Assumptions         |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   |      |         | Conversion A        |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 7.4  |         | g the Mapping       |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 7.4  |         | Automaticall        |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 7.5  |         | nal Consisten       | 500      | 100  |       |      |            | 35.31   | 3000  |       |   |              |     |               |   |   |    |     |

|   | 1.5  | 7.5.1   | Static Consis       | -        |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 76   |         | lizations and I     | 1.50     |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

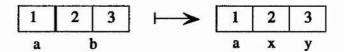

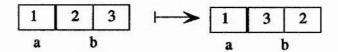

|   | 7.0  | 7.6.1   | Arrays              |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   |      | 7.6.2   | Different Sca       |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   |      | 7.6.3   | Pointers in A       |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   |      | 7.6.4   | Deleted Field       |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   |      | 7.6.5   | Extending the       |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 7.7  |         | onversion           |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 7.7  | 7.7.1   | Example             |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 7.8  |         | Relocation ar       |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 7.9  |         | ing Consisten       |          |      |       |      | -          | TO MODE |       |       |   |              |     |               |   |   |    |     |

|   | ,.,  | 7.9.1   | Aborting a R        | - T      |      | - 276 |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   | 7 10 |         | Work                |          |      |       |      |            |         |       |       |   |              |     |               |   |   |    |     |

|   |      | Conclu  |                     | • • •    | •    |       |      | •          |         |       | 72.00 |   |              | 3.5 | 6 <b>9</b> 81 |   |   |    | 130 |

| 8 | Migr  | ation 14                                    |

|---|-------|---------------------------------------------|

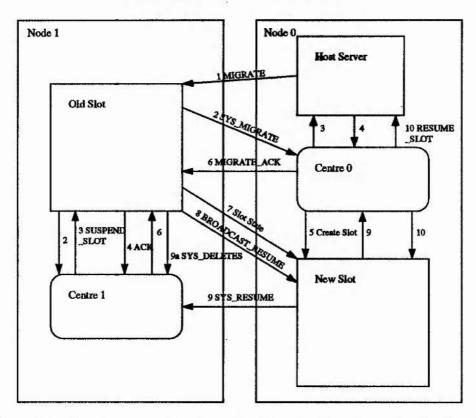

|   | 8.1   | Introduction                                |

|   | 8.2   | Related Work                                |

|   | 8.3   | Synchronous Migration                       |

|   | 8.4   | Asynchronous Migration                      |

|   |       | 8.4.1 Complications                         |

|   |       | 8.4.2 Pointer Updating                      |

|   | 8.5   | Correctness Properties                      |

|   |       | 8.5.1 Correctness of Synchronous Migration  |

|   |       | 8.5.2 Correctness of Asynchronous Migration |

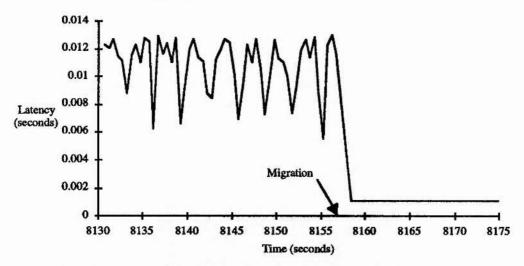

|   | 8.6   | Example                                     |

|   | 8.7   | Conclusions                                 |

| 0 | Conc  | dusions 14                                  |

| , | 9.1   | The Testbed Programming Model               |

|   | 9.2   | Implementation                              |

|   | 9.3   | Testing and Debugging                       |

|   | 9.3   | Dynamic Experimentation                     |

|   | 9.5   | Major Original Contributions                |

|   | 9.5   | Further Work                                |

|   | 5.0   | 9.6.1 Adding Features to Testbed            |

|   |       | 9.6.2 Device Support                        |

|   |       | 9.6.3 Heterogeneous Systems                 |

|   |       | 9.6.4 Using Memory Protection               |

|   |       | 9.6.5 Real-Time Scheduling                  |

|   |       | 9.6.6 Routing                               |

|   |       | 9.6.7 Dynamic Modification                  |

|   |       | 9.6.8 Background Debugging                  |

|   |       | 9.6.9 Fault Tolerance                       |

|   | 9.7   | Closing Remarks                             |

|   | J.,   |                                             |

| A | Testb | ed v1.0 User Guide and Reference 169        |

|   | A.1   | Overview                                    |

|   | A.2   | Running the Testbed                         |

|   |       | A.2.1 Environment Setup                     |

|   |       | A.2.2 Routing Files                         |

|   | A.3   | Using Testbed                               |

|   |       | A.3.1 Testbed Commands                      |

|   |       | A.3.2 Support for Dynamic Modification      |

| A.4    | Structure of a Testbed Application                 |

|--------|----------------------------------------------------|

|        | A.4.1 Message Format                               |

|        | A.4.2 Actions and Modules                          |

|        | A.4.3 User Defined Types                           |

|        | A.4.4 Macros for Defining State Variables          |

|        | A.4.5 Static Variables and Functions               |

|        | A.4.6 Configuration                                |

| A.5    | Detailed Description of Functions                  |

|        | A.5.1 Library Functions Available to all Slots 184 |

|        | A.5.2 Host Library Functions                       |

| B Test | ed System Ports 192                                |

| B.1    | Centre Ports                                       |

| B.2    | Host Server Ports                                  |

| B.3    | Application Slot Ports                             |

| B.4    | Common Ports                                       |

| C Sou  | ce Code for ROV 197                                |

| C.1    | Routing File                                       |

| C.2    | C Definitions                                      |

|        | C Source Code                                      |

## Chapter 1

## Introduction

Embedded systems are computer systems which are embedded in larger systems and running a single custom application program. Examples range in complexity from systems with a single processor such as video recorders, and disk controllers through more complex systems requiring more powerful processors such as data communications boxes to very complex distributed multiprocessor systems such as chemical plant controllers, robots and space craft control systems. An embedded system can generally be decomposed into a number of semi-independent state machines or processes each of which may have the following common characteristics:

- Reactive The process spends most of its time idle, awaiting some event, which may be external (from the outside world) or internal (a message or request from another process). It must then perform some action, possibly within some deadline and return to the idle state.

- Periodic The process repeatedly performs the same task at set intervals of time. Each instance of the task may have a deadline relative to its scheduled start. This can be regarded (and will be in the system described) as a special case of a reactive process in which the triggering event is a time.

- Tightly coupled to hardware and environment Each embedded system has special requirements which depend on the hardware which is to be controlled (actuators) and the interface to the external environment (valuators). The presence of the external environment in the specification of the system results in complex state spaces which are difficult to predict and model.

- Concurrent In all but the simplest systems there will be more than one distinct subsystem and hence process. These processes will need to communicate, with the resulting increase in complexity. In addition each process may well

have to accept new external events while previous ones are still being dealt with.

### 1.1 Example of an Embedded System: The ROV

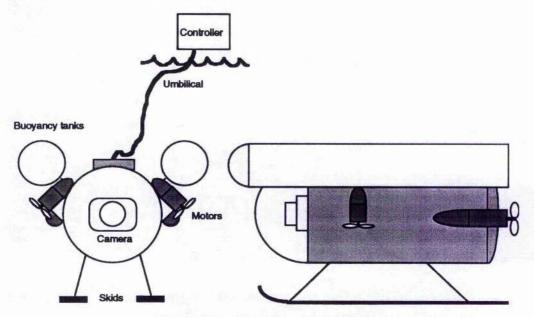

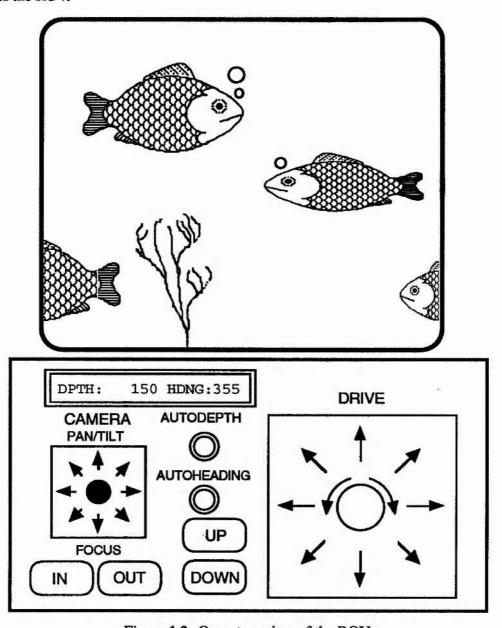

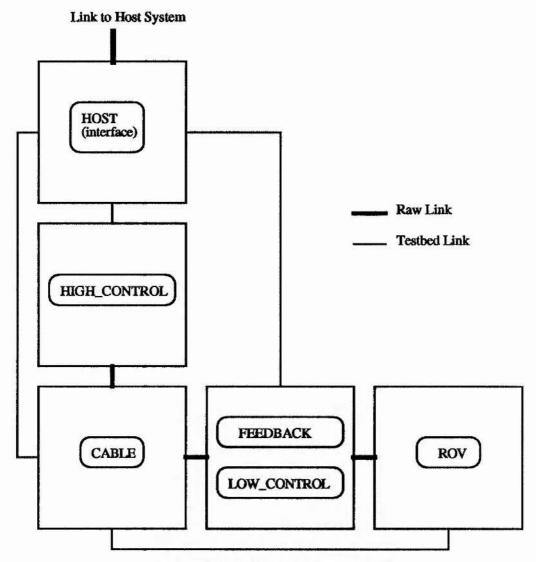

As a motivating example consider a submersible Remotely Operated Vehicle (ROV), typically used for inspection of off-shore oil platforms. The target system consists of a submersible robot attached by an umbilical cord to a surface controller as illustrated in Figure 1.1. The vehicle has four motors; two at the rear and two at the side each of which can be driven individually in either direction. The rear motors provide forward or backward thrust and heading control while the side motors which are inclined at 45 degrees, provide both vertical and sideways thrust. Buoyancy tanks at the top of the vehicle prevent significant tilting when the side motors are driving at different speeds.

Figure 1.1: The submersible ROV.

The ROV is controlled by an operator at the surface who uses visual feedback from a closed circuit video camera mounted on the front of the vehicle and a 20 character LCD display which displays depth and heading reported back by the software from gauges in the vehicle. The control panel includes a joystick for controlling the horizontal motion (speed and direction) of the ROV relative to the current heading, by the position of the joystick, and the heading itself, by twisting the grip of the joystick. The heading control returns to a neutral position when released. There are buttons for driving up or down at a fixed speed and for selecting autodepth and autoheading control. There is also a joystick for pan and

tilt of the camera and buttons for focusing. Figure 1.2 shows the operators view of the ROV.

Figure 1.2: Operators view of the ROV.

While autodepth (autoheading) is selected the control software attempts to maintain depth (heading) at the value reported by the depth gauge (compass) when this mode was entered. Autodepth control is temporarily overridden while one of the up or down buttons is depressed and restored when released with the target depth reset to the current depth. Similarly autoheading is temporarily overridden when the drive joystick is twisted to turn left or right and restored when it returns to its normal position with the target heading reset to the current compass value.

The software is required to ensure the following safety conditions to avoid

#### damage to the hardware:

- 1. There is an upper bound on the rate of change of speed of each motor.

- Each motor must be brought to a stop for a short period before changing direction.

- There is an upper bound on the sum of speeds of the two motors on each side of the vehicle.

The software is divided into two layers. The low level control performed onboard the vehicle consists of switching each motor (including those which control the camera) on or off for a percentage of a duty cycle specified by the high level control software which resides in the surface controller. The onboard software also polls the depth and compass gauges periodically and reports the values back to the surface controller. The high level controller is responsible for converting operator commands into appropriate motor values and for the autodepth and autoheading control while maintaining the safety conditions, as well as displaying the reported depth and compass values.

The original version of the ROV control software was implemented in Z80 assembly language with the only software testing done on the vehicle. Any behavioural faults meant hauling the robot up to the surface, trying to debug the assembly language program, re-assembling the new control code, burning new eproms, and trying again. In Section 2.10 an implementation of the ROV in the Testbed programming model described in Chapter 2 is presented.

### 1.2 Approaches To Embedded System Construction

It might at first seem that as embedded systems are concurrent, they are a special case of general purpose distributed operating systems or perhaps should be studied along with supercomputers. However the first three characteristics on the list on page 1 conflict with the goals of these fields. General purpose computers tend to run multiple competing tasks and are tuned to provide good average throughput. They often have features which embedded systems do not require such as virtual memory and disk/file systems. The maximum memory requirement can usually be determined during an embedded system's development and the extra cost in overhead, loss of predictability and extra power and space requirements often rule out virtual memory and disks. The applications run on general purpose computers and supercomputer applications tend to differ from embedded applications in that they run to completion with as few pauses as possible. If the system fails due to shortage

of resources, it may be acceptable simply to reconfigure and restart the application or even reboot the system if the fault lies there (e.g., memory fragmentation). This is generally not acceptable in an embedded application/system. Most work on embedded systems appears in the real-time systems literature, however there are other important issues which deserve study such as the general development and debugging problems which this work addresses.

Two approaches to embedded system construction are to program the hardware directly or to use an operating system. The advantages of the former are that it is theoretically possible to minimize hardware requirements such as memory and processor performance. This is probably appropriate for the simplest embedded applications where these resources are most limited. The main disadvantage of the direct approach is high software costs; the code is likely to be hard to understand, debug and modify. These become rapidly worse as the complexity of the application increases. Operating systems have the advantage of code reuse, the application programmers task should be easier and the resulting code should be simpler, as much detail is hidden in system calls. The operating system may well provide facilities and tools which make the system easier to develop, debug and modify, such as the ability to test outside the target environment using simulations of the real system. The disadvantages of an operating system include the excess baggage in terms of memory and processor performance requirements, possible loss of control of resource management and the fact that the applications programmer may not be able to obtain detailed information about the behaviour of the system and the consequences/side-effects of system operations. This last difficulty makes verification of the system difficult and also hinders debugging as the programmer may be unsure of whether a bug is in the system or application code. Often such cases arise from a lack of understanding of the operating system's behaviour due to poor documentation.

The difficulties encountered with operating systems often result from the use of a general purpose operating system (such as a Unix<sup>TM</sup> variant or MSDOS<sup>TM</sup>). These systems have not been designed with embedded applications in mind and consequently do not have the required properties such as determinism or level of documentation. Often compromises have had to be made due to the lack of advance information about the application, in order to improve average performance at the cost of occasional unpredictable delays or even potential failure. Even the basic process model supported by such systems is often inappropriate in that it requires the application programmer to provide an event loop which is common to all processes and which might well have been included in the system. It is also likely that the system is not customizable to a fine enough level, requiring

the programmer to work around inappropriate low level mechanisms which add unnecessary overhead. For example it is often not possible for the application to control low level scheduling or inform the system of its timing constraints. The microkernel approach currently in vogue in operating systems design (Amoeba, Mach 3.0 [97]) helps to some extent, however most of these systems have been developed with different objectives to embedded systems operating systems such as implementing a better (e.g., distributed, object oriented) Unix.

An operating system designed specifically for embedded applications should overcome most of these difficulties. Obviously due to the highly disparate nature of embedded applications, it is hard to produce an operating system which is ideal for all and there will always be resource penalties to pay for using one. However for complex embedded applications the benefits should outweigh the costs.

In addition to the attributes of predictability, simplicity and configurability of the kernel, an operating system for embedded systems can also provide higher level features which aid in the development process. These are outlined in the next section which overviews the goals of the Testbed project.

#### 1.3 Goals of the Testbed

Monitoring It is essential that both the whole system and individual running processes can be monitored during their operation. Monitoring inevitably causes perturbation of the target system (called the "probe effect" in [28, 40]). It is important to minimize this effect, and allow the test bed to eavesdrop on the target system as silently as possible. Embedded systems are almost always time-critical. Timing is one of the most delicate aspects of the target system behaviour, making silence a difficult criterion to meet and effectively ruling out interpretive debugging.

Dynamic Modification If a malfunction or undesirable behaviour is detected during monitoring, subsequent modification of the system incurs a cost. For any large system, such as a telephone exchange, airline reservation system or operating system, this cost may be unacceptable. Minimizing the potential cost requires the system to support some degree of dynamic modification. An embedded system will normally have a large range of internal states, reflecting the system's close coupling to its external environment. The state path from startup to the state where the malfunction is detected may therefore be long. The cost of re-creating this path, the "warm up" cost, may be prohibitive; in some cases it may be effectively infinite. It is therefore highly desirable to have dynamic modification at the level of individual

processes.

Process Interconnection In order that a client application interconnection topology can be designed independently of the physical network topology, it is necessary to provide a communication harness that supports a single system wide communication model. This model must provide, as simply and efficiently as possible, deadlock-free, versatile and reliable routing of messages.

Process Migration Time criticality makes the allocation of processes to processors an important issue, and the test bed must also provide for dynamic control over this allocation by allowing processes to be migrated. Migration is another reason for having the system wide communication model. Migration can be viewed as a form of dynamic modification.

Background Debugging Interactive debugging creates a bottleneck, which causes excessive intrusion and contributes to the probe effect mentioned above. One way to minimize the interaction bottleneck is by means of background debugging in which debugging decisions and actions are devolved as far as possible to code which runs alongside the application software.

### 1.4 System Overview

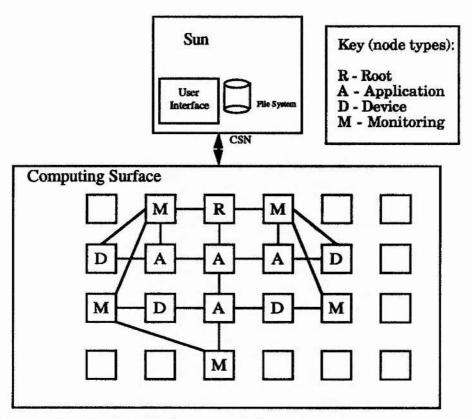

Testbed is currently implemented on a Meiko Computing Surface connected to a Sun workstation. The reconfigurability of the Computing Surface makes it easy to experiment with different interconnection topologies for multiprocessor embedded applications and also provides extra processors which can be used for simulating devices and off-loading monitoring tasks (as suggested in [1] and [33]), reducing interference which might otherwise change the behaviour of the application.

The user interface to the system is a Sun workstation (hosting the Computing Surface) through which the user is able to interact with the application under development through a root node for purposes such as monitoring, debugging and controlling simulation (see Figure 1.3). All communication with the host system uses Meiko I/O functions from the root node. Communication from elsewhere in the system is performed strictly using Testbed functions which communicate over transputer channels with system components which route messages back to the root node.

Figure 1.3: The Testbed development platform supports "in vitro" development with extra nodes used for monitoring and simulating external devices.

### 1.5 Related Work

### 1.5.1 Embedded Systems Development Environments

A number of test beds and development environments for embedded systems have appeared in the literature recently, most with some features in common with Testbed. However none have all the features described in this thesis. In particular dynamic modification facilities are either absent or much more primitive than those described in Chapter 7.

[83] describes testing distributed real-time systems in the context of the MARS architecture and MARDS design environment. The MARS system consists of a set of clusters of components which are stand-alone computers. Each component in a cluster communicates with the others using a real-time bus while some components can be connected to an interface bus or field bus for communicating with other clusters or the external environment. Each component runs a copy of the MARS operating system. Apart from the architectural differences, MARS is fundamentally different from the Testbed system and programming model in that MARS is a time-triggered system in which each action is executed at a predeter-

mined point in time. By contrast, Testbed is an event-triggered system in which the scheduled start time for a time-dependent action is an event.

Similarities in the work described in [83] include the use of passive monitoring rather than interactive debugging to avoid the probe effect and the use of extra processes and processors for environment and device simulation.

[33] describes testing in a "host" environment with device handlers replaced by device simulators for testing the logical function of the system and also in the target system with an environment simulator for testing performance. The environment simulator runs on an external system to avoid perturbing the software under test.

### 1.5.2 Concurrent Debugging

The same techniques which are used for debugging sequential programs may be used to debug concurrent ones, both to detect the same types of bugs and also new ones introduced by communication, such as sequencing errors. In the latter case the efforts of the debugger are often thwarted by the intrusiveness of the debugging process—the probe effect, in which the very presence of the debugger alters the timing properties of the program to mask possible errors. Detecting the special errors which are introduced due to concurrency, and avoiding the probe effect, have led to approaches which concentrate on specific aspects of debugging, or one technique (such as message monitoring).

[60] surveys techniques for debugging concurrent programs and identifies four classes:

- 1. Traditional debugging techniques.

- 2. Event-based debuggers.

- 3. (Graphical) tracing techniques.

- 4. Static analysis.

Here debugging techniques will be divided into the following (non-mutually exclusive) categories:

- Interactive Debugging In which the user may view and interact with execution of the program in real-time.

- Monitoring In which the events/states in the system are captured, and viewed/used either in real-time or post-mortem.

- Replay In which sufficient information is recorded to enable a program to be replayed from a particular point, with more detailed examination.

Static Debugging Where a specification of the program is checked against certain assertions about its valid behaviour.

Background Debugging In which monitoring techniques are used in conjunction with the assertion idea from static debugging to automate the process of interactive debugging.

### 1.5.3 Interactive Debuggers

Conventional source level debuggers are a very useful tool in software development. Unfortunately many systems which support and even encourage concurrent programming, fail to provide interactive source-level debuggers which support multi-threaded programs. For example the dbx and dbxtool debuggers in SunOS and the tdb and tdbtool debuggers for the Meiko Computing Surface cannot cope when a process forks (or PARs), although there have been interactive windows-based debuggers for some time [27, 40, 48, 80, 89] which do support multithreaded programs.

### 1.5.4 Replay

In replay systems [16, 17, 24, 31, 54, 69], the communications which the process under inspection makes with the outside world are recorded. When some incorrect behaviour is noticed, the system is stopped and then the process is "replayed" with the monitored communications performed in the same sequence. This allows full source level debugging with breakpoints and state inspection to be performed without the danger of changing the temporal ordering of events. Replay systems have two major disadvantages for embedded systems. The first is that embedded systems run for an indefinite amount of time. Thus if all communication events are logged, the log may grow indefinitely. Many replay systems cope with this by including periodic checkpointing, allowing the log to be discarded prior to the checkpoint. However any behaviour which the monitoring system (or human observer) is trying to detect must be guaranteed not to have occurred before the checkpoint or the subsequent replay will not be able to identify the root cause. Another problem is that checkpointing is a time consuming activity and may itself interfere with the temporal or timing behaviour of the system. The other major problem with replay is that it only preserves the temporal ordering of the events in the system. Timing behaviour will still be altered by any source level debugging during the replay.

### 1.5.5 Static Debugging

This approach generally involves converting a high level specification into a graph, such as in the Petri net approach [21] which may be analyzed to detect potential invalid communication patterns such as deadlock. Unfortunately for realistic systems the graphs quickly become unmanageable.

[41] describes a method for testing a set of communicating sequential processes, by attempting to construct a feasible sequence of interactions between them from a given set of inputs by an iterative algorithm which initially assumes random inputs to each process. This approach may be suitable for short processes of finite duration, however the artificial time ordering of the communications used may not reflect what happens in the real system.

The research described in this thesis has focused on providing mechanisms to facilitate non-intrusive debugging which is not possible with source level, breakpoint techniques. Consequently Testbed does not provide these facilities. A survey of work on non-intrusive monitoring and background debugging can be found in Chapter 6.

#### 1.6 Thesis Structure

The rest of this thesis is structured as follows: Chapter 2 describes the programming model around which the Testbed is built. Examples are presented to illustrate the use of this model.

Chapter 3 gives details of the higher levels of system software which provide the debugging support and implement the programming model.

Chapter 4 describes the design of the BED (Basically Event Driven) multithreaded kernel which supports the Testbed programming model.

Chapter 5 presents work done in support of Testbed on deadlock-free routing in networks.

Chapter 6 describes the monitoring features of Testbed and discusses how they may be used to debug and tune an embedded application without interfering with the application's behaviour.

Chapter 7 contains a formal treatment of the solution to the pointer updating problem as well as a general description of the mechanisms which support dynamic modification in Testbed. A simple example is provided which illustrates how dynamic modification may be used in practice.

Chapter 8 describes the process migration mechanism of Testbed and illustrates with an example how it can be used to improve load balancing.

Chapter 9 summarizes the project and its contribution.

Appendix A gives a detailed description of the user's view of the current Testbed implementation, Appendix B gives details of system port assignments and Appendix C gives source code for the examples described in the main body of the thesis.

### 1.7 Original Contribution

The original aspects of this work include:

- The programming model (Chapter 2), which differs from the CSP style commonly used for distributed memory systems and is better suited to the reactive nature of embedded systems.

- 2. The integration of time into scheduling (Chapter 4).

- 3. Work on optimizing message routing while preserving deadlock-freedom and extending networks with such routings in a regular way (Chapter 5).

- 4. Monitoring and background debugging (Chapter 6). The structure of Testbed programs provides natural breakpoints which enable non-intrusive monitoring and provide support for background debugging.

- 5. Dynamic modification (Chapter 7) and Migration (Chapter 8). The structure of the Testbed system and applications also allows some of the most difficult problems in these two fields to be solved. Much more flexibility in data structuring and a greater degree of automation of data conversion are provided than with previous work in the field of dynamic modification.

Some of the work contained in this thesis has been previously published by the author [12, 13, 14, 15, 57].

## Chapter 2

## The Programming Model

#### 2.1 Introduction

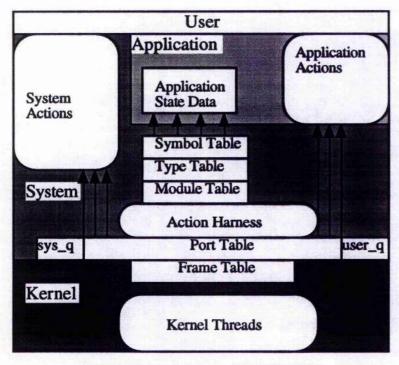

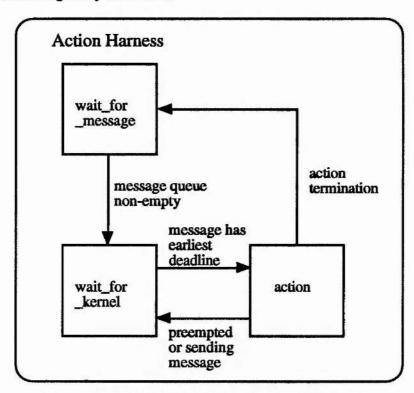

Testbed is based around a distributed reactive processing model in which events are synonymous with messages. The processing entities are known as slots which are active objects consisting of encapsulated state data and code for processing and responding or reacting to messages. Slots may reside on the same processor or different ones separated by a network. In both cases communication is identical from the slot's viewpoint and any slot may send messages to any other without the need to establish a connection. Events may originate outside the system via a device interface or inside when one slot sends a message to another. Similarly a slot sends messages to a device as if it were another slot. When a slot receives a message it is processed by a unit of code called an action. This is a procedure which may update the slot's state in response to the message and any data it may contain and respond by sending new messages. Actions always terminate and do not perform input. Instead new messages are processed by new action instances. Only one action can be in progress at a time in any slot. The slot's state includes a table mapping ports to actions. Each message contains a port identifier and the system uses this to index the port table and determine which action to invoke to process the message. This port assignment may be altered by actions. Time is intrinsic to the model in that each message carries a timestamp which, if in the future, can be used to delay a message. Also a slot can have a deadline for processing each message which the system uses to schedule multiple slots on a single processor.

It will be argued that this simple programming approach is more appropriate to embedded applications than a conventional sequential process-based model such as CSP [43], though the latter is more general. Testbed provides the embedded systems software implementor not only with a debugging and testing environment,

but with a framework for the software. Specifying embedded software using the Testbed model involves breaking the system down into components which form the slots, determining the types of messages which these components need to send and respond to, and designing the ports and associated actions required to receive and process these messages. This resembles the state machine network approach often used in the higher levels of embedded systems design [86]. In fact state machines map naturally onto slots with events corresponding to messages, states to the combination of state data and port settings and state transitions to the operation of actions on the state triggered by the events. The event-action model also greatly simplifies and modularizes the implementation of the monitoring and debugging activities of Testbed. If the user were to provide a complete process then Testbed would be forced to probe at its inner workings from the outside. This would require a great deal of work at the compilation stage and would be especially difficult if the process had multiple threads.

The Testbed programming model is supported by a kernel described in Chapter 4 which transports messages between slots and performs scheduling operations. The rest of the Testbed's application and debugging support is implemented using slots and actions. Each processor has a *centre* slot which performs housekeeping activities and a special version of this slot residing on the root processor provides the user interface via the Unix host using the X Window System and Athena Widgets [71]. This is referred to as the *host server* slot.

### 2.1.1 Platform and Language Issues

Although Transputers were chosen as the platform for Testbed, the programming model is not Transputer specific and in fact differs greatly from the CSP/occam model [43, 103] normally used to program these systems<sup>1</sup>. Transputers are an appropriate platform for Testbed as they were designed for both embedded systems and multiprocessing applications. Testbed is aimed at multiprocessor embedded systems and the availability of Unix workstation hosted Transputer arrays such as the Meiko Computing Surface allow the software to be developed and tested on the same processor as the target system.

Given the event-action model, the choice of programming language had to be made. The obvious choice for Transputers is occam, however the fact that actions are sequential and are not permitted to perform blocking input would mean that the programmer would be restricted to a sequential subset of occam without the input operations. It was decided that it would be better to use a purely sequential

<sup>&</sup>lt;sup>1</sup>See Section 2.11.

language for the actions and since C is also in common use for writing embedded systems software both on Transputers and other platforms, it was chosen.

#### 2.2 Action Semantics

Actions are simple functions which are called by a special harness process. All actions are invoked with the same parameters. A C prototype for an action would have the form:

```

void action(void *data);

```

The parameter is a pointer to the data contained in a the message (if any). System functions are provided for obtaining information from or even a complete copy of the message header. This is useful for reasons such as identifying the sender, checking for expiration of the deadline or rescheduling the message for a later time.

Actions may send messages to other slots, to the same slot or to an external device, but may not perform input. This property reflects the view of action functions as interrupt handlers, which should execute for a short bounded period (without interruption). If blocking input needs to be performed from an external device, it will be performed by a special input handler process which is considered to be part of the system rather than application code. When a new message arrives it is placed by the system into a FIFO queue for the destination slot. When space for messages becomes exhausted, messages are discarded. It is up to the application designer to ensure that there is always enough space for the maximum number of messages which may be waiting at each slot.

### 2.3 Message Semantics

When sending a message, the sender provides the following parameters:

**Destination** The destination slot id.

Size The size of the message data.

Port An indication of the type of message to the destination slot.

Timestamp A time before which the message must not be processed at its destination.

Data Information to be processed.

The application does not need to know on which processor the destination slot is, though this location is specified by the user during initial loading and may change during development as slots are migrated to tune performance. The message is automatically routed to the correct node as described in Chapter 5.

The queue of messages for a slot will be referred to as its schedule. Once a message has reached the head of this queue it will eventually be removed and an action will be dispatched to process it. At this point it is no longer part of the schedule and cannot be overwritten by newly arriving messages.

When a message arrives with a timestamp which is greater than the processor's local clock value, its arrival is delayed until this time has past. Then the message is added to the back of the queue for that slot as if it had just arrived. Each slot also has a post time which is added to the timestamp to give a deadline before which the system should action the message if possible. In cases where no particular deadline is appropriate, a priority may be given. The deadlines and priorities are used by the system to choose between different slots on the same processor. This scheduling is described in Section 4.6. The destination slot has a port table which contains a mapping from the port contained in the message to an appropriate action. This mapping may be changed by the application.

It is possible that an overload situation may arise in which messages need to be discarded. To avoid losing crucial messages, the application may specify a minimum number of buffers which are reserved for use by messages destined for a particular port. On the other hand it may be known by the system designer that certain types of messages are liable to flood the system in exceptional circumstances and so it is possible to specify a maximum number of such messages which may be waiting to be processed at any one time, so protecting other more important messages from being lost. When a message arrives and the slot currently has the maximum number of messages for that port its data field is used to overwrite the data of the most recently arriving message. This mechanism is also useful as an optimization for update messages when only the most recent message is of interest. For example a device may periodically report the current value of some valuator. There is often no need to store several such messages so the maximum value can be set to 1.

The application can specify that messages for a particular port are *critical* in which case they may not be interrupted by the system as long as it performs no output. Also if a slot is waiting to process a critical message whose deadline is earlier than any other slot, the delay before the slot is scheduled will be short and bounded. The critical attribute is a useful way of reducing interference with time critical activities by other slots and by message traffic which would normally take

precedence. This attribute also provides a mechanism for responding to device or timer interrupts deterministically.

#### 2.4 Devices

In keeping with the rule that actions cannot block awaiting input, synchronous devices, such as those attached to Transputer links or which indicate readiness via the event pin, are handled by kernel threads which convert incoming data into Testbed messages. There are also kernel threads which convert Testbed messages into raw data sent to the device. Since the input data does not arrive in the form of Testbed messages the destination slot and size of the data need to be specified by the application in advance. Also the application needs some way of addressing the device. Device links, as well as raw links<sup>2</sup>, are specified as part of the network description<sup>3</sup> at which stage they are given slot identifiers. Any slot can send a message to a device as if it were an ordinary Testbed slot. Two function calls are provided to configure the kernel thread which inputs from the device, telling it the size of the incoming messages and which slot and port to deliver them to. The configure device function causes messages of the given size to be read repeatedly and passed on to the given slot and port, while the read\_device function results in a single message being delivered. In this way slots anywhere in the network can access any device transparently and input from the device can be routed to a receiving slot on any processor.

Asynchronous devices, such as memory mapped, polled devices do not need to be part of the kernel. Application actions can read and write them directly as this does not involve blocking. If access from multiple slots or from remote nodes is required to such a device then a dedicated slot can act as a device driver, but this is part of the application, not part of the system.

### 2.5 System Library

A set of library functions is provided to be called by applications. These include a subset of the standard C library functions as well as many Testbed specific calls which provide features such as communication, memory management and port management. A full explanation of these functions along with some useful macros which are provided in header files, can be found in Appendix A.

<sup>&</sup>lt;sup>2</sup>useful during development, so that a device may be simulated by a Testbed slot on a separate processor

<sup>&</sup>lt;sup>3</sup>See Appendix A.

### 2.6 Initializing Applications for Testing

When the application is ready to be installed on the target system, it will usually be linked with those parts of the Testbed system which are required to support its execution into a set of executable modules which can be loaded from disk or stored in ROM. However during development on the Computing Surface the Testbed system, including its user interface is loaded first using the Meiko system configuration and loading facilities (CSBuild [61]) and then the application is loaded by Testbed.

At system creation time, the physical network of processors, together with routing tables are supplied by the user. The target application is composed of a collection of slots which are assigned to physical processors (not necessarily one-to-one). There is no special compiler for Testbed. Instead the one which comes with the system (e.g., the Meiko C compiler) is used. The source code is divided into modules which are loaded as units. There are three types of modules, declaration modules, initialization modules and application modules. Each declaration or initialization module contains a declaration or initialization function which is called after the module is loaded. Declaration functions define user defined types, state variables and the initial port assignment for the slot. Variables can be given initial values when first defined. Initialization functions contain extra initialization which needs to be performed at system startup. Application modules do not contain a function which is invoked when they are loaded. Any of the three types of module can contain actions and other functions called by them, however the declaration and initialization modules may not call functions in application modules or declaration and initialization modules which are loaded after them. Nor may they refer to variables declared in these later modules. This is because declaration and initialization modules are linked immediately, and invoked, while the application modules are not linked until the end of the load process. The system is bootstrapped by means of a special initialization function executed on the host server. This function makes system calls to create and initialize all other slots in the system. The initialization of these slots is performed by loading the declaration, initialization and application modules which define them.

Actions are linked with the slot's state data. These data may be shared between actions, but there is no danger of conflict, as only one action may execute at a time. The state variables are maintained in a symbol table each entry of which contains the type of the variable and its address. Static and dynamic variables are created in the same way but are distinguished by associating a name with each static variable and allowing it to be linked into actions. Dynamic variables may only be referred to by indirection through pointers contained in other variables.

Type definitions and static variables are generally created by declaration functions which are invoked once when the application starts up or during a reload operation. Such reloads are the means by which the incremental modification occurs.

### 2.7 Programming Interface to Data and Types

Both types and state variables are currently defined using procedures and macros from declaration functions<sup>4</sup>, in the case of static variables, or from action code in the case of dynamic variables. A set of standard types is predefined and these form the basis for the user defined types. With the exception of arrays and pointers, each state object must have a type corresponding to a definition in the type table. This means that all structures must be defined explicitly as types in the type table before being used (equivalent to having to typedef each struct used in a C program). Variables may be declared as pointers to, or arrays of, existing types (or pointers, arrays etc.). This results in all intermediate pointer and array types being added to the type table. The naming convention for these types is based on C syntax. A pointer to base\_type is named base\_type\*, while an array of n base\_types is named base\_type[n]. For multiple dimensional arrays the dimensions are ordered from right to left. So base\_type[n][m] is an array of n base\_type[m]. Pointers and arrays may be combined. For example if a variable is declared of type int\*[3]\*\*[4][5], (with int already declared) then this results in the following types:

```

int*

int*[3]

int*[3]*

int*[3]**

int*[3]**[5]

int*[3]**[4][5]

```

In words the final type is: array of 4 array of 5 pointer to pointer to array of 3 pointer to int. It is not clear whether this is the best convention intuitively since to completely dereference a variable of this type called x, you might say: \*(\*\*x[3][4])[2]. Note that these declaration conventions do not exactly implement the C declaration conventions which are more general and involve brackets. They are used because such expressions are easier to parse than general C type specifiers.

Unions are not currently supported.

<sup>4</sup>detailed in Appendix A

### 2.8 Dynamic Memory Allocation

Dynamic variables may be created at any time by using the same functions as are used for defining static variables in declaration modules. They are distinguished by having a NULL name value. Both dynamic and static variables are stored in the symbol table and are converted during dynamic modification and copied during a migration.

The standard C library malloc and free operations take non-deterministic times, which make them unacceptable for a time critical embedded application. It is also possible that the heap may become fragmented so that requests for storage may fail after the system has been running for some time which is also unacceptable. For these reasons a free storage management scheme based on memory pools is used. The free store consists of a set of pools of free blocks of the same size, with one pool per block size. Allocating a new block consists of searching for the first pool (the pools are kept in a size ordered list) which has a free block large enough and deleting the first element (constant time). Since there is a small fixed number of pools, there is a small upper bound on the time for an allocation. Storage for messages also needs to be allocated dynamically and so a similar mechanism is used as for state variables. As the management of the schedule is performed by the kernel concurrently with the action, there needs to be a separate set of pools for this, known as the system store. Although the system heap allocation/deallocation is only performed by the kernel, the user can specify the heap configuration at slot creation time.

When a slot is created, arrays of pool specifiers are provided for the system and user stores. Each pool specifier consists of the block size and the number of blocks of that size. The system uses this information to initialize the two free stores. A default store configuration is provided so that the user can omit the specification initially. Section 3.3.5 describes the implementation of the heap.

### 2.9 Development Support Environment

In order that the behaviour and performance of the application in vitro be as close as possible to its in vivo state, as much as possible of the development system which will not be present in the live system should be off-loaded onto extra processors available on the development platform. These may be used for simulating external hardware devices and the environment, for off-loading some of the work of monitoring and for providing routing paths back to the root processor.

### 2.9.1 Simulating Hardware and Environment

The concept of simulating external devices using separate processors is suggested in [33] as a way of avoiding perturbing the software under test. This works particularly well with transputers as the external devices are likely to be attached through the same link interface which is used to communicate with other processors. Fortunately these simulation problems have much in common with embedded systems and Testbed is well suited to implementing them. Simulating devices and environment on separate processors from the application also provides an opportunity to perform monitoring on these processors, which does not interfere with the performance of the application system, although care is still needed to ensure that it does not interfere with the performance of the simulation.

### 2.9.2 Using Separate Processors to Reduce Monitoring Overhead

The presence or absence of monitoring software can cause differences in behaviour of the system being monitored, known as the probe effect. Off-loading some of the work involved in monitoring onto separate processors can alleviate the problem. This is the approach taken in [1], where an efficient breakpoint mechanism is used to capture information and pass it to a separate processor where analysis, filtering and logging or reporting back to the user are carried out, while the application is allowed to proceed with minimal interference.

### 2.9.3 Using Extra Routing Nodes to Avoid Interference

Due to the limited number of communication links per transputer, it may be necessary for messages to be routed through intermediate processors to get to their final destination. If these processors are involved in the application then interference may occur, which may be difficult to predict and may make deadlines impossible to guarantee. It is especially undesirable for the messages between processors which will not be present in the target system, such as those used for simulation and monitoring and the root processor, to interfere. This is another example of the probe effect. The problem can be avoided if there are extra processors available which can be used entirely for routing purposes.

### 2.10 Example: Implementing the ROV

The Testbed is particularly suited to the development of reactive embedded systems. The programming model described in this chapter is illustrated with the control software for the submersible Remotely Operated Vehicle (ROV) described in Section 1.1. More than one possibility exists for mapping the control system onto slots. One possibility is to have three slots on two processors, one for the high level control functions which are performed by the surface control module, which has its own processor and two for the low level onboard control functions and status reporting on the other processor. These will be referred to as HIGH\_CONTROL, LOW\_CONTROL and FEEDBACK. Initially it will be assumed that there is a HOST slot which converts operator commands into messages to the HIGH\_CONTROL slot and to which the depth and compass values are reported and an ROV device which accepts motor on/off and direction values from the LOW\_CONTROL slot, without acknowledging and requests for the current depth or compass value from the FEEDBACK slot which result in a reply. Later the method of implementing a user interface and a simulated ROV for testing will be explained. The camera control involves exactly the same sorts of messages and actions as the driving of the vehicle, except that there is no feedback within the system (the video signal is carried back to the monitor by a separate cable). It has been omitted from the implementation described here for simplicity.

#### 2.10.1 Notation

Testbed programs will be described in an Algol-like pseudocode form. For each slot the actions, ports, outgoing messages and pseudocode are presented followed by initialization code. For the ports and messages only the fields which take non-default values are specified. Full C versions of the examples can be found in Appendix C. When a value such as the action corresponding to a port is constant it is indicated using an =, whereas if it may change := is used.

#### 2.10.2 HIGH\_CONTROL

#### **Actions and Ports**

This slot receives separate heading, horizontal and vertical velocity commands from the HOST slot (coming from the joystick and up/down buttons respectively). These are handled by the Heading, H\_Velocity and V\_Velocity actions. Messages which change the autodepth and autoheading status are handled by the AutoDepth and AutoHeading actions. Only the most recent of each of these

message types is of interest, so the corresponding port entry has the max field set to 1 in the following port definitions:

The slot also receives messages carrying depth and compass values from the onboard processor. These are normally handled by the Hold\_Depth and Hold\_Heading actions except when entering or resuming autodepth or autoheading mode when the target depth or heading is reset using the Zero\_Depth or Zero\_Heading actions. As with the messages from the HOST slot only the most recent is relevant, so max is set to 1:

Note that the HIGH\_CONTROL slot is entirely reactive. It only performs actions in response to messages from other slots with no periodic activity scheduled from within the slot. However since the LOW\_CONTROL slot described below periodically sends the depth and compass values, this imposes a periodic behaviour on the HIGH\_CONTROL slot.

### **Outgoing Messages**

Messages are sent to the LOW\_CONTROL slot of the form:

and status messages containing the latest depth and compass readings are sent to the HOST slot:

```

STATUS_REPORT [dest = HOST; port = display_status; data = status]

```

#### Actions