# NANOSCALE CARBON-BASED MEMORY DEVICES

# Submitted by TOBIAS ALBERT BACHMANN

to the

### University of Exeter as a Thesis for the Degree of Doctor of Philosophy in Engineering

in November 2017

This thesis is available for Library use on the understanding that it is copyright material and that no quotation from the thesis may be published without proper acknowledgement.

I certify that all material in this thesis which is not my own work has been identified and that no material has previously been submitted and approved for the award of a degree by this or any other University.

Signature: \_\_\_\_\_

to my family

## List of Publications

- W. W. Koelmans, T. Bachmann, F. Zipoli, A. K. Ott, C. Dou, A. C. Ferrari, O. Cojocaru-Mirédin, S. Zhang, C. Scheu, M. Wuttig, V. K. Nagareddy, M. F. Craciun, A. M. Alexeev, C. D. Wright, V. P. Jonnalagadda, A. Curioni, A. Sebastian, and E. Eleftheriou, "Carbon-Based Resistive Memories," in 2016 *IEEE 8<sup>th</sup> International Memory Workshop (IMW)*, pp. 1–4, IEEE, 2016. DOI: 10.1109/IMW.2016.7493569

- T. A. Bachmann, A. M. Alexeev, W. W. Koelmans, F. Zipoli, A. K. Ott, C. Duo, A. C. Ferrari, V. K. Nagareddy, M. F. Craciun, V. P. Jonnalagadda, A. Curioni, A. Sebastian, E. Eleftheriou, and C. D. Wright, "Joule Heating Effects in Nanoscale Carbon-based Memory Devices," in 2016 *IEEE Nanotechnology Materials and Devices Conference (NMDC).*, pp. 1–2, IEEE, 2016. DOI: 10.1109/NMDC.2016.7777081

- T. A. Bachmann, A. M. Alexeev, W. W. Koelmans, F. Zipoli, A. K. Ott, C. Duo, A. C. Ferrari, V. K. Nagareddy, M. F. Craciun, V. P. Jonnalagadda, A. Curioni, A. Sebastian, E. Eleftheriou, and C. D. Wright, "Temperature Evolution in Nanoscale Carbon-Based Memory Devices due to Local Joule Heating," in 2017 *IEEE Transactions on Nanotechnology*. IEEE, 2017. DOI: 10.1109/TNANO.2017.2674303

- T. A. Bachmann, W. W. Koelmans, V. P. Jonnalagadda, M. Le Gallo, C. A. Santini, A. Sebastian, E. Eleftheriou, M. F. Craciun and C. D. Wright, "Memristive Effects in Oxygenated Amorphous Carbon Nanodevices," in 2017 *Nanotechnology.*, vol. 29, no. 3, p. 035201, 2017. *DOI: 10.1088/1361-6528/aa9a18*

### **Attended Conferences & Events**

- European Workshop on Non-Volatile Memories, Forschungszentrum Jülich, Germany, November 2014.

- *Chalcogenide Advanced Manufacturing Partnership (ChAMP)*, University of Southampton, United Kingdom, March 2015.

- CareRAMM Project Progress Meeting, IBM Zurich Research Lab, Zurich, Switzerland, January 2015, Title: sp<sup>2</sup> / sp<sup>3</sup> Cluster Distribution in ta-C for Finite Element Modelling (Oral presentation).

- *CareRAMM Project Progress Meeting*, University of Exeter, Exeter, United Kingdom, June 2015, *Title: Electrical Switching in Ta-C Confined Cell Devices* (Oral presentation).

- CareRAMM Project Progress Meeting and Final Review, European Commission, Brussels, Belgium, January 2016, *Title: Memory Performance Assessment* (Speaker: W. W. Koelmans).

- *CareRAMM Project Progress Meeting and Final Review*, European Commission, Brussels, Belgium, January 2016, *Title: Electro-Thermal Modelling of a-C* (Speaker: A. M. Alexeev).

- IFF Spring School "Memristive Phenomena From Fundamental Physics to Neuromorphic Computing", Forschungszentrum Jülich, Germany, February / March 2016.

IEEE Nanotechnology Materials and Devices Conference (NMDC), Toulouse, France, October 2016, Title: Joule Heating Effects in Nanoscale Carbon-Based Memory Devices (Oral presentation).

## Acknowledgement

First, I would like to thank my family for their constant support throughout my life. Without their support, it would not have been possible to dedicate so many years to research, which ultimately led to this thesis.

I would like to express my deepest gratitude to Prof. C. David Wright for giving me the opportunity to work in the exciting field of emerging memory technologies under his supervision. The guidance and support I have received throughout the thesis is truly remarkable. Further, I would like to thank Prof. Monica Craciun and Dr. David Horsell for further guidance and support during the initial stages of my PhD.

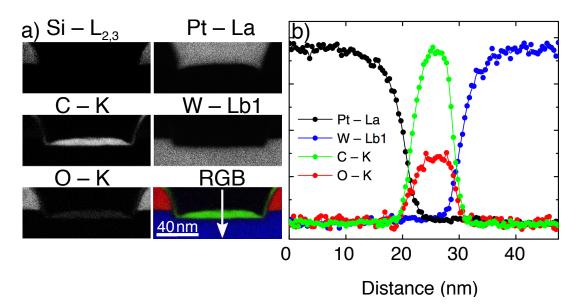

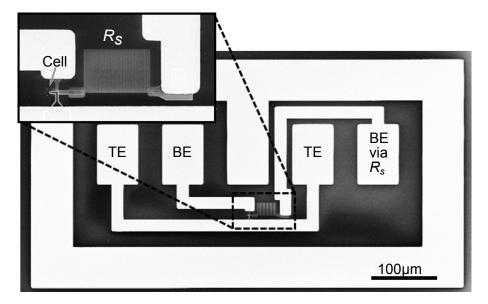

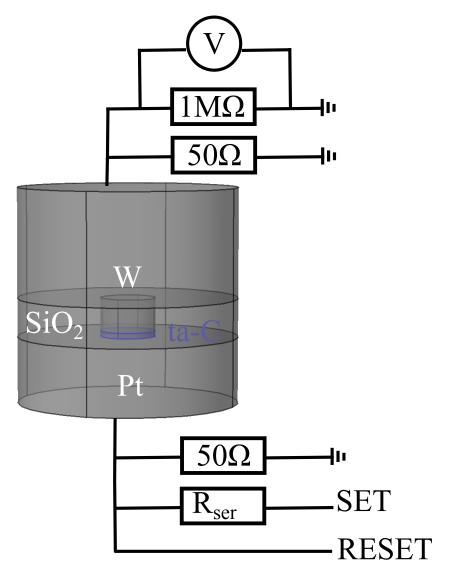

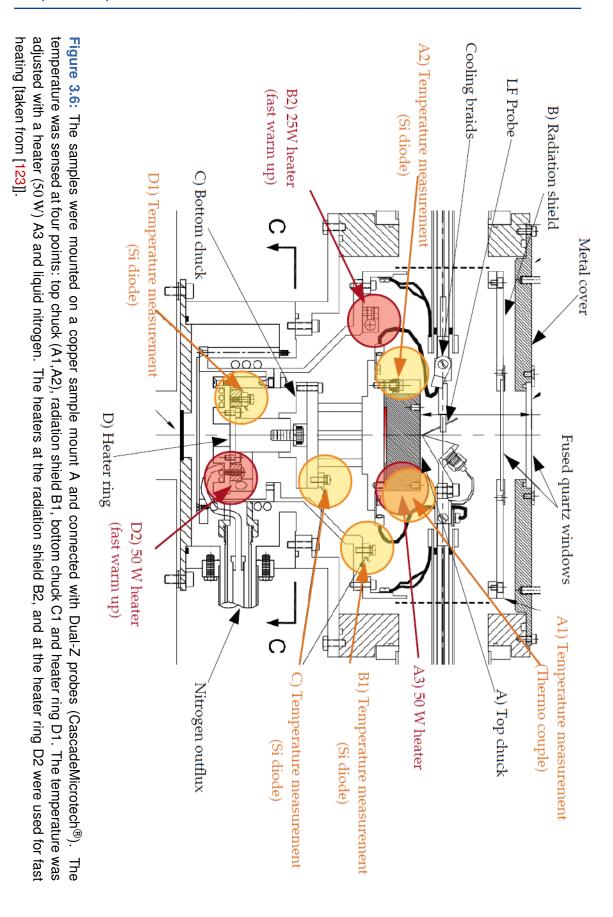

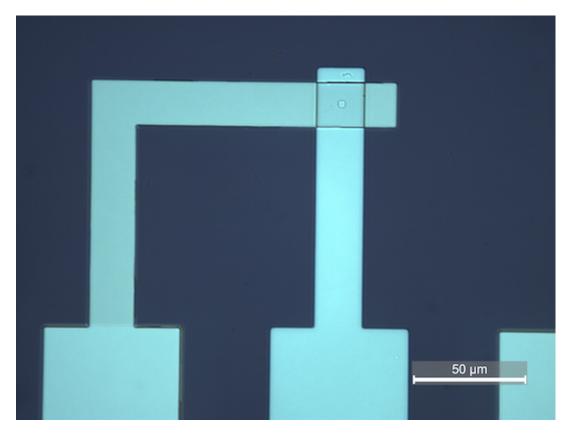

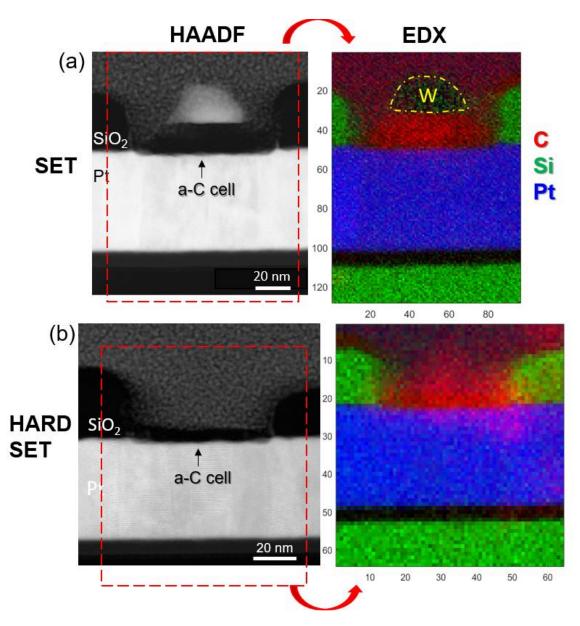

My deep gratitude goes to our collaborators from IBM Research Zurich, where I was given the opportunity to spent eight months as part of the European Union funded Careramm project. In particular, I would like to thank Dr. Abu Sebastian and Dr. Evangelos Eletheriou for the guidance and support I received throughout my stay. I would like to acknowledge Dr. Wabe Koelmans (IBM Research Zurich) who designed the tetrahedral amorphous carbon and oxygenated amorphous carbon devices presented in Section 3.1.3, and Dr. Anna Ott (University of Cambridge) and Vara Prasad Jonnalagadda (IBM Research Zurich) for the fabrication and Raman characterisation of the oxygenated amorphous carbon devices and the fabrication and XPS characterisation of the oxygenated amorphous carbon devices (Section 3.1). Further, I would like to acknowledge Dr. Arseny Alexeev (University of Exeter) for the help with the finite element modelling in Section 5, and Manuel Le Gallo and Urs Egger (both IBM Research Zurich) for the help with the setup used for the experiments in Chapters 4, 5 and 6. Additionally, I would like to acknowledge Dr. Oana Cojocaru-Mirédin (RWTH Aachen) for the TEM and STEM imaging, and the EELS and EDX analysis in Section 4.6.

I would like to thank Dr. Federico Zipoli (IBM Research Zurich) for fruitful discussions regarding the temperature distribution in tetrahedral amorphous carbon cells in Section 5.4, as well as Dr. Christophe Rossell (IBM Research Zurich) and Martin Rütten (RWTH Aachen) for the fruitful discussions about electrical switching in amorphous semiconductors.

A big thank you goes to all colleagues in the research group, and foremost to Dr. Hasan Hayat and Dr. Mustafa Aziz for fruitful discussions regarding finite element modelling, and to Dr. V. Karthik Nagareddy for insightful discussions about the fabrication process. Further, I would like to thank Prof. Gino Hrkac for the mentoring and his very valuable advice throughout all stages of my PhD.

Last but certainly not least, I would like to thank all friends in Exeter and abroad for their inspiration and true friendship.

# **Abbreviations**

| Central Processing Unit                             | CPU      |

|-----------------------------------------------------|----------|

| Static-Random Access Memory                         | SRAM     |

| Dynamic-Random Access Memory                        | DRAM     |

| Storage-Class Memory                                | SCM      |

| International Technology Roadmap for Semiconductors | ITRS     |

| Metal-Oxide-Semiconductor Field-Effect Transistor   | MOSFET   |

| Ferroelectric Random-Access Memory                  | FeRAM    |

| Phase-Change Random-Access Memory                   | PRAM     |

| Ovonic Threshold Switch                             | OTS      |

| Magnetic Random-Access Memory                       | MRAM     |

| Magnetic Tunnel Junction                            | MTJ      |

| Spin Transfer Torque Random-Access Memory           | STT-MRAM |

| Multi-Level Cell                                    | MLC      |

| Conductive Bridging Memory                          | CBRAM    |

| Redox-Based Resistive Random-Access Memory          | ReRAM    |

| Low Resistance State                                | LRS      |

| High Resistance State                               | HRS      |

| Valence Change Memory                           | VCM      |

|-------------------------------------------------|----------|

| Thermochemical Memory                           | TCM      |

| Amorphous Carbon                                | a-C      |

| Tetrahedral Amorphous Carbon                    | ta-C     |

| Diamond-Like Carbon                             | DLC      |

| Filtered Cathodic Vacuum Arc                    | FCVA     |

| Pulsed Laser Deposition                         | PLD      |

| Mass Selected Ion Beam                          | MSIB     |

| Direct Current                                  | DC       |

| Radio Frequency                                 | RF       |

| Ultra-Violet                                    | UV       |

| Density-Of-States                               | DOS      |

| Variable-Range Hopping                          | VRH      |

| Trap-Limited Band (Transport)                   | TLB      |

| Molecular Dynamic                               | MD       |

| Seventh Framework Programme                     | FP7      |

| Carbon Resistive Random Access Memory Materials | CareRAMM |

| Oxygenated Amorphous Carbon                     | $a-CO_x$ |

| Device-Under-Test                               | DUT      |

| Finite Element                                  | FE       |

| Energy-Dispersive X-ray Spectroscopy            | EDX      |

| (Scanning) Transmission Electron Microscope | (S)TEM |

|---------------------------------------------|--------|

| High-Angle Annular Dark Field               | HAADF  |

## Abstract

Amorphous carbon-based memories have gained traction in recent years due to their good scalability and switching performance and are an important contender to close the performance gap between fast but volatile DRAM and slow but non-volatile flash memory. A writing and erasing process driven by the electrically induced formation and rupture of a conductive filament permits switching times in the range of a few nanoseconds. Further, the memristive property of amorphous carbon allows the implementation of beyond von Neumann computation paradigms. However, 'pure' amorphous memories have a low cyclic endurance. To overcome this and to exploit beyond von Neumann computation, devices based on oxygenated amorphous carbon were employed here.

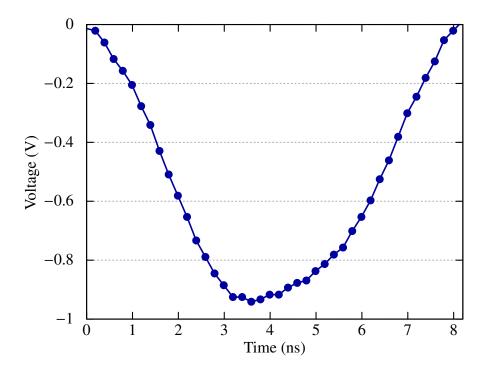

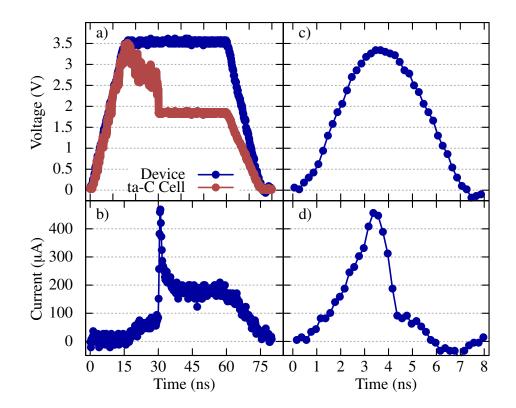

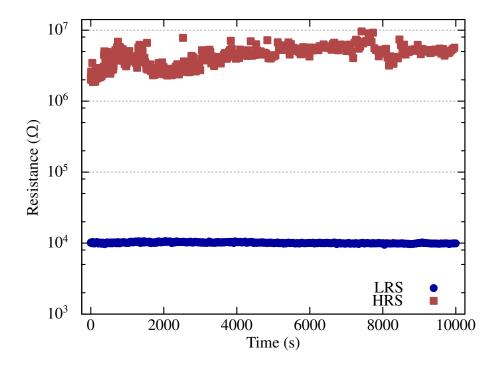

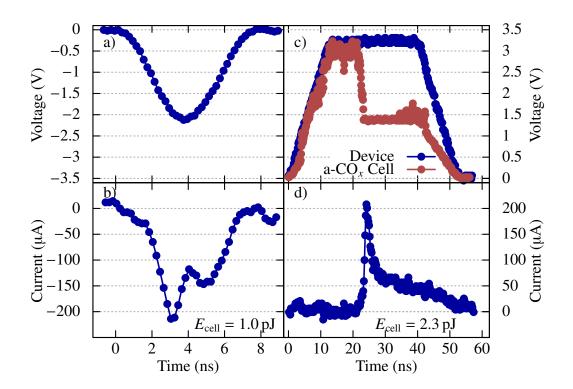

The first part of this thesis evaluated the switching performance and data retention capabilities of tetrahedral amorphous carbon memories. Switching times below 10 ns were achieved for the SET as well as for the RESET times. An energy consumption below 1 pJ was obtained, while data could be retained for more than 300 s at 450 °C. Further, evidence was provided that the SET process is not induced by an electric field alone.

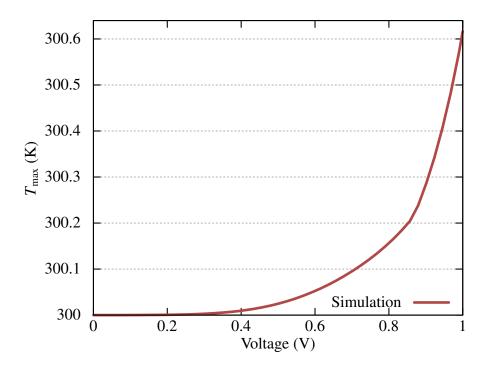

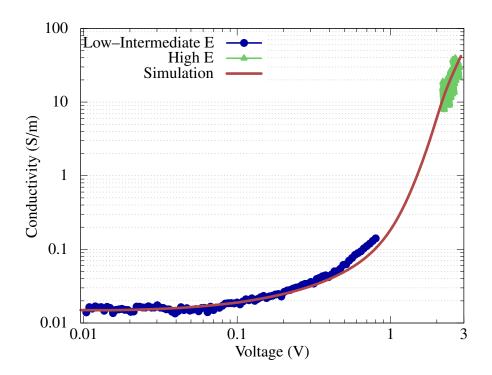

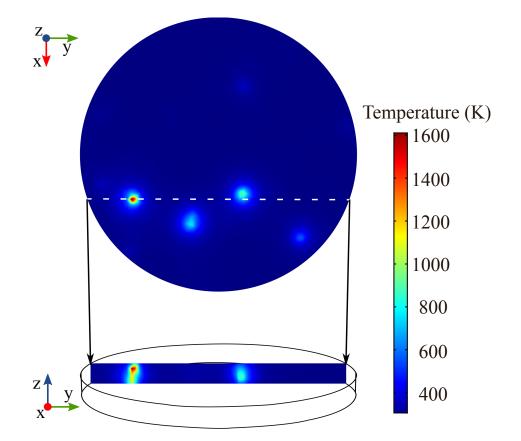

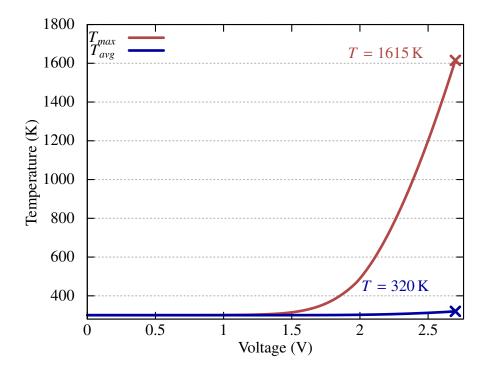

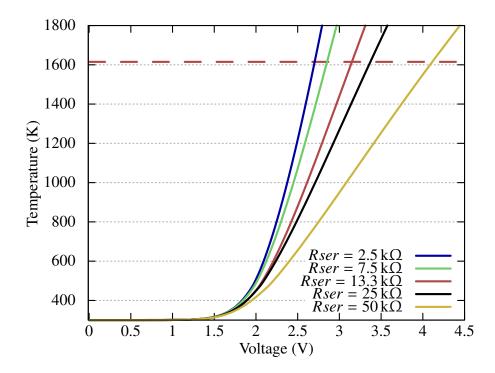

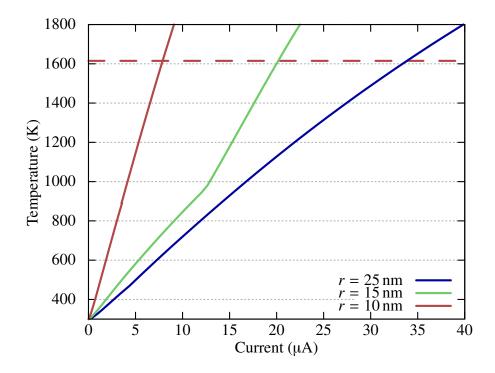

A finite-element simulation was employed in the second part of this thesis to reproduce the experimentally determined conductivity of tetrahedral amorphous carbon (ta-C) memory devices and to shine light on the conditions at the onset switching from the high to low resistance states (dielectric breakdown). The maximum temperature observed at dielectric breakdown was 1615 K. It was found that a reduction of the lateral cell radius from

25 nm to 15 nm and 10 nm increases the switching performance by reducing the switching current from  $34 \,\mu\text{A}$  to  $20 \,\mu\text{A}$  and  $8 \,\mu\text{A}$ .

The third part of this thesis evaluated the switching performance, temperature stability, multilevel storage and memcomputing capabilities of oxygenated amorphous carbon. Switching times below 10 ns for both, SET and RESET were demonstrated. A 3-level  $(1^{1}/_{2})$  bits) data storage was achieved using three different resistance states. Further, a memcomputing approach was implemented using a base-16 accumulation response with energy consumptions as low as <100 fJ per pulse. Additionally, a finite element simulation of a device in the low resistance state (LRS) was used to illustrate the correlation between device resistance and Joule heating effects.

# Contents

| 1 | Introduction |                                                |  |

|---|--------------|------------------------------------------------|--|

|   | 1.1          | Motivation                                     |  |

|   | 1.2          | Traditional Memory Technologies                |  |

|   | 1.3          | Prototypical Storage Technologies              |  |

|   | 1.4          | Emerging Storage Technologies                  |  |

|   | 1.5          | Comparison of Non-Volatile Memory Technologies |  |

|   | 1.6          | Beyond von Neumann Computation                 |  |

|   | 1.7          | Thesis Objectives                              |  |

|   | 1.8          | Thesis Outline                                 |  |

| 2 | Insi         | ulating Amorphous Carbons 25                   |  |

|   |              |                                                |  |

|   | 2.1          | Introduction                                   |  |

|   | 2.2          | Deposition Methods                             |  |

|   | 2.3          | Spectroscopic Characterisation                 |  |

|   | 2.4          | Electronic Transport                           |  |

|   |              | 2.4.1 Density of States                        |  |

|   |              | 2.4.2 Low Electric Field Transport             |  |

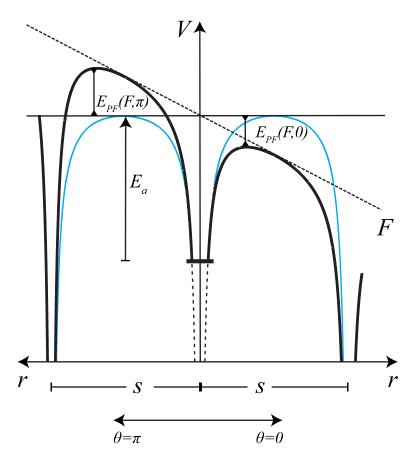

|   |              | 2.4.3 Field Enhanced Transport                 |  |

|   | 2.5          | Resistive Switching Mechanism                  |  |

|   |              | 2.5.1 SET Process                              |  |

|   |              | 2.5.2 RESET Process                            |  |

|   | 2.6          | State-of-the Art Benchmarks                    |  |

| 3 | Ехр  | erimen   | tal & Simulation Methods                                                                 | 55  |

|---|------|----------|------------------------------------------------------------------------------------------|-----|

|   | 3.1  | Experi   | ments                                                                                    | 56  |

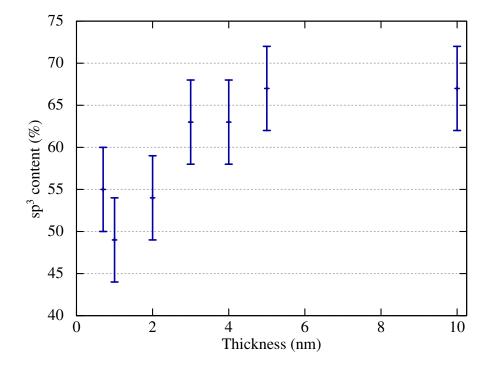

|   |      | 3.1.1    | Tetrahedral Amorphous Carbon (ta-C)                                                      | 56  |

|   |      | 3.1.2    | Oxygenated Amorphous Carbon $(a-CO_x)$                                                   | 59  |

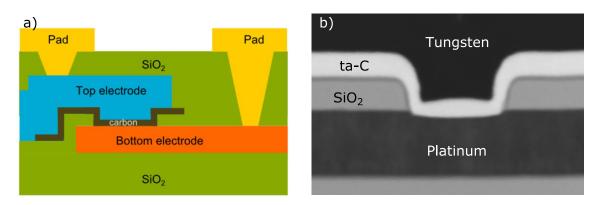

|   |      | 3.1.3    | Device Design                                                                            | 61  |

|   |      | 3.1.4    | Device Test Setup                                                                        | 62  |

|   | 3.2  | Finite   | Element (FE) Simulations                                                                 | 67  |

|   |      | 3.2.1    | Electro-Thermal Model                                                                    | 68  |

|   |      | 3.2.2    | ta-C Device Modelling                                                                    | 69  |

|   |      | 3.2.3    | a-CO <sub>x</sub> Device Modelling $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 73  |

|   |      | 3.2.4    | Simulation Parameters                                                                    | 76  |

|   |      | 3.2.5    | Summary                                                                                  | 78  |

| 4 | Tetr | ahedra   | I Amorphous Carbon (ta-C) Devices                                                        | 79  |

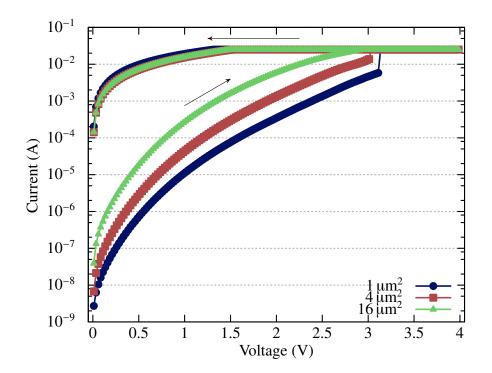

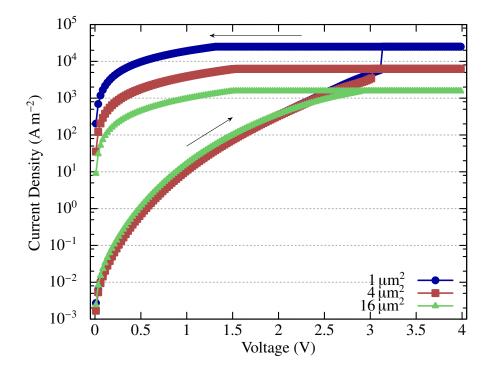

|   | 4.1  |          | Characterisation                                                                         | 81  |

|   |      | 4.1.1    | Area Dependence                                                                          | 81  |

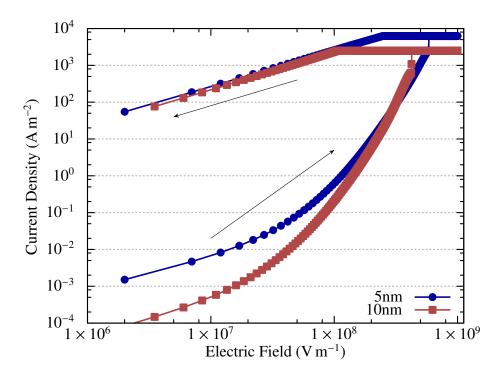

|   |      | 4.1.2    | Electric Field Dependence                                                                | 83  |

|   | 4.2  |          | lar Switching                                                                            | 85  |

|   | 4.3  | 1        | Retention                                                                                | 87  |

|   | 4.4  |          | ning Endurance                                                                           | 91  |

|   | 4.5  |          | Characteristics                                                                          | 92  |

|   | 4.6  |          | ntal Analysis and Bonding Ratio                                                          | 96  |

|   | 4.7  |          |                                                                                          | 102 |

|   | 4.8  |          | ary & Conclusion                                                                         |     |

|   |      | ~        |                                                                                          | 100 |

| 5 | Jou  | le Heati | ing Effects in ta-C Devices                                                              | 109 |

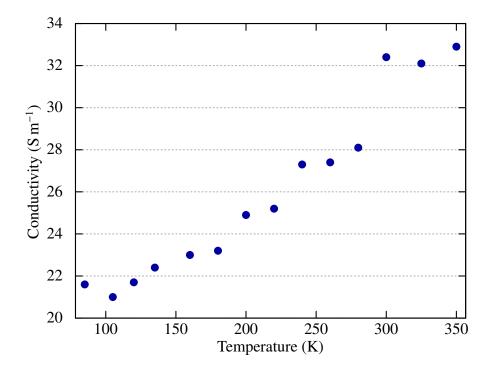

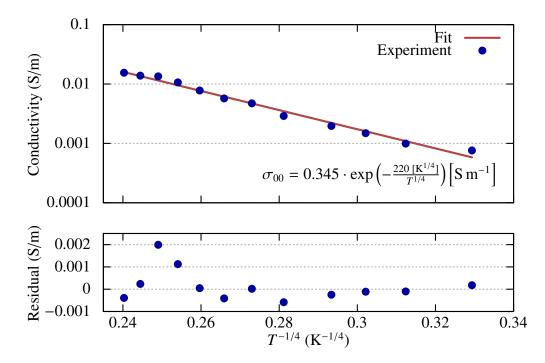

|   | 5.1  | Tempe    | erature-Dependent Conductivity                                                           | 110 |

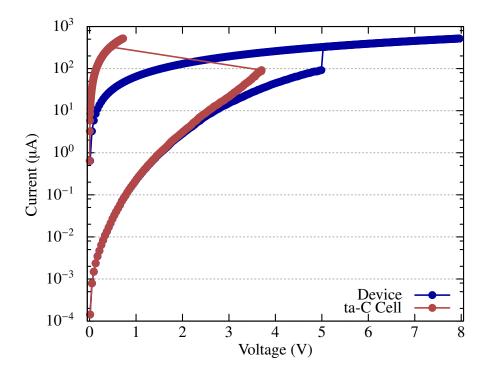

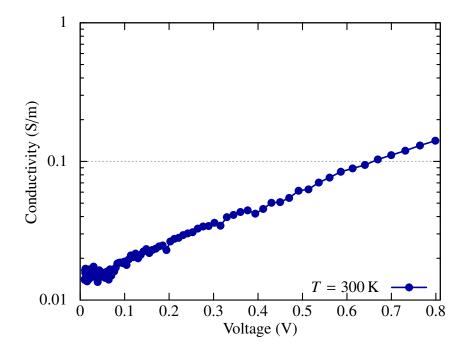

|   | 5.2  | Electric Field-Dependent Conductivity                 | 112   |

|---|------|-------------------------------------------------------|-------|

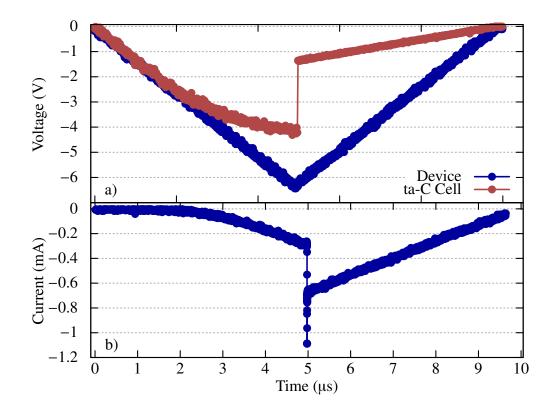

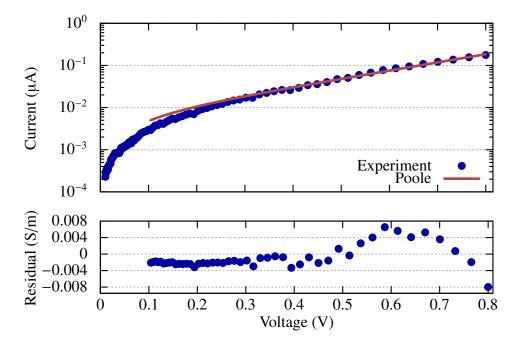

|   | 5.3  | Model Validation                                      | 116   |

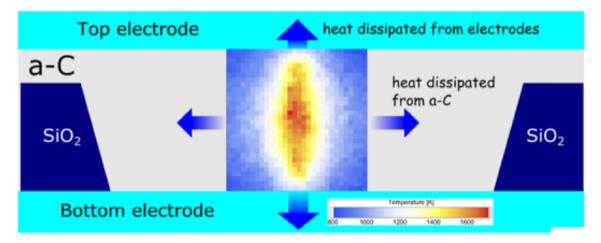

|   | 5.4  | Temperature Distribution at Dielectric Breakdown      | 120   |

|   | 5.5  | Influence of Load Resistor                            | 123   |

|   | 5.6  | Influence of Confined-Cell Lateral Dimension          | 125   |

|   | 5.7  | Summary & Conclusion                                  | 126   |

|   |      |                                                       |       |

| 6 | Оху  | genated Amorphous Carbon (a-CO <sub>x</sub> ) Devices | 129   |

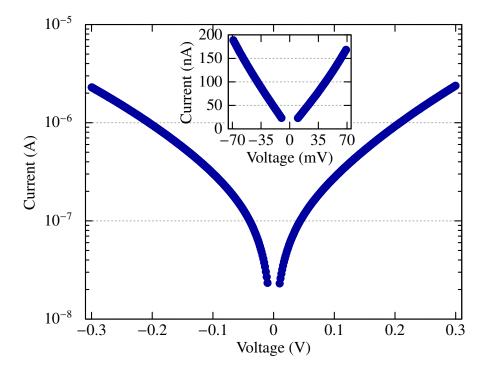

|   | 6.1  | Switching Characteristics                             | 131   |

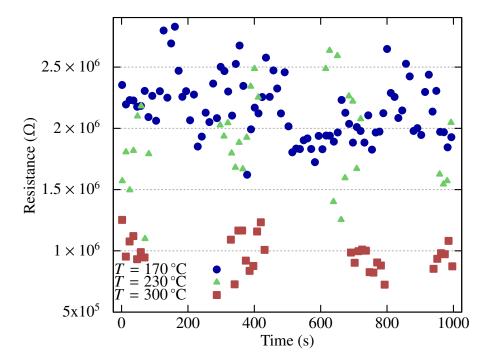

|   | 6.2  | Thermal Annealing                                     | 133   |

|   | 6.3  | Multilevel States                                     | 135   |

|   | 6.4  | Memristive Effects                                    | 136   |

|   | 6.5  | Low Energy Memcomputing                               | 138   |

|   | 6.6  | Thermal Analysis                                      | 142   |

|   | 6.7  | Summary & Conclusion                                  | 146   |

| - | 0    |                                                       | 4 4 7 |

| 7 | Con  | clusions & Future Work                                | 147   |

|   | 7.1  | Conclusions                                           |       |

|   | 7.2  | Future Work                                           | 152   |

| Α | MD : | Simulations                                           | 153   |

|   | A.1  | Dihedral Angle                                        | 153   |

|   |      |                                                       |       |

|   | A.2  | Thermostat                                            |       |

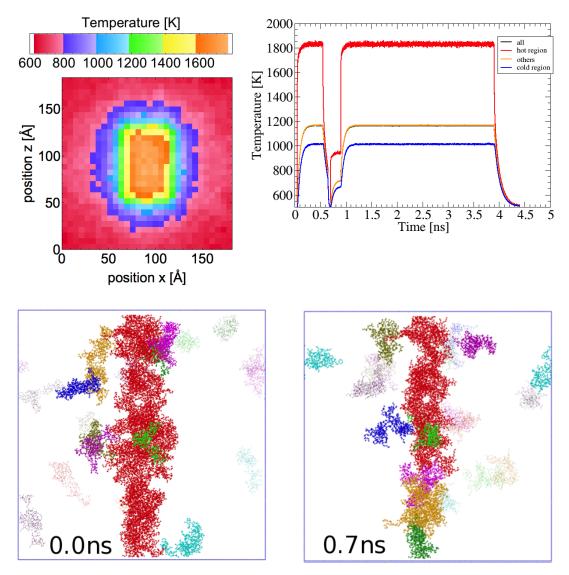

|   | A.3  | SET Process                                           | 157   |

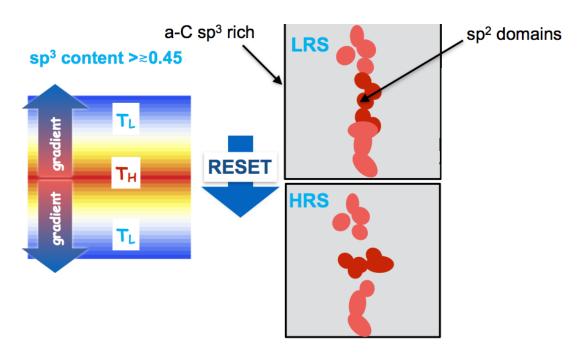

|   | A.4  | RESET Process                                         | 160   |

|   | A.5  | Summary                                               | 162   |

| В   | Device Characterisation |                                        |      |  |  |

|-----|-------------------------|----------------------------------------|------|--|--|

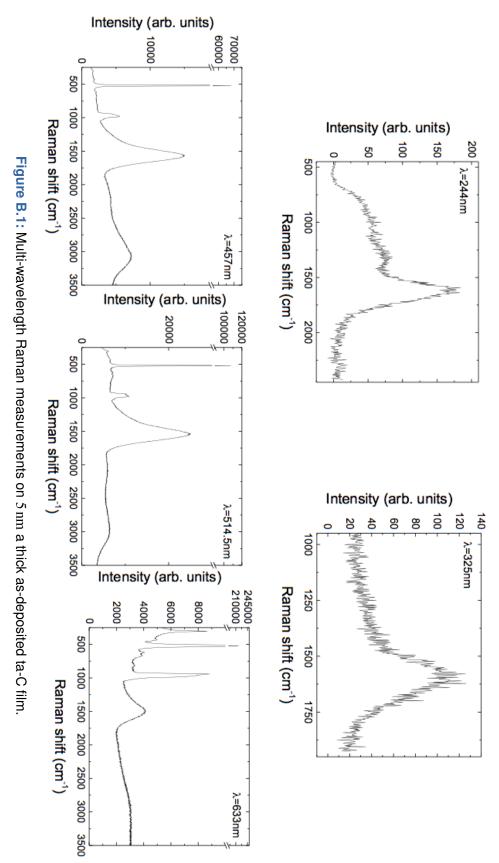

|     | <b>B</b> .1             | Raman Spectroscopy                     | 163  |  |  |

|     | B.2                     | Cross-Bar Devices                      | 166  |  |  |

|     | B.3                     | Confined-Cell Devices                  | 167  |  |  |

|     | B.4                     | X-ray Photoelectron Spectroscopy (XPS) | 168  |  |  |

| Lis | st of F                 | igures                                 | I    |  |  |

| Lis | st of 1                 | ables                                  | XIII |  |  |

| Bil | Bibliography            |                                        |      |  |  |

# **Chapter 1**

## Introduction

#### **1.1 Motivation**

In recent years, the extent to which electronic communication devices have revolutionised our daily life in the form of smartphones, laptops, on demand streaming services, to name a few, is truly striking. This technological revolution was only possible due to ever increasing computational power being available at lower costs, lower energy and power consumption and in smaller and smaller dimensions. The driving force behind this success story is the doubling of the number of transistors that can be integrated in chips every 18 months to 24 months, which has been described as Moore's law [1, 2].

With electronic devices pervading almost every aspect of our lives, the demand for high density, cheap, fast and energy efficient data storage becomes increasingly important. To balance the trade-off for cheap, high density data storage on one hand, and the need for fast access, high performing storage devices on the other hand, different types of memories are currently employed. The size of a given memory design is expressed by its lateral dimensions in multiples of  $F^2$ , where F is the smallest lithographic feature size [3]. An often used criterion that allows one to split different types of memories into two categories is the capability to retain data.

High performance memory is located in close proximity to the central processing unit (CPU) and requires constant power supply to retain the data and hence, falls into the category of volatile memory. The volatile memory that is typically used for fast CPU access and caching is static-random access memory (SRAM) [4]. One level lower in the hierarchy of memories is dynamic-random access memory (DRAM) which is more compact in comparison to SRAM, but slower due to periodical refresh operations that have to be carried out to account for charge leakage [3, 5].

One step lower in the memory hierarchy are memories that fall into the second category and are non-volatile. Non-volatile memories have longer read, write and erase times, but can retain data without refreshing cycles or a constant power supply [6]. They are cheaper in fabrication and offer a higher storage density due to a compact design.

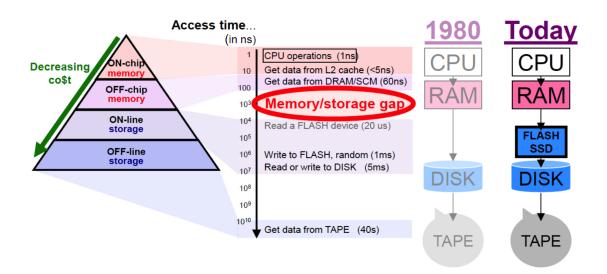

The most ubiquitous current non-volatile memory devices are those based around CMOS Flash technology. However, the speed difference between accessing DRAM and the write-cycle time of Flash is around 4 orders of magnitude, which causes a significant delay between performing logic operations (CPU) and storing the resulting data [7]. The access time for different memory technologies is given in a memory hierarchy diagram in Figure 1.1 [7].

In addition to the speed limitations of Flash-based memory, also the number of re-write processes (endurance cycles) is limited to around 1000 [8]. To fill the performance gap between DRAM and Flash in the memory hierarchy a new class of memory is required. This class of memory is referred to as storage-class memory (SCM) [7]. The limitations of DRAM and NAND Flash are compared in Table 1.1, together with the demands for SCM.

The most promising memory candidates that have the potential to bridge the performance

Figure 1.1: Memory hierarchy and target application for storage-class memory (SCM) [11, 12].

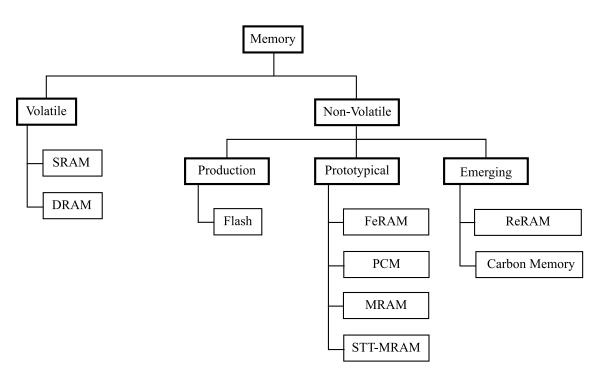

gap between fast, but volatile memory and traditional non-volatile memories are shown in the memory taxonomy in Figure 1.2, which is an adapted version of the International Technology Roadmap for Semiconductors (ITRS) [9, 10]. The non-volatile memories are split according to their current development state into prototypical and emerging memories. An overview of prototypical and emerging SCMs is provided in Sections 1.3 and 1.4, with the focus on technical approach, performance, data storage characteristics, energy consumption and scalability.

Figure 1.2: Memory taxonomy showing the most relevant memories according to the International Roadmap for Semiconductors [modified from [9, 10, 12]].

Table 1.1: Comparison of DRAM and NAND Flash and requirements of SCM [adapted from [12]]

|                           | DRAM              | NAND Flash                 | Memory (SCM)    |

|---------------------------|-------------------|----------------------------|-----------------|

| Maturity                  | Production        | Production                 | _               |

| Read/Write<br>Latency     | <100 ns           | 100 μs<br>Block Erase 1 ms | 5 µs            |

| Retention<br>Time @ 85 °C | 64 ms             | 10 yrs                     | 10 yrs          |

| Endurance<br>Cycles       | >10 <sup>16</sup> | $10^{3}-10^{5}$            | 10 <sup>6</sup> |

| Write Energy<br>per Bit   | 100 pJ            | 100 pJ                     | 100 pJ          |

| Scalability               | poor              | limited (3D)               | _               |

### **1.2 Traditional Memory Technologies**

**Dynamic Random-Access Memory (DRAM)** Dynamic random-access memory (DRAM) is based on charge stored in a capacitor [3]. The access to the storage capacitor is controlled by a transistor to which the (conducting) wordline is connected. During the writing process, the transistor is in forward bias, which allows one to store charge in the capacitor (logic '1') [3, 4]. The erase process discharges the capacitor (logic '0') [3]. The read out of the state of the device is done by applying a reference voltage to the (conducting) bitline – which is orthogonal to the wordline – and sensing the voltage change of the bitline when the capacitor is accessed [3, 4]. In the case that no charge was stored on the capacitor (logic '0'), charge is drawn from the bitline, thus reducing the voltage on the bitline (and vice-versa in the case that the capacitor was charged) [3]. Since the read out is destructive, the addressed cell has to be re-written in the case that a logic '1' was stored [3]. Due to leakage current from the capacitor, cyclic re-freshing of the device state is also required [13].

**Flash** Flash memory is commercially available in two main categories, NOR Flash and NAND Flash [14]. NOR Flash allows one to access stored data randomly, which is in contrast to NAND Flash where data blocks are accessed sequentially. However, NOR Flash has slower writing times and storage density and is therefore commercially less relevant for large data storage applications [14]. Similar to DRAM, Flash memory is based on stored charge in a capacitor [13]. The top electrode (control gate) is connected to the word line and the bottom electrode (floating gate) is surrounded by an insulating oxide on top of a metal-oxide-semiconductor field-effect transistor (MOSFET) channel [14]. To store electrons in the floating gate, a positive bias is applied to the control gate (logic '0') which allows electrons to tunnel through the dielectric [14]. The erase process (logic '1')

requires a positive bias applied to the substrate to discharge the capacitor [14]. To read out the device state, a positive bias (smaller than used for programming) is applied to the control gate and the current response through the transistor channel is sensed [14].

### **1.3 Prototypical Storage Technologies**

**Ferroelectric Random-Access Memory (FeRAM)** Memory based on ferroelectric materials (FeRAM) is based on the polarisation of the ferroelectric [15]. A typical FeRAM cell is composed of a capacitor cell, whereby the polarisation of the dielectric is altered by charging/discharging cycles of the capacitor during the write and erase procedures [15]. The device selection is carried out using a transistor [15]. The read out of the device state is done by draining the capacitor and evaluating the charge flow, which depends on the polarisation of the ferroelectric and hence, allows the determination of the stored logic state [16]. Due to the destructive nature of the read out process, it is necessary to re-write the data if the read out bit was '1' [13].

**Phase-Change Random-Access Memory (PRAM)** Phase-change random-access memory (PRAM) is based on the phase switching of chalcogenides from an amorphous to a crystalline phase [17]. The amorphous phase has a high electrical resistance in comparison to the crystalline phase [18]. The write process that switches the device from logic '0' in the high resistive amorphous state to logic '1' in the low resistive crystalline state is achieved using short electrical pulses that heat the material above its crystallisation temperature but below the melting temperature [7]. The erase process is carried out by applying short electric pulses that heat the material above its melting temperature, followed by rapid cooling which re-amorphises the material [19, 20]. The highly non-linear current-voltage dependence ensures that the temperatures remain low during the read out

processes [21]. The device access is typically done using a transistor, a diode [22] or an Ovonic Threshold Switch (OTS) [23].

Despite progress in the fabrication of sublithographic PRAM structures [24], the main drawback of PRAM remains its high power consumption which is necessary to melt the material during the switching process [25].

**Magnetic Random-Access Memory (MRAM)** Traditional magnetic random-access memory is based on a magnetic tunnel junction (MTJ) or spin valves formed by an insulating layer that is sandwiched between two magnetic layers [16, 26]. One of the two magnetic layers is ferromagnetic and has a fixed spin orientation, while the spin orientation of the free layer can be manipulated. The magnetisation of the free layer is changed by passing sufficiently large currents through two lines ( 'bit' and 'digit') that are adjacent to the stack and induce a sufficiently large magnetic field to change the magnetisation of the free layer [26, 27]. This allows one to store data by using the electron spin orientation [5]. The read out is done by measuring the resistance across the MTJ stack, which depends on the orientation of the magnetic moments of the fixed layer and the free layer. A parallel orientation of the magnetic moments has a high tunnelling probability and hence, a low resistance corresponding to logic '1', while an antiparallel orientation of the magnetic moments results in a high electric resistance which corresponds to logic '0' [16].

The advantages of MRAM are fast switching, comparable to SRAM and high cyclic endurance [26]. The main challenges are related to scaling, due to the potential overlap of the induced magnetic fields that are required for the writing process, which can, aided by the low resistance contrast between the high resistive and low resistive state, lead to writing errors [13, 28]. **Spin Transfer Torque Random-Access Memory (STT-MRAM)** Instead of the magnetic field used in conventional MRAM, a polarised current is directly applied to the MTJ cell [29]. For writing, the control of the magnetisation of the free layer using a polarised current means that STT-MRAM is much better suited than conventional MRAM to down-scaling, since 'free-space' fields are no longer required for switching [29].

To employ STT-MRAM as SCM, the main challenge is to reduce the cost per bit and to achieve a high density integration [15]. The main difficulties in these respects are the need for a transistor as device selector and the low on/off ratio (i.e. high resistance contrast between LRS and HRS) which makes MLC data storage, i.e. the storage of several bits per cell, in STT-MRAM difficult [15].

### **1.4 Emerging Storage Technologies**

**Conductive Bridging Memory (CBRAM)** Conductive bridging memory (or electrochemical metallization memory [25]) belongs to the class of redox-based resistive randomaccess memories (ReRAMs). The characterising feature of ReRAMs is the movement of ions that combined with local structural changes lead to the formation and rupture of a conductive filament. This change in electrical resistance is non-volatile and typically reversible. In CBRAM the resistance change is based on the formation of a conductive metal filament that forms a percolation path within a solid electrolyte that separates two electrodes [13, 15]. The conductive filament starts to form in the presence of an electric field as a consequence of a redox reaction at the active metal electrode / electrolyte interface [25]. The metallic filament grows from the cathode towards the anode, due to the diffusion of mobile metal cations to the inert metal cathode, where they are reduced [25]. The device is switched into a low resistance state (LRS) (logic '1'), when the metallic filament formed bridges the two electrodes. The device is switched back into a high resistance state (HRS) (logic '0') by reversing the polarity of the applied electric field, which dissolves the filament or at least a part of it [30]. This bipolar operation mode is in contrast to the unipolar operation mode, where SET and RESET processes are induced by voltage pulses of the same polarity (the switching process from the HRS into the LRS is called SET process, while the reversible switching process from the LRS into the HRS is referred to as the RESET process). The device state is read out using small voltages that do not affect the state of the device [30].

Due to the solid electrolyte, CBRAM has a good on/off ratio and offers good scaling capabilities [25]. However, the bipolar operation mode makes high density integration challenging. Furthermore, endurance and retention properties still show a large variability from device to device, which is partly due to the chemical potential gradients in the cell that can shift the voltages that are required to switch the cell into the LRS or HRS [25, 31].

**Valence Change Memory (VCM)** Another type of ReRAM is valence change memory (VCM), which is based on the formation of a conductive filament due to the movement of mobile anions in a thin oxide layer that is sandwiched between two inert electrodes [25, 32]. The filament starts to form at the cathode where the formation of oxygen vacancies leads to a valence change and a reduction of the metal cations, which then form a conductive path that grows towards the anode [30, 33]. The conductive filament is typically based on the formation of oxygen vacancies, which is in contrast to CBRAM. The device is switched into the LRS (logic '1'), when the conductive filament connects the two electrodes. Typically, the first switching into the LRS requires a forming pulse using a high voltage to establish the conductive filament. The device is RESET into the HRS

(logic '0') using a reverse polarity [32]. As a consequence of the rupture of the conductive filament (and not complete dissolution) during the RESET process, the HRS has typically a lower resistance than pristine devices [34]. Recently however, forming-free devices were reported [35, 36]. The device state is read out using small voltages that do not affect the state of the device.

If one (chemically) active electrode is used, the switching mechanism changes from filamentary to interface dominated due to the redox reaction taking place at the oxide/active metal interface, and the resistance of the LRS scales with the active electrode area [32].

**Thermochemical Memory (TCM)** Another branch of ReRAMs are thermochemical memories (TCMs), which are based on thermally controlled diffusion and redox processes [37] and thus can be operated in a unipolar manner [25]. The unipolar operation mode sets TCM apart from VCM, which require a bipolar operation mode. Thermochemical memories typically consist of a binary oxide that is sandwiched between two inert metal electrodes [25]. During the SET pulse two conductive filaments start forming from both electrodes and the device is set into the LRS when both conductive filaments merge, creating a conductive percolation path between the two electrodes [25]. The conductive filaments of either an oxygen vacancy defect chain or a metallic filament due to the formation of oxygen vacancies along with a reduction of the metal cations [25, 38]. The reverse switching from the LRS into the HRS occurs then due to oxygen diffusion and local re-oxidation of the conductive filament or by the thermally induced rupture of the metallic filament [37]. A disadvantage of TCMs is the strong dependence on experimental parameters, and the inherent large variability in the device properties [32]. This, and the high energy consumption led to a drop in research activities in recent years [32].

**Carbon Memory** Resistive switching phenomena were also reported in different carbon allotropes, like nanotubes, thin graphitic structures and amorphous carbon (a-C) which are included under the umbrella of carbon memory [12, 39-42]. Carbon memories based on insulating, tetrahedally bonded amorphous carbon (ta-C) have recently gained traction due to their good scalability and simple deposition techniques [43]. They are based on the reversible formation of a conductive  $sp^2$  network, in an otherwise amorphous, insulating carbon matrix [43]. The  $\pi$  bonds of the  $sp^2$  bonded carbon form a delocalised or ('conjugated') network [44]. The amorphous carbon matrix is sandwiched between two electrodes. The conjugated  $sp^2$  network forms a conductive filament within the insulating matrix, when the device is biased with a sufficiently high voltage to induce a dielectric breakdown [45]. The establishment of the conductive filament during the dielectric breakdown event switches the device into the LRS (logic '1'). The SET process leading to the formation of a conductive filament in an otherwise insulating carbon matrix was not well understood at the time when the work leading to this thesis was started. The current understanding, to which this work contributed significantly (see Sections 4.4, 4.6, 5.4 and publications [46], [47]), is that the formation of a conductive filament in a spatially confined memory cell is temperature activated and triggered by a local re-hybridisation from  $sp^3$  to  $sp^2$  carbon. The SET process is discussed in more detail in Section 2.5.1.

Reverse switching is induced by applying a short electric pulse which leads to the rupture of the conductive filament and resets the device into the HRS (logic '0') [43]. The RESET process that causes the reverse switching is less understood in comparison to the SET process. A large contributor to the difficulty in understanding the RESET process is the thermodynamical stability of the LRS. The current understanding, to which this work again contributed significantly (see Section 4.6 and publications [46], [47]), is that the rupture of the conductive filament is induced by the large temperature gradient that arises at the electrode / conductive filament interface during the RESET pulse. The RESET process is discussed in more detail in Section 2.5.2. Similar to other filamentary memories, the HRS after a RESET is typically lower than the resistance of pristine devices [45].

The device state is read out using small voltages that do not affect the state of the device [43]. Carbon memories are typically distinguished from ReRAMs due the formation of a conductive  $sp^2$  percolation path, rather than an oxygen-vacancy formation (in VCM) or metal filament (in CBRAM) [9].

#### **1.5 Comparison of Non-Volatile Memory Technologies**

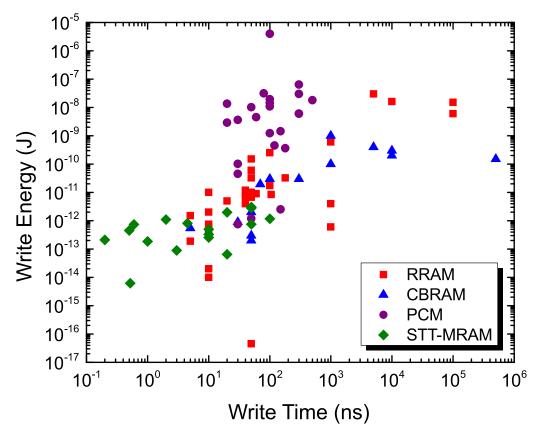

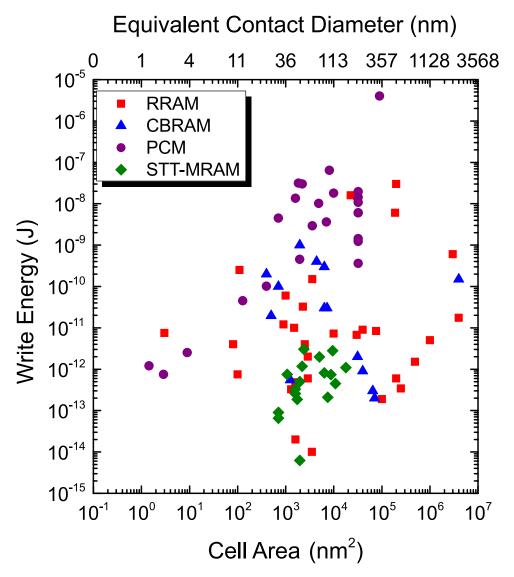

The key characteristics of the most studied data storage memory technologies were introduced in Section 1.4 and are presented with their key attributes in Table 1.2. To avoid a misleading impression about the capabilities of each storage technology, typical specifications that were available from a single device of each type (rather than for devices in large arrays) were taken. The best specifications for each attribute are provided additionally in brackets [48]. The correlation between the energy consumption during the writing process as a function of the writing time and cell area of a device, are also provided in Figure 1.3 and Figure 1.4, respectively [48]. In both figures VCM and TCM are grouped together as ReRAM, meanwhile CBRAM is shown separately (cf. [32]). **Table 1.2:** Specifications of single device performances for selected storage class memories SCMs. VCM and TCM are grouped together as ReRAM, meanwhile CBRAM is shown separately (cf. [32]); the best characteristics for each attribute are given in brackets [adapted from [48]].

|                         | PRAM                                  | STT-MRAM                          | CBRAM                           | ReRAM                 |

|-------------------------|---------------------------------------|-----------------------------------|---------------------------------|-----------------------|

| Maturity                | Prototypical                          | Prototypical                      | Emerging                        | Emerging              |

| Film                    | 10 nm <sup>(1)</sup>                  | ≈5 nm <sup>(2)</sup>              | (3)                             | <5 nm <sup>(4)</sup>  |

| Thickness               | (2 nm)                                | (≈2 nm)                           | (2 nm)                          | <3 nm <sup>(1)</sup>  |

| SET Times               | 30 ns <sup>(1)</sup>                  | 0.5 ns <sup>(2)</sup>             | 5 ns <sup>(3)</sup>             | 5 ns <sup>(4)</sup>   |

| SET TIMES               | (10 ns)                               | (0.2 ns)                          | 5 115                           | (0.3 ns)              |

| RESET Times             | 30 ns <sup>(1)</sup>                  | $0.5  \mathrm{ns}^{(2)}$          | 1 ns <sup>(3)</sup>             | 5 ns <sup>(4)</sup>   |

| RESET TIMES             | (6 ns)                                | 0.5 118                           |                                 | (0.3 ns)              |

| Retention               | 10 <sup>4</sup> s @ RT <sup>(1)</sup> | $30 [E_b/k_bT]^{(2)}$             | 10 yrs @ RT <sup>(3)</sup>      | $10 h @ 200 °C^{(4)}$ |

| Time                    | (10 yrs @ 220 °C)                     | $(120 \left[ E_b/(k_bT) \right])$ | (10 yrs @ 150 °C)               | (10 yrs @ 85 °C)      |

| Endurance               | 10 <sup>5(1)</sup>                    | (2)                               | 10 <sup>7(3)</sup>              | 10 <sup>6(4)</sup>    |

| Cycles                  | $(1.25\times 10^{12})$                | $(10^{15})$                       | 10,(0)                          | $(10^{12})$           |

| Write Energy<br>per Bit | <0.1 pJ <sup>(1)</sup>                | 6 fJ <sup>(2)</sup>               | <2 pJ <sup>(3)</sup><br>(<1 pJ) | <1 pJ <sup>(4)</sup>  |

<sup>(1)</sup> Taken from [49]

$^{(2)}$  Taken from [50]

<sup>(3)</sup> Taken from [51]

<sup>(4)</sup> Taken from [52]

**Figure 1.3:** Writing energy as function of writing time for selected storage class memories (SCMs) [taken from [53]]; VCM and TCM are grouped together as ReRAMs, meanwhile CBRAM is shown separately (cf. [32]).

**Figure 1.4:** Writing energy as function of the cell area for selected storage class memories (SCMs) [taken from [53]]; VCM and TCM are grouped together as ReRAMs, meanwhile CBRAM is shown separately (cf. [32]).

#### **1.6 Beyond von Neumann Computation**

Modern computers are based on the von Neumann architecture where logic and memory operations are physically separated [19]. Logic and arithmetic operations are performed in the CPU from where the data has to be transferred to the memory and retrieved for further computation [19]. This separation between logic and memory is currently a large performance limiting factor and known as the von Neumann bottleneck [19, 54]. To overcome this performance limitation, this separation can be abandoned to perform logic/arithmetic operations and data storage within the same physical unit using a computing-in-memory or memcomputing approach [19, 55, 56]. Concepts to address this issue include the translocation of arithmetic operations from the CPU to the SCM [19, 57]. These concepts can be realised using so-called memristive devices, where the electrical resistance of the device is related to the charge flow through the devices, examples of which are nonvolatile resistive switching memories (such as ReRAM, PRAM, CBRAM etc.) [58–61]. Arithmetic operations can be implemented using multiple pulses to change the resistance state gradually from the LRS into the HRS or vice-versa, as it was shown for phasechange memory devices [19, 57]. The excitation pulses are configured (in amplitude and duration) such that only after all pulses of the predetermined sequence have been applied does the resistance of the cell change significantly enough (either in transitioning from the HRS into the LRS, or vice-versa) to cross a pre-set resistance decision threshold. Thus, for base-n operation, a decision threshold is set between the resistance levels achieved after the input of (n-1) and n pulses. The number of pulses required to pass through the decision threshold determines the arithmetic base of the calculation. When the accumulator exceeds the decision threshold a carry forward is recorded and the device is set back to its starting state and the input pulses are continued until all the remaining input pulses have been sent [19, 62]. More details for carrying out accumulator-based arithmetic operations (addition, subtraction, multiplication, division etc.) are provided in [19, 57, 62]. In contrast to MLC data storage, where the different resistance levels have to be precisely sensed, this arithmetic approach solely requires the distinction of two resistance states that are separated by a decision level [19].

For the remainder of this thesis the focus is on amorphous carbon-based memories, which have the potential to play an important role as non-volatile SCM as well as in beyond von Neumann computation due to their simple structure, cheap manufacturing processes, good scalability, fast switching times and biocompatibility [43, 63, 64].

### 1.7 Thesis Objectives

Memory devices based on ta-C have promising properties, such as nanosecond switching times, a good scalability (possibly to the single bond level), cheap and easy manufacturing processes [43]. The key performance achievements of memory devices based on ta-C are summarised in Table 2.2. Motivated by these promising characteristics, the unipolar switching and data retention capabilities of ta-C devices were investigated in Sections 4.2 and 4.3. The effect of different pulse lengths and amplitudes on the SET process was investigated in Section 4.7 to correlate the switching times with power and energy consumption. Preliminary experiments have shown a low cycling endurance (see Section 4.4), which could be linked to the thermodynamical stability of the LRS. In Section 4.6 this was found to be exacerbated by the unipolar operation mode and the fast switching times, which give rise to large capacitive currents that manifest in large conductive filaments [43]. This led to an intensive investigation into the conditions at the dielectric breakdown event, when the switching from the HRS into the LRS occurs, see Sections 4.6, 5.1, 5.2, 5.3, 5.4. This work contributed to the current understanding of the SET process in ta-C memories, as discussed in Sections 1.4 and 2.5.1.

To address the difficulty of a low cycling endurance, memory devices based on oxygenated amorphous carbon (a- $CO_x$ ), which have shown high cycling endurance in bipolar mode due to oxygen aiding the reset process [63], were investigated in Chapter 6 with respect to data retention, switching time, multi-level storage and beyond von Neumann computation.

The motivation of this work is therefore threefold. Firstly, the switching performance of devices based on elemental amorphous carbon and oxygenated amorphous carbon were evaluated with respect to the switching time, energy consumption and temperature stability. Secondly, a computational model was developed to help shine light on the switching process, in particular on the conditions at dielectric breakdown, especially on the temperature distribution due to the Joule heating effect. Thirdly, the memristive properties of oxygenated amorphous carbon were investigated. As part of this study, a multi-level approach was realised, which allows a significant increase of the storage density. Additionally, a simple base-16 accumulator was implemented to demonstrate some of the beyond von Neumann capabilities of oxygenated amorphous carbon.

### **1.8 Thesis Outline**

**Chapter 1** The first chapter introduces the memory taxonomy and identifies the performance gap in the memory hierarchy that is located between fast, but volatile memory on one side and slow, but non-volatile memory on the other side. The working principles of current memory storage technologies are presented and compared with the most promising and emerging memory storage technologies as identified by the International Roadmap for Semiconductors (ITRS) [9]. The concept of memcomputing to perform arithmetic operations within a memristive device is briefly introduced as means to overcome the speed limitation of the von Neumann architecture.

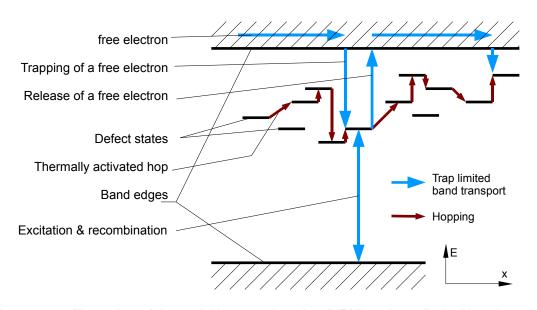

**Chapter 2** The second chapter reviews the most common deposition techniques for amorphous carbon thin films and provides a brief description of the working principle of each. The most typical spectroscopic characterisation methods are reviewed with respect to their capability to determine the  $sp^2$  and  $sp^3$  content of deposited films. A key emphasis is put on Raman spectroscopy which allows one to get insights in the local arrangement of  $sp^2$  bonded carbon, which is a key factor in determining the electric properties of amorphous carbon-based films. Further, the key concepts of electronic transport in localised states is reviewed for low electric fields, together with trap-limited band transport for high electric fields. Additionally, a literature review about the current understanding of the physical origins of the SET and RESET processes in insulating amorphous carbon is provided.

**Chapter 3** The third chapter presents the deposition methods and parameters used for the ta-C and a-CO<sub>x</sub> films and devices used in this thesis, along with the results of the material analysis of ta-C and a-CO<sub>x</sub> films. Further, the design of the ta-C and a-CO<sub>x</sub> memory devices is provided, together with descriptions of the experimental device test setups that were used to investigate the switching and retention properties of the ta-C and a-CO<sub>x</sub> memory devices, and the low temperature conduction properties of the ta-C memory devices. Additionally, the material parameters and electric pulses used within the framework of the computational modelling are provided. It is pointed out that the experimental pulses to be modelled have to be long enough to avoid a time lag between the maximum voltage achieved and onset of the dielectric breakdown. This finding aids

to the understanding of the SET process since the observed time lag suggests that the electric field alone is not sufficient to switch the device from the HRS into the LRS.

**Chapter 4** In chapter four, the switching performance, energy consumption and data retention capabilities of tetrahedral amorphous carbon based memories are investigated experimentally. The fastest switching times and lowest power consumptions achieved to date are reported.

**Chapter 5** The fifth chapter presents the results of the experimentally determined fieldand temperature dependent conductivity of pristine ta-C, which is fed into the computational modelling. The results of the simulated conductivity is then presented and compared with experimental data, which allows one to draw conclusions about the temperature distribution at the onset of dielectric breakdown. The obtained high temperatures, exceeding 1500 K, suggests that temperature activation is important to SET the device, which aids to the understanding of the SET process. The obtained insights are used in an optimisation study that aims to provide a guideline to reduce the energy consumption.

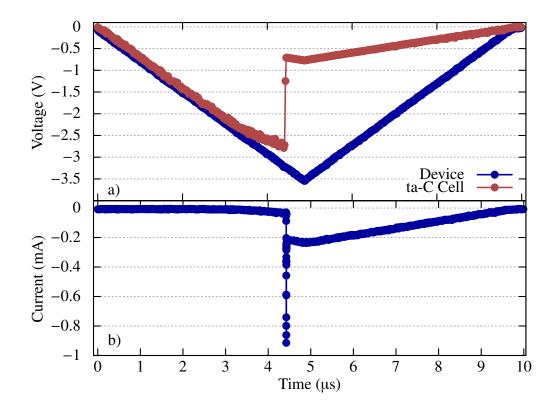

**Chapter 6** The sixth chapter present the switching performance, energy consumption and data retention capabilities of devices based on oxygenated amorphous carbon. The memristive effects are evaluated for the first time, and a 3-level  $(1^{1/2} \text{ bits})$  data storage approach is presented. Additionally, a base-16 accumulator response is successfully achieved. The chapter concludes with a thermal analysis that aims to provide insights into the temperature distribution within a filament during the reset process.

**Chapter 7** In Chapter 7, the key findings are summarised and a future outlook on research on carbon-based materials for memory applications is presented.

In terms of original contribution to knowledge, the work of this thesis achieves this via both significantly improved device performance aspects as well as contributions to the understanding of the switching mechanism in ta-C and a- $CO_x$  devices. Notable contributions include the following:

- Fastest switching in a-CO<sub>x</sub> memory devices reported to date (40 ns).

- Fastest switching in ta-C and a-CO<sub>x</sub> memory reported to date (7 ns).

- Data retention of 300 s @ 450 °C achieved in ta-C memory devices.

- Lowest writing energy per bit in a-CO<sub>x</sub> memory devices reported to date ( $\approx 2 \text{ pJ}$ ).

- First time multi-level storage achieved in a-CO<sub>x</sub> memory devices.

- First time accumulator response (base-16) realised in a-CO<sub>x</sub> memory devices to demonstrate beyond von Neumann capabilities.

- First complete computational modelling of experimentally obtained conductivity in ta-C memory devices ranging from Ohmic conduction until the onset of the dielectric breakdown.

- Realisation that large electric fields in the absence of high temperatures do not suffice to induce a dielectric breakdown in ta-C memory devices.

- Localised Joule heating is captured in the computational model by introducing a random distribution of conductive  $sp^2$  clusters in an otherwise insulating  $sp^3$ -rich matrix.

- Realisation that high temperatures exceeding 1500 K are present in ta-C memory devices at the onset of the dielectric breakdown.

• Highlighting that temperature plays an important role during the RESET process in a-CO<sub>x</sub> devices.

# **Insulating Amorphous Carbons**

# 2.1 Introduction

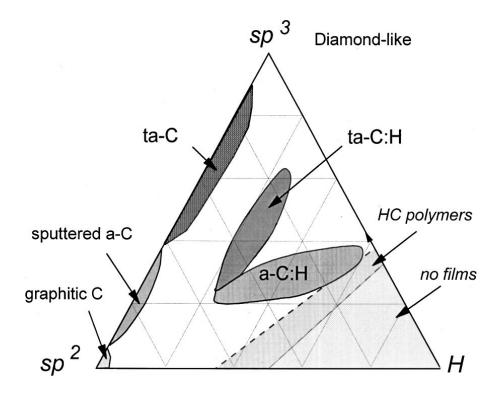

Resistive switching phenomena can be observed in various carbon allotropes, as outlined in Section 1.4. Probably the most promising allotropes with regards to ease of fabrication, scaling, fast switching speeds and the prospective application in beyond von Neumann computation, are based on amorphous carbon and amorphous carbon derivatives [63]. The different a-C derivatives such as diamond-like carbon (DLC) have a large variation in optical, electrical and mechanical properties [65]. These differences arise due to the inherent differences between graphite-like  $sp^2$  bonding and diamond-like  $sp^3$  bonding [65, 66]. The main attributes that affect the electrical properties and hence, influence the resistive switching performance in a memory device, are the  $sp^3$  content, the clustering of the  $sp^2$  phase into conjugated  $sp^2$  rings or networks, the orientation of the  $sp^2$  phase. the cross-sectional nanostructure and the content and bonding of any additional elements, such as hydrogen [67] (or oxygen [63]) [46, 65, 66]. Amorphous carbon with a significant fraction of  $sp^3$  bonds is referred to as diamond-like carbon (DLC) or tetrahedral amorphous carbon (ta-C), in the case of a very high  $sp^3$  C-C bonding content [65, 66, 68]. The relation (in terms of  $sp^3$ ,  $sp^2$  and H content) between graphitic carbon, diamond-like carbon and hydrogenated carbon is shown in the ternary phase-diagram in Figure 2.1.

**Figure 2.1:** Ternary phase diagram of amorphous carbon and amorphous carbon-based alloys (*here* a-C:H) [taken from [69]].

For the use of amorphous carbon as an active material in memory devices, it is necessary to disrupt any existing conjugated (delocalised)  $\pi$  networks (see Section 1.4) to achieve reversible switching from the LRS into the HRS [43]. The current densities that are required for this RESET process were reported to be  $\approx 350 \text{ MA cm}^{-2}$  [43]. In amorphous carbon containing a high  $sp^2$  content, these current densities translate into large currents that are required to disrupt the large extended conjugated  $sp^2$  networks connecting the electrodes. This is power and energy inefficient, and in the case of conductive carbon only feasible for areal cross-sections with diameters below 10 nm [43, 45]. The reason for this is that practically the entire volume has to be amorphised. Thus, a more viable route is the use of ta-C or a-C-based alloys that reduce C=C  $sp^2$  bonding, (such as hydrogenated amorphous carbon (a-C:H) or oxygenated amorphous carbon (a-CO<sub>x</sub>)).

### 2.2 Deposition Methods

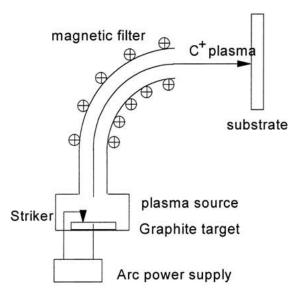

**Filtered Cathodic Vacuum Arc (FCVA)** The filtered cathodic vacuum arc (FCVA) method is based on the creation of a plasma, which in the case of a graphite target, contains a high ion density of *C*<sup>+</sup> species [65]. The plasma is created through an electric arc discharge between a graphite target and a small striker anode in a high vacuum environment [65, 70]. To remove large ion clusters, the plasma is guided through a curved magnetic filter before hitting the substrate [70]. To control the energy range of the impinging ions, a DC or RF bias can be applied to the substrate [65, 70]. The plasma net charge is neutral which allows the deposition of ta-C films on insulating substrates [65]. A schematic of a single bend FCVA apparatus is shown in Figure 2.2. The FCVA is the most commonly used method for producing high-quality ta-C films, and as such is used widely for e.g. ta-C coatings of magnetic hard disks [70–72]. The FCVA method was also used to prepare the ta-C films for the resistive switching investigations that are presented in this thesis.

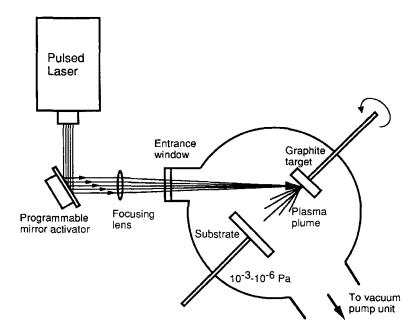

**Pulsed Laser Deposition (PLD)** The pulsed laser deposition (PLD) method uses short, high energetic laser pulses which create a plasma by vaporising carbon particles from a graphite target. [65]. The plasma consists of ionised and neutral carbon species that condense on the substrate as a consequence of the plasma expansion [73]. For industrial application, the high initial costs and the requirement for homogeneous depositions on the wafer-scale, are the biggest obstacle to the widespread adaption of PLD for a-C deposition [73]. A schematic of a PLD system is shown in Figure 2.3.

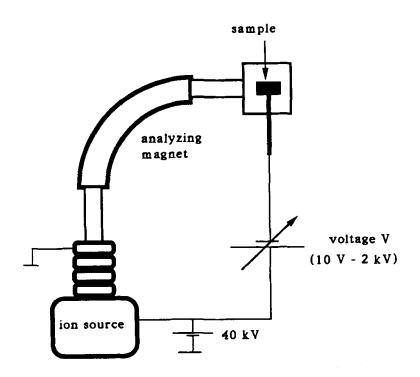

**Mass Selected Ion Beam (MSIB)** The mass selected ion beam method (MSIB) is based on the extraction of  $C^+$  ions from a graphite target or a carbon containing gas [74]. To select only  $C^+$  species, the ion beam is accelerated to around 40 keV and guided through a 90° bent magnet for mass selection [75]. The ion beam is decelerated before reaching the substrate [75]. Although ta-C films produced with the MSIB method are of high quality, the deposition rate is too low (0.001 Å/s) for industrial applications [65, 70, 74]. A schematic of an MSIB system is shown in Figure 2.4.

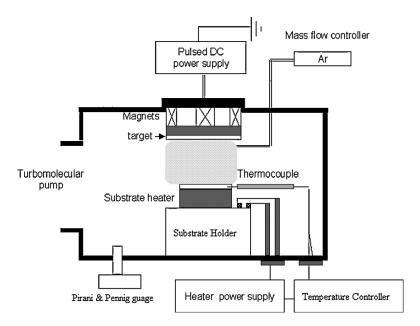

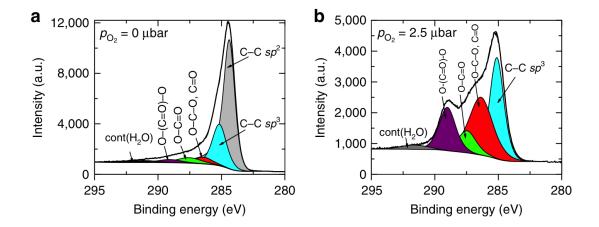

**DC Magnetron Sputtering** The sputtering method is widely used in industry due to its capability to deposit electrically conductive as well insulating materials on a large scale [65]. Conductive materials are deposited using direct current (DC) sputtering, whereas insulating materials have to be deposited using radio frequency (RF) sputtering to avoid charge build-up [70]. Amorphous carbon thin films are usually deposited from a graphite target using the DC magnetron sputtering technique. The DC magnetron sputtering technique is based on the creation of a plasma in a noble-gas, typically argon, atmosphere [70]. The  $Ar^+$  ions are accelerated towards a conductive target, where typically lumps of particles are released as consequence of the  $Ar^+$  ions' impact on the target [70]. The particles are then deposited on the substrate. To increase the yield, magnets are placed behind the target [65]. The magnetic field increases the ion path, which leads to a higher ion density, and ultimately to a higher yield [65]. A schematic of a magnetron sputtering system is shown in Figure 2.5. Although a-C films of high quality can be produced using this method, the deposited carbonaceous species are of low energy (several eV) and consequently, the resulting film has a low  $sp^3$  content [65, 70]. The high  $sp^2$  content (>80%) inhibits their use in resistive switching applications (see Section 1.4) [76]. The  $sp^3$  content can be increased by adding a reactive gas like oxygen during the deposition process which produces a-CO<sub>x</sub> films, whereby the ratio of  $sp^3$  and  $sp^2$  bonded carbon varies as function of the oxygen partial pressure [63, 65, 70]. The deposition of carbon from a graphite target in an  $O_2$  atmosphere was used in the work of this thesis to produce a-CO<sub>x</sub> films for resistive switching studies.

**Figure 2.2:** The FCVA method: Single bend filtered cathodic vacuum arc deposition technique; the plasma arc is ignited by touching the cathode (graphite target) with a striker. The high energy plasma is then filtered for neutral species using a magnetic filter, before impinging on the substrate. The net-charge is neutral which allows the deposition on insulating substrates [modified from [65].

**Figure 2.3:** The PLD method: A laser beam is focused on a graphite target inside the vacuum deposition, which leads to the evaporation and condensation of carbonaceous species on a substrate. The energy density of the laser beam is directly correlated to the kinetic energy of carbon ions, which in turn affects the  $sp^3$  content of the resulting carbon film [65, 73] [taken from [73]].

**Figure 2.4:** The MSIB method: The  $C^+$  ions extracted from an ion source are accelerated up to 40 keV and guided through a  $90^\circ$  bend magnet for mass selection [75]. The ion energy is decreased prior to the deposition on the substrate [taken from [75].

**Figure 2.5:** The magnetron sputtering method: Noble-gas ions (typically  $Ar^+$ ) are accelerated towards a cathodic graphite target, which leads to the release of lumps of carbonaceous species from the target and deposition on a substrate [70]. Some neutralised noble-gas ions are incorporated into the deposited film [70] [modified from [77].

## 2.3 Spectroscopic Characterisation

It is important to characterise the structural and chemical composition of the deposited carbon-based films with respect to their use in resistive switching applications. An overview of the typical characterisation methods and their key characteristics is presented in Table 2.1. The state-of-the art methods are explained in more detailed in the following.

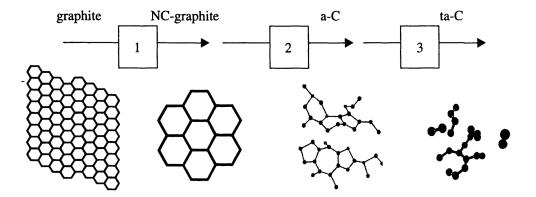

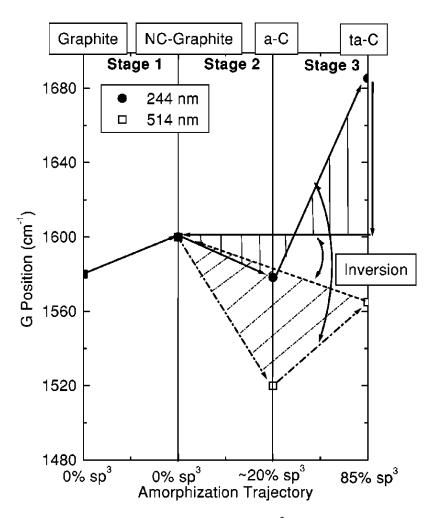

**Raman Spectroscopy** Raman spectroscopy is based on the inelastic scattering of photons in matter [78]. Raman spectroscopy is a non-destructive method to characterise the chemical and structural properties that influence the switching performance of carbonbased memories [65, 66]. The amorphisation of carbon from a crystalline graphitic form to tetrahedral amorphous carbon can be described in Raman spectroscopy by a three-stage model as originally introduced by Ferrari et al. [69]. The first stage involves the transition from graphite to nano crystalline graphite, the second from nano crystalline graphite to a-C and the last stage describes the transition from a-C to ta-C and the inherent increase of the  $sp^3$  content [69]. The three-stage model is visualised in Figure 2.6.

The Raman spectra of amorphous carbons are dominated by  $sp^2$  bonded carbon atoms due to the larger scattering cross-section in comparison to  $sp^3$  bonded carbon atoms [65]. The difference of the cross-section is related to the larger polarisability of  $\pi$  bonds, and

| Method     | Remarks                                  |

|------------|------------------------------------------|

| ESCA (XPS) | Small shifts for homopolar bonding       |

| Raman      | Multi-wavelength (including uv) analysis |

| EELS       | Time-consuming, destructive              |

Table 2.1: Characterisation methods for amorphous carbon-based films [adapted from [65]].

**Figure 2.6:** Variation of the  $sp^2$  configuration as function of the amorphisation trajectory according to the 3-stage amorphisation model [66] [taken from [66]].

the lower energetic position of  $\pi$  states [65, 69]. To characterise the structural properties the intensity and position of the Raman *G* and *D* peaks are relevant for all three-stages in the transition from graphite to ta-C [69]. The *G* peak originates from bond stretching of  $sp^2$  coordinated pairs [69]. The *D* peak is a breathing mode for benzene rings ( $sp^2$ bonded carbon) and is only active within defective 6-fold rings [69].

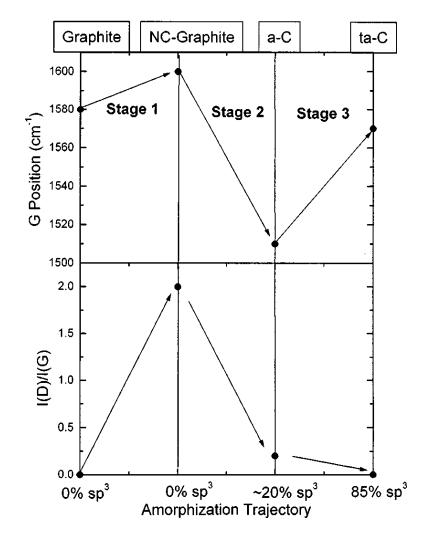

The transition from graphite to nano crystalline graphite in stage one leads to a shift in the G peak position from 1581 cm<sup>-1</sup> to 1600 cm<sup>-1</sup> due to phonon confinement [65, 69]. The D peak also appears and consequently, the ratio of the intensities of the D and G peaks (I(D)/I(G)) increases [65, 69]. Stage two involves a weakening of the  $sp^2-sp^2$  bonds due to the rearrangement of  $sp^2$  bonded atoms from sixfold rings into odd membered rings, which leads to a decrease in the G peak position from 1600 cm<sup>-1</sup> to 1510 cm<sup>-1</sup> and at the same time the I(D)/I(G) ratio approaches zero [69]. Stage three involves the transition from  $sp^2$ -rich a-C to  $sp^3$ -rich ta-C [69]. This transition causes an upward shift in the G peak position from 1510 cm<sup>-1</sup> to 1570 cm<sup>-1</sup> [69]. The origin of this G peak position shift is caused by two counteracting effects, namely the rearrangement of the  $sp^2$  bonded atoms into olefinic chains leads to shorter bonds and thus higher vibrational frequencies, and the mixing of  $sp^2$  vibrational modes with  $sp^3$  vibrational modes, which are at lower frequency

[65, 69]. A Raman spectrum of the amorphisation trajectory is shown in Figure 2.7 for a 514 nm illumination wavelength [69]. Thus, the combined study of the *G* peak position shift and the change of the I(D)/I(G) ratio can be used to determine the  $sp^3$  content, in the absence of thermal annealing effects [69].

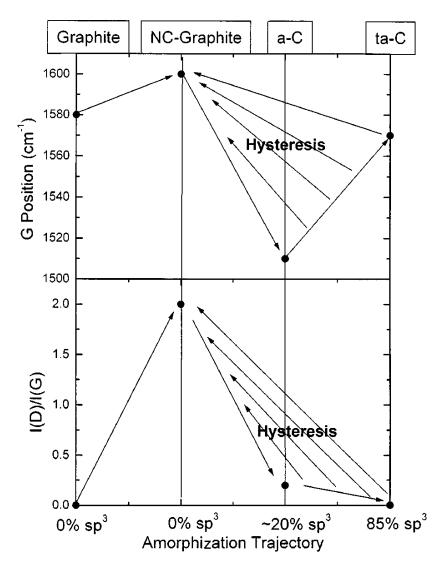

Upon annealing or deposition at elevated temperatures, a clustering process sets in which causes the  $sp^2$  sites to form aromatic, sixfold rings [69]. The clustering process causes the appearance of the D peak and leads to a shift in the G position, when using a laser with a wavelength in the visible range [69]. This upward shift in the G position is a direct consequence of the larger cross-section of aromatic rings in comparison to chains [79]. The second effect of annealing is the conversion from  $sp^3$  bonded carbon to  $sp^2$ bonded carbon. The larger cross-section of clusters outweighs the influence of the conversion on the shift in the G peak position [69]. As a consequence, there is no unique relationship anymore between G peak position, I(D)/I(G) peak ratio and the  $sp^3$  content for visible wavelength Raman spectra [69]. This leads to a hysteresis between the G peak position and the I(D)/I(G) peak ratio as a function of the  $sp^3$  content, which prevents an accurate and unambiguous determination of the  $sp^3$  content using solely visible Raman spectroscopy [69]. It has to be noted that while the variation of the G peak full width half maximum shows a unique relation with the  $sp^3$  content even for one (visible) wavelength, it is advisable to perform further measurements in order to minimise experimental uncertainties [66]. The hysteresis is schematically shown in Figure 2.8.

However, to determine the  $sp^3$  content it possible to use the fact that the *G* peak position is dispersive, i.e. wavelength dependent, in amorphous carbon [69, 80]. The an upward shift in the *G* position with increasing wavelength is caused by the stronger weighting of olefinic bonded  $sp^2$  groups, which have a higher vibrational frequency [65, 69]. This causes the *G* peak position to be shifted to higher wavenumbers than the *G* peak position

**Figure 2.7:** Raman spectrum of the *G* peak position and the I(D)/I(G) peak ratio as a function of the amorphisation trajectory for a 514 nm laser wavelength [69] [adapted from [69]].

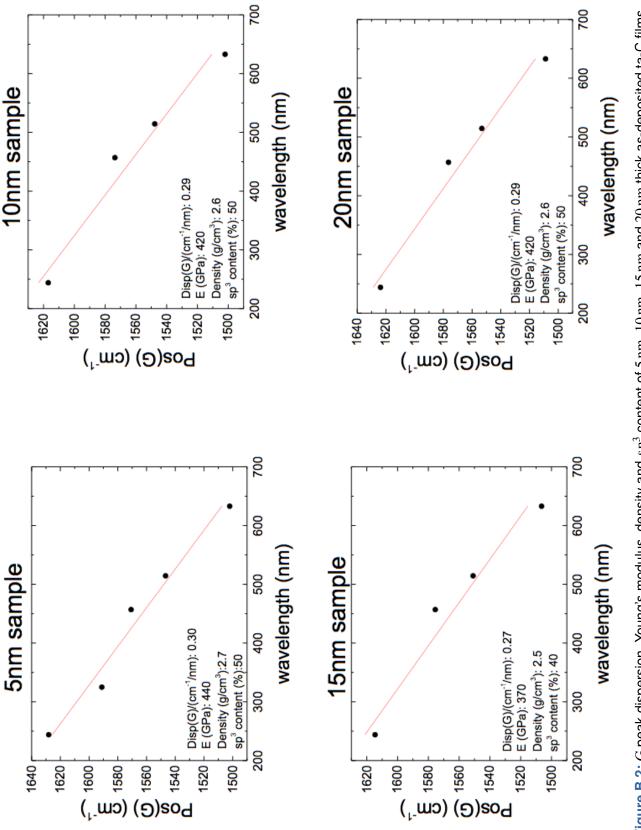

of graphite and leads to an inversion in the *G* peak position between ultra-violet (UV) Raman spectra and visible Raman spectra [79]. Upon annealing, the *G* position (under UV illumination) is shifted downwards to the *G* peak position of graphite due to clustering of the  $sp^2$  bonded carbons, which is in contrast to the upwards peak shift in visible Raman [79]. It is this inversion that allows the determination of the  $sp^3$  content unambiguously, as shown in Figure 2.9. Hence, the G peak dispersion, i.e. the rate of change of the G peak position as function of the illumination wavelength, allows the evaluation of important structural parameters such as the  $sp^3$  content [66]. Multi-wavelength Raman spectroscopy

**Figure 2.8:** Hysteresis of the *G* peak position and the I(D)/I(G) peak ratio due to cluster formation of  $sp^2$  bonded carbon [69] [taken from [69]].

(UV and visible) was used extensively to characterise ta-C films used in the work of this thesis.

**Figure 2.9:** The stronger weighting of olefinic bonded  $sp^2$  groups in UV-Raman spectroscopy leads to an inversion in the *G* peak position and I(D)/I(G) peak ratio in comparison to visible Raman spectroscopy [79] [taken from [79]].

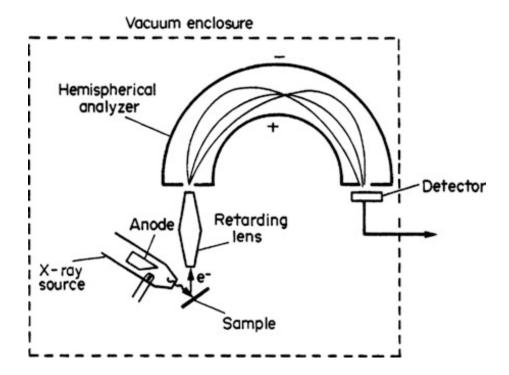

**X-ray Photoelectron Spectroscopy (XPS)** Another popular method to determine the  $sp^3$  content is X-ray photoelectron spectroscopy (XPS), also known as electron spectroscopy for chemical analysis (ESCA) [65]. X-ray photoelectron spectroscopy is based on the interaction between X-rays and the core electrons of the material under study and is typically performed in ultra-high vacuum (UHV) [81]. The material is irradiated with X-rays of a well defined energy hv that is above the ionisation threshold of the material [82]. The energy of the X-ray photon is completely transferred to a core electron, whereby the specific binding energy  $E_b$  of the electron is significantly lower than hv, which causes the electron (photoelectron) to overcome the work function and to potentially leave the surface of the solid [81]. The binding energy is not only element specific, but also depends on the chemical environment [81, 82]. The emitted photoelectron is then detected, and its kinetic energy  $E_k$  analysed by a spectrometer, which allows the obtaining of information about  $E_b$  and hence, about the chemical environment [81]. The relation between  $E_b$  and  $E_k$  is given in equation 2.1, where  $\phi_a$  is the work function of the material [81]. A conventional XPS set-up is schematically shown in Figure 2.10.

$$E_b = h\nu - E_k - \phi_a \tag{2.1}$$

The analysis of the binding energy of the 1*s* core electron of carbon allows the determination of the bonding type, and hence, the  $sp^3/sp^2$  ratio [82, 83]. The binding energy of the 1*s* core electron depends on the hybridisation of the *C* atoms, whereby the binding energy for  $sp^3$  hybridised carbon is  $\approx 0.9 \text{ eV}$  higher than the binding energy of  $sp^2$  hybridised carbon [82].

The advantage of XPS in comparison to visible Raman spectroscopy is that the ionisation cross-sections are independent of the chemical state (bonding) and therefore, the  $sp^2/sp^3$

**Figure 2.10:** XPS set-up: The energy of X-ray photons to core electrons leads to the emission of the latter. The core electrons are then energetically filtered through the hemispherical analyser prior to arriving at the detector. The kinetic energy of the arriving photo electron allows to draw conclusions about the hybridisation specific binding energy of the photo electron [taken from [81]].

ratio can be determined by comparing their relative peak intensities [82]. The performance of single elemental amorphous carbon in resistive switching memories, however, is largely dependent on the organisation of  $sp^2$  bonded carbon into clusters of sixfold rings. This favours multi-wavelength Raman spectroscopy over XPS as a tool to characterise ta-C thin films. However, XPS can be successfully employed to characterise amorphous carbon alloys like a-C:H and a-CO<sub>x</sub> for resistive switching purposes, where — depending on the composition — no or little *C-C*  $sp^2$  bonds are present [63, 69]. XPS spectroscopy was used to determine the composition and the  $sp^3$  content of the a-CO<sub>x</sub> films used in the work of this thesis (see [63]). Exemplar XPS results are given in Figure B.3 of Appendix B.4 and were obtained by collaborators at IBM Research Zurich. For further details regarding the XPS analysis of the a-CO<sub>x</sub> thin films see [63].

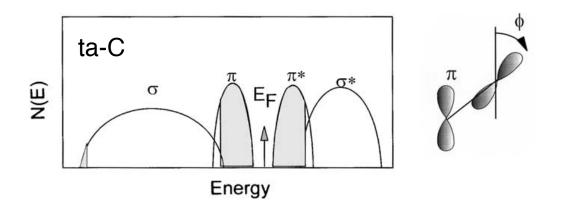

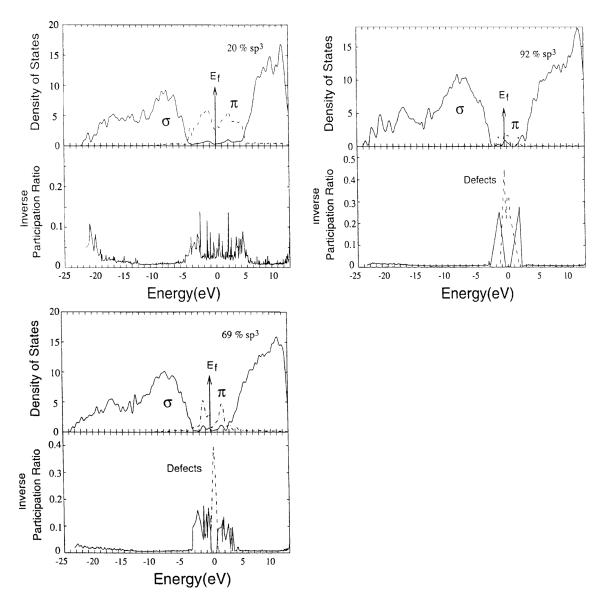

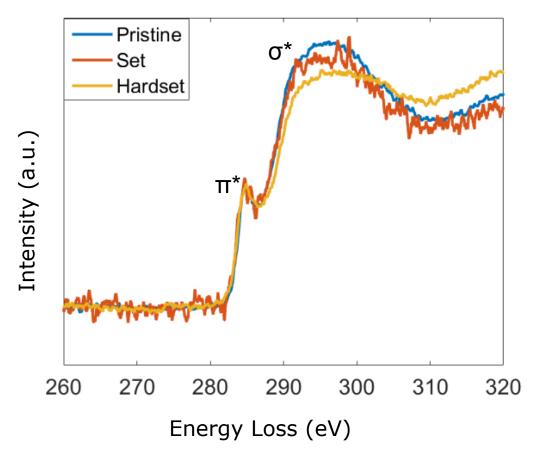

Electron Energy Loss Spectroscopy (EELS) Electron energy loss spectroscopy (EELS) allows the reliable determination of the  $sp^2/sp^3$  ratio by evaluating the energy loss of electrons that undergo inelastic scattering when transmitted through a thin film of the order of 10 nm to 20 nm (to avoid multiple scattering) [65, 70, 84]. The 2p orbitals in ta-C are degenerated into delocalised and localised bonding bands ( $\pi$  and  $\sigma$ ), and into anti-bonding bands ( $\pi^*$  and  $\sigma^*$ ) [70]. The Fermi level ( $E_f$ ) in ta-C is pinned between the filled  $\pi$  and the empty  $\pi^*$  states [70]. The  $\pi$  and  $\pi^*$  bands are absent in purely  $sp^3$  bonded carbon [70]. The  $sp^2/sp^3$  ratio can then be determined by evaluating the energy loss of electrons that excite 1s core electrons in the ta-C film into either the  $\pi^*$  or  $\sigma^*$  band [70]. The  $\pi$  and  $\pi^*$  excitation is around 5 eV lower than the 1s to  $\sigma^*$  excitation [70]. Assuming sp bonding is negligible, the  $sp^2$  content is then evaluated by comparing the ratio of the peak area  $A_{\pi^*}$  corresponding to the 1s to  $\pi^*$  excitations divided by the total excitation peak area  $A_{\pi^*} + A_{\sigma^*}$ , with the peak area ratio of 100 %  $sp^2$  bonded carbon (like graphite) [70]. This relation is given by equation 2.2, where  $G_{\pi^*}$  and  $G_{\sigma^*}$  are the peak areas for the 1s to  $\pi^*$  excitation and the 1s to  $\sigma^*$  excitation in graphite [70]. An indirect estimate of the  $sp^3$  content can be obtained by evaluating the position of the plasmon energy peak at the low-energy end of an EELS spectrum [85]. The EELS analysis was used to characterise the  $sp^2/sp^3$  ratio in ta-C films used in the work of this thesis. The results of the EELS characterisation are presented in Sections 3.1.2 and 4.6.

$$sp^{2}[\%] = \frac{A_{\pi^{*}}}{A_{\pi^{*}} + A_{\sigma^{*}}} \cdot \frac{G_{\pi^{*}} + G_{\sigma^{*}}}{G_{\pi^{*}}} \cdot 100\%$$

(2.2)

### 2.4 Electronic Transport

The difference in conductivity between the HRS and LRS in amorphous carbon arises due to changes in the density of states (DOS). The main difference in conductivity arises from

the transition from localised  $\pi$  states in the vicinity of  $E_f$  in ta-C, into ordered clusters [68].

#### 2.4.1 Density of States

A feature of the DOS in disordered materials is the presence of defect states within the band gap, which separates the valence band and the conduction band [65]. The defect states closer to the band edges originate from distortions in bond lengths and angles [65]. Deep defects originating from a different bonding configuration are typically located in the middle of the band gap [65, 86].

The extended, i.e. delocalised, states (valence and conduction band) in ta-C are comprised by  $\sigma$  and  $\sigma^*$  states, whereas the deep defects arise from  $\pi$  and  $\pi^*$  states of  $sp^2$  bonded carbon within the  $sp^3$ -rich matrix [65]. The Fermi level in ta-C is pinned between the  $\pi$  and  $\pi^*$  states and the low conductivity of as-deposited ta-C originates<sup>5</sup> from the localisation of the charge carriers in the  $\pi$  and  $\pi^*$  states as schematically shown in Figure 2.11 [65].

The change from localised to delocalised (extended) states occurs at the mobility edge  $(E_m)$  [86]. In the case of isotropic orbital interactions (*s* and  $\sigma$  states),  $E_m$  can be related to the DOS via the insulator-metal transition as first described by Mott [86, 87].

The insulator-metal transition describes the transition of an electrically insulating material to an electrically conducting material once the DOS is high enough [86, 87]. The insulator-metal transition can be described by equation 2.3. This equation is an approximation which states that once the DOS at the mobility edge ( $N(E_m)$ ) is high enough

<sup>&</sup>lt;sup>5</sup>ta-C has to be deposited at temperatures low enough to avoid cluster formation [69].

(the cubic root of the DOS equals a constant *c* divided by the Bohr radius  $(a_0)$ ), then the material becomes conductive (i.e. insulator-metal transition) [86, 88, 89].

$$\sqrt[3]{N(E_m)} = \frac{c}{a_0} \tag{2.3}$$

However, it is important to note that this approximation of metal-insulator transition does not apply for ta-C, where the interaction of  $\pi$ - $\pi$  states depends on their projected dihedral angle  $\phi$  [65]. This leads to the strong localisation of  $\pi$  states that is observed in ta-C [65]. The DOS for ta-C is schematically shown in Figure 2.11 together with the dihedral angle  $\phi$ . This is important as it explains why as-deposited a-C is insulating even at high  $sp^2$ contents [90]. A measure for the  $\pi$  states localisation is the inverse participation ratio Pwhich describes the localisation of a state and varies between 1 for strong localisation and 1/N for delocalisation over N sites [65, 90]. The DOS and the inverse participation ratio are shown in Figure 2.12 for  $sp^3$  concentration of 20 %, 80 % and 92 % [90]. The calculations were performed using atomistic modelling [90].

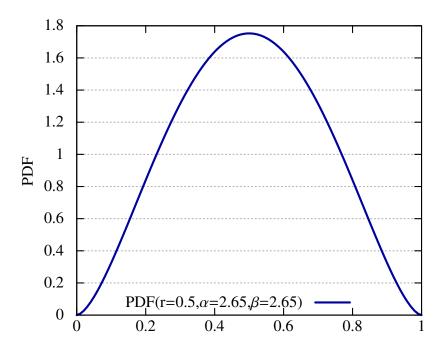

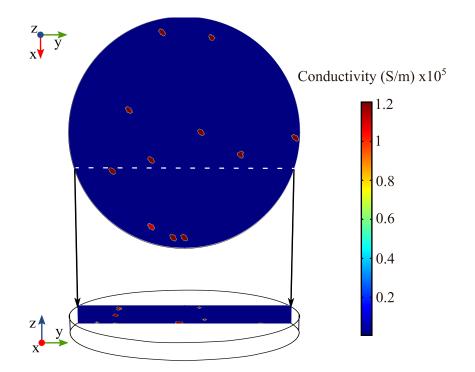

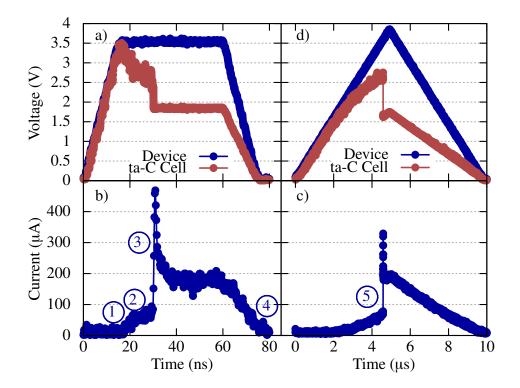

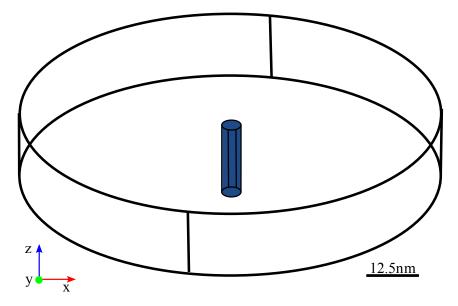

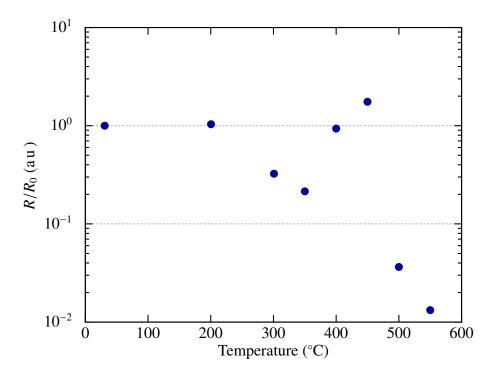

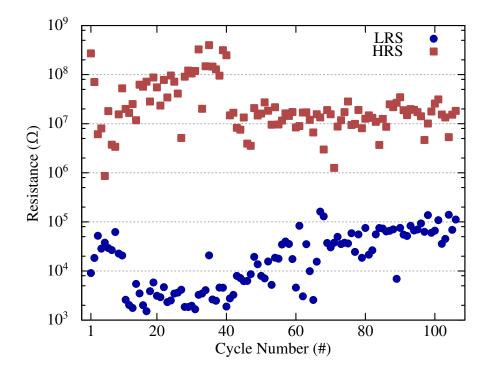

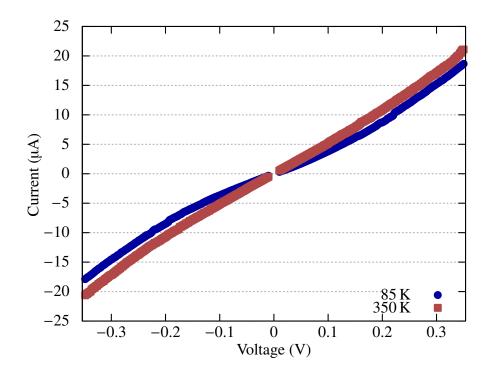

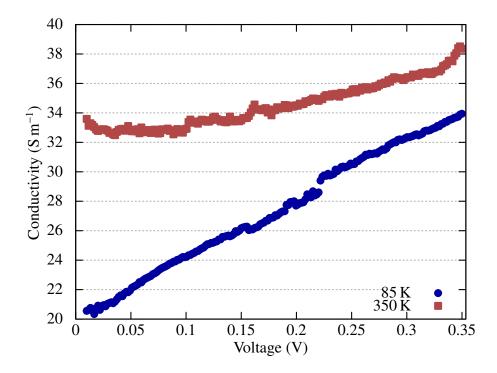

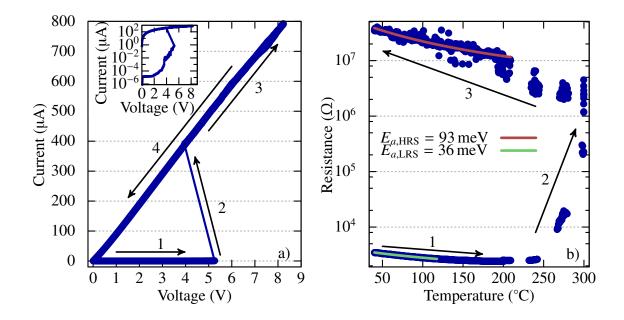

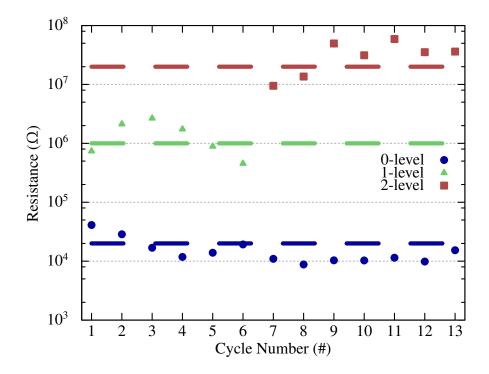

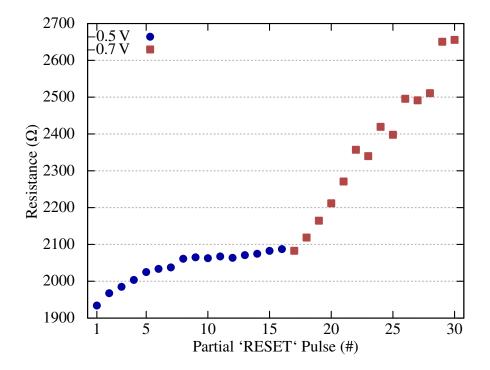

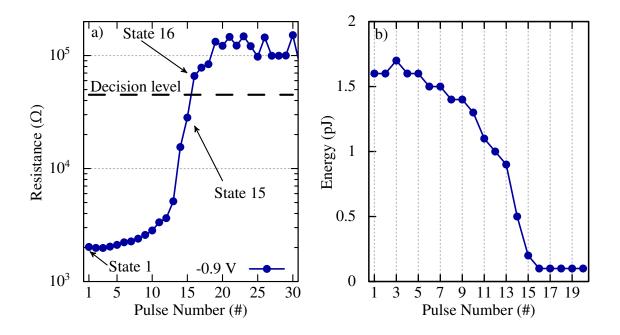

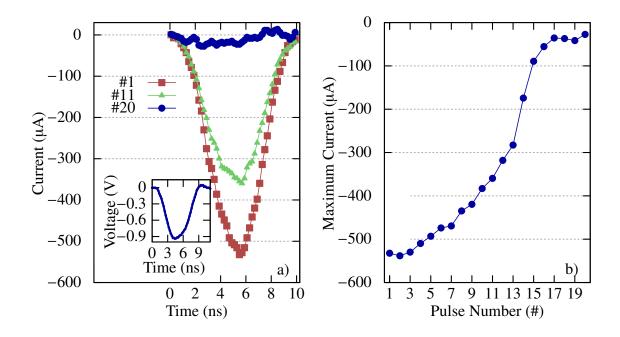

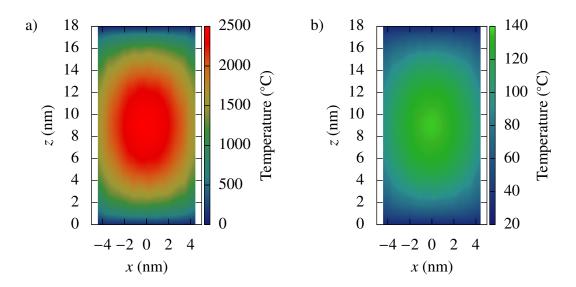

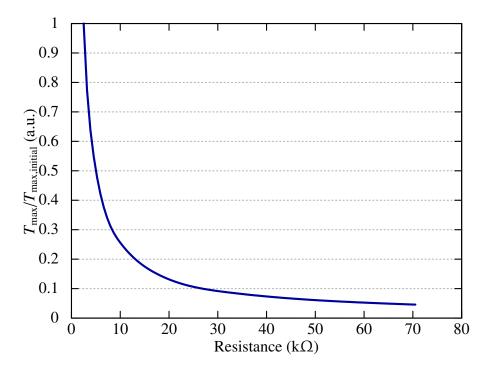

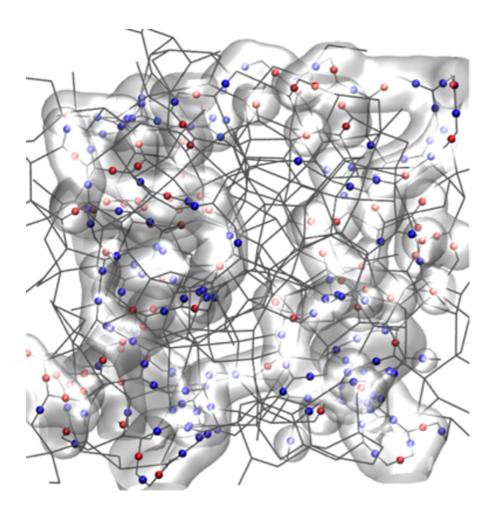

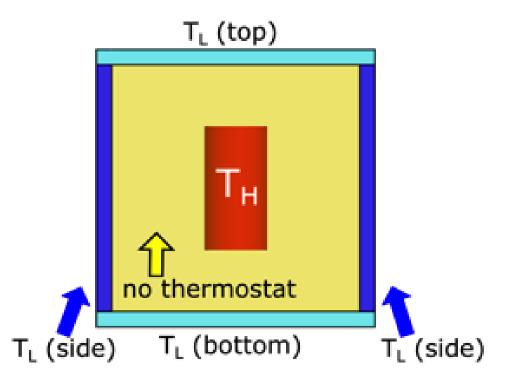

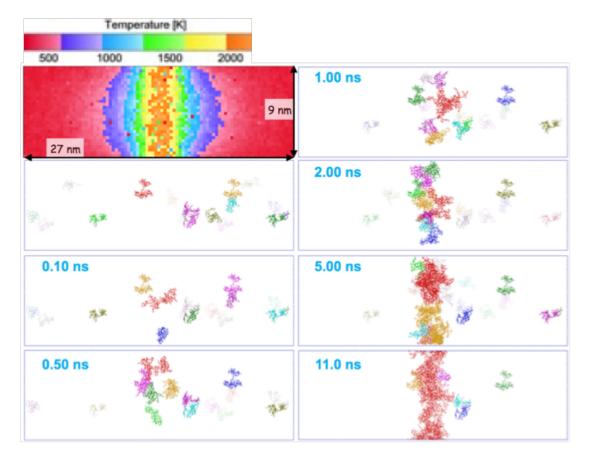

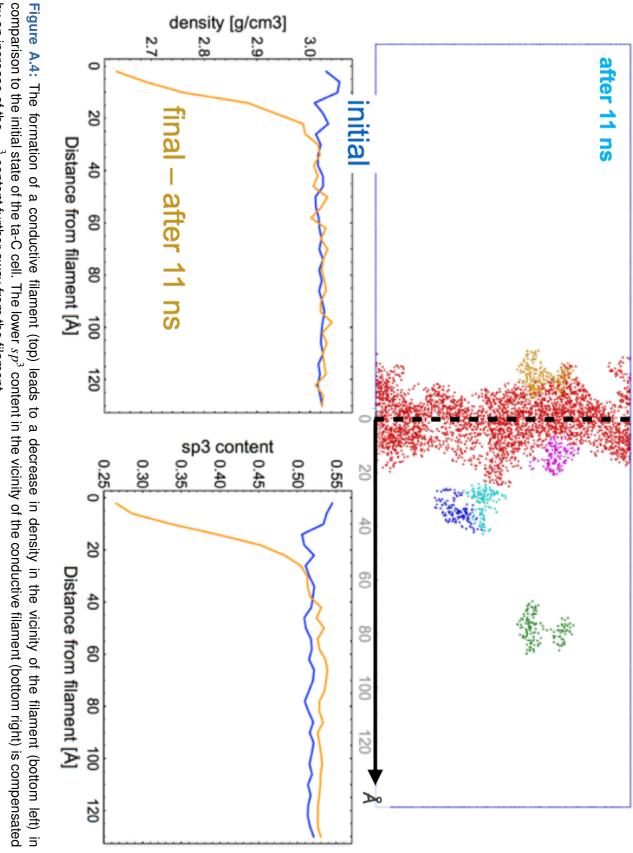

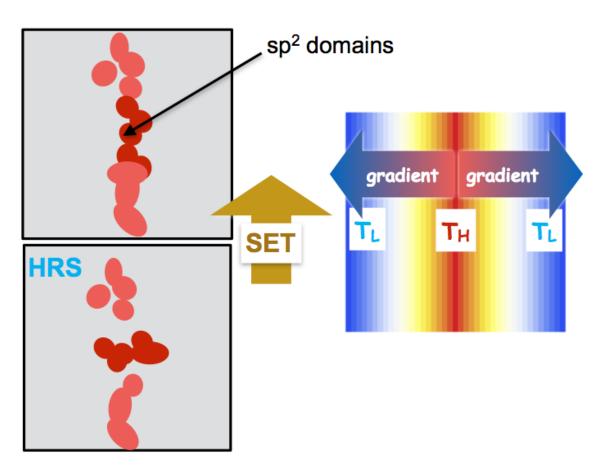

**Figure 2.11:** The dependence of the delocalisation of  $\pi$  states on the dihedral angle  $\phi$  leads to a strong localisation of  $\pi$  states within the band gap [65] [modified from [65]].