UNIVERSITAT POLITÈCNICA DE CATALUNYA BARCELONATECH

Escola Tècnica Superior d'Enginyeria de Telecomunicació de Barcelona

# ANALYSIS OF CLOCK TREE IMPLEMENTATION ON ASIC BLOCK QOR

A Master's Thesis Submitted to the Faculty of the Escola Tècnica d'Enginyeria de Telecomunicació de Barcelona Universitat Politècnica de Catalunya

by

Javier Antúnez Sánchez

In partial fulfilment of the requirements for the degree of MASTER IN ELECTRONIC ENGINEERING

**Advisor: Francesc Moll Echeto**

**Barcelona, October 2017**

# Title of the thesis: Analysis of clock tree implementation on ASIC block QoR

Author: Javier Antúnez Sánchez

Advisor: Francesc Moll Echeto

# Abstract

The scope of this project is to develop a base methodology for clock tree synthesis that can improve the base results regarding the clock structure. The analysis of results will be done with a *Quality of Results* sets of metrics and by analysing the physical structure of the clock.

The analysis has been performed on three blocks with different physical characteristics to achieve a transversal solution. The initial tests performed have been focused on configuration options of the EDA tool used but were disregarded. The main tests upon this thesis is based are referred to the clock physical structure such as *fanout* constraints, *slew* constraints and clock cell selection.

One of the main results obtained is the importance of the layout of the block to set up the optimal constraints, limiting the transversal solution approach. It is as well an important point considering the internal algorithms followed by the tool.

# **Acknowledgements**

I would like to acknowledge the help and knowledge provided by Ferran Martorell Cid and all the ASIC and Layout Design engineers at Esilicon for all the help granted for the development of this project, both in the project orientation as for help learning the methodology to be followed.

I would like to thank Esilicon for the chance of doing my master thesis project as it has been a great experience to go through.

I want to acknowledge too the help provided by Francesc Moll, to set up this project and by helping me whenever is necessary and helping me polish the project as well as structuring and giving format to this document.

# **Revision history and approval record**

| Revision | Date       | Purpose                                    |  |

|----------|------------|--------------------------------------------|--|

| 0        | 13/10/2017 | Document creation                          |  |

| 1        | 15/10/2017 | Document revision - Draft 1                |  |

| 2        | 15/10/2017 | Document expansion - Draft 2               |  |

| 3        | 16/10/2017 | Document expansion - Draft 3               |  |

| 4        | 17/10/2017 | Document revision and correction - Draft 4 |  |

| 5        | 19/10/2017 | Final Version                              |  |

| Written by: |                        | Reviewed and approved by: |                    |  |

|-------------|------------------------|---------------------------|--------------------|--|

| Date        | 12/10/2017             | Date                      | 19/10/2017         |  |

| Name        | Javier Antúnez Sánchez | Name                      | Francesc Moll      |  |

| Position    | Project Author         | Position                  | Project Supervisor |  |

# Table of contents

| Abstract   | t                                                              | 1  |

|------------|----------------------------------------------------------------|----|

| Acknowl    | ledgements                                                     | 2  |

| Revisior   | history and approval record                                    | 3  |

| Table of   | contents                                                       | 4  |

| List of F  | igures                                                         | 7  |

| List of Ta | ables                                                          | 8  |

| 1. Intro   | oduction                                                       | 11 |

| 1.1.       | Requirements and Specifications                                | 11 |

| 1.2.       | Statement of purpose                                           | 12 |

| 1.3.       | Methods and procedures                                         | 12 |

| 1.4.       | Work plan                                                      | 12 |

| 1.5.       | Gantt diagram                                                  | 15 |

| 2. Stat    | te of the art of the technology used or applied in this thesis | 17 |

| 2.1.       | Planar CMOS to FinFET                                          | 17 |

| 2.1.       | 1. Planar CMOS technology and its limitations                  | 17 |

| 2.1.       | 2. FinFET technology and its advantages                        | 19 |

| 2.2.       | Terminology and Concepts                                       | 21 |

| 2.3.       | Adjustable Delay Buffers                                       | 22 |

| 2.4.       | Reconfigurable Clock Trees for Multi-Corner Multi-Mode designs | 23 |

| 3. Met     | hodology and Project Development                               | 25 |

| 3.1.       | Block Definition and Characteristics                           | 25 |

| 3.1.       | 1. Block 1                                                     | 26 |

| 3.1.       | 2. Block 2                                                     | 28 |

| 3.1.       | .3. Block 3                                                    | 30 |

| 3.1.       | .4. Block 4                                                    | 32 |

| 3.2.       | Metrics Definition                                             | 34 |

| 3.2.       | 1. Power Performance Analysis metrics                          | 34 |

| 3.2.       | .2. Support metrics                                            | 34 |

| 3.3.       | Scripts and Automatic Block Generation                         | 35 |

| 3.3.       | 1. Automatic Block generation                                  | 35 |

| 3.3.       | .2. Reference shell blocks                                     | 36 |

| 3.3.   | 3. Configuration sets directory                                | 36 |

|--------|----------------------------------------------------------------|----|

| 3.3.   | 4. Auxiliary scripts directory                                 | 37 |

| 3.3.   | 5. General block directory:                                    | 37 |

| 3.3.   | 6. Block generation script                                     | 37 |

| 3.4.   | Script Analysis and Explanation                                | 38 |

| 3.4.   | 1. Block Generation Script: <i>run_gen.tcl</i>                 |    |

| 3.4.   | 2. Reporter and parser: report_parser.tcl                      |    |

| 3.4.   | 3. Clock Structure Analyser: clock_structure_analyser.tcl      | 40 |

| 3.4.   | 4. Clock pin modification script: replace_clockpin.tcl         | 41 |

| 3.4.   | 5. Report combiner: <i>block_combiner.tcl</i>                  | 41 |

| 3.5.   | Methodology and Experiment Sets                                | 42 |

| 3.5.   | 1. Reference block parameters                                  | 42 |

| 3.5.   | 2. Initial Experiment Sets                                     | 42 |

| 3.     | 5.2.1. Configuration options explanations and expected results | 43 |

| 3.5.   | 3. Slew Analysis                                               | 45 |

| 3.     | 5.3.1. Experiment Set Definition                               | 46 |

| 3.5.   | 4. Fanout Analysis                                             | 47 |

| 3.     | 5.4.1. Experiment Set Definition                               | 47 |

| 3.5.   | 5. Clock Cell Analysis                                         | 48 |

| 3.     | .5.5.1. Experiment Set Definition                              | 50 |

| 3.5.   | 6. Concurrent Clock and Data Optimization analysis             | 51 |

| 3.     | 5.6.1. Experiment Set definition                               | 52 |

| 3.5.   | 7. Clock Placement Analysis                                    | 52 |

| 3.     | .5.7.1. Experiment Set Definition                              | 53 |

| 4. Res | ults                                                           | 55 |

| 4.1.   | Initial Experiment Sets                                        | 55 |

| 4.1.   | 1. Block 1 analysis                                            | 56 |

| 4.1.   | 2. Block 2 analysis                                            | 56 |

| 4.2.   | Change on the Original Approach                                | 57 |

| 4.3.   | Slew Analysis                                                  | 58 |

| 4.3.   | 1. Block 1 analysis                                            | 58 |

| 4.3.   | 2. Block 2 analysis                                            | 60 |

| 4.3.   | 3. Block 3 analysis                                            | 62 |

| 4.4.   | Fanout Analysis                                                | 64 |

|    | 4.4.′   | 1.   | Block 1 Analysis                               | 65 |

|----|---------|------|------------------------------------------------|----|

|    | 4.4.2   | 2.   | Block 2 Analysis                               | 67 |

|    | 4.4.3   | 3.   | Block 3 Analysis                               | 69 |

|    | 4.5.    | Clo  | ck Cell Analysis                               | 71 |

|    | 4.5.´   | 1.   | Block 1 analysis                               | 72 |

|    | 4.5.2   | 2.   | Block 2 Analysis                               | 75 |

|    | 4.5.3   | 3.   | Block 3 Analysis                               | 79 |

|    | 4.6.    | Cor  | ncurrent Clock and Data Optimization Analysis  | 84 |

|    | 4.6.1   | 1.   | Block 1                                        | 84 |

|    | 4.6.2   | 2.   | Block 2                                        | 86 |

|    | 4.7.    | Clo  | ck Placement Analysis                          | 88 |

|    | 4.7.1   | 1.   | Blocks Clock Tree Trunk                        | 88 |

|    | 4.7.2   | 2.   | Block 1 Analysis                               | 94 |

|    | 4.7.3   | 3.   | Block 2 Analysis                               | 95 |

|    | 4.7.4   | 4.   | Block 3 Analysis                               | 97 |

| 5. | Bud     | get. |                                                | 99 |

| 6. | Con     | clus | ions and future development1                   | 01 |

|    | 6.1.    | Slev | w Analysis1                                    | 01 |

|    | 6.2.    | Fan  | out Analysis1                                  | 01 |

|    | 6.2.2   | 1.   | Block 1 1                                      | 02 |

|    | 6.2.2   | 2.   | Block 2 1                                      | 02 |

|    | 6.2.3   | 3.   | Block 3 1                                      | 02 |

|    | 6.3.    | Clo  | ck Cell Analysis1                              | 03 |

|    | 6.3.1   | 1.   | Block 1 1                                      | 03 |

|    | 6.3.2   | 2.   | Block 2 1                                      | 03 |

|    | 6.3.3   | 3.   | Block 3 1                                      | 04 |

|    | 6.4.    | Cor  | ncurrent Clock and Data Optimization Analysis1 | 04 |

|    | 6.5.    | Clo  | ck Placement Analysis1                         | 05 |

|    | 6.6.    | Futu | ure development1                               | 06 |

| Bi | bliogra | phy. |                                                | 07 |

| Aŗ | opendia | ces. | 1                                              | 20 |

| G  | lossary | ·    |                                                | 81 |

# List of Figures

Figure 1.1: Thesis Gantt diagram. pp.17

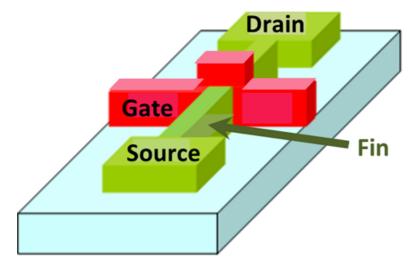

Figure 2.1: Physical structure of a FinFET. [8] pp.22

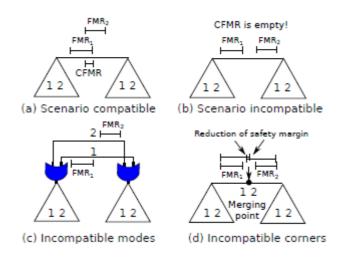

Figure 2.3: Clock tree merging possibilities depending on scenario and mode incompatibilities. pp.26

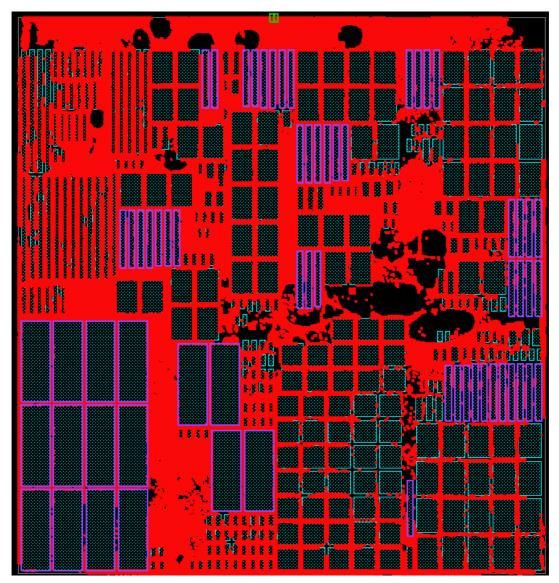

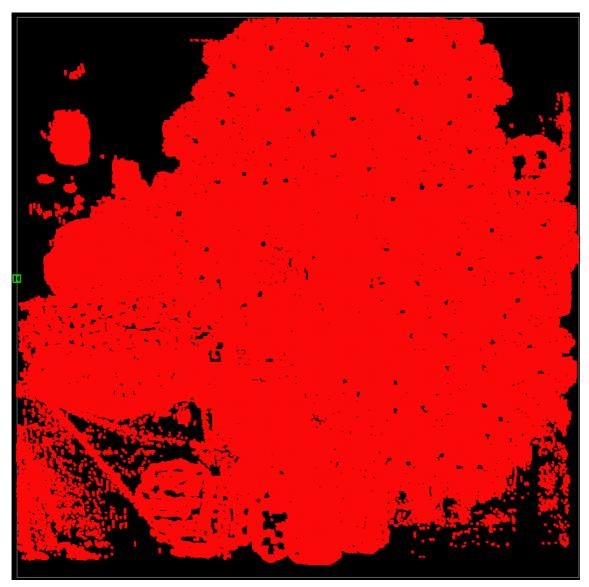

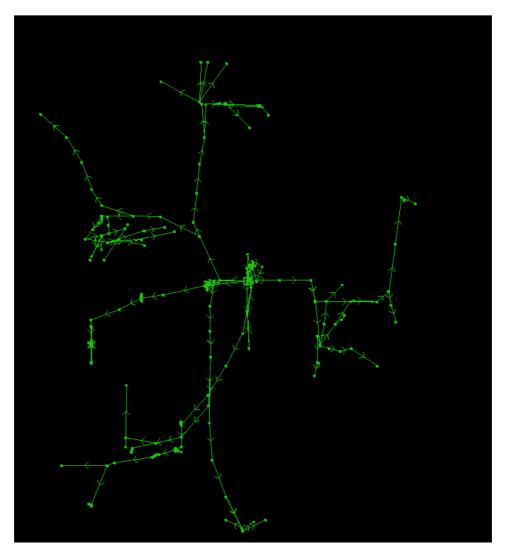

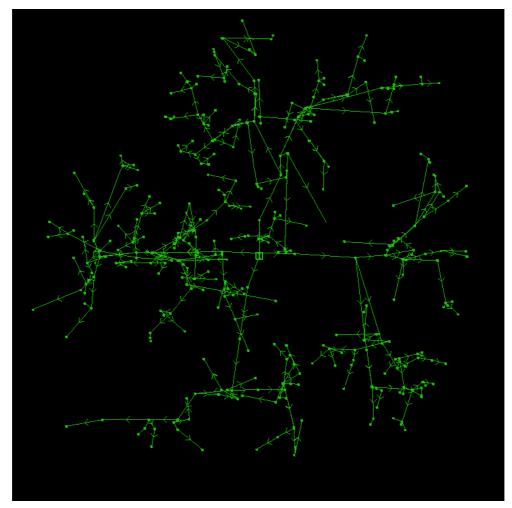

Figure 3.1: Memory and flip-flop distribution at Block 1. pp.29

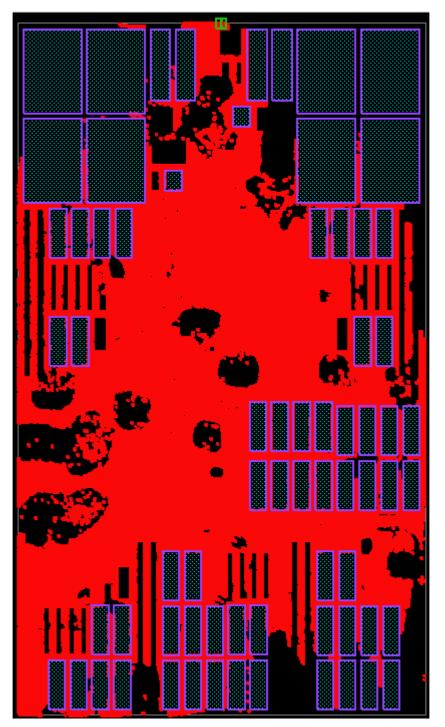

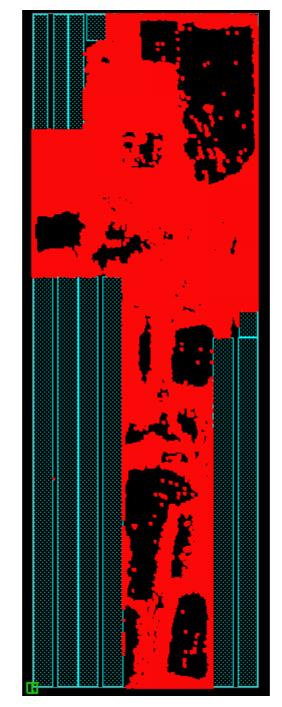

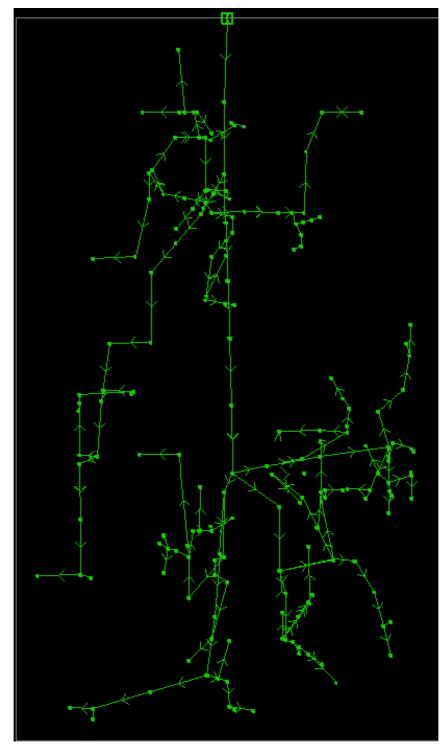

Figure 3.2: Memory and flip-flop distribution at Block 2. pp.31

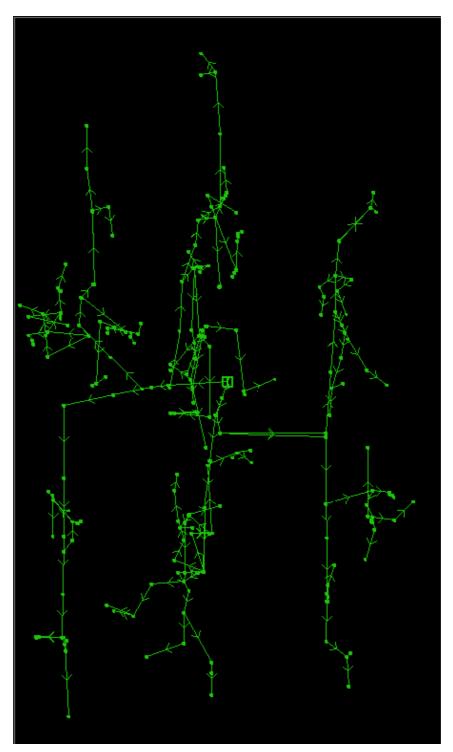

Figure 3.3: Memory and flip-flop distribution at Block 3. pp.33

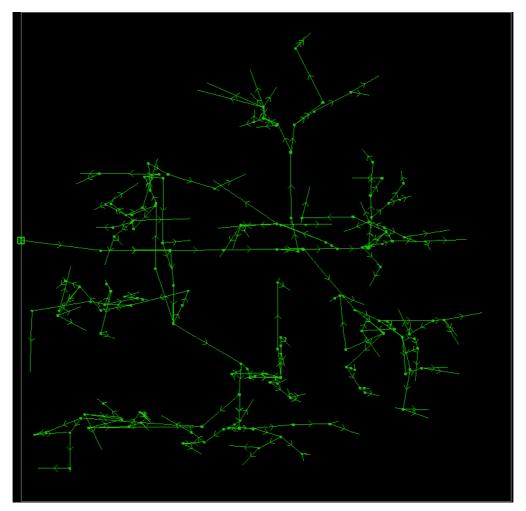

Figure 3.4: Memory and flip-flop distribution at Block 4. pp.35

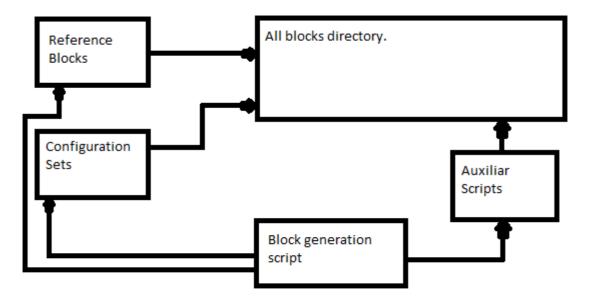

Figure 3.5: Automatic Block Generation Structure. pp.38

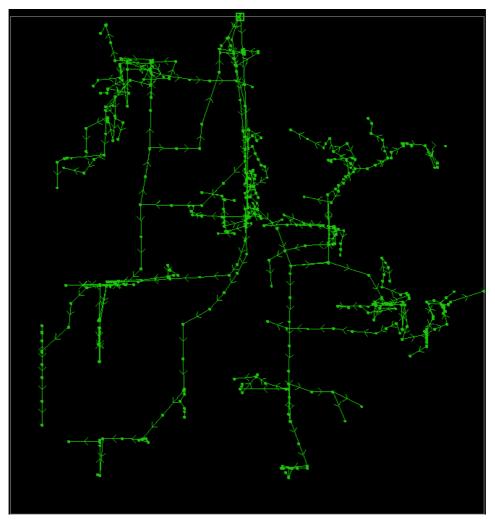

Figure 4.1: Clock tree trunk of Block 1 using the reference clock tree input pin with CCD algorithm. pp.90

Figure 4.2: Clock tree trunk of Block 1 using the centred clock tree input pin with CCD algorithm. pp.91

Figure 4.3: Clock tree trunk of Block 2 using the reference clock tree input pin with CCD algorithm. pp.92

Figure 4.4: Clock tree trunk of Block 2 using the centred clock tree input pin with CCD algorithm. pp.93

Figure 4.5: Clock tree trunk of Block 3 using the reference clock tree input pin with CCD algorithm. pp.94

Figure 4.6: Clock tree trunk of Block 3 using the centred clock tree input pin with CCD algorithm. pp.95

# List of Tables

Table 3.1: Block 1 characteristics. pp.28

Table 3.2: Block 2 characteristics. pp.30

Table 3.3: Block 3 characteristics. pp.32

Table 3.4: Block 4 characteristics. pp.34

Table 3.5: Block 1, Block 2 and Block 3 default parameters. pp.44

Table 3.6: Experiment set definition table for the slew constraint experiment set at Block 1, Block 2 and Block 3. pp.48

Table 3.6: Experiment set definition table for the fanout constraint experiment set at Block 1, Block 2 and Block 3. pp.49

Table 3.7: Experiment set definition table for the clock cell selection with fanout variation constellation at Block 1. pp.52

Table 3.8: Experiment set definition table for the clock cell selection with fanout variation constellation at Block 2. pp.52

Table 3.9: Experiment set definition table for the clock cell selection with fanout variation constellation at Block 3. pp.53

Table 4.1: Clock power and number of repeaters used and clock wirelength for the slew variations considered at Block 1 for a logic activity factor of 10% and clock activity factor of 200%. pp.61

Table 4.2: Repeater breakdown distribution at Block 1 for the different slew constraints analysed. pp.62

Table 4.3: Repeater fanout breakdown distribution and average clock cells fanout at Block 1 for the different slew constraints analysed. pp.62

Table 4.4: Clock power and number of repeaters used for the slew variations considered at Block 2 for an activity factor of 10%. pp.63

Table 4.5: Repeater breakdown distribution at Block 2 for the different slew constraints analysed. pp.64

Table 4.6: Repeater fanout breakdown distribution and average clock cells fanout at Block 2 for the different slew constraints analysed. pp.64

Table 4.7: Repeater breakdown distribution at Block 3 for the different slew constraints analysed for a fanout constraint of 32. pp.66

Table 4.8: Repeater fanout breakdown distribution and average clock cells fanout at Block 3 for the different slew constraints analysed for a fanout constraint of 32. pp.68

Table 4.9: Repeater breakdown distribution at Block 1 for the different fanout constraints analysed. pp.68

Table 4.10: Repeater fanout breakdown distribution and average clock cells fanout at Block 1 for the different fanout constraints analysed. pp.70

Table 4.11: Repeater breakdown distribution at Block 2 for the different fanout constraints analysed. pp.70

Table 4.12: Repeater fanout breakdown distribution and average clock cells fanout at Block 2 for the different fanout constraints analysed. pp.72

Table 4.13: Clock power, total power and clock power to total power distribution for all test blocks at a logic activity factor of 10% and a clock activity factor of 200%. pp.72

Table 4.14: Repeater breakdown distribution at Block 3 for the different fanout constraints analysed. pp.72

Table 4.15: Repeater fanout breakdown distribution and average clock cells fanout at Block 3 for the different fanout constraints analysed. pp.75

Table 4.16: Repeater breakdown distribution at Block 1 for the different clock cell and fanout constellations using the bigger repeater sets. pp.75

Table 4.17: Repeater fanout breakdown distribution and average clock cells fanout at Block 1 for the different clock cell and fanout constellations using the bigger repeater sets. pp.76

Table 4.18: Repeater breakdown distribution at Block 1 for the different clock cell and fanout constellations using the smaller repeater sets. pp.78

Table 4.19: Repeater fanout breakdown distribution and average clock cells fanout at Block 1 for the different clock cell and fanout constellations using the smaller repeater sets. pp.77

Table 4.20: Repeater breakdown distribution at Block 2 for the different clock cell and fanout constellations using the bigger repeater sets. pp.80

Table 4.21: Repeater fanout breakdown distribution and average clock cells fanout at Block 2 for the different clock cell and fanout constellations using the bigger repeater sets. pp.79

Table 4.22: Repeater breakdown distribution at Block 2 for the different clock cell and fanout constellations using the smaller repeater sets. pp.80

Table 4.23: Repeater fanout breakdown distribution and average clock cells fanout at Block 2 for the different clock cell and fanout constellations using the smaller repeater sets. pp.80

Table 4.24: Repeater breakdown distribution at Block 3 for the different clock cell and fanout constellations using the bigger repeater sets. pp.82

Table 4.25: Repeater fanout breakdown distribution and average clock cells fanout at Block 3 for the different clock cell and fanout constellations using the bigger repeater sets. pp. 82

Table 4.26: Repeater breakdown distribution at Block 3 for the different clock cell and fanout constellations using the smaller repeater sets. pp.83

Table 4.27: Repeater fanout breakdown distribution and average clock cells fanout at Block 3 for the different clock cell and fanout constellations using the smaller repeater sets. pp.84

Table 4.28: Repeater breakdown distribution at Block 3 for the different clock cell and fanout constellations using a mixed set. pp.85

Table 4.29: Repeater fanout breakdown distribution and average clock cells fanout at Block 3 for the different clock cell and fanout constellations using a mixed set. pp.85

Table 4.30: Repeater breakdown distribution at Block 1 for the different CCD block variations analysed. pp.87

Table 4.31: Repeater fanout breakdown distribution and average clock cells fanout at Block 1 for the different for the different CCD block variations analysed. pp.87

Table 4.32: Repeater breakdown distribution at Block 2 for the different CCD block variations analysed. pp.88

Table 4.33: Repeater fanout breakdown distribution and average clock cells fanout at Block 2 for the different for the different CCD block variations analysed. pp. 89

Table 4.34: Repeater breakdown distribution at Block 1 for the different clock pin configurations analysed. pp.96

Table 4.35: Repeater fanout breakdown distribution and average clock cells fanout at Block 1 for the different clock pin configurations analysed. pp.97

Table 4.36: Repeater breakdown distribution at Block 2 for the different clock pin configurations analysed. pp.98

Table 4.37: Repeater fanout breakdown distribution and average clock cells fanout atBlock 2 for the different clock pin configurations analysed. pp.98

Table 4.38: Repeater breakdown distribution at Block 3 for the different clock pin configurations analysed. pp.100

Table 4.39: Repeater fanout breakdown distribution and average clock cells fanout at Block 3 for the different clock pin configurations analysed. pp.100

# 1. Introduction

High frequency ASICs require large clock structures that toggle continuously. On the state-of-the-art chip clock tree power becomes one of the main contributors to the total power consumption.

Besides the direct consumption of power and area due to clock tree buffering there is also the indirect effect of clock *skew* on the number of hold buffers and timing closure effort.

Congestion problems can also be generated due to a bad clock tree building strategy.

The main goal of this project is to investigate ways to improve the clock tree building using EDA tools and quantify and qualify the results obtained and the direct and indirect effects of different clock tree building strategies using state-of-the-art blocks using sub-20nm *FinFET* technologies.

## 1.1. <u>Requirements and Specifications</u>

The scope of this master thesis is to generate a set of constraints to optimize the clock tree synthesis using EDA tools. To check the optimal constraints, they will be tested against several test blocks with different physical characteristics.

To assess the results obtained, it will be defined a set of metrics that will conform the *Quality of Results*. The *Quality of Results* will be used to determine from the metrics checked, which yields the best results and consequences on why it happens.

The first objective of the master thesis will be focused on how different configuration options provided by the EDA tool used on the test blocks can be used to improve the *Quality of Results* of all the blocks and try to obtain a transversal solution.

The second objective will be focused on the optimization of the clock structure by modifying constraints regarding their physical clock structure and design constraints.

### 1.2. <u>Statement of purpose</u>

The main objectives that are being covered on this master thesis are the following ones:

- Learning of the EDA tools used by the company where this master thesis is being developed.

- Analysis of state-of-the-art clock tree building techniques and methodologies regarding clock tree structures.

- Assessment of *Quality of Results* metrics used to analyse the results obtained on the different blocks being tested.

- Generation of experiment sets to be tested.

- Development of a test structure within the software to automatize the experiment testing in each block and the extraction of the metrics.

- Analysis of the metrics obtained by the tool and selection of the best experiment tests performed.

#### 1.3. <u>Methods and procedures</u>

This project has been developed within *ICC2 Synopsys* EDA tools. The blocks upon the project has been developed have been provided by *Esilicon S.L.* such as the basic flow structure that runs on *ICC2*. Some additional scripts used have been designed by *Synopsys* engineers being used to extract some of the *Quality of Results* metrics.

All the scripts included on this thesis have been developed personally and focus on metric extraction. Some parts of the code have been inspired by codes provided by *Esilicon S.L.* and *Synopsys.*

#### 1.4. Work plan

The project in a general approach can be separated in two main tasks.

- Learning of the development environment: The project was developed on the ICC2 EDA tool. The first part of the project involved gaining some competency in how the software environment and the company flow works.

- Project development: The main tasks that have been developed regarding the main project are the analysis of the blocks, generation of the auxiliary scripts and result analysis.

In a more detailed list, the work plan in chronological order is the following one:

- Research on Clock Tree Synthesis:

- a. Research on clock tree synthesis and basic metrics regarding CTS.

- b. Research on methodologies focused on CTS improvement.

- Software learning.

- a. Basic courses around *ICC2*.

- b. Company and software environment learning through a learning block provided by the company through all the steps.

- c. Analysis of the different company scripts to identify the procedures followed on each step.

- d. Learning of *ICC*<sup>2</sup> and company environment through scripts and graphical interface.

- e. Analysis of the reports generated by the tool for future work.

- Milestone: Acquiring competence in the software and company environment to develop the project.

- Generation of basic auxiliary scripts regarding report generation:

- a. Selection of useful metrics of the data that can be provided by the tool and generated reports.

- b. Learning of *TCL* expressions regarding data parsing through tutorials and *Esilicon S.L.* and *Synopsys* scripts.

- c. Creation of the script that must call reports, obtain the relevant data and save it on separate files depending on what area they belong.

- Test of the blocks to be analysed:

- a. Unmodified flow running, script testing and initial metrics extraction.

- Generation of the initial experiment sets and results extraction:

- a. Analysis of the tool configuration option sets using the online documentation provided by *Synopsys.*

- b. Addition of the configuration option sets to the company flow structure.

- c. Running of the experiment sets on the test block and existing analysis blocks and extraction of initial results.

- d. Deprecation of the experiment sets due to faulty methodology.

- Generation of the test structure:

- a. Automatic run generation without using the graphical interface.

- b. Modification of the company flow to include several auxiliary scripts.

- c. Modification of the report scripts to use a modified set of the *Quality of Results* Metrics.

- Generation of new experiment sets regarding physical modifications:

- a. Selection of the variations with help from company colleagues.

- b. Test of the configuration options in the blocks.

- c. Extraction of results, previous analysis and further experiment sets generations.

- Generation of a clock analysis script.

- a. Analysis of the report structure.

- b. Test of regular expressions to extract information.

- c. Basic script generation.

- d. Refinement of the script adding further functionalities.

- Final analysis of the experiment sets.

- a. Inclusion of final test block.

- b. Running missing experiment sets.

- c. Creation of a block combiner script.

- d. Obtaining QoR data and analysis.

- Thesis documentation

# 1.5. Gantt diagram

|        |                |                 |                 | 20              | 17             |                  |               |          |

|--------|----------------|-----------------|-----------------|-----------------|----------------|------------------|---------------|----------|

| Feb    | Mar            | Apr             | May             | Jun             | Jul            | Aug              | Sep           | Oct      |

| -      |                |                 |                 |                 |                |                  |               | _        |

|        |                |                 |                 |                 |                |                  |               |          |

| Previo | us Work an     | d Previous      | Work and Res    | search          |                |                  |               |          |

| Online | Online Tra     | ining           |                 |                 |                |                  |               |          |

|        |                | Example Flow    | run             |                 |                |                  |               |          |

|        | Docun          |                 | tation Resear   | ch              |                |                  |               |          |

|        |                |                 |                 | nitial Experime | unt Cate       |                  |               |          |

|        |                | itial Experim   |                 |                 | ani ocia       |                  |               |          |

|        |                | _               | Initial parsing |                 |                |                  |               |          |

|        | _              |                 |                 | olock test      |                |                  |               |          |

|        | Ini            | ti Initial expe | eriment sets    |                 |                |                  |               |          |

|        |                | Blocktest       | with expe       | Block test witl | n experiment : | sets             |               |          |

|        |                |                 | Ini             | Initial resul   | t analysis     |                  |               |          |

|        |                |                 |                 | Gene Gen        | eration and up | odate of scrip   | ts            |          |

|        |                |                 |                 | Qo QoR so       | ript update    |                  |               |          |

| Stru   | icture scripts | and automate    | ed systems      | Struc           |                |                  |               |          |

|        |                |                 |                 | New s           | New sets       | generation       |               |          |

|        |                |                 |                 | Blog            | Block run      | and analysis     |               |          |

|        |                |                 |                 | G G             | eneration of r | ew results       |               |          |

|        |                |                 |                 |                 | Clock Stru     | cture Analys     | er Script     |          |

|        |                |                 |                 |                 | New exp        |                  | eriments sets |          |

|        |                |                 |                 |                 |                | riment definitio | 'n            |          |

|        |                |                 |                 |                 | Block          |                  | and analysis  |          |

|        |                |                 |                 | 2rd Block of    |                | · _              | -             |          |

|        |                |                 |                 |                 | ddition and an |                  |               |          |

|        |                |                 | Latest exp      | eriment sets :  | and complete   |                  |               |          |

|        |                |                 |                 |                 |                | Document cr      |               | ument    |

|        |                |                 |                 |                 | Corre          | ction of data    | errors Cor    | rect     |

|        |                |                 |                 |                 |                | Writing o        | of thesis W   | riting c |

|        |                |                 |                 |                 |                |                  | Thesis rev    | ísion    |

Figure 1.1: Thesis Gantt diagram.

# 2. <u>State of the art of the technology used or applied in this</u> <u>thesis</u>

The state-of-the-art will cover the current technology used in the project as well as information on clock tree synthesis techniques.

## 2.1. Planar CMOS to FinFET

The development of this Master Thesis is focused on the optimization of clock tree building in ASIC blocks. The technology on which all the blocks have been developed is sub-20nm *FinFET* and thus will be part of the state-of-the-art of this project.

#### 2.1.1. Planar CMOS technology and its limitations

During a long time, planar CMOS technology has been the standard on IC design. In general terms it is reliable, cheap to design and it was possible to scale while improving the performance.

The Moore's Law, formulated in 1965 by Gordon Moore, predicted doubling on the number of transistors on integrated circuits every 18 months. This theorem explained the scaling of transistor's node technology up to 2010 approximately.

Planar CMOS technology has provided improvements in performance with scaling up to the 28 nm technology node. The main limitation for further scaling using planar CMOS is the increase of the leakage current as the technology nodes become smaller.

In general terms, the power consumption of a given integrated circuit can be expressed as:

$$P = \alpha \cdot C \cdot V_{DD}^2 \cdot f + V_{DD} \cdot I_{leakage} \tag{1}$$

The dynamic power depends of the circuit capacitance, the transistor capacitance, the number of gates, the power supply voltage, the frequency and the activity factor of the circuit. The activity factor of a given circuit depends on the probability of the integrated circuit working. This activity factor takes in consideration clock gating and cutting of power to certain parts of the circuit.

The usage of smaller technology nodes seeks mainly to increase the maximum frequency achievable, the optimization of power consumption.

The increase of the maximum frequency requires decreasing the transistor parasitic capacitance. One of the parameters to define the maximum frequency is the transition frequency. It is defined as the frequency on which the small signal gain of a transistor is 1.

It is defined as:

$$w_T = \frac{\sqrt{2 \cdot I_D \cdot \mu \cdot \mathcal{L}_{ost} \frac{W}{L}}}{\mathcal{L}_{gs}} \tag{2}$$

$$f_T = \frac{\sqrt{2 \cdot I_D \cdot \mu \cdot \mathcal{C}_{0X} \cdot \frac{W}{L}}}{2 \cdot \pi \cdot \mathcal{C}_{qS}} \tag{3}$$

Usually, the maximum frequency will be decades below the transition frequency, however it serves to determine an approximate maximum frequency. From expression (3), increasing the transition frequency are increasing the drain current, the aspect ratio of the transistors or reducing the gate capacitance of a transistor.

Assuming that the aspect ratio cannot be increased indefinitely and that increasing the drain current results on an increase of the power consumption, it is discarded.

Thus, the main option to increase the maximum frequency is reducing the gate capacitance. The gate capacitance depends on the transistor size, thus transistor scaling reduces the parasitic capacitance and increases the maximum achievable frequency.

The reduction on the transistor size requires lowering the supply voltage to keep in check the electric field of the transistor. With the reduction of the power supply, it is needed a reduction on the threshold voltage to keep a correct switching operation.

Thus in general terms, from expression (1), the dynamic power consumption is kept on check with the reduction of the power supply despite the frequency increase, assuming a constant activity factor and capacitance.

Regarding the leakage power, it depends mainly on two factors, the circuit power supply and the leakage power. As seen before, technology scaling requires a reduction on the power supply voltage to keep a stable electric field.

The leakage current or subthreshold current on a transistor can be defined as:

$$I_{sub} \propto I_o \cdot e^{\frac{-V_T}{n \cdot K \cdot T/q}} \propto I_o \cdot e^{\frac{-V_T}{n \cdot u_T}}$$

(4)

$$I_{sub} = I_s \cdot e^{q \cdot \frac{V_{GS} - V_T}{n \cdot K \cdot T}} \cdot \left(1 - e^{-q \cdot \frac{V_{DS}}{KT}}\right)$$

(5)

Assuming  $I_o$  being approximately constant and knowing that the thermal voltage at a given temperature will also be constant, the subthreshold current will depend on the threshold voltage. Given that it is required to reduce the threshold voltage to ensure a correct switching operation, this results on an increase of the subthreshold current as the threshold voltage is reduced.

Then, considering the leakage power expression in (1), technology node scaling causes an exponential increase on the subthreshold voltage and a linear decrease on the power supply.

Moreover, the reduction on the technology node and thus the channel length, makes it impossible to achieve a completely off-state while keeping a good on-state current drive.

Usually, the maximum frequency will be decades below the transition frequency, however it serves to determine an approximate maximum frequency. From expression (3), increasing the transition frequency are increasing the drain current, the aspect ratio of the transistors or reducing the gate capacitance of a transistor.

Assuming that the aspect ratio cannot be increased indefinitely and that increasing the drain current results on an increase of the power consumption, it is discarded.

Thus, the main option to increase the maximum frequency is reducing the gate capacitance. The gate capacitance depends on the transistor size, thus transistor scaling reduces the parasitic capacitance and increases the maximum achievable frequency.

The reduction on the transistor size requires lowering the supply voltage to keep in check the electric field of the transistor. With the reduction of the power supply, it is needed a reduction on the threshold voltage to keep a correct switching operation.

Thus in general terms, from expression (1), the power dynamic power consumption is kept on check with the reduction of the power supply despite the frequency increase, assuming a constant activity factor and capacitance.

Assuming  $I_{\circ}$  being approximately constant and knowing that the thermal voltage at a given temperature will also be constant, the subthreshold current will depend on the threshold voltage. Given that it is required to reduce the threshold voltage to ensure a correct switching operation, this results on an increase of the subthreshold current as the threshold voltage is reduced.

Then, considering the leakage power expression in (1), technology node scaling causes an exponential increase on the subthreshold voltage and a linear decrease on the power supply.

Moreover, the reduction on the technology node and thus the channel length, makes it impossible to achieve a completely off-state while keeping a good on-state current drive.

## 2.1.2. FinFET technology and its advantages

As specified before, the technology used is sub-28nm *FinFET*. On this section, it will be discussed the advantages and limitations of *FinFET*.

It has been seen that with newer technology nodes, the leakage current and thus the leakage power increases being comparable to the dynamic power consumption on a given integrated circuit.

*FinFET* technology uses a tri-dimensional gate, also called fin. *FinFET*s can have mainly two structures, the double-gate structure and the tri-gate structure.

The double-gate structure has the drain and source connected by the fin. The gate of the device is placed at both sides of the fin and covers with a ultra-thin layer of silicon the fin to connect the gate at both sides.

On the other hand, on tri-gate structures, the gate covers completely the fin, allowing gate control from either the sides or top of the fin.

One of the main advantages of the *FinFET* over planar technologies is the capability of increasing the width of the channel in a much easier way. Considering a given fin transistor, the effective width of the channel for a tri-gate structure will be:

$$W_{eff} = 2 \cdot H_{fin} + W_{fin} \tag{6}$$

Where  $H_{fin}$  is the fin height and  $W_{fin}$  is the fin width.

The physical structure of a *FinFET* is:

Figure 2.1: Physical structure of a FinFET. [8]

Knowing that the current is dependent on the width of the channel, it is possible to increase the driving current of a given transistor by increasing the fin height. Moreover, this tri-dimensional structure, makes possible to achieve higher levels of transistor density by increasing the fin height instead of making wider transistors, when comparing to planar CMOS.

Given the nature of the gate in tri-gate structures, it is easier to control the transistor in smaller technology nodes, as opposed to planar CMOS where for a similar technology node, the required threshold voltage would difficult a proper switching.

This results also on a reduced leakage current with a lower threshold voltage due to better gate control. The use of the fin also makes redundant the doping of the channel in order to prevent Drain Induced Barrier Lowering and other short-channel effects that appeared in planar CMOS technology.

The reduction on the threshold voltage allows as well the reduction of the power supply voltage, effectively lowering the dynamic and leakage power of a transistor.

The elimination of channel doping processes increases carrier mobility and reduces the process variability.

On the other hand, the use of a tri-dimensional structure poses many challenges that have to be solved.

There is less flexibility in the control of the on-state current drive due to the nature of the fin. The effective channel width will depend on the fin height and on the number of fin fingers used on the design.

Multiple fins are used in order to limit the drain-source resistance introduced by reducing the fin width. By using multiple fins, the total channel width can be estimated to:

$$W_{tot} = W_{eff} \cdot N_{fin} = \left(2 \cdot H_{fin} + W_{fin}\right) \cdot N_{fin} \approx 2 \cdot H_{fin} \cdot N_{fin} \tag{7}$$

This expression considers that the fin width is negligible compared to the fin height. The fin height will be fixed by the technology considering technical limitations and process design.

As it can be seen, the channel width and thus the driving strength becomes quantized and can only be increased by the number of fins, compared to planar CMOS where it is possible to achieve better control the on-state current by modifying the channel width.

It must also be considered tri-dimensional structure for physical layout design. It must be considered in closer detail the placement of transistors. Previously, for the designer it was not as important to know the relationship between the design layout and the manufacturing process.

This however cannot be applied to *FinFET* structures. It is necessary by the technology provider to give detailed information on the physical characteristics of the device and it is necessary for the designer to have knowledge on the manufacturing process.

## 2.2. <u>Terminology and Concepts</u>

The main topic of this thesis is the optimization of the clock structure on ASIC blocks. In this section, it will be covered the main definitions regarding clock power.

The *Worst Negative Slack* is referred to the maximum difference between the clock and data arrival at given flip-flop. If the *Worst Negative Slack* obtained is lower than zero, it means that this path and the design is not meeting timing enclosure and thus will not work at the desired frequency.

The Total Negative Slack is the sum of all the slack values obtained on a given design.

The *Skew* indicates the timing difference of the earliest clock signal arrival and the latest clock signal arrival at the flip-flops of a design. The *skew* values obtained can be misleading and thus the term *Local skew* is used.

The *Local skew*, in contrast with the Global *Skew* indicates the maximum timing difference of the clock arrival at flip-flops of a given timing path. *Local skew* will then not consider the maximum timing difference between flip-flops that do not share the same timing path and will give more accurate timing information.

The *Latency* or *Insertion delay*, indicates which is the time it takes for the clock signal to propagate from the clock source to the furthest flip-flop of the design.

The Utilization of a given design is the quotient between the area used by standard cells and macro cells and the total area of a design. The tool used defines the utilization as the quotient between the standard cell area and the total area.

## 2.3. Adjustable Delay Buffers

The next sections will cover the use of several techniques referring to clock tree synthesis and improvement on the clock tree structure. The first section will cover the use of Adjustable Delay Buffers, while the second one will cover the use of reconfigurable clock trees.

On current designs, the effect of process variations such as temperature, voltage on multi-power mode designs can affect and degrade the performance of a given block. All this processes variations and the problems they may cause, become much more severe as technology scales down.

One of the main problems to arise is the hold and setup timing violations. The use of hold-fixing and effective *skew* management techniques can be used in order to improve results. Several other methodologies have been explored to deal with process variation such as buffer insertion and sizing and wire sizing.

However on multi-power designs with on-chip-variations considered, the resulting clock can present high wirelengths that may affect negatively signal routing or have no clock distribution that meets the timing requirements of the design on all the scenarios.

Adjustable Delay Buffers (ADBs) are used on post-silicon tuning to deal with timing enclosure. ADBs can have their delay modified by a control input.

By replacing some buffers on the base design by ADBs it can be possible to modify the delay they present for different power modes or OCV. However, ADBs in comparison to regular buffers they require a bigger area, additional control logic and have a higher power consumption. This sets a limit on how many buffers can be inserted to avoid excessive power consumption.

The problem for buffer insertion can be formulated as:

- Add the minimum number of buffers that allow meeting mode *skew* requirements with the least power overhead.

- Meet the global *skew* requirements imposed by the design.

This first algorithm for ADB insertion takes into consideration the global design *skew* or local module *skew*. Under these considerations, although the *skew* requirements are met, there can be hold and setup time violations on individual nodes across multiple power modes and domains.

Considering the setup and skew bounds as:

$$x_j - x_i \ge D_{max}(Ckt_{i,j}) + t_{setup} - t_{clk}$$

(8)

$$x_i - x_j \ge t_{hold} - D_{min}(Ckt_{ij}) \tag{9}$$

$x_i$  and  $x_j$  are the clock arrival at sinks i and j (where data goes from i to j).  $D_{max}(Ckt_{i,j})$  and  $D_{min}(Ckt_{i,j})$  are the maximum and minimum delays from the output of sink i to the input of sink j.  $t_{clk}$  is the clock period.  $t_{setup}$  and  $t_{hold}$  are the setup and hold constraints that must be met. If the inequalities are met, then the design will have no setup or hold violations.

The addition of ADBs will allow modifying the delay between the sinks and allowing meeting the timing constraints.

Negative setup time violations are quite hard to fix as it will usually imply increasing the clock period and thus lowering the maximum frequency of the circuit. It can also be fixed by optimizing the datapath structure.

However, negative hold time violations imply that data can change before the clock captures it. This can be fixed easier by adding delays to the datapath in order to delay the data arrival.

By modifying existing ADB insertion algorithms to take into consideration setup and hold time, it is possible to achieve designs that can meet timing enclosure as well as reducing the number of violations of the design.

As explained before, as technology scales down, on-chip-variation effects become more prevalent. This makes timing enclosure harder and thus worsens chip performance. Frequency scaling has also limited the *skew* bounds to meet timing enclosure.

Process variations considered to be relevant to affect buffer delay are wire width, supply voltage, temperature, load capacitance and input *slew*.

### 2.4. <u>Reconfigurable Clock Trees for Multi-Corner Multi-Mode designs</u>

Clock network of integrated circuits must be able to operate on multiple corners and multiple modes (MCMM).

It is purposed the use of multiple clock trees to meet the *skew* requirements for each scenarios. As building several clock trees it requires an increase of area and power consumption, the bottom end of the tree is shared and always active.

To determine which parts of the clock network are active, or gates and a one-input noutputs demultiplexer is used.

Each scenario will have different *skew* constraints. The *skew* for each scenario will take into consideration a safety margin.

If two subtrees are active on a group of scenarios, a feasible *skew* graph will be made. This graph will contain a paired table of all sinks and *skew* constraints.

After applying the safety margin on the *skew* constraints, both subtrees will be paired and if a common merging region exists (*skew* margin for the common sinks  $\geq$  0), both subtrees can be merged obtaining a feasible clock schedule for the new tree.

If the merging region of both subtrees is empty (the *skew* margin for common sinks < 0).

Two type of incompatibility are considered, mode and scenario incompatibility. When two subtrees are scenario incompatible but mode compatible it implies that there is no common merging region. If by decreasing the safety margin applied initially a common merging region exists then the two subtrees are scenario compatible and can be merged.

Mode incompatible trees will not be able to be merged in any case and will be buffered and controlled by combinational logic on the final tree.

*Figure 2.2:* Clock tree merging possibilities depending on scenario and mode incompatibilities.

# 3. <u>Methodology and Project Development</u>

The Master thesis was initially focused on analysing how the modifications of the configuration options on the EDA tool used could improve the results obtained regarding clock building.

Mid-project, that approach was abandoned due to the reasons presented in the next chapter and a new focus was followed.

The new approach upon which the majority of the master thesis will be focused is regarding clock tree structural changes such as the *slew* or the *fanout* constraint.

This chapter will cover how the project structure has been developed in order to generate an automated block and report system.

It will also be presented the blocks being used on this thesis as well as which experiment sets have been used and the reasoning behind them while the most relevant results will be presented on the next chapter.

#### 3.1. Block Definition and Characteristics

To test the different experiment sets that will be explained later it is necessary to select different blocks to present a transversal picture. To make an appropriate block constellation several conditions should be met:

- Same technology in all blocks: To have more reliable results due to the limitations on the tests developed all blocks should be developed on the same technology to reduce variability in the results and to ease analysis.

- Blocks with different characteristics: The blocks should be different enough and have different characteristics in terms of physical layout.

By having different blocks it might be possible to give an optimal set of configurations for all blocks.

Block selection will be done considering their layout distribution. Three blocks have been selected: a block dominated by memory, a block dominated by logic and a mixed block.

The usage of memories affects how flip-flop distribution and routing is done. Most usually, memory placement in a block requires of a restricted area around it where neither cells nor routing can be done.

This differs from mostly logical blocks where this restriction does not exist usually resulting on a better and easier block development.

Asides from this block classification it will be considered the following characteristics to define each bloc:

- Number of flip-flops

- Number of memory instances

- Number of logic instances

- Total area

- Memory area and memory area percentage

- Logic area and logic area percentage

- Memory to logic ratio

#### 3.1.1. Block 1

This block is memory dominated and has the following characteristics:

| Number of flip-flops       | 433,290          |

|----------------------------|------------------|

| Number of memory instances | 417              |

| Number of logic instances  | 329177           |

| Total area                 | 5,924,460.81 um2 |

| Utilization                | 0.3186           |

| Memory area                | 3,329,044.77 um2 |

| Memory area percentage     | 56.19%           |

| Logic area                 | 792194.14 um2    |

| Logic area percentage      | 13.37%           |

| Memory to logic ratio      | 4.2              |

Table 3.1: Block 1 characteristics.

In terms of area and physical layout this is the most complex block. It has the most memory instances taking roughly 60% of the total area with a memory to logic ratio of 4.2.

In the physical layout the memories are placed all across the block. Flip-flops are distributed across all the block and in-between the memories. Open areas without memory blockages are not fully used to place flip-flops.

The following figure shows the memory placement and flop distribution of Block 1. The clock input pin is marked on green.

Figure 3.1: Memory and flip-flop distribution at Block 1.

## 3.1.2. Block 2

This block is considered as mixed and its characteristics are the following ones:

| Number of flip-flops       | 347,531          |

|----------------------------|------------------|

| Number of memory instances | 110              |

| Number of logic instances  | 243,314          |

| Total area                 | 2,132,247.05 um2 |

| Utilization                | 0.4576           |

| Memory area                | 856,478.89 um2   |

| Memory area percentage     | 40.16%           |

| Logic area                 | 570,155.27 um2   |

| Logic area percentage      | 26.73%           |

| Memory to logic ratio      | 1.5              |

Table 3.2: Block 2 characteristics.

This block is considered as a mixed block in terms of memory and logic distribution as it has a memory to logic ratio of 4.2 compared to Block 1.

The physical layout on this case is different from Block 1. This block has less memory instances which take less area than on the first case. There are open spaces with no memory blockages that are used for flip-flop placement. The number of in-between memories flip-flops is also lower than on the first block.

The following figure shows the memory placement and flop distribution of Block 2. The clock input pin is marked on green.

Figure 3.2: Memory and flip-flop distribution at Block 2.

## 3.1.3. Block 3

The final block considered to perform the different experiment sets is purely logic. Its characteristics are the following ones:

| Number of flip-flops       | 339,959          |

|----------------------------|------------------|

| Number of memory instances | 0                |

| Number of logic instances  | 2,084,106        |

| Total area                 | 1,276,547.46 um2 |

| Utilization                | 0.3609           |

| Memory area                | 0 um2            |

| Memory area percentage     | 0                |

| Logic area                 | 460,769.45 um2   |

| Logic area percentage      | 36.09%           |

| Memory to logic ratio      | 0                |

Table 3.3: Block 3 characteristics.

On this case, there are no restrictions for flip-flop placement and routing as there are no memory or other types of blockages in the block layout.

The following figure shows the clock pin placement as well as the flip-flop placement across the block.

Figure 3.3: Memory and flip-flop distribution at Block 3.

## 3.1.4. Block 4

The final block does not classify into the test blocks used to develop this project. The objective of this block was to make an initial test in the configuration options and variations tested in the experiment blocks before passing them to the test blocks.

This block has a much simpler structure than the other blocks which allows having faster runtimes to correct possible errors that may happen in the sets test.

The block characteristics are the following ones:

| Number of flip-flops       | 39,785         |

|----------------------------|----------------|

| Number of memory instances | 11             |

| Number of logic instances  | 284,307        |

| Total area                 | 194,977.09 um2 |

| Utilization                | 0.4528         |

| Memory area                | 66,240.06 um2  |

| Memory area percentage     | 33.97%         |

| Logic area                 | 63,370.27 um2  |

| Logic area percentage      | 32.5%          |

| Memory to logic ratio      | 1.05           |

Table 3.4: Block 4 characteristics.

Figure 3.4: Memory and flip-flop distribution at Block 4.

#### 3.2. <u>Metrics Definition</u>

To perform the analysis on the different experiment sets that have been performed, a group of metrics have been used to define the *Quality of Results*.

The definition of the metrics have been classified under two groups.

- Power Performance Analysis metrics (*PPA*): These are the main metrics used to analyse the results obtained, they are related to timing, clock power and clock area metrics.

- Support metrics: These metrics are used to support the results obtained and include skew, insertion delay, number of clock instances, utilization, DRC violations and clock structure.

#### 3.2.1. Power Performance Analysis metrics

This metrics specified are the most important considered . The *Worst Negative Slack* is the main timing metric considered as it indicates if the block can work at the specified frequency.

The clock power and area give a general idea on the optimization of the clock structure. The clock power is relevant as the dynamic clock power can represent large portions of the total power.

The clock area, albeit it is not relevant when considering to the total area of the circuit can be used to compare different runs.

The number of clock instances can be used together with the clock power and area to compare between different runs.

#### 3.2.2. Support metrics

The support metrics are used together with the PPA metrics.

The *skew* gives an indication of the clock tree balance and indicates the maximum difference of the clock arrival at the flip-flops of a block.

The *latency* is the maximum delay from the clock input pin to any of the end-points of the block.

The number of clock instances can be used together with the clock power and area to compare between different runs.

The utilization determines the total area used by the logic compared to the total block area.

The number of *DRC* violations can be used to indicate possible problems on a block. They indicate problems during the design in terms of spacing, overlapping, etc.

## 3.3. <u>Scripts and Automatic Block Generation</u>

This section will cover how the block and report generation system has been build up. The first part of this section will cover how the system in charge of generating blocks and the modifications to be made, as well as running the block and extracting the information of interest has been designed.

The second part of the section will cover the most relevant points of the scripts done in order to have this system.

In general lines, the system had to be able to use the basic shell scripts provided by the company that form the flow to be followed, while being flexible enough to introduce modifications and report the desired values.

#### 3.3.1. Automatic Block generation

The automatic block generation system is made out of several sub-blocks. Essentially the system can be simplified in the following blocks:

- Reference shell blocks: Contains the reference blocks modified to fit the automated system.

- Configuration sets directory: Folder that contains all the configuration scripts in Tool Command Language (*TCL*)

- Auxiliary scripts directory: Folder that contains reporting scripts and other modification scripts for some options in Tool Command Language (TCL)

- General block directory: Directory in which all blocks are run. Has several subdirectories for each block type.

- Block generation script: Script in charge of copying the shell blocks, the auxiliary scripts and chosen configuration sets in the main block directory and start the flow.

The following figure summarizes the block structure used:

Figure 3.5: Automatic Block Generation Structure.

# 3.3.2. Reference shell blocks

The shell blocks contain the basic company flow, the constraints file and the floorplan file. This file has the following modifications:

- Activation of all the scenarios at each step to avoid having any scenarios inactive. This is necessary to obtain the best results across all scenarios by analysing the worst case.

- Inclusion of the configuration sets in all steps. This is done as some configuration options must be used first at different steps. By running in all steps this possible error is avoided.

- At the final of the routing stage, runs all the reporting scripts and stores them in the desired folders.

# 3.3.3. Configuration sets directory

As specified before, this directory contains all the desired configuration scripts. The script specified at block generation script is copied and added into a selected folder on the modified reference block.

Asides from some specified experiment sets that do require additional modification, the configuration script will be the only one needed to generate the desired modification.

# 3.3.4. Auxiliary scripts directory

This directory contains additional reports to add functionalities to the block generation script as well as other scripts that must be used. Most scripts are added automatically to the flow while some others are used manually for specific uses.

These auxiliary scripts can be classified on the following types:

- Reporter and parser scripts: Used to generate partial and final files that contain the desired reported information for the *Quality of Results*

- Clock Structure Analyser: Extracts information about the clock structure and stores it in a file.

- Clock pin modification script: This code changes the positioning of the clock pin placement for an experiment set.

- Report combiner: This script combines the *Quality of Results* obtained by the parser scripts and adds some mathematical operations to have more complete comparison results.

#### 3.3.5. General block directory:

All the block runs are placed in the same directory folder. For each block a new subdirectory is needed. In each subdirectory the block flows are placed. The flows are based on the reference company flow with some modifications done to fit the designed system.

To ensure proper working it is needed to create the directory either manually or set it up in the block generation generation script.

#### 3.3.6. Block generation script

All the following scripts and directories are managed by the block generation script. The block generation script follows this sequence.

- Creates block sub-directory in the general block directory.

- Copies the floorplan, scripts and auxiliary override folder.

- Copies the configuration script to the override folder and renames it.

- Copies the rest of auxiliary scripts.

- Changes to the subfolder and runs the start-up script from the copied flow.

Despite being able to automate the running of scripts flows it has some limitations that must be taken into consideration else the script will fail at the start-up script or give an erroneous block.

- The shell block flows must be modified to take into account the scripts added that must be run.

- The copied scripts must be placed at the same subdirectory within each block.

- In the block generator script, if any block should be added, the script must be added manually, that is, it has no self-modification capabilities to include newer blocks.

Within the specified parameters, the script behaves correctly while being quite inflexible if the block structure or script placement is out of the planned norm.

## 3.4. Script Analysis and Explanation

This section will include more detailed explanations and remarks on the scripts that have been used in the block generation script and other auxiliary scripts. Only the user-written scripts will be explained and included on the annexes while giving general explanations on company and *Synopsys* scripts.

## 3.4.1. Block Generation Script: *run\_gen.tcl*

As explained on the previous section, this script is in charge of copying the desired scripts and running the set-up flow script to start and run the block.

As specified before, the initial code block of the script will copy and rename the needed scripts in the block folder.

After copying the desired scripts, sets up the main setup script of the flow, choosing different memory assignation depending on the block type.

One of the main points to take into consideration from the setup script calling:

- Typical setups will call an interface and a Graphical User Interface (GUI) while this script does not. This adds flexibility and reduces user managed steps, however it removes tolerance to errors as a block error will shut down the current job and give no error warning unless specified.

- User modifications are needed to change the memory requirements, log reports, type of machine used amongst others.

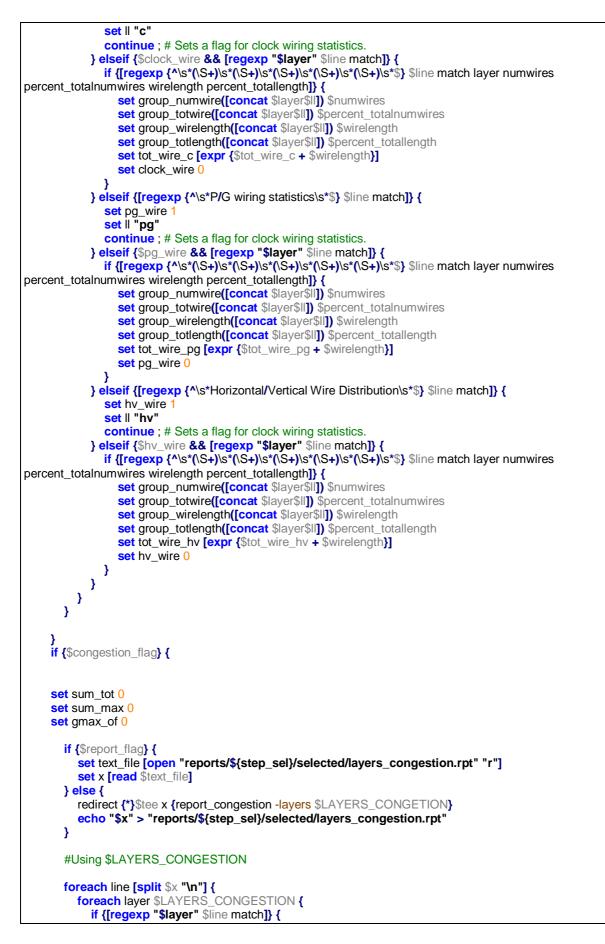

#### 3.4.2. Reporter and parser: report\_parser.tcl

This is the script in charge of generating reports and parsing them in a more compact format. The output files of this script are given in a Comma Separated Values format (.csv) to use them in other programs in order to analyse results.

The script has been designed to generate individual reports on different areas of interest such as:

- Total power information.

- Clock power information.

- Insertion delay.

- Routing information.

- Local skew reports.

- Wirelength information

- Layer congestion.

- Utilization.

- Clock area information.

By running the report manually it is also possible to execute this script on any step by selecting it in a script option.

Asides from the reports generation there are options to generate a more compact file with the final selected *QoR* file format. To avoid problems regarding scenario name due it being able to vary, the information is passed to the script manually.

The basic structure that is followed at each individual report and parsing of it is the following one:

- Check existence of scenarios.

- Generates the report or uses an existing report if present in the flow.

- Line by line analysis using the regular expression structure provided in the TCL package.

- Assignation to user made variables of the relevant information obtained via parsing.

This procedure is repeated for all individual report types, parsing and storing the information into user defined variables.

Once all the variables are obtained, individual *CSV* files are generated with all the information. Asides from the individual reports, a final file is generated containing the most relevant information. The information preparation and storage in a file is done as it follows:

- First, it is checked if the file must be generated and pre-preparation of obtained information is done.

- Once the data preparation is done, the file is created and opened. Then the information is written and the file is closed to avoid errors. It is necessary to define the separator used, to then make it available data sheet programs.

Most scripts with certain complexity in *TCL* require argument declaration to work correctly. The argument declaration is done outside of the main script and it must be parsed at the beginning of the script to extract the information.

At the argument declaration it must be declared how it is called, a description, and which type of variable it requires and whether it is optional or not.

## 3.4.3. Clock Structure Analyser: clock\_structure\_analyser.tcl

This script is in charge of analysing the physical clock structure file of a given block and extract relevant information. The main information being obtained is:

- Number of *repeaters*, Integrated Clock Gating Cells (*ICG*), clock sinks, balance pins and clock sources.

- Fanout of repeaters and ICGs.

- Types of *repeaters* and *ICGs* used.

- Location of clock cells and sink pins.

- Wire and cell capacitance.

Asides from this information, this script provides basic math support to extract average *fanout*, average Manhattan distance between clock cells and sinks, average cell and wire capacitance, etc.

Debugging code has been added to check if the assumptions made in terms of possible line structures in the report exist.

Overall, the data parsing and handling has been done similarly to the *report\_parser.tcl* script with some modifications to data treatment, focusing more on the use of arrays when possible as they prove to be better optimised and given the sheer size of the clock reports analysed can cut some machine time needed.

As done previously, the first step is checking if a clock structure report file exists, if it does not, or it is wanted anyways, a new file will be created on a user selected directory while keeping old files.

When the file is extracted, several counters and auxiliary variables will be declared to be used later. The counters will be used to obtain numbers on how many *repeaters*, *ICGs*, sink pins and balance pins are obtained. The sink pins are the flip-flops of the design while the balance pins are used to balance capacitance in the clock branches.

Five different structures have been found to be present in any clock structure file generated by the tool reporter and thus taken into consideration. There is one line type for clock sources, *repeaters*, *ICGs*, sink pins and balance pins.

For each type, it is checked if the current line follows its structure and then the information is extracted following the same pattern used in the other scripts that need parsing.

The obtention of the average and maximum repater and *ICG* is done iterating over the obtained arrays in the regular expression. For each position on the array, the *fanout* obtained is read and several counters are increased depending on the value of the *fanout*.

The Manhattan distance is defined as the distance measured along the defined axis. On this case, Cartesian axis are used and the total Manhattan distance will be defined as:

$$M_{distance} = x_{distance} + y_{distance}$$

(12)

On this case, the Manhattan distance has been calculated between and endpoint driver and the downstream sinks and balance pins.

The capacitance information is also obtained via the attribute of the nets connected to an endpoint driver.

## 3.4.4. Clock pin modification script: *replace\_clockpin.tcl*

In some experiment sets, the input clockpin is centered and a superior layer is used to check if better results can be obtained in terms of clock building. The pin movement was done after the initial cell placement. To move the clock pin it is needed to give the initial clock name to locate and remove it, and then create a new clockpin on the new position.

To perform the pin movement several information is needed:

- Current clockpin name.

- Block dimensions.

- Pin shape type

- Pin margin.

The block dimensions are used to calculate the middle point of the block, while the pin margin is used to avoid conflict with other block tracks, memories, etc. The shape type is defined in by the tool and is needed to create the shape.

To move the clockpin, the existing shape must be deleted and a new clockshape is created.

#### 3.4.5. Report combiner: *block\_combiner.tcl*

Given how the block generator and report generation is done, one report is generated for each block. Because of that reason, it is needed an auxiliary report to combine existing report *CSV* files.

This script combines the existing reports given separated by block type and block name and has the capability of performing some mathematical operations to simplify the analysis. Similar to other blocks, the *CSV* file generation is done following a similar procedure as in other cases.

The block selection is done with an empty list that adds all the blocks on which data has been defined. Similarly to other cases, the existing data has been parsed in order to simplify the results.

For each list, the data is obtained using a regular expression as in previous cases. For each block, the report parsed file is analysed which simplifies obtaining the data.

A math flag has been enabled to perform some percentages to ease further analysis.

Once the data is obtained, if the math flag is active, it will perform some percentages to ease further analysis, the first block passed is used as a reference and the information obtained is passed to a new set of variables.

## 3.5. <u>Methodology and Experiment Sets</u>

As explained before, the methodology followed in the thesis development and result analysis has followed two main approaches. One followed on the selection of optimal configuration options within the EDA tool and one focused on physical modifications in the clock characteristics. On this section, all the experiment sets will be defined with explanations on why they were chosen.

#### 3.5.1. Reference block parameters

| Default Slew Constraint         | 80 ps                       |

|---------------------------------|-----------------------------|

| Default Clock Fanout Constraint | 32                          |

| Default Repeater Inverters      | INV_D16, INV_D12 and INV_D6 |

| CCD Application                 | Active                      |

| Clock Pin Placement             | Default                     |

The reference parameters used on each block are the following ones:

**Table 3.5**: Block 1, Block 2 and Block 3 default parameters.

All the experiment sets performed after the initial set have been done by modifying one of the given parameters unless it is specified on the experiment set definition.

## 3.5.2. Initial Experiment Sets

The initial approach from which the project was to work upon the configuration options of the tool.

Compared to modifications in a block done by an engineer, modifications done in the application options of a design tool do not affect as heavily the physical design of a block.

To limit the scope of the project, the application options were intended to focus only on the Clock Tree Synthesis of the block.

Given modifications on the application options of the design tool, it is desired to optimize the design based around a given set of blocks with different physical characteristics.

The initial application options experiment sets that were considered were based around the following considerations:

- Concurrent Clock and Data Optimization

- Layer Optimization

- Integrated Clock Gater Optimization

- Congestion Effort

- Clock Miscellaneous Configurations

- Local skew Optimization

- Other Configuration Options

#### 3.5.2.1. Configuration options explanations and expected results

The explanation for the configuration options given before is the following one:

Concurrent Clock and Data Optimization: Concurrent Clock and Data Optimization (CCD) is a configuration option introduced by Synsopsys to help meeting timing constraints on high frequency circuits.

The main application options that were covered in this experiment sets revolved around enabling *Concurrent Clock and Data Optimization* were:

- a. *CCD* enabling during placement, clock routing and general routing.

- b. Boundary timing enabling: *Concurrent Clock and Data Optimization* can either be applied to all the flip-flops in the design or only to non-boundary flip flops. Omitting boundary flip-flops is useful when signals can be introduced from outside, pin capacitance may not be stable or controlled and thus omitting them from being applied to *CCD* can be benefitial.

- c. Clock aware placement: Enables placement of Integrated Clock Gaters (*ICG*) and their *fanout* cells considering timing criticality.

- Layer Optimization: Layer optimization considers layer resistance and capacitance, as well as possible congestion problems to manage how routing is distributed through different layers.

- a. Placement and clock routing layer optimization: If critical nets are detected, those are assigned to upper metal layers to improve timing.

- b. Layer overlapping: Metal layers are set in pairs, this option enables mixing the metal layer pairs to improve the *QoR* obtained.

- Integrated Clock Gaters Optimization: Integrated Clock Gaters are clock cells designed to switch off certain parts of the clock tree to avoid unnecessary power consumption in certain scenarios.

- a. Clock aware placement and trial clock tree: Enables an early clock tree during placement used for *ICG* optimization flow.

- b. *ICG* auto bound: Creates group bounds for *ICG*s automatically for placement.

- c. *ICG* placement optimization: Enables *ICG* optimization with the specified options.

- d. *ICG* splitting: Enables *ICG* splitting to meet timing constraints unless specified otherwise.