UNIVERSITAT POLITÈCNICA DE CATALUNYA

# TRABAJO FINAL DE GRADO

TÍTULO DEL TFG: Diseño de un circuito discriminador de frecuencia de microondas en banda Ka.

TITULACIÓN: Grado en Ingeniería de Sistemas de Telecomunicación

**AUTOR: Christian López Corcuera**

**DIRECTOR: Ignacio Llamas-Garro**

FECHA: 07/09/2017

Título: Diseño de un circuito discriminador de frecuencia de microondas en banda Ka.

**Autor: Christian López Corcuera**

**Director: Ignacio Llamas-Garro**

Fecha: 07/09/2017

#### Resumen

Este proyecto final de grado describe el concepto, los criterios y el diseño de un discriminador de microondas de 2 puertos, que es el elemento fundamental en un sistema de medición de frecuencia.

El discriminador de microondas realiza la función de detectar frecuencias desconocidas en la banda Ka (30-40 GHz).

El discriminador está formado por cinco líneas: la primera línea es un desfasador de  $180^{\circ}$  que actúa como referencia y permite generar discriminadores de microondas reconfigurables de reducido tamaño y peso. Las siguientes líneas de retardo de longitud " $\lambda$ ", " $3\lambda/2$ ", " $2\lambda$ " y " $5\lambda/2$ " son los elementos principales para la construcción del discriminador, todas estas líneas están conectadas al divisor de potencia a la entrada y al combinador de potencia a la salida del circuito, por último se conecta un sistema de conmutación SPQT que se encargará de la conmutación entre los discriminadores. Para su diseño se emplea tecnología coplanar.

El divisor de potencia empleado está diseñado con tecnología coplanar. Es un divisor de Wilkinson que actúa también como combinador de potencia conectado a la línea de referencia y a las de retardo. Los puertos de entrada y salida del discriminador serán el puerto de entrada del divisor y el puerto de salida del combinador respectivamente.

Las simulaciones de cada línea de retardo y el diseño final del discriminador se han realizado con ADS/Momentum obteniendo resultados satisfactorios. Esto ha permitido integrar el diseño resultante con los demás componentes del discriminador para obtener posteriormente los bits de identificación de la señal.

Title: Design of a microwave frequency discriminator network in Ka band.

**Author: Christian López Corcuera**

**Director: Ignacio Llamas-Garro**

Date: 07/09/2017

#### Overview

This final grade project describes the concept, criteria and design of a 2-port microwave discriminator, which is the fundamental element in a frequency measurement system.

The microwave discriminator performs the function of detecting unknown frequencies in the Ka band (30-40 GHz).

The discriminator consists of five lines: the first line is a 180 ° phase shifter that acts as a reference and allows the generation of microwave discriminators reconfigurable of reduced size and weight. The following delay lines of length " $\lambda$ ", " $3\lambda$ / 2", " $2\lambda$ " and " $5\lambda$ /2" are the main elements for the construction all these lines are connected to the power divider at the input and power combiner at the output and finally a system of SPQT switching. Coplanar technology is used for its design.

The power divider used is designed with coplanar technology. It is a Wilkinson splitter that also acts as a power combiner connected to the reference line and to the delay line. The input and output ports of the discriminator will be the input port of the splitter and the output port of the combiner respectively.

The simulations of each delay line and the final design of the discriminator were performed with ADS / Momentum obtaining satisfactory results. This has enabled the resulting design to be integrated with the other components of the discriminator to subsequently obtain the signal identification bits.

# ÍNDICE

| CAF        | PÍTULO 1. INTRODUCCIÓN                     | 6        |

|------------|--------------------------------------------|----------|

| 1.1.       | Motivación                                 | 6        |

| 1.2.       | Objetivos                                  | 6        |

| 1.3.       | Descripción de componentes                 | 7        |

| 1.4.       | Organización del proyecto                  | 8        |

| 1.5.       | Bibliografía                               | 10       |

| CAF        | PÍTULO 2. LÍNEAS DE TRANSMISIÓN            | 11       |

| 2.1.       | Tecnología coplanar                        | 11       |

| 2.2.       | Modo Coplanar Par                          | 12       |

| 2.3.       | Modo Coplanar impar                        | 13       |

| 2.4.       | Bibliografía                               | 15       |

| CAF        | PÍTULO 3. DISCRIMINADOR DE MICROONDAS      | 16       |

| 3.1.       | Introducción                               | 16       |

| 3.2        | Tipos de discriminadores                   | 16       |

| 3.3        | Criterios de diseño                        | 18       |

| 3.4        | Resultados teóricos                        | 19       |

| 3.5        | Resultado de simulaciones                  | 23       |

| 3.6        | Comparación de resultados                  | 26       |

| 3.7        | Bibliografía                               | 27       |

| CAF        | PÍTULO 4. DIVISOR / COMBINADOR DE POTENCIA | 28       |

| 4.1.       | Introducción                               | 28       |

| 4.2.       | 4.2.1. Pérdida por Retorno del Divisor     | 30<br>31 |

| <b>4</b> 3 | 4.2.3. Aislamiento entre los Puertos 2 y 3 |          |

| TIU.       |                                            |          |

|      | CAPÍTULO 5. DISCRIMINADOR DE MICROONDAS EN FUNCIONAMIENTO33 |    |  |  |  |  |  |

|------|-------------------------------------------------------------|----|--|--|--|--|--|

| 5.1. | Introducción                                                | 33 |  |  |  |  |  |

| 5.2. | Detección de bits                                           | 34 |  |  |  |  |  |

|      | Detección de bits                                           | 34 |  |  |  |  |  |

|      | 5.2.2 Detección de 4 estados - 4-bits                       | 37 |  |  |  |  |  |

| 5.3. | Bibliografía                                                | 43 |  |  |  |  |  |

| CAF  | PÍTULO 6. CONCLUSIÓN Y TRABAJO A FUTURO                     | 44 |  |  |  |  |  |

| 6.1. | Conclusión                                                  | 44 |  |  |  |  |  |

| 6.2. | Trabajo a futuro                                            | 44 |  |  |  |  |  |

# **CAPÍTULO 1. INTRODUCCIÓN**

#### 1.1. Motivación

En las últimas décadas ha existido un enorme interés y una gran motivación en identificar la frecuencia instantánea de señales, técnica utilizada en distintas disciplinas de la ciencia, como por ejemplo radar o sismología.

El enorme crecimiento y avance de las telecomunicaciones ha ocasionado congestión y/o saturación en las bandas del espectro comercial disponible y ha sido necesario buscar nuevas bandas de frecuencia, hasta el punto de llegar a una nueva reorganización del espectro comercial en la actualidad.

También se ha podido comprobar la utilidad de la identificación de la frecuencia instantánea en la detección de amenazas conjuntamente con la detección de objetivos. Un ejemplo es la inteligencia de señales, donde identificar señales desconocidas revela estaciones de comunicaciones o radar en una zona de vigilancia.

Una de las características de funcionalidad de los medidores de frecuencia para ser incluidos en sistemas de detección y seguridad, es que deben de contar con un espectro de trabajo amplio, como por ejemplo dentro de la banda Ka 30-40 GHz, así conseguir un tamaño reducido, alta probabilidad de detección, ligereza, bajo coste y bajo consumo de energía. Todos ellos son factores de gran importancia desde el punto de vista comercial.

# 1.2. Objetivos

La finalidad de este proyecto es el diseño de un discriminador de microondas, que es el componente fundamental en un sistema de medición de frecuencia reconfigurable. El discriminador identifica la frecuencia de la señal recibida por medio de una secuencia de bits generada, mientras que los demás componentes cumplen la función de acondicionar la señal en un receptor. Cada discriminador genera un bit de identificación de frecuencia.

Los sistemas de medición de frecuencia instantánea tienen como función la identificación de señales desconocidas determinando la frecuencia y otros parámetros tales como la amplitud, ancho de pulso (Pulse Width, PW), tiempo de arribo (Time of Arrival, TOA), ángulo de arribo (Angle of Arrival, AOA), modulación y frecuencia de intrapulso.

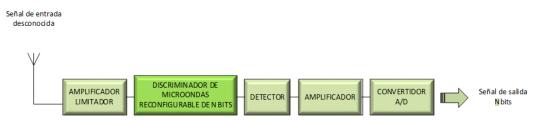

Los componentes de un sistema de medición de frecuencia son: un amplificador limitador, el discriminador de microondas reconfigurable, un detector, un amplificador y un convertidor analógico/digital, tal como se muestra en la **Fig. 1.1**

Fig. 1.1 Sistema de medición de frecuencia reconfigurable de N bits [1].

El discriminador de microondas consta de dos puertos. Siguiendo la secuencia de los componentes que integran el dispositivo, se consigue un diseño de tamaño y peso reducido, se disminuye el consumo energético al usar una arquitectura reconfigurable.

# 1.3. Descripción de componentes

El encargado de realizar la identificación de señales desconocidas es el discriminador de microondas reconfigurable (DMR). A continuación se muestra su funcionamiento y se describen los componentes que lo integran.

El funcionamiento del sistema consiste en detectar y determinar la frecuencia, amplitud, tiempo de llegada (tiempo que tarda en llegar una señal de radio desde un transmisor a un receptor), anchura del pulso, ángulo de llegada, modulación y frecuencia de intrapulso de la señal. El discriminador una vez diseñado y puesto en funcionamiento genera una secuencia de bits para la identificación de la información.

La banda de operación se encuentra en el intervalo de frecuencia de 30 a 40 GHz correspondiente a la banda Ka. Últimamente se han venido desarrollando un gran número de servicios y aplicaciones de telecomunicaciones en este rango de frecuencia, destinados a proporcionar comunicaciones inalámbricas, comunicaciones vía satélite, radares, etc. Una de las aplicaciones de este dispositivo consiste en detectar las bandas disponibles o en uso del espectro electromagnético para comunicaciones.

El detector sirve para realizar una autocorrelación de la señal de entrada debido a su característica de no linealidad.

El amplificador es el responsable de acondicionar la señal de salida del detector a los niveles necesarios para su procesado digital en el siguiente componente.

Por último, el convertidor analógico/digital se encarga de digitalizar la señal analógica resultante del proceso de detección de frecuencia de la señal recibida. En esta etapa se obtiene una palabra digital de identificación de frecuencia.

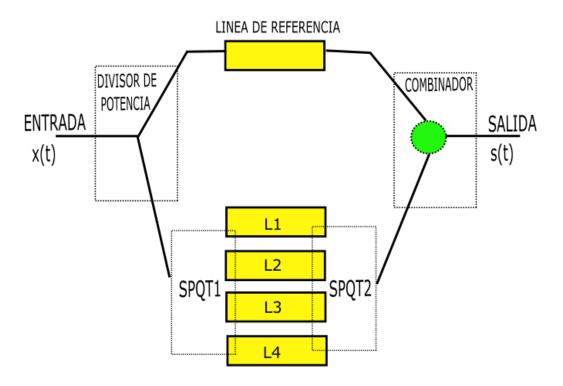

El discriminador de microondas reconfigurable está formado por los siguientes componentes: un desfasador de 180°, un divisor de potencia que actúa también

como un combinador de potencia, una transición CPW, una línea de referencia de longitud  $\lambda/2$  y un sistema de conmutación SPQT, tal como se muestra en la **Fig. 1.2**

**Fig. 1.2** Diagrama de bloques de los componentes que forman un Discriminador de Microondas Reconfigurable [2].

Después de la etapa de detección y conversión de la señal, se obtiene una palabra digital compuesta por los bits usados para la identificación de frecuencia. El receptor estudiado en [1], muestra cómo se forman las palabras digitales.

# 1.4. Organización del proyecto

Este proyecto consta de 6 capítulos. A continuación se describe brevemente el contenido de cada uno de ellos.

En el primer capítulo se realiza una breve introducción a los discriminadores de microondas. Se describe el funcionamiento y la finalidad de estos dispositivos y se exponen los componentes que lo conforman.

En el segundo capítulo se realiza una descripción detallada de la tecnología utilizada para el diseño de las líneas de transmisión, describiendo sus modos de propagación y destacando sus principales características.

El tercer capítulo es la fase de diseño del componente donde se aplican los criterios y pautas para conseguir un resultado final óptimo. También se realizan las comparaciones entre los resultados teóricos y los resultados simulados.

En el cuarto capítulo se lleva a cabo un estudio del divisor/combinador que se utilizará para el funcionamiento del discriminador.

En el quinto capítulo se presenta el diseño final del discriminador de microondas con todos los elementos que lo integran. Se realiza la unión de los divisores de potencia con la línea de referencia y las líneas de retardo; se exponen los resultados obtenidos para los dos y cuatro estados del discriminador y se comprobarán los resultados tanto en circuito abierto como en corto circuito para generar los bits de los resultados.

En el sexto capítulo se presentan las conclusiones finales de este proyecto y el trabajo a desarrollar en un futuro.

# 1.5. Bibliografía

- [1] Pozar, D. M., "Transmission Line and Waveguide", Cap. 3 en Microwave Engineering Fourth Edition, John Wiley & Sons, Inc., pp. 95-164, Hoboken, New Jersey, 2012.

- [2] Espinosa-Espinosa, "Dispositivos de medición de Frecuencia Reconfigurables", Tesis doctoral, Centre tecnològic de Catalunya y la Universitat Politècnica de Catalunya, Barcelona, España 2015.

- [3] Espinosa-Espinosa, M., Oliveira, B. G., Llamas-Garro, I., Melo, M. T. y Jung-Mu Kim., "Four-bit reconfigurable discriminator for frequency identification receivers: A Building block approch", Radio Sci., 51, 826-835 (2016).

# **CAPÍTULO 2. LÍNEAS DE TRANSMISIÓN**

# 2.1. Tecnología coplanar

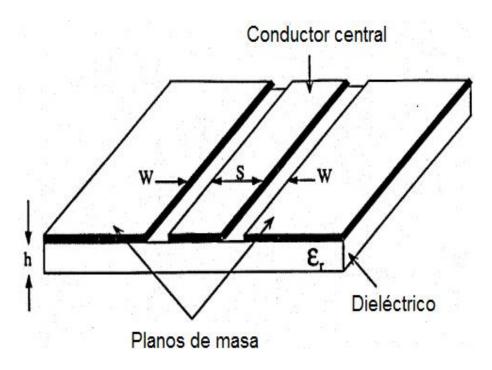

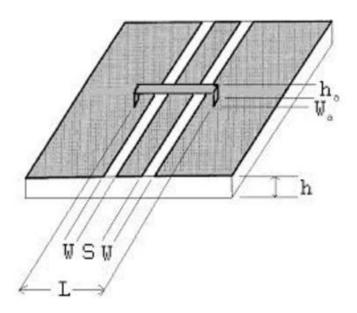

Las líneas de transmisión realizadas con tecnología coplanar consisten en una guía de ondas formada por dos ranuras que dividen la metalización del sustrato sobre el que se fabrica, tal como se indica en [1].

El comportamiento electromagnético de la línea coplanar está caracterizado por la definición de su sustrato, el grosor del dieléctrico h, la tangente de pérdidas  $tan(\delta)$ , la constante dieléctrica, el grosor de las metalizaciones, el ancho de las ranuras (W) y el ancho del conductor central (S). Un estudio de esta línea de transmisión para el diseño de circuitos se encuentra en [2]

Se definen tres zonas en el mismo plano de metalización: el conductor central y dos planos de masa en ambos lados, como podemos observar en la **Fig. 2.1**

Fig. 2.1 Configuración línea coplanar. Fuente [3].

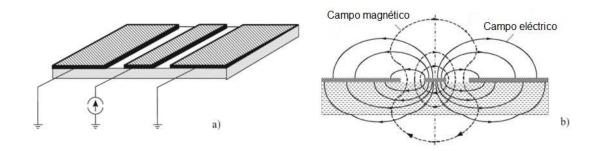

Una de las principales características de este tipo de tecnología es la propagación multimodal que permite propagar dos modos fundamentales: modo coplanar par y modo coplanar impar [3].

#### 2.2. Modo Coplanar Par

El modo coplanar par es un modo quasi-TEM. Esto implica que el diseño del circuito es poco dispersivo y por lo tanto permite trabajar con aplicaciones de banda ancha. Con este modo de propagación se logra que la impedancia característica de la línea y su velocidad de propagación muestren poca dependencia con la frecuencia [4].

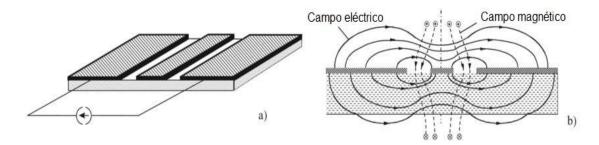

Las líneas del campo eléctrico comienzan o acaban en el conductor central y terminan o comienzan en los dos planos de tierra de los lados. El hecho de que el campo eléctrico tenga sentido opuesto respecto al conductor central, hace que las pérdidas por radiación del modo par sean bajas y el campo quede muy confinado en el dieléctrico. Las líneas de campo magnético rodean el conductor central. La excitación de corriente (Fig. 2.2 (a)) y la distribución de campo (Fig. 2.2 (b))

Fig. 2.2 Modo par en una línea de transmisión CPW.

(a) Excitación de corriente, (b) distribución de campo. Fuente [4].

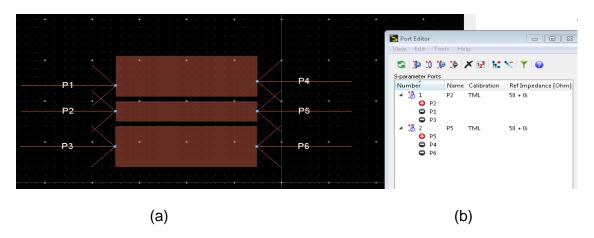

En la siguiente imagen (**Fig. 2.3**) se muestra un ejemplo de una línea en layout usando Advanced Design System (ADS versión 2016). Se trata de una línea de transmisión coplanar en modo par con la configuración de los puertos. La configuración queda establecida con los puertos #2, #5 conectados al material conductor y los demás puertos (#1, #3, #4, #6) conectados al plano de masas.

**Fig. 2.3** Modo par en una línea de transmisión CPW en ADS. (a) Dibujo sobre layout en ADS, (b) Configuración de puertos modo par.

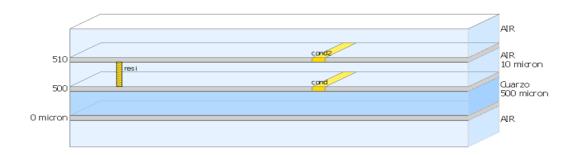

A la hora de realizar un diseño de circuito, el modo par es el más utilizado. En la siguiente figura (**Fig. 2.4**) se muestran las capas utilizadas para simular este ejemplo de línea de transmisión coplanar; el sustrato es cuarzo con un espesor de 500  $\mu$ m, una permitividad de 3,8 y tangente de pérdidas tan $\delta$ =0.00006; el conductor es plata "AG" de anchura 1  $\mu$ m con conductividad 6,3e7 siemens/m.

**Fig. 2.4** Capas utilizadas en la simulación de la CPW con sustrato de cuarzo y plata como conductor.

#### 2.3. Modo Coplanar impar

El modo coplanar impar es un modo no-TEM y es poco utilizado debido a su comportamiento dispersivo. Los componentes del campo eléctrico y magnético viajan en la dirección de propagación, con lo cual la impedancia característica y su velocidad de propagación no son constantes con la frecuencia.

Las líneas del campo eléctrico empiezan en un plano de tierra y terminan en el otro plano de tierra, lo que significa que los potenciales de los dos planos de masa tienen signos opuestos [4]. Además, no todas las líneas del campo eléctrico tocan el conductor central. Si el ancho del plano de tierra es finito, las líneas del campo magnético se encierran en la sección transversal que incluye los planos de tierra.

Se muestra la excitación de corriente en la Fig. 2.5 (a) y la distribución de campo en la Fig. 2.5 (b).

Fig. 2.5 Modo impar en una línea de transmisión CPW.

(a) Excitación de corriente, (b) Distribución de campo. Fuente [4].

La configuración de campos para el modo impar es tal que el conductor central no transporta corriente y en cambio en los planos de tierra circulan corrientes longitudinales en sentido opuesto. De esta forma, el conductor central es transparente a la propagación de la señal en el modo impar.

El modo coplanar impar es un modo que tradicionalmente se ha considerado como no deseado por su comportamiento dispersivo. Este modo de propagación se puede eliminar mediante puentes de conexión equipotenciales o *airbridge*.

Se puede utilizar uno de estos puentes para conectar dos planos de masa de la guía de ondas CPW, con la finalidad de que el potencial sea el mismo en ambos planos de masa.

Esta unión no produce ningún efecto en el modo par de la línea. En la **Fig. 2.6** se muestra un ejemplo de conexión con *airbridges* [5].

El airbridge se modela como dos postes rectangulares de altura ho unidos por un conductor con un determinado grosor Wo.

Fig. 2.6 Conexión equipotencial o airbridge en una línea CPW. Fuente [5].

# 2.4. Bibliografía

- [1] Abad, G. F., "Estudio de Líneas uniplanares", Cap. 2 en Diseño, fabricación y caracterización de una red configurable de alimentación de antenas tipo slotline, proyecto fin de carrera, pp. 13-26, Universitat Politècnica de Catalunya, Barcelona, 2001.

- [2] Xirgu, A. X., "Tipos de Líneas de transmisión", Cap. 6 Líneas de transmisión, Fisica\_II, pp. 89-100, Universitat Oberta de Catalunya, Barcelona, 2006.

- [3] Nihad, I.D. y Linda P.B, Theoretical Characterization of Coplanar Waveguide Transmission Lines and Discontinuities, Radiation Lab., University of Michigan, Ann Arbor, MI (1992).

- [4] Wollf, I., Coplanar Microwave Integrated Circuits, John Wiley & Sons, Inc., Hoboken, New Jersey, (2006).

- [5] Chung-Yi Lee, Yaozhong Liu, Tatsuoltoh, "The Effect of the Coupled slotline Mode and Air-Bridges on CPW and NLC Waveguide Discontinuities", IEEE Trans., Vol. 43, pp. 2759-2765, (1995).

# **CAPÍTULO 3. DISCRIMINADOR DE MICROONDAS**

#### 3.1. Introducción

El discriminador de frecuencia es el componente esencial en el desarrollo de receptores identificadores de señales de microondas, como por ejemplo los medidores de frecuencia instantánea (MFI). Actualmente estos dispositivos son utilizados para la implementación de medidores de frecuencia reconfigurable y su funcionamiento consiste en un interferómetro basado en líneas de retardo.

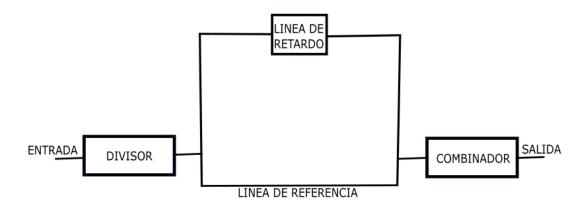

Estos dispositivos se encargan de identificar la frecuencia de las señales desconocidas. En la **Fig. 3.1** se muestra el diagrama de bloques de un discriminador de microondas.

**Fig. 3.1** Diagrama de bloques de un discriminador de frecuencias.

# 3.2 Tipos de discriminadores

Los discriminadores de microondas se subdividen en dos tipos: discriminadores fijos y discriminadores reconfigurables. Estos últimos son los que se describirán con más detalle en los próximos capítulos.

# 3.2.1 Discriminadores de microondas fijos

Los discriminadores fijos son sistemas de dos puertos cuyos componentes están conectados en cascada. Los componentes básicos que los forman son: un divisor de potencia, una línea de referencia, una línea de retardo y por último un combinador de potencia (ver **Fig. 3.1**). Este tipo de discriminadores solo pueden generar 1 - bit de identificación de frecuencia.

#### 3.2.2 Discriminadores de microondas reconfigurables

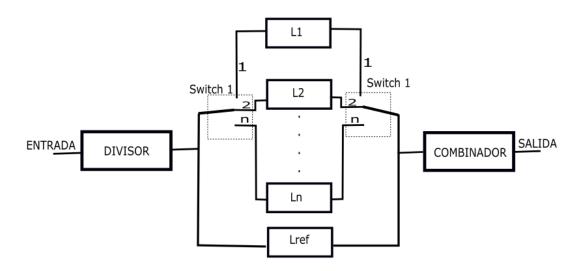

Los discriminadores de microondas reconfigurables (DMR) basan su funcionamiento en un discriminador de microondas fijo, con la diferencia de que este sistema cuenta con interruptores controlados por voltaje que seleccionan el estado de operación.

Los DMR son sistemas escalables y reconfigurables. En la **Fig. 3.2** se muestra el diagrama de bloques de un discriminador de microondas reconfigurable de n-bits.

Fig. 3.2 Diagrama de bloques de un DMR de n-bits, Fuente [1].

En la siguiente **Tabla 3.1**, se muestra una comparación de un discriminador de microondas fijo [2] y un discriminador de microondas reconfigurable [3], en términos de potencia consumida, número de discriminadores, dimensiones y ancho de banda.

En la tabla se puede apreciar en términos de dimensiones que el discriminador fijo presenta un área mayor, de casi un 50% más, que el discriminador reconfigurable de 4-bits.

Los discriminadores reconfigurables tienen un mayor consumo de potencia, debido a la conmutación realizada con diodos. Esta desventaja en el discriminador se ve compensada al requerir menos componentes electrónicos para implementar un sistema medidor de frecuencia, lo cual se traduce en un ahorro de energía con respecto a un sistema medidor de frecuencia implementado con discriminadores fijos.

La única desventaja que presenta un discriminador reconfigurable está en el tiempo de respuesta, debido a que este depende del tiempo de respuesta de los diodos del conmutador. Por lo tanto, el tiempo total de respuesta del discriminador reconfigurable se verá afectado por el número de diodos utilizados.

**Tabla 3.1** Comparación entre discriminador fijo y discriminador reconfigurable.

| Discriminador                     | Filtro Rechaza Banda | Reconfigurable      |

|-----------------------------------|----------------------|---------------------|

| Tipo de discriminador             | Fijo                 | Reconfigurable      |

| Ancho de Banda (GHz)              | 1.5-4.66             | 1-4                 |

| Resolución (Mhz)                  | 62.5                 | 187.5               |

| Consumo de potencia (mW)          | 0                    | 93.4                |

| Tecnología uniplanar              | Microstrip           | Microstrip          |

| Nº de discriminadores<br>/Nº-bits | 4/4                  | 1/4                 |

| Tiempo de respuesta               | Instantáneo          | 10ns por cada diodo |

| Implementación                    | Filtro rechaza Banda | Líneas de retardo   |

| Dimensiones (mm)                  | 199X113              | 102x96              |

| Configuración                     | Paralelo             | Cascada             |

| Referencia                        | [2]                  | [3]                 |

#### 3.3 Criterios de diseño

Como punto de partida al comenzar el diseño de las líneas de retardo, se deben cumplir los valores mencionados en la **Tabla 3.2**, ya que son los valores ideales de cada componente para asegurar un buen diseño y respetar los requerimientos iniciales.

Tabla 3.2 Valores iniciales de diseño.

| Línea de retardo | Longitud | Desfase |

|------------------|----------|---------|

| Lref             | λg/2     | 180°    |

| L1               | λg       | 360°    |

| L2               | 3λg/2    | 540°    |

| L3               | 2λg      | 720°    |

| L4               | 5λg/2    | 900°    |

Este discriminador reconfigurable puede generar 4 - bits de identificación de frecuencia en tiempos diferentes.

En el tiempo t1, se selecciona la línea de retardo L1 y en combinación con la línea Lref, se obtiene el estado 1. En el tiempo t2, se seleccionan las líneas L2 y Lref para obtener el estado 2. Y así sucesivamente se generan los estados 3 y 4 de operación del discriminador.

La línea de referencia es la misma línea para los cuatro estados del dispositivo, donde  $\lambda g$  es la longitud de onda guiada a una frecuencia central de 35 GHz, que está dentro de la banda de trabajo 30 – 40 GHz (Banda Ka).

#### 3.4 Resultados teóricos

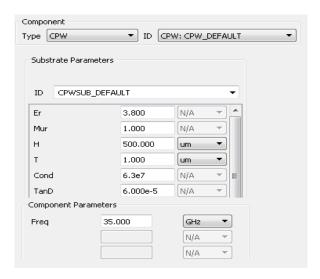

Teniendo en cuenta previamente los criterios iniciales de diseño, el paso siguiente es el cálculo mediante la herramienta Line Calc de las dimensiones físicas de cada línea. El Line Calc es una herramienta de ADS muy utilizada para obtener unas medidas iniciales de diseño teniendo en cuenta el sustrato y materiales empleados, la frecuencia y otros valores que serán de vital importancia en el comportamiento de la línea. Estas características se pueden observar en la **Fig. 3.3.** En la **Tabla 3.3**, se describen brevemente los valores mencionados.

Fig. 3.3 Sustrato y frecuencia central cargados en Line Calc.

| T-11- ^ ^  | D . ( . II . |          |             |                 |

|------------|--------------|----------|-------------|-----------------|

| צ צ בוחבו  | 1 1010110    | an valor | ne cardado  | e an Lina Caic  |

| i avia J.J | Detaile      | ue valui | to Caluado. | s en Line Calc. |

| Type: CPW      | Tipo tecnología, coplanar     |

|----------------|-------------------------------|

| Er: 3.8        | Permitividad                  |

| Mur: 1         | Valor predefinido             |

| H: 500 µm      | Anchura del sustrato          |

| T: 1 µm        | Grosor del material conductor |

| Cond: 6.3 e7   | Conductividad del material    |

| TanD: 6.000e-5 | Tangente de pérdidas          |

| Freq: 35 GHz   | Frecuencia central de trabajo |

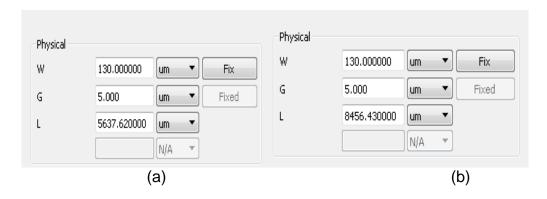

A continuación se procede a calcular las longitudes de la Lref, L1, L2, L3, L4 mediante la herramienta Line Calc. Los resultados obtenidos serán las dimensiones iniciales físicas de cada línea de retardo. Todas estas líneas tienen en común las mismas características descritasen la **Fig. 3.3** y la **Tabla 3.3**. Otros valores a tener en cuenta serán los mismos valores del diseño de las líneas de retardo. Son el valor W = 130  $\mu$ m (anchura del conductor) y G = 5  $\mu$ m (Gap, espacio de separación entre conductor y masa).

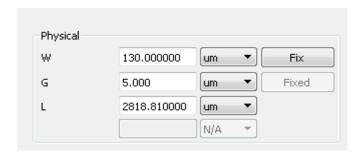

En la **Fig. 3.4** se muestra el valor de Lref con una longitud inicial de 2818,81  $\mu$ m, W=130  $\mu$ m, G=5  $\mu$ m.

Fig. 3.4 Cálculo de Lref en Line Calc.

En la **Fig. 3.5 (a),** se muestra el valor de L1 con una longitud de 5637,62  $\mu$ m. En la **Fig. 3.5 (b),** se muestra el valor de L2 con una longitud de 8456,43  $\mu$ m y ambas líneas con los mismos valores de W=130  $\mu$ m, G=5  $\mu$ m

Fig. 3.5 Cálculo de L1 (a) y L2 (b) en Line Calc.

En la **Fig. 3.6 (a)**, se obtiene el valor de L3 con una longitud de 11328,40 μm. En la **Fig. 3.6 (b)**, obtenemos el valor de L4 con una longitud de 14094μm y ambas líneas con los mismos valores de W=130μm, G=5 μm

Fig. 3.6 Cálculo de L3 (a) y L4 (b) en Line Calc.

#### 3.5 Resultado de simulaciones

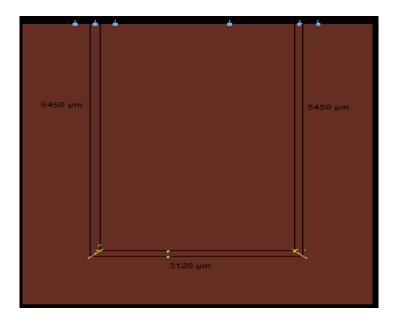

En este apartado se exponen los resultados obtenidos de cada línea de retardo. En la **Fig. 3.7** se muestra el diseño finalizado de Lref que tiene una longitud de 2770 µm y cuya función será la de conmutar conjuntamente con las otras líneas de retardo que forman parte del diseño.

Fig. 3.7 Diseño de Lref en layout.

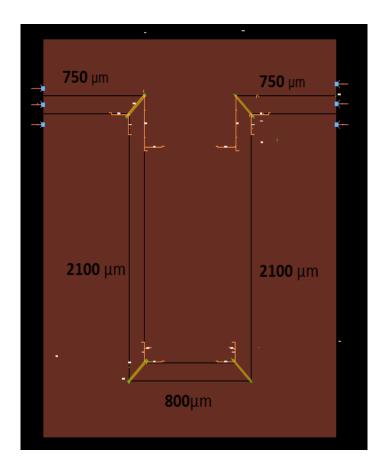

En la **Fig.3.8** tenemos la L1 que será la siguiente línea de retardo y al conmutar con Lref obtendremos el primer estado. La línea tiene una longitud total de 6500 µm.

Fig. 3.8 Diseño de L1 en layout.

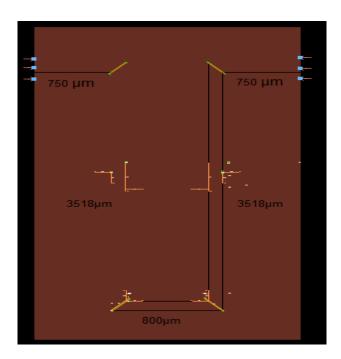

En la **Fig. 3.9** se muestra la L2, otra línea que forma parte del diseño. Cuando conmuta con Lref obtendremos el segundo estado. La línea tiene una longitud total de 9336 µm.

Fig. 3.9 Diseño de L2 en layout.

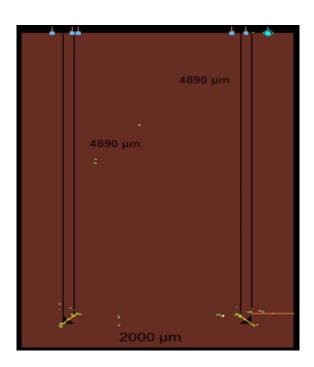

En la **Fig. 3.10** se muestra la L3 que al conmutar con Lref obtendremos el tercer estado. La línea tiene una longitud total de  $11780 \ \mu m$ .

Fig. 3.10 Diseño de L3 en layout.

En la **Fig. 3.11** se muestra la L4. Esta línea en el momento de conmutar con Lref obtendremos el cuarto estado. La línea tiene una longitud total de 14020  $\mu m$ .

Fig. 3.11 Diseño de L4 en layout.

#### 3.5.1 Pérdidas por retorno

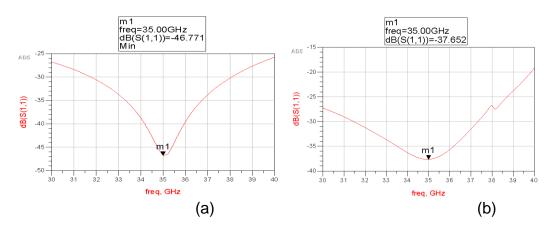

En la **Fig. 3.12 (a)** se observa la pérdida por retorno (S11) de Lref y puede apreciarse una buena adaptación de la línea a 35 GHz dentro del margen de trabajo. En la **Fig. 3.12 (b)** se observa la pérdida de retorno (S11) de L1. Ambas líneas cumplen satisfactoriamente en toda la banda de trabajo de 30 – 40 GHz con reflexiones por debajo de -20 dB.

Fig. 3.12 Pérdida por retorno. (a) S11 de Lref, (b) S11 de L1.

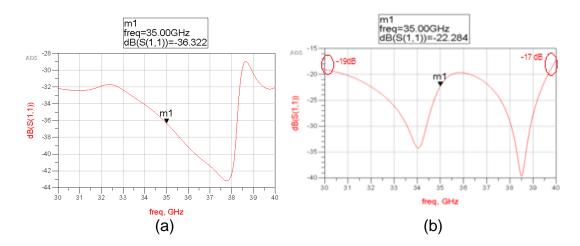

En la **Fig. 3.13 (a)** se muestra la pérdida por retorno (S11) de L2. Aún se mantienen los valores deseados en la franja de trabajo, y a pesar de no estar centrada totalmente a 35 GHz es un valor óptimo para el diseño. En la **Fig. 3.13 (b)** se muestra la pérdida de retorno (S11) de L3 y se observa que presenta una reducción de la caída en dB a la frecuencia central (35 GHz) comparándola con las representaciones anteriores. La línea L2 cumple

satisfactoriamente en toda la banda de trabajo de 30 - 40 GHz con reflexiones por debajo de los -20dB, aunque considerando L3 se ve afectado ligeramente en los extremos, donde obtenemos valores de -19 dB y -17 dB.

Fig. 3.13 Pérdida por retorno. (a) S11 de L2, (b) S11 de L3.

En la **Fig. 3.14** se representa la pérdida de retorno (S11) de L4. Esta última línea es la más crítica para el margen de trabajo de 30 – 40 GHz, a pesar de tener reflexiones más elevadas comparándola con las otras líneas se puede considerar como buena para continuar con el diseño y su correspondiente estudio.

Fig. 3.14 Pérdida por retorno (S11) de L4.

#### 3.5.2 Pérdidas por Inserción

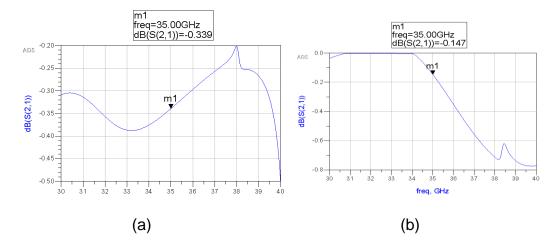

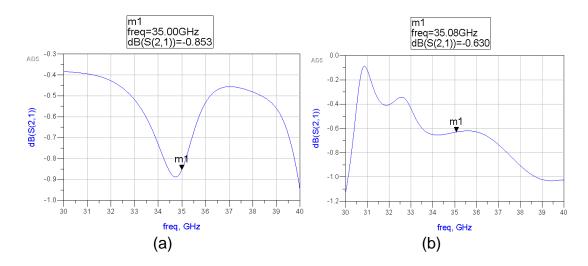

En la **Fig. 3.15 (a)** se obtienen las pérdidas por transmisión (S21) en el puerto de salida de L1 con unos valores de 0.2 a 0.5 dB. En la **Fig. 3.15 (b)** se muestran las pérdidas por transmisión (S21) en el puerto de salida de L2 con unos valores de 0 a 0.8 dB. Ambas líneas cumplen satisfactoriamente las pérdidas de transmisión en todo el margen de trabajo de 30 a 40 GHz al estar dentro del intervalo de 0 a 1dB en la banda de transmisión.

Fig. 3.15 Pérdida por inserción. (a) S21 de L1, (b) S21 de L2.

La **Fig. 3.16(a)** muestra las pérdidas por transmisión (S21) en el puerto de salida de L3, con unos valores de 0.4 a 0.95 dB. En la **Fig. 3.16(b)** tenemos las pérdidas por transmisión (S21) en el puerto de salida de L4 con unos valores de 0.1 a 1 dB en todo el margen de la banda de trabajo.

Fig. 3.16 Pérdida por inserción. (a) S21 de L3, (b) S21 de L4.

# 3.6 Comparación de resultados

Para el diseño de este discriminador partimos de unos valores teóricos obtenidos a partir del sustrato, del material conductor, de la frecuencia de trabajo y de la teoría que define su diseño. Pero a la hora de implementarlo y realizar las distintas simulaciones se ven alterados estos valores, como se puede observar en la **tabla 3.4**

Tabla 3.4 Comparativa de valores teóricos con los valores simulados en ADS.

| Línea | Calculado en Line Cal (µm) | Simulado en ADS (µm) |

|-------|----------------------------|----------------------|

| Lref  | 2818,81                    | 2770                 |

| L1    | 5637,62                    | 6500                 |

| L2    | 8456,43                    | 9336                 |

| L3    | 11328,40                   | 11780                |

| L4    | 14094                      | 14020                |

Estos valores son las primeras desviaciones que se originan al implementar el diseño, se observan estas diferencias en las longitudes al momento de realizar las simulaciones, debido al posicionamiento del material conductor, es decir los valores iniciales tienen en cuenta el conductor en una única línea horizontal pero al momento de montarlo en una placa puede originar líneas rectas seguidas de líneas curvas o esquinas de 90 grados, conjuntamente con sus respectivas masas, también influyen el tipo de metal conductor, sustrato y elementos varios que se añadan al diseño.

A medida que vayamos juntando las líneas en un único diseño, estos valores se verán alterados nuevamente. Los únicos valores que siempre se mantendrán fijos son el GAP (ranuras de separación entre masa y conductor) con un valor de 5 µm y la anchura del conductor de 130 µm. Se mantienen fijos porque vienen predefinidos por características del divisor y combinador utilizados para obtener una adaptación de impedancias a 50 ohms.

# 3.7 Bibliografía

- [1] Espinosa-Espinosa, M., Oliveira, B. G., Llamas-Garro, I. y Melo, M. T., "2-Bit, 1-4 GHz Reconfigurable Frequency Measurement Device", *IEEE MWCL.*, Vol.24, NO.8, 569-571, August 2014.

- [2] De Oliveira B. G. M.; de Melo M.T; Llamas-Garro I; Espinosa M; de Oliveira M.R.T.; de Oliveira E.M.F; Integrated Instantaneous Frequency Measurement Subsystem Based on Multi-Band-Stop Filters, in Procedigns of Asia Pacific microwave Conference (APCMC 2014), 4-7 novembre 2014, Sendai(Japan).

- [3] Espinosa-Espinosa, M., Oliveira, B. G. M.; Llamas-Garro, I. y Melo, M. T.; Kim Jung-Mu;4-bit, 1 to 4 Ghz Reconfigurable Discriminator for Frequency Measurement, In Proceedings of 44th european Microwave Conference (EuMW 2014), 5-10 October 2014, Rome (Italy).

# CAPÍTULO 4. DIVISOR / COMBINADOR DE POTENCIA

#### 4.1. Introducción

El siguiente componente que forma el discriminador de microondas reconfigurable es un divisor de potencia. Este mismo elemento se utiliza como combinador de potencia a la salida.

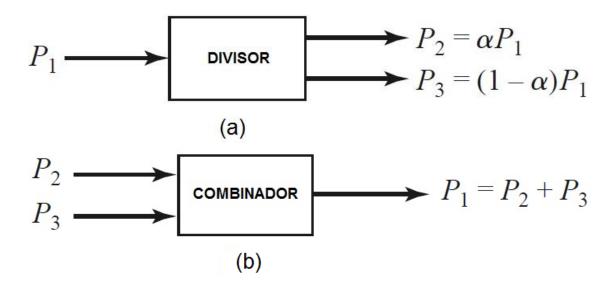

Tanto el divisor como el combinador de potencia son dispositivos pasivos utilizados en sistemas de radiofrecuencia o microondas. La señal de entrada del divisor de potencia es dividida en dos o más señales de salida de menor potencia (ver **Fig. 4.1(a)**).

El combinador realiza la operación inversa: dadas dos o más señales de entrada, las combina o suma en su puerto de salida (ver **Fig. 4.1(b)**).

**Fig. 4.1** Divisor/Combinador de potencia.

(a) Divisor de Potencia, (b) Combinador de Potencia. Fuente [1].

El divisor de potencia utilizado en este proyecto es capaz de distribuir la potencia que recibe por su puerto de entrada entre sus puertos de salida, con una relación de división de potencia igual a 3 dB, lo que indica una distribución equitativa de potencia. Pero también puede diseñarse para conseguir una división de potencia arbitraria [1].

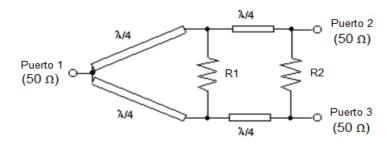

El divisor de potencia que se considera en este proyecto es un divisor Wilkinson de dos etapas. Se utiliza este divisor para que opere en un mayor ancho de banda (como es la banda Ka) que es donde funciona el discriminador de microondas diseñado. Sus ventajas son bajas pérdidas de inserción, buen aislamiento entre sus puertos de salida y que todos sus puertos están

adaptados a  $50\Omega$  [2]. En la **Fig. 4.2** se muestra un diagrama típico de un divisor Wilkinson de 2 etapas.

Fig. 4.2 Divisor Wilkinson de 2 etapas.

#### 4.2. Diseño del Divisor de Potencia

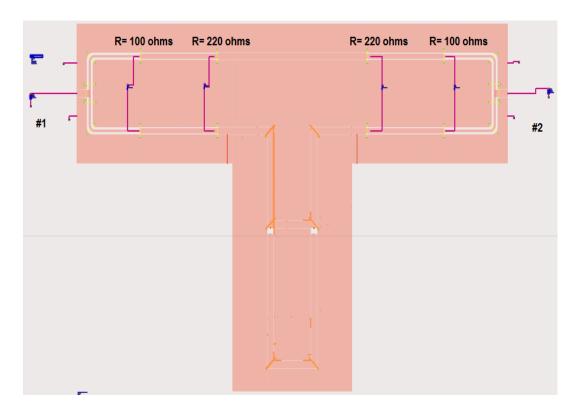

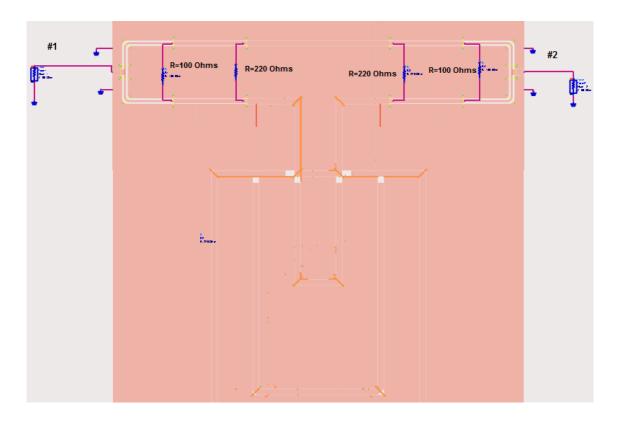

El discriminador de microondas emplea un divisor en el puerto de entrada y un combinador en el puerto de salida. El diseño del divisor/combinador se lleva a cabo mediante el uso de líneas coplanares (*CPW*) y como se comentó anteriormente se trata de un divisor Wilkinson de dos etapas, donde la primera etapa tenemos una resistencia de 100 ohms y en la segunda etapa del divisor tiene una resistencia de 220 ohms, para compensar esta variación de los valores de impedancias y obtener una única impedancia a lo largo del divisor, se varían las anchuras de las líneas donde están conectadas las resistencias y así no afectar al diseño.

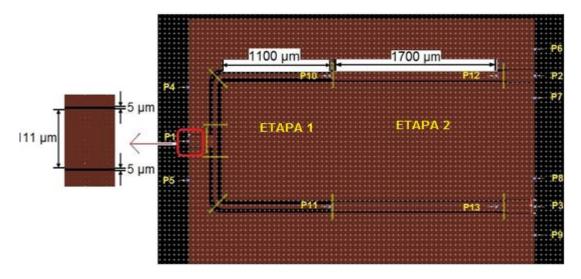

Se define el ancho de 5  $\mu$ m de la ranura y el ancho del conductor central de 111  $\mu$ m en los puertos; se fija una longitud de 1100  $\mu$ m para las primeras dos líneas de la primera etapa y 1700  $\mu$ m de longitud para las otras dos líneas de la segunda etapa (ver **Fig. 4.3**). El tamaño del diseño es de 3631.7  $\mu$ m x 2492.6  $\mu$ m.

Fig. 4.3 Divisor Wilkinson de 2 etapas.

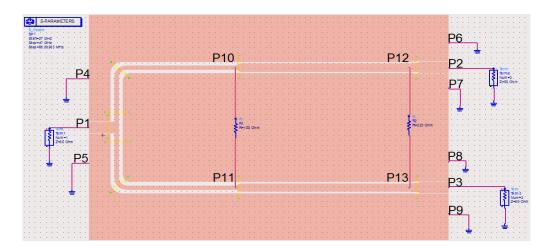

A continuación se guarda el diseño como un componente en la biblioteca de ADS y se importa en un esquemático. Utilizando terminales, identificamos el puerto de entrada y los puertos de salida. El puerto de entrada es el pin P1 y los puertos de salida son P2 y P3. El resto de pines (P4....P9) corresponden a masa. Todos los puertos presentan una impedancia característica de 50 $\Omega$ . Los pines P10, P11, P12 y P13 sirven para ubicar los resistores SMD, uno de 100  $\Omega$  (en la primera etapa) y otro 220  $\Omega$  (en la segunda etapa), para conseguir un aislamiento máximo. La **Fig. 4.4** ilustra los terminales y resistores para simular el divisor.

Fig. 4.4 Divisor Wilkinson con terminales y resistores.

#### 4.2.1. Pérdida por Retorno del Divisor

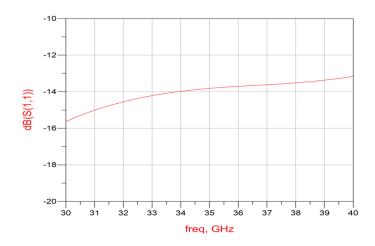

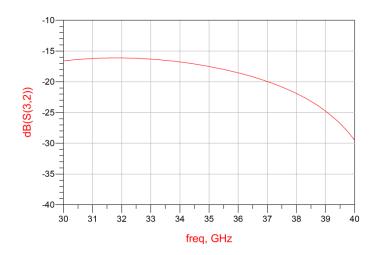

La **Fig. 4.5** muestra la pérdida por reflexión ( $S_{11}$ ) simulada en el puerto 1 del divisor. La señal muestra un buen nivel de pérdida de reflexión que está por debajo de 13 dB en la banda de operación de 30 a 40 GHz.

Fig. 4.5 Pérdida por reflexión (S<sub>11</sub>) simulada del divisor.

#### 4.2.2. Pérdidas por Transmisión

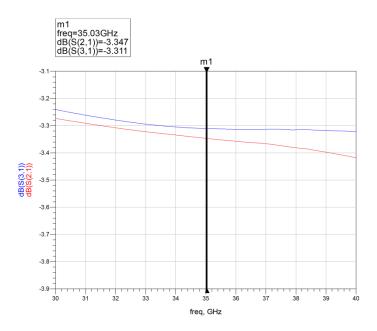

La **Fig. 4.6** muestra las pérdidas por transmisión  $(S_{21})$  y  $(S_{31})$  vista en los dos puertos de salida. La pérdida por transmisión  $S_{21}$  es de 3,35 dB y en el otro puerto  $S_{31}$  es de 3,31 dB a la frecuencia central de 35 GHz.

Fig. 4.6 Pérdidas por transmisión (S<sub>21</sub>) y (S<sub>31</sub>) simuladas del divisor.

#### 4.2.3. Aislamiento entre los Puertos 2 y 3

Por último, se muestra el nivel de aislamiento (S<sub>32</sub>) entre los puertos de salida del divisor. Se ha conseguido que en toda la banda de trabajo de 30 a 40 GHz, el aislamiento se encuentre por debajo de 15 dB, tal como se ve en la **Fig. 4.7**.

Fig. 4.7 Aislamiento entre los puertos de salida del divisor (S<sub>32</sub>).

# 4.3. Bibliografía

- [1] Pozar, D. M., "Power Dividers and Directional Couplers", Cap. 7 en *Microwave Engineering Fourth Edition*, John Wiley & Sons, Inc., pp. 317-379, Hoboken, New Jersey, 2012.

- [2] Wilkinson E., "An N-Way Hybrid Power Divider", *IRE Transactions on Microwave Theory and Techniques*, Vol. MTT-8, pp. 116-118, January 1960.

# CAPÍTULO 5. DISCRIMINADOR DE MICROONDAS EN FUNCIONAMIENTO

#### 5.1. Introducción

Una vez diseñadas todas las líneas de retardo y añadido a la entrada el divisor de potencia y a la salida el combinador, se procede a realizar las simulaciones en conjunto de todo el bloque. Para ello son necesarios dos interruptores SPQT formados por diodos PIN que serán los que permitirán la conmutación entre las líneas.

Una de las características que presenta el diseño propuesto de discriminador de Microondas Reconfigurable es la escalabilidad. Para demostrar dicha característica se presenta el diseño de un DMR de 4-bits. El discriminador es un dispositivo de dos puertos que puede producir una salida de 4 bits para la identificación de una señal desconocida, después de que el sistema de conmutación seleccione todas las líneas L1, L2, L3, L4 en los tiempos t1, t2, t3 y t4, respectivamente.

Las redes de polarización para cada diodo están formadas por dos inductores de choke [1], cuya función consiste en aislar los puertos de corriente directa (CD) de la señal de Radio Frecuencia (RF), y un resistor SMD, de 100 ohms para generar una corriente de polarización. El interruptor también cuenta con dos capacitores de bloqueo (DC Block) de banda ancha C1 y C2 [2] para aislar las redes de polarización de corriente directa y lograr la combinación adecuada para el funcionamiento del sistema.

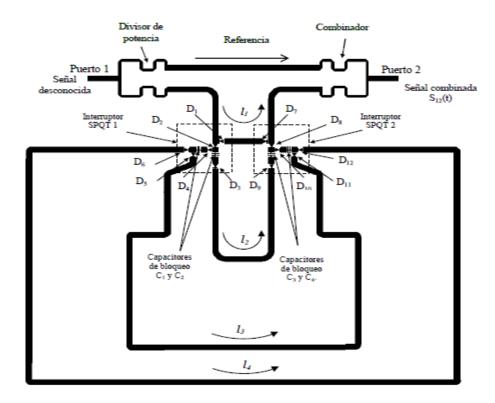

Los cuatro estados de operación del discriminador reconfigurable son obtenidos mediante la polarización de cada diodo de un interruptor SPQT. El interruptor SPQT 1 está formado por los diodos D1-D6 y dos condensadores de bloqueo C1 y C2, el interruptor SPQT 2 está formado por los diodos D7-D12 y los capacitores de bloqueo C3 y C4. Se puede ver la topología en la Fig. 5.1. Los capacitores de bloqueo permiten realizar las combinaciones adecuadas para generar los estados de operación del discriminador.

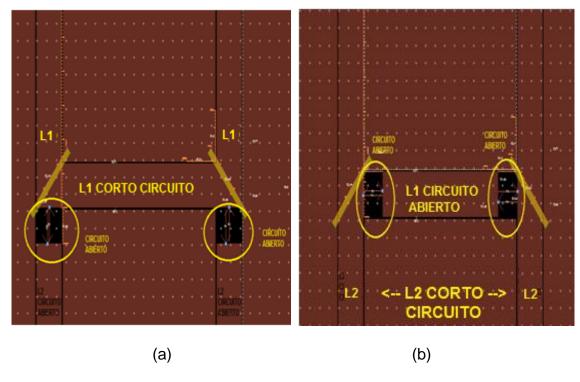

En este proyecto la simulación de los interruptores y diodos se va a realizar de forma ideal, es decir, la conmutación se hará mediante circuitos abiertos y corto circuitos. Para conseguir este resultado se realizará simulando la línea de interés en corto circuito y las demás en circuito abierto y así sucesivamente con cada línea para obtener todos los estados del diseño.

El sistema de conmutación del discriminador de microondas reconfigurable, que está formado por los dos interruptores SPQT, consume un promedio de potencia de 93.4 mW.

**Fig. 5.1** Topología del discriminador de microondas reconfigurable de 4 bits usando líneas microstrip. Fuente [1].

#### 5.2. Detección de bits.

La detección de bits se va realizar en dos partes. La primera incluyendo únicamente las líneas L1, L2, la siguiente añadiendo las líneas L3, L4. Se pueden realizar las comprobaciones a medida que añadimos líneas ya que el resultado final puede verse alterado por posibles acoplos entre líneas.

#### 5.2.1 Detección de 2 estados - 2-bits

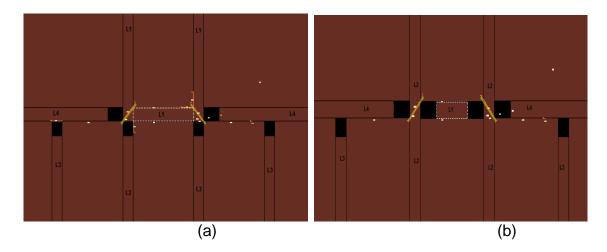

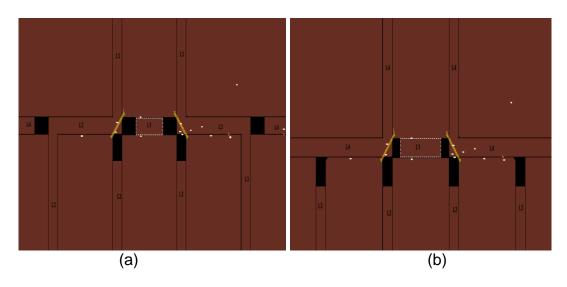

Una vez realizados los cálculos y las simulaciones en los capítulos anteriores, se procede a unir en un único diseño Lref, L1, L2 (ver **Fig. 5.2**). Para la obtención de los dos estados estudiados se realiza la conmutación entre Lref-L1 (ver **Fig. 5.3 (a)**) y Lref-L2 (ver **Fig. 5.3 (b)**). Una vez realizadas ambas simulaciones se procede a generar el componente en esquemático (ver **Fig. 5.4**). Este componente estará disponible en la librería del esquemático y se podrá seleccionar para realizar la simulación y obtener los bits deseados.

Fig. 5.2 Diseño incluyendo Lref, L1, L2.

Fig. 5.3 Conmutación entre líneas. (a) Lref-L1, (b) Lref-L2.

Fig. 5.4 Modelo de componente en el esquemático de ADS.

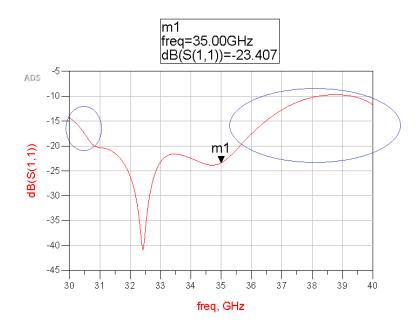

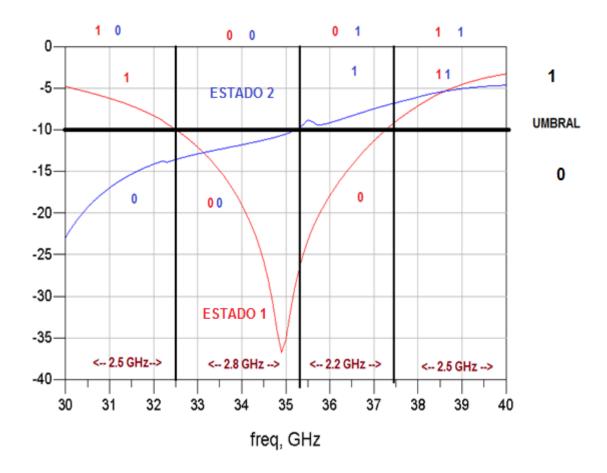

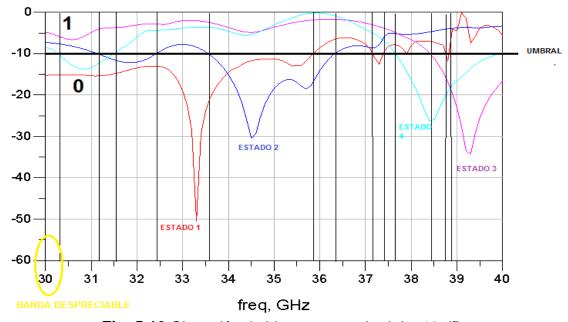

Una vez representadas las pérdidas de inserción (S21) de ambas líneas de retardo, se procede a evaluar los dos estados representado por la línea de color rojo como estado uno y la línea de color azul como estado dos. Para ello es necesario definir un umbral para la extracción de bits, que serán los encargados de definir la identificación de la señal desconocida en la entrada del circuito y que a su vez será asignada a cada una de las sub-bandas, tal como se observa en la **Fig. 5.5.**

Para la etapa de detección y conversión, se fijará un umbral de -10 dB para los bits de identificación. Se ha de configurar la etapa de conversión analógico /digital, donde el nivel lógico 1 se obtiene cuando se cumple la condición de |S21| ≥ -10 dB y el de 0 lógico se obtiene cuando |S21| < -10 dB.

Fig. 5.5 Asignación de bits del discriminador.

En la **tabla 5.1** se muestran las sub-bandas definidas para los bits 1 y 2 con las respectivas resoluciones. La resolución depende del retardo mayor presentado por el sistema de medición de frecuencia: a mayor número de bits obtenemos mayor resolución para un ancho de banda fijo.

Tabla 5.1 Subbandas del discriminador de microondas reconfigurable.

| Subbanda         | 1       | 2           | 3           | 4         |

|------------------|---------|-------------|-------------|-----------|

| Bit 1            | 1       | 0           | 0           | 1         |

| Bit 2            | 0       | 0           | 1           | 1         |

| Resolución (GHz) | 2.5 GHz | 2.8 GHz     | 2.2 GHz     | 2.5 GHz   |

| Subbandas (GHz)  | 30-32,5 | 32,5 - 35,3 | 35,3 - 37,5 | 37,5 - 40 |

#### 5.2.2 Detección de 4 estados - 4-bits

Para la detección de los estados se procede a combinar todas las señales digitales de salida generadas en la etapa de conversión analógico/digital. La banda de frecuencia es dividida en 16 sub-bandas en función de la resolución del sistema que es de 625 MHz y en este diseño coincide con la resolución deseada. En la **Tabla 5.2** se presentan los bits ideales de identificación, obtenidos en la etapa de conversión A/D.

Tabla 5.2 Sub-bandas ideales de un discriminador de 4 bits.

| Sub-banda | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Sub-banda (GHz) | Resolución (MHz) |

|-----------|-------|-------|-------|-------|-----------------|------------------|

| 1         | 1     | 0     | 0     | 1     | 30 - 30,625     | 625              |

| 2         | 1     | 0     | 0     | 0     | 30,625 - 31,25  | 625              |

| 3         | 1     | 1     | 1     | 1     | 31,25 – 31,875  | 625              |

| 4         | 1     | 1     | 1     | 0     | 31,875 - 32,5   | 625              |

| 5         | 0     | 1     | 0     | 1     | 32,5 - 33,125   | 625              |

| 6         | 0     | 1     | 0     | 0     | 33,125 - 33,75  | 625              |

| 7         | 0     | 0     | 1     | 1     | 33,75 - 34,375  | 625              |

| 8         | 0     | 0     | 1     | 0     | 34,375 - 35     | 625              |

| 9         | 0     | 0     | 0     | 1     | 35 – 35,625     | 625              |

| 10        | 0     | 0     | 0     | 0     | 35,625 - 36,25  | 625              |

| 11        | 0     | 1     | 1     | 1     | 36,25 – 36,875  | 625              |

| 12        | 0     | 1     | 1     | 0     | 36,875 - 37,5   | 625              |

| 13        | 1     | 1     | 0     | 1     | 37,5 – 38,125   | 625              |

| 14        | 1     | 1     | 0     | 0     | 38,125 - 38,75  | 625              |

| 15        | 1     | 0     | 1     | 1     | 38,75 – 39,375  | 625              |

| 16        | 1     | 0     | 1     | 0     | 39,375 - 40     | 625              |

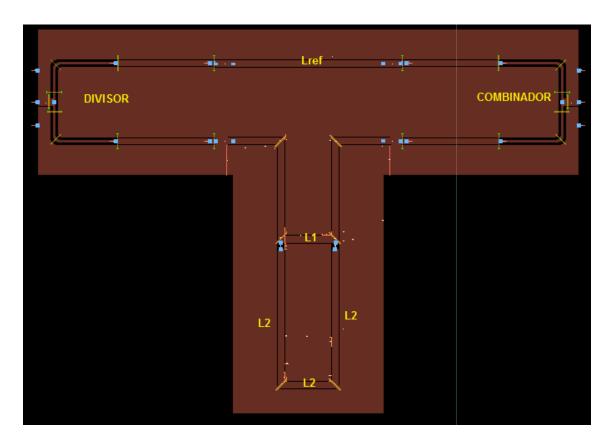

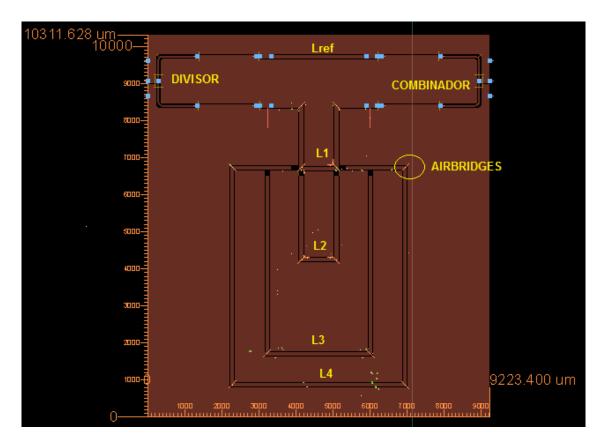

En la **Fig. 5.6** se muestra el diseño finalizado del discriminador reconfigurable de 4 bits con unas medidas de 10315 μm X 9225 μm, donde están unificadas en un mismo diseño todas las líneas de retardo (Lref, L1, L2, L3, L4), divisor y combinador del circuito.

En el diseño se puede apreciar la ubicación de los airbridges cuya función es eliminar la propagación del modo impar, colocados en las discontinuidades de las líneas de transmisión.

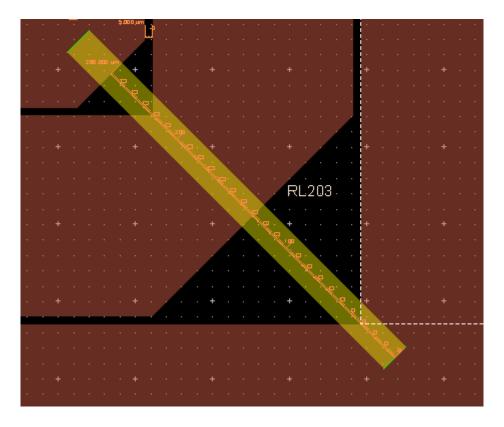

Otro comportamiento a tener en cuenta en las esquinas (ángulos de 90°)o discontinuidades, son la formación de condensadores parasíticos que afectan de manera considerable las simulaciones de los parámetros S de las líneas estudiadas. La manera de anular los parasíticos no deseados se puede observar en la **Fig. 5.7**, donde las esquinas son recortadas.

Fig. 5.6 Discriminador reconfigurable de 4 bits.

Fig. 5.7 Optimización de discontinuidades para evitar efectos parasíticos

En la **Fig. 5.8** tenemos el componente generado desde ADS. El siguiente paso es simularlo y obtener los 4 estados con las combinaciones de bits, ahora de una forma real, aunque no coincida del todo con los resultados de la **Tabla 5.2** anterior.

Fig. 5.8 Componente generado en el esquemático.

En las siguientes imágenes tenemos las conmutaciones realizadas para la obtención de los 4 estados; en la **Fig. 5.8 (a)** conmutan Lref – L1, en la **Fig. 5.8 (b)** Lref – L2.

Fig. 5.8 Conmutación entre las líneas. (a) Lref – L1, (b) Lref- L2.

Las siguientes conmutaciones realizadas entre las líneas Lref – L3 se aprecian en la **Fig. 5.9 (a)**, y por último la conmutación entre Lref – L4, en la **Fig. 5.9 (b)**

Fig. 5.9 Conmutación entre las líneas. (a) Lref – L3, (b) Lref- L4.

En la **Fig. 5.10** se muestra la etapa de detección de bits finalizado. Fijando el umbral en -10 dB y configurando previamente la conversión analógico /digital, donde el nivel lógico 1 se obtiene cuando se cumple la condición de  $|S21| \ge -10$  dB y el de 0 lógico se obtiene cuando |S21| < -10 dB, para obtener los bits de identificación. El resultado se muestra en la **Fig. 5.10.** El resultado de la franja de 30 GHz - 30,4 GHz se puede despreciar porque se trata de una sub-banda repetida.

Fig. 5.10 Obtención de bits con un umbral de -10 dB.

En la siguiente **Tabla 5.3** se muestran las combinaciones obtenidas. Se observa una pequeña reducción en la zona de trabajo, pasando de 30 GHz – 40 GHz a una nueva franja de trabajo de 30,4 GHz a 40 GHz.

**Tabla 5.3** Listado de sub-bandas y combinación de bits resultantes.

| Sub-bandas | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Sub-banda (GHz) | Resolución<br>(MHz) |

|------------|-------|-------|-------|-------|-----------------|---------------------|

| 1          | 0     | 1     | 1     | 0     | 30,4 - 31,1     | 700                 |

| 2          | 0     | 0     | 1     | 0     | 31,1 – 31,55    | 450                 |

| 3          | 0     | 0     | 1     | 1     | 31,55 – 32,45   | 900                 |

| 4          | 0     | 1     | 1     | 1     | 32,45 - 33,55   | 100                 |

| 5          | 0     | 0     | 1     | 1     | 33,55 – 35,85   | 300                 |

| 6          | 1     | 0     | 1     | 1     | 35,85 – 36,4    | 550                 |

| 7          | 1     | 1     | 1     | 1     | 36,4 - 37,1     | 700                 |

| 8          | 0     | 1     | 1     | 1     | 37,1 – 37,45    | 350                 |

| 9          | 1     | 1     | 1     | 1     | 37,45 – 37,6    | 150                 |

| 10         | 1     | 1     | 1     | 0     | 37,6 – 38,45    | 850                 |

| 11         | 1     | 1     | 0     | 0     | 38,45 – 38,8    | 350                 |

| 12         | 0     | 1     | 0     | 0     | 38,8 - 38,9     | 100                 |

| 13         | 1     | 1     | 0     | 0     | 38,9 - 40       | 1100                |

# 5.3. Bibliografía

- [1] M. Espinosa-Espinosa; B. G. M. de Oliveira; I. Llamas-Garro; M. T. de Melo; J. M. Kim; 4-bit, 1 to 4 GHz Reconfigurable Discriminator for Frequency Measurement, In *Proceedings of 44th European Microwave Conference* (EuMW 2014), 5-10 October 2014, Rome (Italy).

- [2] www.avx.com/docs/catalogs/gx.pdf gx02yd104kat2-500.

# CAPÍTULO 6. CONCLUSIÓN Y TRABAJO A FUTURO

#### 6.1. Conclusión

En este proyecto final de grado se presenta y demuestra el concepto de discriminadores de microondas reconfigurables de 2 y 4 bits. Desde el inicio del proyecto se ha tratado de cumplir con los objetivos iniciales establecidos, el diseño en banda Ka de circuitos discriminadores de frecuencia implementados con líneas CPW. Esto incluyó saber desarrollar discriminadores de microondas reconfigurables con alta miniaturización, bajo consumo de potencia, peso y coste reducido, que permitan implementar sistemas de medición de frecuencia con pocos componentes electrónicos comparados con los sistemas convencionales.

Un aspecto importante que determinará el tamaño y el coste de fabricación es la combinación de la tecnología y del tipo de sistema a desarrollar. Un diseño que utiliza tecnología de estado sólido y es reconfigurable, es más pequeño y de menor coste comparado con los diseños fijos.

La resolución de los discriminadores reconfigurables presentados en este proyecto se pueden mejorar aumentando el número de bits de identificación como se ha mostrado en el caso del discriminador de 2bits, donde se obtuvo una resolución de 2500 MHz en comparación con el de 4bits con una resolución de 500 MHz.

# 6.2. Trabajo a futuro

El objetivo de este proyecto ha sido diseñar y demostrar el funcionamiento de un discriminador de microondas reconfigurable de 4 bits unificándolo en un solo dispositivo. A medida que hemos ido añadiendo líneas de retardo, el diseño ha necesitado un reajuste en las medidas de cada línea, los interruptores fueron simulados idealmente, realizando la simulación en corto circuito y circuito abierto. Lo que está previsto en un futuro diseño es realizar la polarización delos diodos PIN para poder implementar en un diseño real los interruptores, incluyendo los inductores de choke y los capacitadores de bloqueo de corriente directa. De esta manera se lograría conseguir la implementación real de los interruptores SPQT mencionados.

A la hora de integrar todos los componentes en un diseño único, será necesario un reajuste de las longitudes de las líneas, sobretodo la última línea L4, para poder obtener todas las posibles combinaciones que puede ofrecer este dispositivo con todas las combinaciones de los 4 bits.

Otro objetivo de cara al futuro es la fabricación de este componente con micro y nanotecnología. Para ello tendrán que realizarse las mediciones reales y ver si

tiene un comportamiento parecido al obtenido en la simulación. Por último, se integrará este diseño junto con el resto de componentes electrónicos mencionados en el primer capítulo de esta memoria para formar un receptor identificador de frecuencia. Es decir, hay que añadir componentes al medidor de frecuencia reconfigurable, como son: la antena, los amplificadores, el detector y el convertidor analógico/digital. Posteriormente se deberá proceder a comprobar los resultados con medidas en el laboratorio.