#### Technical University of Denmark

#### Integrated Off-Line Power Converter

Fan, Lin

Publication date: 2018

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Fan, L. (2018). Integrated Off-Line Power Converter. Technical University of Denmarik.

#### DTU Library

Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# **Integrated Off-Line Power Converter**

Lin Fan PhD thesis January 2018

**DTU Electrical Engineering** Department of Electrical Engineering

# Integrated Off-Line Power Converter

Lin Fan

January 2018

#### Integrated Off-Line Power Converter

PhD thesis 2018

By Lin Fan

Supervisors: Ivan Harald Holger Jørgensen, Associate Professor, DTU Electrical Engineering Arnold Knott, Associate Professor, DTU Electrical Engineering

| Copyright:    | Reproduction of this publication in whole or in part must include the customary bibliographic citation, including author attribution, thesis title, etc. |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Published by: | Department of Electrical Engineering                                                                                                                     |

|               | Elektrovej, Building 325                                                                                                                                 |

|               | 2800 Kgs. Lyngby                                                                                                                                         |

|               | Denmark                                                                                                                                                  |

| PhD thesis    | www.elektro.dtu.dk                                                                                                                                       |

# Preface

This research project of integrated off-line power converter is conducted in the Electronics Group at the Department of Electrical Engineering in the Technical University of Denmark (DTU).

The duration of the research project is 3 years from February 2015 to January 2018. It includes approximately 30 ECTS (European Credit Transfer System) PhD courses study, equivalently 6 months compulsory workload and dissemination requirements such as teaching activities and students supervision, and vacation days with a total amount of officially 18 weeks in addition to public holidays. It also includes an external research stay with Prof. Fred C. Lee and Prof. Qiang Li at the CPES (Center for Power Electronics Systems) at the Virginia Tech (Virginia Polytechnic Institute and State University) in Blacksburg, Virginia, United States for about 3 months from July to September 2017.

The research project is the first project in the Electronics Group starting research on Power IC and/or PwrSoC (Power Supply on Chip). The research topics are multi-disciplinary, and mainly across the fields of integrated circuits, power electronics, and radio frequencies.

The supervisors are Prof. Ivan Harald Holger Jørgensen with a background of integrated circuits and Prof. Arnold Knott with a background of power electronics.

The research project is funded by a grant (No. 67-2014-1) for the TinyPower project from Innovationsfonden, Denmark.

The research project is performed with seven external partners: Niko-Servodan, Nordic Power Converters, Noliac, DTU Danchip, IPU, SimpLight, and Viso Systems.

The detailed acknowledgements are in the last section of this thesis.

Kgs. Lyngby, Denmark, January 2018

Lin Fan PhD Student

# Content

| Abstract (English)                                            | 7  |

|---------------------------------------------------------------|----|

| Abstract (Danish)                                             | 9  |

| 1. Introduction 1                                             | 11 |

| 1.1 Background and Motivation 1                               | 1  |

| 1.2 Project Objectives                                        | 12 |

| 1.3 Scope of the Thesis 1                                     | 13 |

| 1.4 Thesis Structure 1                                        | 13 |

| 2. State of the Art 1                                         | 15 |

| 2.1 Review of Power Supply on Chip (PwrSoC) Workshops         | 15 |

| 2.2 Power MOSFETs                                             | 17 |

| 2.2.1 Modelling of Power MOSFETs                              | 17 |

| 2.2.2 Layout Structures of Power MOSFETs                      | 18 |

| 2.2.3 Figuire-of-Merits (FOMs) of Power MOSFETs               | 21 |

| 2.3 Topologies                                                | 24 |

| 2.3.1 Resoant Converter Topologies                            | 24 |

| 2.3.2 Switched-Capacitor Topologies2                          | 28 |

| 3. Integrated Power MOSFETs                                   | 33 |

| 3.1 On-chip Nonlinear Parasitic Capacitance Modelling         | 33 |

| 3.2 On-chip Layout Capacitance Coupling and Structure Impacts | 43 |

| 3.3 On-chip Nonlinear Figure-of-Merits and Optimization       | 51 |

| 3.4 Off-chip Parasitic Considerations of Packages             |    |

|                                                               | 58 |

| 3.6 Summary                                                                | 64  |

|----------------------------------------------------------------------------|-----|

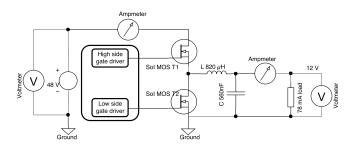

| 4. Inductuctor-Based Converters (Low-Voltage Output Converter)             | 65  |

| 4.1 Buck Converter Using Integrated Power MOSFETs                          | 65  |

| 4.2 IC-Based Resonant Power Stage Investigations                           | 67  |

| 4.3 Piezo-Based Resonant Power Stage Investigations                        | 71  |

| 4.4 GaN-Based Resonant Power Stage Investigations                          | 74  |

| 4.5 Summary                                                                |     |

| 5. Switched-Capacitor Converters (High-Voltage Input Converter)            | 79  |

| 5.1 High-Voltage Switched-Capacitor Power Stage                            |     |

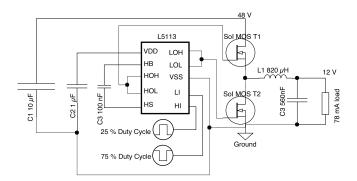

| 5.2 High-Voltage Switched-Capacitor Driving Circuit                        | 83  |

| 5.3 High-Voltage Switched-Capacitor Power Converter                        |     |

| 5.4 Asynchronous-Switched-Capacitor Power Converter                        | 85  |

| 5.5 Summary                                                                | 87  |

| 6. Conclusions                                                             |     |

| 7. Future work                                                             |     |

| References                                                                 |     |

| Appendix A Publications                                                    | 115 |

| Appendix A.1 Publication (journal and conference)                          | 115 |

| Appendix A.2 Publication (conference)                                      |     |

| Appendix A.3 Publication (conference)                                      |     |

| Appendix A.4 Publication (PwrSoC, First Prize Award, IEEE PELS)            | 133 |

| Appendix A.5 Publication (journal and conference, accepted)                | 137 |

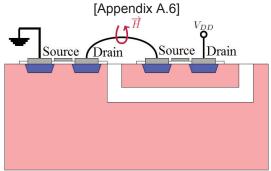

| Appendix A.6 Publication (journal and conference, accepted, second author) |     |

| Appendix A.7 Publication (conference, accepted)                            |     |

| Appendix A.8 Publication (journal and conference, accepted) | 154 |

|-------------------------------------------------------------|-----|

| Acknowledgements                                            | 163 |

| Acknowledgements                                            | 100 |

# Abstract (English)

The miniaturization trend of industrial and consumer electronics continuously drives the demand of reductions in size, weight, and cost of power supplies. The examples of such applications considered in this research are light-emitting diode (LED) drivers for intelligent lighting systems and internet of things (IoT). These power supplies convert the mains power of 220-240 Vrms AC in Europe to low DC voltages around 13 V with an output power of 5-20 W. This research focuses on the DC-DC power conversion, with rectified AC mains as input. The size reduction is the direct requirement, and it can only be obtained by simultaneously improving efficiency to maintain thermal limits at maximum losses. However, fundamental trade-off relationships exist between the power density and the efficiency. To achieve both high efficiency and high power density, systematic development is imperative for components, topologies, and architectures.

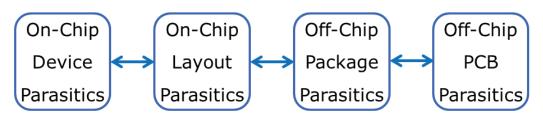

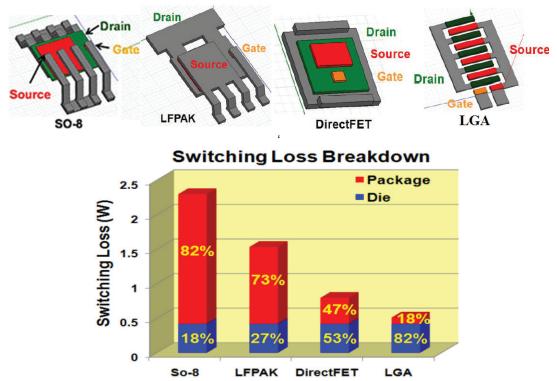

The research started from integrating active components on a single chip, i.e. integrated high voltage (≥ 100 V) power MOSFETs in a Silicon-on-Insulator (SOI) process. The extreme performances (such as maximum switching speeds and minimum attainable on-resistances) of these devices are jointly determined by the device, layout, package, and PCB parasitic properties. The research highly contributes to the development towards Power Supply on Chip (PwrSoC) regardless of topologies and switching technologies. First, parasitic capacitances of power semiconductors are a part of the key design parameters of power supplies, for both hardswitched and soft-switched converters. A modelling method is proposed to systematically analyse the nonlinear parasitic capacitances of the power MOSFETs in different states, whereas datasheets typically specify capacitances only in transistor off-states. Second, the nonlinear figure-of-merits (FOMs), which might be used for device-to-device comparisons, are systematically analysed and optimized up to 18.3 times for a given device with quasi-zero voltage switching conditions. Third, four layout structures are proposed and their parasitic capacitive coupling effects are analytically compared, which shows that parasitic capacitances of on-chip interconnections could dominate over intrinsic capacitances of power devices. In addition, the parasitic effects of package and PCB are gualitatively analysed.

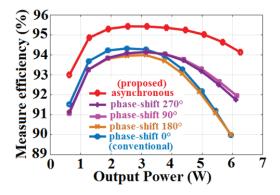

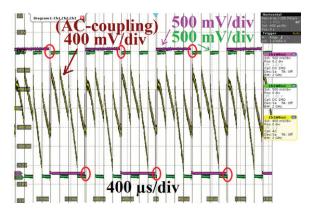

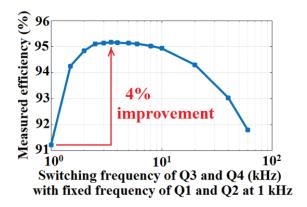

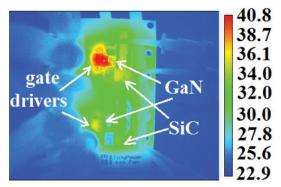

For topologies and architectures, a two-stage power converter architecture is proposed, where the input stage is a high-voltage switched-capacitor converter and the output stage is a lowvoltage inductor-based converter. For the output stage, a buck converter using the integrated power MOSFETs is implemented with measured efficiencies around 93 %. For resonant converters, integrated power stages with parasitic bipolar effects, using piezo elements as resonant tanks, and discrete prototypes of class-DE series-parallel LCLC converters are investigated. The input stage is implemented as 380 V input switched-capacitor converters, using both Gallium Nitride (GaN) and Silicon Carbide (SiC) devices to properly address switching losses at high-voltage low-power levels. For power stages, a 10 W prototype reaches a peak efficiency of 98.6 % and a power density of 7.5 W/cm<sup>3</sup>. For converters including driver and its supply, a 21.3 W prototype achieves a full-load efficiency of 97.6 % and a power density of 2.7 W/cm<sup>3</sup>. For switching schemes, a concept of Asynchronous-Switched-Capacitor (ASC) is proposed for a 380 V, 4:1 switched-capacitor converter, and a peak efficiency of 95.4 % is achieved with reduced output voltage ripples. All these prototypes demonstrate the switchcapacitor feasibility at higher-voltage (> 200 V) lower-power (< 30 W) levels than previously published ones.

The main conclusions are that this research contributes to the analysis and design of the integrated high voltage power MOSFETs for on-chip integrated power converters, and contributes to the design and implementation of the switched-capacitor based two-stage architecture for discrete off-line power converters. It is concluded that efficient integrated off-line power conversion is currently in its infancy, and this research work fosters the framework and paves the way for future development in this area.

### Abstract (Danish)

Miniaturisering tendensen i industriel og konsumer elektronik stiller konstant krav til reduktion i størrelse, vægt og pris på strømforsyninger. I dette forskningsarbejde er der taget udgangspunkt i lysdioder (LED) driver konstruktioner til intelligent belysnings systemer samt til brug i "internet of things" (IoT). Strømforsyninger i denne kategori konverterer lysnet 220-240V AC Vrms europæisk standart, til lavspænding jævnstrøm (DC) i størrelsesordenen 13V med en effekt på 5-20W. Denne forskning fokuserer på DC-DC konvertere, med ensrettet AC-forsyning. Fysisk størrelses reduktion er kravet, men kan kun opnås samtidig med bedre effektoverførsel for at fastholde termiske grænser og tab. Fundamentale relationer begrænser, i form at afhængigheder imellem energitætheden og effektivitet, for at opnå både høj effektivitet samt høj energitæthed er, systematisk udvikling af udformning, komponenter og arkitekturen, ufravigelig.

Dette forskningsarbejde startede med integration af aktive komponenter på en enkelt "chip" initialt høj spændings (≥ 100 V) Power MOSFETs på Silicon-on-Insulator (SOI). Den høje ydelse af løsningen er en kombination af, opbygningen, indkapsling og PCB, snylte egenskaber. Forskningen peger imod udvikling med Power Supply on Chip (PwrSoC) uanset opbygning og switch teknologi. Snylte kapaciteter I effekt halvledere er en yderst vigtig konstruktion parameter til strømforsyninger, for både hard-switched og soft-switched konvertere. En modellerings metode bliver fremlagt til systematisk analyse af ikke lineær snylte kapaciteter i Power MOSFETs, i forskellige tilstande, hvor der i datablade typisk specificerer kapaciteten i transistorens off-stadie. Ydermere den ikke lineære godhed (FOMs) som benyttes til sammenligning bliver systematisk analyseret og endvidere optimeret op til 18,3 gange for et givent stykke udstyr med quasi-zero voltage switching drift. Fire forskellige konstruktioner bliver foreslået og deres snylte kapaciteters effekt bliver analytisk sammenlignet, som viser at snylte kapaciteters effekt på både IC og print kvalitativt analyseret.

Opbygning og arkitektur til en to trins effekt-konverter bliver fremlagt hvor indgangs trinnet er en højspændings switched-capacitor kobling og udgangs trinnet er en lav spænding induktions baseret konverter. Udgangstrinnet er en buck konverter som benytter den integrerede power MOSFETs og yder en effektivitet i omegnen af 93 %. Resonans konvertere bliver belyst i forskellige udformninger herunder klasse-DE Seriel-parallel LCLC konverter. Indgangs trinnet er implementeret som 380 V switched-capacitor konverter der benyttes både Gallium Nitride (GaN) og Silicon Carbide (SiC) halvledere for at reducere switching tab ved høj spændings niveauer samt lille effekt. Udgangstrinnet, en 10W prototype opnår en peak effektivitet på 98,6 % og en energi tæthed på 7,5 W/cm<sup>3</sup>. En prototype Konverter med effekt på 21,3 W viste en effektivitet på 97,6 % ved fuld belastning og en energitæthed på 2,7 W/cm<sup>3</sup>. Valg a switch blev et koncept bestående af asynkron switche kondensatorer (ASC) drift på 380 V, 4:1 switchede kondensator konverter leverede en spids belastning effektivitet på 95,4 % med reduceret ripple. Alle de fremstillede prototyper leverede bedre resultater ved høj spænding (> 200 V) lav effekt (< 30 W) end tidligere publicerede konstruktioner.

Hoved konklusionen er at dette forskningsprojekt bidrager til konstruktion og analyse af integreret høj spændings effekt MOSFET i on-chip integreret strømforsyninger, ydermere bidrager det til konstruktion og implementering af switched-capacitor i to trins arkitektur for diskrete off-line strømforsyninger. Effektive integreret off-line strøm forsyninger er stadig på en spæd stadie, og dette forskningsarbejde baner vejen for fremtidig udvikling på dette område.

# 1. Introduction

#### 1.1 Background and Motivation

Power supplies that convert universal mains AC power to low DC voltages (e.g. 5 V and 12 V) are essential parts of numerous products of industrial and consumer electronics. The examples of the applications are Solid State Lighting (SSL) products including light-emitting diodes (LEDs), organic light-emitting diodes (OLEDs), and polymer light-emitting diodes (PLEDs). The emerging intelligent systems for internet of things (IoT) are further examples, such as intelligent lighting systems (wall switches and movement sensors), intelligent electronic thermostats, intelligent liquid pumps, and alarm and surveillance systems. The power supplies of the household appliances used in our daily life are common examples, such as power supplies for television and kitchen appliances, and miniature chargers for computers and mobile phones.

As the development of the size reduction of the power supplies in all above examples relatively lag behind the advances of the technology development of other electronic parts in these applications, the power supplies significantly contribute to the overall system sizes of these applications. The miniaturization trend of electronic technologies continuously drives the demand of reductions in size, weight, and cost of power supplies. Among these demands, the size reduction of the power supplies is the direct requirement, and the weight and cost reduction requirement accompany the ministration trend.

The reduction of the sizes of the power supplies can, in principle, be realized from two perspectives, i.e. passive components and active components. The passive components, especially magnetic components, typically dominate the sizes of nowadays power supplies [1]. For the size reduction of passive components, increasing the switching frequency of power supplies can reduce the passive component values and energy storage requirements, and potentially (but not necessarily) reduce the sizes of passive components [1], [2]. The ongoing evolution of very high frequency (VHF) power supplies significantly contribute to the size reduction of passive components [3].

The size reduction of active components benefits and enables the size reduction of passive components. While maintaining other performances, the size reduction (relatively) of active components not only reduces the cost (the device area related) but also reduces on-chip device/layout parasitics and minimizes off-chip package/PCB parasitics, which increases the maximum permissible operating frequency thus enabling small passive components. Therefore, the research and development of active components is one of the important aspects of the miniaturization of power supplies. The integration of power semiconductors on integrated circuits (ICs), e.g. integrated high voltage power Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs), is hereby considered. This is an emerging research and development area, and directly contributes of the development of to the development towards Power Supply on Chip (PwrSoC), which significantly reduces the sizes of the power supplies. This motivates the first aspect of this research about the investigations of intrinsic properties and layout impacts of integrated power MOSFETs.

With the technologies to reduce the sizes of power supplies, the practical difficulties and challenges reside in the increased power density (output power divided by volume). While the size is reduced, the power density is increased for a given output power, and the thermal density is also increased for a given efficiency. As a result, the power density cannot unlimitedly be increased, in other words, the size cannot be unlimitedly reduced, because the thermal limits of the power supplies have to be maintained for the maximum losses of the power supplies. At the point when thermal limits are reached, further increasing the power density requires simultaneously improving the efficiency. Otherwise, the efficiency becomes limiting the power density, and starts to lower the power density due to additional sizes of heat sinks. Therefore, increasing the efficiency is the primary development goal and the premise of the realization of the size reduction of power supplies. Before the thermal limits are reached, i.e. within a temperature rise constraint, fundamental trade-off relationships exist between the power density and the efficiency. In principle, increasing the efficiency is fundamentally always possible by increasing the volume [4]. To achieve both high efficiency and high power density, systematic development is needed not only for components, but also for topologies, and architectures.

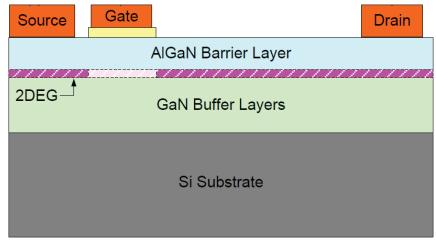

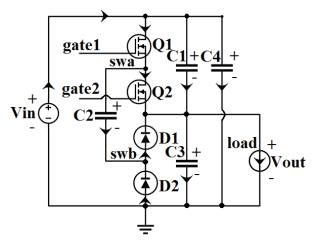

This motivates the second aspect of this research about architectures and topologies that potentially realize the integration of power converters. The switched-capacitor converters are of great considerations for on-chip integration [5] – [9]. The discrete switched-capacitor converters can potentially realize off-line power conversion [10]. One of the main challenges of switched-capacitor converters is the regulation, which can promisingly be resolved by a two-stage architecture, where the input stage is a high-voltage low-frequency switched-capacitor converter that is mainly responsible for power conversion, and the output stage is a low-voltage high-frequency inductor-based converter that is mainly responsible for regulation. The emerging wide band gap semiconductors such as Gallium Nitride (GaN) [11], [12] and Silicon Carbide (SiC) [13], [14] have superior properties and have the potentials to enable both high efficiency and high power density. These devices can also be actively combined to properly address certain topologies and architectures.

#### **1.2 Project Objectives**

The primary objective of the project is to investigate ways and feasibility of integrating high voltage active components on integrated circuits that can potentially enable further integration of high voltage off-line power converters. The investigations of topologies and architectures accompany this primary objective with the development goal of achieving both high efficiency and high power density. These are the essential properties to reduce the sizes of power supplies that can find their ways into numerous emerging applications such as power supplies in AC outlets and wall plugs for internet of things (IoT).

| Parameters     | Specifications             |

|----------------|----------------------------|

| Input voltage  | 220 – 240 Vrms AC          |

| (AC)           | (European mains)           |

| Input voltage  | 310 – 340 Vdc              |

| (DC)           | (Rectified European mains) |

| Output voltage | 12 – 13 V                  |

| Output Power   | 5 – 20 W                   |

Table 1.1 General specifications of the research project.

#### 1.3 Scope of the Thesis

The scope of thesis is about the integrated technologies and the utilization of wide band gap semiconductors for the DC-DC power conversion. The focus of the DC-DC power conversion has two areas. One focus area is about integrated power MOSFETs that can potentially realize integrated power converters. This includes the modelling of the nonlinear parasitic capacitances of the power MOSFETs in a Silicon-on-Insulator (SOI) process, the modelling of the parasitic capacitive coupling of on-chip interconnections and the layout structures realization and comparison, and the analysis and optimization of nonlinear figure-of-merits (FOMs). The other focus area is for power stages and their driving circuits that can properly utilize power devices. This includes a two-stage power conversion architecture that is composed of high-voltage switched-capacitor converters and low-voltage inductor-based converters.

The contents of the thesis focus on the research work of related topics within the above scope. A large amount of work has been conducted with partner companies and manufacture foundries. Confidential contents such as information from collaborating companies and PDK (process design kit) information from IC foundries are not included in the thesis, except open access/public information for which references are provided.

#### **1.4 Thesis Structure**

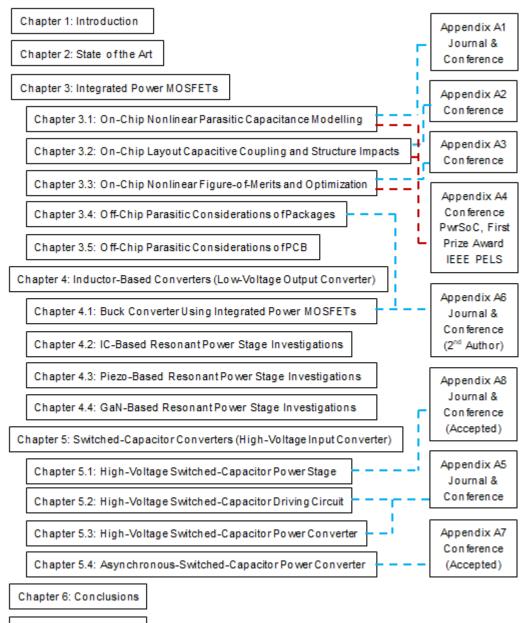

The overall thesis structure is shown in Fig. 1.1. The relationships between the chapters and the appendix publications are indicated with the dotted lines. Chapter 1 is the introduction of the thesis, which includes the scope of the thesis, background and motivation, project objectives, and the thesis structure. Chapter 2 is the state-of-the-art, which summarizes the recent advances in components, topologies, and architectures. This chapter is the basis of the research work and to which the following chapters contribute to. Chapter 3 focuses on the integrated power MOSFETs, where both on-chip and off-chip characteristics are described and discussed. Chapter 4 is regarding the low-voltage inductor-based converters, where the implementation of a buck converter using the integrated power MOSFETs and other resonant power stage investigations are presented. Chapter 5 concentrates on the high-voltage switched-capacitor converters, which includes the analysis and design of the power stage, the driving circuit, the complete power converter, and a proposed switching scheme of asynchronous-switched-capacitor and its realization based on GaN and SiC devices. Chapter 6 summarizes and concludes the thesis. Chapter 7 describes the future work.

Chapter 7: Future Work

Fig. 1.1 Thesis structure and relations to appendix publications.

# 2. State of the Art

This chapter summarizes the state of the art of the related research topics and recent advances in components, topologies, and architectures. This formulates the background of the research work and to which the research work contributes to. The initial and original motivation of the technical development of the following chapters is also included.

#### 2.1 Review of Power Supply on Chip (PwrSoC) Workshops

The first aspect of this research work is about the integration of high voltage ( $\geq$  100 V) power MOSFETs. This is tightly related to and contributes to the development towards Power Supply on Chip (PwrSoC). The international workshop on PwrSoC [15], organized by the Institute of Electrical and Electronics Engineers (IEEE) Power Electronics Society (PELS) and the Power Sources Manufacturers Association (PSMA), is the leading workshop in this research field where world-leading companies and universities present cutting-edge advances in integrated power conversion technologies. The selected representative publications in PwrSoC are [16]-[58] for the years from 2008 to 2016. Each of the contributions is state-of the-art and covers a broad range of topics. It is hardly possible to categorize these contributions. Generally speaking, [16]-[28] are switched-capacitor related, [29]-[35] are about system and applications, [36]-[47] are semiconductor technologies related, [48], [49] are about magnetics, [50] is about capacitors, [51], [52] are regarding integration and packaging, [53]-[56] are about topologies and control, [57], [58] are about granular power. A 3 mW micro power supply [59] is composed of an integrated AC-DC converter, an integrated DC-DC converter, and one external capacitor in between. Nearly all of the published work focuses on integrated converters with 48 V and 12 V bus lines or lower intermediate voltages, except discrete prototypes or processes development.

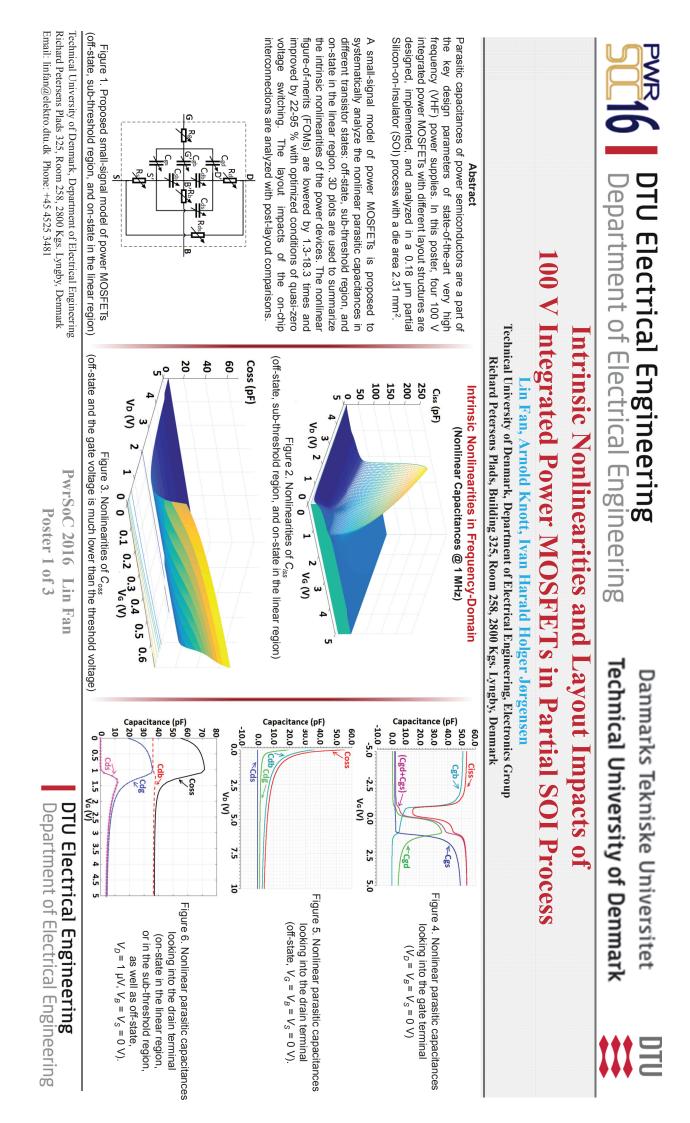

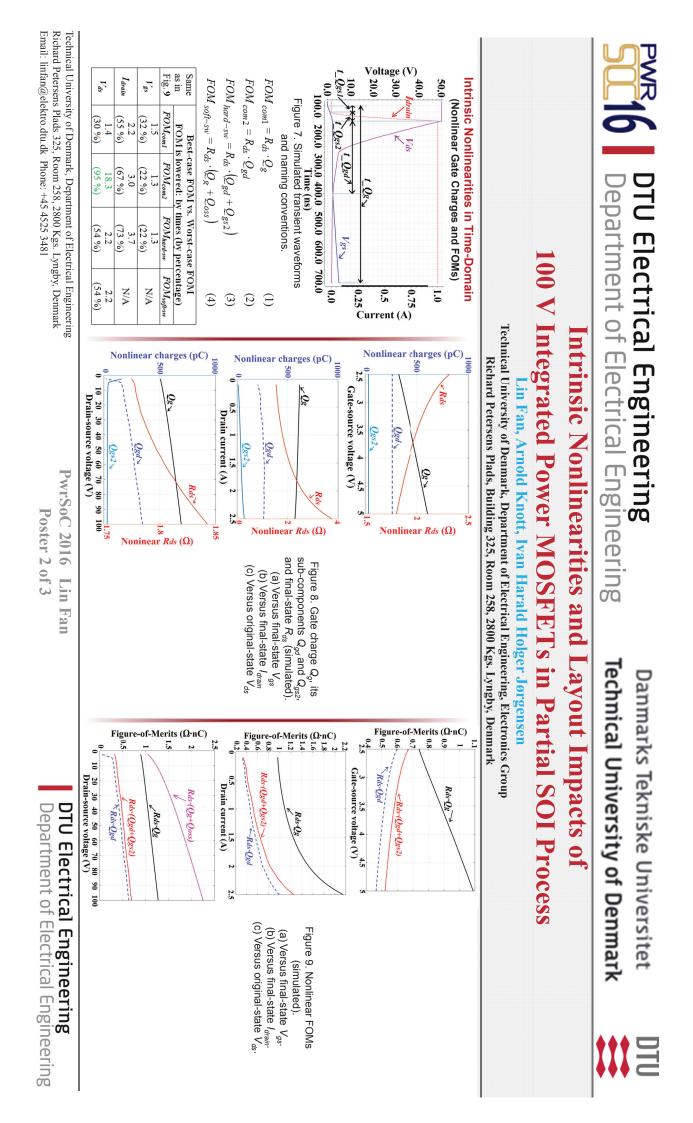

The only four cases of integrated converters that interface voltages above 48 V in [16]-[59] are summarized in Table 2.1. All these reported cases have capacitor-based topologies. The case 1 [23], [60] have a relatively low input voltage, and the case 2 [24], [61] is limited by the level of integration with a two-chips stacking structure and other external components. The case 3 [25], [62] is AC mains interfaced, but most of the chip area is occupied by a single large high-voltage capacitor [62], and this  $\mu$ W-level converter is not easily scalable to higher output power levels unless external components are used [63]. The case 4 [59], [64] uses a directly coupled full wave rectifier combined with two shunt regulators, so the input transistors have to be high-voltage devices that are connected to the mains voltage. Both the case 3 and the case 4 are mains interfaced but the output powers of these converters are in the  $\mu$ W-mW range. This research started with investigations of directly integrating high voltage ( $\geq$  100 V) power MOSFETs on a single chip. The intrinsic nonlinearities and layout impacts of 100 V power MOSFETs in a partial SOI process have been investigated, and this work contributes to the PwrSoC workshop in 2016.

| Case           | 1 [23]     | 2 [24]       | 3 [25]                       |            | 4 [59]        |

|----------------|------------|--------------|------------------------------|------------|---------------|

| Year           | 2010       | 2014         | 2014                         |            | 2016          |

| Prior art      | 2009 [60]  | 2013 [61]    | 20                           | 13 [62]    | 2016 [64]     |

| Contributors   | KU         | Columbia     | KU                           | Leuven     | Reutlingen    |

|                | Leuven     | University   |                              |            | University    |

|                |            | UC Berkeley  |                              |            |               |

| Topology       | Switched-  | Switched-    | Capacit                      | tive AC-DC | Full wave     |

|                | Capacitor  | Capacitor    | (Capacitive voltage divider) |            | rectifier and |

|                |            | (Hybrid      |                              |            | Switched-     |

|                |            | resonant)    |                              |            | capacitor     |

| Integration    | Integrated | Limited-     | Integrated                   | Partly-    | Partly-       |

|                |            | Integrated   |                              | Integrated | Integrated    |

| Input voltage  | 12 Vdc     | 85 Vdc       | 230 Vrms                     | 230 Vrms   | 230 Vrms      |

| Output voltage | 70 Vdc     | 42.5 Vdc     | 3.3 Vdc                      | 3.3 Vdc    | 3.3 Vdc       |

| Output power   | 320 mW     | 17W, 2-chips | 9.5 μW                       | 7 mW       | 3 mW          |

|                |            | stacking     |                              |            |               |

Table 2.1 Only 4 cases of integrated converters that interface voltages above 48 V in [16]-[59].

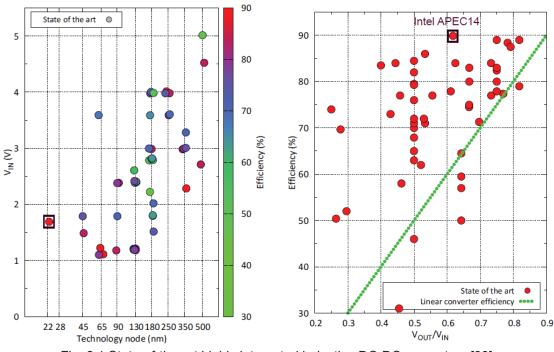

Fig. 2.1 State-of-the-art highly integrated inductive DC-DC converters [33].

In addition to the above high voltage capacitor-based topologies, high frequency inductor-based converters are also of the state-of-the-art considerations [65]-[97]. Generally speaking, the majority of the research combines high frequency operation and multiphase technology to enable small values of passive components [65] so that these components can be integrated on-chip. In addition, advanced topologies are used such as hybrid converters composed of buck converters and regulators [66], [67], three-level buck converters [68], [69], and resonant gate drivers [70], [71]. Special processes are also used such as SiGe [72], GaAs [73], and SOI [74].

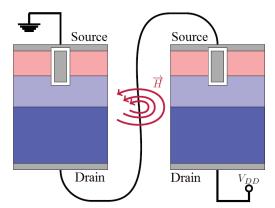

Zero voltage switching (ZVS) technology is used in [72], [75]. Customized solutions for specific applications are possible [76]-[78]. Two major research fields are about different ways of packaging and integration [79]-[91] and control technologies [92]-[97] such as frequency control [92], and hysteretic related control [93]-[97].

The state-of-the-art high frequency, highly integrated inductive DC-DC converters are summarized in Fig. 2.1 [33]. The most important thing to note is that the input voltages of these DC-DC converters are limited to 5 V or below. The implementation of on-chip inductors is still the blocking issue for high-voltage power converters. The voltage impacts at high-voltage levels on active components are to be discussed below.

#### 2.2 Power MOSFETs

This section summarizes the recent advances in modelling, layout structures, and figure-ofmerits (FOMs) of power MOSFETs. These topics are related to each other and are the areas to which this research work contributes.

#### 2.2.1 Modelling of Power MOSFETs

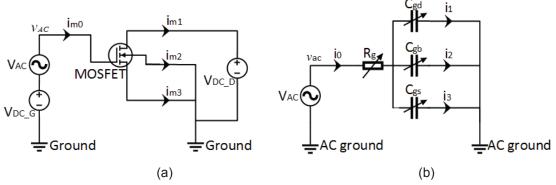

Inductor-based converters such as resonant converters (resonant converters will be discussed in the section 2.3.1) generally use or tend to use soft-switching technologies. Soft-switching technologies such as zero-voltage switching (ZVS) and zero-current switching (ZCS) are precisely about turn-on and turn-off transients and properties of power switches, e.g. power MOSFETs. Academia and industry have been trying to design, operate, and control power converters as close as soft-switching conditions of power switches. However, difficulties of accurate soft-switching reside on the hard-to-be-determined nonlinear parasitic capacitances of power switches. Conventionally, power switches are characterized in terms of switching time and/or gate charge, which give little insight to the nonlinearities of the parasitic capacitances.

The analyses of the nonlinear parasitic capacitances of the power MOSFETs can benefit power converter designers for getting insight into soft-switching technologies and investigating new topologies such as resonant converters, where parasitic capacitances are a part of the key design parameters. These analyses also benefit hard-switching converters where switching losses and gating losses are determined by the nonlinear parasitic capacitances as well. However, such information is typically not available, and this is particularly due to the fact that industrial datasheets typically specify capacitances only in off-states, e.g. the input capacitance  $C_{iss}$  and the output capacitance  $C_{oss}$  are provided only at the condition when the gate and the source of the power MOSFETs are shorted [98], [99]. There is no direct information about how the parasitic capacitances behave versus different bias voltages. Further analysis shows that simple extrapolation from the off-state capacitances could sometimes be even misleading. Therefore, this research work intends to establish a proper way to characterize the nonlinear parasitic capacitances of the power MOSFETs, and the nonlinearity analysis will be described in the section 3.1.

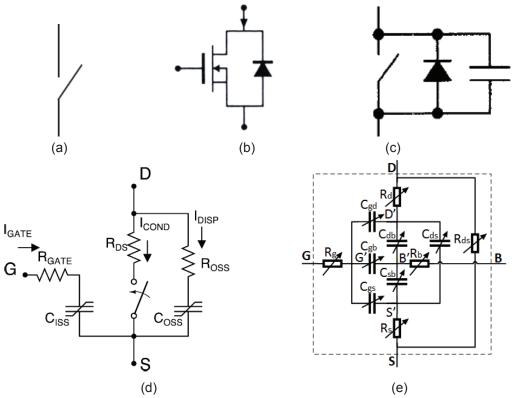

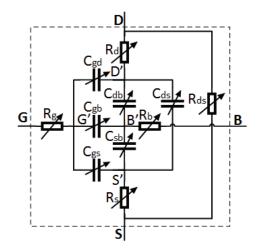

Fig. 2.2 Conventional and state-of-the-art modelling of power MOSFETs. (a) Model used in a Bachelor degree textbook [100]. (b) Model used in a Master degree textbook [101]. (c) Model used in a scientific paper [102]. (d) State-of-the-art loss model by MIT [1], [103], [104]. (e) State-of-the-are small-signal model by this work [Appendix A.1].

The conventional and the state-of-the-art modelling of power MOSFETs are shown in Fig. 2.2. The most simplified model of an ideal switch, with or without on-resistance, is shown in Fig. 2.2 (a). This model is generally used for system level analysis. The model in Fig. 2.2 (b) takes the body diode into account and facilitates basic converter level analysis. For analytical equations development, an ideal capacitor is typically added and assumed, as shown in Fig. 2.2 (c). The state-of-the-art loss model of power MOSFETs is shown in Fig. 2.2 (d). The most important thing to note for this model is that the drain-to-gate capacitance  $C_{gd}$  is ignored [103], i.e. the coupling from the output port back to the input port (through  $C_{gd}$ ) is neglected [1]. Furthermore, for loss analysis purpose, the input and output capacitances in this model are lumped with equivalent linear capacitances. All the above models do not provide the nonlinearities of the parasitic capacitances and are not used for the purpose of analysing the switching transients. The small-signal model in Fig. 2.2 (e), which is proposed by this work and further described in the section 3.1, focuses on the analysis of the nonlinear behaviour of the parasitic capacitances.

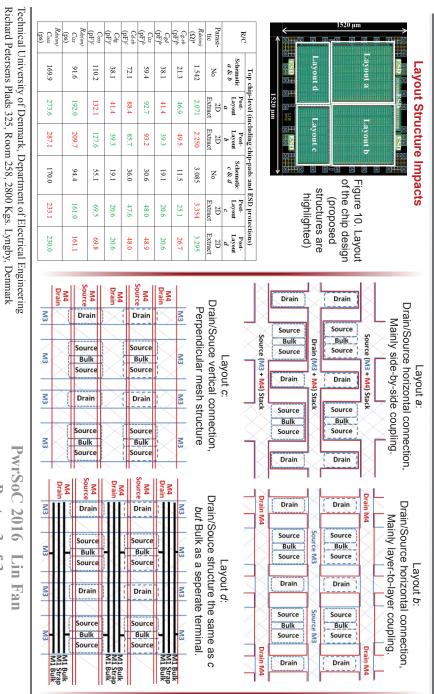

#### 2.2.2 Layout Structures of Power MOSFETs

The electrical parameters of on-chip interconnections become the practical bottlenecks of circuit performances [105], and this is especially true for high-power-density converters [106]. The coupling capacitances may be measured directly on-chip but the accuracy of the measurements suffers from the supply noise [107]. Therefore, a modelling/analysis method is needed.

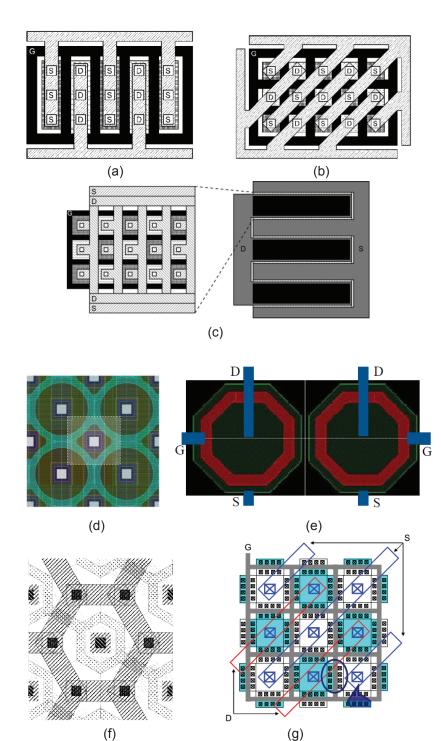

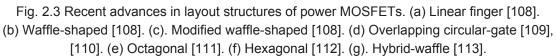

The capacitive coupling of on-chip interconnections is embedded in the layout structures of power MOSFETs. Accordingly, the layout structures impact the performances of power MOSFETs. The examples of recent advances in layout structures are summarized in Fig. 2.3. In Fig. 2.3 (a), the linear finger structure is shown as a relatively conventional structure. As a

comparison, the waffle-shaped structure is shown in Fig. 2.3 (b). The waffle-layout structure is known of having a reduced overall area in a compact fashion, and hence a high density is the main advantage. In addition, the structure can potentially have low parasitic drain capacitances [108]. However, the 45-degrees routing of the drain and source connections is not optimal for high current applications, due to the current unbalance caused by the angled non-symmetrical connections [108]. In addition, the total width of the drain and source connections is relatively small for handling high peak currents.

Another way of implementing waffle-layout is shown in Fig. 2.3 (c). This modified waffle-layout structure has 90-degrees (vertical and horizontal) drain and source connections, which are located in different metal layers. Note that the drain and the source are connected on both sides, and the space between the waffle-layout structures has to be reserved for substrate contacts and guard rings. On the right side of Fig. 2.3 (c), the overall drain and source connections are implemented in a large metal finger structure. The width of the metal fingers is not only associated with the current handling capability. There is a trade-off to consider, i.e. the wider the metal finger is, the lower the parasitic series resistance becomes, but the parasitic capacitances increase simultaneously. The metal fingers are normally made in upper metal layers, to minimize the parasitic capacitances of drain and source to substrate.

The overlapping circular-gate structure, as shown in Fig. 2.3 (d), is used to improve the powerdensity of integrated power MOSFETs. Gate overlapping is possible by overlapping the circular gates of the neighboring cells of CGT (Circular-Gate Transistor), which can save up to 30-60 % layout area, as compared to RGT (Rectangular-Gate Transistor) with an equivalent aspect ratio [109]. The lower on-resistance can also be achieved at the same time, due to the higher current stirring capability per active area. The parasitic junction capacitances associated with drainsubstrate can also be minimized. One drawback of the overlapping circular-gate structure is that there is a section of gate annulus that does not contribute to the drain current. In addition, the gate overlapping slightly reduces the breakdown voltage, as compared to conventional CGT, but it is still slightly above the breakdown voltage of RGT.

The octagonal structure is shown in Fig. 2.3 (e). It is mainly used to achieve good gate-source voltage matching in the sub-threshold region for low-power applications at very low current levels [111]. The octagonal structure can remove the hump effect, which would otherwise strongly degrade the device matching in the weak-inversion sub-threshold region. For the octagonal structure, the polysilicon gate is already approaching the ring shape. The hexagonal structure is shown in Fig. 2.3 (f). The main advantage of hexagonal structure is the low parasitic drain and source capacitances, due to the very small drain and source area. This hexagonal structure can achieve good matching and small area at the same time [112].

Finally, the hybrid-waffle structure is shown in Fig. 2.3 (g). By comparing the HW (Hybrid Waffle) structure and the conventional MF (Multi Finger) structure, it shows that the hybrid-waffle structure is actually an effective trade-off [113], between the metal width of the diagonal source/drain connections and the active area of the device, which allows effective optimization between conduction loss and switching loss. It also shows that, with large enough area, both reduction in overall on-resistance and smaller total gate charge can be achieved at the same time with the hybrid-waffle structure, compared to the multi-finger structure. Note that the total width of the multi-finger structure is wider than that of the hybrid-waffle structure for the same

chip area, thus the W/L ratio of the hybrid-waffle structure is smaller than that of the multi-finger structure. It means that the hybrid-waffle structure can achieve smaller overall on-resistance with a large enough device area, and it is fundamentally because of the reduction of parasitic resistances due to wide metal connections.

All these layout structures, especially the overlapping circular-gate structure, the octagonal structure, the hexagonal structure, the waffle-shaped structure, and the hybrid-waffle structure actually become obsolete. These layout structures are commonly not permitted in deep submicron processes, due to the polysilicon DRC (Design Rule Check) rules, i.e. the 90-degrees (or other angles) of the turn of the gate polysilicon is generally not allowed in deep submicron processes. The linear finger structure and the modified waffle-shaped structure have the potentials to be further improved to comply with the corresponding DRC rules, e.g. the gate network can be re-distributed in upper metal layers. Furthermore, a high active-area density cannot be a single FOM (Figure of Merit) of a layout structure. The substrate contacts and the guarding rings should also be taken into account between the active-areas. This is especially true when the waffle-shaped structure [114], [115] is actually an effective trade-off between the metal interconnections and the active-areas and/or interconnections in all geometrical directions.

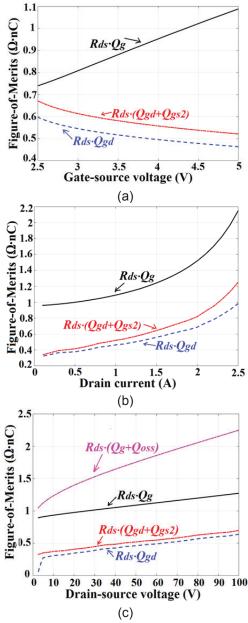

#### 2.2.3 Figure-of-Merits (FOMs) of MOSFETs

The primary purpose of figure-of-merits (FOMs) in power semiconductor industry is for technology-to-technology comparisons. Different technologies are quantitatively compared using FOMs [12], and a lower FOM index represents a better performance. The second usage of FOMs is for evaluating the overall performance of a power device for a switching application [116]. The conventional BFOM (Baliga FOM) is solely based on the conduction loss minimization [117]. Therefore, the BFOM is not applicable to applications where switching losses are not negligible. Various forms of FOMs exist [12], [42], [43.], [116]. However, it is found that these FOMs are not consistently used [116], [118].

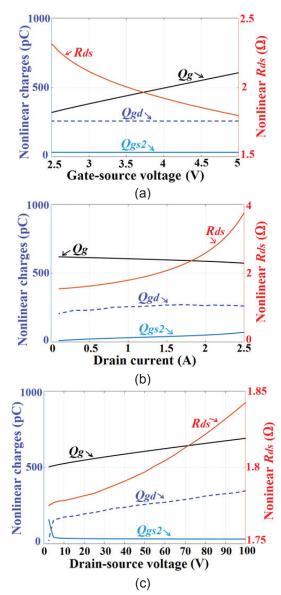

FOMs typically consist of trade-off parameters, e.g. on-resistance and gate charge (or specific parts of gate charge). These trade-off parameters depend on the specific operating conditions. Therefore, the values of the FOMs are fundamentally nonlinear, and application-dependent on voltage and current conditions. A systematic analysis is needed to optimize the nonlinear FOMs in order to fully explore the performance potentials of integrated power MOSFETs.

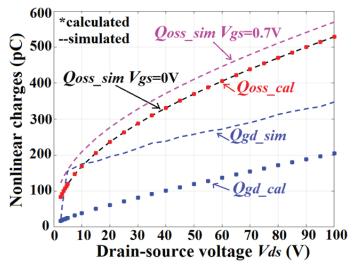

For the parameters on which FOMs are based, e.g. the gate charge and/or the output charge may be derived by calculating the integration of the parasitic capacitances as a function of an operating voltage such as the drain-source voltage  $V_{ds}$  [12], [119], [120]. In fact, the parasitic capacitances depend on not only the drain-source voltage  $V_{ds}$  but also the gate-source voltage  $V_{gs}$  [Appendix A.1]. Therefore, the calculated results, which take only one of the voltages as a variable for the calculation of the integration, tend to lead to errors.

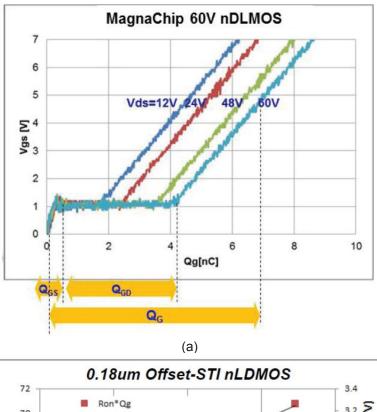

Fig. 2.4 Recent investigations of figure-of-merits (FOMs). The NFOM is defined as Normalized FOM in [43]. (a)  $Q_g$  depends on the applied  $V_{ds}$ . (b) Different trends of the FOM and the NFOM.

Capacitance values or resistance values cannot be used as standalone indicators for device-todevice comparisons [121]. A device with a higher capacitance value may switch faster than another device with a lower capacitance value [122]. A device with a higher on-resistance value may show a better overall efficiency for a converter, compared to another device with a lower on-resistance value [123]. In addition, a charge parameter may also not correctly reflect switching performances, e.g. the output charge of a device is more than 100 times lower than the output charge of another device, but it turns out that the output charge energies of these two devices are nearly the same [37]. There is no standard test circuit to obtain the gate charge parameters, and different configurations [124]-[134] are compared in this research work for choosing the most appropriate test circuit for the purpose of obtaining the FOMs.

$$\frac{A \cdot R_{on}}{V_B^2} = \frac{k}{\mu_n \cdot \varepsilon_s \cdot E_c^3} = \text{Semiconductor material}^* \text{ figure of merit (FOM)}$$

(2.1)

\*process specific for majority carrier devices, e.g. MOSFETs

A = device area

$R_{on} = switch on - resistance$

$V_B$  = device breakdown votlage

$\mu_n = electron mobility$

$\epsilon_s$  = semiconductor permittivity

$E_c = critical electric field (for avalanche breakdown)$

The semiconductor material FOM [135], as shown in (2.1), can be applied to majority carrier devices (e.g. MOSFETs) in different semiconductor technologies such as silicon (Si), Silicon Carbide (4H-SiC), Gallium Nitride (GaN), and the element semiconductor diamond (C) [136], [137]. There are two key points of this FOM. First, the wide band gap semiconductors SiC and GaN are superior to the conventional Si technology. This is fundamentally because the critical electric fields E<sub>c</sub> of SiC and GaN are about an order of magnitude higher than that of Si. As a result, the FOMs of SiC and GaN are theoretically about three orders of magnitude lower/better than that of Si. Second, this semiconductor material FOM reveals the fundamental theory underneath the common trade-offs such as the gate charge with the switch on-resistance, and the parasitic capacitances with the switch on-resistance. For a given semiconductor technology, the root performance-limiting factor is actually the device breakdown voltage  $V_{B}$ . The product of A·R<sub>on</sub> is proportional to the square of V<sub>B</sub>, i.e.  $(A \cdot R_{on}) \propto V_B^2$ . For example, if the device breakdown voltage  $V_B$  increases 10 times from 10 V to 100 V, the result is that the switch on-resistance  $R_{on}$ is increased 100 times for a given device area, or the device area (and the cost) is increased 100 times to keep the same on-resistance Ron. This is generally applicable regardless of switching frequencies and hard/soft switching technologies. Therefore, a strategical way of development is to use architectures and topologies that can reduce the voltage stresses of power semiconductors to fully enhance the performances of the devices.

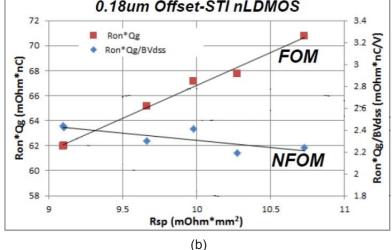

Fig. 2.5 Inspection work [123] [138] of research on resonant inverters and converters.

$$\eta \sim \frac{P_{out}}{V_{in}^2} \cdot \frac{1}{f_s}$$

(2.2)

$$f_{s,max} \propto \frac{P_{out}}{v_{in}^2} \tag{2.3}$$

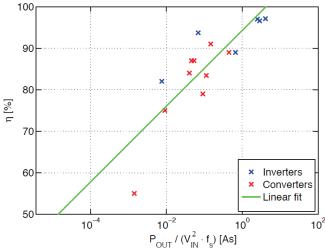

The challenge of the research project is not only about the high input voltage level, it is also about the combination of the high input voltage and the low output power, i.e. it is furthermore challenging for a high-voltage low-power converter design. It is interesting to mention the inspection work [123], [138] of previous research on resonant inverters and converters. It shows that there is a connection between the efficiency  $\eta$  and the ratio of  $P_{out}/V_{in}^2$ , as shown in Fig. 2.5. The efficiency  $\eta$  tends to get worse with the square of the input voltage, and it gets even worse for a low output power at a given high input voltage. This is also reflected in (2.2). As an example, the maximum switching frequency of a class-E inverter/amplifier for optimum-efficiency is proportional to the ratio of  $P_{out}/V_{in}^2$  in (2.3) [123]. Early research [139] in 1989 shows the same relationship. Therefore, from an efficiency perspective, the output power needs to track the input voltage, i.e. the constraints to achieve a high efficiency of a high-voltage high-power design or a low-voltage low-power design are generally smaller compared to a high-voltage low-power design.

#### 2.3 Topologies

This section has two parts, i.e. resonant converter topologies, and switched-capacitor topologies. The advanced topologies such as resonant-switched-capacitor topologies are considered as switched-capacitor related in this section.

#### 2.3.1 Resonant Converter topologies

State-of-the-art resonant converters and resonant gate drivers are summarized in Table 2.2.

| Topics                                                              | References                                     |

|---------------------------------------------------------------------|------------------------------------------------|

| Review of advances in resonant converters                           | [1], [3]                                       |

| Nonlinear parasitic capacitances/resistances of                     | [140]-[145]                                    |

| power switches impacts on resonant converters                       |                                                |

| Resonant converters use air core PCB inductors                      | [146]-[148]                                    |

| Class $\varphi_2$ /Class EF <sub>2</sub> based inverters/converters | [149]-[155]                                    |

| Resonant boost converters                                           | [103], [104], [156]-[158]                      |

| Resonant rectifier                                                  | [152], [160]-[163]                             |

| Matching network related                                            | [164], [165]                                   |

| Resonant SEPIC converters                                           | [166]-[168]                                    |

| Architectures of resonant converters                                | [169], [170]                                   |

| Conventional class E converters                                     | [123], [172]-[175]                             |

| Review of half-bridge resonant converts                             | [176], [177]                                   |

| Specific class DE inverters/converters                              | [102], [178]-[186]                             |

| Resonant gate drivers related                                       | [152]-[154], [156], [157], [166], [168]-[171], |

|                                                                     | [179], [187]-[197].                            |

Table 2.2 Resonant converter related topics and references.

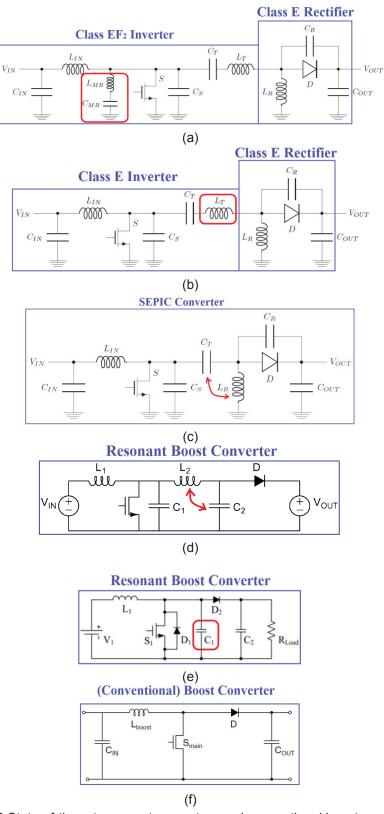

Fig. 2.6 State-of-the-art resonant converters and conventional boost converter.

(a) Class EF<sub>2</sub> inverter and Class E rectifier [167]. (b) Class E inverter and Class E rectifier [167].

(c) SEPIC converter [167]. (d) Resonant boost converter [157]. (e) Resonant boost converter [159]. (f) Conventional boost converter [1].

State-of-the-art resonant inverters/converters commonly use zero voltage switching (ZVS), or use ZVS with further zero dv/dt switching at the switches turn on transients to address the switching losses at the increased switching frequencies. Increase in switching frequency directly reduces the energy storage requirements of power converters [1], thus potentially enabling small passive components and fast transient response. As the switching frequency increases, a design strategy is to either utilize or compensate the parasitics of semiconductor devices. Topologies that absorb device parasitic capacitances as part of the operation are generally preferred. Note that the absorption of the parasitic capacitances is only applicable to the extent that device package inductances are not large and can be ignored [157]. The interconnection inductances of packages and PCB become increasingly contributing to the element impedance as switching frequencies increase. Therefore, topologies that can also absorb device parasitic inductances are further desirable. Several state-of-the-art resonant converter topologies are compared in Fig. 2.6. These topologies are described from a topology derivation point of view.

In Fig. 2.6 (a), class  $\varphi_2/EF_2$  inverters use low-order lumped network to shape the drain-source voltage waveform to a quasi-trapezoidal voltage waveform across the switch, which aims to lower the peak drain-source voltage value, i.e. lower the voltage stress of the switch. This is achieved by tuning the input impedance of the low-order lumped network to have low impedance at the second harmonic and high impedances at the fundamental and the third harmonic of the switching frequency [150], [151]. Class  $\varphi_2/EF_2$  inverters are simplified variants of the class  $\varphi/EF$  inverters that use high-order lumped network.

By removing the  $L_{MR}$  and  $C_{MR}$  in Fig. 2.6 (a), a conventional class E inverter is retrieved in Fig. 2.6 (b). Class E inverters are commonly used but have two main drawbacks. First, class E inverters need large valued (choke) input inductors, which also slow down the setting time of the inverters to the operating points. Second, for the idealized operation of class E inverters with ideal switches at 50 % duty cycle, the peak switch voltage stress is about 3.6 times the input voltage [150], [151]. In practice, the nonlinearities of the device parasitic capacitances have to be taken into account, which further increase the switch voltage stress to about 4-4.4 times the input voltage [150], [151], [153], [154]. By removing the L<sub>r</sub> in Fig. 2.6 (b), a SEPIC (Single-Ended Primary Inductor Converter) converter is derived, as shown in Fig. 2.6 (c). The SEPIC converter topology is tightly close to a class E inverter cascaded with a class E converters [166]-[168]. In other words, SEPIC converters do not reduce peak switch voltage stresses as compared to class E converters.

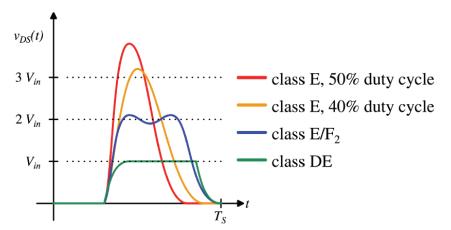

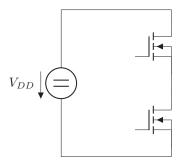

By interchanging the matching network components of  $C_r$  and  $L_R$  in Fig. 2.6 (c), a resonant boost converter [157] is obtained in Fig. 2.6 (d). Note that in the resonant boost converter, a portion of the power is transferred directly from the input to the output [157], but it shows that the resonant boost converter still suffers from the peak switch voltage stresses about 3.3-3.7 times the input voltage. By replacing the  $L_2$  with the diode D in Fig. 2.6 (d), another resonant boost converter [159] is derived in Fig. 2.6 (e). The resonant boost converter in Fig. 2.6 (e) can also be obtained by adding a capacitor in parallel with the switch of the conventional boost converter [1], [100] that is shown in Fig. 2.6 (f). For both converters in Fig. 2.6 (e) and (f), the rectifier diode transfers the energy stored in the inductor directly to the output [159]. Therefore, the peak switch voltage stresses of these two converters closely track the output voltages. All the above topologies use (single) ground-referenced switches, which are generally preferred at very high frequencies [1]. Switches that are referenced to switching nodes add challenges of driving circuits to provide desired gate drive waveforms with nonlinear parasitic capacitances tied to the switching nodes. However, a half-bridge class DE converter (class DE converter topologies will be discussed in details in the section 4.4) reduces the peak switch voltage stress to the level of the input voltage. This is a major advantage for high voltage resonant converters, e.g. off-line power converters. The general comparison of the voltage stresses on switches of different resonant converters is summarized in Fig. 2.7. In addition to the resonant inverter/converter topologies that strive to trapezoidal wave-shaping the drain-source voltage of switches, trapezoidal wave-shaping the gate-source voltage of switches also shows better performances for resonant gate drives (e.g. [187]) compared to the conventional sinusoidal or hard-switched gate drives.

Fig. 2.7 General comparison of voltage stresses of switches in resonant topologies [3], [195]. In practice, nonlinear parasitic capacitances add further voltage stresses on switches, e.g. about 4-4.4 times the input voltage for class E inverters [150], [151], [153], [154].

There are only four cases of on-chip implemented resonant converters in [140]-[197] and the four cases are summarized in Table 2.3. The case 1 [175], the case 2 [184], and the case 3 [185] are simulation results only. The case 4 [186] is implemented in a 130 nm 1.2 V CMOS process with an on-chip spiral inductor and an on-chip MIM capacitor. However, its output power is very low up to 11.6 mW. The development of on-chip resonant converters is still in its infancy, and high voltage ones are further challenging.

| Case               | 1 [175]    | 2 [184]       | 3 [185]    | 4 [1      | 86]         |

|--------------------|------------|---------------|------------|-----------|-------------|

| Topology           | Class E    | Class DE      | Class DE   | Class     | B DE        |

| Inverter/Converter | Converter  | Inverter Only | Converter  | Inverte   | r Only      |

| Input Voltage      | 5 V        | 2 V           | 2 V        | 1.2       | V           |

| Output Voltage     | 4.5 V      | 0.32 V        | 0.5 V      | 0. 585 V  | 0.312 V     |

| Output Power       | 200 mW     | 12.5 mW       | 12.5 mW    | 6.9 mW    | 11.6 mW     |

| Efficiency         | 72 %       | 48 %          | N/A        | 65.2 %    | 47 %        |

| Comments           | Simulation | Simulation    | Simulation | Measureme | ent Results |

|                    | Only       | Only          | Only       |           |             |

Table 2.3 Only 4 cases of on-chip integrated resonant converters in [140]-[197].

#### 2.3.2 Switched-Capacitor topologies

With the high-voltage challenge in mind, the on-chip capacitor technologies are reviewed [5], [9], [50] and summarized in Table 2.4. The capacitance densities of these technologies decrease from deep trench capacitors, MOS capacitors, MIM capacitors, to MOM capacitors. For high-voltage integrated converter designs that interface voltages above 48 V, the MOM technology is the only practical choice. However, by comparing the deep trench technology (assume 300 nF/mm<sup>2</sup>) and the MOM technology (assume 0.3 nF/mm<sup>2</sup>), there is three orders of magnitude difference between the capacitance densities. For the same capacitance that is needed, the capacitor size of a high-voltage design is 1000 times larger than the capacitor size of a low-voltage design. Naturally, the power density of a high-voltage converter design is dramatically lower than that of a low-voltage converter design, if the size of the high-voltage converter is at all acceptable considering that the cost is generally proportional to the chip area. For an intuitive example, if a capacitor with a capacitance value of 3 nF is implemented with the deep trench technology and the MOM technology, respectively, then a 1.5 V, 3 nF deep trench capacitor occupies 0.01 mm<sup>2</sup>, whereas a 100 V, 3 nF MOM capacitor would consume 10 mm<sup>2</sup>. A chip area of 10 mm<sup>2</sup> for a single capacitor that is 1000 times larger than a deep trench capacitor with the same capacitance is generally not acceptable. Therefore, other approaches are needed for the high-voltage switched-capacitor converters in the chapter 5.

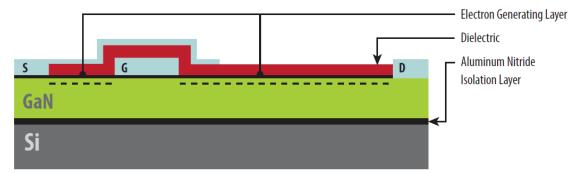

The general comparison of semiconductor technologies is summarized in Table 2.5. It is seen that the emerging wide band gap semiconductors GaN and SiC are superior to the conventional Si technology in the voltage range of hundreds of volts. Therefore, GaN and SiC are of the great considerations to be used for converter designs of this research.

| IC Capacitor | Capacitance Density                             | Examples    |

|--------------|-------------------------------------------------|-------------|

| Deep Trench  | 100~300* nF/mm <sup>2</sup> =fF/µm <sup>2</sup> | ~1.5 V [9]  |

| MOS          | ~10 nF/mm <sup>2</sup> =fF/µm <sup>2</sup>      | ~1.8 V/ 5 V |

| MIM          | 1~3 nF/mm <sup>2</sup> =fF/µm <sup>2</sup>      | ~5 V        |

| MOM          | 0.2~1 nF/mm <sup>2</sup> =fF/µm <sup>2</sup>    | ~5-50 V     |

|              | (decrease with voltage)                         |             |

Table 2.4 On-chip capacitor technologies are generally not for high voltage designs above 48 V.

\*500~1000 nF/mm<sup>2</sup> in research, e.g. [50] MOS=Metal-Oxide-Semiconductor MIM=Metal-Isolator-Metal MOM=Metal-Oxide-Metal

|              | Туре 1           | Туре 2        | Туре 3  | Туре 4        |

|--------------|------------------|---------------|---------|---------------|

| Voltage      | < ~30 V          | ~30 V - 600 V | > 600 V | < 200 V       |

| III-V vs. IV | GaAs             | GaN           | SiC     | Si-based      |

| Frequency    | High (> 100 MHz) | Medium        | Low*    | Low (< 1 MHz) |

| Body Diode   | No               | No            | Yes     | Yes           |

\*Compare with Si: lower Electron Mobility, but higher Electron Saturation Velocity

Switched-capacitor circuits have been known and used for long time. Historically, there were up and down periods for the development of switched-capacitor circuits. Many switched-capacitor circuits were rediscovered and revisited, including state-of-the-art advances. In 1873, J. C. Maxwell published the effects of regularly switched condenser (a former name of capacitor) [198]. Research on switched-capacitor converters already commenced since 1930s by Cockcroft and Walton [199]. In 1976, Dickson published switched-capacitor converters for memory applications on IC (Integrated Circuit) [200]. The topology is nowadays known as Dickson converter. It is noted that the Dickson converter has an equivalent circuit to the classical Cockcroft-Walton multiplier, where the capacitors are in parallel instead of in series. The drawback of this converter is that the capacitors have to withstand voltages that are developed along the diode chain. This may not be an issue for on-chip capacitors, because the MOM capacitors can be customized for different voltage ratings, as previously shown Table 2.4. The most important contribution of this work is that efficient multiplication of the switchedcapacitor converter is achieved with relatively high on-chip parasitic capacitances. This facilitates the development of on-chip switched-capacitor converters, and the Dickson topology developed in 1970s is still commonly used for state-of-the-art research.

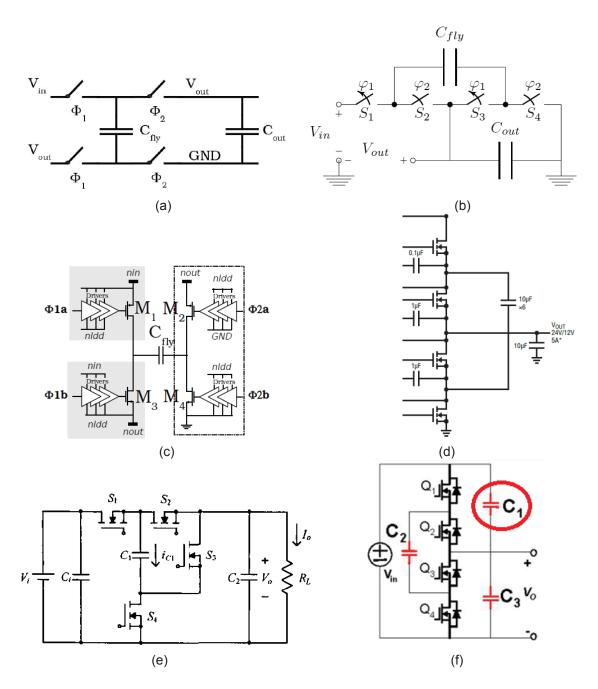

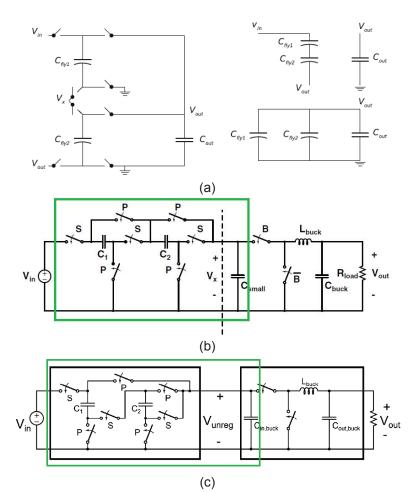

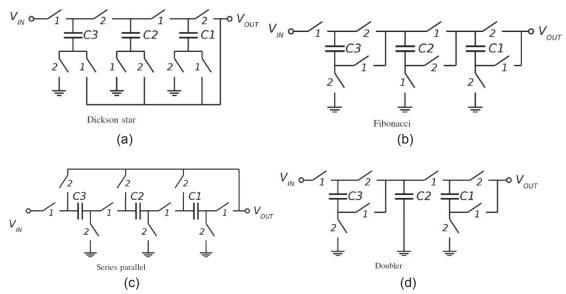

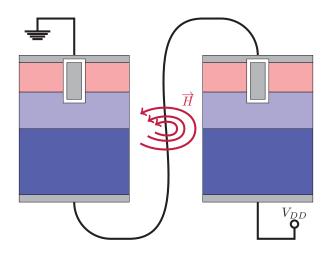

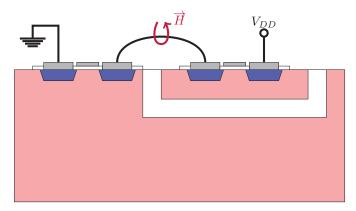

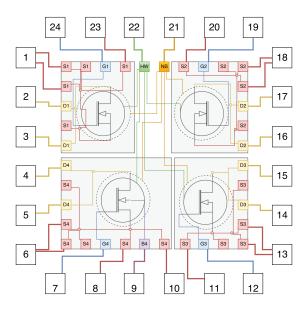

The examples of previously published switched-capacitor converters of 2:1 conversion ratio are summarized in Fig. 2.8. In fact, all the topologies are the same, but they are drawn differently. Similarly, several previously published switched-capacitor converters of 3:1 conversion ratio are shown in Fig. 2.9. These topologies are actually the same and just appear differently. The switched-capacitor converter topologies of 4:1 or 5:1 conversion ratio such as Dickson, Fibonacci, Series-Parallel, and Doubler are summarized in Fig. 2.10. It should be noted that all the above topologies when simplified at 2:1 conversion ratio are actually identical [213], [214].

Previous research on switched-capacitor DC-DC converters has focused on low-voltage and/or high-power applications, compared to the high-voltage and low-power requirements. State-of-the-art on-chip switched-capacitor DC-DC converters either have low input voltages ( $\leq 12$  V) or have low output powers ( $\leq 2$  W) [5]-[9]. To be simultaneously above both practical limits, switched-capacitor converters are commonly implemented with discrete components by industry [204] and academia [206]-[207]. Recent advances in switched-capacitor DC-DC power converters are up to a 200 V input voltage with output powers of 30-53 W [2],[215]. These state-of-the-art high-voltage switched-capacitor converters are summarized in Table 2.6.

|                  | Case 1   | Case 2  |

|------------------|----------|---------|

| Year             | 2015     | 2015    |

| Reference        | [2]      | [215]   |

| Conversion ratio | 2:1      | 8:1     |

| Input Voltage    | 200 Vdc  | 200 Vdc |

| Output Power     | 30 W     | 53 W    |

| Impedance level  | ≈ 1333 Ω | ≈ 755 Ω |

| Normalized       | 1.8x     | 1x      |

| Impedance level  |          |         |

Table 2.6 State-of-the-art high-voltage switched-capacitor converters.

Fig 2.8 Switched-capacitor converters of 2:1 conversion ratio. All topologies are the same, but drawn differently. (a) 2011 [5], [201]. (b) 2016 [202]. (c) 2011 [203]. (d) 2017 [204]. (e) 2004 [205]. (f) 2006-2007 [206]-[209].

Fig. 2.9 Switched-capacitor converters of 3:1 conversion ratio. All topologies are the same, but drawn differently. (a) 2013 [106]. (b) 2008 [210]. (c) 2011-2012 [7], [211].

Fig. 2.10 Switched-capacitor converters of 4:1 or 5:1 conversion ratio. [212]. All topologies at 2:1 conversion ratio are actually identical [213], [214]. (a) Dickson 4:1. (b) Fibonacci 5:1. (c) Series-Parallel 4:1. (d) Doubler 4:1.

Fig. 2.11 Recent research work on loss analysis of switched-capacitor converters. Summary by the author.

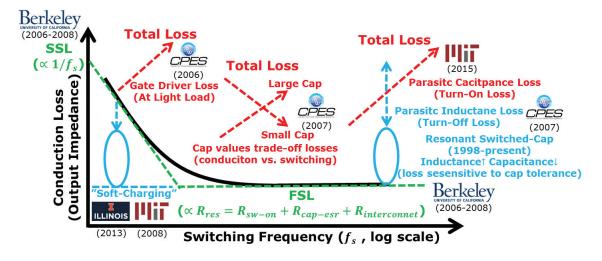

The loss analyses of switched-capacitor converters of the previous research work [2], [7], [205]-[211], [213]-[215] are summarized in Fig. 2.11. The conventional loss modelling of switchedcapacitor converters, i.e. the SSL (slow switching limit) and the FSL (fast switching limit) [213]-[214] focuses only on conduction loss. The analysis of solely conduction loss is not adequate for switched-capacitor converters at high-voltage levels [2], where the switching loss related to charging/discharging the output capacitances of the switches becomes significant, compared to the charge transfer loss related to charging/discharging the energy transfer capacitors. At lowpower levels, other switching losses such as gate driver losses and losses caused by parasitic inductances also heavily affect the total loss of the switched-capacitor converters [206]-[209]. There are two research trends, i.e. the soft-charging technologies [7], [210], [211], [215] that attempt to reduce capacitor charging/discharging loss, and the resonant switched-capacitor technologies [16]-[22], [205], [216]-[229] that try to reduce switch turn-on/turn-off loss. There are similar mechanisms behind these two technologies, and further merging of the two may lead to advanced topologies. Nevertheless, at high-voltage low-power levels, the design challenges are not the same as low-voltage designs. High efficiency and high power density implementation remains a challenge. Switched-capacitor converters at high characteristic impedance levels (high-voltage and low-current) that are significantly higher than those of other state-of-the-art high-voltage switched-capacitor converters are to be demonstrated in this research wok for potential applications such as LED drivers that are compatible with AC mains.

# 3. Integrated Power MOSFETs

This chapter summarizes the first aspect of this research work regarding on-chip integrated high voltage power MOSFETs. In section 3.1, the intrinsic nonlinearities of the parasitic capacitances of high voltage power MOSFETs in a SOI process are analysed by a proposed modelling method. In section 3.2, the additional impacts of the parasitic capacitive coupling of on-chip interconnections and layout structures are analysed. In section 3.3, the nonlinearities of the gate charges and the related figure-of-merits (FOMs) are analysed. In section 3.4, the parasitic considerations of packages are qualitatively discussed. In section 3.5, the parasitic considerations of PCB layout are briefly summarized. This chapter focuses on the research on components level that includes device, layout, package, and PCB.

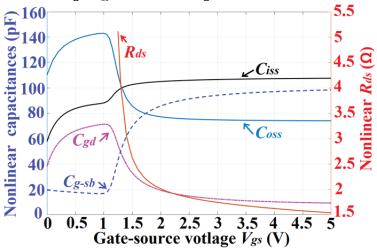

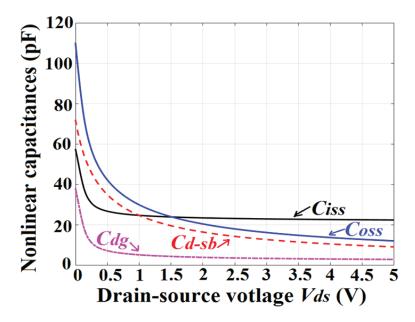

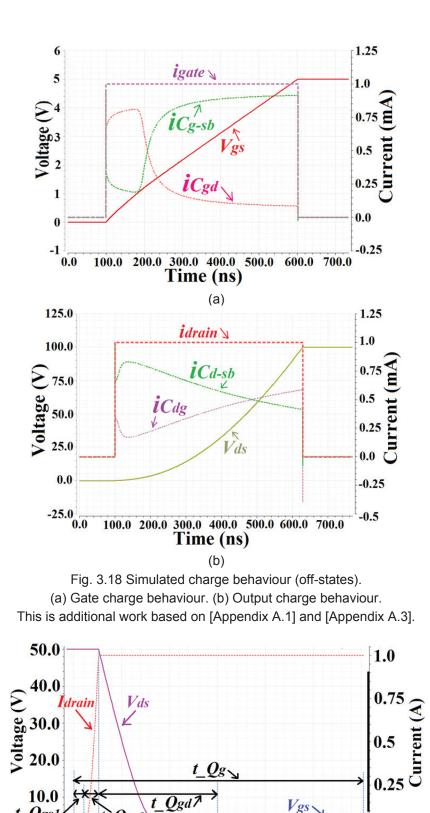

#### 3.1 On-chip Nonlinear Parasitic Capacitance Modelling

In this section, a modelling method is presented to systematically analyze the nonlinear parasitic capacitances of power switches versus different bias voltages. The modelling method is originally proposed for integrated power MOSFETs in a Silicon-on-Insulator (SOI) process, but the principle is general and can be applied to other integrated circuit processes. The existing ways of characterizing the off-state capacitances can be extended by the proposed modelling method that covers all the related operation states: off-state, sub-threshold region, and on-state in the linear region.

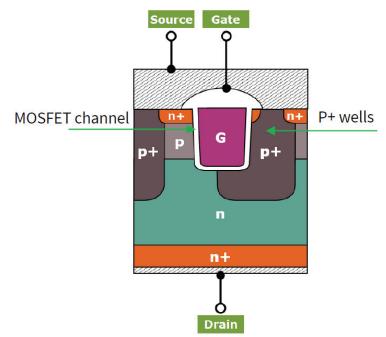

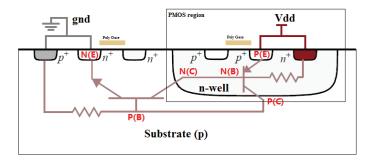

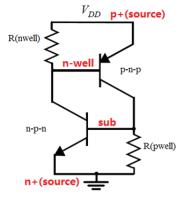

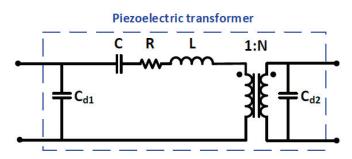

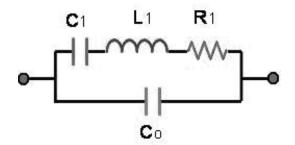

High voltage power MOSFETs do not have the relatively simple structures as low voltage MOSFETs, e.g. those in general Complementary Metal-Oxide-Semiconductor (CMOS) processes. Despite that on-chip integrated lateral devices are researched in this work, most of the high voltage power MOSFETs are discrete and vertical devices. High voltage power MOSFETs normally have cellular structures that are composed of parallel connected unit cells [109], [110]. The purpose of the parallelization is to reduce the on-state resistance, not only in nominal operation conditions, but also over high temperatures and low overdriving conditions. The parasitic capacitive coupling effects of the on-chip interconnections and layout structure impacts are discussed in the next section. In addition, the integration of high voltage power MOSFETs is favourable in a SOI process. The name Silicon-on-Insulator does not only mean dielectric isolation in the vertical direction, but also it consists of dielectric isolation in the horizontal direction. The isolation in the vertical direction is achieved with the buried oxide, and the isolation in the horizontal direction is achieved with the Deep Trench Isolation (DTI) and the Shallow Trench Isolation (STI). In this way, it is feasible to integrate high voltage power MOSFETs that operate at different voltage domains. For high voltage operations, the electric field should be properly distributed and the fringing electric field should also be properly terminated, thus handle wafer contacts (connecting different wells and the handle wafer) are needed through the buried oxide, namely a partial SOI process.

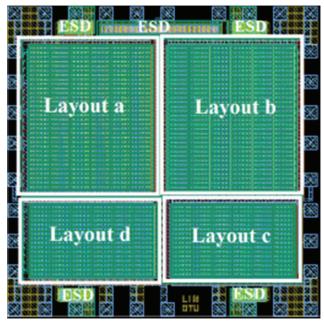

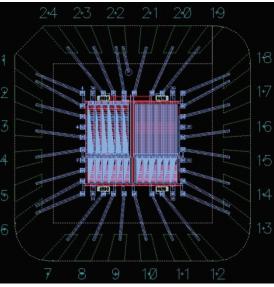

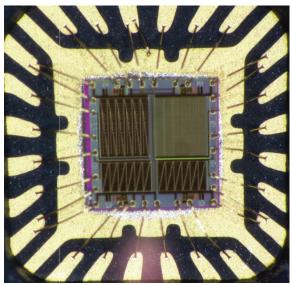

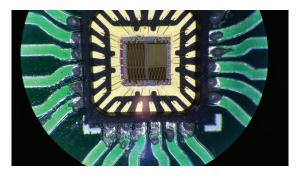

A high voltage power MOSFET is firstly designed in a 0.18  $\mu$ m partial SOI process, and its nonlinear parasitic capacitances are analyzed. The power MOSFET is dielectrically isolated from other MOSFETs and circuits with a full three-dimensional isolation that is form with the combination of the SOI wafer and the deep trench isolation, as previously discussed. It has electrical properties shown in Table 3.1.

692 µm

≻

|       | N I REPRESENTATION ADDRESS ADDRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

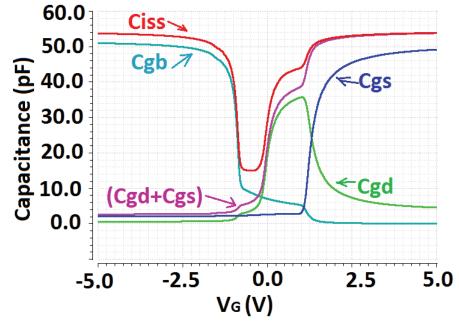

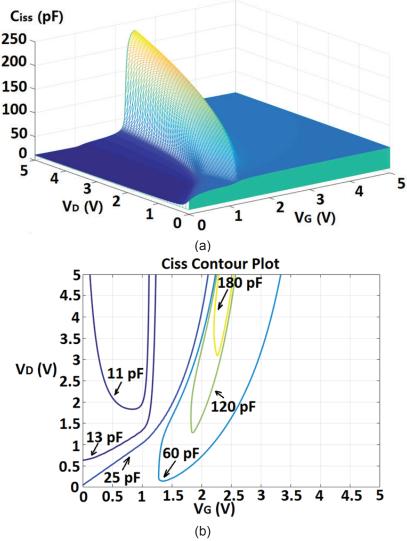

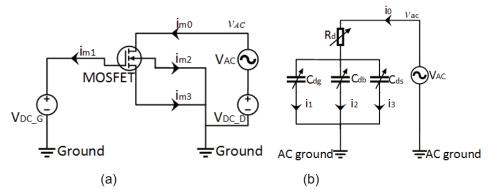

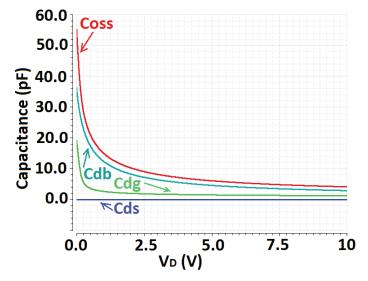

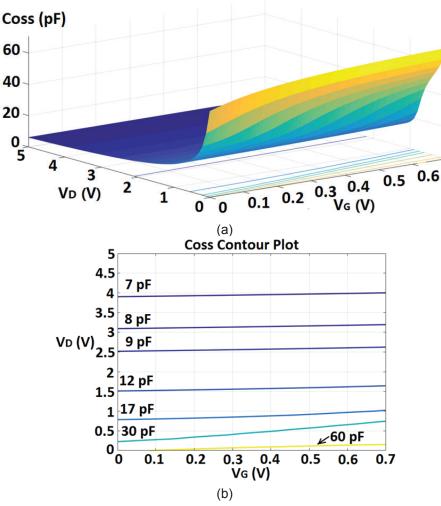

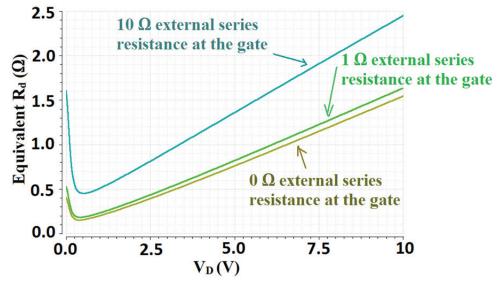

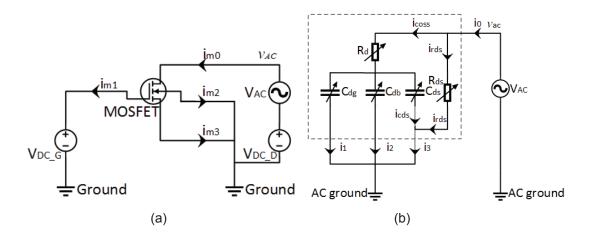

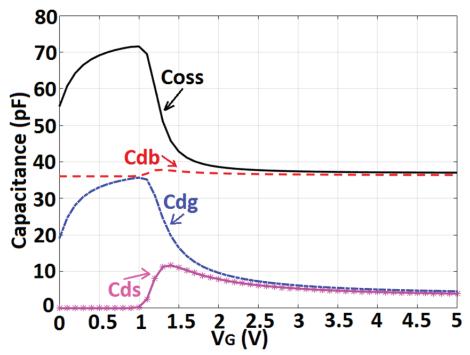

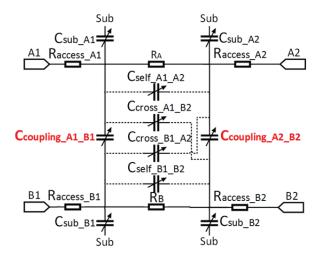

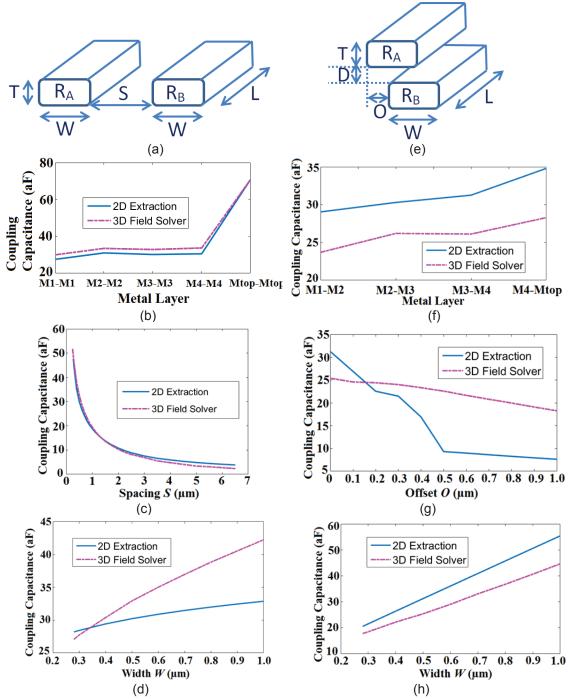

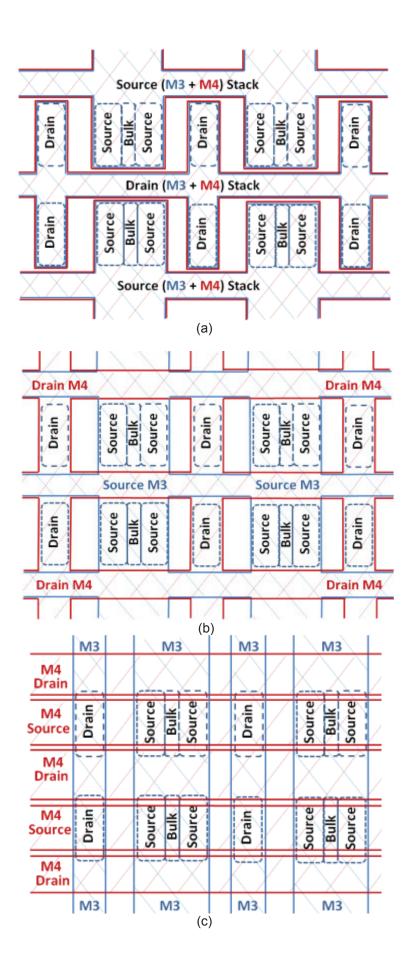

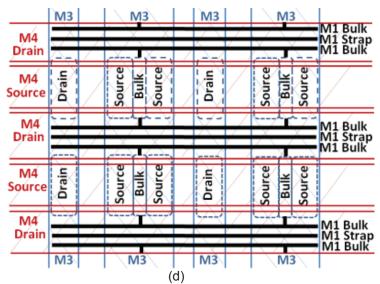

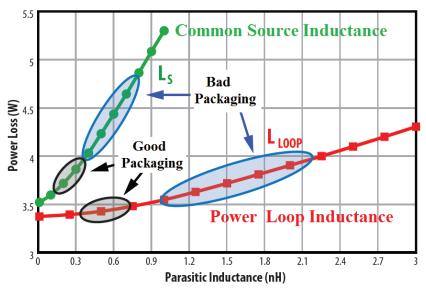

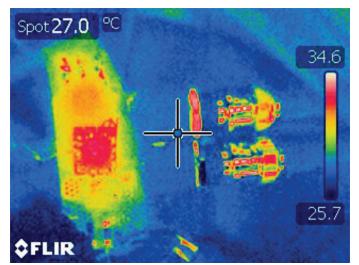

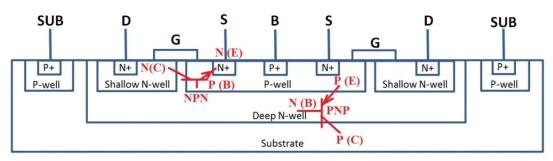

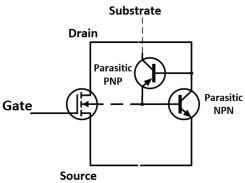

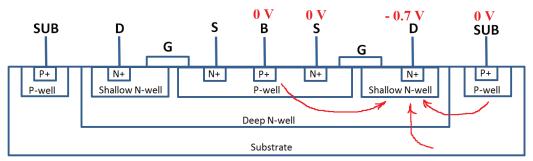

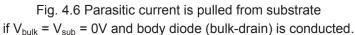

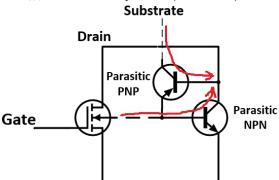

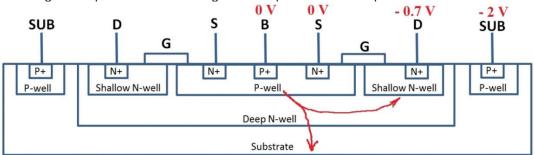

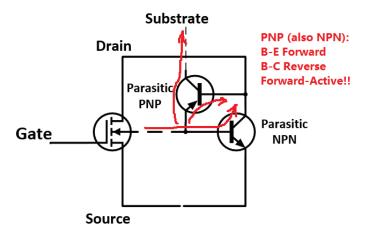

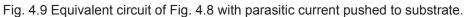

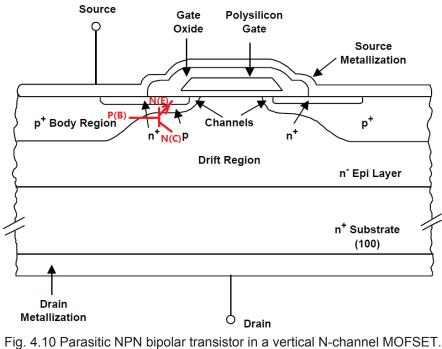

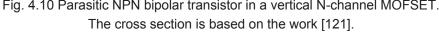

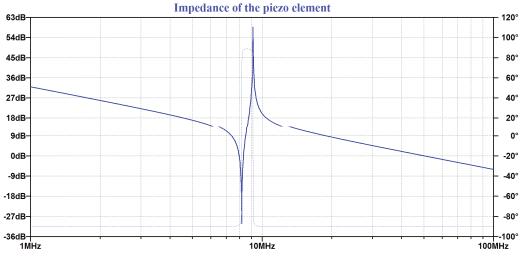

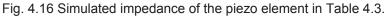

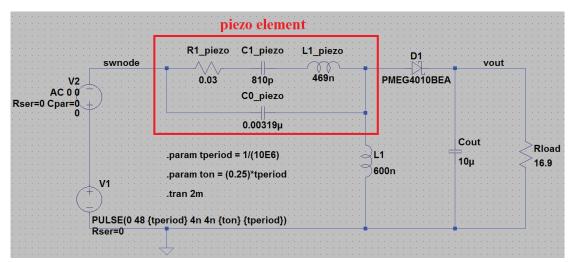

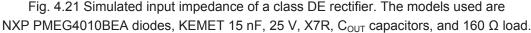

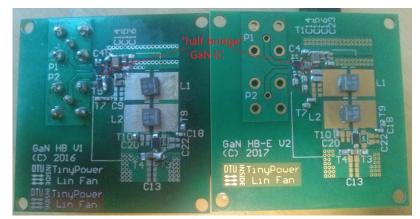

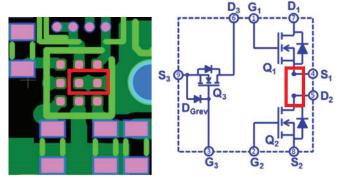

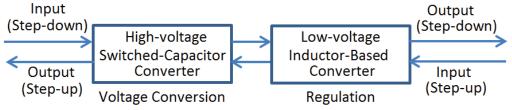

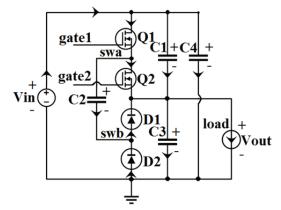

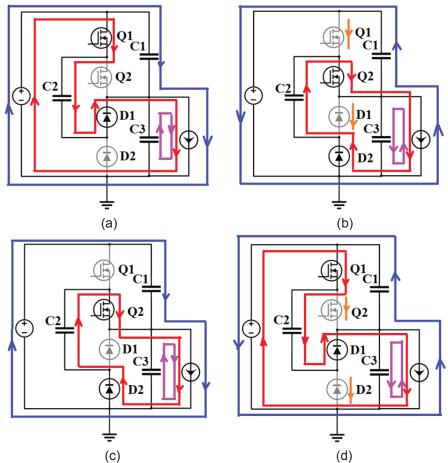

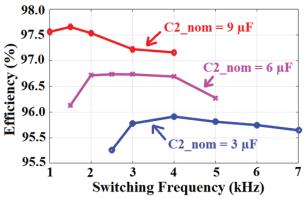

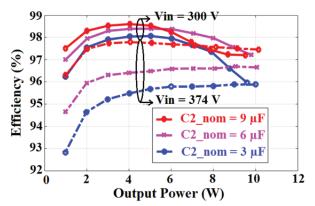

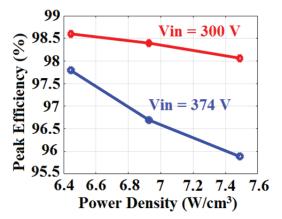

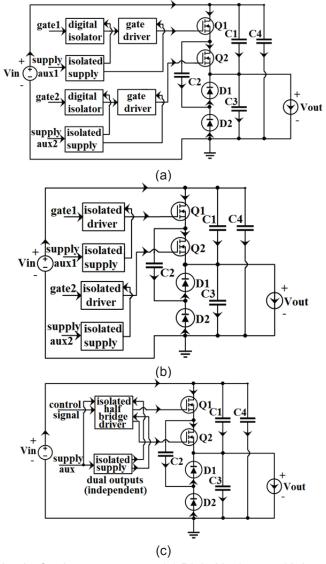

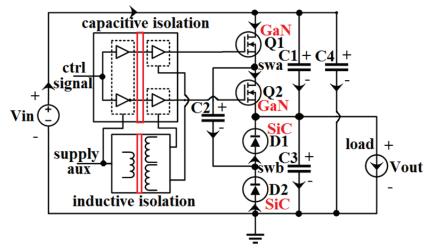

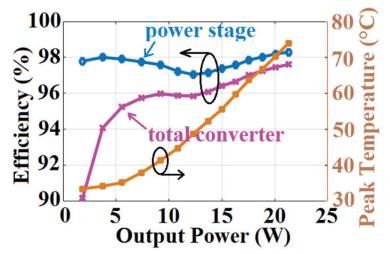

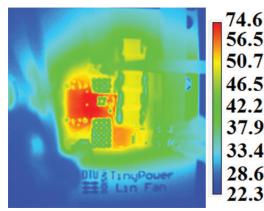

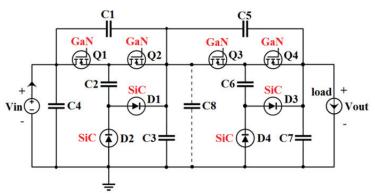

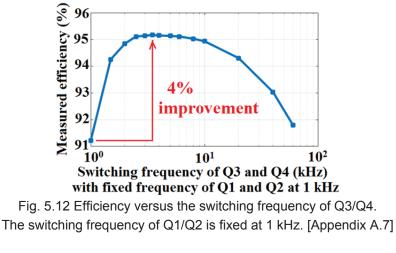

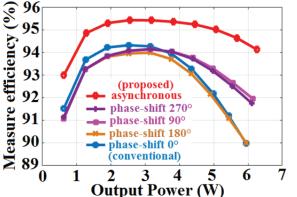

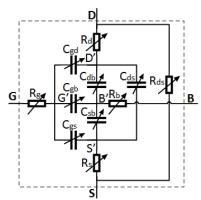

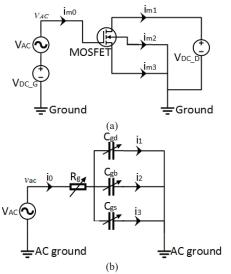

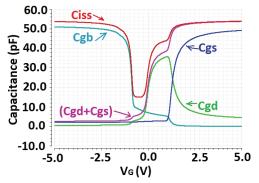

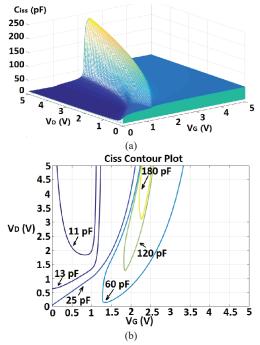

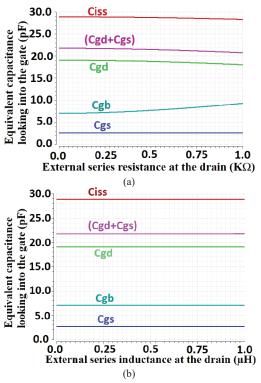

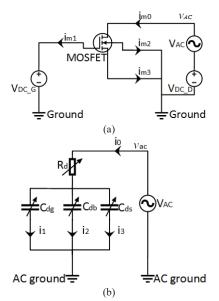

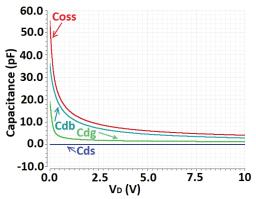

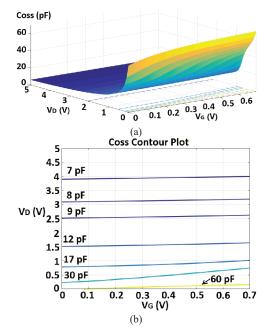

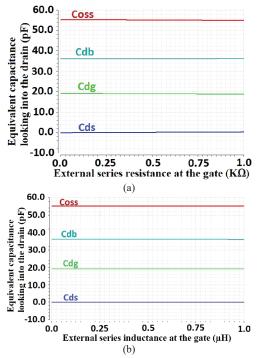

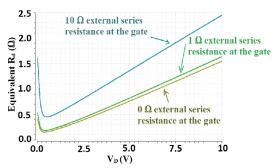

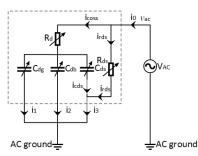

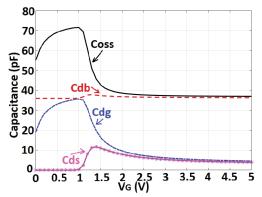

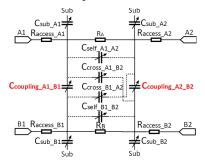

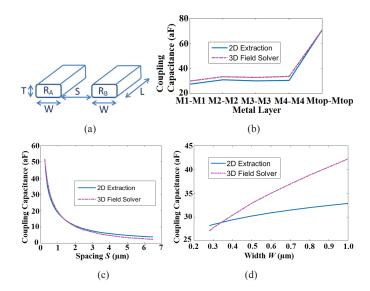

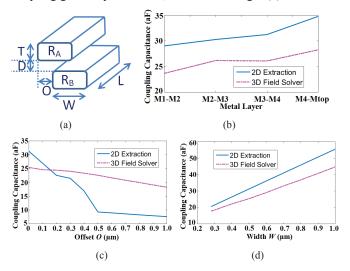

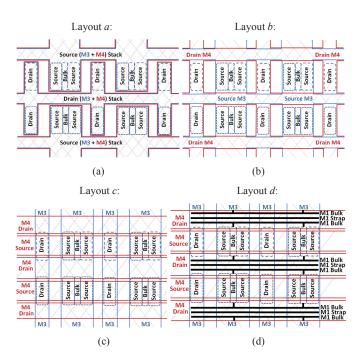

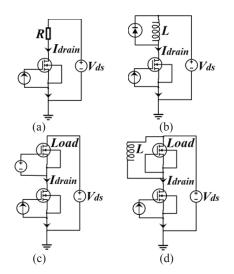

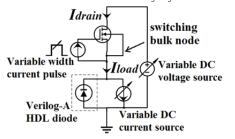

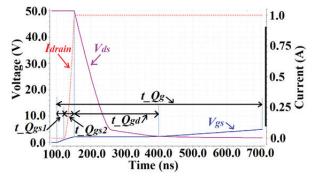

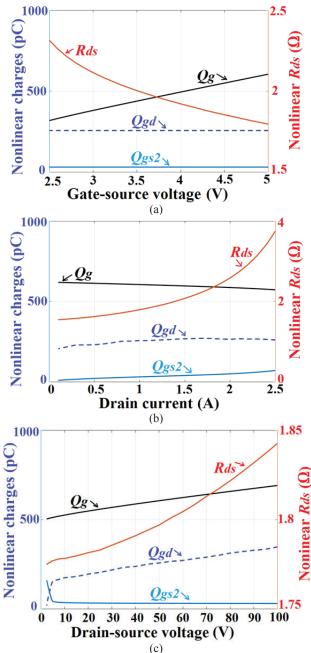

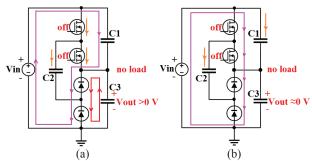

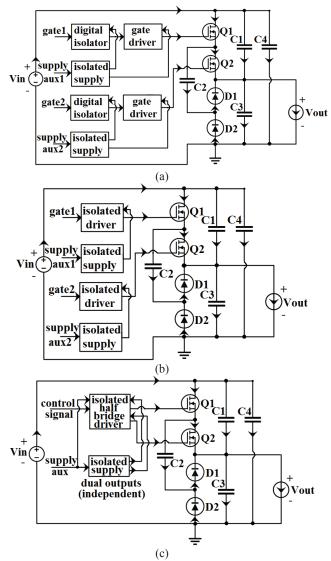

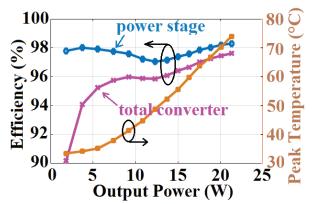

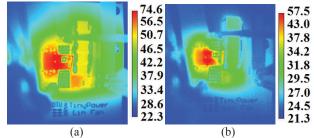

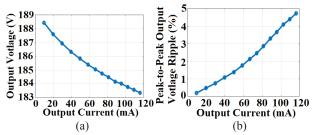

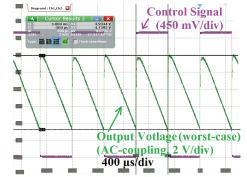

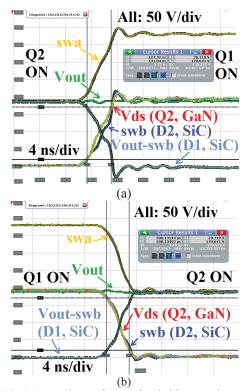

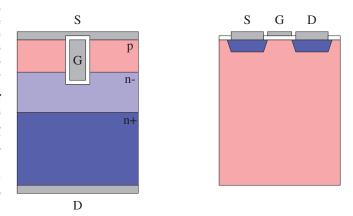

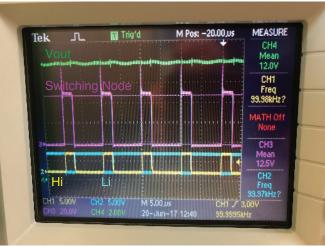

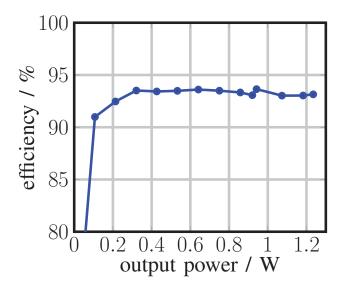

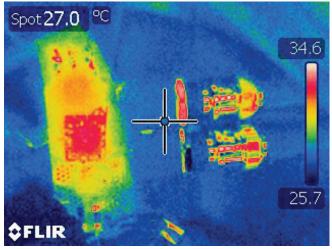

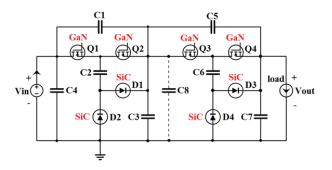

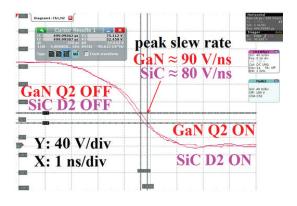

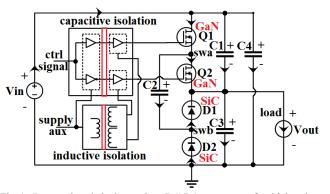

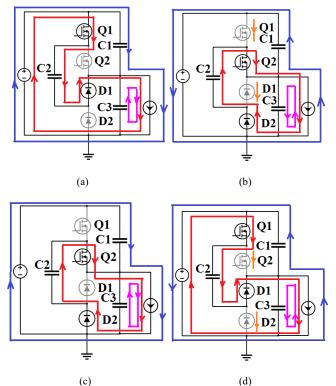

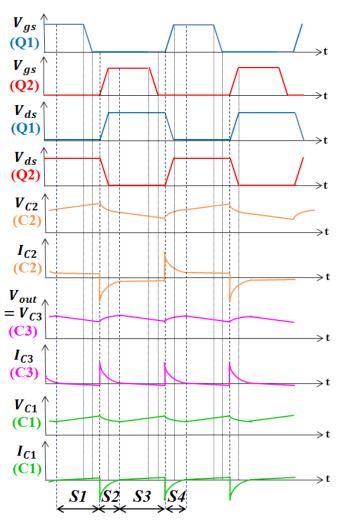

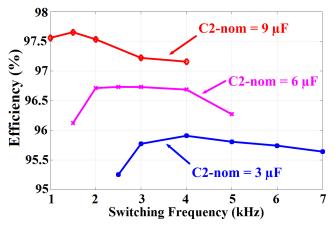

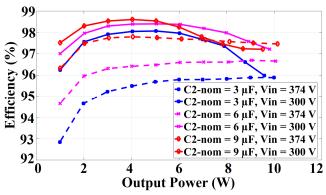

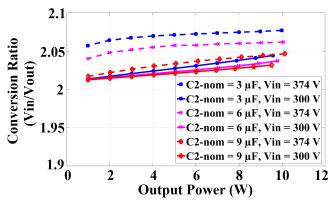

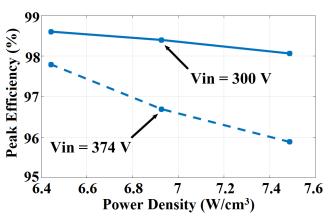

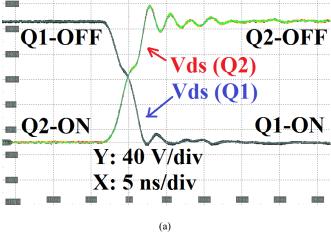

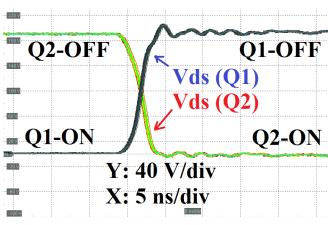

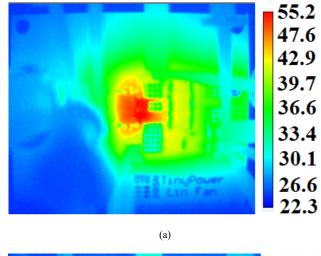

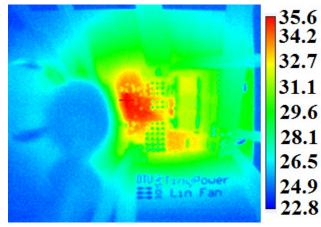

|       | UNIVERSITY AND A A A A A A A A A A A A A A A A A A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |