### **Tesis doctoral**

Evaluación y análisis de una aproximación a la fusión sensorial neuronal mediante el uso de sensores pulsantes de visión / audio y redes neuronales de convolución.

José Antonio Ríos Navarro Sevilla, Mayo de 2017

## Departamento de Arquitectura y Tecnología de Computadores Escuela Técnica Superior de Ingeniería Informática Universidad de Sevilla

Evaluación y análisis de una aproximación a la fusión sensorial neuronal mediante el uso de sensores pulsantes de visión / audio y redes neuronales de convolución.

por José Antonio Ríos Navarro

PROPUESTA DE TESIS DOCTORAL

PARA LA OBTENCIÓN DEL GRADO DE

DOCTOR INGENIERO EN INFORMÁTICA

SEVILLA, MAYO DE 2017

#### Directores:

Dr. Alejandro Linares Barranco Dr. Gabriel Jiménez Moreno Dr. Ángel Jiménez Fernández

#### UNIVERSIDAD DE SEVILLA

Memoria presentada para optar al grado de Doctor Ingeniero en Informática por la Universidad de Sevilla.

Autor: José Antonio Ríos Navarro

Título: Evaluación y análisis de una aproximación a la fusión sensorial neuronal mediante el uso de sensores pulsantes de visión/audio y redes neuronales de convolución.

Departamento: Arquitectura y Tecnología de Computadores Vº Bº Directores Dr. Alejandro Linares Barranco Profesor Titular de Universidad Dr. Gabriel Jiménez Moreno Profesor Titular de Universidad Dr. Ángel Jiménez Fernández Profesor Interino Contratado Doctor El autor

José Antonio Ríos Navarro

Ingeniero Técnico en Informática de Sistema

## Agradecimientos

Este trabajo no hubiese sido posible sin la implicación, colaboración y apoyo de muchas personas, por lo que me gustaría que estas líneas sirvan para agradecerles su motivación y orientación en el desarrollo del trabajo presentado en esta tesis. En especial me gustaría hacer llegar mi más sincero y profundo agradecimiento a:

- Mi familia, que ha tenido que lidiar con todos los malos momentos, agradezco su continuo apoyo y constancia, sin los cuales no hubiera tenido la fuerza para terminar este reto. Gracias por la educación que me habéis prestado, con la cual he podido llegar donde ahora mismo me encuentro. En especial a mis padres, que desde muy pequeño me han inculcado ese espíritu de ser constante y no conformista, necesarios en el trabajo, para conseguir los objetivos. A ellos va dedicado este trabajo.

- A mis directores de tesis, Alejandro, Gabriel y Ángel, pues son los que me han guiado en todo momento y han dedicado incontables horas en aconsejarme y guiarme en los problemas encontrados en la elaboración de esta tesis, además de haber sido un pilar fundamental en mi formación científica e investigadora.

- A todos los miembros del departamento de Arquitectura y Tecnología de computadores, de los que he aprendido mucho y con lo que he disfrutado tanto trabajando como en momentos inolvidables de ocio. En especial a ese núcleo joven, Juan Pedro, Ricardo, Daniel, Ángel, Manu y Elena, por su contagiosa ilusión y ganar de trabajar.

- De manera particular, se merece un párrafo uno de mis directores de tesis, Alejandro, que me abrió las puertas de esta gran familia y siempre ha confiado y creído en mí.

- A mis amigos más próximos, cuyo apoyo y ánimo me ha ayudado a seguir adelante en la realización de este trabajo.

A todos aquellos que no han sido nombrados expresamente en los párrafos anteriores y que siempre han estado ahí, gracias.

# Índice de Contenido

| Agradecimientos                                   | i    |

|---------------------------------------------------|------|

| Índice de Contenido                               | iii  |

| Índice de Figuras                                 | vii  |

| Índice de Ecuaciones                              | xi   |

| Índice de Tablas                                  | xiii |

| Resumen                                           | 1    |

| Abstract                                          | 3    |

| I. Introducción                                   | 5    |

| I.1 Motivación                                    | 6    |

| I.2 Ingeniería neuromórfica                       | 8    |

| I.2.1 Inicios y evolución                         | 9    |

| I.2.2 Sistemas neuro-inspirados                   | 10   |

| I.2.3 Address-Event-Representation                | 14   |

| I.3 Visión artificial                             | 17   |

| I.3.1 Adquisición de una imagen digital           | 19   |

| I.3.2 La retina de silicio                        | 21   |

| I.4 Procesamiento de audio. El habla              | 24   |

| I.4.1 Conversión analógico-digital                | 26   |

| I.4.2 Sistemas de audio neuromórficos             | 28   |

| I.5 Redes neuronales de aprendizaje profundo      | 32   |

| I.5.1 Breve historia sobre DNN y sus aplicaciones | 32   |

| I.6 Estructura de la tesis                        | 34   |

| II. Objetivos                                     | 35   |

| III. Visión con computación paralela              | 37   |

| III.1 Capas de procesado de una CNN               | 38   |

| III.2.1 Capa de convolución                                   | 38  |

|---------------------------------------------------------------|-----|

| III.2.2 Capa de pooling                                       | 39  |

| III.2.3 Capa dropout                                          | 40  |

| III.2.4 Capa fully-conected                                   | 41  |

| III.1 OpenCL                                                  | 41  |

| III.1.1 Modelo de plataforma                                  | 41  |

| III.1.2 Modelo de memoria                                     | 42  |

| III.1.2 Modelos de ejecución                                  | 44  |

| III.2 Implementación de CNN utilizando OpenCL                 | 46  |

| III.2.1 Optimización de los kernels y ejecución la aplicación | 48  |

| III.2.3 Resultados                                            | 49  |

| III.3 Aceleradores de CNN (NullHop)                           | 50  |

| III.3.1 NullHop                                               | 51  |

| III.3.2 Implementación del NullHop en SoC                     | 57  |

| III.3.3 Resultados                                            | 61  |

| IV. Integración sensorial                                     | 73  |

| IV.1 Tipos de integración sensorial                           | 74  |

| IV.2 Clasificación auditiva                                   | 75  |

| IV.3 Aplicación práctica y resultados experimentales          | 81  |

| V. Fusión sensorial                                           | 87  |

| V.1 Generación de los datos de entrada                        | 88  |

| V.1.1 Generación de datos del DVS128                          | 91  |

| V.1.2 Generación de datos del NAS                             | 92  |

| V.2 Modelo CNN para la fusión sensorial audiovisual           | 95  |

| V.3 Resultados                                                | 98  |

| VI. Aportaciones más importantes y conclusiones               | 103 |

| VII Trabajo futuro                                            | 105 |

| VIII. Bibliografía                                                      | 107 |

|-------------------------------------------------------------------------|-----|

| V. Anexo                                                                | 115 |

| OKAERTool. Herramienta de depuración y testeo de sistemas neuromórficos | 115 |

# Índice de Figuras

| Figura 1. Reproducción de un dibujo de Ramón y Cajal que muestra algunas neuros        | nas del   |

|----------------------------------------------------------------------------------------|-----------|

| córtex de un mamífero.                                                                 | 11        |

| Figura 2. Esquema básico de una neurona.                                               | 11        |

| Figura 3. Diagrama de un pulso eléctrico, o spike, generado por una neurona            | 12        |

| Figura 4. Vista transversal de las células del córtex en capas con sus dendritas en la | materia   |

| gris y los axones proyectando hacia la materia blanca.                                 | 15        |

| Figura 5. Multiplexado de diferentes neuronas en un único canal de comunicación .      | 16        |

| Figura 6. Demultiplexación de una entrada AER en spikes individuales para cada d       | endrita   |

|                                                                                        | 17        |

| Figura 7. Izquierda, primera fotografía que se conoce. Derecha, primera fotografía d   | londe     |

| aparece una persona                                                                    | 18        |

| Figura 8. Izquierda, imagen captada por un telescopio. Derecha, primera radiografía    | a que se  |

| conoce                                                                                 | 18        |

| Figura 9. Sistema de conducción autónomo de Tesla                                      | 19        |

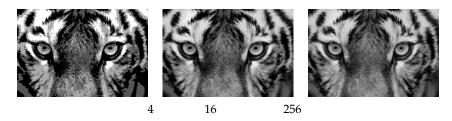

| Figura 10. Imagen con diversos niveles de gris                                         | 21        |

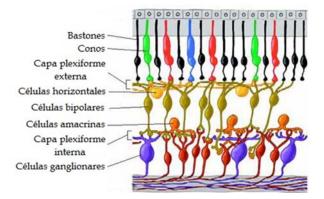

| Figura 11. Diagrama de una sección transversal de la retina                            | 22        |

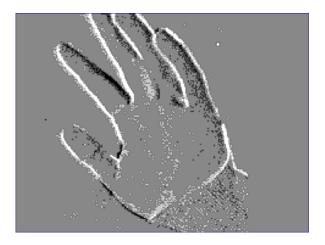

| Figura 12. Representación en jAER de la salida de un sensor DVS frente a una mano      | en en     |

| movimiento                                                                             | 24        |

| Figura 13. Primera patente de un teléfono por Alexander Graham Bell                    | 25        |

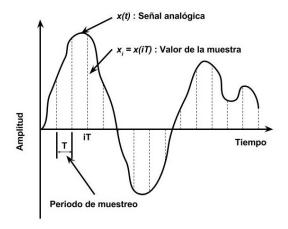

| Figura 14. Muestreo en el dominio del tiempo                                           | 27        |

| Figura 15. Ejemplo de las características de entrada-salida de una cuantificación de   | 8 niveles |

|                                                                                        | 28        |

| Figura 16. El oído humano                                                              | 29        |

| Figura 17. Representación de la salida del NAS                                         | 30        |

| Figura 18. (a) Arquitectura general del NAS. (b) Banco de filtros dispuestos en casca  | ada, CFB. |

| (c) Etapa básica del CFB                                                               | 31        |

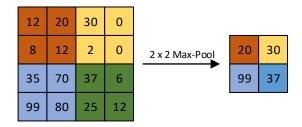

| Figura 19. Ejemplo de operación max-pooling                                            | 40        |

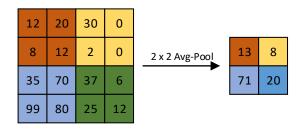

| Figura 20. Ejemplo de operación avg-pooling                                            | 40        |

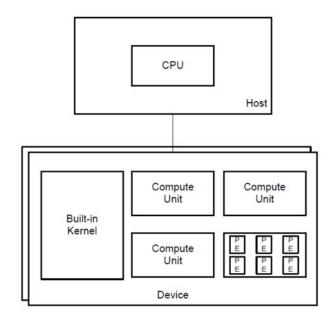

| Figura 21. Esquema general del modelo de plataforma OpenCL (Xilinx 2016b)              | 42        |

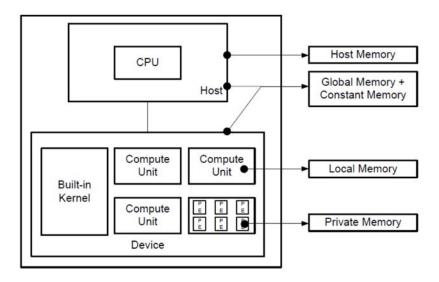

| Figura 22. Esquema del modelo de memoria OpenCL (Xilinx 2016b)                         | 43        |

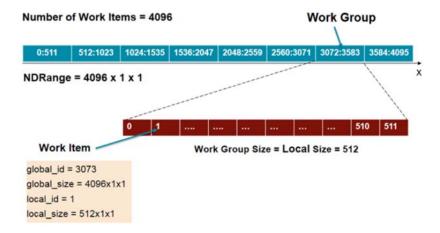

| Figura 23. Modelo de ejecución unidimensional (Xilinx 2016a)                           | 45        |

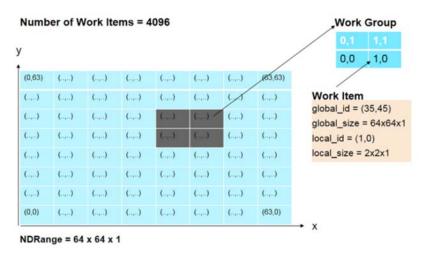

| Figura 24. Module de ejecución bidimensional (Xilinx 2016a)                            | 45        |

| Figura 25. Modelo de ejecución tridimensional (Xilinx 2016a)                           | 46        |

| Figura 26. Arquitectura CNN LeNet5.                                                    | 47        |

| Figura 27. Diagrama de ejecución de los kernels en el dispositivo hardware (Tapiador et            | al. |

|----------------------------------------------------------------------------------------------------|-----|

| 2017)                                                                                              | 49  |

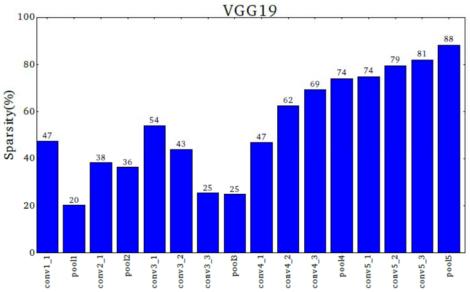

| Figura 28. Porcentaje de zeros en cada capa de la CNN GoogleNet (arriba) y la VGG19                |     |

| (abajo) (Aimar et al. 2017)                                                                        | 52  |

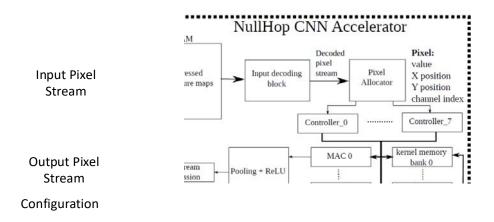

| Figura 29. Esquema de global del accelerador de CNN NullHop (Aimar et al. 2017)                    | 53  |

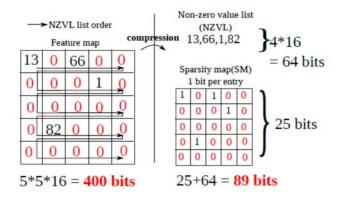

| Figura 30. Esquema de compresión utilizando mapa de dispersión (Aimar et al. 2017)                 | 53  |

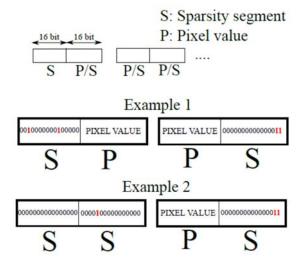

| Figura 31. Formato de las palabras enviadas al acelerador (Aimar et al. 2017)                      | 54  |

| Figura 32. Secuenciación de los datos de entrada/salida por filas en un acelerador de CN           | N   |

|                                                                                                    | 56  |

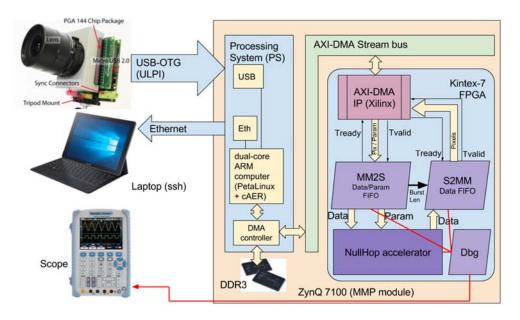

| Figura 33. Diagrama de bloques del escenario de test implementado en el SoC                        | 59  |

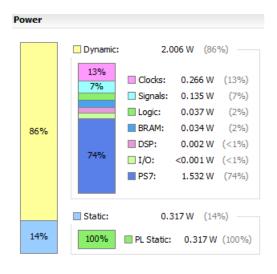

| Figura 34. Resultado de la estimación de consumo del NullHop utilizando la herramienta             |     |

| XPower de Vivado                                                                                   | 60  |

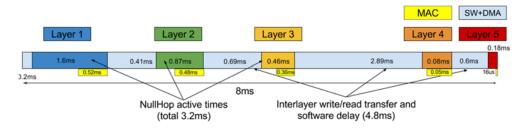

| Figura 35. Esquema temporal del prcesado de un frame en la plataforma Zynq para la rec             | d   |

| RoShambo                                                                                           | 63  |

| Figura 36. Esquema del módulo hardware de medición de latencias                                    | 64  |

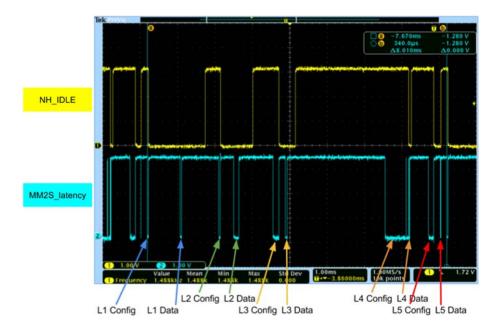

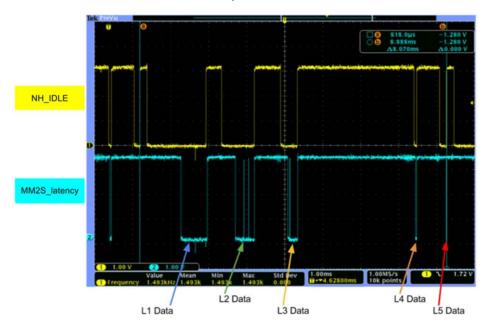

| Figura 37. Captura de la señal nh_idle y mm2s_latency en el osciloscopio para la                   |     |

| computación de un frame                                                                            | 65  |

| Figura 38. Captura de la señal nh_idle y s2mm_latency en el osciloscopio para la                   |     |

| computación de un frame                                                                            | 65  |

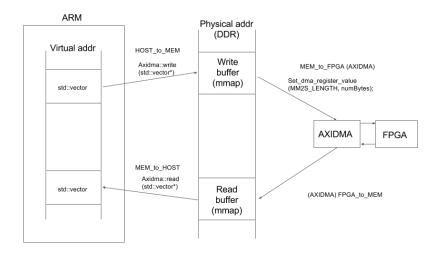

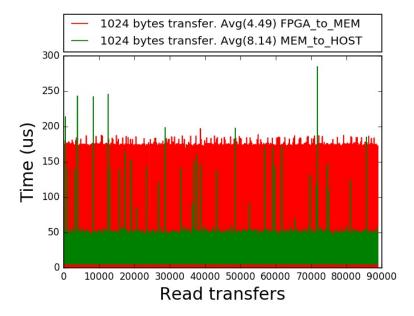

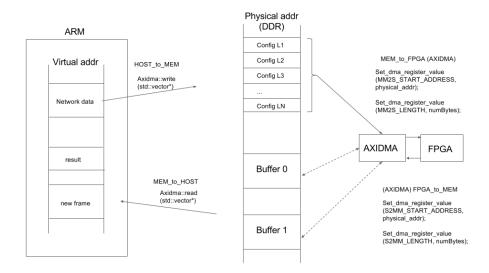

| Figura 39. Transferencias de datos PS→ PL y viceversa                                              | 66  |

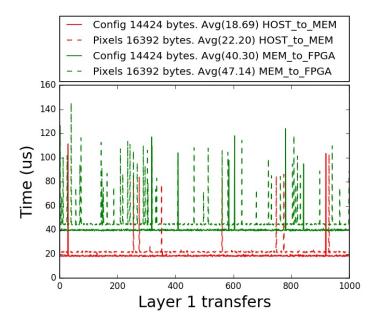

| Figura 40. Transferencias de escritura de la capa 1                                                | 67  |

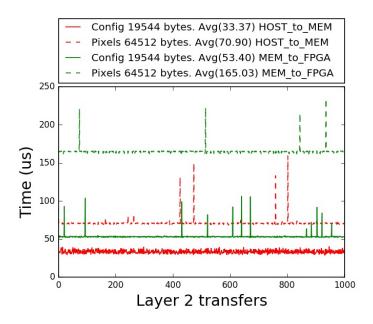

| Figura 41. Transferencias de escritura de la capa 2                                                | 67  |

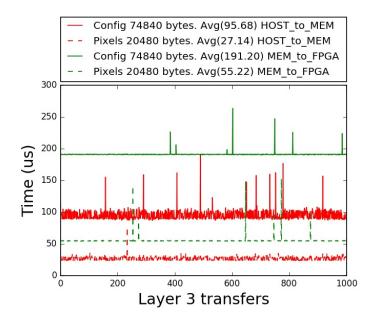

| Figura 42. Transferencias de escritura de la capa 3                                                | 68  |

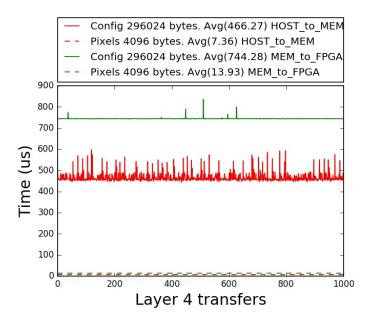

| Figura 43. Transferencias de escritura de la capa 4                                                |     |

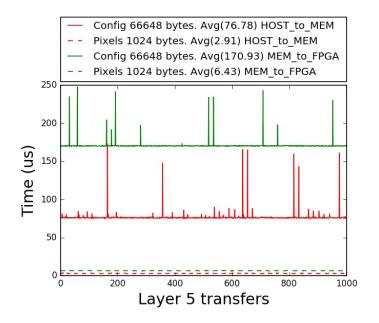

| Figura 44. Transferencias de escritura de la capa 5                                                | 69  |

| Figura 45. Transferencias de lectura d fijadas a 1KB/transfer                                      | 69  |

| Figura 46. Transferencias de datos PS $\Rightarrow$ PL y viceversa. Implementación de doble buffer |     |

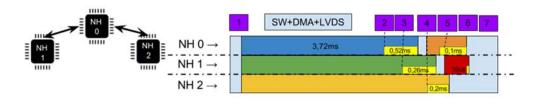

| Figura 47. Arquitectura multi-core HullHop                                                         | 71  |

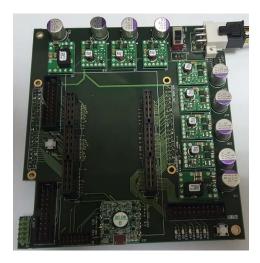

| Figura 48. Plataforma Zynq_Dock. Interfaz entre la plataforma Zynq 7100 MMP y AERN                 |     |

| Figura 49. Diagrama de bloques de un filtro paso de banda del NAS (Cerezuela Escuder               |     |

| 2015)                                                                                              | 76  |

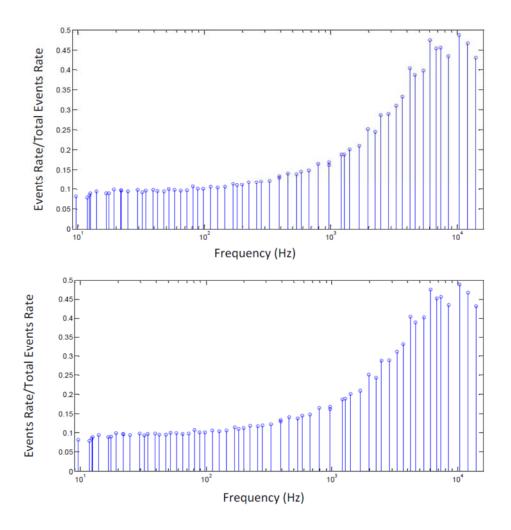

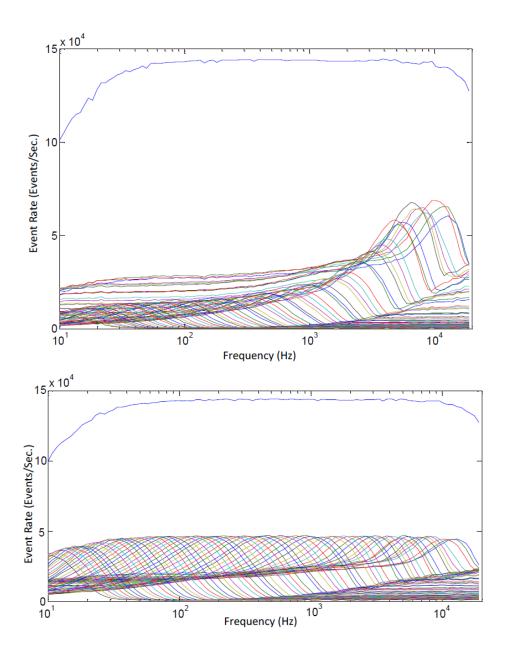

| Figura 50. Valores para normalizar los filtros de spikes de cada una las bandas, arriba par        | ra  |

| la cóclea izquierda, abajo para la cóclea derecha (Cerezuela Escudero 2015)                        | 77  |

| Figura 51. Diagramas de bode del banco de filtros. Arriba NAS no normalizado, abajo NA             | AS  |

| normalizado                                                                                        | 78  |

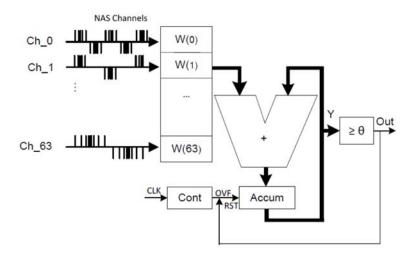

| Figura 52 Arquitectura de una neurona (Cerezuela Escudero 2015)                                    | 80  |

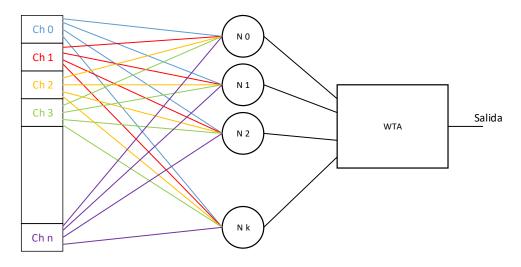

| Figura 53. Estructura de una red de neuronas de convolución mono-dimensional             | 81          |

|------------------------------------------------------------------------------------------|-------------|

| Figura 54. Elementos intervinientes en la demostración del sistema de integración s      |             |

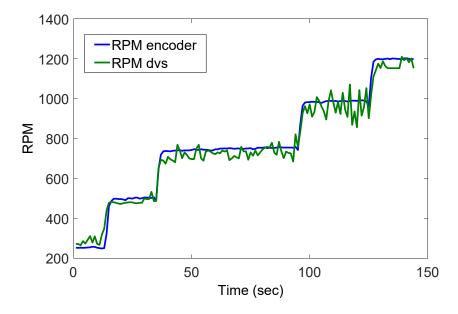

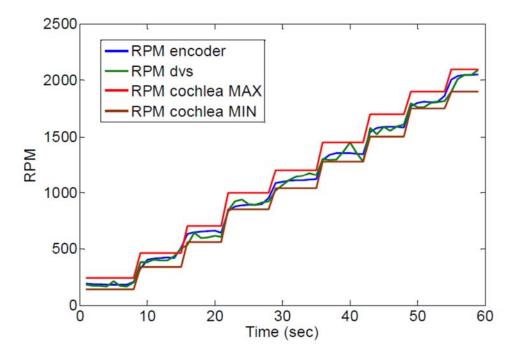

| Figura 55. Estimaciones de las rpm del motor haciendo uso de la información de la        | DVS128      |

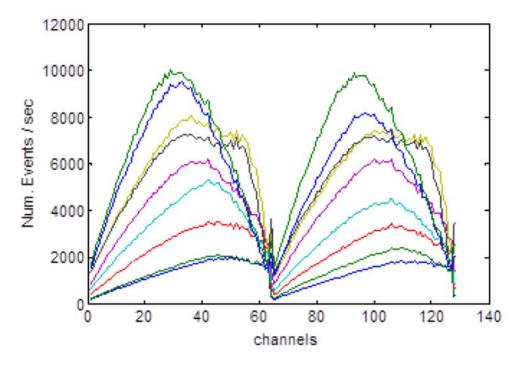

| Figura 56. Salida de los diferentes canales de salida del NAS para diferentes velocic    |             |

| Figura 57. Salida del sistema para las diferentes velocidades                            | 85          |

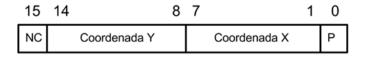

| Figura 58. Salida AER del DVS128                                                         |             |

| Figura 59. Salida AER del NAS                                                            | 90          |

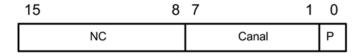

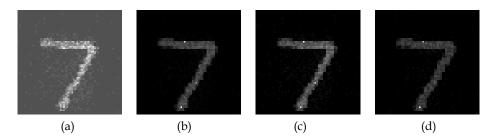

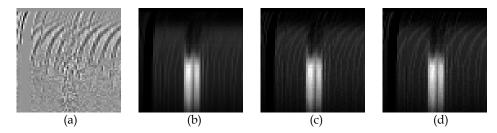

| Figura 60. Muestras del resultado de los diferentes métodos de integración para la v     | visión. (a) |

| full-integration, (b)unsigned-integration, (c)half-rectified positive, (d)half-restified | -           |

| Figura 61. Muestras del resultado de los diferentes métodos de integración del audi      |             |

| full-integration, (b)unsigned-integration, (c)half-rectified positive, (d)half-restified | _           |

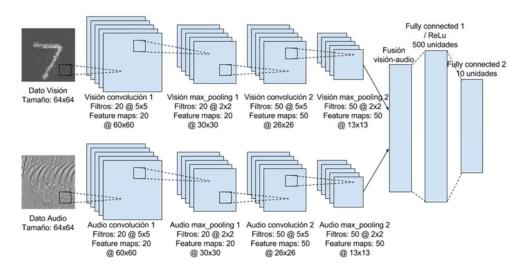

| Figura 62. Modelo CNN de fusión sensorial de audio y visión                              |             |

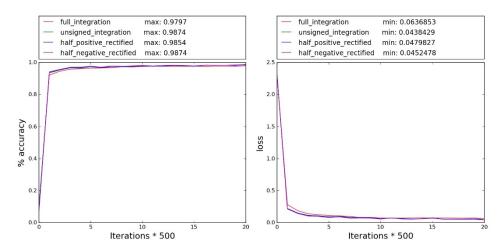

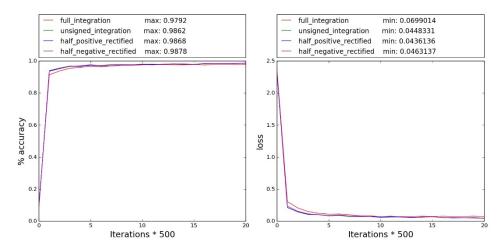

| Figura 63. Accuracy y loss siguiendo la estrategia de entrenamiento número 1             | 99          |

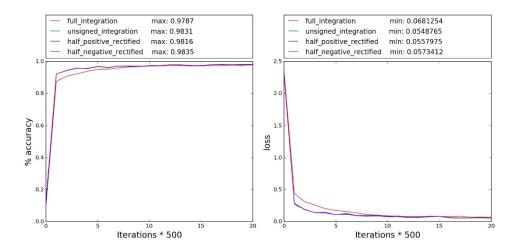

| Figura 64. Accuracy y loss siguiendo la estrategia de entrenamiento número 2             | 100         |

| Figura 65. Accuracy y loss siguiendo la estrategia de entrenamiento número 3             | 100         |

| Figura 66. Dato de visión alterado y dato de audio sin alterar para el dígito 5          | 101         |

| Figura 67. Dato de visión sin alterar y dato de audio alterado para el dígito 5          | 102         |

| Figura 68. Ambos datos, visión y audio, alterados para el dígito 5                       | 102         |

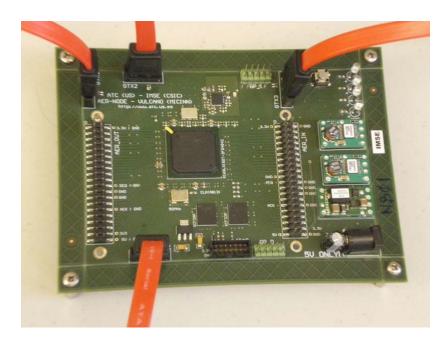

| Figura 69. Plataforma AERNode de procesamiento basado en spikes con conexión I           | VDS.117     |

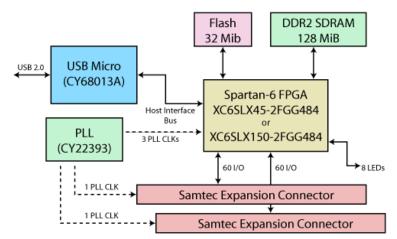

| Figura 70. Diagrama de bloques de la plataforma Opal Kelly XEM6010-LX150-2FGC            | G (Opal     |

| Kelly 2014)                                                                              | 118         |

| Figura 71. Plataforma OKAERTool. Placa de interconexión AER-Node-OKAERTool               | junto       |

| con la placa Opal Kelly XEM6010-LX150-2FGG                                               | 118         |

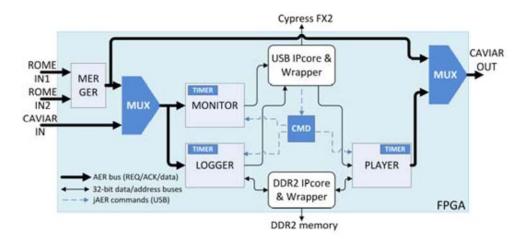

| Figura 72. Diagrama lógico de bloques de la plataforma OKAERTool                         | 119         |

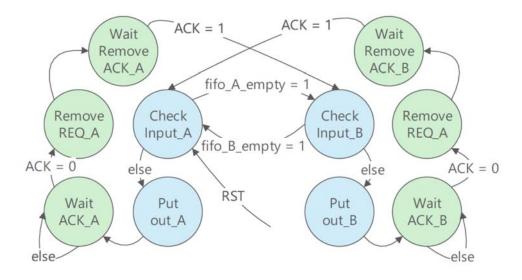

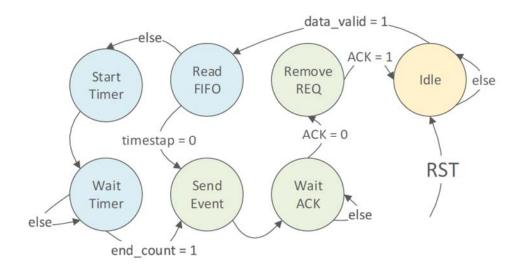

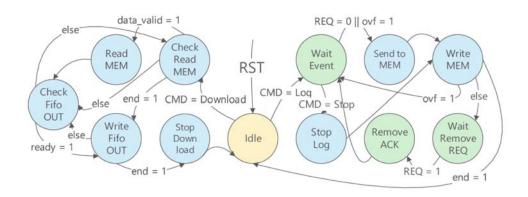

| Figura 73. Máquina de estados finita del módulo merger                                   | 120         |

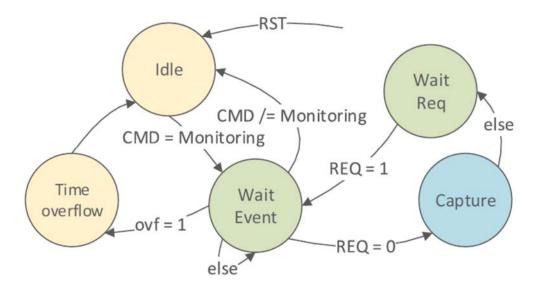

| Figura 74. Máquina finita de estados del módulo monitor                                  | 121         |

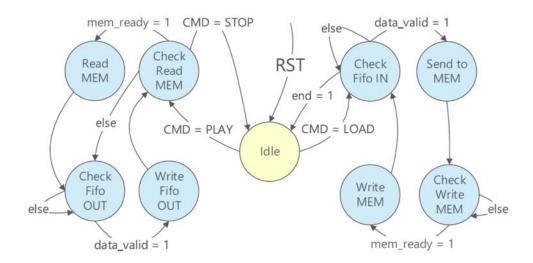

| Figura 75. Primera máquina de estados del módulo player                                  | 122         |

| Figura 76. Segunda máquina de estados del módulo player                                  | 123         |

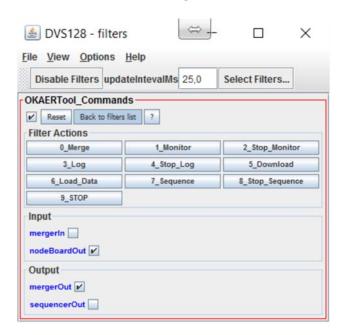

| Figura 77. Máquina de estados del módulo logger                                          | 124         |

| Figura 78. Interfaz de control de la herramienta OKAERTool en jAER                       | 125         |

# Índice de Ecuaciones

| Ecuación 1. Función asociada a una imagen de intensidad                           | 20 |

|-----------------------------------------------------------------------------------|----|

| Ecuación 2. Cálculo del número de bits necesarios para almacenar una imagen       | 21 |

| Ecuación 3. Selección de los parámetros Δ y B para la cuantificación              | 27 |

| Ecuación 4. Error de cuantificación                                               | 27 |

| Ecuación 5. Función completa de la capa de convolución                            | 38 |

| Ecuación 6. Función de convolución por cada feature-map                           | 39 |

| Ecuación 7. Función no lineal de activación ReLU                                  | 47 |

| Ecuación 8. Cálculo del rendimiento máximo del NullHop en Gops                    | 63 |

| Ecuación 9. Divisor de spikes                                                     | 76 |

| Ecuación 10. Operación mono-dimensional de convolución de una neurona             | 79 |

| Ecuación 11. Condición de generación de la salida de una neurona                  | 79 |

| Ecuación 12. Cálculo del error cometido por el sistema al realizar una estimación | 85 |

| Ecuación 13. Número de muestras por sujeto para la BBDD de dígitos hablados       | 93 |

| Ecuación 14. Función "inv" para modificar la tasa de entrenamiento                | 99 |

| Ecuación 15. Función "sigmoid" para modificar la tasa de entrenamiento            | 99 |

# Índice de Tablas

| Tabla 1. Comparativa cualitativa entre un computador y un sistema neuronal             | 14   |

|----------------------------------------------------------------------------------------|------|

| Tabla 2. Asignación de capas de la CNN LeNet5 a los kernels OpenCL                     | 48   |

| Tabla 3. Resultados de la ejecución y consumo hardware de la CNN LeNet5 OpenCL         | 50   |

| Tabla 4. Comparativa de NullHop con otros aceleradores de CNN                          | 56   |

| Tabla 5. Consumo de recursos de la Zynq 7100 necesarios para la implementación del     |      |

| NullHop                                                                                | 59   |

| Tabla 6. Mediciones de consumo real de la plataforma Zynq 7100 MMP                     | 61   |

| Tabla 7. Configuración de la red RoShambo                                              | 62   |

| Tabla 8. Parámetros de entrenamiento para las diferentes estrategias utilizadas        | 98   |

| Tabla 9. Máximos y mínimos de accuracy / loss respectivamente según estrategia de      |      |

| entrenamiento y método de integración de frame                                         | 101  |

| Tabla 10. Accuracy de la robustez del modelo de fusión para cada método de integración | n de |

| frames                                                                                 | 102  |

| Tabla 11. Comparación entre varias herramientas para la depuración de sistemas AER     | 116  |

#### Resumen

En este trabajo se pretende avanzar en el conocimiento y posibles implementaciones hardware de los mecanismos de *Deep Learning*, así como el uso de la fusión sensorial de forma eficiente utilizando dichos mecanismos. Para empezar, se realiza un análisis y estudio de los lenguajes de programación paralela actuales, así como de los mecanismos de *Deep Learning* para la fusión sensorial de visión y audio utilizando sensores neuromórficos para el uso en plataformas de FPGA.

A partir de estos estudios, se proponen en primer lugar soluciones implementadas en OpenCL así como en hardware dedicado, descrito en systemverilog, para la aceleración de algoritmos de *Deep Learning* comenzando con el uso de un sensor de visión como entrada. Se analizan los resultados y se realiza una comparativa entre ellos.

A continuación se añade un sensor de audio y se proponen mecanismos estadísticos clásicos, que sin ofrecer capacidad de aprendizaje, permiten integrar la información de ambos sensores, analizando los resultados obtenidos junto con sus limitaciones. Como colofón de este trabajo, para dotar al sistema de la capacidad de aprendizaje, se utilizan mecanismos de *Deep Learning*, en particular las CNN¹, para fusionar la información audiovisual y entrenar el modelo para desarrollar una tarea específica.

Al final se evalúa el rendimiento y eficiencia de dichos mecanismos obteniendo conclusiones y unas proposiciones de mejora que se dejarán indicadas para ser implementadas como trabajos futuros.

1

<sup>&</sup>lt;sup>1</sup> Convolutional Neural Networks

#### **Abstract**

In this work it is intended to advance on the knowledge and possible hardware implementations of the Deep Learning mechanisms, as well as on the use of sensory fusion efficiently using such mechanisms. At the beginning, it is performed an analysis and study of the current parallel programing, furthermore of the Deep Learning mechanisms for audiovisual sensory fusion using neuromorphic sensor on FPGA platforms.

Based on these studies, first of all it is proposed solution implemented on OpenCL as well as dedicated hardware, described on systemverilog, for the acceleration of Deep Learning algorithms, starting with the use of a vision sensor as input. The results are analysed and a comparison between them has been made.

Next, an audio sensor is added and classic statistical mechanisms are proposed, which, without providing learning capacity, allow the integration of information from both sensors, analysing the results obtained along with their limitations.

Finally, in order to provide the system with learning capacity, Deep Learning mechanisms, in particular CNN, are used to merge audiovisual information and train the model to develop a specific task.

In the end, the performance and efficiency of these mechanisms have been evaluated, obtaining conclusions and proposing improvements that will be indicated to be implemented as future works.

#### I. Introducción

Desde los principios del mundo que conocemos, el ser humano ha tratado de resolver de manera artificial los diferentes problemas que se ha ido encontrado en el camino de su progreso. Para ello, se ha fijado en cómo esos problemas que ha experimentado están resueltos en la naturaleza que nos rodea. La inquietud que el ser humano ha mostrado siempre por intentar conocer lo desconocido le ha llevado a ingeniar soluciones para resolver el problema de sobrevivir en medios en los cuales no está naturalmente adaptado para ello. Desde la navegación, que se conoce desde la más remota antigüedad, pasando por el primer submarino navegable en 1620 de Cornelius Drebbel (BBC), hasta el primer vuelo a motor en 1903 de los hermanos Wright (Bede & Collum 2002), el ser humano no ha dejado de evolucionar controlando el medio que le rodea.

Paralelamente a este progreso, se ha desarrollado la capacidad de crear nuevas máquinas que permitan resolver problemas cada vez más complejos, con mayor precisión y cada vez de manera más eficiente. Parte de aquí la idea de dotar de cierta autonomía e inteligencia a estos nuevos sistemas para que sean capaces de automatizar tareas sin necesidad de la intervención del ser humano. Esta nueva investigación abre nuevos campos de estudio sobre la forma de tratar la información que captamos sobre el entorno que nos rodea mediante diferentes sensores.

A lo largo del progreso tecnológico hemos podido ir viendo la adaptación de cada uno de estos avances en el campo de la industria, con el fin de crear robots que realicen diversas tareas peligrosas, repetitivas o de alta precisión que no serían posibles o rentables si un ser humano las realizara. Pero hoy día, y cada vez con más frecuencia, podemos ver que los dispositivos tecnológicos que adquirimos y utilizamos en nuestro día a día poseen cierta inteligencia que nos ayudan o facilitan muchas de las tareas o acciones que antes no hacían, por ejemplo, cómo una cámara fotográfica convencional es capaz de enfocar automáticamente la imagen al sujeto que se fotografía o cómo nuestro teléfono móvil es capaz de cancelar parte del ruido ambiente para que nuestra voz se oiga mejor al otro lado de la conversación.

Es en la historia más reciente de la inteligencia artificial cuando nace un nuevo paradigma de aprendizaje y procesamiento automático, inspirado en el funcionamiento el sistema nervioso. En inteligencia artificial se les conoce como redes neuronales, y se trata de un sistema de interconexión de neuronas que procesan la información de manera colaborativa entre ellas para producir unos estímulos en forma de resultado en las neuronas de salida. Actualmente este tipo de algoritmos son usados para la búsqueda de patrones, o características, en los datos de entrada con el fin de obtener una salida concreta. Un claro ejemplo son las redes neuronales de convolución, conocidas en la literatura como CNN, que se ha comprobado, a lo largo de la literatura, que son un buen mecanismo para obtener información semántica de los datos de entradas para realizar tareas de clasificación, detección y segmentación.

En relación a esta serie de cuestiones y problemas nace una nueva línea de investigación a finales de los años 80, la cual se centra en estudiar los sistemas biológicos e internos del procesamiento neuronal humano (Maher et al. 1989; Mead & Mahowald 1988), con el fin de conseguir sistemas analógicos y digitales que sigan los mismos patrones de funcionamiento utilizados por las neuronas del cerebro humano. Esta nueva línea de investigación es conocida como ingeniería Neuromórfica, la cual plantea nuevos sensores y sistemas bio-inspirados cuyos objetivos más destacables son los de ofrecer soluciones de muy alta velocidad de transferencia de información y procesamiento, como el de entender el funcionamiento del cerebro intentando de imitarlo. En la literatura más reciente podemos encontrar sensores de visión (Lichtsteiner et al. 2008; Serrano-Gotarredona & Linares-Barranco 2013), auditivos (Chan et al. 2007; Jimenez-Fernandez et al. 2016), sistemas de control motor (Jimenez-Fernandez et al. 2012; Perez-Peña et al. 2013), redes neuronales pulsantes (Stromatias et al. 2015), entre otros muchos.

#### I.1 Motivación

Muchas son las soluciones aportadas en el campo de las redes neuronales en las que los datos de entrada de dichos sistemas son provenientes de un solo sensor o tipo de dato. ¿Por qué no pensar que estos tipos de sistemas podrían ser mejores y resolutivos si tenemos más de un tipo de dato en su entrada o una combinación de ellos?

La principal motivación del presente trabajo se centra en el ámbito científico y en el estudio de las redes neuronales de convolución para una aproximación de la fusión sensorial, en concreto haciendo uso de sensores neuromórficos. Este tipo de sensores tienen la

particularidad de obtener información relevante del entorno evitando aquella que nos aportaría menos valor a la hora de procesarla.

El presente trabajo trata de realizar un análisis y estudio de la viabilidad de uso de las redes neuronales de convolución combinando la información de dos tipos de sensores neuromórficos, audio y vídeo, en el campo de la fusión sensorial. Para ello se plantean dos modelos de red neuronal de convolución, cuyos datos de entradas proceden de cada uno de los dos sensores anteriormente mencionados para efectuar una tarea en concreto.

En cuanto a lo personal, cabe destacar la inquietud del autor por dotar de múltiples sensores a los sistemas diseñados para realizar diferentes tareas como la navegación de robots móviles, la integración de sensores inerciales para orientación en el espacio o tareas como la verificación de la calidad de un sistema motor. Parte de aquí la motivación de utilizar y estudiar nuevos enfoques que alineados a las nuevas tendencias de la inteligencia artificial, sean capaces de aprender la tarea que se le encomienda haciendo uso de más de un tipo de sensor. Los sensores utilizados tanto para vídeo como para audio son sensores neuromórficos, los cuales presentan algunas ventajas frente a los convencionales para este trabajo. El sensor de visión consiste en una retina de silicio que solamente recoge la información de la escena que presenta movimiento, eliminando aquella menos relevante. Para su conversión a frames, se integra dicha información con el fin de crear un histograma, por lo que podemos reducir el frame rate del sensor a nuestra necesidad. El sensor de audio utilizado, nos genera a su salida la división en frecuencias del sonido original captado, evitándonos todo el postprocesamiento para obtener esa información. Además, como líneas futuras se plantean la evolución de los modelos de fusión sensorial que se presentan en este trabajo al dominio pulsante, por lo que ambos sensores son ideales para los futuros modelos.

Todo lo expuesto anteriormente se enmarca en la trayectoria investigadora del grupo *Robotic and Technology of Computes (RTC*, TEP-108) al que pertenece el autor. Este trabajo se encuentra focalizado y alineado con diversas tareas de los proyectos de investigación nacionales e internacionales, que han servido de guía, causa y financiación. Los proyectos referidos son los siguientes:

- Proyecto nacional BIOSENSE: Sistema bio-inspirado de fusión sensorial y

procesamiento neuro-cortical basado en eventos. Aplicaciones de alta velocidad

y bajo coste en robótica y automoción.

- Proyecto de excelencia MINERVA: Mota-Infraestructura de Sensado y Transmisión Inalámbrica para la Observación y Análisis de la Pauta de Animales Salvajes o en Semilibertad

Proyecto internacional NPP<sup>2</sup>: Procesador neuromórfico. Acelerador de redes neuronales de convolución.

A continuación se hará una introducción detallada de los grandes campos de la ciencia donde se enmarca este trabajo, empezando por la ingeniería neuromórfica, continuando con la visión y audición artificial, y finalizando con la evolución de la inteligentica artificial, focalizando en el aprendizaje profundo.

### I.2 Ingeniería neuromórfica

Como se comentaba al principio de este capítulo, los seres vivos se han extendido a lo largo y ancho de la tierra colonizando los diversos hábitats. Una de las claves de esta expansión de la vida ha sido la capacidad de adaptación de los seres vivos, estando dotados por la naturaleza de las cualidades necesarias para poder sobrevivir a un determinado entorno. Por ejemplo, una abeja demuestra una notable tarea en navegación e inteligencia social mientras busca alimento del néctar, y logra este rendimiento usando menos de un millón de neuronas. Es por ello que la capacidad de los cerebros de los animales para interactuar con el mundo que los rodea ha proporcionado un desafío continuo para la tecnología.

A lo largo de la historia y en infinidad de ocasiones, los ingenieros se han inspirado y observado las soluciones alcanzadas por la naturaleza para resolver problemas en diversos campos, siendo éste el origen de los sistemas bio-inspirados, encontrándolos a nuestro alrededor cada vez con más frecuencia. Ejemplos muy claros que hoy día tenemos bastante interiorizados pueden ser los aviones, submarinos y más recientemente los robots con capacidad de aprender.

Por otro lado, tanto la industria como nuestra vida cotidiana han sufrido una gran revolución gracias a la aparición de los sistemas computacionales y robóticos. En la industria se ha ido incorporando de manera progresiva el uso de robots destinados a tareas en las que se necesita elevada precisión, repetitividad o la realización de esfuerzos sobrehumanos. Sin embargo, este tipo de robots están programados para realizar un número muy limitado de tareas, sin capacidad de aprendizaje, en entornos muy controlados y por norma general tienen un alto consumo energético. Si los contrastamos con las habilidades de los animales, no sólo pueden navegar inteligentemente (dentro de sus posibilidades) por su entorno, sino que son

<sup>&</sup>lt;sup>2</sup> Neuromorphic Processor Project

capaces de procurarse su propia energía, aprender, desarrollar actividades sociales, personalidades propias, organizarse para conseguir fines comunes, etc... Resumiendo en otras palabras, el desarrollo de habilidades sociales, cognitivas y culturales.

Por regla general, este tipo de robots en la actualidad están gobernados por comportamientos algorítmicos procesados por sistemas basados en computadores. En los últimos años los computadores han evolucionado a un ritmo muy elevado, alcanzando una capacidad de cálculo elevadísima, tal y como predecía la Ley de Moore (Moore 1965). A pesar de este avance en los computadores, los robots no han aumentado en la misma medida, progresando a un ritmo mucho más lento. En este punto podríamos plantearnos si sería posible modelar con suficiente fidelidad el comportamiento de un ser vivo o de alguna habilidad concreta para ser codificado algorítmicamente. En caso de que este planteamiento fuera posible, ¿se podría ejecutar ese algoritmo en un tiempo razonable y con suficiente fiabilidad en un computador? Las posibles respuestas a este planteamiento y pregunta podrían dar lugar a nuevos planteamientos y preguntas, pero entre ellas cabe plantearse si los sistemas basados en computador actuales son los sistemas más apropiados para proporcionar a los robots de habilidades cognitivas avanzadas (Penrose 1990).

La solución a todas estas cuestiones es actualmente desconocida, pero tal vez pase por imitar al "controlador" de los propios seres vivos, el sistema nervioso central, realizando tareas de "ingeniería inversa", surgiendo los sistemas neuro-inspirados.

### I.2.1 Inicios y evolución

El inicio de la ingeniería neuromórfica data de los años 80, cuando el grupo de Caver Mead en Caltech³ (Mead 1989), plantea como objetivo inicial imitar el comportamiento de las neuronas en el sistema nervioso mediante circuitos analógicos VLSI o aVLSI (Liu 2002). Sin embargo, el campo de estudio de los ingenieros neuromórficos se ha expandido en los últimos años, usando tanto circuitos analógicos, como digitales para modelar el comportamiento de las neuronas. Para conseguir este objetivo es muy importante el entender como la naturaleza ha sido capaz de crear arquitecturas neuronales muy robustas al ruido, increíblemente eficientes y que además son capaces de aprender. En la ingeniería neuromórfica se dan cabida una serie de investigadores de los más diversos campos, como son físicos, matemáticos, psicólogos, médicos, biólogos e ingenieros.

-

<sup>&</sup>lt;sup>3</sup> California Institute of Technology

Desde el comienzo de la ingeniería neuromórfica hasta hoy día, esta comunidad se ha expandido considerablemente desde sus orígenes en Caltech y Johns Hopkins. Al principio sólo unos cuantos de prototipos de sistemas neuromórficos podían ser encontrados en algunos laboratorios, pero en los últimos 20 años, tenemos plataformas neuromórficas donde desplegar modelos con cientos y miles de neuronas (Furber et al. 2014; Indiveri et al. 2006). Además podemos encontrar sensores neuromórficos con un gran rango dinámico que pueden ser utilizados para aplicaciones de alto rendimiento (Chan et al. 2007; Lichtsteiner et al. 2008; Jimenez-Fernandez et al. 2016; Serrano-Gotarredona & Linares-Barranco 2013) además de herramienta para la depuración de estos sistemas (Serrano-Gotarredona et al. 2009) como métodos de conversiones *frame-spikes* sintéticos (Linares-Barranco et al. 2004; Linares-Barranco et al. 2006).

Hoy en día se celebran dos convenciones internacionales sobre ingeniería neuromórfica, una con sede en Telluride (Estados Unidos) y otra con sede en CapoCaccia (Italia), representando un punto de encuentro para investigadores de todo el mundo. En estos workshops los investigadores tienen la oportunidad de exponer a la comunidad científica sus últimos avances, además de trabajar con personas de otros centros de investigación y compartir diversos dispositivos hardware neuro-inspirados para el diseño de sistemas de procesamiento de información pulsante.

#### I.2.2 Sistemas neuro-inspirados

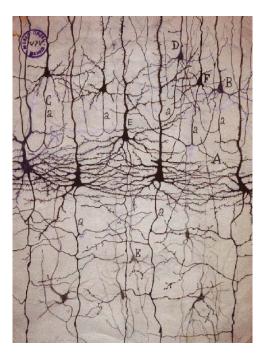

En 1906 el científico español Santiago Ramón y Cajal recibió el premio Nobel de medicina por sus pioneras investigaciones sobre la estructura microscópica del cerebro, descubriendo que el cerebro estaba formado por un conjunto de células independientes conectadas entre sí, las neuronas. Sus estudios fueron posibles gracias a los avances en los métodos de tinción y de la tecnología de los microscopios, que permitieron obtener en láminas ilustradas sus observaciones. En la Figura 1 se puede ver una reproducción de unos de los dibujos del científico español.

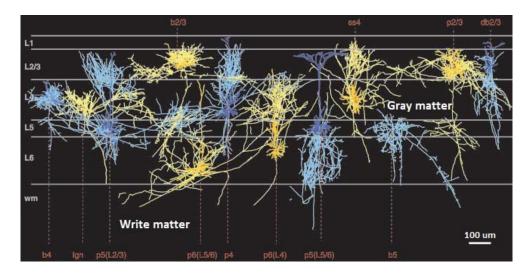

Figura 1. Reproducción de un dibujo de Ramón y Cajal que muestra algunas neuronas del córtex de un mamífero.

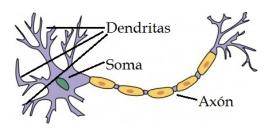

Una típica neurona puede ser dividida en tres partes funcionalmente distintas, llamadas dendritas, soma y axón. En la Figura 2 se puede ver un esquema básico de las partes de una típica neurona. Hablando a grandes rasgos, las dendritas juegan el rol de "dispositivos de entrada" que colectan información de otras neuronas y la transmiten al soma. El soma es "la unidad central de procesamiento" que realiza un tratamiento no lineal de la información recibida. La información recibida modifica el potencial de membrana que posee la neurona, y si éste alcanza un cierto umbral, una señal es generada y viajará por el "dispositivo de salida", el axón, y será entregada a otras neuronas conectadas a ésta.

Figura 2. Esquema básico de una neurona.

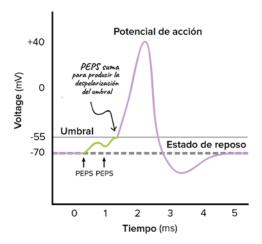

La conexión entra dos neuronas se conoce como sinapsis. Si suponemos que una neurona envía una señal, o pulso eléctrico (también llamado spike), a través de una sinapsis, a la neurona que envía el spike se le conoce como neurona pre-sináptica y a la neurona que recibe el spike se le conoce como neurona post-sináptica. En el caso que la neurona pre-sináptica envíe pulsos excitatorios tendremos un cambio llamado PEPS<sup>4</sup>, mientras que si envía pulsos inhibitorios tendremos un cambio llamado PIPS<sup>5</sup> (ver Figura 3). Una sola neurona del córtex vertebral suele estar conectada a  $10^4$  neuronas post-sinápticas. Muchas de las terminaciones de un axón terminan directamente en las neuronas más próximas, pero otros pueden llegar a medir varios centímetros, para alcanzar a neuronas que están en otras áreas del cerebro.

Figura 3. Diagrama de un pulso eléctrico, o spike, generado por una neurona

Uno de los puntos clave de los mecanismos de procesamiento neuronales es la hipótesis de la representación de la información por parte de las neuronas. Mucho se ha debatido sobre cómo codificar la información en los spikes, Horace Barlow en 1961 propuso varios modelos (Barlow 1961), siendo un modelo muy aceptado por parte en el campo de la ingeniería neuromórfica el que propone la codificación de la información en la frecuencia de los spikes, siguiendo una modulación en frecuencia de pulsos, spikes o PFM (Maass & Bishop 1999; Westerman et al. 1997). De esta manera la información puede ser codificada de manera continua, sin necesidad de realizar una discretización temporal de la información (Hynna & Boahen 2001; Fujii et al. 1996).

<sup>&</sup>lt;sup>4</sup> Potencial exitatorio post-sináptico

<sup>&</sup>lt;sup>5</sup> Potencial inhibitorio post-sináptico

La representación pulsante es muy eficiente desde varios puntos de vista, empezando por su simplicidad, reduciendo la cantidad de canales de comunicación necesarios para transmitir spikes, y finalmente y no menos importante, proporcionando una información continua en el tiempo y no discreta. Así pues, la representación pulsante proporciona una minimización de canales de comunicación, permitiendo una alta tasa de conectividad entre neuronas, y además, al no estar la información muestreada, evita la transmisión de información redundante, transmitiéndose así únicamente los spikes cuando son necesarios, no saturando los canales de comunicación de manera innecesaria.

En la mayoría de los animales, el cerebro es el sistema nervioso central localizándose en la cabeza, protegido por el cráneo y cerca de los principales órganos sensitivos. En el caso de los humanos, el cerebro es extremadamente complejo y se estima que tiene entre 15 y 33 billones de neuronas, pudiendo estar una de ellas conectadas a otras 10 mil. Las estructuras neuronales se agrupan por capas, las cuales están destinadas a procesar parte de la información que obtiene y tienen una funcionalidad definida (Shadlen & Newsome 1994; Rakic 1988). Para procesar la información cada neurona está conectada a un campo proyectivo de neuronas a lo largo de diferentes capas, fluyendo la información entre capas, y procesándose en este mismo fluir.

En la Tabla 1 se realiza una comparativa cualitativa generalizada acerca de la manera en la que funcionan un computador y el sistema neuronal de los animales. La primera diferencia que encontramos es que un computador se encuentra dominado bajo una señal global de reloj, que lo hace reaccionar continuamente en cada ciclo de reloj, sin embargo, las neuronas se comportan de manera totalmente asíncrona, no existiendo ningún mecanismo de sincronización entre ellas. Además, el computador es un elemento totalmente determinista, que dictamina en todo momento tras una sucesión de operaciones aritméticas y lógicas en qué estado debe encontrarse, mientras que las neuronas responden a un modelo estocástico, dependiendo su reacción de modelos probabilísticos dinámicos. Actualmente los sistemas basados en computador tienen una alta resolución de la información que manejan, muestreada a un ritmo constante, una vez más, los sistemas neuronales son completamente opuestos, la resolución no es tan elevada, pero son capaces de adaptarse a las características de la información para mejorar su representación. En los sistemas computacionales actuales el procesamiento en sí está muy centralizado, por ejemplo, un ordenador personal, comparado con la manera en que las neuronas procesan la información, ya que cada neurona procesa una pequeña parte de la información, no dependiendo de otras neuronas, implementando así una arquitectura de procesamiento masivamente paralela. El uso de computadores tiene como imperativo el uso de memoria tanto para almacenar los algoritmos

a utilizar, así como los datos iniciales, intermedios y finales, en contraposición, los sistemas neuronales no necesitan memoria para ninguno de estos fines, ya que el "algoritmo neuronal" que ejecutan está codificado en la conexión de las distintas neuronas que lo componen así como las características fisiológicas de cada una de ellas.

| Computador                              | Sistema neuronal                               |  |  |

|-----------------------------------------|------------------------------------------------|--|--|

| Reloj centralizado de alta velocidad.   | Asíncrono, sin ninguna señal global de reloj.  |  |  |

| Dictamina perfectamente y de manera     | Las neuronas se comportan de forma             |  |  |

| determinista el estado lógico en que se | estocástica, respondiendo a modelos            |  |  |

| debe encontrar.                         | probabilísticos dinámicos.                     |  |  |

| Alta resolución de la información con   | De baja resolución, pero adaptativo. Sin       |  |  |

| una tasa de muestreo constante.         | período de muestreo, estando la información    |  |  |

|                                         | contenida en los spikes.                       |  |  |

| La computación está centralizada o      | Cada neurona procesa una pequeña parte de      |  |  |

| levemente distribuida.                  | la información, implicando una computación     |  |  |

|                                         | completamente distribuida y masivamente        |  |  |

|                                         | paralela.                                      |  |  |

| La memoria está muy "lejos" del         | Las características morfológicas y las         |  |  |

| computador, necesitando memoria         | interconexiones de cada neurona son el         |  |  |

| tanto para el algoritmo como para       | algoritmo en sí, la información está contenida |  |  |

| almacenar los datos.                    | en el fluir de los spikes.                     |  |  |

Tabla 1. Comparativa cualitativa entre un computador y un sistema neuronal

#### I.2.3 Address-Event-Representation

El córtex cerebral de los animales está estructurado en diferentes capas divididas en lo que se conoce como materia gris y materia blanca. En la Figura 4 se muestra una sección transversal de un pequeño pedazo del córtex visual del cerebro de un gato. Los muchos tipos de neuronas, de los cuales hay unas  $10^5/\mathrm{mm}^3$ , están conectadas a otras muchas neuronas a través de sus axones (con una densidad de "cableado" de 9m de axón por mm³) en la zona de materia blanca, mientras la materia gris está compuesta mayormente por las dendritas, con una densidad de "cableado" enorme de 4km/mm³ (Braitenberg & Schüz 1991).

Figura 4. Vista transversal de las células del córtex en capas con sus dendritas en la materia gris y los axones proyectando hacia la materia blanca.

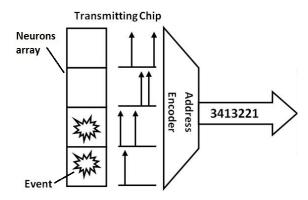

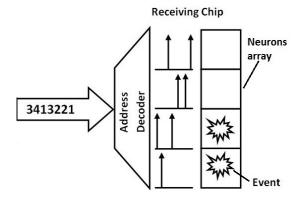

Una típica neurona tiene una frecuencia de disparo en el rango 1-10 Hz, por lo tanto, cientos de neuronas combinadas tendrán una frecuencia de disparo en el rango de los KHz o MHz. Los sistemas digitales actuales pueden soportar esta frecuencia de datos. Para modelar la comunicación en los sistemas neuromórficos electrónicos, no se crean redes o conexiones entre neuronas de manera individual, se crean conjuntos de neuronas que se conectan unos con otros, correspondiéndose cada conjunto de neuronas con una capa de procesamiento. Los circuitos utilizados multiplexan la comunicación para un conjunto de neuronas en un canal de comunicación individual donde cada neurona es identificada con una dirección única dentro del conjunto. Este tipo de representación es conocida como representación por dirección de evento (AER6). AER fue propuesto por primera vez en 1991(Sivilotti 1991; Lazzaro et al. 1993; Lazzaro & Wawrzynek 1995; Mahowald 1992).

La función de los circuitos AER es la de proporcionar funcionalidades de *multiplexión / demultiplexión* para los spikes que son *generados por / entregados a* un conjunto individual de neuronas. La Figura 5 muestra un ejemplo de codificación de los spikes de cuatro neuronas en un único canal de salida. Los spikes son generados asíncronamente y recogidos por el circuito AER que los codificará y multiplexará en el canal de salida en el orden que fueron generados. La secuencia de valores producidos en el canal de salida indica que neurona (su dirección en el array de neuronas) disparó. El tiempo en el que la dirección de la neurona es

<sup>&</sup>lt;sup>6</sup> Address Event Representation

generado se corresponde con el tiempo en el que esa neurona generó un spike, más un pequeño retraso debido al proceso de codificación. Mientras que los spikes estén suficientemente separados en el tiempo, el proceso de codificación asegura que las direcciones que identifican a las neuronas están correctamente ordenadas en la secuencia.

Figura 5. Multiplexado de diferentes neuronas en un único canal de comunicación

Si en el array de neuronas se garantizara que sólo una neurona puede generar un spike mientras que las restantes no pueden en el mismo instante de tiempo, el proceso de multiplexión se correspondería con un circuito de codificación asíncrono estándar. Sin embargo, esta no es una restricción válida para los conjuntos de neuronas, se puede dar que varias neuronas disparen al mismo tiempo produciendo solapamiento en los spikes, denominado colisión. Así pues, los circuitos de codificación utilizan una lógica para manejar la arbitración de la potencial llegada simultánea de spikes de varias neuronas.

Los codificadores AER tienen varios axones de neuronas como entradas y tienen que implementar principalmente dos funcionalidades. La primera es la de determinar qué spike tiene que ser el siguiente en ser comunicado en el canal de salida. Esto se corresponde a un problema clásico de arbitración asíncrona en el que una vez seleccionado el axón de la neurona que ha disparado, el circuito debe de codificar dicho axón en una dirección. Este funcionamiento es el de un codificador tradicional, donde una de las N direcciones diferentes es codificada utilizando  $log\ N$  bits. La diferencia entre los distintos codificadores AER que hay en la literatura es el mecanismo utilizado para resolver el conflicto entre múltiples spikes simultáneos y cómo las direcciones de las neuronas son codificadas. Cada opción utilizada tiene sus ventajas e inconvenientes, y son apropiados para diferentes tipos de sistemas neuromórficos. En (Liu 2015) podemos encontrar una amplia explicación de cada uno de los mecanismos y sus diferentes usos.

El circuito de decodificación o demultiplexación es menos complejo que el anterior. En este proceso se reciben unos valores de entrada proveniente de un canal AER que especifican las direcciones de las dendritas/axones (dependiendo el punto de vista) en el que los spikes deben de ser entregados. La dirección de la dendrita es decodificada utilizando un decodificador asíncrono, y el spike es entregado a la neurona correspondiente. La Figura 6 muestra cómo una secuencia de direcciones de spikes es decodificada en spikes que son entregados a cada dendrita individualmente y que están conectadas a su neurona correspondiente. Si el retraso entre los spikes adyacentes en la secuencia AER de entrada es lo suficientemente grande, la salida del decodificador AER entregará los spikes a las dendritas en el tiempo que corresponde al tiempo de llegada en la entrada más un pequeño retraso debido al circuito de decodificado.

Figura 6. Demultiplexación de una entrada AER en spikes individuales para cada dendrita

En el esquema AER más simple posible, las direcciones de las neuronas generadas por el circuito de codificación se corresponden con las direcciones de las dendritas de las neuronas en el destino. Si conectamos, por ejemplo, directamente la salida de la Figura 5 con la entrada de la Figura 6, tendríamos una conexión directa entre los axones de las neuronas del array fuente con las dendritas de las neuronas del array de destino.

# I.3 Visión artificial

Uno de los sentidos más importantes de los seres humanos es la visión. A través de este sentido podemos captar información visual, de una forma muy directa, del entorno físico que nos rodea. Es uno de los sentidos más complejos que el ser humano posee y se calcula que más del 70% de las tareas del cerebro están dedicadas al análisis de información visual.

El hecho de conectar una cámara a un computador, captar información visual del entorno y ser capaz de procesarla, supuso un gran avance en la era tecnológica. Es a partir de este momento donde nace la visión por computador, o visión artificial, (Harmon & Knowlton 1969) como disciplina que intenta emular la capacidad que poseen algunos seres vivos para captar información de su alrededor y procesarla. A lo largo de su historia se han ido diseñando e implementando algoritmos para realizar tareas como la segmentación, clasificación de patrones, localización de objetos, etc.

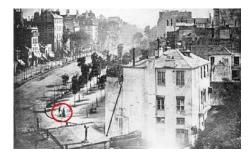

Si echamos la vista atrás, en el año 1826 el químico francés Niepce (1765-1833) llevó a cabo la primera fotografía colocando una superficie fotosensible dentro de una cámara oscura para fijar la imagen (Meteyard 1871). Posteriormente, en 1838 el químico francés Daguerre (1787-1851) hizo el primer proceso fotográfico práctico. Daguerre utilizó una placa fotográfica que era revelada con vapor de mercurio y fijada con trisulfato de sodio.

Figura 7. Izquierda, primera fotografía que se conoce. Derecha, primera fotografía donde aparece una persona

Figura 8. Izquierda, imagen captada por un telescopio. Derecha, primera radiografía que se conoce.

Desde que se inventó la fotografía se ha venido intentando extraer características o patrones de las imágenes. Por ejemplo, las radiografías transformaron el campo de la medicina, llegando a tener hoy día imágenes en 3D de nuestro cerebro completo o también la astronomía avanzó enormemente debido a la capacidad de adquirir imágenes de sistemas muy lejanos al nuestro a través de los telescopios.

Hoy en día existen sistemas autónomos, que gracias a la visión artificial junto con otros tipos de sensores, son capaces de interactuar con su entorno y navegar a través de él. Este tipo de sistemas, son capaces de obtener gran cantidad de información visual y procesarla en busca de ciertas características o patrones, que en función de esa información procesada son capaces de realizar tareas que previamente han aprendido. Un claro ejemplo de ello es el sistema de conducción autónomo de Tesla.

Figura 9. Sistema de conducción autónomo de Tesla

### I.3.1 Adquisición de una imagen digital

La primera etapa en la visión artificial pasa por la adquisición y digitalización de la imagen que se muestra frente a nuestro sensor visual. En particular para este trabajo, existen tres tipos interesantes de imágenes que somos capaces de adquirir; las imágenes de intensidad, térmicas y las de profundidad.

- Las imágenes de intensidad se basan en la cantidad de luz recogida por el dispositivo de captura en cada uno de los puntos de la escena. Son las más comúnmente utilizadas debido principalmente a la facilidad de obtener este tipo de sensores.

- Imágenes térmicas: Para la adquisición de este tipo de imágenes se hace uso de dispositivos que son capaces de recoger la señal de calor que emiten los cuerpos creando un mapa de color atendiendo al calor recogido de cada uno de los objetos de la escena infrarroja.

- Las imágenes de profundidad, también conocidas como mapas de profundidad, atiendes a imágenes 3D donde el valor de cada punto *x*, *y* se corresponde a la dimensión *z* que denomina la profundidad de ese punto en la escena.

Si nos centramos en las imágenes de intensidad, debido a su amplio uso, tras su captura obtenemos una matriz de dos dimensiones donde cada posición indica el valor de la intensidad de ese punto de la escena. El concepto de imagen está asociado a una función bidimensional f(x,y), cuya amplitud o valor será el grado de iluminación en el espacio de coordenadas (x,y) de la imagen para cada punto. El valor de esta función depende de la cantidad de luz que incide sobre la escena vista, así como de la parte que sea reflejada por los objetos que aparecen en dicha escena. Estos componentes llamados iluminación y reflexión son descritos por i(x,y) y r(x,y) respectivamente. El producto de ambas funciones da como resultado la función f(x,y).

$$f(x,y) = i(x,y) \cdot r(x,y)$$

Ecuación 1. Función asociada a una imagen de intensidad

La función de imagen f(x,y) es digitalizada espacialmente y en amplitud. La digitalización de las coordenadas espaciales (x,y) está asociada al concepto de muestreo, mientras que la digitalización de la amplitud al de cuantificación de los niveles de gris. Así pues, una imagen está almacenada en una matriz de N x M elementos teniendo en cuenta que el origen de coordenadas es la esquina superior izquierda, donde el eje x es el horizontal y el eje y el vertical

El muestreo es la conversión que sufren las dos coordenadas espaciales de la señal analógica, y que genera la noción de píxel. La imagen se comporta como una matriz donde el valor de los elementos es su nivel de gris, la fila y la columna su posición en el espacio. La cuantificación es la conversión que sufre la amplitud de la señal analógica; así se genera el concepto de nivel de gris o intensidad. Para el caso de tener por ejemplo 256 niveles de gris en cada píxel (0-255), el 0 corresponde a un píxel no iluminado o a un punto que absorbe todos

los rayos luminosos que inciden sobre él (negro), mientras que el nivel 255 corresponde a un píxel muy iluminado o a un punto que refleja todos los rayos que inciden en él (blanco).

Figura 10. Imagen con diversos niveles de gris

En el proceso de digitalización es preciso determinar el valor de N y M así como el número de niveles de gris asignados para cada píxel. Es una práctica común en el proceso de digitalización de imágenes que estas cantidades sean números enteros potencias de dos. Para calcular el número de bits nb requeridos para almacenar la imagen digitalizada se hace uso de la siguiente ecuación, siendo  $2^g$  el número de niveles de gris:

$$nb = MNg$$

Ecuación 2. Cálculo del número de bits necesarios para almacenar una imagen

Por último cabe destacar el concepto de resolución, que está asociado al número de muestras y niveles de gris necesarios para tener una buena aproximación de la imagen. La resolución de una imagen se mide en ppp (píxel por pulgada) y es tenido en cuenta para medir la calidad de una imagen.

#### I.3.2 La retina de silicio

Emular la retina electrónicamente es uno de los mayores objetivos de los ingenieros electrónicos neuromórficos desde el inicio de los tiempos. Cuando Fukushima y su grupo (Fukushima et al. 1970) demostraron su modelo discreto de la retina, se generó una gran expectación aunque el impacto en la industria fue minúsculo. En la ingeniería neuromórfica se ha realizado un gran esfuerzo en los últimos 20 años para convertir esos primeros prototipos de los laboratorios en dispositivos comerciales que pueden ser incluidos en aplicaciones reales.

#### I.3.2.1 Retinas biológicas

La retina es una estructura compleja con tres capas primarias: la capa foto-receptora, la capa plexiforme externa y la capa plexiforme interna (Werblin & Dowling 1969; Masland 2001; Kuffler 1953). La capa foto-receptora contiene dos tipos de células: los conos y los bastones, los cuales transforman la luz que entra en una señal eléctrica que afecta a la liberación de los neurotransmisores en las sinapsis de salida del foto-receptor. Las células foto-receptoras a su vez conducen las células horizontales y bipolares en la capa plexiforme externa. Las dos principales clases de células bipolares, las células ON y OFF, codifican por separado los cambios de contrate espacio-temporal del brillo y oscuridad. En la capa plexiforme externa, las células bipolares ON y OFF realizan la sinapsis con diversos tipos de células amacrinas y con varios tipos de células ganglionares en la capa plexiforme interna.

Figura 11. Diagrama de una sección transversal de la retina

Las retinas biológicas tienen muchas características deseables de las que carecen las cámaras convencionales, de las cuales vamos a mencionar dos que han sido incorporadas en las retinas de silicio. En primer lugar, los ojos operan sobre un amplio rango dinámico (RD) de intensidad de luz, permitiendo la visión en condiciones de iluminación muy variada. Por otro lado, las células de las capas plexiformes interna y externa codifican el contraste espacio temporal, eliminando así la información redundante y permitiendo a las células codificar las señales dentro de su limitado RD (Barlow 1961).

#### I.3.2.2 Retinas AER

La naturaleza asíncrona de la salida AER está inspirada en la forma en que las neuronas se comunican. Mejor que muestrear los valores de los píxeles, los píxeles de la retina AER escriben asíncronamente en la salida sus direcciones (dirección del evento) cuando ellos detectan una señal significante. La definición de "significante" depende del tipo de píxel, pero

en general, el número de eventos a la salida de estos sensores deberían de ser menor que los valores analógicos obtenidos a la salida de un sensor visual típico. En otras palabras, los píxeles de una retina determinan asíncronamente su propia región de interés (ROI), una tarea que por ejemplo en los sistemas de visión convencionales se deja para un procesado algorítmico y comúnmente pesado en términos computacionales.

Las retinas AER pueden ser divididas generalmente en las siguientes clases:

- <u>Contraste espacial</u>: Estos sensores reducen la redundancia espacial basada en las relaciones de intensidad versus a los sensores de diferencia espacial los cuales utilizan las diferencias de intensidad. Este tipo de sensor es especialmente útil para analizar el contenido de escenas estáticas con el fin de obtener características y reconocer objetos.

- <u>Contraste temporal</u>: Estos sensores reducen la redundancia temporal basada en los cambios relativos de intensidad a diferencia de los sensores de diferencia temporal que utilizan los cambios absolutos de intensidad. Este tipo de sensor se utiliza en escenas dinámicas con iluminación uniforme para aplicaciones de seguimiento de objetos y navegación.

Actualmente en la literatura científica se pueden encontrar cuatro tipos más significativos de retinas de silicio: el sensor de visión dinámica (DVS7) (Lichtsteiner et al. 2008; Serrano-Gotarredona & Linares-Barranco 2013; Guo & Chen 2016), el sensor de imagen asíncrona basada en el tiempo (ATIS8) (Posch et al. 2008), la retina Magno-Parvo (Zaghloul & Boahen 2004a; Zaghloul & Boahen 2004b), el sensor de imagen biométrica Octopus (Culurciello et al. 2003), y el sensor de contraste espacial y orientación (VISe) (Rüedi et al. 2003). Particularmente en el presente trabajo se hará uso de un sensor DVS (Serrano-Gotarredona & Linares-Barranco 2013), por lo que se procederá a explicar con un poco más de detalle este tipo de sensor.

#### Sensor de Visión Dinámica

El sensor DVS responde asíncronamente a los cambios relativos temporales de intensidad lumínica. El sensor tiene como salida un flujo asíncrono de direcciones de eventos (AEs<sup>9</sup>) que codifican los cambios de reflectancia en la escena, reduciendo así la redundancia de datos mientras se preserva una precisa información temporal. Estas propiedades se consiguen modelando las siguientes propiedades claves de la visión biológica: dispersión, salida basada

<sup>&</sup>lt;sup>7</sup> Dynamic Vision Sensor

<sup>&</sup>lt;sup>8</sup> Asynchronous Time-based Image Sensor

<sup>&</sup>lt;sup>9</sup> Adress Events

en eventos, representación de los cambios de luminancia relativa y la rectificación de señales positivas y negativas en diferentes canales de salida. Este tipo de sensor ha sido utilizado en varias aplicaciones: Seguimiento de una bola a alta velocidad en un robot portero (Delbruck & Lichtsteiner 2007), detección y seguimiento de las manos de un conductor al volante (Rios-Navarro et al. 2012), cálculo de la velocidad de un motor en tiempo real (Rios-Navarro et al. 2015), robot que mantiene en equilibrio un lápiz (Conradt et al. 2009) entre otras. Muchos de los proyectos desarrollados con este sensor pueden encontrase implementados en un proyecto open-source llamado jAER (jAER 2007), que está enfocado al procesado por eventos. En la Figura 12 se puede ver una salida de un sensor DVS visualizado en esta aplicación.

Figura 12. Representación en jAER de la salida de un sensor DVS frente a una mano en movimiento

# I.4 Procesamiento de audio. El habla

Otro de los principales sentidos que posee el ser humano, como otras muchas especies animales, es la audición o el oído. A través de este sentido muchos seres vivos son capaces de obtener ondas acústicas del entorno en el que se encuentran, además es fundamental para la comunicación mediante sonido. En el caso del ser humano esta comunicación es conocida como el habla.

La comunicación mediante habla es uno de las capacidades más básicas y esenciales procesadas por el ser humano. El habla puede ser considerada como el mecanismo más importante con el que las personas pueden realmente transmitir información sin la necesidad de utilizar ninguna herramienta. La onda del habla no es una onda simple, ya que lleva

consigo información lingüística, características vocales y la emoción del emisor. El intercambio de información mediante el habla juega un rol claramente esencial en nuestras vidas.

Atendiendo a la historia, en 1875, Alexander Graham Bell le comenta a su asistente (Laboratories & Schindler 1975); "Watson, tengo otra idea que aún no te he comentado que creo que te sorprenderá. Si puedo obtener un mecanismo que sea capaz de convertir la variación de la corriente eléctrica en su intensidad como el aire varía en densidad cuando un sonido está pasando a través de él, yo puedo telegrafiar cualquier sonido, incluso el sonido del habla". Esto, comúnmente se conoce como el concepto base del teléfono, pero hay que apuntar que en 1854, Antonio Meucci, construyó el teletrófono (Schiavo 1958), que posteriormente fue bautizado como teléfono. Debido a su carencia económica fue incapaz de patentar su invento por lo que no pudo defenderlo contra futuras invenciones.

Figura 13. Primera patente de un teléfono por Alexander Graham Bell

La invención del teléfono no constituye sólo la época más importante de la historia de las comunicaciones, sino que también representa el punto de partida en el que el habla se convierte en un objetivo de la ingeniería. Para satisfacer este objetivo, la evolución en el procesamiento de audio a lo largo de la historia ha jugado un papel fundamental, teniendo como punto de inflexión el paso del procesamiento analógico al digital. El audio digital comprende nuevos conceptos y técnicas distintas a las utilizadas en la tecnología analógica, y con los computadores y sistemas de procesamiento actuales es mucho más simple trabajar con la representación digital de una señal que con la señal misma.

Actualmente podemos encontrar sistemas que realizan procesamiento del habla en ámbitos muy diversos. Muchas entidades poseen sistemas automáticos para la atención básica de sus usuarios a través del teléfono. Existen aplicaciones de dictado en las que se traduce la

voz del usuario en las frases que está dictando. También son comúnmente conocidos los asistentes inteligentes Siri<sup>10</sup> y Cortana<sup>11</sup>, integrados en algunos teléfonos móviles y en el sistema operativo Windows 10, que nos permiten interactuar con el sistema a través de la voz.

### I.4.1 Conversión analógico-digital

Lo expuesto en este apartado se entiende que son conocimientos básicos para el lector, pero se repasa de manera global por el hecho de que se trata de un mecanismo utilizado por uno de los sensores que se usan en este trabajo.

La conversión analógico-digital, comúnmente conocida como digitalización, consiste en los procesos de muestreo, cuantificación y codificación. El muestreo es el proceso para representar una señal continua y variable como una secuencia periódica de valores. La cuantificación implica la representación aproximada de los valores de la forma de onda por uno de los valores de un conjunto infinito. Por último, la codificación consiste en asignar un número a cada valor. Para esta última tarea, la codificación binaria es comúnmente utilizada. A continuación se explicarán cada uno de estos procesos aunque no se entrará a un gran nivel de detalle debido a que no es objetivo de este trabajo tal efecto.

#### I.4.1.1 Muestreo

En el proceso de muestreo, una señal analógica x(t) es convertida en una secuencia (secuencia muestreada) de valores  $\{x_i\} = \{x(iT)\}$  en un tiempo periódico  $t_i = iT$  (siendo i un número entero). T [s] es el periodo de muestreo, y su homóloga, S = 1/T [Hz] es denominada frecuencia de muestreo. Si T es demasiado grande, se puede perder información y por tanto la señal original no puede ser reproducida a partir de la secuencia muestreada, y a la inversa, si T es muy pequeña, podemos llegar a tener sobre-información por lo que muestras inservibles de la conversión de la señal original son introducidas en la secuencia de muestras resultantes.

<sup>&</sup>lt;sup>10</sup> Asistente inteligente de Apple

<sup>&</sup>lt;sup>11</sup> Asistente inteligente de Microsoft

Figura 14. Muestreo en el dominio del tiempo

### I.4.1.2 Cuantificación y codificación

Durante la cuantificación, todo el rango de amplitud continua es dividido en sub-rangos finitos, así pues a las amplitudes que están en el mismo sub-rango se les asignará el mismo valor de amplitud. La Figura 15 muestra un ejemplo de características de entrada/salida de una cuantificación de 8 niveles (3 bits), donde  $\Delta$  es el tamaño del paso de cuantificado. En este ejemplo, cada codificación es asignada de la forma que representa el valor de la amplitud. Las características de la cuantificación depende tanto del número de niveles como del tamaño del paso de cuantificado. Cuando se va a cuantificar la señal utilizando B bits, el número máximo de niveles será  $\Delta$  y  $\Delta$  son seleccionados simultáneamente con el fin de cubrir adecuadamente el rango de la señal. Si asumimos que  $\Delta$  y  $\Delta$  son seleccionados de establecer:

$$2x_{max} = \Delta 2^B$$

Ecuación 3. Selección de los parámetros Δ y B para la cuantificación

La diferencia entre el valor muestreado después de la cuantificación  $x_i'$  y el valor de la señal original  $x_i$ , es llamado error de cuantificación, distorsión de la cuantificación o ruido de cuantificación.

$$e_i = x_i' - x_i$$

Ecuación 4. Error de cuantificación

Figura 15. Ejemplo de las características de entrada-salida de una cuantificación de 8 niveles

### I.4.2 Sistemas de audio neuromórficos

La cóclea es el sensor de audio de la biología, capaz de convertir variaciones de presión del aire en una señal neuronal pulsante. En el campo de la ingeniería neuromórfica podemos encontrar varios tipos de cócleas artificiales, entre las que se pueden destacar las de silicio y las digitales implementadas en FPGA<sup>12</sup>. Ambas soluciones tienen a la salida el mismo tipo de codificación (AER) para la descomposición de la señal original en cada canal de frecuencia.

#### I.4.2.1 La cóclea biológica

La cóclea biológica es una estructura huesuda, en forma de espiral y llena de fluido que compone la mayoría del oído interno. Realiza la traducción entre la señal de presión, que representa la entrada acústica y las señales neuronales pulsantes que llevan la información al cerebro. En la Figura 16 se muestra la localización relativa de la cóclea con otros elementos importantes del oído humano.

La cóclea se enrolla en espiral desde la base (vuelta más baja) hasta el ápice (vuelta más alta) y contiene aproximadamente 2.5 vueltas. Dentro, la cóclea se divide en tres cámaras: la rampa vestibular, el conducto medio y el conducto timpático; la membrana Reissner separa la primera de la segunda cámara y la membrana basilar (BM¹³) separa la segunda de la tercera cámara. Encima de la BM se sitúa el órgano de Corti, que contiene las células ciliadas del oído

<sup>&</sup>lt;sup>12</sup> Field Programmable Gate Array

<sup>&</sup>lt;sup>13</sup> Basilar Membrane

tanto internas como externas (IHC<sup>14</sup> y OHC<sup>15</sup>). Las extremidades de estas células son estereocilios parecidos a pequeños vellos. Los cambios de direcciones de las estereocilias de IHC generan señales neuronales pulsantes que viajan hacia el cerebro (Meddis 1986; Meddis 1988). Las señales neuronales pulsantes provenientes del cerebro pueden alterar la longitud y anchura de los cuerpos de las células OHC.

Figura 16. El oído humano

La BM cambia tanto en anchura como en rigidez, estrecha y rígida en la base, y ancha y flexible en el ápice. Estos cambios en las características físicas de la BM asisten a como la cóclea divide una señal de entrada en sus componentes frecuenciales. En la base de la cóclea las características de la BM son tales que responden mejor a estímulos de altas frecuencias, mientras que en el ápice responde mejor a los estímulos de bajas frecuencias.

#### I.4.2.2 El sistema de audición neuromórfico AER (NAS)

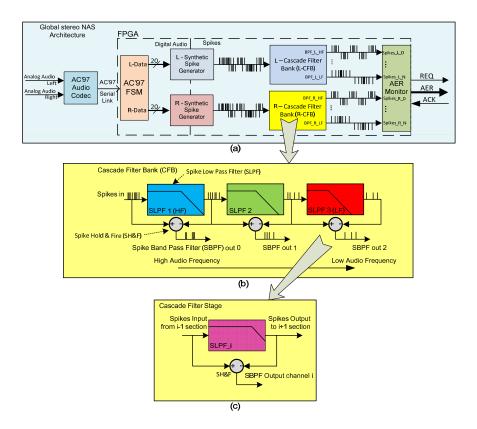

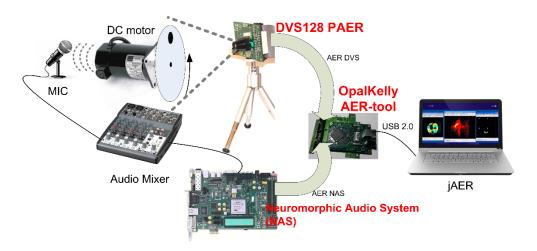

En el presente trabajo se utiliza el sensor de audio neuromórfico (NAS¹6) que es implementado digitalmente en una FPGA (Jimenez-Fernandez et al. 2016) en vez de la cóclea de silicio, por lo que se procede a explicarla arquitectura y funcionamiento del NAS. La Figura 18 (a) muestra la arquitectura global del NAS correspondiente a un sistema biaural o estéreo. El propósito de este sensor es descomponer dos señales digitalizadas (señales correspondientes al oído izquierdo y derecho) en un conjunto de bandas (correspondientes a frecuencias determinadas) que previamente son convertidas en secuencia de pulsos o spikes. La descomposición de las señales en cada una de las bandas correspondientes se lleva a cabo

<sup>&</sup>lt;sup>14</sup> Inner Hair Cells

<sup>&</sup>lt;sup>15</sup> Outer Hair Cells

<sup>&</sup>lt;sup>16</sup> Neuromorphic Auditory Sensor

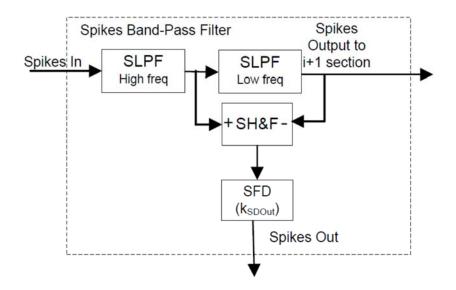

por dos bancos de filtros en el dominio pulsante SLPF<sup>17</sup> (Jimenez-Fernandez et al. 2010; Dominguez-Morales et al. 2011) conectados en cascada. La salida del sensor es codificada utilizando la representación por dirección del evento AER, tal y como la retina de silicio explicada anteriormente.

Para la descomposición de cada señal de entrada (izquierda y derecha) se realiza el mismo procesamiento. Este procesamiento es modelado utilizando un banco de filtros basados en el dominio pulsante dispuestos en cascada (CFB¹8). Cada CFB posee varias etapas donde cada una de ellas se corresponde con un SLPF y un SH&F¹9 (Jimenez-Fernandez et al. 2010) capaces de extraer dos secuencias de pulsos, una que pasa como entrada a la siguiente etapa y otra que es la correspondiente a la señal filtrada por la etapa actual. Como en otras implementaciones de Cócleas (Liu et al. 2010; Leong et al. 2003; Clive & Lyon 1992; Lyon & Mead 1988), varias etapas de filtros paso de baja conectados en cascada sustraen la información relevante eliminando aquella correspondiente a las frecuencias que están fuera de banda, obteniendo una respuesta equivalente a filtros paso de banda.

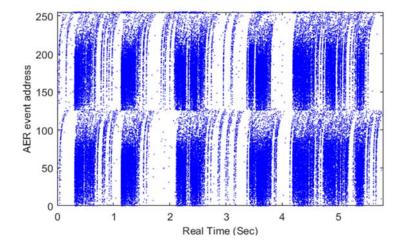

Figura 17. Representación de la salida del NAS

Atendiendo a la arquitectura global del NAS mostrada en la Figura 18 (a), el primer elemento que aparece en la cadena de conversión es el códec de audio AC97, éste tiene como entrada las dos señales analógicas (izquierda y derecha), las cuales que son digitalizadas y

<sup>&</sup>lt;sup>17</sup> Spike Low Pass Filter

<sup>&</sup>lt;sup>18</sup> Cascade Filter Bank

<sup>&</sup>lt;sup>19</sup> Spike Hold and Fire

multiplexadas en un canal de salida. Esta señal de salida es dividida con el fin de obtener los valores muestreados y digitalizados correspondientes a cada señal de entrada. En este punto, el procesamiento para cada una de esas muestras es común para ambas señales (izquierda y derecha). Es aquí donde se realiza el cambio del contexto digital al pulsante utilizando un generador sintético de pulsos RBSSG (Jimenez-Fernandez et al. 2010). A la salida del generador de pulsos se obtienen los pulsos positivos y negativos que codifican el valor digital anteriormente muestreado.

Figura 18. (a) Arquitectura general del NAS. (b) Banco de filtros dispuestos en cascada, CFB. (c) Etapa básica del CFB

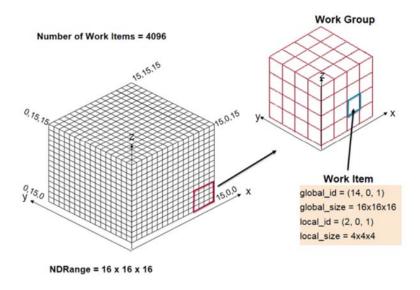

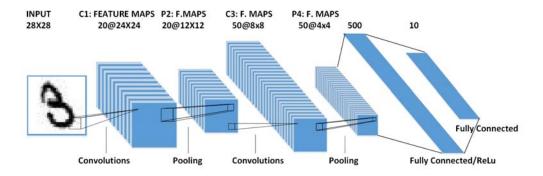

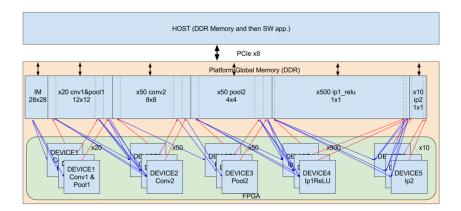

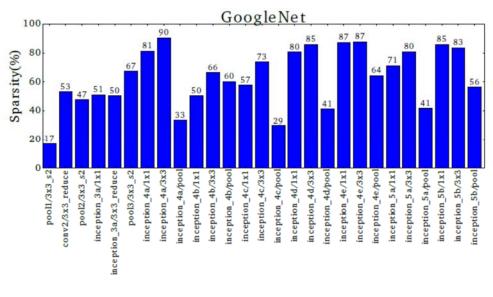

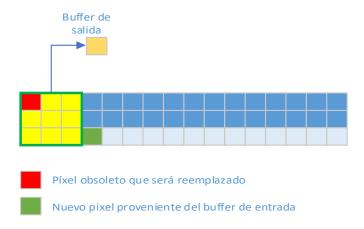

Ese tren de pulsos es la entrada al banco de filtros pulsantes dispuestos en cascada CFB. La Figura 18 ¡Error! No se encuentra el origen de la referencia.(b) muestra cómo están distribuidos esos filtros formando dicho banco, donde los primeros filtros se corresponden a los de alta frecuencia mientras que los últimos se corresponden a los de baja frecuencia. Como se comentaba anteriormente, el banco de filtros pulsantes están divididos en etapas, donde cada etapa se corresponde con un filtro pulsante paso de baja junto con un SH&F (Figura 18