## Hugo Alexandre de Andrade Serra

Mestre em Engenharia Electrotécnica e de Computadores

# Analysis and Design Methodologies for Switched-Capacitor Filter Circuits in Advanced CMOS Technologies

Dissertação para obtenção do Grau de Doutor em Engenharia Electrotécnica e de Computadores

| Orientador:    | Nuno Filipe Silva Veríssimo Paulino,                                             |

|----------------|----------------------------------------------------------------------------------|

| Co-orientador: | Prof. Auxiliar, Universidade Nova de Lisboa<br>Rui Manuel Leitão Santos Tavares, |

|                | Prof. Auxiliar, Universidade Nova de Lisboa                                      |

|             | Júri:                                |

|-------------|--------------------------------------|

| Presidente: | Paulo da Costa Luís da Fonseca Pinto |

| Arguentes:  | Nuno Cavaco Gomes Horta              |

|             | João Pedro Abreu de Oliveira         |

| Vogais:     | Jorge Manuel Correia Guilherme       |

|             | Andrzej Jaszkiewicz                  |

|             | Nuno Filipe Silva Veríssimo Paulino  |

Dezembro, 2017

# Analysis and Design Methodologies for Switched-Capacitor Filter Circuits in Advanced CMOS Technologies

Copyright © Hugo Alexandre de Andrade Serra, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa

A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objectivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

### **ACKNOWLEDGEMENTS**

First of all, I would like to thank my supervisor, Prof. Nuno Paulino, for his dedication, encouragement, and patience throughout the five years of my Ph.D., without his help the work presented in this thesis would not have been possible. I am also grateful to my co-supervisor, Prof. Rui Tavares, for his help and guidance in the development of the optimization software.

I would also like to thank Prof. Manuel Medeiros Silva, for his constructive criticism regarding the structure, organization and writing of my scientific papers; the professors of the electronics group, Prof. João Goes, Prof. João Pedro Oliveira, Prof. Luís Oliveira, and Prof. Maria Helena Fino, for their availability and support; and Nuno Correia for his technical support with the simulation server.

I gratefully acknowledge the financial support received towards my Ph.D. from the Portuguese Foundation for Science and Technology under a Ph.D. Grant (SFRH/BD/87476/2012) and from the European Union's H2020 Programme through project PROTEUS under grant agreement No. 644852. I also acknowledge the Electrical Engineering Department of FCT/UNL and CTS-UNINOVA for providing the necessary conditions to perform the research work.

I am grateful to my colleagues and friends, Edinei Santin, Ivan Bastos, João de Melo, Błażej Nowacki, Somayeh Abdollahvand, Diogo Inácio, Nuno Pereira, Ana Correia, Miguel Fernandes, Ricardo Madeira, Miguel Teixeira and Rogério Rebelo for all the support.

Last but not least I wish to thank my family for their continuous support over the years.

### ABSTRACT

Analog filters are an extremely important block in several electronic systems, such as RF transceivers, data acquisition channels, or sigma-delta modulators. They allow the suppression of unwanted frequencies bands in a signal, improving the system's performance. These blocks are typically implemented using active RC filters,  $g_m$ -C filters, or switched-capacitor (SC) filters.

In modern deep-submicron CMOS technologies, the transistors intrinsic gain is small and has a large variability, making the design of moderate and high-gain amplifiers, used in the implementation of filter blocks, extremely difficult. To avoid this difficulty, in the case of SC filters, the opamp can be replaced with a voltage buffer or a low-gain amplifier (< 2), simplifying the amplifier's design and making it easier to achieve higher bandwidths, for the same power. However, due to the loss of the virtual ground node, the circuit becomes sensitive to the effects of parasitic capacitances, which effect needs to be compensated during the design process.

This thesis addresses the task of optimizing SC filters (mainly focused on implementations using low-gain amplifiers), helping designers with the complex task of designing high performance SC filters in advanced CMOS technologies. An efficient optimization methodology is introduced, based on hybrid cost functions (equation-based/simulation-based) and using genetic algorithms.

The optimization software starts by using equations in the cost function to estimate the filter's frequency response reducing computation time, when compared with the electrical simulation of the circuit's impulse response. Using equations, the frequency response can be quickly computed (< 1 s), allowing the use of larger populations in the genetic algorithm (GA) to cover the entire design space. Once the specifications are met, the population size is reduced and the equation-based design is fine-tuned using the more computationally intensive, but more accurate, simulation-based cost function, allowing to accurately compensate the parasitic capacitances, which are harder to estimate using equations. With this hybrid approach, it is possible to obtain the final optimized design within a reasonable amount of computation time.

Two methods are described for the estimation of the filter's frequency response. The first method is hierarchical in nature where, in the first step, the frequency response is optimized using the circuit's ideal transfer function. The following steps are used to optimize circuits, at transistor level, to replace the ideal blocks (amplifier and switches) used in the first step, while compensating the effects of the circuit's parasitic capacitances in the ideal design. The second method uses a novel efficient numerical methodology to obtain the frequency response of SC filters, based on the circuit's first-order differential equations. The methodology uses a non-hierarchical approach, where the non-ideal effects of the

transistors (in the amplifier and in the switches) are taken into consideration, allowing the accurate computation of the frequency response, even in the case of incomplete settling in the SC branches.

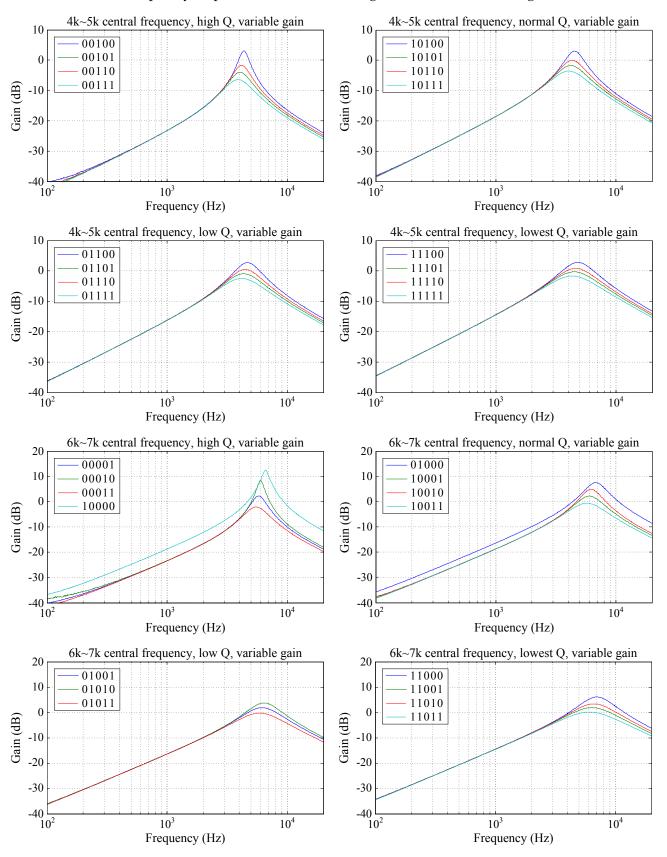

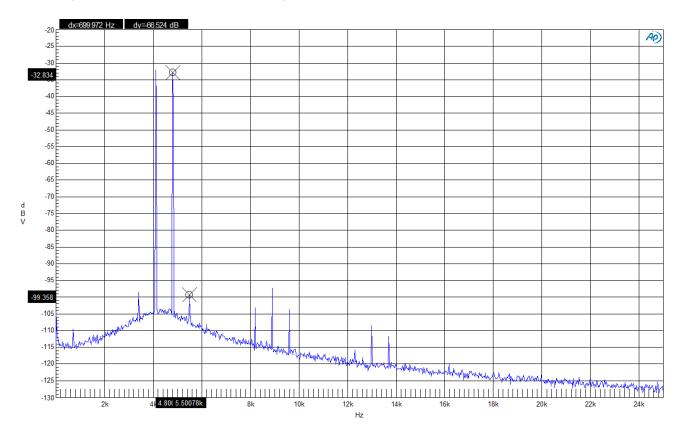

Several design and optimization examples are given to demonstrate the performance of the proposed methods. The prototypes of a second order programmable bandpass SC filter and a 50 Hz notch SC filter have been designed in UMC 130 nm CMOS technology and optimized using the proposed optimization software with a supply voltage of 0.9 V. The bandpass SC filter has a total power consumption of 249  $\mu$ W. The filter's central frequency can be tuned between 3.9 kHz and 7.1 kHz, the gain between -6.4 dB and 12.6 dB, and the quality factor between 0.9 and 6.9. Depending on the bit configuration, the circuit's THD is between -54.7 dB and -61.7 dB. The 50 Hz notch SC filter has a total power consumption of 273  $\mu$ W. The transient simulation of the circuit's extracted view (C+CC) shows an attenuation of 52.3 dB in the 50 Hz interference and that the desired 5 kHz signal has a THD of -92.3 dB.

**Keywords:** Bandpass filter, computer-aided design, Fleischer-Laker topology, genetic algorithms, hybrid cost function, low-gain amplifiers, lowpass filter, notch filter, Sallen-Key topology, switched-capacitor filters.

### RESUMO

Filtros analógicos são um bloco extremamente importante em vários sistemas eletrónicos, como transceptores de rádio frequência, canais de aquisição de dados ou modeladores sigma-delta. Eles permitem a supressão de bandas de frequências indesejadas num sinal, melhorando o desempenho do sistema. Estes blocos são geralmente implementados utilizando filtros RC activos, filtros g<sub>m</sub>-C ou filtros de condensadores comutados.

Nas tecnologias CMOS submicrométricas modernas, o ganho intrínseco dos transístores é pequeno e tem uma grande variabilidade, tornando extremamente difícil o projecto de amplificadores de ganho moderado e elevado, que são necessários para a implementação de blocos de filtragem. Para evitar esta dificuldade, no caso de filtros de condensadores comutados, o amplificador pode ser substituído por um seguidor de tensão ou por um amplificador de ganho reduzido (< 2), simplificando o projecto do amplificador e tornando mais fácil atingir larguras de banda mais elevadas para a mesma potência. No entanto, devido à perda do nó de massa virtual, o circuito torna-se sensível aos efeitos das capacidades parasitas, cujo efeito é necessário compensar durante a fase de dimensionamento.

Esta tese aborda a tarefa de optimizar filtros de condensadores comutados (focando-se principalmente em implementações com amplificadores de ganho reduzido), ajudando engenheiros na tarefa complexa de projectar filtros de condensadores comutados com alto desempenho em tecnologias CMOS avançadas. Uma metodologia de optimização eficiente é introduzida, com base em funções de custo híbridas (baseada em equações/simulações) e utilizando algoritmos genéticos.

O software de optimização começa por utilizar equações na função de custo para estimar a resposta em frequência do filtro, reduzindo o tempo de computação quando comparado com a simulação eléctrica da resposta ao impulso do circuito. Utilizando equações, a resposta em frequência pode ser calculada rapidamente (< 1 s), permitindo o uso de populações maiores no algoritmo genético para cobrir todo o espaço de busca. Uma vez que as especificações sejam cumpridas, o tamanho da população é reduzido e o dimensionamento obtido através de equações é ajustado utilizando simulações transientes na função de custo. Embora seja computacionalmente intensivo, as simulações permitem compensar com precisão as capacidades parasitas, que são mais difíceis de estimar através de equações. Com esta abordagem híbrida, é possível obter o dimensionamento final optimizado num tempo de computação razoável.

Dois métodos são descritos para estimar a resposta em frequência do filtro. O primeiro método usa uma abordagem hierárquica onde, inicialmente, a resposta em frequência é optimizada recorrendo à função de transferência ideal do circuito. As etapas seguintes são utilizadas para optimizar os circuitos, ao nível do transístor, para substituir os blocos ideais (amplificador e interruptores) utilizados no primeiro passo, compensando os efeitos das capacidades parasitas destes blocos no dimensionamento ideal. O segundo método utiliza uma nova metodologia numérica e eficiente para obter a resposta em frequência de filtros de condensadores comutados, com base nas equações diferenciais de primeira ordem do circuito. A metodologia usa uma abordagem não-hierárquica, onde os efeitos não ideais dos transístores (no amplificador e nos interruptores) são tidos em consideração, permitindo a computação precisa da resposta em frequência, mesmo em casos onde o equilíbrio de carga não é atingido antes do final da fase.

Vários exemplos de dimensionamento e optimização são apresentados para demonstrar o desempenho dos métodos propostos. Os protótipos de um filtro de condensadores comutados passa-banda programável de segunda ordem e de um filtro de condensadores comutados rejeita-banda para 50 Hz foram projectados em tecnologia CMOS de 130 nm da UMC e optimizados utilizando o software de optimização proposto com uma tensão de alimentação de 0.9 V. O filtro de condensadores comutados passa-banda tem um consumo de 249  $\mu$ W. A frequência central do filtro é ajustável entre 3.9 kHz e 7.1 kHz, o ganho entre -6.4 dB e 12.6 dB e o factor de qualidade entre 0.9 e 6.9. Dependendo dos bits de configuração a THD do circuito está entre -54.7 dB e -61.7 dB. O filtro de condensadores comutados rejeita-banda de 50 Hz tem um consumo de 273  $\mu$ W. A simulação transiente da vista extraída do circuito (C+CC) mostra uma atenuação de 52,3 dB no sinal interferente de 50 Hz e que o sinal de desejado de 5 kHz possui uma THD de -92,3 dB.

**Palavras-chave:** Algoritmos genéticos, amplificadores de ganho reduzido, desenho assistido por computador, filtros de condensadores comutados, filtro passa-baixo, filtro passa-banda, filtro rejeita-banda, função de custo híbrida, topologia Fleischer-Laker, topologia Sallen-Key.

# **CONTENTS**

| A  | cknov        | wledge  | ments                                                         | v   |

|----|--------------|---------|---------------------------------------------------------------|-----|

| A  | Abstract vii |         |                                                               |     |

| C  | onten        | lts     |                                                               | xi  |

| Li | st of        | Figures |                                                               | xv  |

| Li | st of        | Tables  |                                                               | xix |

| Li | st of        | Abbrev  | riations and Acronyms                                         | xxi |

| 1  | Intr         | oductio | n                                                             | 1   |

|    | 1.1          | Backg   | round and Motivation                                          | 1   |

|    | 1.2          | Resear  | rch Question and Hypothesis                                   | 3   |

|    | 1.3          | Origir  | al Contributions and Publications                             | 3   |

|    | 1.4          | Thesis  | Organization                                                  | 4   |

| 2  | Bac          | kgroun  | d on Switched-Capacitor Filters                               | 7   |

|    | 2.1          | Switch  | ned-Capacitor Filters Building Blocks                         | 7   |

|    |              | 2.1.1   | Switches                                                      | 8   |

|    |              | 2.1.2   | Non-Overlapping Clock Phases                                  | 10  |

|    |              | 2.1.3   | Capacitors                                                    | 10  |

|    |              | 2.1.4   | Operational Amplifiers                                        | 10  |

|    | 2.2          | Switch  | ned-Capacitor Resistor Emulation Networks                     | 11  |

|    |              | 2.2.1   | Parasitic-Sensitive Switched-Capacitor Integrator             | 12  |

|    |              | 2.2.2   | Parasitic-Insensitive Switched-Capacitor Integrator           | 13  |

|    | 2.3          | Noise   | in Switched-Capacitor Circuits                                | 14  |

| 3  | Des          | ign Tec | hniques to Increase Performance of Switched-Capacitor Filters | 17  |

|    | 3.1          | Active  | SC Filters using Capacitance Spread Reduction Techniques      | 17  |

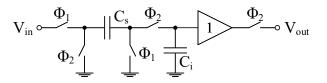

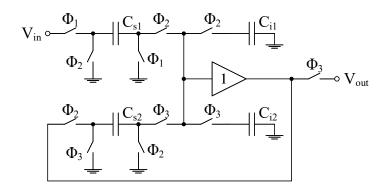

|    |              | 3.1.1   | Basic SC Integrator                                           | 18  |

|    |              | 3.1.2   | SC Integrator using Capacitive T-cell Network                 | 18  |

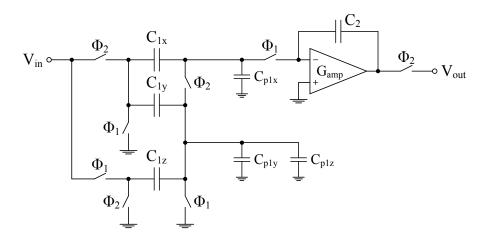

|   |     | 3.1.3   | SC Integrator using Partial Charge Transfer Network                         | 19 |

|---|-----|---------|-----------------------------------------------------------------------------|----|

|   |     | 3.1.4   | SC Integrator using Split Integrating Capacitor Technique                   | 20 |

|   |     | 3.1.5   | SC Integrator using Charge Recombination Technique                          | 22 |

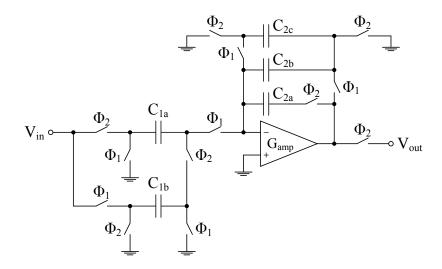

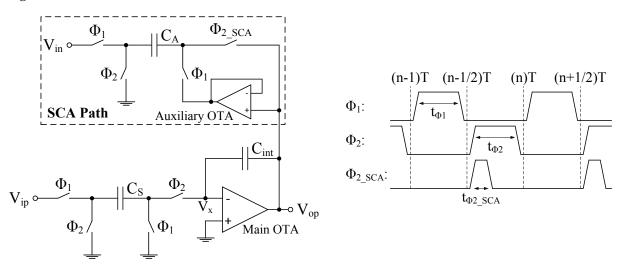

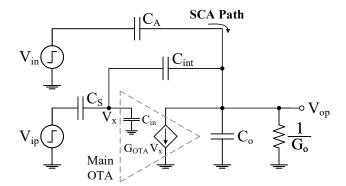

|   | 3.2 | Active  | e SC Lowpass Filter using Switched-Current-Assisting Technique              | 23 |

|   | 3.3 | Virtua  | l Ground Reference Buffer Technique in SC Circuits                          | 25 |

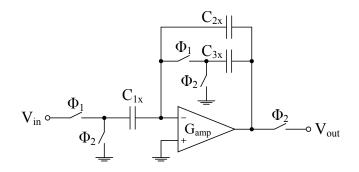

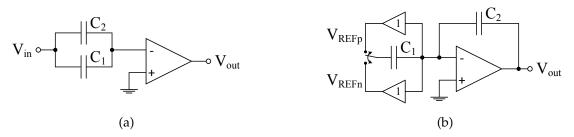

|   | 3.4 | Recyc   | ling SC Buffer Biquad                                                       | 26 |

| 4 | Con | nputer  | Methods for the Analysis and Optimization of Switched-Capacitor Circuits    | 29 |

|   | 4.1 | Noda    | Analysis Method to Obtain the Transfer Function of SC Circuits              | 32 |

|   |     | 4.1.1   | Example: Second-Order Lowpass SC Filter                                     | 34 |

|   | 4.2 | Topol   | ogy Exploration for Optimal Capacitance Sizing in SC Biquads                | 37 |

|   | 4.3 | Optin   | nal Capacitance Sizing of SC Filters using Linear Programming and Simulated |    |

|   |     | Annea   | aling                                                                       | 38 |

| 5 | Ana | lysis N | Iethodologies for the Design of Switched-Capacitor Filters                  | 41 |

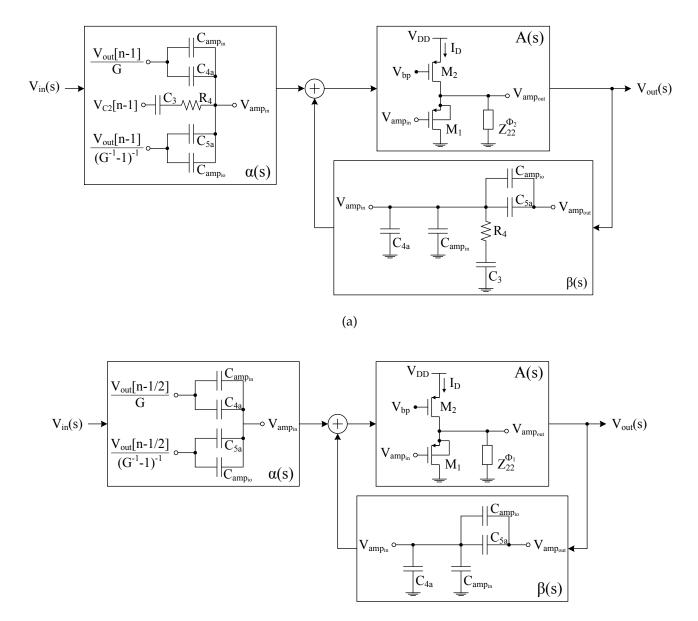

|   | 5.1 | Hiera   | rchical Symbolic Methodology for the Analysis of SC Filters                 | 42 |

|   |     | 5.1.1   | Method Description                                                          | 42 |

|   |     | 5.1.2   | Example: Second-Order Lowpass SC Filter                                     | 45 |

|   | 5.2 | Non-H   | Hierarchical Numeric Methodology for the Analysis of SC Filters             | 53 |

|   |     | 5.2.1   | Method Description                                                          | 53 |

|   |     | 5.2.2   | Example I: First-Order Passive SC Filter                                    | 59 |

|   |     | 5.2.3   | Example II: Second-Order Bandpass SC Filter                                 | 62 |

|   |     | 5.2.4   | Example III: Second-Order Lowpass SC Filter                                 | 64 |

|   | 5.3 | Concl   | usions                                                                      | 67 |

| 6 | Opt | imizati | on Methodologies for the Design of Switched-Capacitor Filters               | 69 |

|   | 6.1 | Optin   | nization Procedure                                                          | 70 |

|   |     | 6.1.1   | Chromosome Evaluation                                                       | 70 |

|   |     | 6.1.2   | Chromosome Grading (Fitness)                                                | 74 |

|   |     | 6.1.3   | Types of Optimization                                                       | 75 |

|   |     | 6.1.4   | Chromosome Reproduction                                                     | 76 |

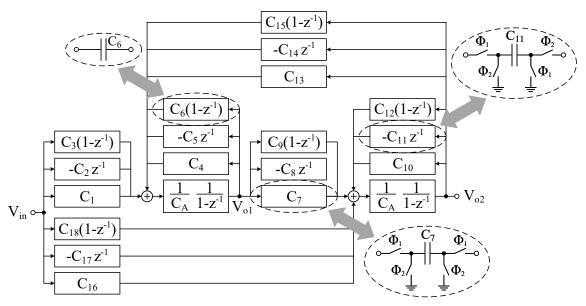

|   | 6.2 | Hiera   | rchical Optimization Methodology                                            | 78 |

|   |     | 6.2.1   | Method Description                                                          | 78 |

|   |     | 6.2.2   | Example I: Second-Order Lowpass SC Filter                                   | 82 |

|   |     | 6.2.3   | Example II: Second-Order Bilinear Bandpass SC Filter                        | 86 |

|   |     | 6.2.4   | Example III: Sixth-Order Bilinear Bandpass SC Filter                        | 90 |

|   | 6.3 | Non-H   | Hierarchical Optimization Methodology                                       | 95 |

|   |     | 6.3.1   | Method Description                                                          | 95 |

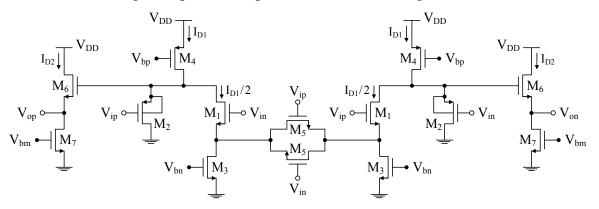

|   |     | 6.3.2   | Example I: Second-Order Lowpass SC Filter                                   | 98 |

|    |       | 6.3.3   | Example II: Second-Order Bandpass SC Filter                                      | 102  |

|----|-------|---------|----------------------------------------------------------------------------------|------|

|    | 6.4   | Conclu  | isions                                                                           | 106  |

| 7  | Swi   | tched-C | Capacitor Filter Prototypes and Measurement Results                              | 107  |

|    | 7.1   | Progra  | mmable Second-Order Bandpass Switched-Capacitor Filter                           | 109  |

|    | 7.2   | 50 Hz   | Notch Switched-Capacitor Filter                                                  | 116  |

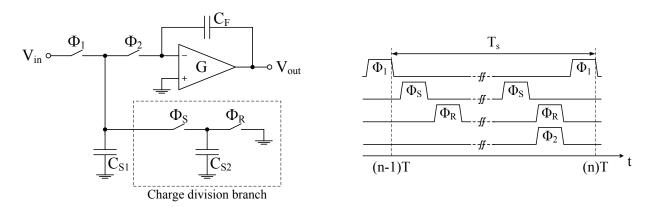

|    |       | 7.2.1   | Parasitic-Sensitive Switched-Capacitor Integrator using a Charge Division Branch | n116 |

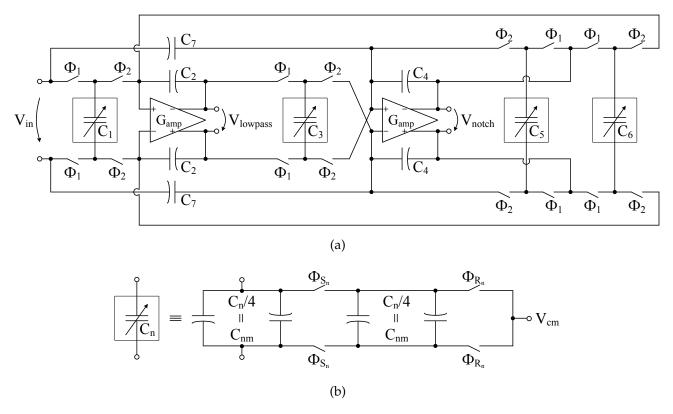

|    |       | 7.2.2   | Notch Switched-Capacitor Filter using Charge Division Branches                   | 117  |

|    | 7.3   | Conclu  | isions                                                                           | 126  |

| 8  | Con   | clusion | s and Future Work                                                                | 129  |

|    | 8.1   | Genera  | al Conclusions                                                                   | 129  |

|    | 8.2   | Future  | Work                                                                             | 131  |

| Bi | bliog | raphy   |                                                                                  | 133  |

# LIST OF FIGURES

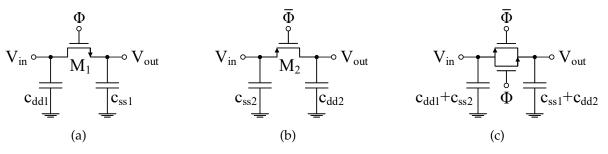

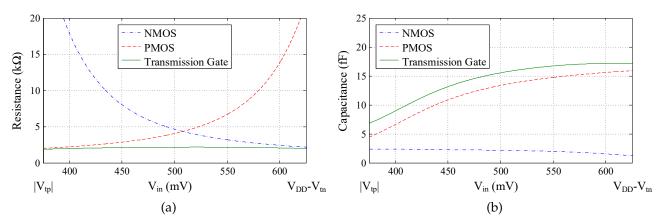

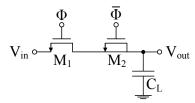

| 2.1  | MOS switches: (a) NMOS, (b) PMOS, (c) Transmission gate.                                                                    | 8  |

|------|-----------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Example of switch (a) $r_{ds}$ resistance and (b) $c_{ss}$ capacitance, as a function of the $V_{in}$ voltage.              | 9  |

| 2.3  | Simple circuit using dummy switch technique.                                                                                | 9  |

| 2.4  | Simple circuit using bottom plate sampling technique                                                                        | 9  |

| 2.5  | Two-phase non-overlapping clock generator: (a) Circuit implementation, (b) Phase scheme.                                    | 10 |

| 2.6  | Non-overlapping clock phase scheme                                                                                          | 11 |

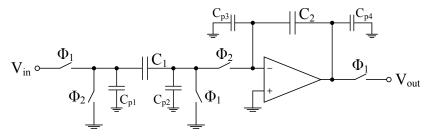

| 2.7  | Parasitic-sensitive switched-capacitor integrator.                                                                          | 12 |

| 2.8  | Parasitic-insensitive switched-capacitor integrator.                                                                        | 13 |

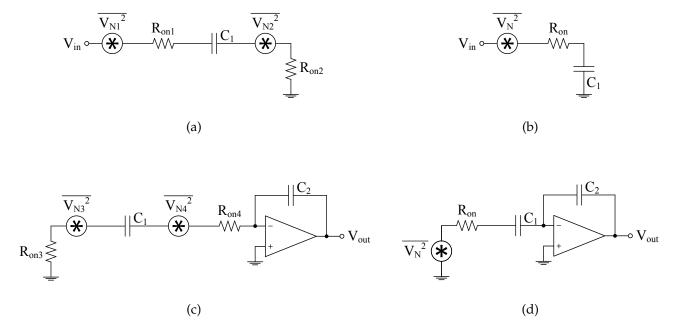

| 2.9  | Equivalent noise circuits during phase: (a) $\Phi_1$ , (b) $\Phi_1$ (simplified), (c) $\Phi_2$ , (d) $\Phi_2$ (simplified). | 15 |

| 3.1  | Basic SC integrator.                                                                                                        | 18 |

| 3.2  | SC integrator using capacitive T-cell network                                                                               | 18 |

| 3.3  | SC integrator using partial charge transfer network.                                                                        | 20 |

| 3.4  | SC integrator using split integrating capacitor technique.                                                                  | 21 |

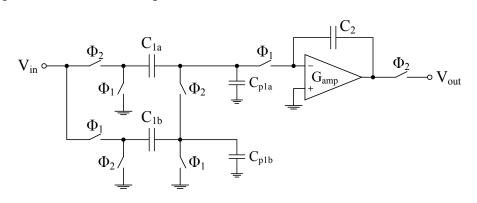

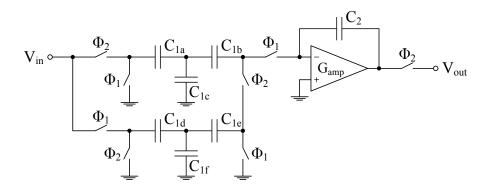

| 3.5  | SC integrator using charge recombination technique.                                                                         | 22 |

| 3.6  | Switched-current-assisting SC integrator.                                                                                   | 23 |

| 3.7  | Small signal equivalent circuit of the SCA SC integrator                                                                    | 24 |

| 3.8  | MDAC using VGRB technique during: (a) sampling phase and (b) transfer phase                                                 | 25 |

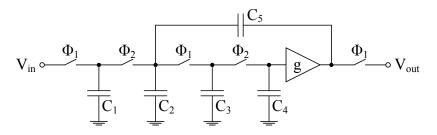

| 3.9  | First-order SC buffer lowpass filter                                                                                        | 26 |

| 3.10 | SC buffer biquad lowpass filter by recycling the buffer.                                                                    | 26 |

| 3.11 | Recycling SC-buffer biquad as a 4th-order SC lowpass filter.                                                                | 27 |

| 4.1  | Second-order lowpass SC filter                                                                                              | 34 |

| 4.2  | Simplified second-order lowpass SC filter                                                                                   | 34 |

| 4.3  | Signal flow graph of the biquad template                                                                                    | 37 |

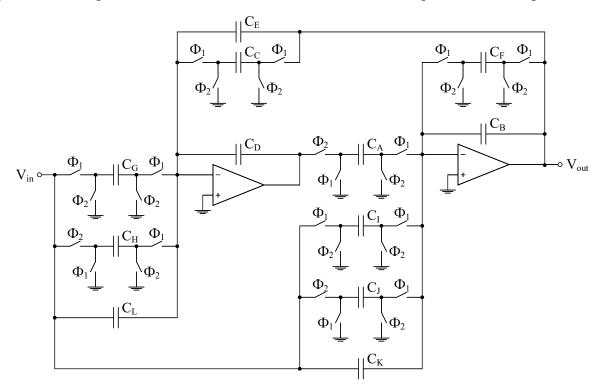

| 4.4  | Fleischer-Laker SC filter.                                                                                                  | 38 |

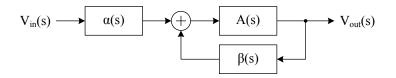

| 5.1  | General closed-loop signal-flow diagram                                                                                     | 42 |

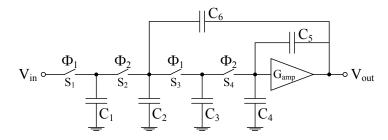

| 5.2  | Second-order lowpass SC filter.                                                                                             | 45 |

| 5.3  | Equivalent circuit during (a) phase $\Phi_1$ and (b) phase $\Phi_2$ .                                                       | 45 |

| 5.4  | Closed-loop diagram during (a) phase $\Phi_2$ and (b) phase $\Phi_1$ .                                                      | 47 |

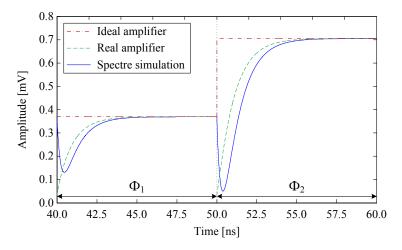

| 5.5  | Time-domain comparison of the amplifier's output node between the closed-loop analysis                  |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | method and the Spectre simulation of the filter during one sampling period                              | 49 |

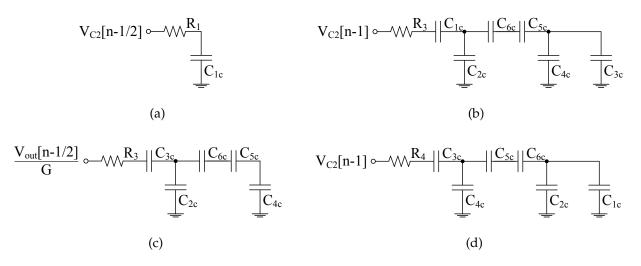

| 5.6  | Circuit used to calculate the switched network time constant using first-order RC approxi-              |    |

|      | mation for switch: (a) $S_1(\Phi_1)$ , (b) $S_2(\Phi_2)$ , (c) $S_3(\Phi_1)$ , and (d) $S_4(\Phi_2)$    | 50 |

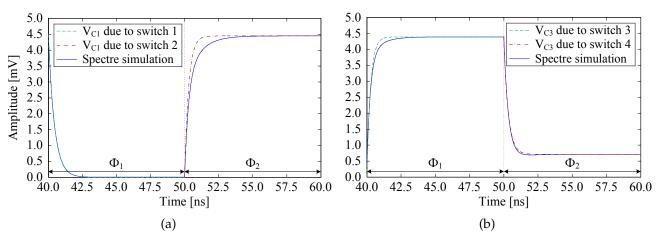

| 5.7  | Time-domain comparison of the switches time constants between the first order RC ap-                    |    |

|      | proximations method and the Spectre simulation of the filter during one sampling period.                | 51 |

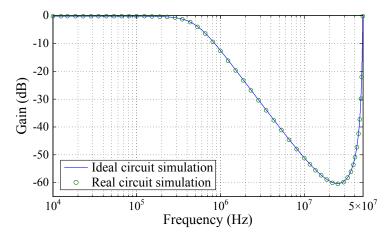

| 5.8  | Frequency response comparison of the SC filter (ideal design Vs. real compensated design).              | 52 |

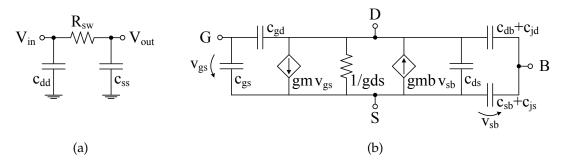

| 5.9  | Transistor model: (a) linear region (switch), (b) saturation region (amplifier).                        | 54 |

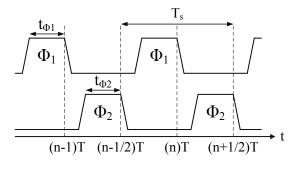

| 5.10 | Non-overlapping clock phases                                                                            | 57 |

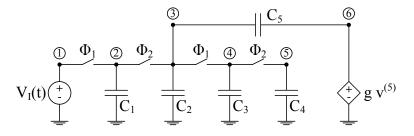

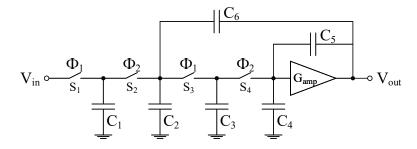

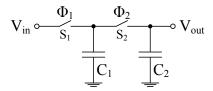

| 5.11 | First-order passive SC filter.                                                                          | 59 |

| 5.12 | First-order passive SC filter considering the switches as resistors.                                    | 59 |

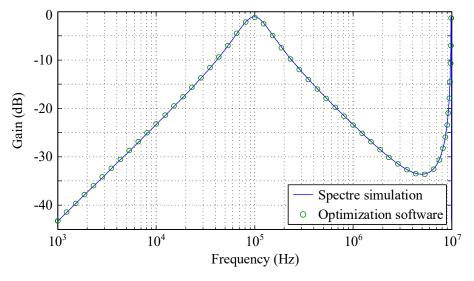

| 5.13 | Frequency response comparison between the Spectre simulation and the proposed non-                      |    |

|      | hierarchical analysis methodology for different values of switch resistance in the circuit of           |    |

|      | Fig. 5.11                                                                                               | 61 |

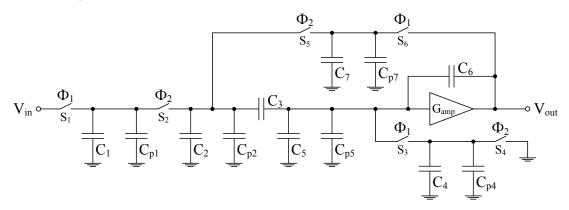

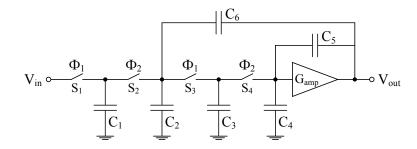

| 5.14 | Second-order bandpass SC filter.                                                                        | 62 |

| 5.15 | Differential voltage-combiner amplifier with source degeneration with a DC level shifter.               | 62 |

| 5.16 | Frequency response comparison between the Spectre simulation and the proposed non-                      |    |

|      | hierarchical analysis methodology of the bandpass filter with (a) complete and (b) incom-               |    |

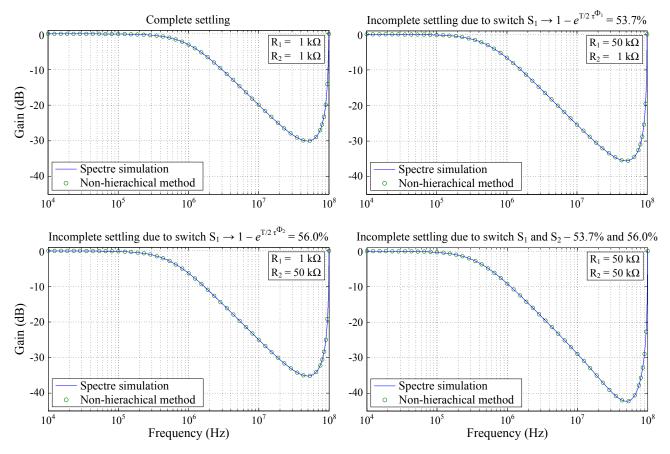

|      | plete settling                                                                                          | 63 |

| 5.17 | Second-order lowpass SC filter.                                                                         | 64 |

| 5.18 | Second-order lowpass SC filter considering the switches as resistors and the amplifier as               |    |

|      | its equivalent medium frequency small signal model.                                                     | 64 |

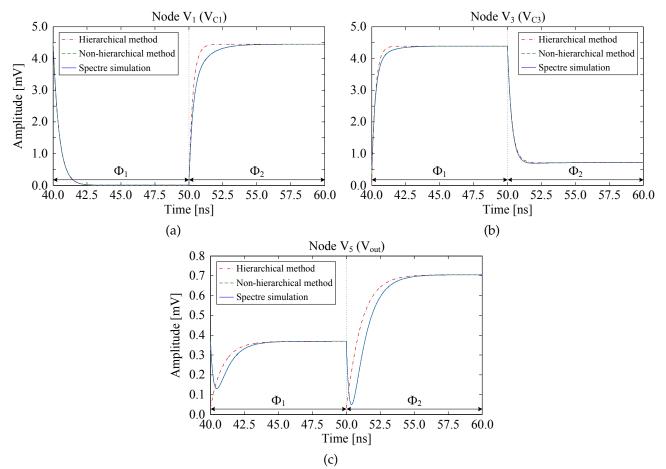

| 5.19 | Time-domain comparison between the hierarchical and non-hierarchical method for nodes                   |    |

|      | (a) $V_1$ ( $V_{C1}$ ), (b) $V_3$ ( $V_{C3}$ ), and (c) $V_5$ ( $V_{out}$ ) during one sampling period. | 65 |

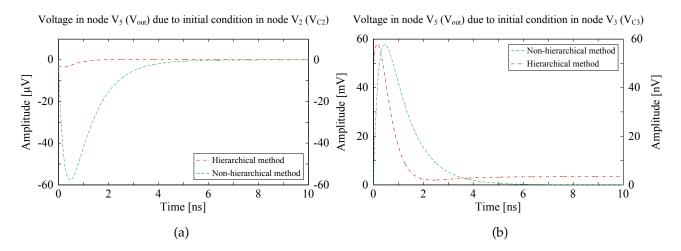

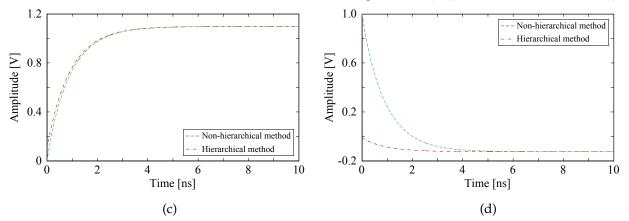

| 5.20 | Effects of the initial conditions on the circuit's output voltage, during phase $\Phi_1$ , with the     |    |

|      | hierarchical and non-hierarchical method                                                                | 66 |

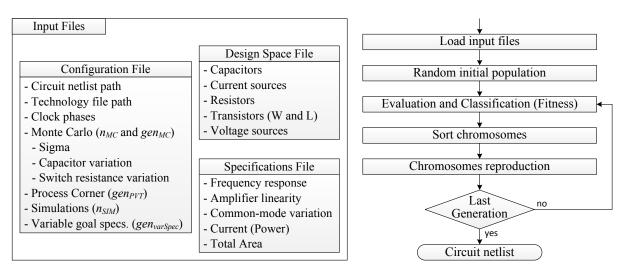

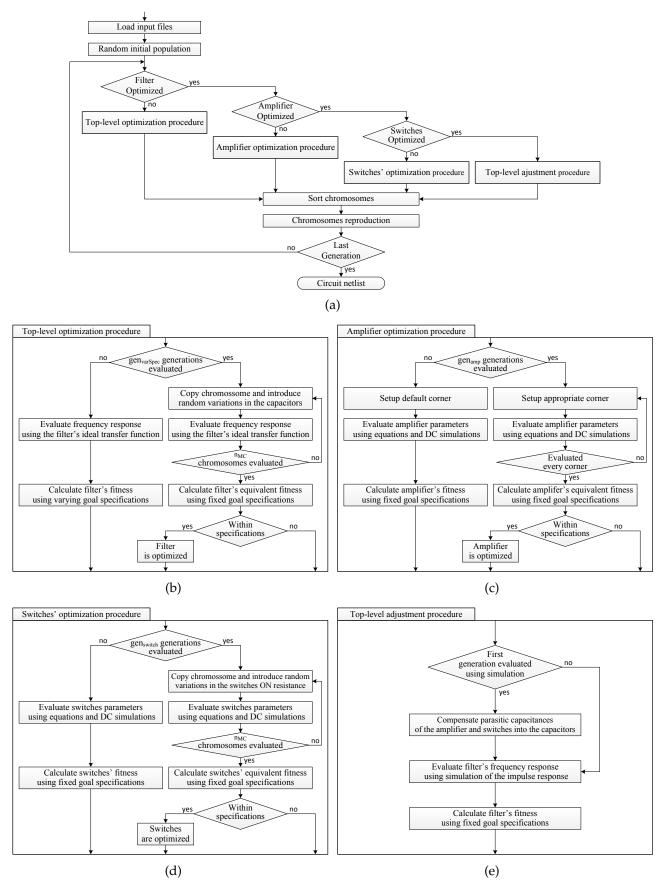

| 6.1  | General design flow of the optimization procedure.                                                      | 71 |

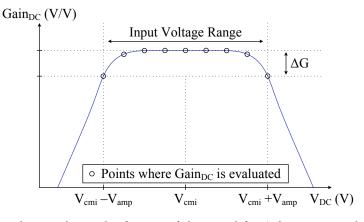

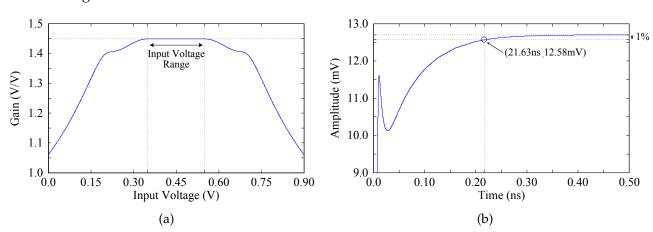

| 6.2  | Indicators used to evaluate the fitness of the amplifier's linearity in the input voltage range.        | 71 |

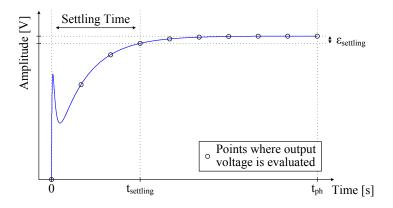

| 6.3  | Indicators used to evaluate the fitness of the amplifier's settling time                                | 72 |

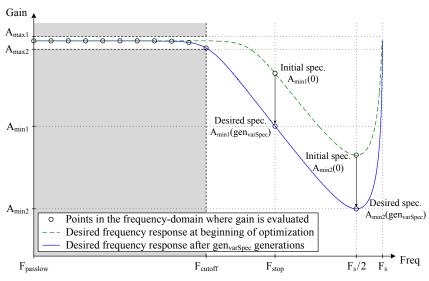

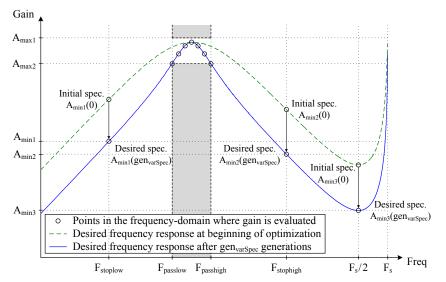

| 6.4  | Indicators used to evaluate the fitness of the frequency response of lowpass SC filters                 | 73 |

| 6.5  | Indicators used to evaluate the fitness of the frequency response of bandpass SC filters.               | 73 |

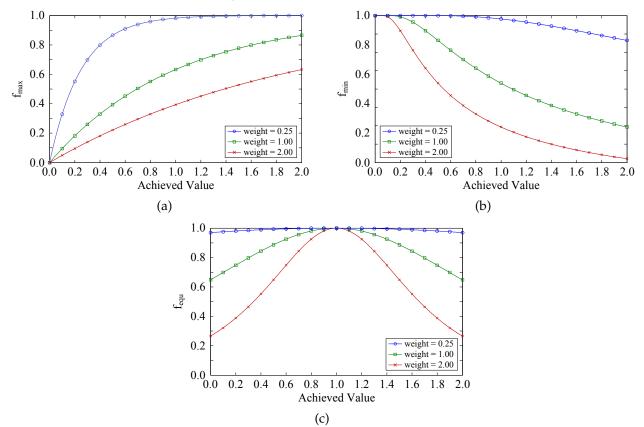

| 6.6  | Fitness function (a) maximize, (b) minimize, and (c) equalize goal as a function of achieved            |    |

|      | for different <i>weight</i> values and <i>desired</i> = $1.0$                                           | 74 |

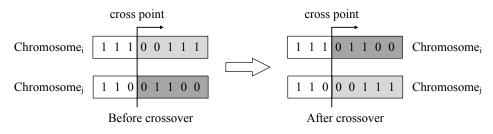

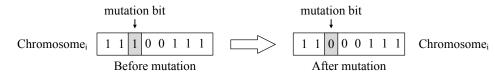

| 6.7  | Example of the one-point crossover operator.                                                            | 77 |

| 6.8  | Example of the mutation operator.                                                                       | 77 |

|      |                                                                                                         |    |

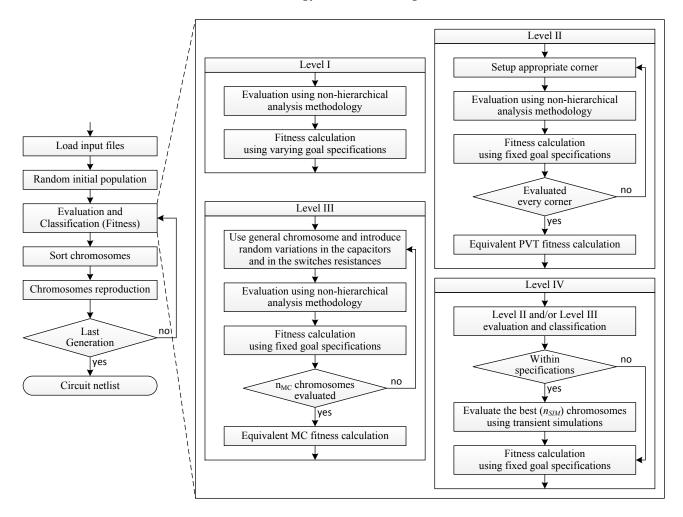

| 6.9  | Flow of the hierarchical optimization methodology: (a) simplified diagram of the optimization  | ı   |

|------|------------------------------------------------------------------------------------------------|-----|

|      | procedure, and diagrams of the (b) ideal filter, (c) amplifier, (d) switches, and (e) complete |     |

|      | filter evaluation and classification procedure.                                                | 79  |

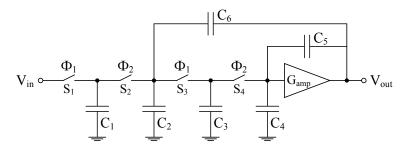

| 6.10 | Second-order lowpass SC filter.                                                                | 82  |

| 6.11 | Differential voltage-combiner amplifier with source degeneration                               | 83  |

| 6.12 | Second-order bilinear bandpass SC filter.                                                      | 86  |

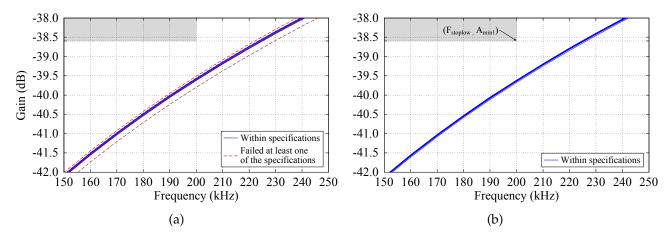

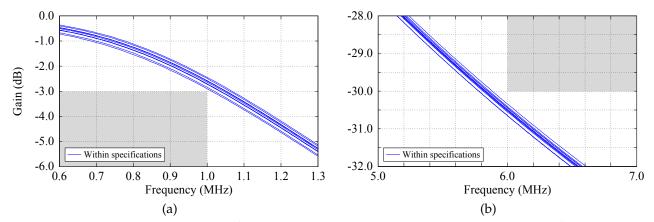

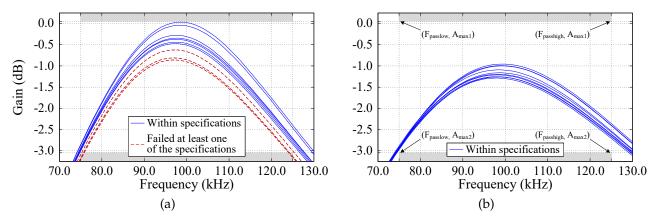

| 6.13 | Frequency response of the best chromosome around the stopband frequency (a) before and         |     |

|      | (b) after the capacitor mismatch optimization                                                  | 87  |

| 6.14 | Frequency response of the best chromosome around the passband frequency (a) before and         |     |

|      | (b) after the capacitor mismatch optimization                                                  | 87  |

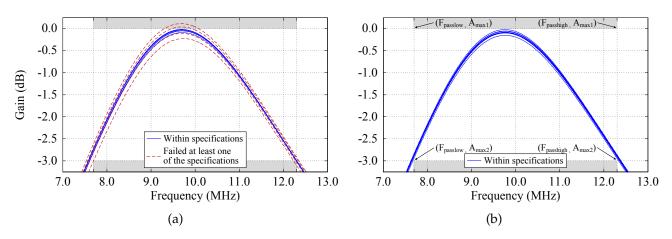

| 6.15 | Closed-loop diagram of the bandpass SC filter during phase $\Phi_1$                            | 88  |

| 6.16 | Simulation results of the (a) amplifier's DC gain and the (b) filter's step response of the    |     |

|      | best chromosome obtained from the amplifier optimization step.                                 | 89  |

| 6.17 | Frequency response of the best chromosome once the optimization process is complete.           | 90  |

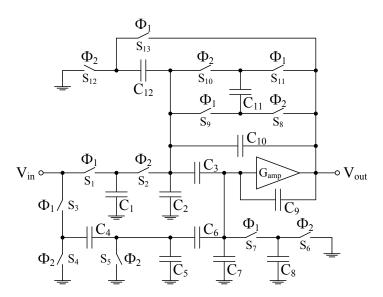

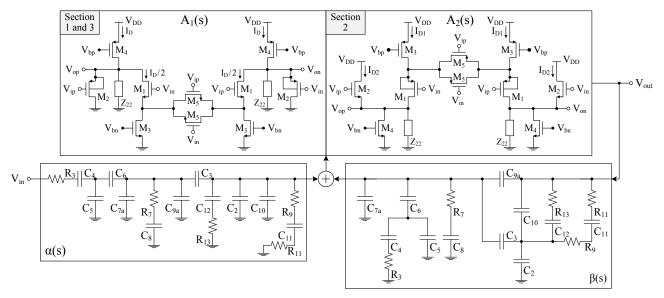

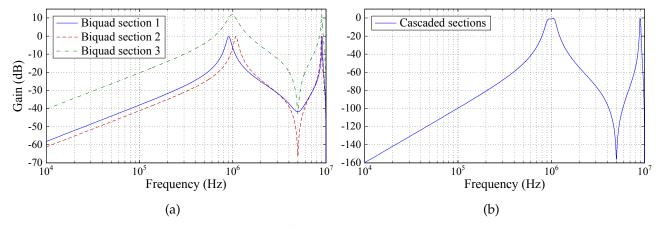

| 6.18 | Bilinear bandpass SC biquad section used to implemented the sixth-order filter                 | 91  |

| 6.19 | Closed-loop diagram of the bandpass SC filter during phase $\Phi_1$                            | 92  |

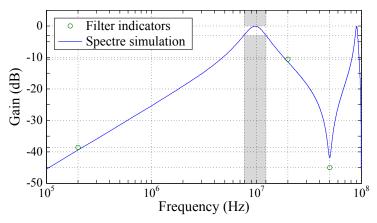

| 6.20 | Frequency response obtained from Spectre: (a) biquad sections, (b) cascaded sections           | 94  |

| 6.21 | Flow of the non-hierarchical optimization methodology.                                         | 96  |

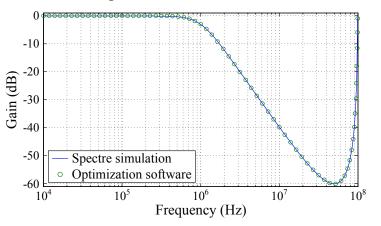

| 6.22 | Second-order lowpass SC filter.                                                                | 98  |

| 6.23 | Frequency response of an arbitrary run once the optimization procedure is complete             | 99  |

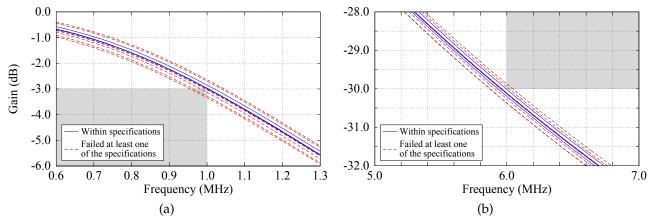

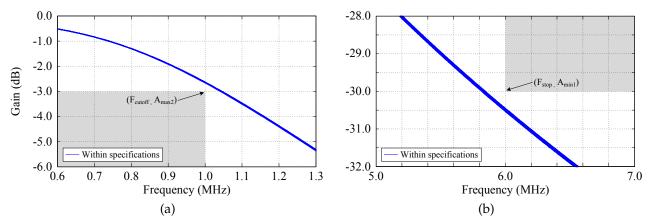

| 6.24 | Frequency response of the best chromosome (a) around the passband frequency and                |     |

|      | (b) around the stopband frequency before the PVT corners and mismatch variations opti-         |     |

|      | mization                                                                                       | 100 |

| 6.25 | Frequency response of the best chromosome (a) around the passband frequency and                |     |

|      | (b) around the stopband frequency after the PVT corners optimization                           | 100 |

| 6.26 | Frequency response of the best chromosome (a) around the passband frequency and                |     |

|      | (b) around the stopband frequency after the PVT corners and mismatch variations opti-          |     |

|      | mization.                                                                                      | 100 |

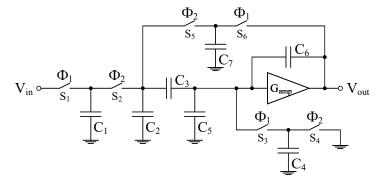

| 6.27 | Second-order bandpass SC filter.                                                               | 102 |

| 6.28 | Differential voltage-combiner amplifier with source degeneration with a DC level shifter.      | 103 |

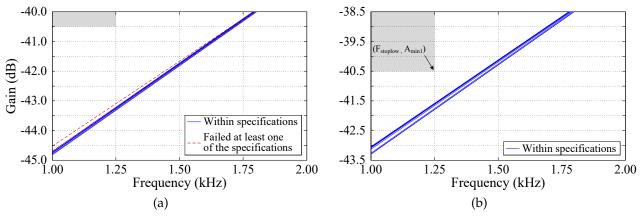

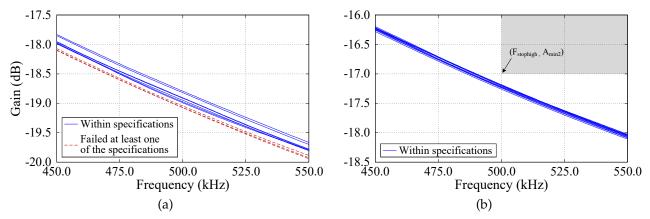

| 6.29 | Frequency response of the best chromosome around the lower stopband frequency (a) be-          |     |

|      | fore and (a) after the PVT corners and mismatch variations optimization                        | 104 |

| 6.30 | Frequency response of the best chromosome around the central frequency (a) before and          |     |

|      | (a) after the PVT corners and mismatch variations optimization                                 | 104 |

| 6.31 | Frequency response of the best chromosome around the higher stopband frequency (a) be-         |     |

|      | fore and (a) after the PVT corners and mismatch variations optimization                        | 105 |

| 6.32 | Frequency response of an optimization run once the optimization procedure is complete.         | 105 |

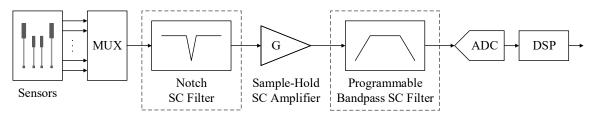

| 7.1  | Simplified diagram of the acquisition channel used in a water management sensor node.                           | 107 |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

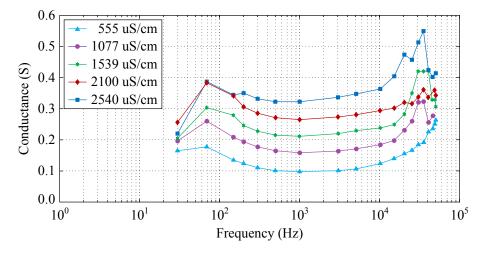

| 7.2  | Frequency response of the sensor's conductance for different conductivity values                                | 108 |

| 7.3  | Programmable second-order bandpass SC filter using a low gain amplifier: Differential                           |     |

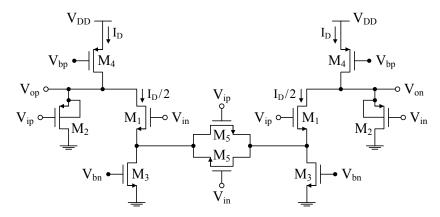

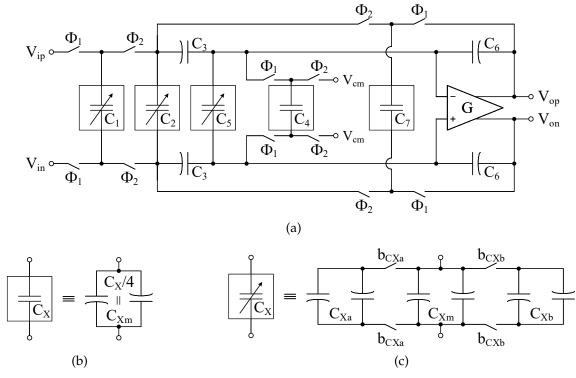

|      | implementation of the (a) filter, (b) capacitor, and (c) programmable capacitor                                 | 109 |

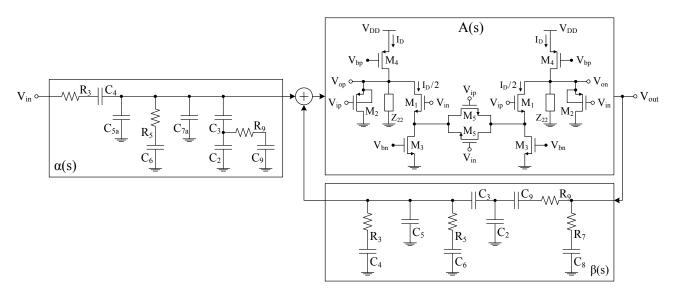

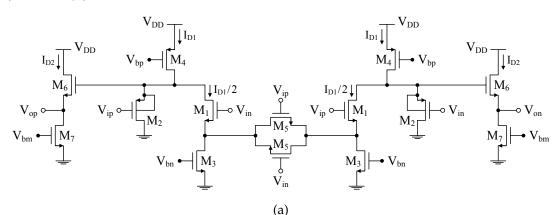

| 7.4  | Voltage-combiner amplifier with source degeneration and DC level shifter: (a) differential                      |     |

|      | implementation of the circuit and (b) biasing circuit.                                                          | 110 |

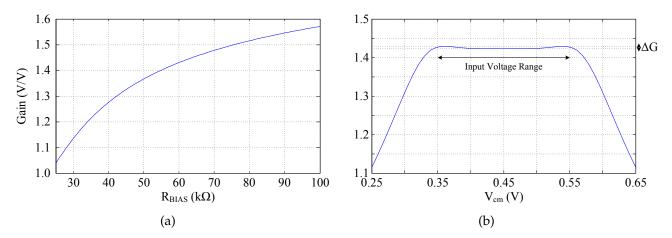

| 7.5  | Voltage-combiner's DC gain as a function of the (a) bias resistance and (b) input common-                       |     |

|      | mode voltage                                                                                                    | 111 |

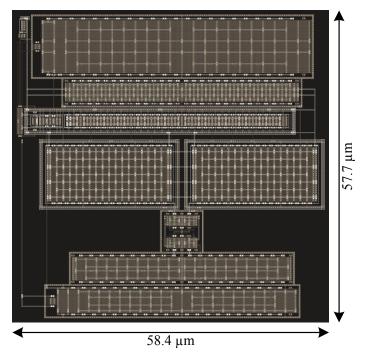

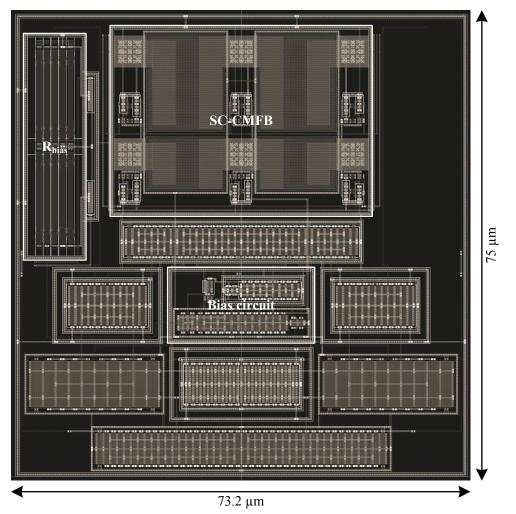

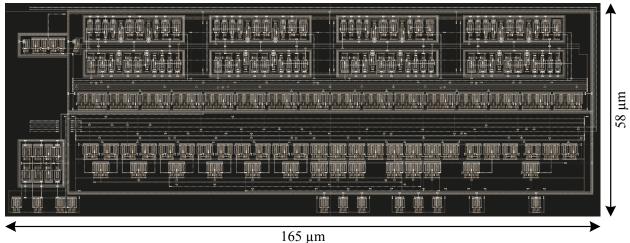

| 7.6  | Layout of the voltage-combiner amplifier with source degeneration and DC level shifter.                         | 112 |

| 7.7  | Layout of the programmable second-order bandpass SC filter                                                      | 112 |

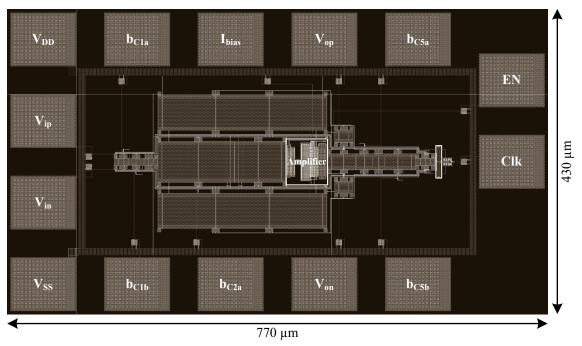

| 7.8  | Programmable second-order bandpass SC filter test board                                                         | 113 |

| 7.9  | Frequency response comparison of the programmable second-order bandpass SC filter in                            |     |

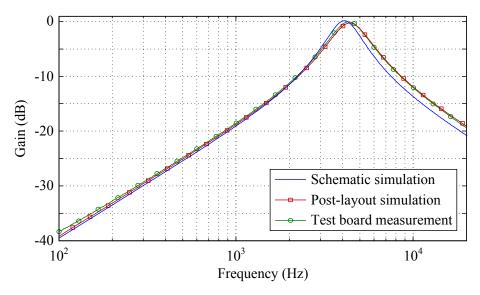

|      | the default bit configuration ( $b_{C1a} = 1$ , $b_{C1b} = 0$ , $b_{C2a} = 1$ , $b_{C5a} = 1$ , $b_{C5b} = 0$ ) | 113 |

| 7.10 | Measured frequency responses of the programmable second-order bandpass SC filter for                            |     |

|      | the different bit codes (bit sequence: $b_{C1a}$ , $b_{C1b}$ , $b_{C2a}$ , $b_{C5a}$ , $b_{C5b}$ ).             | 114 |

| 7.11 | Measured output spectrum of the programmable second-order bandpass SC filter in the                             |     |

|      | default bit configuration for an input with two tones ( $f_1 = 4.1 \text{ kHz}$ and $f_2 = 4.8 \text{ kHz}$ ).  | 115 |

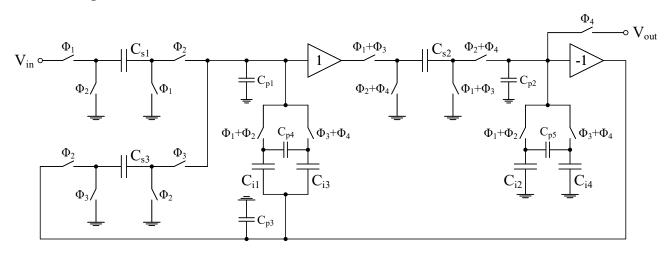

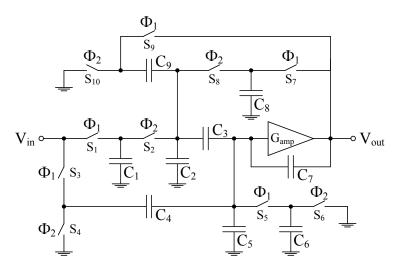

| 7.12 | Parasitic-sensitive switched-capacitor integrator using charge division branch                                  | 116 |

| 7.13 | Notch SC filter: Differential implementation of the (a) filter and (b) capacitor using charge                   |     |

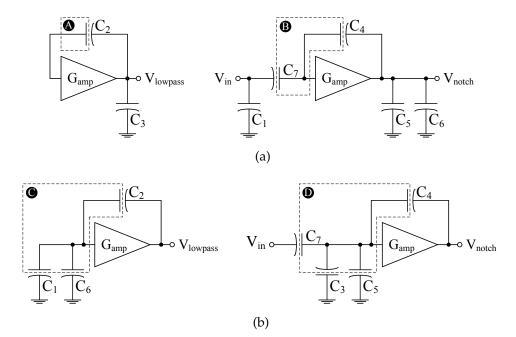

|      | division branch, for $n = 1, 3, 5$ , and $6$                                                                    | 118 |

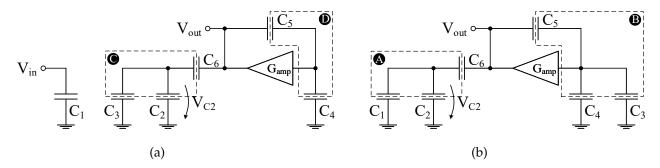

| 7.14 | Equivalent circuit during (a) phase $\Phi_1$ and (a) phase $\Phi_2$                                             | 118 |

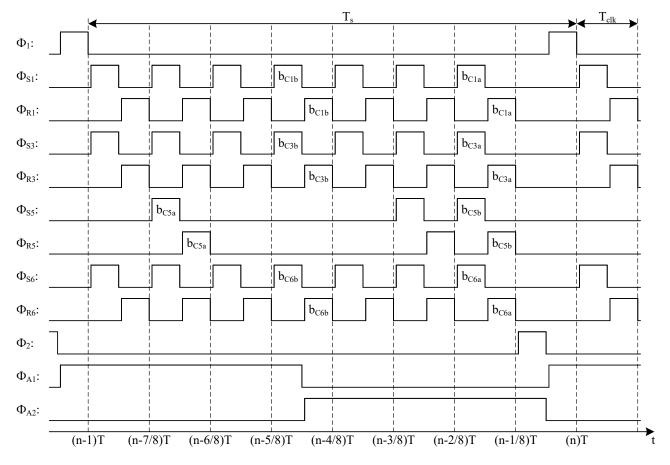

| 7.15 | Diagram of the phases controlling the notch SC filter and the charge division branches.                         | 120 |

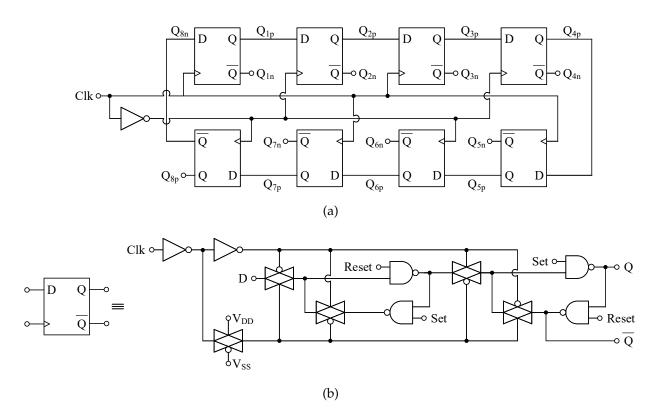

| 7.16 | Circuit implementation of the (a) divide by 8 clock circuit and (b) flip-flop D                                 | 121 |

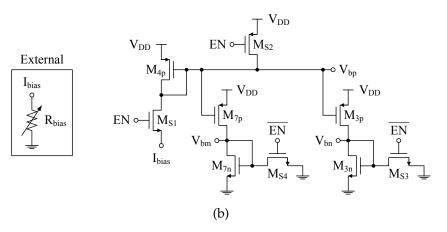

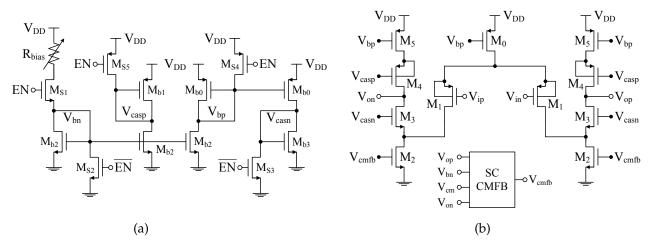

| 7.17 | Folded-cascode amplifier: (a) Bias circuit, (b) Differential implementation.                                    | 122 |

| 7.18 | Layout of the folded-cascode amplifier and common-mode feedback circuit                                         | 123 |

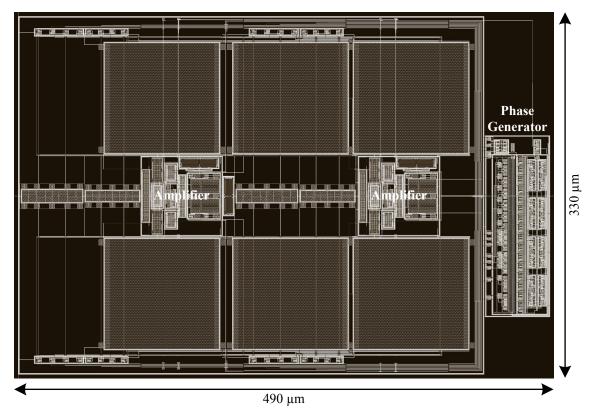

| 7.19 | Layout of the clock phase generator circuit.                                                                    | 123 |

| 7.20 | Layout of the notch SC filter using charge division branches.                                                   | 124 |

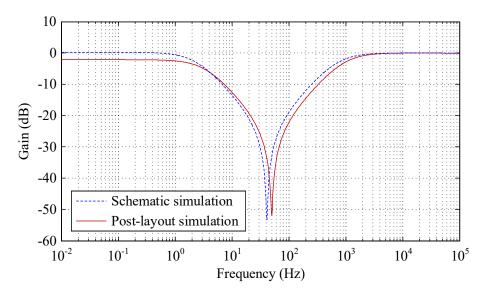

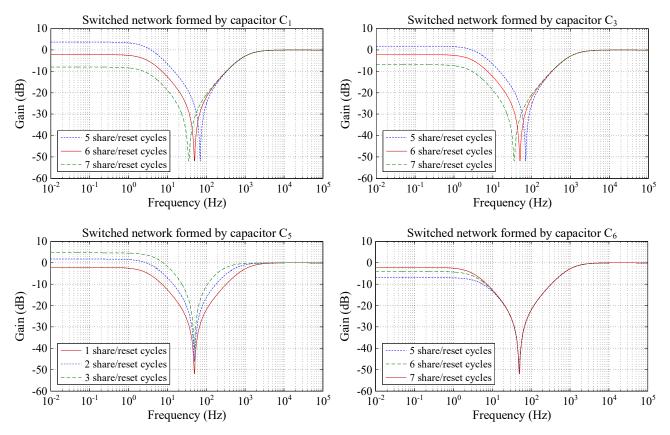

| 7.21 | Frequency response comparison of the notch SC filter for the default number of share/reset                      |     |

|      | cycles ( $\Phi_{S1,R1} = 6$ , $\Phi_{S3,R3} = 6$ , $\Phi_{S5,R5} = 1$ , $\Phi_{S6,R6} = 7$ ).                   | 125 |

| 7.22 | Post-layout frequency responses of the notch SC filter for different numbers of share/reset                     |     |

|      | cycles                                                                                                          | 125 |

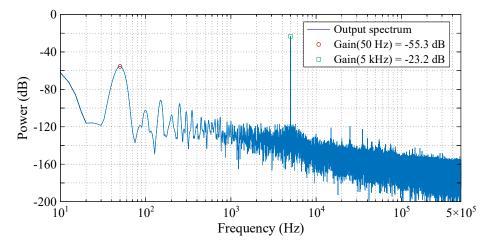

| 7.23 | Output spectrum of the extracted notch SC filter with the default number of share/reset                         |     |

|      | cycles for an input with two tones ( $f_1 = 50$ Hz with 100 mV amplitude and $f_2 = 5$ kHz with                 |     |

|      | 10 mV)                                                                                                          | 126 |

# LIST OF TABLES

| 2.1  | SC resistor emulation circuits.                                                              | 11 |

|------|----------------------------------------------------------------------------------------------|----|

| 2.2  | Capacitor charge in each phase of the parasitic-sensitive integrator.                        | 12 |

| 2.3  | Capacitor charge in each phase of the parasitic-insensitive integrator.                      | 13 |

| 2.4  | Circuit elements and noise models.                                                           | 14 |

| 3.1  | Design comparison between the basic and the T-cell SC integrators                            | 19 |

| 3.2  | Design comparison between the basic and the partial charge transfer SC integrators           | 20 |

| 3.3  | Design comparison between the basic and the split integrating capacitor SC integrators.      | 21 |

| 3.4  | Design comparison between the basic and the charge recombination SC integrators              | 22 |

| 3.5  | MDAC performance comparison between conventional approach and VGRB technique.                | 25 |

| 5.1  | Design used in the ideal lowpass SC filter.                                                  | 46 |

| 5.2  | Common-drain amplifier design and parameters.                                                | 49 |

| 5.3  | Comparison of the time taken to reach a settling error below 1 % between the first-order     |    |

|      | approximation used and the Spectre simulation.                                               | 51 |

| 5.4  | Design used in the switches and compensated capacitor values                                 | 52 |

| 5.5  | Design used in the bandpass SC filter                                                        | 63 |

| 6.1  | Specifications used to optimize the frequency response of the lowpass SC filter              | 82 |

| 6.2  | Chromosomes and design space bounds used by the GA in the top-level optimization $\ .$       | 82 |

| 6.3  | Lowpass SC filter design obtained after the top-level optimization.                          | 83 |

| 6.4  | Amplifier specifications and simulation results of the best chromosome                       | 83 |

| 6.5  | Chromosomes and design space bounds used by the GA in the amplifier optimization             | 84 |

| 6.6  | Amplifier design obtained and compensated capacitances after the amplifier optimization.     | 84 |

| 6.7  | Chromosomes and design space bounds used by the GA in the switches optimization              | 84 |

| 6.8  | Switch design obtained after the switches' optimization.                                     | 84 |

| 6.9  | Chromosomes and design space bounds used by the GA in each optimization step                 | 85 |

| 6.10 | Lowpass SC filter design obtained after the top-level adjustment.                            | 85 |

| 6.11 | Specifications and simulation results of the lowpass SC filter after each optimization step. | 85 |

| 6.12 | Chromosome format used by the GA in each optimization step                                   | 86 |

| 6.13 | Specifications used to optimize the frequency response of the bilinear bandpass SC filter.   | 87 |

|      |                                                                                              |    |

| 6.14 | Bandpass SC filter design obtained (A) before and (B) after mismatch optimization in the       |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | top-level optimization step.                                                                   | 88  |

| 6.15 | Amplifier specifications and simulation results of the best chromosome.                        | 88  |

| 6.16 | Amplifier design obtained and compensated capacitances after the amplifier optimization.       | 89  |

| 6.17 | Bandpass SC filter design obtained after the top-level adjustment                              | 89  |

| 6.18 | Specifications and simulation results of the bandpass SC filter after each optimization step.  | 90  |

| 6.19 | Amplifier's parameters specifications, mean value, and standard deviation before and after     |     |

|      | the PVT optimization: (S1) section 1, (S2) section 2, (S3) section 3.                          | 93  |

| 6.20 | Specifications and simulation results of the bandpass SC filter after the optimization process |     |

|      | is complete: (S1) section 1, (S2) section 2, (S3) section 3, (CS) cascaded sections.           | 94  |

| 6.21 | Design obtained for each biquad section after the optimization procedure ends: (S1) sec-       |     |

|      | tion 1, (S2) section 2, (S3) section 3                                                         | 95  |

| 6.22 | Specifications used to optimize the frequency response of the lowpass SC filter                | 98  |

| 6.23 | Design obtained from a run without PVT corners or mismatch variations optimization.            | 99  |

| 6.24 | Specifications and frequency response results of the lowpass SC filter obtained from           |     |

|      | different methods                                                                              | 99  |

| 6.25 | Design obtained from a run with PVT corners and mismatch variations optimization               | 101 |

| 6.26 | Comparison between non-hierarchical and hierarchical methods after 30 optimization runs.       | 102 |

| 6.27 | Specifications used to optimize the frequency response of the bandpass SC filter 1             | 103 |

| 6.28 | Average results and standard deviation after performing 30 optimization runs 1                 | 103 |

| 6.29 | Design obtained from a run without PVT corners or mismatch variations optimization             | 103 |

| 6.30 | Specifications and frequency response results of the bandpass SC filter obtained from          |     |

|      | different methods                                                                              | 104 |

| 6.31 | Design obtained from a run with PVT corners and mismatch variations optimization 1             | 105 |

| 7.1  | Design used in the capacitors of the bandpass SC filter.                                       | 109 |

| 7.2  | Design used in the voltage-combiner amplifier and bias circuit.                                | 111 |

| 7.3  | Measurement summary of some of the filter metrics for the different bit configurations 1       | 115 |

| 7.4  | Frequency response specifications used in the design of the notch SC filter                    | 119 |

| 7.5  | Possible design for the ideal notch SC filter ( $C_{max}/C_{min} = 3333.33$ )                  | 119 |

| 7.6  | Capacitor design and default number of share/reset cycles used in the notch SC filter          |     |

|      | $(C_{max}/C_{min} = 140.37)$                                                                   | 120 |

| 7.7  | Design used in the folded-cascode amplifiers                                                   | 122 |

| 7.8  | Simulation summary of some of the filter metrics for different numbers of share/reset cycles.  | 126 |

# LIST OF ABBREVIATIONS AND ACRONYMS

| A/D  | Analog-to-Digital.                       |

|------|------------------------------------------|

| AAF  | Anti-Aliasing Filter.                    |

| ADC  | Analog-to-Digital Converter.             |

| CDB  | Charge Division Branch.                  |

| CDS  | Correlated Double Sampling.              |

| CLG  | Closed-Loop Gain.                        |

| CMFB | Common-Mode Feedback.                    |

| CMOS | Complementary Metal-Oxide-Semiconductor. |

| DC   | Direct Current.                          |

| ENOB | Effective Number of Bits.                |

| ESD  | Electrostatic Discharge.                 |

| FFT  | Fast Fourier Transform.                  |

| GA   | Genetic Algorithm.                       |

| GBW  | Gain-Bandwidth Product.                  |

| GSL  | GNU Scientific Library.                  |

| IC   | Integrated Circuit.                      |

| IM3  | 3rd Order Intermodulation Product.       |

| ΙοΤ  | Internet-of-Things.                      |

| KCL  | Kirchhoff's Current Law.                 |

| LP   | Linear Programming.                      |

| LSE  | Large-Signal Excitation.                 |

| MC   | Monte Carlo.                             |

| MDAC    | Multiplying Digital-to-Analog Converter.           |  |  |

|---------|----------------------------------------------------|--|--|

| MIM     | Metal Insulator Metal.                             |  |  |

| MINLP   | Mixed Integer Nonlinear Programmming.              |  |  |

| MNA     | Modified Nodal Analysis.                           |  |  |

| MOSFET  | Metal-Oxide-Semiconductor Field-Effect Transistor. |  |  |

| NMOS    | n-channel MOSFET.                                  |  |  |

| ОР      | Operating Point.                                   |  |  |

| OSR     | Oversampling Ratio.                                |  |  |

| ΟΤΑ     | Operational Transconductance Amplifier.            |  |  |

| PAC     | Periodic Alternating Current.                      |  |  |

| PMOS    | p-channel MOSFET.                                  |  |  |

| PSS     | Periodic Steady State.                             |  |  |

| PVT     | Process, Voltage supply, and Temperature.          |  |  |

| S/H     | Sample and Hold.                                   |  |  |

| SA      | Simulated Annealing.                               |  |  |

| SAR     | Successive Approximation Register.                 |  |  |

| SC      | Switched-Capacitor.                                |  |  |

| SC-CMFB | Switched-Capacitor Common-Mode Feedback.           |  |  |

| SCA     | Switched-Current-Assisting.                        |  |  |

| SFG     | Signal Flow Graph.                                 |  |  |

| SNDR    | Signal-to-Noise + Distortion Ratio.                |  |  |

| THD     | Total Harmonic Distortion.                         |  |  |

| VCVS    | Voltage-Controlled Voltage Source.                 |  |  |

| VGRB    | Virtual Ground Reference Buffer.                   |  |  |

CHAPTER

### INTRODUCTION

#### 1.1 Background and Motivation

The scaling-down of transistors in advanced deep-submicron CMOS technologies has led to undisputed advantages in terms of chip area, transistor transit frequency, and power consumption, mainly exploited by digital circuits. Yet, there are also disadvantages due to the reduction of the transistor's channel length. Ideally, voltages and transistor's dimensions should be scaled proportionally in order to maintain the same electric field. However, the threshold voltage ( $V_{TH}$ ) can not be scaled in the same proportion as the supply voltage, since a high  $V_{TH}$  is needed to achieve a low current when the transistor is turned OFF. With the generalized scaling taken over the past decades, the maximum output swing of analog circuits is decreasing, as well as the intrinsic gain ( $g_m/g_{ds}$ ) of the transistors, impacting the functionality and performance of analog blocks [1].

Filter circuits are commonly used in data acquisition channels to remove unwanted signals. They can be implemented using passive or active RC filters, g<sub>m</sub>-C filters, or switched-capacitor (SC) filters. Typically, these channels require some degree of bandwidth tunability.

In traditional  $g_m$ -C or active-RC filters architectures, the frequency tuning is achieved through the use of on-chip capacitor and resistor banks, increasing the circuit's cost. Although their speed-to-power efficiency has improved with the scaling of CMOS technology, these circuits have become harder to design due to the reduction of the supply voltage and of the intrinsic gain of the transistors.

SC filters, on the other hand, can be a competitive alternative for their inherent frequency tuning, by changing the clock's frequency; for their small die area, when compared with other types of filters (especially for low frequency filters); and for their low sensitivity to parameter deviation, since the circuit's transfer function is given by capacitor ratios, which have a very good accuracy in integrated circuit (IC) technology, and not by their absolute value. However, traditional active SC filters require high-gain high-bandwidth opamps, which are harder to design in advanced technologies.

In the case of SC filters, to overcome the difficulty of designing high-gain high-bandwidth opamps, alternative architectures can be used, where the opamp is replaced with a voltage buffer or a low-gain (< 2) amplifier. Although this simplifies the amplifier's design, it also eliminates the filter's virtual ground node. This means that, even if parasitic-insensitive switched networks are used, the circuit's transfer function is susceptible to the effects of parasitic capacitances. However, the historical disadvantage of parasitic-sensitive switched networks (parallel branch) is no longer critical, since the scaling down of transistors and supply voltage has also led to a reduction of the parasitic capacitances, allowing their influence to be compensated during the circuit's design process [2]. The use of parasitic-sensitive networks has the advantage of allowing the implementation of filters with more than one pole per amplifier, improving the filter's power-per-pole efficiency. Additionally, due to the amplifier's low gain, it is possible to achieve a higher bandwidth for the same power, when compared with implementations using amplifiers with a high gain.

Independently of the type of amplifier used, the manual design of SC filters can be a challenging and time consuming process, since the value of a single design variable can change several performance parameters (cutoff frequency, gain, poles quality factor). Even after finding a set of parameter values that produce the desired filtering function, it is also necessary to evaluate the solution's sensitivity to process, voltage supply, and temperature (PVT) variations and mismatches errors, to improve the circuit's yield after fabrication. As a consequence, the number of evaluations increase considerably.

As an alternative to the manual design of SC filters, optimization tools can be used to automatize the circuit's design process. The frequency response of a SC filter can be obtained by simulating the circuit's impulse response. However, due to the large computation time needed to get enough points to accurately compute the frequency response, this approach in not efficient to be used in an optimization environment, due to the number of evaluation needed to find an optimal solution. A more efficient method is then needed to obtain an optimized solution, with good accuracy, within a reasonable amount of computation time.

The main motivation of this PhD work is the development of an efficient analysis and optimization software for the design of SC filters, capable of accurately obtain and optimize the filter's frequency response, considering the non-ideal effects of the circuit's transistors, within a reasonable amount of computation time.

The proposed tool has been used to design and optimize the prototypes of a programmable bandpass SC biquad filter, implemented with a low-gain amplifier, and the prototype of a 50 Hz notch SC filter, implemented with high-gain amplifiers. These circuits have been designed in a standard 130 nm CMOS technology with a supply voltage of 0.9 V. Measurement results of the bandpass SC filter show that the filter's central frequency can be tuned between 3.9 kHz and 7.1 kHz, the gain between -6.4 dB and 12.6 dB, and the quality factor between 0.9 and 6.9. Depending on the bit configuration of the capacitor banks, the THD is between -54.7 dB and -61.7 dB. The transient simulation of the extracted view (C+CC) of the notch SC filter shows an attenuation of 52.3 dB in the 50 Hz interference and that the desired 5 kHz signal has a THD of -92.3 dB. The filters have a total power consumption of 249  $\mu$ W and 273  $\mu$ W, respectively.

#### **1.2 Research Question and Hypothesis**

How to design highly selective SC filter circuits in nanometer CMOS technologies using the available transistors with intrinsic low-gain while reducing the power consumption and area? Is it possible to achieve these requirements while maintaining insensitivity to PVT variations and mismatch errors?

If low DC gain amplifiers can be easily designed in nanometer technologies and it is possible to use SC filter topologies with low-gain amplifiers then, it should be possible to design high performance, low power, low area filters in nanometer CMOS technologies.

If a numerical methodology for the analysis of SC filters, capable of reliably describing the circuit's behavior and accounting for the non-ideal effects of the circuit's transistors can be developed then, it should be possible to implement an optimization software, using said methodology, capable of automatically finding the best filter design, for a given set of filter specifications and, at the same, that is robust to PVT variations and mismatch errors.

#### **1.3 Original Contributions and Publications**

The main contributions of this PhD thesis are as follows:

- Development of an efficient numerical methodology to obtain the frequency response of SC filters, based on the circuit's first-order differential equations. This methodology uses a nonhierarchical approach, where the non-ideal effects of the transistors in the amplifier and in the switches are taken into consideration, using the transistors' medium frequency small-signal model, allowing the accurate computation of the circuit's frequency response, at transistor level, even in the case of incomplete settling in the SC branches. Since the analysis methodology is purely numeric in nature, it can be efficiently implemented in a computer. The result of this work has been published in [3].

- Development of a software library for the optimization of SC filters using hybrid cost functions (equation-based/simulation-based). This library was integrated into an existing circuit optimization software platform, based on the open-source circuit simulator Ngspice. Initially, equations are used in the cost function to estimate the filter's frequency response. This reduces the computation time of each evaluation, allowing the use of large populations to increase the probability of completely exploring the design space. Once all specifications are met, the population size is reduced and transient simulations of the circuit's impulse response are used in the cost function, resulting in the accurate determination of the filter's frequency response and allowing to accurately compensate the parasitic capacitances, which effect is harder to estimate through equations. This approach allows the final design solution to be obtained in a reasonable amount of computation time. The result of this work has been published in [4]–[6].

- Implementation of the prototype of a programmable second-order bandpass SC filter using low gain amplifiers and of a 50 Hz notch SC filter using high gain amplifiers in UMC 130 nm CMOS technology, with a supply voltage of 0.9 V, using the proposed analysis and optimization methodologies.

The research work performed during the PhD resulted in the following authored and co-authored publications:

- H. Serra, R. Santos-Tavares, and N. Paulino, "A top-down optimization methodology for SC filter circuit design using varying goal specifications", in *Proc. Doctoral Conf. Computing, Elect., Ind. Syst. (DoCEIS),* Apr. 2014, pp. 535–542. DOI: 10.1007/978-3-642-54734-8\_59.

- H. Serra, R. Santos-Tavares, and N. Paulino, "A top-down optimization methodology for SC filter circuit design", in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, Jun. 2014, pp. 1672–1675. DOI: 10.1109/ISCAS.2014.6865474.

- H. Serra, R. Madeira, and N. Paulino, "Analysis of a multi-ratio switched capacitor DC-DC converter for a supercapacitor power supply", in *Proc. Doctoral Conf. Computing, Elect., Ind. Syst.* (*DoCEIS*), Apr. 2015, pp. 477–485. DOI: 10.1007/978–3–319–16766–4\_51.

- H. Serra, R. Santos-Tavares, and J. Goes, "Automatic design of high-order SC filter circuits", in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2015, pp. 1937–1940. DOI: 10.1109/ISCAS. 2015.7169052.

- H. Serra, R. Santos-Tavares, and N. Paulino, "A numerical methodology for the analysis of switched-capacitor filters taking into account non-ideal effects of switches and amplifiers", *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 1, pp. 61–71, Jan. 2017. DOI: 10.1109/TCSI.2016. 2601343.

- N. Pereira, H. Serra, and J. Goes, "A two-step radio receiver architecture fully embedded into a charge-sharing SAR ADC", in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2017, pp. 1201–1204. DOI: 10.1109/ISCAS.2017.8050563.

- H. Serra, J. P. Oliveira, and N. Paulino, "A 50 Hz SC notch filter for IoT applications", in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2017, pp. 2435–2438. DOI: 10.1109/ISCAS.2017. 8050904.

### 1.4 Thesis Organization

Besides this introductory chapter, the thesis is organized in seven additional chapters, which are briefly described below.

In Chapter 2, an overview of the fundamental concepts for SC filters and their main building blocks is given, including non-ideal effects that need to be considered when designing this type of circuits. Different SC resistor emulation networks are shown and two SC integrators, one using a parasitic-sensitive network and the other using a parasitic-insensitive network, are described to show the advantage of using parasitic-insensitive switched networks to minimize the effects of the parasitic capacitances when an amplifier with high gain is used.

In Chapter 3, an overview of design techniques used in SC filters to reduce the capacitance spread and to improve the trade-off of speed and linearity with the circuit's power consumption is given. Four techniques to reduce a SC filter's capacitance spread are described, using a SC integrator as an example. The capacitance spread is improved by reducing the amount of charge delivered from the sampling capacitor to the integrating capacitor or by integrating only a small amount of charge, while destroying the rest. A switched-current-assisting (SCA) technique for a SC integrator is also described, which improves the trade-off of speed and linearity with the circuit's power consumption. This is achieved by using an assisting branch connected to the circuit's output to alleviate the slew rate and bandwidth requirements of the main amplifier. A virtual ground reference buffer (VGRB) technique is described where the amplifier's feedback factor is improved, without affecting the signal gain, through the use of an auxiliary voltage buffer, breaking away from the inverse relation between signal gain and feedback factor, relaxing the amplifiers bandwidth and noise requirements. A recycling SC-buffer biquad is described. Since this circuit is implemented without gain, effects of non-linearities and parasitic capacitances are intrinsically low, making it easier to achieve higher bandwidths for the same power when compared with SC filters implemented with high-gain amplifiers.

In Chapter 4, an overview of analysis methods for SC filters is given. Several analysis and optimization software programs are briefly described. A general method for the analysis of ideal switched networks, based on matrix computations, is described. Three approaches to deal with the minimization of the total capacitance value in SC circuits are described. One of the methods uses a mixed integer nonlinear programmming (MINLP) software to find the optimal capacitance sizing for a given prototype transfer function, while minimizing the number of capacitors needed and prioritizing solutions with lower sensitivity to component mismatches. The other two methods use linear programming (LP) and simulated annealing (SA) algorithms to minimize the total capacitance value. Both methods are compared to show their capability in finding global minimums for the optimal capacitance sizing problem.

In Chapter 5, two methods for the design of SC filters are proposed. In the first method, the SC filter is designed hierarchically, i.e., the filter's transfer function is initially designed considering every component as ideal and, afterwards, the amplifier circuit and the switches are designed with the necessary performance to replace the ideal components and the parasitic capacitances are compensated into the ideal capacitance values to obtain a frequency response that is as close as possible to the one obtained from the ideal transfer function. In the second method, the SC filter is designed using a non-hierarchical approach, considering the non-ideal effects of the circuit's transistors, allowing the accurate computation of the filter's frequency response. Some design examples are given in this chapter to demonstrate the accuracy of both methods.

In Chapter 6, an optimization software, using genetic algorithms (GAs) and two equation-based optimization methodologies, for SC filters, is described. The first optimization methodology (hier-archical) optimizes the filter's frequency response using a multi-step approach where, initially, the filter's ideal transfer function is optimized and, once the specifications are met, the next two steps

are used to optimize the amplifier's closed-loop transfer function and the switches RC time constants to replace the ideal blocks used in the first step. The final step is used to validate the equation-based design, through transient simulations of the impulse response, and to accurately compensate the effect parasitic capacitances. The second optimization methodology (non-hierarchical) optimizes the filter's frequency response using a single system of equations that completely describe the circuit's continuous-time behavior in any clock phase, independently of the number of phases that control the circuit. Once a good solution is found, it is validated through a transient simulation of the impulse response. Both optimization methods include PVT and Monte Carlo (MC) optimization modes to increase the solution's robustness under different PVT corners and to mismatch variations. Several optimization examples are given in this chapter to demonstrate the performance of both optimization methodologies, including an example where the optimization times of both methods are compared.

In Chapter 7, the prototypes of a programmable bandpass SC biquad filter, using a low-gain amplifier, and of a 50 Hz notch SC filter, using high-gain amplifiers, are presented. Both circuits are implemented with 0.9 V supply voltage in a 130 nm CMOS technology and designed using the analysis and optimization methodologies described in Chapters 5 and 6. A comparison between the programmable bandpass SC filter's frequency responses obtained from the schematic and post-layout simulations and from the measurement of the test board is given. In the case of the 50 Hz notch SC filter, the comparison is made between the schematic and post-layout simulations.

Finally, in Chapter 8, the conclusions are drawn and the future work is discussed.

6

Снартек

### **BACKGROUND ON SWITCHED-CAPACITOR FILTERS**

Interest in switched-capacitor (SC) networks began in the late 1970's due to the possibility of implementing precision analog filters using integrated circuit (IC) technology, since it is possible to achieve good accuracy in the ratio between two capacitor values. Typically, high valued resistors are used in the implementation of analog filters, that can be replaced by small on-chip capacitors, making it an attractive option for monolithic fabrication, since it occupies a small substrate area.

SC circuits operate as analog discrete-time circuits. When used as filters, these circuits have an accurate frequency response, good linearity, and good dynamic range. The accuracy of these circuits results from the time constants being determined by capacitor ratios, that typically have an accuracy close to 0.1 %, while integrated RC circuits have a time constant error that can range from 20 to 50 %, due to the accuracy of the resistors and the capacitors. Another advantage of these circuits is the incorporation of a certain degree of frequency tuning, that is achieved by changing the circuit's clock frequency [8].

There are also several non-ideal characteristics of SC circuits which need to be considered, such as charge injection, offset error, noise, and parasitic capacitances [9]. Generally, due to the sampling of the signal, SC filters need an anti-aliasing filter at the input and a smoothing filter at the output [10].

This chapter provides a brief overview on the building blocks of SC filters, the non-ideal effects of these blocks, that need to be carefully considered during the circuit's design, and some techniques commonly used to minimize these effects.

### 2.1 Switched-Capacitor Filters Building Blocks

SC filters are implemented using switches, capacitors, non-overlapping clock generators, and opamps. These blocks are briefly described in this section along with some techniques to eliminate or minimize their non-linear effects.

#### 2.1.1 Switches

In SC circuits, switches need high resistance when they are open, in order to minimize charge leakage, and low resistance when they are closed, to ensure that charge equilibrium is achieved within the time the switch is closed. Depending on their size, MOSFET transistors satisfy these requirements, having very high OFF resistance and low ON resistance ( $G\Omega$  and  $k\Omega$ , respectively). These values change inversely with the width of the transistor and directly with the length.

Fig. 2.1 shows three possible configurations for the implementation of the switches: NMOS transistors, which are better for lower input voltages since they stop conducting when the input voltage is close to  $V_{DD} - V_{tn}$ ; PMOS transistors, which are better for higher input voltages since they only conduct when the voltage is above  $|V_{tp}|$ ; and transmission gates, which allow rail-to-rail input signal swing. Lower voltages will travel via the NMOS switch, since it offers less resistance to the signal while, for the same reason, higher voltages will travel via the PMOS switch.

Figure 2.1: MOS switches: (a) NMOS, (b) PMOS, (c) Transmission gate.

When designing parasitic-sensitive SC filters, it is necessary to consider the effect of parasitic capacitances ( $c_{dd}$  and  $c_{ss}$ ) since the filter's transfer function is affected by these capacitances. Although the resistance of a switch can be decreased by increasing the transistors width, in order to guarantee charge equilibrium before the switch opens, doing so will increase the value of the parasitic capacitances. It is important to note that the parasitic capacitances of MOS transistors are non-linear, i.e., their value changes with the applied voltage in the transistor's terminals and depending on if the switch is open or closed.

Fig. 2.2 shows an example of the switches' ON resistance and parasitic capacitances as a function of the input voltage (1:5 ratio between the NMOS and the PMOS devices). Although the transmission gate allows rail-to-rail signal swing and a more linear resistance value within the output voltage range, it takes up more area, requires complementary phases, and has larger parasitic capacitances. In high speed signals, both switches need to turn OFF simultaneously otherwise the distortion in the signal will increase.

Decreasing the ON resistance leads to larger switches and bigger parasitic capacitances. In these situations, and especially in parasitic-sensitive circuits, clock bootstrapping can be used to increase the voltage applied to the gate of the transistor, decreasing the resistance value and increasing its linearity, allowing the use of smaller switches and a single NMOS device instead of a transmission gate, also decreasing the value of the parasitic capacitances [11].

Figure 2.2: Example of switch (a)  $r_{ds}$  resistance and (b)  $c_{ss}$  capacitance, as a function of the  $V_{in}$  voltage.

Besides the non-linear effects of the resistance and parasitic capacitances, switches are susceptible to other non-ideal effects, such as charge injection and clock feedthrough. Both of these effects produce disturbances in the sampled voltage when the transistor is turned OFF. Charge injection occurs due to charge being released from the transistor's channel to the drain and source junctions and clock feedthrough due to the coupling between the gate-source and gate-drain overlap capacitances [12].

Frequently used techniques to improve charge injection include the use differential signals, canceling offset errors and even-order distortion, although gain errors and odd-order distortion remain.

Another technique is shown in Fig. 2.3, using a dummy switch configuration to perform charge injection cancellation. When the main transistor ( $M_1$ ) turns OFF and the dummy ( $M_2$ ) turns ON, the charge released by the former is absorbed by the latter to form the channel. Typically the dummy transistor is designed to have half the width of the main transistor to cancel charge injection [13]. Note that this technique is sensitive to the alignment of both clock phases.

Figure 2.3: Simple circuit using dummy switch technique.

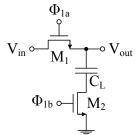

Fig. 2.4 shows yet another technique, the bottom plate sampling. The bottom transistor ( $M_2$ ) turns OFF sightly before the top transistor ( $M_1$ ), injecting a constant amount of charge that can be eliminated using differential signaling. When the top transistor turns OFF, the bottom plate of capacitor  $C_L$  is floating and no current will flow through the capacitor, as a result no signal dependent charge is injected [14].

Figure 2.4: Simple circuit using bottom plate sampling technique.

#### 2.1.2 Non-Overlapping Clock Phases

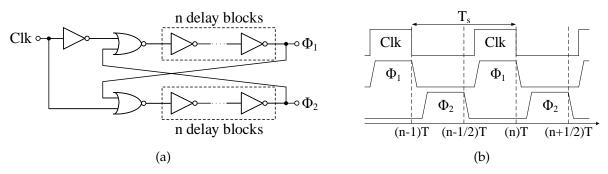

In SC filters, switches require at least a pair of non-overlapping clock phases to perform the charge transfer. Typically, the phases do not overlap, in order to ensure that no charge is accidentally lost by having switches with different phases closed at the same time. Fig. 2.5 shows an example of a two-phase non-overlapping clock generator [15].

Figure 2.5: Two-phase non-overlapping clock generator: (a) Circuit implementation, (b) Phase scheme.

#### 2.1.3 Capacitors

Depending on the network used to emulate resistors and the SC filter's architecture, capacitors are another element where it may be necessary to consider the effects of parasitics. The bottom plate parasitic capacitance can be as high as 20 % of the nominal value, while the top plate can be as high as 5 %, depending on the technology and capacitor structure [8].

#### 2.1.4 **Operational Amplifiers**

Depending on the amplifier's gain, opamps can provide a virtual ground node in SC circuits. When using parasitic-insensitive networks, parasitic capacitances connected to this node do not influence the circuit's transfer function since, in one phase, they will be connected to the circuit's ground, and to the virtual ground during the other. Note, however, that the parasitic capacitances will still influence the time constant of the nodes they are connected to. Opamps also have non-ideal effects that influence the performance of SC circuits like, DC gain, unity gain frequency and phase margin, slew rate, and common-mode voltage [16].

In [17], a general technique to reduce the amplifier's finite gain effect is described. The basic principle of this technique is to obtain an estimate of the amplifier's finite gain error during the first phase and subsequently use this error for correction during the second phase. Since the input has to be held constant during these two phases, a third phase might be necessary when this circuit is connected to other stages. With this approach, it was reported that the finite gain error, which is proportional to 1/A in conventional circuits [18], becomes proportional to  $1/A^2$ , where *A* is the amplifier's gain.

### 2.2 Switched-Capacitor Resistor Emulation Networks

SC circuits emulate resistors using switches, switching periodically at a given frequency, and capacitors. Table 2.1 shows four different switched networks that emulate resistors, their equivalent resistance, and the charge stored in the capacitors after each phase [19].

| Circuit         | Schematic                                                                                                            | R <sub>eq</sub>          | $Q(\Phi_1)$                             | $Q(\Phi_2)$                               |

|-----------------|----------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------|-------------------------------------------|

| Parallel        | $V_{in} \circ \underbrace{\Phi_1  \Phi_2}_{\Box} \circ V_{out}$                                                      | $\frac{T}{C}$            | V <sub>in</sub> C                       | V <sub>out</sub> C                        |

| Series          | $V_{in} \circ \underbrace{\Phi_1}_{C} \xrightarrow{\Phi_2}_{Out} V_{out}$                                            | $\frac{T}{C}$            | 0                                       | $(V_{in} - V_{out}) C$                    |

| Series-Parallel | $V_{in} \circ \underbrace{\Phi_1  \Phi_2}_{C_1} \circ V_{out}$                                                       | $\frac{T}{C_1 + C_2}$    | 0<br>V <sub>in</sub> C <sub>2</sub>     | $(V_{in} - V_{out}) C_1$<br>$V_{out} C_2$ |

| Bilinear        | $V_{in} \circ \underbrace{\begin{array}{c} \Phi_1 \\ \Phi_2 \\ \Phi_2 \\ \Phi_1 \end{array}}^{\Phi_2} \circ V_{out}$ | $\frac{1}{4}\frac{T}{C}$ | (V <sub>in</sub> – V <sub>out</sub> ) C | (V <sub>out</sub> – V <sub>in</sub> ) C   |

Table 2.1: SC resistor emulation circuits.

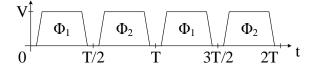

Considering the series-parallel network and the phase scheme shown in Fig. 2.6, in which the input current flows into the circuit in both phases, the calculation of the average current contemplates both phases.

$$i_{avg} = \frac{1}{T} \left( \int_0^{T/2} dq_{C_2}(t) + \int_{T/2}^T dq_{C_1}(t) \right) = \frac{Q_{C_2}(T/2) - Q_{C_2}(0)}{T} + \frac{Q_{C_1}(T) - Q_{C_1}(T/2)}{T}$$

(2.1)

Figure 2.6: Non-overlapping clock phase scheme.

Replacing the charge variables with the corresponding values that are shown in Table 2.1,

$$i_{avg} = \frac{(V_{in} - V_{out})C_2}{T} + \frac{(V_{in} - V_{out})C_1 - 0}{T}$$

(2.2)

and considering that the average current that flows through the resistance,

$$i_{avg} = \frac{V_{in} - V_{out}}{R}$$

(2.3)

by equating (2.2) and (2.3), the equivalent resistance for the series-parallel network is obtained.

$$R_{eq} = \frac{T}{C_1 + C_2}$$

(2.4)

Depending on the switched network used and the topology of the filter, it may be possible to implement parasitic-insensitive circuits. The parasitic-sensitive and parasitic-insensitive integrators are briefly described next.

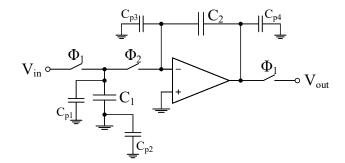

#### 2.2.1 Parasitic-Sensitive Switched-Capacitor Integrator