#### José Manuel Atalaia Rosa

Licenciado em Ciências de Engenharia de Micro e Nanotecnologias

# Solution-based IGZO nanoparticles memristor

Dissertação para obtenção do Grau de Mestre em Engenharia de Micro e Nanotecnologias

Orientadora: Doutora Asal Kiazadeh, Professora Auxiliar, Faculdade de Ciências e Tecnologias da Universidade Nova de Lisboa

Co-orientadora: Doutora Lídia Sofia Leitão Santos, Investigadora, Faculdade de Ciências e Tecnologias da Universidade Nova de Lisboa

Júri:

Presidente: Prof. Doutor Rodrigo Ferrão de Paiva Martins Arguente(s): Prof. Doutor João Carlos da Palma Goes Vogal(ais): Prof. Doutora Lídia Sofia Leitão Santos

Copyright © José Manuel Atalaia Rosa Faculdade de Ciências e Tecnologia Universidade Nova de Lisboa

A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objetivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

#### **Acknowledments**

Firstly, I would like to thank the Faculty of Science and Technology of Nova University of Lisbon for all the opportunities and teaching quality it has provided me.

Secondly, I would like to express my gratitude and admiration to Prof. Rodrigo Martins and Prof. Elvira Fortunato. Not only for having created the Msc in Micro and Nanotechnology Engineering course, but also for all the confidence placed in everyone who works and were taught by them and for the super working conditions of CENIMAT|i3N. Without those, my thesis would not exist.

To my supervisor Dr. Asal Kiazadeh and co-supervisor Dr. Lídia Santos I must say I am deeply grateful for all their valuable ideas, for their teaching and their support throughout this journey. Their readiness to help me whenever I needed was definitely crucial to this work. It was truly a privilege to have worked with such remarkable human beings.

I would also like thank Pedro "Monchique" Freitas for all the support, the discussions, and struggles to reach the conclusions that we made on the fascinating RRAM subject.

I should also express my gratitude towards all the researchers who somehow supported my work: Prof. Luís Pereira, Prof. Joana Pinto, Jonas Deuermeier, Shumam Nandy, Sumita Goswami, Daniela Gomes, Sónia Pereira, Emanuel Carlos, Tomás Calmeiro, Ana Santa, Cristina Fernandes, Carolina Marques. To all the others who worked in CENIMAT and CEMOP who have indirectly contributed to this project with their kindness and by creating a great work environment, Additionally, I thank all my course mates for all the good moments, team work and friendship, especially to: Ângelo Santos, José Rui Silva, Ismael Domingues, Tomás Vasconcelos, Marco Moreira, Zé Correia, Ricardo Farinha, Gonçalo Santos, Rodrigo Santos, Pedro Trigo, Sofia Chamiço, Beatriz Coelho and Júlio Costa.

I am also grateful to junior enterprise iNOVAfuture for always believing in my projects and my vision towards for developing products but also for having been elected to relevant positions over the years.

I am also grateful to for the excellent companionship, motivation and all the jokes and pranks of my very good friends: António Vilarinho Lopes, João Tornada and Rodrigo Granja. For their brilliant minds and potential, I cannot wait to see what you will become!

Finally, to my closest family: mother, father and sister for the comprehension, words of motivation that meant a lot to me. Again, without their support this journey would not have been possible. Also, to my beloved cousins for keeping me sane and creative, especially to Jorge and João Miguel. I simply lack the words to thank you for all that you have done for me, and what you represent in my live. Also, a special thanks to my aunt Rosa.

I dedicate all my work to the people who influenced me and made me what I am today, even to those are no longer with me, my grandmothers, grandfather and uncle.

#### **Abstract**

This work aims to characterize Indium-Gallium-Zinc-Oxide nanoparticles (IGZOnp) as a resistive switching matrix in metal-insulator-metal (MIM) structures for memristor application. IGZOnp was produced by low cost solution-based process and deposited by spin-coating technique. Several top and bottom electrodes combinations, including IZO, Pt, Au, Ti, Ag were investigated to evaluate memory performance, yield and switching properties. The effect of ambient and annealing temperature using 350 °C and 200 °C was also analysed in order to get more insight into resistive switching mechanism.

The Ag/IGZOnp/Ti memristor structure annealed at 200 °C exhibits the best results with a large yield. The device shows a self-compliant bipolar resistive switching behavior. The switching event is achieved by the set/reset voltages of -1 V/+1 V respectively with an operating window of 10, and it can be programmed for more than 100 endurance cycles. The retention time of on and off-states is up to 10<sup>4</sup> s. The obtained results suggest that Ag/IGZOnp/Ti structure could be applied in system on a panel (SoP) as a viable device.

**Keywords:** IGZO nanoparticles, solution-base, bipolar resistive switching, Valence Change Memory, self-compliant.

#### Resumo

Este trabalho visa à caracterização de nanopartículas de óxido de índio-gálio-zinco (IGZOnp) como uma matriz de comutação numa estrutura metal-isolante-metal (MIM), para aplicações como memristores. As IGZOnp foram produzidas por processos químicos de baixo custo e depositados por técnica de *spin-coating*. Para avaliar a performance das memórias, foram investigados os rendimentos e propriedades de comutação para vários tipos de elétrodos inferiores e superiores incluindo combinações de IZO, Pt, Au, Ti, Ag. O efeito ambiente e temperaturas de recozimento utilizando de 350 °C a 200 °C, foi também analisada de modo a obter mais informações sobre o mecanismo de comutação resistivo.

O memristor com a estruturas de Ag/IGZOnp/Ti recozidos a 200 °C exibem os melhores resultados com um elevado rendimento. O dispositivo revela um comportamento de comutação resistiva bipolar de *self-compliant*. A operação de comutação é atingida por tensões de set/reset de -1 V/+1 V respetivamente com uma janela de operação de 10, e pode ser programada por mais de 100 ciclos de resistência. O tempo de retenção no estado on e off chegam aos 10<sup>4</sup> s. Os resultados obtidos sugerem que a estrutura de Ag/IGZOnp/Ti pode ser aplicada em *system on a panel* (SoP) como um dispositivo viável.

**Palavras-chave:** Nanopartículas de IGZO, à base de solução, RRAM, comutação resistiva bipolar, Valence Change Memory, self-compliance.

#### List of abbreviations

AE - Active Electrode

AFM - Atomic force microscopy

a-IGZO - amorphous - Indium Gallium Zinc Oxide

ALD - Atomic Layer Deposition

CBRAM - Conductive bridge random access memory

CE - Contra Electrode

CF - Conductive Filament

DLS - Dynamic light scattering

DRAM - Dynamic random access memory

DSC-TG - Differential scanning calorimetry and thermogravimetry

ECM - Electrochemical metallization memory

EDS - Energy-dispersive X-ray spectroscopy

FeRAM – Ferroelectric Random Access Memory

FTIR - Fourier Transformed Infra-Red

HCS - High Conductive State

HRS - High Resistance State

HRTEM - High Resolution Transmission electron microscopy

IGZO - Indium Gallium Zinc Oxide

IGZOnp - Indium Gallium Zinc Oxide nanoparticles

IoT - Internet of Things

LCS - Low Conductive State

LRS - Low Resistance State

MIM – Metal-insulator-metal

MLC - Multilevel cell

MRAM - Magnetic Random Access Memory

NVM - Non-volatile memory

OxRAM - Oxide-based Random Access Memory

PCM - Programmable metallization cell

PC-RAM - Phase-change - Random Access Memory

Rms – Surface roughness (Root mean square)

rpm - Rotations per minute

RRAM - Resistive Random Access Memory

RT - Room Temperature

SCLC - space-charge-limited conduction

SEM - Scanning electron microscopy

SMU - Source measure unit

SoP - System on a Panel

SRAM - Static random access memory

SSD - Solid State Drive

TE - Top Electrode

TFT – Thin Film Transistor

ULSI - Ultra-large-scale-integration

UV - Ultraviolet

VCM - Valence Change Memory

Vis - Visible

VO - Oxygen Vacancies

XPS - X-ray photoelectron spectroscopy

XRD - X-Ray Diffraction

### **List of Symbols**

C.C. - Current Compliance

$\varphi$  – Magnetic Flux

q - Charge

M – Memristance

$\alpha$  – absorption coefficient

*hv* – photon energy

Eg – Band gap

V<sub>SET</sub> – Set Voltage

V<sub>RESET</sub> – Reset Voltage

### **Table of contents**

| 1.        | Motivation and objectives                                          | 1  |

|-----------|--------------------------------------------------------------------|----|

| <b>2.</b> | Introduction                                                       | 3  |

| 2.1       | 1. Non-volatile memory device                                      | 3  |

| 2.2       | 2. Resistive Random Access Memories                                | 3  |

| :         | 2.2.1. RRAM classification                                         | 3  |

| 2.3       |                                                                    |    |

| 2.4       |                                                                    |    |

| 2.5       | 5. IGZO as a RRAM switching layer                                  | 7  |

| 3.        | Materials and Methods                                              | 9  |

| 3.1       | 1. IGZO Nanoparticles Preparation and characterization             | 9  |

| 3.2       | 2. IGZO Thin Film Deposition and Characterization                  | 9  |

| 3.3       | 3. RRAM assembly and characterization                              | 10 |

| 3.4       | 4. Electrical IGZO RRAM characterization                           | 10 |

| 4         | Results and discussion                                             | 44 |

|           | 1. Memory cell activation                                          |    |

|           | 4.1.1. Forming                                                     |    |

|           | 4.1.2. Pre-forming                                                 |    |

|           | 4.1.3. Free forming                                                |    |

|           | 2. Electrical characterization of standard IGZOnp memristors       |    |

|           | 4.2.2. IGZO nanoparticles RRAM with active electrode               |    |

| 4.3       | 3. Conduction mechanisms                                           | 16 |

|           | 4.3.1. Ti/IGZOnp/Ti devices                                        |    |

| •         | 4.3.2. Ag/IGZOnp/Ti devices                                        |    |

| 4.4       | 4. Air and Vacuum influence                                        | 19 |

|           | 5. Effect of annealing temperature                                 |    |

|           | 4.5.1. Ti/IGZOnp/Ti annealed at 200 °C                             |    |

| 4.6       | •                                                                  |    |

| 4.0       |                                                                    |    |

|           | •                                                                  |    |

| 4.8       | ,                                                                  |    |

| 4.9       | •                                                                  |    |

|           | 10. Electrode material Influence                                   |    |

|           | 11. Performance of sputtered a-IGZO memories                       |    |

| 4.1       | 12. Pt/Al <sub>2</sub> O <sub>3</sub> /Cu <sub>2</sub> O/ITO CBRAM | 29 |

| 5.        | Conclusion and Future Perspectives                                 | 31 |

| 5.1       | 1. Final conclusions                                               | 31 |

| 5.2       | 2. Future perspectives                                             | 32 |

| 6. | . References | 33 |

|----|--------------|----|

| 7. | . Annexes    | 35 |

| 4  | Annex A      | 35 |

| 4  | Annex B      | 36 |

| 4  | Annex C      | 37 |

|    | Annex D      |    |

| 4  | Annex E      | 38 |

| 4  | Annex F      | 39 |

| 4  | Annex G      | 39 |

| 4  | Annex H      | 40 |

| 4  | Annex I      | 41 |

| 4  | Annex J      | 42 |

|    | Annex K      | 42 |

|    | Annex I      | 43 |

## List of figures

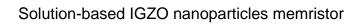

| Figure 2.1– (a-d) Schematic of a VCM in p-type semiconductor, (a) mobile oxygen ions randomly distributed, (b) nucleation and cation vacancy filament growth from anode to cathode, (c) CF achieving LRS, (d) CF rupture achieving HRS. (e-h) Schematic of a VCM in n-type semiconductor, (e) Vos randomly distributed, (f) nucleation and Vos CF formation from cathode to anode, (g) CF achieving LRS, (h) CF rupture achieving HRS [9] |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| time and resultant I-V characteristic; (b) experimental I-V characteristic of a Pt/TiO <sub>2-x</sub> /Pt [22], [23]                                                                                                                                                                                                                                                                                                                      |

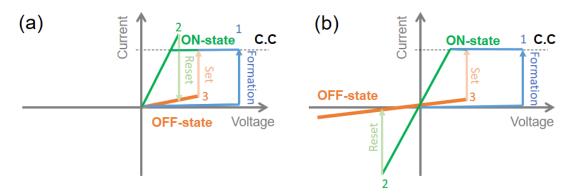

| Figure 2.4 – Schematic of I-V linear curves for (a) unipolar behavior and (b) bipolar behavior.  C.C represent the current compliance required to protect the memory cell from break down, during set process                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 4.1 – Linear I-V (a) unipolar and (b) bipolar behaviours with typical forming steps (blue).                                                                                                                                                                                                                                                                                                                                        |

| The numbers indicate the occurrence order for (1) forming, (2) reset and (3) set, respectively. 11                                                                                                                                                                                                                                                                                                                                        |

| Figure 4.2 - I-V characteristics containing forming and first cycle for (a) Ti/IGZOnp/Ti and (b)                                                                                                                                                                                                                                                                                                                                          |

| Ag/IGZOnp/Ti, depicting two distinct bipolar behaviours                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 4.3 - I-V characteristics of Au/Ti/IGZOnp/Ti annealed at 200 °C, showing a pre-forming                                                                                                                                                                                                                                                                                                                                             |

| and consecutive forming mechanism. The depicted arrows (1-6) demonstrate the orientation in which the memory is operated                                                                                                                                                                                                                                                                                                                  |

| Figure 4.4 - I-V characteristic of Ag/IGZOnp/Ti annealed at 350 °C showing a free forming                                                                                                                                                                                                                                                                                                                                                 |

| behaviour                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 4.5 - (a) Typical I-V characteristic of Ti/IGZOnp/Ti annealed at 350 °C over 100 cycles                                                                                                                                                                                                                                                                                                                                            |

| and respective, set and reset voltages indicated by a deep blue arrow, represent the respective                                                                                                                                                                                                                                                                                                                                           |

| value for each process in the first cycle. (b) Endurance characteristics at read voltage of 0.1 V                                                                                                                                                                                                                                                                                                                                         |

| at room temperature. (c) Typical retention characteristics read at -0.1 V at RT14                                                                                                                                                                                                                                                                                                                                                         |

| Figure 4.6 – (a) Typical I-V characteristic of Ag/IGZOnp/Ti annealed at 350 °C over 100 cycles                                                                                                                                                                                                                                                                                                                                            |

| and respective, set and reset voltages indicated by a deep blue arrow, represent the respective                                                                                                                                                                                                                                                                                                                                           |

| value for each process in the first cycle. (b) Endurance characteristics at read voltage of -0.1 V                                                                                                                                                                                                                                                                                                                                        |

| at RT. (c) Typical retention characteristics read at -0.1 V at RT                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 4.7 - I-V characteristics of Ti/IGZOnp/Ti structure plotted in log-log scale, showing a                                                                                                                                                                                                                                                                                                                                            |

| SCLC mechanism                                                                                                                                                                                                                                                                                                                                                                                                                            |

| region and Steep Increase region                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 4.9 - I-V characteristic of Ag/IGZOnp/Ti device showing a swift to a preferential set                                                                                                                                                                                                                                                                                                                                              |

| process with negative voltage aplication on AE                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 4.10 - I-V characteristics of Ag/IGZOnp/Ti structure plotted in log-log scale, showing a                                                                                                                                                                                                                                                                                                                                           |

| SCLC mechanism in both (a) ECM and (b) VCM regime                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 4.11– I-V characteristics of Ti/IGZOnp/Au/Ti first and second cycle (a) under air and (b)                                                                                                                                                                                                                                                                                                                                          |

| vacuum19                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 4.12 – (a) I-V characteristic of Au/Ti/IGZOnp/Ti annealed at 200 °C over 100 cycles and                                                                                                                                                                                                                                                                                                                                            |

| respective, set and reset voltages indicated in blue represent the minimum value for each                                                                                                                                                                                                                                                                                                                                                 |

| process; (b) endurance characteristics at read voltage of 0.1 V                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 4.13 – (a) I-V characteristic of Ag/IGZOnp/Ti annealed at 200 °C over 100 cycles and respective, set and reset voltages indicated in blue represent the value for each process in the                                                                                                                                                                                                                                              |

| first cycle; (b) endurance characteristics at read voltage of -0.1 V; and (c) retention                                                                                                                                                                                                                                                                                                                                                   |

| characteristics read with a constant applied -0.1 V during 10 <sup>4</sup> s                                                                                                                                                                                                                                                                                                                                                              |

| Figure 4.14 - Morphological characterization by AFM deflection images of 1 $\times$ 1 $\mu$ m <sup>2</sup> IGZOnp on                                                                                                                                                                                                                                                                                                                      |

| Ti annealed at (a) 350 °C and (b) 200 °C. Respective nanoparticles radius size distribution                                                                                                                                                                                                                                                                                                                                               |

| measured with Gwyddion software of IGZOnp on Ti annealed at (c) 350 °C and (d) 200 °C, the                                                                                                                                                                                                                                                                                                                                                |

| insert corresponds to the respective phase images23                                                                                                                                                                                                                                                                                                                                                                                       |

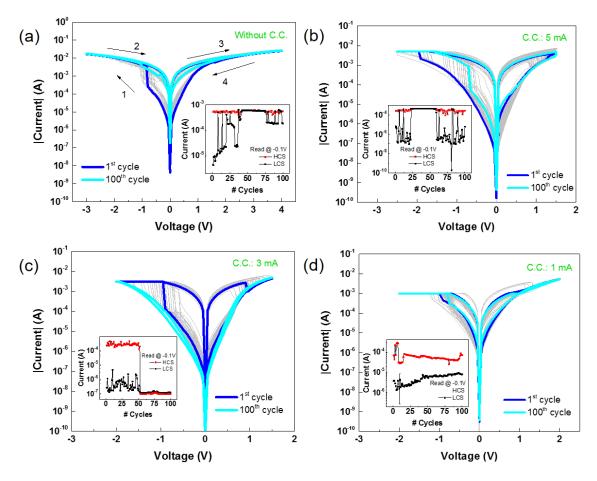

| Figure 4.15 - Ag/IGZOnp/Ti cell I-V characteristics in (a) bipolar behaviour and (b) unipolar                                                                                                                                                                                                                                                                                                                                             |

| behaviour from the same device                                                                                                                                                                                                                                                                                                                                                                                                            |

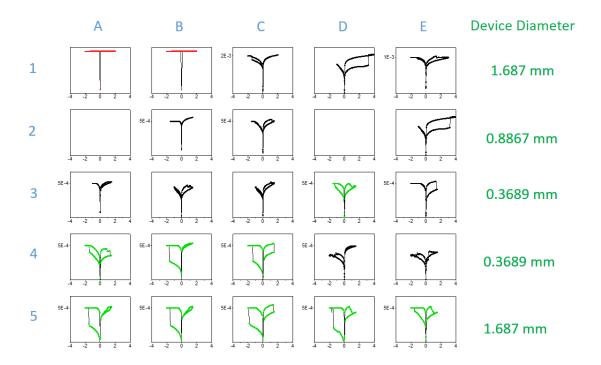

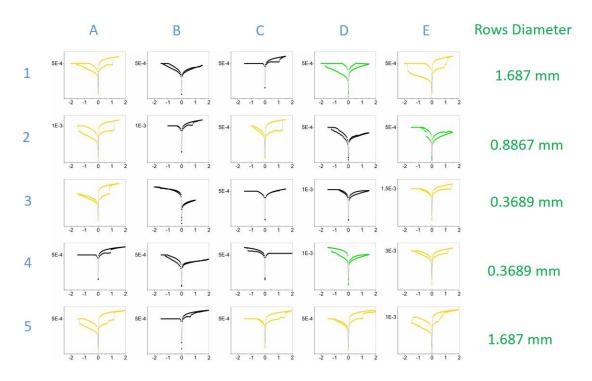

| Figure 4.16 - Typical behaviour of Ag/IGZOnp/Ti/Au annealed at 200 °C, subjected to 100 cycles with no C.C. (a) or distinct current compliances values: 5 mA (b), 3 mA (c) and 1 mA (d); and respective endurance characteristics (small inserted graphic)                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

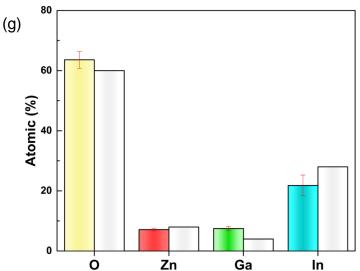

| Figure 7.1- (a,b) SEM images of the small nanoparticles agglomerates with different magnifications; (c-f) EDS elements mapping; and (g) atomic percentages calculated as an average of 10 different samples of IGZO (coloured) and respective percentages before synthesis (blank) |

| filtration                                                                                                                                                                                                                                                                         |

| Figure 7.9 - I-V characteristics of Au/Ti/IGZOnp/Ti structure plotted in log-log scale to evaluate the conduction mechanism                                                                                                                                                        |

### List of tables

| Table 4.1 - Electrical characteristics for the devices depicted in Figure 4.11           | 19  |

|------------------------------------------------------------------------------------------|-----|

| Table 4.2 - Performance comparison between Ti/IGZOnp/Ti and Ag/IGZOnp/Ti for 350 °C ar   | nd  |

| 200 °C annealing temperatures                                                            | 22  |

| Table 4.3 - Comparison values of the first cycles from different devices using (1)       |     |

| Ag/IGZOnp/IZO, (2) Au/Ti/IGZOnp/Pt/Ti and (3) Ti/IGZOnp/IZO structures                   | 27  |

| Table 7.1 – IGZO RRAM state of the art                                                   | 35  |

| Table 7.2 - Approximated resistance values for each electrode used in IGZO memory device | es. |

|                                                                                          | 42  |

#### 1. Motivation and objectives

Resistive Random Access Memories (RRAM) development has received a lot of attention by the scientific community in the past few years. Until now the most reliable and efficient technology for storage information was based on floating gate devices build on silicon technology, like flash drives and solid state drives (SSD). Therefore, due to Moore's law limitations there are a necessity to look for alternative architectures and new types of memories.

To suppress this problem and increase the speed and performance, keeping the same evolution rhythm, several types of non-volatile memories (NVM) have been developed. From which RRAM received a huge highlight as it consists a two terminal device with metal-insulator-metal (MIM) structure, allowing ultra-large-scale-integration (ULSI) densities. Other advantages like faster switching, low-operation voltage and longer storage time, support the idea that the future of storage devices rely on RRAM. This would generate the control of an enormous market, which involves all consumer electronic products from computing technology to health care. Furthermore, it would expand even more the internet of things (IoT) advent, becoming clear the huge economic motivation to create such devices.

Furthermore, it is important to notice the growing interest in flexible, printable and transparent electronics subject, which promises a huge impact on society. Therefore, it is propitious a compatibility from these new memories devices with this kind of technologies. Since Indium Gallium Zinc Oxide (IGZO) is one of the most efficient and investigated material regarding those topics, it will be studied in this master thesis. Adding the peculiarity of being solution based, obtained through hydrothermal process in nanoparticles form, which will act as switching layer in RRAM.

The main objective of this work focus on development, analysis and optimization of a non-volatile RRAM in a simple device configuration like MIM structure where solution based IGZO nanoparticles (IGZOnp) acts as insulator layer, normally used as semiconductor. In order to achieve a solid study over this devices, several steps were taken, such as:

- RRAM fabrication with different types of metal and transparent conductive oxide electrodes and consequent study over conductive mechanism.

- Temperature, solvents presence and vacuum influence on device performance and yield.

- Transition from bipolar to unipolar.

- Current Compliance influence.

All devices will be characterized with aim to record: set voltage, reset voltage, minimum read voltage, operation window. Being also submitted to retention and endurance tests.

Additionally, a comparative report to a MIM-double layer device produced at Universität *Darmstadt* will be performed and discussed.

#### 2. Introduction

#### 2.1. Non-volatile memory device

Memories devices are categorized into two: volatile and non-volatile. In volatile memories with which is possible to achieve fast operations, although there is a need to refresh periodically the storage cell, retaining the information which fades when the power supply is turned off. Static random access memory (SRAM) and dynamic random access memory (DRAM) are good examples. Non-volatile Memory (NVM) devices do not lose the information even after removing the power supply, however they operate slowed than volatile memories. Memories such as magnetic tapes, floppy disks, optical disks and flash memories are types of NVM [1], [2].

Motivated by silicon technology limitations, mainly the feature sizes, the scientific community have research and developed new types of NVM where the most relevant can be present as: (1) magnetic (MRAM), (2) phase change (PCM-RAM, PCRAM or PRAM), (3) ferroelectric (FeRAM) and (4) resistive (RRAM) random access memories [1].

#### 2.2. Resistive Random Access Memories

From all the emerging NVM referred, RRAM stands out as the most promising one. This fact is supported by its simple capacitor-like structure, composed by two electrodes and an insulator or semiconducting layer arranged between the electrodes. It is commonly known as MIM structure capable to be used as a cross point structure, allowing ultra-high density without using access devices. Adding the possibility of being compatible with silicon technology and the advantages of fast operations, low power consumption and simple fabrication process, it is easy to perceive a future for RRAM as a cheap universal memory technology [1], [3]–[5].

As it is explicit in the name, Resistive RAM include memories that store information by changing the MIM cell resistance. This behavior is controlled by applying different voltages at the device terminals. Usually a RRAM memory cell can have two resistive states: high-resistance state (HRS) (or low-conductive state LCS) and a low-resistance state (LRS) (or high-conductive state HCS), representing a logic value "0" or "1" respectively. In this case the cell is called single level cell (SLC). There are also memories cell that can achieve more than two resistive states being designated by multilevel cell (MLC) [1], [6]–[8].

#### 2.2.1. RRAM classification

RRAM can be classified in two categories depending on the switching mechanism. If the cell changes its resistance by cation motion is often designated as electrochemical metallization memory (ECM), atomic switch, or conductive bridge RAM (CBRAM). The second category relies on anionic-based device where the switching process is driven by oxygen ion motion (or oxygen vacancy, VO) these devices are called valence change memory (VCM) or oxide-based RAM (OxRAM) [1], [9]. There are also reports where both mechanism work together to improve the device performance [10].

#### **Electrochemical metallization system**

In this system a MIM cell is compose of two different electrodes: an electrochemical active metal, such as Ag, Cu, or Ni, and an electrochemically inert, where Au, Pt, Ir, W, can be used as

counter electrode (CE). Also, the thin film sandwiched between these two metals should allow a M<sup>Z+</sup> ion conduction [9], [11].

To occur the set mechanism, i.e. switch the cell resistance from HRS to LRS, three steps must be considered: (1) over a bias at AE (active electrode), takes place a metal anodic dissolution which generates metal cations ( $M^{Z+}$ ) and equivalent number of electron ( $Z^+$ ) in the following equation  $M \to M^{Z+} + Ze^-$ ; (2)  $M^{Z+}$  migration through the electrolyte/insulator layer by an electric field; (3) active metal reduction and electrocrystallization at CE, forming a filament, which preferentially grows from CE to AE, in the following equation  $M^{Z+} + Ze^- \to M$  [1], [5], [9]. A metal filament formation can also occur from AE to CE in specific cases where selenides and sulfides are used as insulator materials, due to a  $M^{Z+}$  smaller diffusion coefficient [9], [11].

When the filament reaches the AE the cell resistance switch from HRS to LRS, since electrons can move freely across the bridge. In order to recover the HRS it is usually applied a sufficient opposite voltage bias which beyond an electronic current in the filament, will create an electrochemical current responsible for the filament dissolution. It is also important to retain that switching speed is mainly driven by kinetics from the previous (1) and (3) steps [1], [5], [9].

#### Valence change system

In contrast to ECM which are cation based systems, valence change system is characterized by oxygen vacancies ( $V_0$ ) migration, created though anions movements. Generally, oxides are the most common switching media for these devices, such as  $TiO_x$  [12], [13],  $NiO_x$  [14], [15],  $HfO_x$  [16], [17],  $TaO_x$  [18], [19]. It is possible to divide VCM in two groups: (1) interface-and (2) filament-type.

Interface-type definition comes from the entire cell area involvement in the switching behavior, since the LRS is inversely proportional to the cell area. This type of device is generally composed by a metal-oxide ohmic contact and on the other electrode a metal-oxide schottky contact which allows RS behavior. The switching mechanism takes place when a negative voltage is applied to the electrode with schottky barrier on the oxide, which leads to an Vo accumulation. With the end of Vo from the opposite electrode, a higher electric field will result in a Vo depleted zone beneath the Vo-rich interface layer, leading to a HRS. Applying a positive voltage to metal-oxide schottky barrier will cause a reverse process resulting in a LRS [4], [5], [9], [20].

Regarding filament-type VCM, the mechanism behind resistive switching depends on formation and rupture of conductive filaments in the switching layer. For this reason, there is no or a very weak dependency between the resistance at LRS and cell area. It is possible to use p-type or n-type semiconductors to achieve the filament formation, since both can present abundant cation vacancies and anion vacancies, respectively [4], [5], [9], [20].

If the switching layer is composed of a p-type semiconductor, then the filament formation happens through a positive bias application at the top electrode (TE) which causes an oxygen ion migration from near crystal defects, such as Vo and grain boundaries, to the TE and accumulating in its vicinity, resulting in abundant cation vacancies, Figure 2.1 (b). Consequently, some of these vacancies can develop into nuclei that will grow preferentially due to effectively electrical field concentration and act as anode extension. This leads to a full filament formation which causes the device enter in a LRS, Figure 2.1 (c). When a negative bias voltage is applied to the TE a Joule heat phenomenon causes oxygen ions mobility acceleration which will migrate toward the CE and be stored in interface switching layer/CE or CE grain boundaries. Subsequently, this

process will reduce the cation vacancies concentration in conductive filament (CF) resulting in its rupture, near the cathode, switching the device from LRS to HRS, Figure 2.1 (d) [4], [5], [9], [20].

In the case of n-type switching layer, as it has many Vo, when a positive bias is applied to the TE, these Vo will migrate towards the CE and accumulate in its vicinity Figure 2.1 (f). This will form a nuclei of n-type semiconducting CFs which will grow and act as a cathode extension. The completion of this process will lead to a change in resistance state from HRS to LRS. Since this type of filament grows from the cathode to the anode, the thinner part will be located at the anode, Figure 2.1 (g). This part is easily ruptured by a negative bias over the TE, as the bias leads to a localized Joule heating resulting in a significant mobility acceleration of Vo towards the TE conducted by the electrical field. At the TE these Vo will be eliminated by the presence of stored oxygen. Again, the filament disruption leads to a switching mechanism from LRS to HRS, Figure 2.1 (h) [4], [5], [9], [20].

Figure 2.1– (a-d) Schematic of a VCM in p-type semiconductor, (a) mobile oxygen ions randomly distributed, (b) nucleation and cation vacancy filament growth from anode to cathode, (c) CF achieving LRS, (d) CF rupture achieving HRS. (e-h) Schematic of a VCM in n-type semiconductor, (e) Vos randomly distributed, (f) nucleation and Vos CF formation from cathode to anode, (g) CF achieving LRS, (h) CF rupture achieving HRS [9].

#### 2.3. Memristor

Memristor corresponds to the fourth basic circuit element, aside of (1) resistor, (2) capacitor and (3) inductor, predicted by Professor Leon Chua in 1971 [21], due to the studied symmetry between all this devices. It consists in a nanodevice capable of recording the voltage or current applied to itself [1], [21], [22]. Its behavior can be described by the equation (2.1) where the electrical charge is related to the magnetic flux.

$$d(\varphi) = M \cdot d(q)$$

(memristance) (2.1)

With its hysteretic behavior is possible to use the described device as a nonvolatile memory. In fact, is particularly useful because it can store and process multilevel resistance values as well as analog values. [5]

Although the memristor has been theorized in the 70s, only in 2008 was announced the first memristor fabrication, by HP Lab. This device consisted in a MIM structure, where "M" is Pt and the "I" a TiO<sub>2</sub> thin film. The mechanism behind the memory cell is explained by the switching from low conductivity to high conductivity. This event can happen due to TiO<sub>2</sub> stoichiometry, an exact 2:1 ratio of oxygen to titanium, shows an insulator characteristic though a conductive phenomenon takes place if the TiO<sub>2</sub> loses some oxygen resulting in an oxygen-deficient titanium oxide (TiO<sub>2-x</sub>) [1], [22].

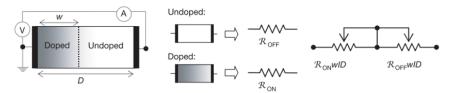

To achieve the described process, it is necessary a positive voltage bias applied to the top electrode, resulting in a doping front movement, i. e. the oxygens move towards the insulator part leaving a doped region behind, which consequently causes a cell resistance drop. If a negative bias is provided to the TE, then the oxygens will move toward TiO<sub>2-x</sub> zone generating TiO<sub>2</sub> and so increasing the overall resistance, as it is shown in Figure 2.2 [1], [22].

Figure 2.2 - Diagram of a coupled variable-resistor model for a memristor where V is voltmeter and A an ammeter, with the respective equivalent simplified circuit, resulting in a RonwID and RoffwID series [22].

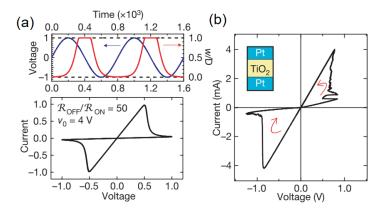

The resulting I-V characteristics can be seen in Figure 2.3 where (a) represents the predicted memristor behaviour by Strukov et. al. [22] and a real memristor result from a Pt-TiO<sub>2</sub>-x-Pt achieved by Stewart et. al. [23].

Figure 2.3 - Linear I-V characteristics of a TiO<sub>2</sub> memristor device: (a) Simulation plotting voltage stimulus (blue) and corresponding change in the normalized state variable w/D (red) versus time and resultant I-V characteristic; (b) experimental I-V characteristic of a Pt/TiO<sub>2-x</sub>/Pt [22], [23].

#### 2.4. RRAM operations

As it is expressed previously, low and high resistance states, so-called "LRS" and "HRS" can be achieved by different voltage bias applications. There are two basic operations can be considered: set and reset. It is called a set process when the cell passes from HRS to LRS, and

reset when the cell shifts from LRS to HRS. The RRAM are categorized in two operation types: unipolar resistive switching and bipolar resistive switching [1], [22].

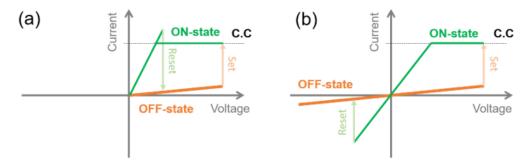

Unipolar behavior occurs when the switching procedure does not depend on the polarity of the applied programming voltage. Also, set process should have a certain current compliance (C.C.) to prevent the definitive short circuit of the cell. Reset voltage is always below the set voltage and do not need any kind of C.C. because it occurs at higher currents, Figure 2.4 (a) [1], [22].

Contrary to the previous operation, bipolar switching take place with a set voltage polarity different from the reset voltage polarity. The set process need C.C., and the reset do not need it, for the same reason as before, Figure 2.4 (b) [1], [5].

Figure 2.4 – Schematic of I-V linear curves for (a) unipolar behavior and (b) bipolar behavior. C.C represent the current compliance required to protect the memory cell from break down, during set process.

#### 2.5. IGZO as a RRAM switching layer

IGZO is one of the most studied and well documented oxide materials for TFTs applications since it can present high mobility, allowing also high flexibility, high transparency and is compatible with low-temperature fabrication process. With this characteristics, it is easy to conclude that is an optimal material to applied in systems on a panel (SoP) [24], [25]

The study over IGZO memory devices for a compatible usage in SoP did not start with resistive memories, instead the first device with an IGZO layer was a floating gate type memory develop in 2008 by Huaxiang Yin at. al. [26]. Only in 2010 start to appear developments on IGZO based RRAM with studies over bipolar behavior in full transparent devices [27], [28], unipolar behavior [19] and electrode influence [29]. In the following years more studies where made with this oxide, analyzing filament nature [30], achieving flexible devices [31], and more reports on the ways to improve this type of RRAM [8], [32]–[34].

Inspired on previous IGZO solution based TFT (Thin Film Transistor), Moon-Seok Kim and his team developed IGZO solution based RRAM [35]. However, the obtained results did not exceed one order of magnitude regarding the operation window. Moreover, Wei Hu [36] and his group were able to acquire a RRAM device by low temperature process, in this case, a photochemical solution deposition, resulting in uniform performance as well as a stable distribution of LRS and HRS. State of the art on *a*-IGZO RRAM devices (sputtered and solution-based) are shown in Table 7.1 in Annex A.

Until now there are no reports on IGZO nanoparticles applied to RRAM and for this reason opportunity arise to demonstrate the performance of these devices with such material produced with low-cost processes.

#### 3. Materials and Methods

In order to produce IGZO nanoparticle switching layer in a Resistive Radom Access Memory (RRAM) it was used a process developed by Santos et. al. [37], proven to work as semiconductor layer in electrolyte-gated transistors. However, in the present work it will be studied as an insulator layer in the same way as a-IGZO RRAM. Thus, to optimize the yield and performance some parameters were analysed such as annealing temperature and consequent presence of ethylene glycol. Also, an a-IGZO RRAM was produced for comparison with the obtained results.

#### 3.1. IGZO Nanoparticles Preparation and characterization

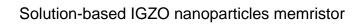

IGZO nanoparticles were prepared with gallium nitrate hydrate (Ga(NO<sub>3</sub>)<sub>3</sub>)·xH<sub>2</sub>O, Sigma-Aldrich, 99,9%), indium acetate (In(CH<sub>3</sub>COO)<sub>3</sub>, Sigma-Aldrich, 99,99%) and zinc acetate (Zn(CH<sub>3</sub>COO)<sub>3</sub>·2H<sub>2</sub>O, Sigma-Aldrich, 99%) precursors in a molar ratio 3:6:2, respectively. The mixture was dissolved in 2-methoxyethanol (6 ml, Sigma-Aldrich, 99,5%) and ethanolamine (0.2 mL, Fluka, 98%) as a cation reductor was added to the solution before left stirring at 50 °C for 1 h. The final solution was transferred to a 23 mL of PTFE (polytetrafluoroethylene) chamber, set inside a stainless steel autoclave (4745 general purpose vessel, Parr) and placed in an oven (L3/11/B170, Nabertherm) at 180 °C for 24 h. The resulted products were collected by centrifugation at 4000 rpm for 5 min (F140, Focus instruments) and dispersed in ethanol (20 mL).

Structural and morphological characterization of IGZO nanoparticles was performed by scanning electron microscopy (SEM, Carl Zeiss AURIGA) equipped with energy-dispersive X-ray spectroscopy (EDS), where a sacrificial layer of carbon has been previously deposited (quorum q150t es). EDS was used to determine the average atomic weigh from 10 samples, Annex B.

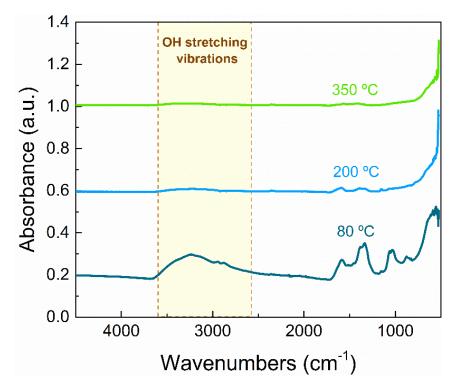

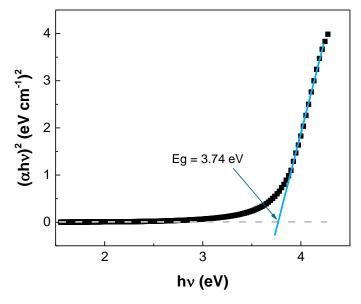

Fourier Transformed Infra-Red (FTIR, Thermo Nicolet 6700 Spectrometer) spectroscopy data was recorded using an Attenuated Total Reflectance (ATR) sampling accessory (Smart iTR) equipped with a single bounced diamond crystal (4500 to 525 cm<sup>-1</sup>). These results can be consulted in, Annex C. Optical band gap was performed in Perkin Elmer lambda 950 UV/VIS/NIR spectrophotometer resulting in 3.74 eV, Annex D.

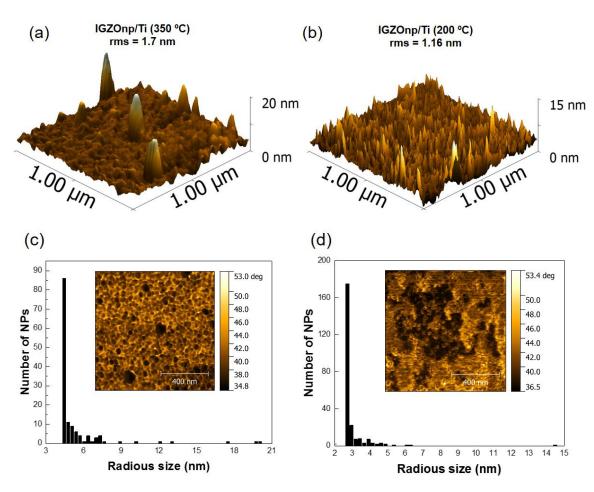

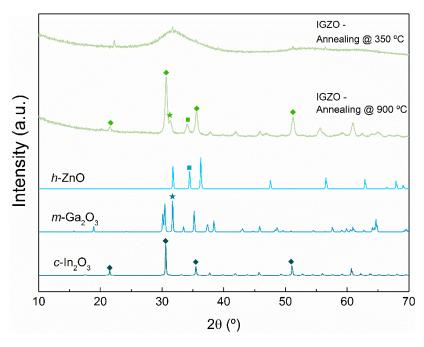

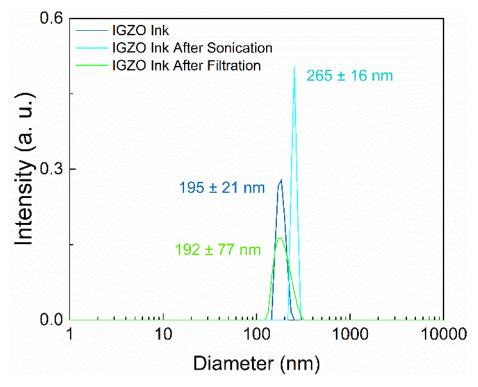

The nanoparticles were deposited on a silicon substrate for the x-ray diffraction (XRD) measurements being scanned in the 5-65° 2θ range with a step 0.033° in a PANalytical's X'Pert PRO MRD diffractometer with CuKα radiation, Annex E. The IGZO thin film surface roughness was analysed by atomic force microscopy (AFM) in a commercial microscope, Asylum research MFP-3D, on IZO thin film and examined in data analysis software (Gwyddion). Dynamic light scattering (DLS) technique using W130i Avid Nano, was employed to record the nanoparticles hydrodynamic diameter, Annex F.

#### 3.2. IGZO Thin Film Deposition and Characterization

To deposit the nanoparticles is necessary to create an ink, for that, ethylene glycol (Carlo Erba, 95,5%) was mixed with the nanoparticle dispersion in a 0.4:1.6 proportion, respectively, and left stirring for 24 h. Then was sonicated for 2 min and filtered with a 0.45  $\mu$ m porous diameter filter (Sartorius CA). The deposition process was performed by spin coating 4 layers at 2000 rpm during 35 s and dried at 100 °C for 1 min between each layer. The annealing process was made

after the fourth deposition at 350 °C and 200 °C for 1 h. Notice that the IGZO ink was deposited on different substrate materials depending on the device construction under study.

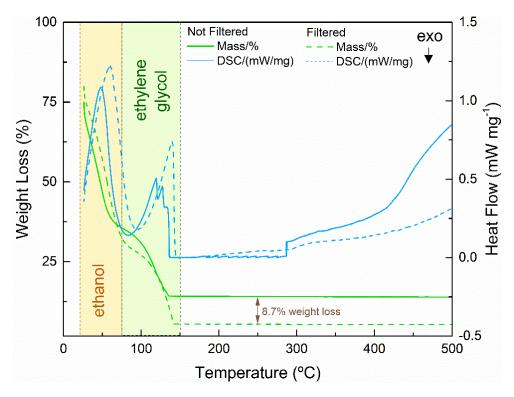

Moreover, IGZO inks were characterized by differential scanning calorimetry and thermogravimetry (DSC-TG, model STA 449 F3 Jupiter, Netzsch) with the solution in air with a heat ramp of 5 °C/min starting from room temperature up to 550 °C. These results can be consulted in annex G.

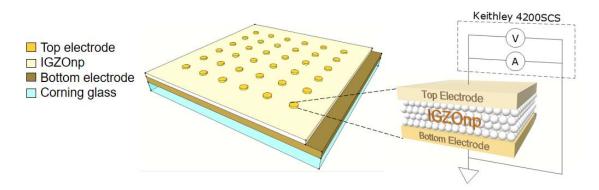

#### 3.3. RRAM assembly and characterization

Metal-insulator-metal (MIM) structures were fabricated by depositing different types of bottom electrodes on glass substrates (1737, Corning). In this case, (1) titanium (6 nm) and gold (60 nm); (2) titanium (6 nm) and platinum (60 nm); and (3) titanium (60 nm) were deposited by ebeam evaporation (homemade apparatus). Also, it was used an IZO (indium zinc oxide, 140 nm) layer deposited by radio frequency (13.56 MHz) magnetron sputtering (homemade apparatus), using a ceramic oxide target of  $In_2O_3$ :ZnO (89.3:10.7 weight fraction, Super Conductor Materials, Inc., 99.99%) at room temperature in the presence of a mixture of argon (20 sccm) and oxygen (0.4 sccm) at a deposition pressure of  $2 \times 10^{-3}$  Pa with a r.f. power of 75 W and a target–substrate distance of 15 cm [38].

Secondly, IGZO ink was deposited by spin coating process, previously described. Additionally, the devices for comparison made of *a*-IGZO switching layer were sputtered onto bottom electrodes using a IGZO (2:1:2) commercial ceramic target (LTS Chemical, Inc.) by a r.f. magnetron sputtering (AJA 1300-F system), without intentional substrate heating for 13 min and 30 s, under an air flow of 14 sccm and oxygen of 0.5 sccm, final pressure of 0.3 Pa, and a power of 100 W to achieve 30 nm thickness [39].

Finally, the top electrode (TE) deposition was executed in the same way as the bottom electrodes (BE), where (1) silver (60 nm); (2) titanium (6 nm) and gold (60 nm); and (3) titanium (60 nm) were used in different substrates. The final structure can be visualized in Annex H.

#### 3.4. Electrical IGZO RRAM characterization

IGZO RRAM electrical characterization was performed using a semiconductor characterization system (Keithley 4200SCS). These two terminal devices were connected to source measure unit (SMU) onto top and bottom electrode with the objectives to investigate: (1) set voltage, (2) reset voltage, (3) operation window, (4) retention time and (5) endurance.

Set voltage is executed applying positive sweep voltage on TE, with a fixed C.C. Starting always with 0 V to +1 V and going back to 0 V. The C.C. should be the smallest possible to achieve low power consumption [40], between 1  $\mu$ A to 10 mA range.

The reset voltage is performed also applying negative voltage sweep on TE, stating from 0 V to -1 V back to 0 V, without C.C. In case the reset process does not occur the voltage is increased. In some cases, the polarization for set and reset follow an opposite polarization, i. e. set is performed with negative voltages and reset is performed with positive voltage.

The I-V characteristics was always performed without delay time. Retention times test for both ON/OFF states where performed under a +0.1 V or -0.1 V constant voltage bias and the corresponding current value was recorded every 60 s.

#### 4. Results and discussion

This chapter addresses all the electrical characterizations of various IGZO RRAM types and configuration, where two structures will be taken as standard devices: (1) Ti/IGZOnp/Ti (from top contact to bottom contact) and (2) Ag/IGZOnp/Ti associated behaviours. Both standard memories present an area of 1.96x10<sup>-4</sup> cm<sup>2</sup>, were annealed at 350 °C, and analysed in air at room temperature (RT). We note that some variations in structure or and the fabrication parameters may occur during the work in order to achieve a more complete study based on IGZO RRAM.

#### 4.1. Memory cell activation

#### **4.1.1.** Forming

A forming step is required for the activation of the switching property, regardless the type of RRAM in the case of presenting a filament behavior [9]. This forming step corresponds to the first set process applied to the device. For this phenomenon to occurs a larger electrical field is required than the consecutives set processes. The cell will be formed from pristine state to low resistive state (LRS) by formation of the nanoscale filament. Then the on-state can be erased to high resistive state (HRS) by application of voltage bias at the opposite polarity.

Thenceforth, set and reset processes only occur in the weakest filament location within a small area, explaining the low voltage operation, after the first cycle [9]. Also, the forming is always performed with C.C. to avoid a filament overgrowth which otherwise could provoke a short circuit. Figure 4.1 identify the typical (a) unipolar and (b) bipolar behavior with the formation step in linear plot.

Figure 4.1 – Linear I-V (a) unipolar and (b) bipolar behaviours with typical forming steps (blue). The numbers indicate the occurrence order for (1) forming, (2) reset and (3) set, respectively.

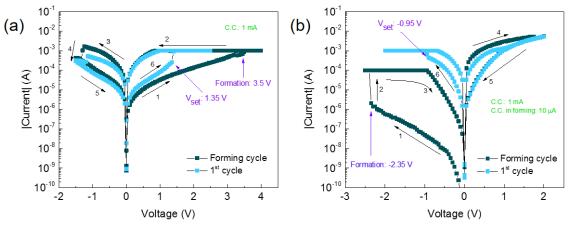

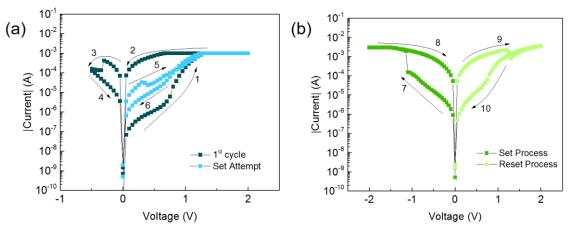

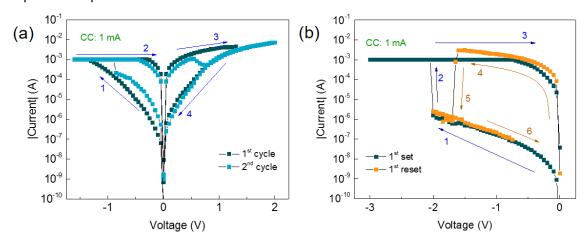

Figure 4.2 depicts two typical and distinct forming behaviours obtained for bipolar mechanism (a) Ti/IGZOnp/Ti and (b) Ag/IGZOnp/Ti, along this work. Figure 4.2 (a) present a similar mechanism to the one already represented in Figure 4.1 (b) considered to be a usual electroforming step and set/reset process for TI/IGZOnp/Ti devices. We note that for symmetric structure with both inert electrodes (Ti) the electroforming can be executed applying positive or negative polarization.

On the other hand, Figure 4.2 (b) shows a curious mechanism where the electroforming can be performed for lower C.C. than the consecutive cycles. Also, this forming step does not achieve the high conductive state (HCS), instead it only defines the low conductive state LCS, supported by the fact that arrow 3 is more compatible with arrow 6 than the HCS (set process

after arrow 6). Any reset attempt to achieve the same resistance as the one in pristine state is impossible even for higher reset voltages. By other words, the consecutive reset (arrows 4 and 5) is enable to drop the HCS to a conductive state equivalent to the pristine state. This effect limits the operating window to 10 or 10<sup>2</sup> in the best cases. Moreover, the electroforming polarization has a preferential polarization in order to occur, this fact is commonly seen in Conductive Bridge Random Access Memory (CBRAM) since one side has an active electrode which diffuses through the insulator matrix. The true mechanism will be explained in later sections.

Figure 4.2 - I-V characteristics containing forming and first cycle for (a) Ti/IGZOnp/Ti and (b) Ag/IGZOnp/Ti, depicting two distinct bipolar behaviours.

#### 4.1.2. Pre-forming

There is also a mechanism identified as pre-forming where the pristine state is in LRS instead of HRS, meaning that the cell has a filament formed before any electrical field application. It is speculated that such filament is created during annealing or deposition processes, and can rely on top electrode diffusion and/or vacancies defects within the switching layer due to temperature and/or lower thickness. However, the pre-formed state should be reset to LCS satisfying the memory criteria, i. e., should be able to operate normally regarding endurance cycles and retentions.

Since this phenomenon takes place during fabrication it is impossible to control and it may appear in different current states. As it starts with LRS a reset process with extra electrical field is needed, compared to the consecutive reset processes, in order to disrupt the filament and converting the cell into a working device.

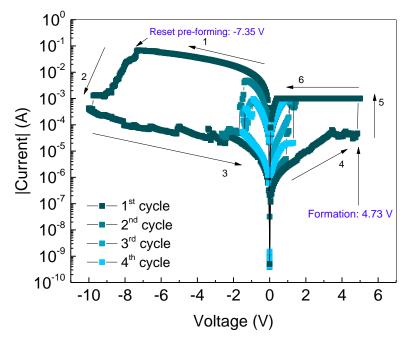

Figure 4.3 represents a typical pre-forming behaviour where the first step (1) is a reset process performed with negative voltage, -7.35 V, and a current value of 67 mA. Meaning that a high power is required to activate the cell. Furthermore, in order to achieve to memory performance a forming step of 4.73 V was needed.

Consequent set and reset cycles show a usual bipolar behaviour, between -2 and 2 V, highlighting that even after two non-ideal and stochastic process (pre-forming and forming) resistance switching can be occurred.

It is unknown for the author if there is any report over the pre-forming subject, since the memory performance can be drastically affected after the pre-form reset. One may also think it is a short circuit due to the similarities. In fact, pre-forming is an undesirable characteristic considering the need of a high electrical field in order to rupture the pre-existing filament(s).

Figure 4.3 - I-V characteristics of Au/Ti/IGZOnp/Ti annealed at 200 °C, showing a pre-forming and consecutive forming mechanism. The depicted arrows (1-6) demonstrate the orientation in which the memory is operated.

#### 4.1.3. Free forming

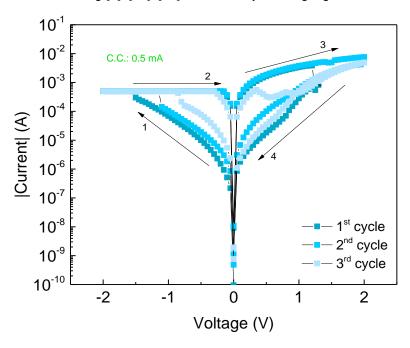

Finally, there are reports where RRAM do not need electroforming, i. e. present a forming free mechanism [28], [34]. From a practical point of view forming free is an interesting feature since allows lower operation power by eliminating the forming step. Consequently, resulting in a more stable resistive switching [7], [41], [42], theoretically causing lager endurance.

Figure 4.4 - I-V characteristic of Ag/IGZOnp/Ti annealed at 350 °C showing a free forming behaviour.

In this work, it was possible to achieve a forming free memory with the Ag/IGZOnp/Ti device annealed at 350 °C, depicted in Figure 4.4. Forming free behavior is discerned by looking at the

similarity in the first two set cycles. Since both first and second set cycles follow the same LCS (arrow 1) preforming the set in a very similar voltage, 1.5 V and 1.1 V respectively.

It is suggested that the reason for a forming free behavior in IGZOnp solution based memories rely on specific IGZOnp thickness, consequent number of nanoparticles in a certain volume as well as number of defects after annealing. Nevertheless, the appearance of forming free memories where rare and only occur for Ag/IGZOnp/Ti.

#### 4.2. Electrical characterization of standard IGZOnp memristors

#### 4.2.1. IGZO nanoparticles RRAM with inert electrodes

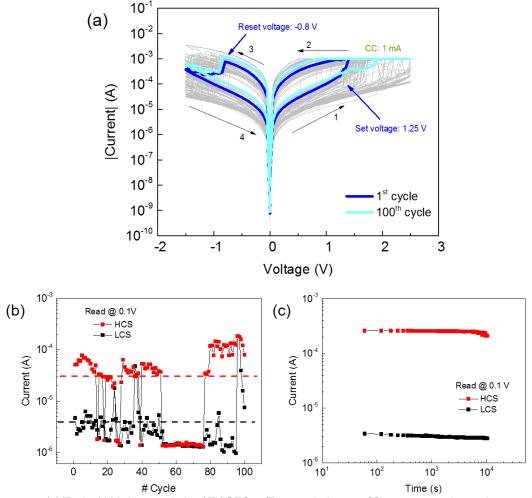

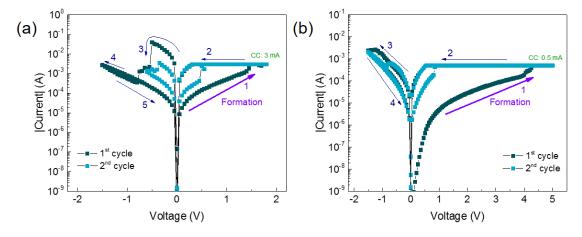

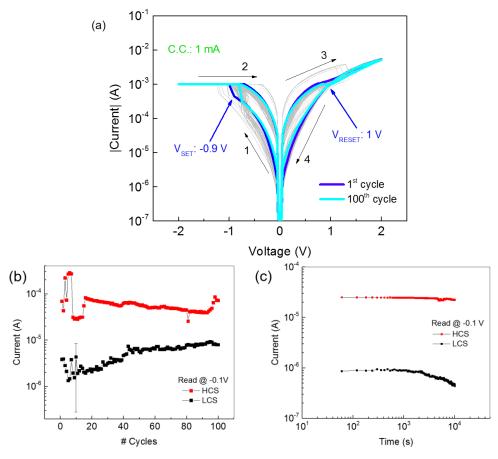

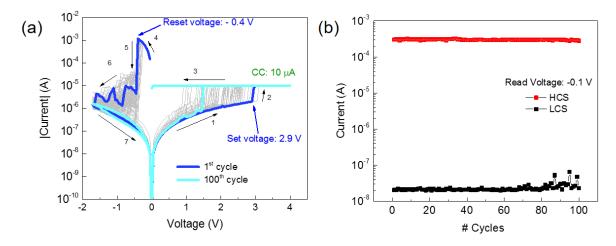

In order to IGZO nanoparticles act as a switching layer in an valence change memory (VCM) device it is necessary to be sandwiched by two inert electrodes, hence a Ti/IGZOnp/Ti structure annealed at 350 °C was fabricated. The correspondent electrical characterization is depicted in Figure 4.5, where (a) represents an endurance test over 100 cycles in sweep voltage mode. Set process is performed at 1.25 V in the first cycle, with a tendency to increase along the number of cycles. Reset process occurs between -0.8 V and -1.5 V.

Figure 4.5 - (a) Typical I-V characteristic of Ti/IGZOnp/Ti annealed at 350 °C over 100 cycles and respective, set and reset voltages indicated by a deep blue arrow, represent the respective value for each process in the first cycle. (b) Endurance characteristics at read voltage of 0.1 V at room temperature. (c) Typical retention characteristics read at -0.1 V at RT.

Arrows 1 to 4 represent the counterclockwise hysteresis direction. In fact, the hysteresis could be made with a clockwise direction (not shown) since this structure is a symmetric and operated as oxide based RAM (OxRAM). The respective electroforming process is already shown in Figure 4.2 (a) occurring at 3.5 V with 1 mA C.C.

Figure 4.5 (b) represents the alternated conductive value read with 0.1 V after each set and reset process that should correspond to HCS and LCS respectively. It is possible to distinguish two different levels with a ON/OFF ratio of one order of magnitude despite the unstable behavior. Notice that from cycle 52 to 72 the memory stopped working. This issue could rely on insufficient applied power for those cycles. Yet it regains the memory ability in the consecutive operations.

Figure 4.5 (c) is referent to a typical retention test executed over 10<sup>4</sup> s, being visible a stable behavior for both HCS and LCS.

#### 4.2.2. IGZO nanoparticles RRAM with active electrode

It is expected that a metal-insulator-metal (MIM) structure including IGZO nanoparticles with an active electrode on top acts as a CBRAM, in the same way that an *a*-IGZO sputtered memory in the same conditions does [8].

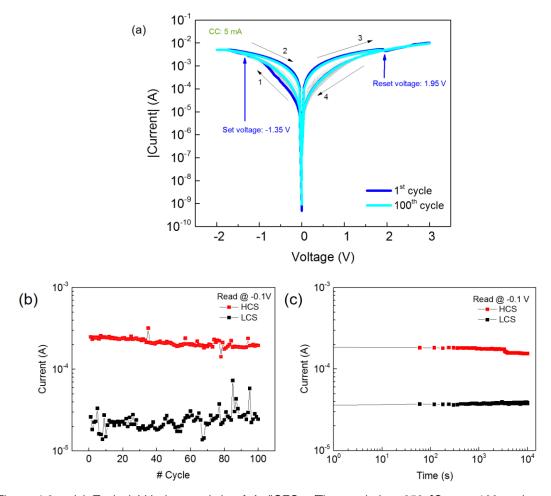

Figure 4.6 – (a) Typical I-V characteristic of Ag/IGZOnp/Ti annealed at 350 °C over 100 cycles and respective, set and reset voltages indicated by a deep blue arrow, represent the respective value for each process in the first cycle. (b) Endurance characteristics at read voltage of -0.1 V at RT. (c) Typical retention characteristics read at -0.1 V at RT.

In order to show a conductive bridge mechanism, IGZO nanoparticle layer need to behave as an amorphous thin film acting as a matrix for fast ion transport [5]. Although this layer takes an important role in the overall switching mechanism, the main focus is given to the active electrode, since it will drift through the IGZOnp matrix creating a filament. However, the true mechanism behind the switching operation is reveled to be different from the expected ECM behavior, which will be discussed in later sections.

Figure 4.6 (a) depicts a 100 cycles endurance test in sweep voltage mode applied to Ag/IGZOnp/Ti device annealed at  $350\,^{\circ}$ C. Set process is performed at -1.35 V approximately and reset occurs at 1.95 V. The represented arrows (1-4) demonstrate the hysteresis direction needed in order to have a working memory, as it was described in section 4.1.1, further details will be discussed in the conduction mechanism section (section 4.3.2). Respective cell activation is similar to the one represented in Figure 4.2 (b), however the first C.C. value is 0.5 mA instead of  $10\,\mu$ A.

It is possible to see in Figure 4.6 (b) that the analysed device endured for 100 cycles with a more stable behaviour than the OxRAM studied in section 4.2.1. Furthermore, the ON/OFF ratio is fixed with a 10 value during the endurance test.

Figure 4.6 (c) demonstrate a stable behavior during the retention test over 10<sup>4</sup> s.

#### 4.3. Conduction mechanisms

#### 4.3.1. Ti/IGZOnp/Ti devices

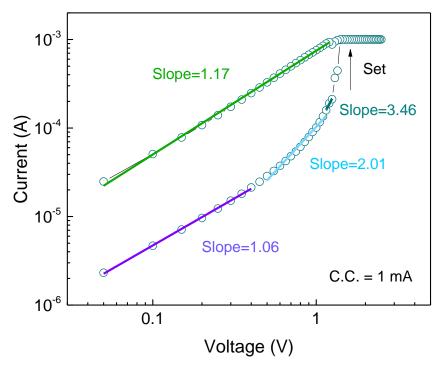

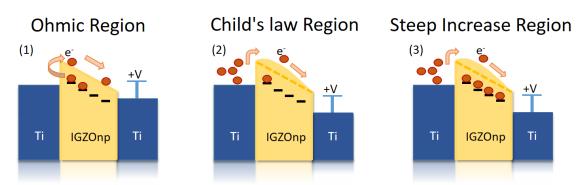

Until this point it was referred that memories with both inert contacts and an oxide as switching layer acted as a VCM. In this section we present the conduction mechanism of the Ti/IGZOnp/Ti devices.

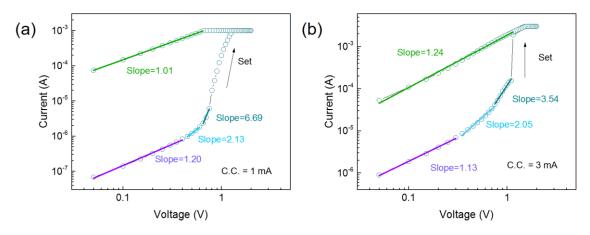

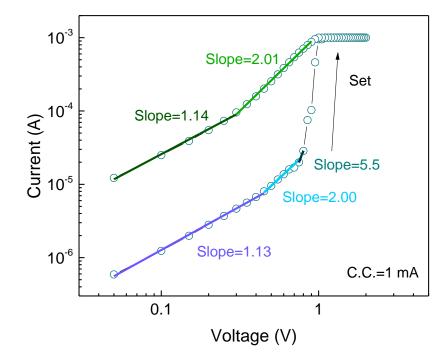

Figure 4.7 - I-V characteristics of Ti/IGZOnp/Ti structure plotted in log-log scale, showing a SCLC mechanism.

In order to determine the conductive mechanism is necessary to plot the first set I-V characteristics in a log-log scale, as it is represented in Figure 4.7, and analyse the respective fittings to determine the carrier transport. At LCS the curve reveals a linear ohmic behavior since it presents an approximate slope of 1, from 0 to 0.4 V. An ohmic behavior is characterized by the mobile electrons movement in the conduction band [27], and holes in the valence band. It can also suggest that the density of thermally generated free carriers inside the switching layer is larger than the injected carriers [43].

From 0.4 V to 1.15 V the curved can be fitted with a slope of 2, which is in accordance to Child's square law (I  $\propto$  V²), where the current becomes dominated by injected electrons. Consequently, injected electrons can be divided into two groups, one will occupy the traps and the other will act as free electrons. When all the traps are filled with electrons, than the last region is reached in accordance to steep increase region (I  $\propto$  V<sup>n</sup>, n>2) allowing the shift between LCS to HCS [44].

The referred three regions: (1) ohmic, (2) Child's law and (3) steep increase, belong to space-charge-limited conduction (SCLC) mechanism, as represented on Figure 4.8 where the traps in bulk are the key factor to the switching operation [8]. These results are in agreement with the ones obtained by similar *a*-IGZO memories sandwiched by inert electrodes [28], [36].

Figure 4.8 - Schematic of SCLC mechanism composed by (1) ohmic region, (2) Child's law region and Steep Increase region.

On the other hand, HCS only shows ohmic behaviour, indicating the presence of highly conductive paths during the switching event [34]. Furthermore, the difference between the ON and OFF state suggests a confined effect in the HCS rather than homogenously distributed [8].

The filament nature can only be determined by fitting a I-T characteristic at HCS and support from X-ray photoelectron spectroscopy (XPS) as well as High Resolution Transmission electron microscopy (HRTEM). Those tests were not performed due to time and/or equipment restrictions. As the previous mechanisms for LCS and HCS matches with studies already made [28], [36] it is expected that the nature of the filaments are similar to oxygen vacancies.

#### 4.3.2. Ag/IGZOnp/Ti devices

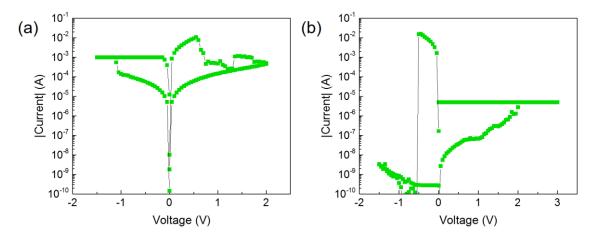

Notice that Ag/IGZOnp/Ti devices operate with set process in negative voltage and reset with positive voltage, shown in Figure 4.6 (a). Which is the opposite of Ti/IGZOnp/Ti memories and Ag/a-IGZO memories [8]. This phenomenon suggests that instead of Ag filament the switching mechanism is effectuated with Vo. Supported by the fact that Ag needs positive voltage application to turn into Ag<sup>+</sup> and diffuse. On the other hand, Vo migration do not need a specific polarization since the switching mechanism occurs in the IGZOnp layer instead of an electrode.

The previous notion of a dominant Vo switching mechanism can be explained by the test depicted in Figure 4.9. In Figure 4.9 (a) set and reset process occurs with positive and negative voltage sweep application, respectively (arrows 1-4), as expected from a usual voltage application in case of VCM or ECM mechanisms. Consequently, if a positive voltage is applied to the memory, it gets a second reset (arrows 5, 6 Figure 4.9 (a)) instead of a set process. In turn, if a negative voltage is then applied a set process (arrows 7, 8, Figure 4.9 (b)) is followed by a reset process (arrows 9, 10, Figure 4.9 (b)).

Thus, it is noticeable a preferential VCM mechanism with preferential set at negative voltage and reset at positive voltage. Excluding any ECM mechanism occurrence.

Figure 4.9 - I-V characteristic of Ag/IGZOnp/Ti device showing a swift to a preferential set process with negative voltage aplication on AE.

Regarding the conductive mechanisms both set with positive and negative voltages present a SCLC behaviour, depicted in Figure 4.10, as reported by previous works [8], [28].

Figure 4.10 - I-V characteristics of Ag/IGZOnp/Ti structure plotted in log-log scale, showing a SCLC mechanism in both (a) ECM and (b) VCM regime.

Furthermore, oxygen vacancies conducting filaments (CF) are formed at higher voltages in the range of 0.2 V to 1 V than metallic CF approximately in the range of 1 to 1.5 V [45]. In addition, conventional CBRAM devices show larger ON/OFF ratios compared to OxRAMs. Here, the LCS and HCS are maintained with an ON/OFF ratio of slightly more than one order of magnitude Ag/IGZOnp/Ti devices which is desirable for practical application [46]. We note that the Ag/IGZO form a Schottky contact as already known in literatures [46], [47] leading to difficult forming process at the positive polarity.

Combining the above results, we suggest that VCM is the responsible resistive switching mechanism.

#### 4.4. Air and Vacuum influence

Air and vacuum influence were tested for OxRAM devices with the Ti/IGZOnp/Au/Ti configuration since these memories are not passivated. Furthermore, there are reports showing an atmospheric impact on the device performance, mostly over VCMs [28], [48], [49].

In this case, all devices present an area of  $3.3 \times 10^{-3}$  cm<sup>2</sup> and were annealed at 350 °C, the analysis under vacuum were performed with a pressure of  $3.33 \times 10^{-4}$  mBar.

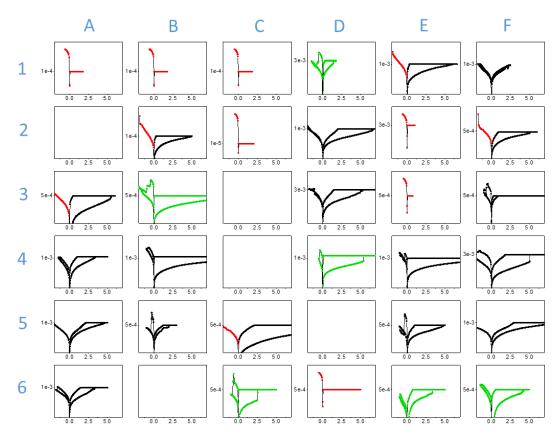

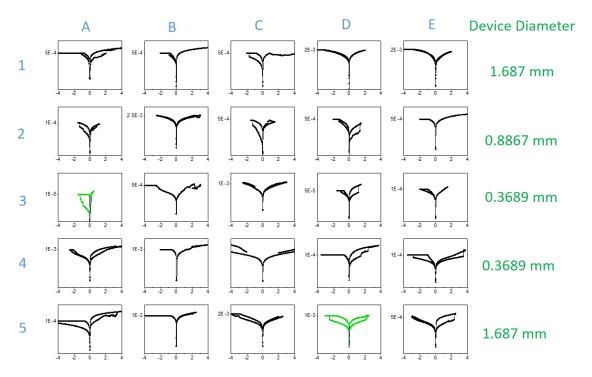

Taking into account that spin coating process can influence the thickness along the substrate and consequently the devices performance, exactly half of the devices were analysed under air (rows 1 to 3) and vacuum conditions (rows 4 to 6) of the same substrate, shown in Annex I.

Based on the overall results provided by the working devices in Annex I, it is difficult to assume an existence of atmospheric influence, since it is impossible to make a statistical analysis with a 19% yield associated with very different RS results. This low yield equally achieved in both air and vacuum devices can be explained by a non-uniform nanoparticle coating, which conceded different thicknesses in the nanoparticle layer over the substrate.

Nevertheless, it is depicted in Figure 4.11 the best results for each case, (a) air and (b) vacuum. From the data shown in Table 4.1 it is possible to confirm that C.C. under vacuum conditions can be one order of magnitude lower than in air conditions. Meaning that the power consumption will be also one order of magnitude lower.

Figure 4.11– I-V characteristics of Ti/IGZOnp/Au/Ti first and second cycle (a) under air and (b) vacuum.

Table 4.1 - Electrical characteristics for the devices depicted in Figure 4.11.

|        | C. C.  | Forming | Set<br>Voltage | Reset<br>Voltage | Read<br>Voltage | Operating<br>Window |

|--------|--------|---------|----------------|------------------|-----------------|---------------------|

| Air    | 3 mA   | 1.45 V  | 0.5 V          | -0.35 V          | 0.1 V           | 10                  |

| Vacuum | 0.5 mA | 4.25 V  | 0.8 V          | -0.8 V           | 0.1 V           | 10                  |

This fact can be supported by a larger initial resistance which allows a formation process for smaller C.C. but for higher voltages. In the other hand, because the device working in vacuum shows higher resistance at pristine state compared to the working device in air, it needs a larger C.C. in order to show a significant operation widow (≥10).

Also, notice that Figure 4.11 (a) presents a low forming voltage compared to those in Annex A, allowing reduced damage from the forming process.

Nonetheless, there is no difference between the all working Ti/IGZOnp/Au/Ti memories in relation to the operating window at 0.1 V read voltage.

#### 4.5. Effect of annealing temperature

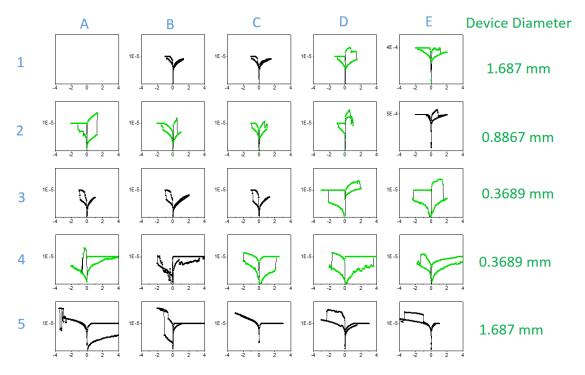

The devices were also produced with an annealing temperatures of 200 °C to be compared with the previous 350 °C annealed Ti/IGZOnp/Ti and Ag/IGZOnp/Ti structures. Lower process temperatures can unlock advantages since the fabrication process is cheaper and can be possible to integrate the memories on flexible substrates.

This test will also indicate if there is some influence regarding the ethylene glycol present in the IGZOnp layer, since 200  $^{\circ}$ C is an insufficient temperature to degradate the ethylene glycol (annex G) [37]. As previously in this section all devices present the same dimension of 1.96x10 $^{-4}$  cm $^{2}$ .

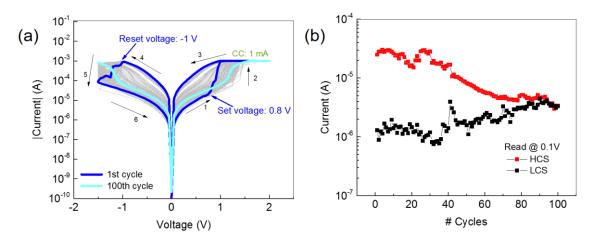

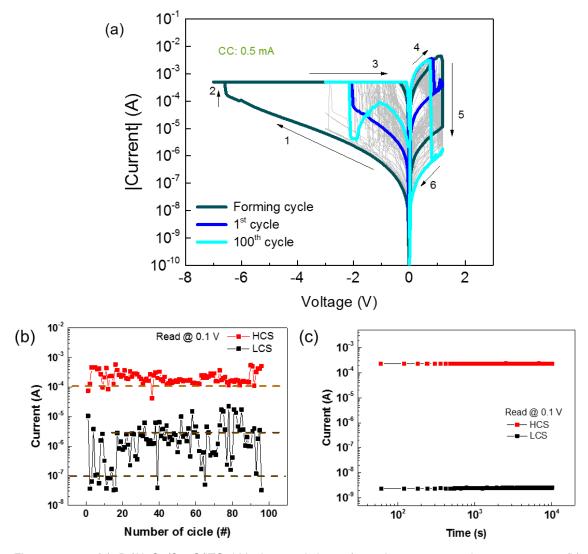

### 4.5.1. Ti/IGZOnp/Ti annealed at 200 °C

Figure 4.12 (a) depicts a Ti/IGZOnp/Ti structure annealed at 200 °C over 100 cycles as an endurance test, in sweep voltage mode. Set process occurs with positive voltage between 0.8 and 1.3 V and reset voltage appears for -1 to -1.5 V. The hysteresis direction is represented by the arrows (1-6), in a counterclockwise direction as usual, however it can be performed in the opposite direction due to the use of inert electrodes in both sides of IGZOnp, in the same manner as the previous Ti/IGZOnp/Ti annealed at 350 °C.

Respective cell activation was already presented in Figure 4.3 as a pre-forming mechanism with a consecutive forming appearing at 4.73 V applying 1 mA C.C.

Figure 4.12 – (a) I-V characteristic of Au/Ti/IGZOnp/Ti annealed at 200  $^{\circ}$ C over 100 cycles and respective, set and reset voltages indicated in blue represent the minimum value for each process; (b) endurance characteristics at read voltage of 0.1 V.

Figure 4.12 (b) represents the correspondent conductive value read at 0.1 V after each set and reset, equivalent to LCS and HCS respectively. It is possible to confirm an ON/OFF ratio > 10 until the 40<sup>th</sup> cycle, after which both LCS and HCS start to gradually degrade, also shown in Figure 4.12 (a) by the set and reset shift to higher values. This phenomenon can be explained by the performance drop due to overpower during pre-forming reset and consecutive forming, as seen in Figure 4.3.