#### **Ângelo Emanuel Neves dos Santos**

Licenciado em Ciências da Engenharia de Micro e Nanotecnologias

## Design and simulation of a smart bottle with fill-level sensing based on oxide TFT technology

Dissertação para obtenção do Grau de Mestre em Engenharia de Micro e Nanotecnologias

Orientador: Doutor Pedro Miguel Cândido Barquinha,

Professor Auxiliar, Faculdade de Ciências e Tecnologia,

Universidade Nova de Lisboa

Co-orientador: Doutor João Carlos da Palma Goes,

Professor Associado com Agregação, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa

Presidente: Professor Doutor Rodrigo Ferrão de Paiva Martins Arguente: Professor Doutor Vítor Manuel Grade Tavares Vogal: Professor Doutor Pedro Miguel Cândido Barquinha

Outubro, 2016

## Design and simulation of a smart bottle with fill-level sensing based on oxide TFT technology

Copyright © Ângelo Emanuel Neves dos Santos, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa.

A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objectivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

"The beginning of wisdom is found in doubting; by doubting we come to the question, and by seeking we may come upon the truth."

Pierre Abelard

## **Acknowledgments**

A finalização desta dissertação representa uma enorme etapa na minha vida, sendo que durante estes cinco anos de estudo na Faculdade de Ciências e Tecnologias tenho a agradecer a muitas pessoas, muitos momentos, e muitos problemas que fizeram de mim o que eu sou hoje.

Em primeiro lugar, não poderia deixar de agradecer ao Prof. Dr. Rodrigo Martins e à Prof.ª Dra. Elvira Fortunato, pela criação do magnífico mestrado em Engenharia de micro e nanotecnologias, cuja excelência e multidisciplinaridade é verdadeiramente notável para qualquer um que entenda a natureza dos conceitos científicos que são lecionados. Complementando o curso, os professores criaram ainda as excelentes instituições CENIMAT|i3N e CEMOP providenciando os meios científicos e tecnológicos necessários para o avanço da investigação nos mais diversos ramos nas áreas de materiais e da eletrónica, tendo eu a agradecer a possibilidade de trabalhar e de fazer parte de um grupo com uma qualidade e renome de nível mundial.

Em segundo lugar gostaria de agradecer aos meus orientadores Prof. Pedro Barquinha e Prof. João Goes sendo que ambos foram importantíssimos no desenvolvimento deste projeto. Ao Prof. Pedro tenho a agradecer toda a motivação e votos de confiança que me foram dados ao longo do projeto, e ainda por toda a ajuda e conhecimentos partilhados para que os objetivos finais fossem atingidos. Ao Prof. João Goes tenho a agradecer toda a ajuda inicial no desenvolvimento e consolidação dos requisitos necessários do projeto a nível eletrónico, sendo esta fulcral para o correto desenvolvimento do mesmo. Não podendo deixar de agradecer pela disponibilidade de ambos os professores, que apesar do pouquíssimo tempo livre, sempre se mostraram disponíveis para que eu, em caso de qualquer dúvida, não hesitasse em contactar.

Gostava ainda de deixar o meu agradecimento ao Prof. João Pedro Oliveira, foi graças a ele e às suas motivadoras aulas e palestras que descobri a minha paixão pelo mundo da eletrónica, muito obrigado por todas as conversas fora de aula sobre os mais diversos temas.

Gostaria também de deixar o meu enorme agradecimento à Ganga Bahubalindruni, que se mostrou incansável no apoio em tudo o que pudesse estar relacionado com o projeto. Obrigado pela ajuda no debugging de vários blocos eletrónicos e ainda pelos conhecimentos transmitidos relativamente ao desenho de layouts.

Um especial obrigado aos meus grandes amigos e colegas "Mágico" e José Rosa. Obrigado por todas as discussões às horas de almoço, por toda a amizade e apoio nos momentos mais difíceis e cruciais ao longo deste curso, se existem amizades que se sabe à partida que duram para toda a vida, eu sei que vocês são uma delas. Não posso deixar de agradecer aos restantes colegas que de alguma forma me ajudaram ou simplesmente fizeram parte deste meu percurso académico: Tomás, José Correia, Ismael, Pedro Trigo, Gonçalo Santos, Ana Correia, Diogo Lima e João Loureiro.

Nada disto seria possível sem o apoio da minha família, a eles devo tudo o que tenho hoje, um muito obrigado a todos, nomeadamente às minhas irmãs Sandrina, Cindy e Priscilla pela motivação, alegria e maluquice que me transmitem todos os dias, ao meu Pai Manuel, à minha segunda família da qual fazem parte a Maria e o Diogo pelo carinho e apoio que me dão desde que era praticamente uma criança, e especialmente à minha mãe, por todos os conselhos, e por toda a ajuda ao longo dos meus anos de vida. Mãe, não existem palavras que possam descrever a minha gratidão por tudo o que fizeste por mim, sei que, contigo posso contar até ao final da vida!

Um infinito obrigado à minha namorada Rutie, por tudo e por nada. Por tudo o que fazes por mim para me ver feliz e por nada mudar ao longo de todos estes anos. És, e sempre serás das pessoas mais importantes da minha vida, e a ti agradeço-te tudo. Mesmo sem perceberes a área cientifica em que trabalho, consegues-me sempre ajudar com as tuas palavras e ideias malucas, nunca mudes.

Obrigado ainda ao meu "tropa" Mihai Cotoman, por todos aqueles momentos que só ele sabe, e por todas as conversas "cientificas" e cafés que ajudaram a desanuviar a cabeça de todos os problemas que surgiam.

Em último lugar não posso deixar de agradecer a todos os amigos exteriores à faculdade que de alguma forma me ajudaram ao longo da minha vida: Ivan Côrte-Real, João Miguel, André Pinto, Fernando Vieira, Diogo Araújo, Natacha Moreira, Diogo Fernandes, Filipe Macário, e todos os restantes que me possa ter esquecido.

Do fundo do meu coração, um muito obrigado a todos!

#### **Abstract**

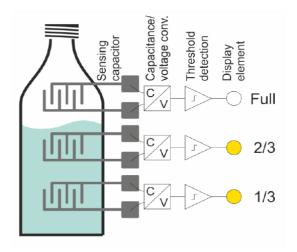

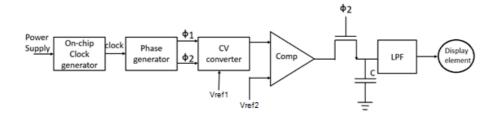

Packaging is an important element responsible for brand growth and one of the main reasons for producers to gain competitive advantages through technological innovation. In this regard, the aim of this work is to design a fully autonomous electronic system for a smart bottle packaging, being integrated in a European project named ROLL-OUT. The desired application for the smart bottle is to act as a fill-level sensor system in order to determine the liquid content level that exists inside an opaque bottle, so the consumer can exactly know the remaining quantity of the product inside.

An in-house amorphous indium—gallium—zinc oxide thin-film transistor (a-IGZO TFT) model, previously developed, was used for circuit designing purposes. This model was based in an artificial neural network (ANN) equivalent circuit approach.

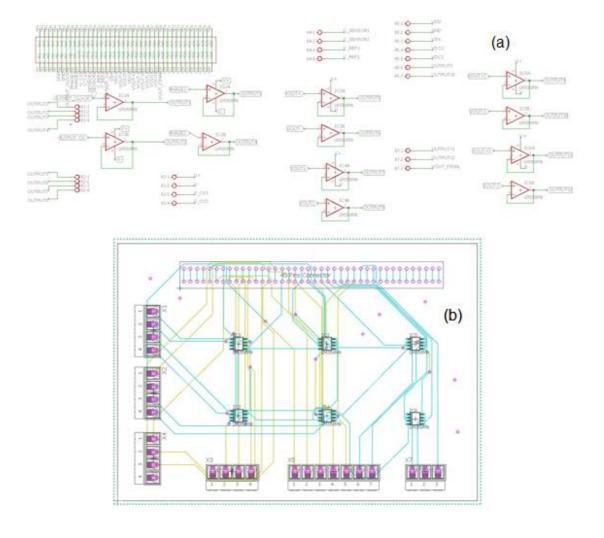

Taking into account that only n-type oxide TFTs were used, plenty of electronic building-blocks have been designed: clock generator, non-overlapping phase generator, a capacitance-to-voltage converter and a comparator. As it was demonstrated by electrical simulations, it has been achieved good functionality for each block, having a final system with a power dissipation of 2.3 mW ( $V_{DD}$ =10 V) not considering the clock generator. Four printed circuit boards (PCBs) have been also designed in order to help in the testing phase.

Mask layouts were already designed and are currently in fabrication, foreseeing a successful circuit fabrication, and a major step towards the design and integration of complex transducer systems using oxide TFTs technology.

Keywords: Smart packaging; a-IGZO TFTs; capacitance-to-voltage converter; comparator; oxide TFTs circuit integration.

#### Resumo

As embalagens são um elemento importante no crescimento de determinadas marcas e uma das principais razões pelas quais certos produtores ganham vantagem competitiva através de inovações tecnológicas. Neste âmbito, o objetivo deste trabalho corresponde ao desenvolvimento de um sistema eletrónico totalmente autónomo para uma garrafa inteligente, estando este integrado num projeto europeu designado de ROLL-OUT. A aplicação pretendida da garrafa, é que esta contenha um sistema sensível ao nível de enchimento do liquido da mesma, de forma a que o consumidor possa determinar, de forma exata, a quantidade restante de produto existente dentro de uma garrafa opaca.

Para o propósito de desenho de circuitos, foi usando um modelo de transístores de filme fino baseados em óxido de gálio-índio-zinco amorfo (a-IGZO TFTs), sendo que o mesmo fora anteriormente desenvolvido. Este modelo foi baseado numa aproximação de circuitos equivalentes através de redes neuronais artificiais.

Tendo em conta que apenas transístores do tipo-n foram utilizados, foram desenvolvidos vários blocos eletrónicos: gerador de relógio, gerador de fases não sobrepostas, conversor capacidade/tensão e um comparador. Tal como foi demonstrado através de simulações elétricas, foi alcançada uma boa funcionalidade para cada bloco, tendo-se obtido um sistema final com uma dissipação de potência de 2.3 mW (VDD=10 V), não considerando o gerador de relógio. Foram ainda desenvolvidas quatro placas de circuito impresso com o objetivo de futuramente auxiliar o teste dos circuitos produzidos.

Os layouts das máscaras já foram desenvolvidos estando neste momento em fase de fabricação, prevendo-se assim uma produção de circuitos bem-sucedida, e um grande passo no desenvolvimento e integração de sistemas transdutores complexos usando a tecnologia de transístores de óxidos semicondutores.

Palavras-chave: Embalagens inteligentes; a-IGZO TFTs; conversor capacidade/tensão; comparador; integração de circuitos com transístores de óxidos.

## **Contents**

| Acknowledgments                                                                 | V    |

|---------------------------------------------------------------------------------|------|

| Abstract                                                                        | vii  |

| Resumo                                                                          | ix   |

| Contents                                                                        | xi   |

| List of figures                                                                 | xiii |

| List of Tables                                                                  | xv   |

| Symbols                                                                         | xvii |

| Acronyms                                                                        | xix  |

| 1 Motivation and Objectives                                                     | 1    |

| 2 Introduction                                                                  | 3    |

| 2.1 Thin-Film Transistors                                                       |      |

| <ul><li>2.2 Capacitance-to-voltage converters</li><li>2.3 Comparators</li></ul> |      |

| 3 Materials and Methods                                                         | 9    |

| 3.1 Modelling, Design and Simulation Tools                                      | 9    |

| 3.2 Electrical characterization of transistors and circuit                      | ts10 |

| 4 Results and Discussion                                                        | 11   |

| 4.1 Fill level sensing in smart bottle: Concept and Blo                         | =    |

| 4.2 Circuit design, simulations and layouts                                     |      |

| 4.3 Printed circuit board design                                                |      |

| 5 Conclusions and Future Perspectives                                           | 35   |

| 6 References                                                                    | 37   |

| 7 Annexes                                                                       | 39   |

| Annex A – Design rules considered in each layer                                 | 39   |

| Annex B – Transistor dimensions                                                 |      |

| Annex C - Printed circuit boards schematics and layouts                         | s 43 |

## **List of figures**

| Figure 1.1- Scheme of the smart bottle functioning principle and the main electronic block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ks 1      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

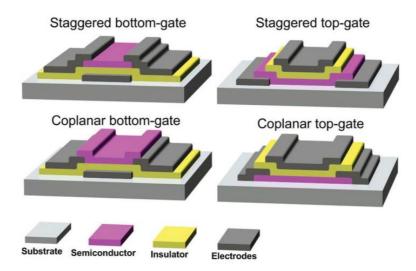

| Figure 2.1- Scheme of the most conventional TFT strutures, according to the position of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | the       |

| gate electrode and sorce/drain electrodes relatively to the semiconductor, adapted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | from      |

| [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4         |

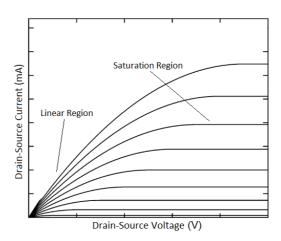

| Figure 2.2- Ideal output curves of a n-type TFT, adapted from [37]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5         |

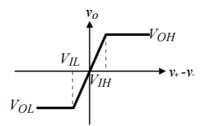

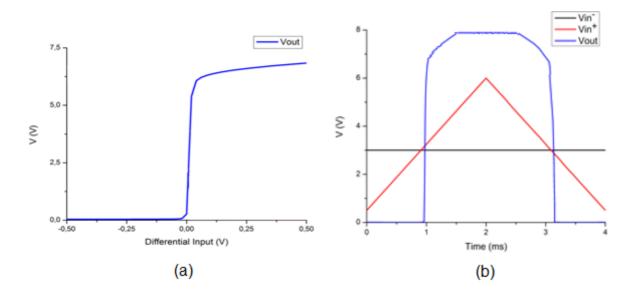

| Figure 2.3- Voltage transfer characteristic of a comparator with infinite gain, adapted from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | n [27]. 8 |

| Figure 4.1- Block diagram of the full fill-level sensing smart bottle system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11        |

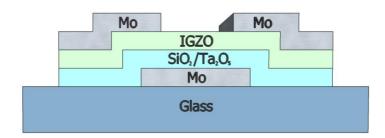

| Figure 4.2- Staggered bottom gate structure of the IGZO TFTs, adapted from [30]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13        |

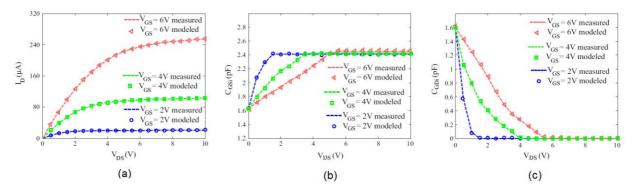

| Figure 4.3- Verilog-A neural model performance validation from the measurements 0 ≤ V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ′DS ≤     |

| 10 V in steps of 0.5 V and 2 ≤ VGS ≤ 6 V in steps of 2 V.(a)- Output characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | curvers   |

| of the TFT. (b)- C-V characteristics curves CGSi. (c)- CGDi. Adapted from [29]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13        |

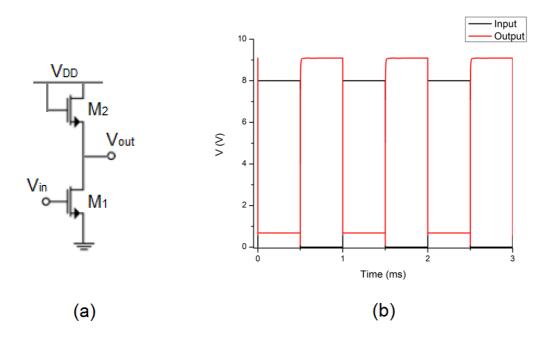

| Figure 4.4- (a)- Circuit schematic of an inverter with a diode-connected load. (b)- Transie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ent       |

| simulation result for the inverter considering the n-type load W/L= 10/20 μm/μm and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | d driver  |

| W/L= 80/20 μm/μm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14        |

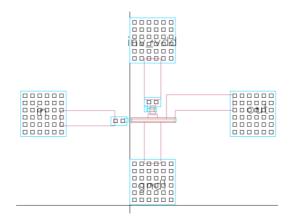

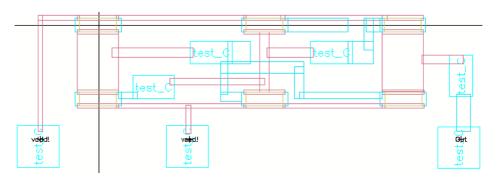

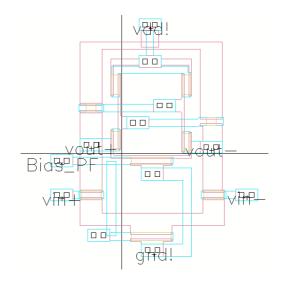

| Figure 4.5- Layout of the inverter circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15        |

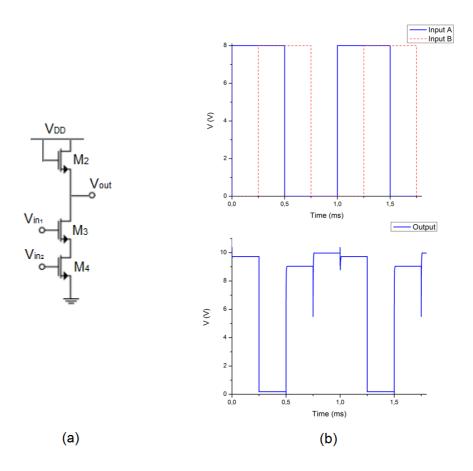

| Figure 4.6- (a)- Circuit schematic of a NAND with a diode-connected load. (b)- Transient                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

| simulation result of the NAND considering the n-type load W/L= 10/20 μm/μm and α                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | drivers   |

| W/L= 80/20 μm/μm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16        |

| Figure 4.7- Layout of the NAND gate circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16        |

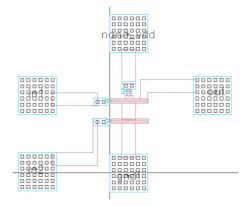

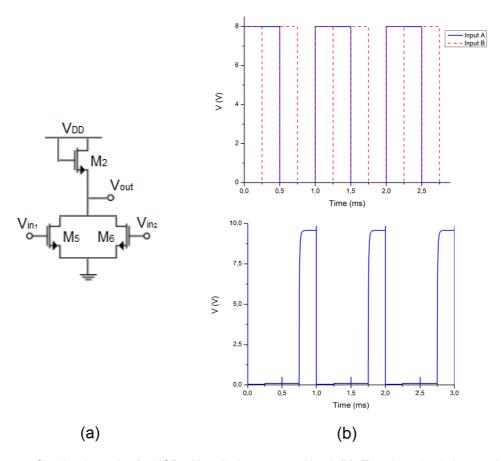

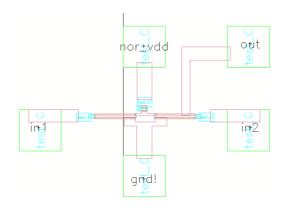

| Figure 4.8- Circuit schematic of a NOR with a diode-connected load. (b)- Transient simul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ation     |

| result of the NOR considering the n-type load W/L= 10/20 μm/μm and drivers W/L=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 80/20     |

| μm/μm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17        |

| Figure 4.9- Layout of the NOR gate circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18        |

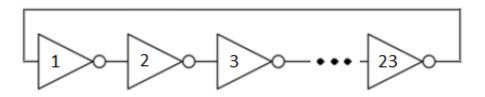

| Figure 4.10- Scheme of a 23-stages ring oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19        |

| Figure 4.11- 23-stages ring oscillator layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19        |

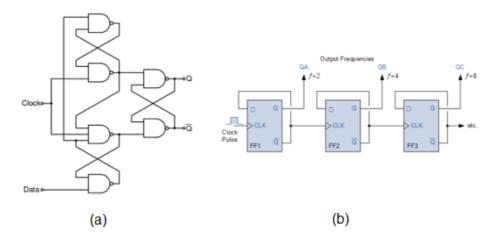

| Figure 4.12- (a)- Circuit schematic of a D-type flip-flop. (b)- Scheme of the frequency divi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | der       |

| feedback connections using a D-type flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20        |

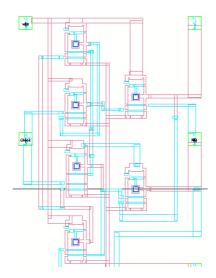

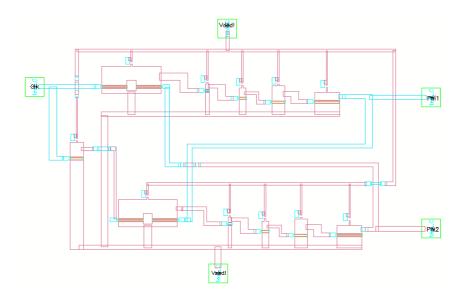

| Figure 4.13- D-type flip-flop counter layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20        |

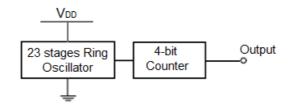

| Figure 4.14- Scheme of the clock generator, comprising the ring oscillator and the 4-bit c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ounter.   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21        |

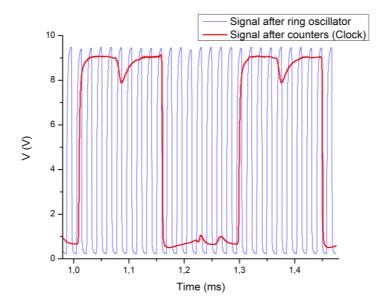

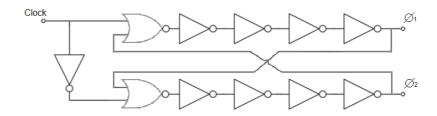

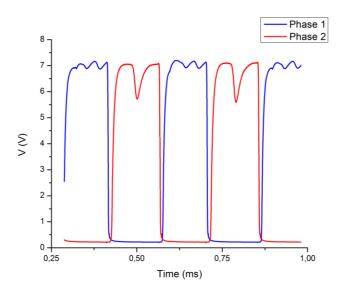

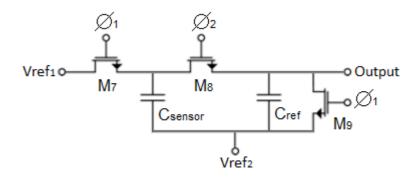

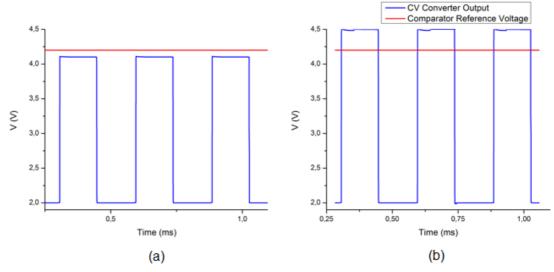

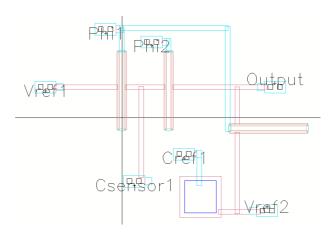

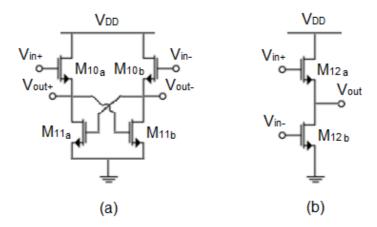

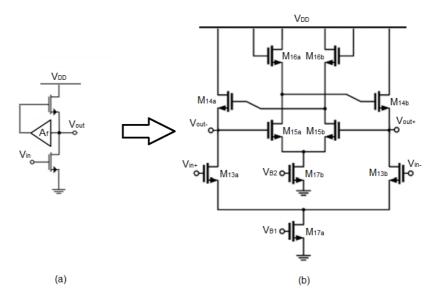

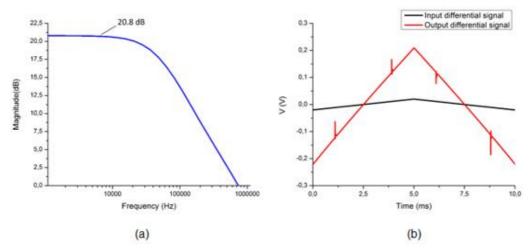

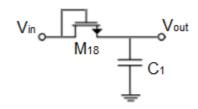

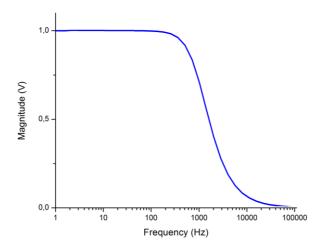

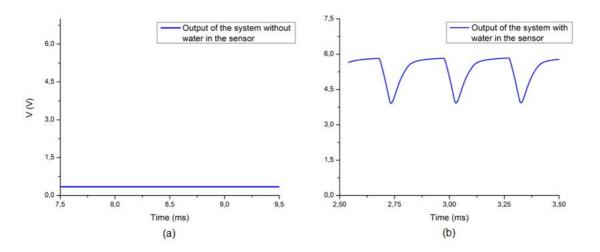

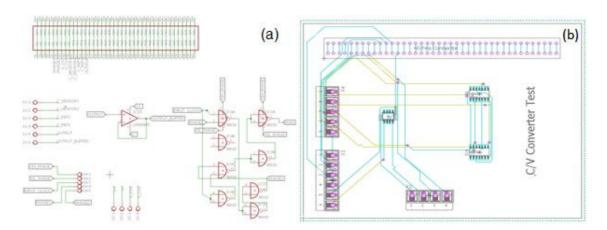

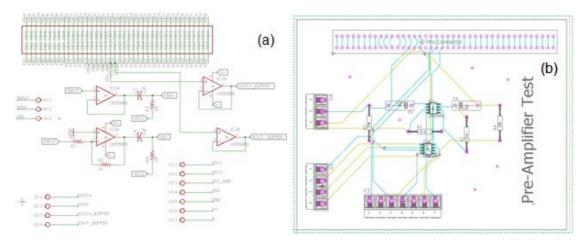

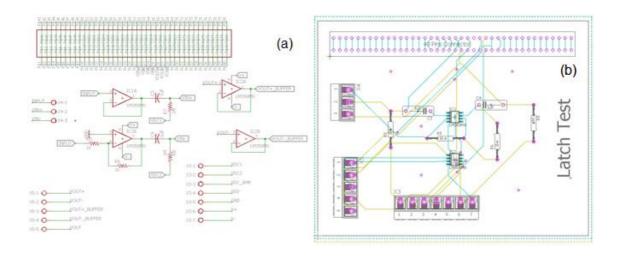

| Figure 4.15- Simulation result of the 4-bit counter, when the signal generated by the ring $\frac{1}{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |