## **Ricardo Filipe Malaia Neves**

Licenciado em Ciências da Engenharia Electrotécnica e de Computadores

# 8-Phase Ring Oscillator for Modern Receivers

Dissertação para obtenção do Grau de Mestre em Engenharia Electrotécnica e de Computadores

Orientador: Luís Augusto Bica Gomes de Oliveira, Prof. Auxiliar, Universidade Nova de Lisboa

Júri:

Presidente:

Arguentes:

Vogais:

Março, 2015

#### 8-Phase Ring Oscillator for Modern Receivers

Copyright © Ricardo Filipe Malaia Neves, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa.

A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objectivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

À minha mãe, que é essa grande mulher, a quem eu devo tudo o que sou.

## Agradecimentos

É devido a uma sensação de enorme gratidão para com certas pessoas que, quer já trouxesse no coração, quer tenha conhecido durante todos estes anos de conquistas, tenho de fazer alguns agradecimentos.

Em primeiro lugar, reconhecer que a FCT-UNL é uma mais-valia como instituição de ensino superior. Instituição essa que me concedeu a extraordinária oportunidade de conhecer e trabalhar com alguns professores verdadeiramente notáveis nas suas respectivas áreas.

Professores como João Goes, que foi o responsável pelo início da minha paixão pela Microelectrónica, passando pelos professores Luís Gomes e Anikó Costa por terem depositado em mim toda a sua compreensão e fé em tempos mais difíceis e, como seria óbvio, pelo meu orientador Prof. Luís Oliveira, pela sua dedicação enquanto professor, e agora poderia ficar a escrever durante horas que nunca conseguiria descrever a real importância que o professor teve, tanto a nível académico como pessoal, na minha vida. Agradeço assim a todos eles por terem tido um papel relevante no meu percurso académico.

Em segundo lugar gostaria de reconhecer a importância de alguns colegas e amigos. Colegas como Ivan Bastos e Edinei Santin que sem os quais este documento não teria o valor que tem. Amigos como o Carlos Carvalho, Manuel Gomes, João Matos, Ali Saad e o meu amigo de infância Tiago Silva, que me ajudaram a crescer e fizeram valer a pena cada "baixo" que encontrei no meu percurso durante estes anos, porque eles mesmos foram os "altos" que anularam os "baixos". O meu muito obrigado por serem quem são.

Ainda assim gostaria de relevar e destacar de uma forma muito clara, dois amigos em particular que, contribuíram decisivamente, para que esta meta final se tornasse uma realidade. São eles o Pedro Dias e o Luís Neto.

Queria também agradecer a toda a minha família incluindo àqueles que já cá não estão por me terem podido colocar o pão na minha mesa durante a minha vida inteira e porque sem eles eu nunca teria passado pelos melhores anos que se pode viver, os anos de faculdade.

Para finalizar os meus agradecimentos, gostaria de reconhecer as três mulheres que mais importância têm na minha vida, elas são a minha mãe Fátima Neves, a minha irmã Ana Neves e a minha namorada Halyna Korol. Estas mulheres são a principal razão pela qual eu me esforço para alcançar os objectivos que me são lançados. A elas o meu muito obrigado por tudo.

# Abstract

The evolution of receiver architectures, built in modern CMOS technologies, allows the design of high efficient receivers. A key block in modern receivers is the oscillator. The main objective of this thesis is to design a very low power and low area 8-Phase Ring Oscillator for biomedical applications (ISM and WMTS bands).

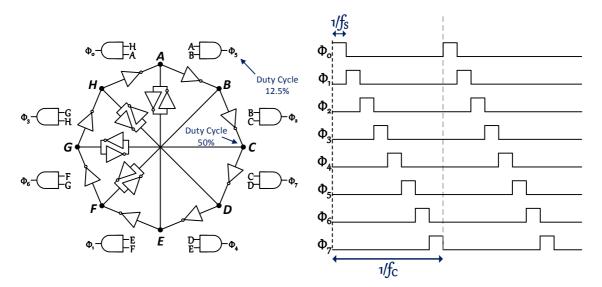

Oscillators with multiphase outputs and variable duty cycles are required. In this thesis we are focused in 12.5% and 50% duty-cycles approaches. The proposed circuit uses eight inverters in a ring structure, in order to generate the output duty cycle of 50%. The duty cycle of 1/8 is achieved through the combination of the longer duty cycle signals in pairs, using, for this purpose, NAND gates. Since the general application are not only the wireless communications context, as well as industrial, scientific and medical plans, the 8-Phase Oscillator is simulated to be wideband between 100 MHz and 1 GHz, and be able to operate in the ISM bands (447 MHz-930 MHz) and WMTS (600 MHz).

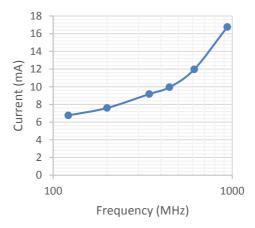

The circuit prototype is designed in UMC 130 nm CMOS technology. The maximum value of current drawn from a DC power source of 1.2 V, at a maximum frequency of 930 MHz achieved, is 17.54 mA. After completion of the oscillator layout studied (occupied area is 165  $\mu$ m x 83  $\mu$ m). Measurement results confirm the expected operating range from the simulations, and therefore, that the oscillator fulfil effectively the goals initially proposed in order to be used as Local Oscillator in RF Modern Receivers.

Keywords: CMOS Inverters, Layout, Ring Oscillator, Multi-Phase Oscillator, Low-IF Receivers

### Resumo

A evolução das arquitecturas de receptores, construídos através de tecnologias modernas CMOS, permite o dimensionamento de receptores altamente eficientes. Um bloco importante nos receptores modernos é o oscilador. O principal objectivo desta dissertação, passa pelo estudo de um Oscilador em Anel de 8 Fases de área e consumo muito reduzidos, para uso em aplicações biomédicas (bandas ISM e WMTS).

São cada vez mais necessários, osciladores capazes de fornecer variadas fases e fabricar diferentes *duty cycles*. Nesta tese o foco encontra-se em aproximações com *duty cycles* de 12.5% e 50%. O circuito apresentado utiliza 8 inversores em formação de anel, de forma a gerar os *duty cycles* de 50%. O *duty cycle* de 1/8 é alcançado através da combinação dos sinais já existentes, dois a dois, nas entradas de uma porta lógica NAND. Tendo em conta que o Oscilador de 8 Fases não é projectado apenas com vista a comunicações sem fios, mas também com vista os planos industriais, científicos e médicos, o Oscilador de 8 Fases é simulado de forma obter uma largura de banda entre os 100 MHz e 1 GHz, e ser capaz de funcionar dentro das bandas ISM (447 MHz-930 MHz) e WMTS (600 MHz).

O circuito protótipo é implementado numa tecnologia UMC 130 nm CMOS. A corrente máxima, fornecida pela fonte de tensão DC de 1,2 V, alcançada a uma frequência de oscilação de 930 MHz, é 17,54 mA. Após a conclusão do *layout* do oscilador em estudo (área ocupada de 165 µm x 83 µm), resultados das medições confirmam a banda de funcionamento prevista pelas simulações e, também, que o oscilador cumpre de forma eficaz todas as metas propostas inicialmente com a finalidade de ser utilizado em Receptores RF Modernos como Oscilador Local.

**Palavras-chave:** "Layout", Inversores CMOS, Oscilador em anel, Oscilador de várias fases, Receptores "Low-IF".

# **Abbreviations**

ADC Analog-To-Digital Converter Complementary Metal-Oxide-Semiconductor CMOS DC **Direct Current** DT **Discrete-Time** HR Harmonic-Rejection IF Intermediate Frequency IIP Intermodulation Intercept Point IIR Infinite Impulse Response ISM Industrial, Scientific and Medical Low Noise Amplifier LNA LO Local Oscillator NF **Noise Figure** NMOS Nchannel Metal-Oxide-Semiconductor PLL Phase Locked Loop Pchannel Metal-Oxide-Semiconductor PMOS RF **Radio Frequency** SC Switched-Capacitor VCO Voltage-Controlled Oscillator WMTS Wireless Medical Telemetry Service LPF Low Pass Filter BPF **Band Pass Filter**

# Contents

| 1 | INT                                                                                                    | rroi                                                                      | DUCTION                                                                                                                                                                                                                               |                      |  |

|---|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

|   | 1.1                                                                                                    | BAG                                                                       | CKGROUND AND MOTIVATION                                                                                                                                                                                                               | 1                    |  |

|   | 1.2                                                                                                    | TH                                                                        | ESIS ORGANIZATION                                                                                                                                                                                                                     | 2                    |  |

|   | 1.3                                                                                                    | MA                                                                        | IN CONTRIBUTIONS                                                                                                                                                                                                                      |                      |  |

| 2 | RE                                                                                                     | RECEIVER ARCHITECTURES AND RF BLOCKS                                      |                                                                                                                                                                                                                                       |                      |  |

|   | 2.1                                                                                                    |                                                                           | CEIVER ARCHITECTURES                                                                                                                                                                                                                  |                      |  |

|   | 2.                                                                                                     | 1.1                                                                       | Heterodyne or IF Receivers                                                                                                                                                                                                            | 6                    |  |

|   | 2.                                                                                                     | 1.2                                                                       | Homodyne or Zero-IF Receivers                                                                                                                                                                                                         | 7                    |  |

|   | 2.                                                                                                     | 1.3                                                                       | Low-IF Receivers                                                                                                                                                                                                                      | 9                    |  |

|   | 2.2 LNA BASIC CONCEPTS                                                                                 |                                                                           |                                                                                                                                                                                                                                       |                      |  |

|   | 2.                                                                                                     | 2.1                                                                       | S-Parameters                                                                                                                                                                                                                          |                      |  |

|   | 2.                                                                                                     | 2.2                                                                       | Stability                                                                                                                                                                                                                             |                      |  |

|   | 2.                                                                                                     | 2.3                                                                       | Noise Figure                                                                                                                                                                                                                          |                      |  |

|   | 2.3                                                                                                    | MIX                                                                       | KERS                                                                                                                                                                                                                                  |                      |  |

|   | 2.                                                                                                     | 3.1                                                                       | Performance Parameters of Mixers                                                                                                                                                                                                      | 15                   |  |

|   | 2.                                                                                                     | 3.2                                                                       | Different Types of Mixers                                                                                                                                                                                                             |                      |  |

| 3 | OS                                                                                                     | CILL                                                                      | ATORS                                                                                                                                                                                                                                 | 21                   |  |

|   | 3.1                                                                                                    | BAI                                                                       | RKHAUSEN CRITERION                                                                                                                                                                                                                    | 21                   |  |

|   | 3.2 Рн/                                                                                                |                                                                           | ASE-NOISE                                                                                                                                                                                                                             | 22                   |  |

|   | 3.2                                                                                                    | Рн                                                                        |                                                                                                                                                                                                                                       |                      |  |

|   | 3.2<br>3.3                                                                                             |                                                                           | ality Factor                                                                                                                                                                                                                          |                      |  |

|   | -                                                                                                      | QU                                                                        | ALITY FACTOR                                                                                                                                                                                                                          | 24                   |  |

|   | 3.3<br>3.4                                                                                             | QU                                                                        |                                                                                                                                                                                                                                       | 24                   |  |

|   | 3.3<br>3.4<br><i>3.</i>                                                                                | QU.<br>Ex4                                                                | AMPLES OF OSCILLATORS                                                                                                                                                                                                                 | 24<br>26<br>26       |  |

|   | 3.3<br>3.4<br><i>3.</i><br><i>3.</i>                                                                   | QU.<br>EXA<br>4.1                                                         | AMPLES OF OSCILLATORS                                                                                                                                                                                                                 | 24<br>26<br>26<br>27 |  |

| 4 | 3.3<br>3.4<br><i>3.</i><br><i>3.</i><br><i>3.</i><br><i>3.</i>                                         | QU.<br>EX4<br>4.1<br>4.2<br>4.3                                           | AMPLES OF OSCILLATORS<br>LC Oscillator<br>Relaxation Oscillators                                                                                                                                                                      |                      |  |

| 4 | 3.3<br>3.4<br><i>3.</i><br><i>3.</i><br><i>3.</i><br><i>3.</i>                                         | Qu.<br>Ex4<br>4.1<br>4.2<br>4.3<br>PHAS                                   | AMPLES OF OSCILLATORS<br>LC Oscillator<br>Relaxation Oscillators<br>Coupled Ring Oscillators                                                                                                                                          |                      |  |

| 4 | 3.3<br>3.4<br><i>3.</i><br><i>3.</i><br><i>3.</i><br><i>3.</i><br><i>3.</i><br><i>3.</i><br><i>8</i> P | QU.<br>EXA<br>4.1<br>4.2<br>4.3<br>PHAS<br>INT                            | AMPLES OF OSCILLATORS<br>LC Oscillator<br>Relaxation Oscillators<br>Coupled Ring Oscillators<br>ES OSCILLATOR                                                                                                                         |                      |  |

| 4 | 3.3<br>3.4<br><i>3.</i><br><i>3.</i><br><i>3.</i><br><i>3.</i><br><b>8 P</b><br>4.1                    | QU.<br>EXA<br>4.1<br>4.2<br>4.3<br>PHAS<br>INT<br>DO                      | AMPLES OF OSCILLATORS<br>LC Oscillator<br>Relaxation Oscillators<br>Coupled Ring Oscillators<br>ES OSCILLATOR<br>RODUCTION                                                                                                            |                      |  |

| 4 | 3.3<br>3.4<br><i>3.</i><br>3.<br><i>3.</i><br><i>3.</i><br><i>4.1</i><br>4.2<br>4.3                    | QU.<br>EXA<br>4.1<br>4.2<br>4.3<br>PHAS<br>INT<br>DO                      | AMPLES OF OSCILLATORS<br>LC Oscillator<br>Relaxation Oscillators<br>Coupled Ring Oscillators<br>ES OSCILLATOR<br>RODUCTION<br>WNCONVERTER ARCHITECTURE                                                                                |                      |  |

| 4 | 3.3<br>3.4<br>3.<br>3.<br>3.<br>3.<br><b>8 P</b><br>4.1<br>4.2<br>4.3<br>4.3                           | QU.<br>EX4<br>4.1<br>4.2<br>4.3<br>PHAS<br>INT<br>DO<br>CIR               | AMPLES OF OSCILLATORS<br>LC Oscillator<br>Relaxation Oscillators<br>Coupled Ring Oscillators<br>ES OSCILLATOR<br>RODUCTION<br>WNCONVERTER ARCHITECTURE<br>CUIT BLOCKS: SAMPLING CELL AND LOCAL OSCILLATOR                             |                      |  |

| 4 | 3.3<br>3.4<br>3.<br>3.<br>3.<br>3.<br><b>8 P</b><br>4.1<br>4.2<br>4.3<br>4.3                           | Qu.<br>Ex4<br>4.1<br>4.2<br>4.3<br>PHAS<br>INT<br>DO<br>CIR<br>3.1<br>3.2 | AMPLES OF OSCILLATORS<br>LC Oscillator<br>Relaxation Oscillators<br>Coupled Ring Oscillators<br>ES OSCILLATOR<br>RODUCTION<br>WNCONVERTER ARCHITECTURE<br>CUIT BLOCKS: SAMPLING CELL AND LOCAL OSCILLATOR<br>Sampling/IIR filter cell |                      |  |

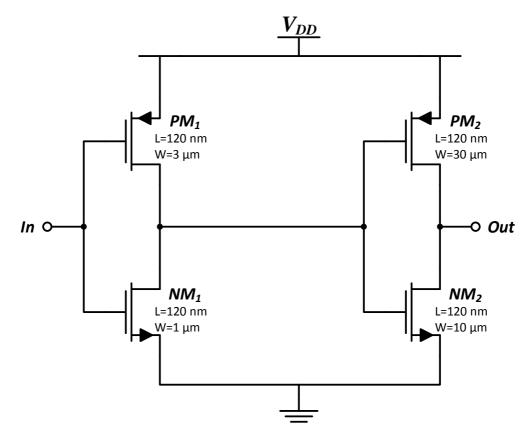

|   | 4.5             | 5.1  | Inverters                             |    |

|---|-----------------|------|---------------------------------------|----|

|   | 4.5             | 5.2  | Buffer                                |    |

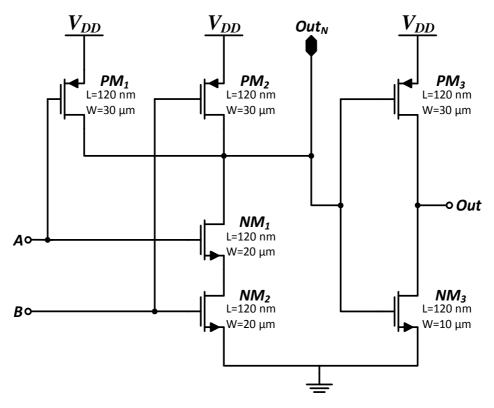

|   | 4.5             | 5.3  | AND                                   |    |

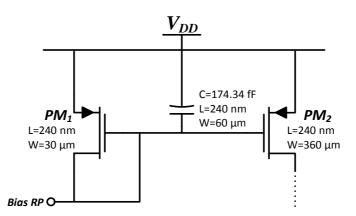

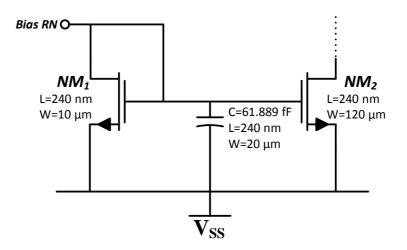

|   | 4.5             | 5.4  | Current Mirrors                       |    |

| 5 | SIM             | ULA  | ATION AND MEASUREMENT RESULTS         | 47 |

|   | 5.1             | Sch  | iematic Simulations                   | 47 |

|   | 5.1             | .1   | 12.5 % Duty Cycle                     |    |

|   | 5.1             | .2   | 50 % Duty Cycle                       |    |

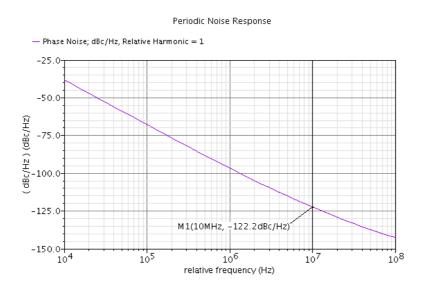

|   | 5.1             | .3   | Phase Noise                           |    |

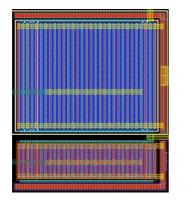

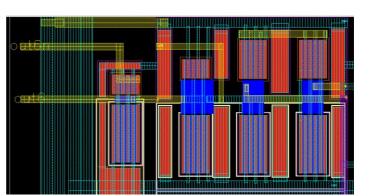

|   | 5.2             | LAY  | /OUT                                  |    |

|   | 5.3             | Pos  | ST-LAYOUT SIMULATIONS                 |    |

|   | 5.3             | 8.1  | 12.5 % Duty Cycle                     |    |

|   | 5.3.2           |      | 50 % Duty Cycle                       |    |

|   | 5.3             | 3.3  | Phase Noise                           |    |

|   | 5.3             |      | Schematic vs. Post-Layout Simulations |    |

|   | 5.4             | Me   | ASUREMENT RESULTS                     | 62 |

| 6 | CON             | ICLU | USIONS AND FUTURE WORK                | 65 |

|   | 6.1 CONCLUSIONS |      |                                       |    |

|   | 6.2 FUTURE WORK |      | 66                                    |    |

| 7 | REF             | ERE  | ENCES                                 |    |

# **List of Figures**

| FIGURE 2-1 – BASIC HETERODYNE ARCHITECTURE [1]                                                  | 6  |

|-------------------------------------------------------------------------------------------------|----|

| FIGURE 2-2 – IMAGE REJECTION FUNDAMENTALS [13].                                                 | 7  |

| FIGURE 2-3 – BASIC HOMODYNE ARCHITECTURE [1].                                                   | 8  |

| FIGURE 2-4 – HARTLEY ARCHITECTURE [1].                                                          | 10 |

| FIGURE 2-5 – WEAVER ARCHITECTURE [1].                                                           | 10 |

| FIGURE 2-6 – S-PARAMETERS [16].                                                                 | 12 |

| Figure 2-7 – Noise Network [16].                                                                | 13 |

| Figure 2-8 – Noise Network [2].                                                                 | 14 |

| FIGURE 2-9 – MIXING OPERATION.                                                                  | 15 |

| FIGURE 2-10 – DOWN-CONVERSION RESULTING SPECTRUM.                                               | 15 |

| FIGURE 2-11 – 3 <sup>RD</sup> Order Intercept Point (IIP3).                                     | 17 |

| FIGURE 2-12 – PASSIVE MIXER USING ACTIVE DEVICE [2].                                            | 18 |

| FIGURE 2-13 – SINGLE BALANCED MIXER [1]                                                         | 19 |

| FIGURE 2-14 – GILBERT CELL.                                                                     | 20 |

| FIGURE 3-1 – SIMPLE FEEDBACK SYSTEM [1].                                                        | 22 |

| FIGURE 3-2 – IDEAL CARRIER AND CARRIER WITH PHASE-NOISE (ADOPTED FROM [17]).                    | 23 |

| FIGURE 3-3 – PHASE-NOISE EFFECT IN DOWN-CONVERSION (ADOPTED FROM [17]).                         | 23 |

| FIGURE 3-4 – PHASE-NOISE SINGLE SIDE BAND (ADOPTED FROM [17]).                                  | 24 |

| FIGURE 3-5 – CARRIER SPECTRUM REGARDING VARIATIONS IN THE QUALITY FACTOR.                       | 24 |

| FIGURE 3-6 – LC OSCILLATOR [1].                                                                 | 26 |

| FIGURE 3-7 – LC OSCILLATOR LINEAR MODEL.                                                        | 27 |

| FIGURE 3-8 – RELAXATION OSCILLATOR [1].                                                         | 28 |

| FIGURE 3-9 – 3-STAGE SINGLE-ENDED RING OSCILLATOR.                                              | 28 |

| FIGURE 3-10 – TWO SETS OF 3-STAGE RING OSCILLATORS COUPLED TOGETHER [20]                        | 29 |

| FIGURE 3-11 – QUADRATURE FOUR-STAGE RING OSCILLATOR [34].                                       | 30 |

| FIGURE 3-12 – TWO DIMENSIONAL ARRAY OSCILLATOR [20].                                            | 31 |

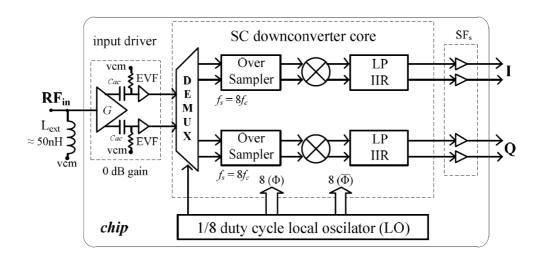

| FIGURE 4-1 – BLOCK DIAGRAM OF THE IMPLEMENTED DT MIXING CIRCUIT COMPRISING THE INPUT DRIVER, SC |    |

| DOWNCONVERTER CORE AND THE LO (ADOPTED FROM [11])                                               | 34 |

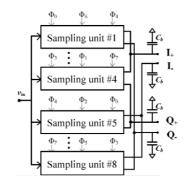

| FIGURE 4-2 – SC CORE OF THE DOWNCONVERTER (ADOPTED FROM [11])                                   | 35 |

| FIGURE 4-3 – A) SCHEMATIC OF A SU; B) MOS CAPS WITH EMBEDDED PA (ADOPTED FROM [11])             | 35 |

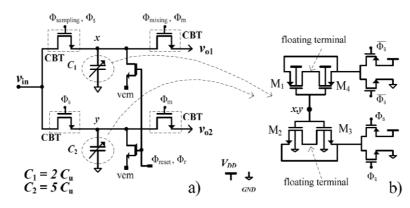

| FIGURE 4-4 – (A) LOCAL OSCILLATOR; (B) 8-PHASE 12.5 %-DUTY-CYCLE WAVE FORMS.                    | 36 |

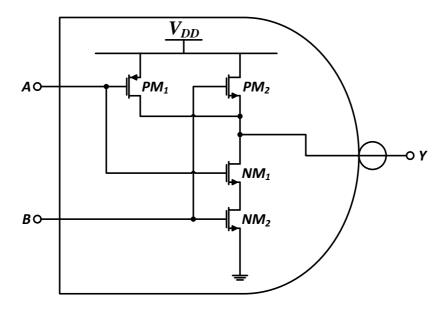

| FIGURE 4-5 – NAND GATE SCHEMATIC.                                                               | 37 |

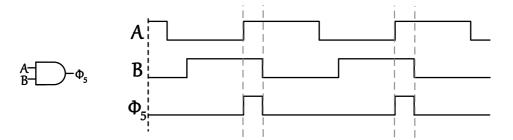

| FIGURE 4-6 – TRANSFORMATION OF 12,5% TO 50% DUTY CYCLE WAVE.                                    |    |

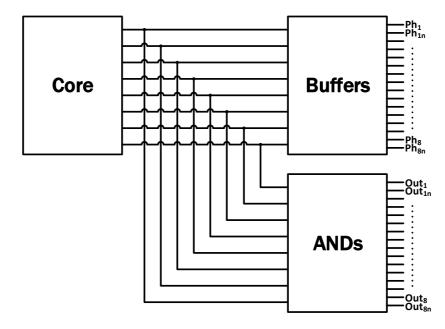

| FIGURE 4-7 – OSCILLATOR CORE PLUS AND AND BUFFER BLOCKS IN A BLOCK DIAGRAM.                     |    |

| FIGURE 4-8 – INVERTER BLOCK SCHEMATIC                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------|

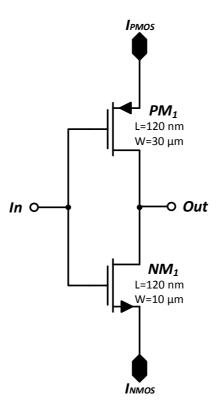

| FIGURE 4-9 – BUFFER BLOCK SCHEMATIC                                                                                     |

| FIGURE 4-10 –AND BLOCK SCHEMATIC                                                                                        |

| FIGURE 4-11 – PMOS CURRENT MIRROR BLOCK SCHEMATIC                                                                       |

| FIGURE 4-12 – NMOS CURRENT MIRROR BLOCK SCHEMATIC                                                                       |

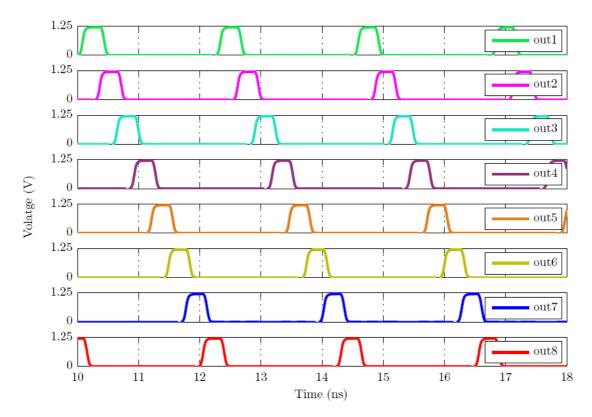

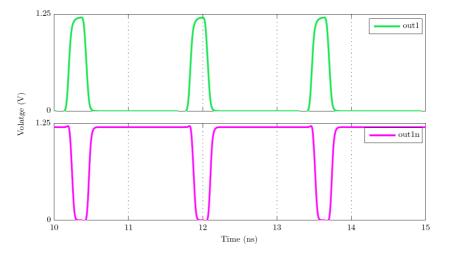

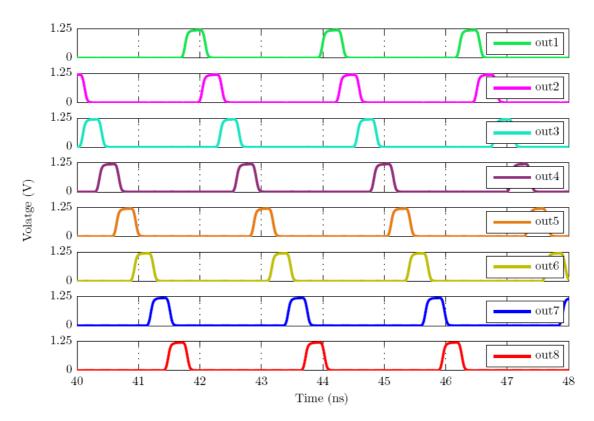

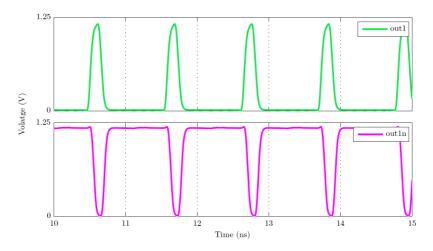

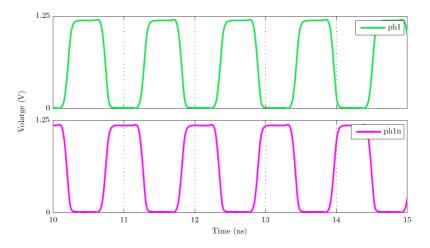

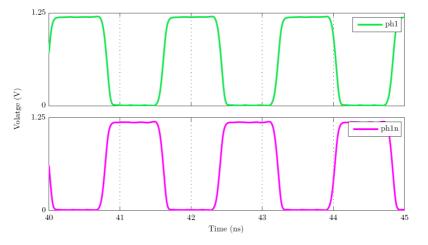

| FIGURE 5-1 – SCHEMATIC SEQUENTIAL SIGNALS WITH DUTY CYCLE OF 12.5 %.                                                    |

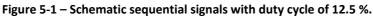

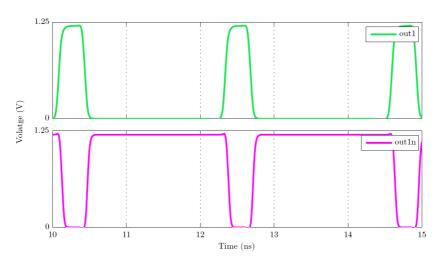

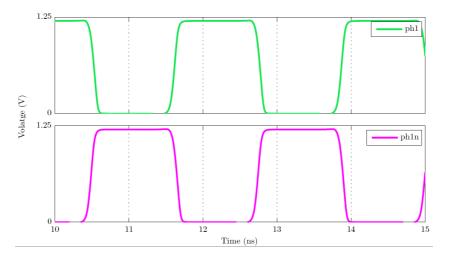

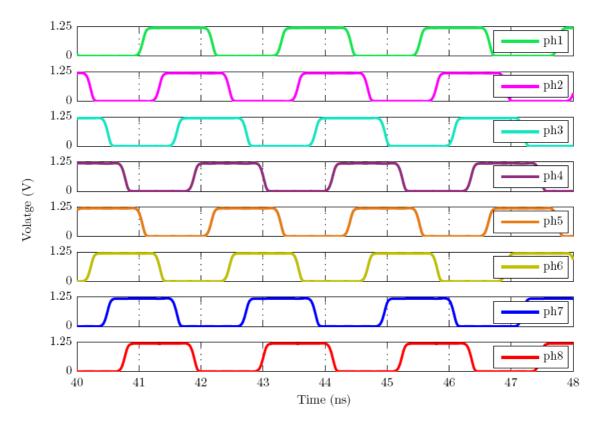

| FIGURE 5-2 – SCHEMATIC SEQUENTIAL SIGNALS WITH DUTY CYCLE OF 50 %.                                                      |

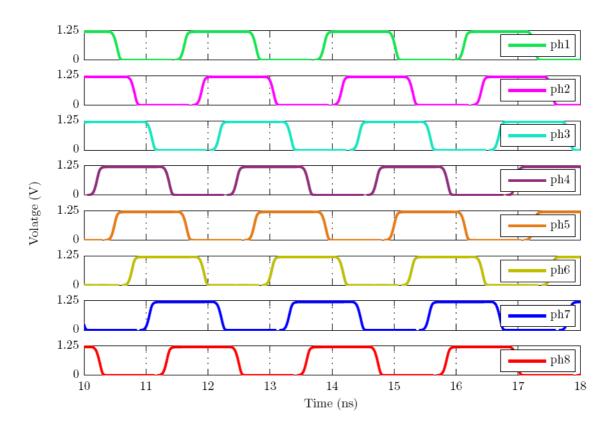

| FIGURE 5-3 – SCHEMATIC SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 12.5 % AT 900 MHz, IN-PHASE AND IN PHASE           |

| INVERSION                                                                                                               |

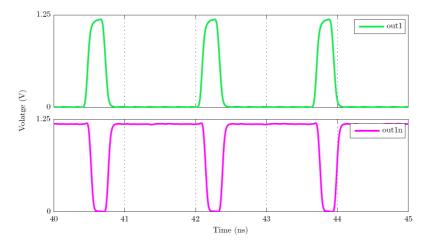

| FIGURE 5-4 – SCHEMATIC SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 12.5 % AT 600 MHz, IN-PHASE AND IN PHASE           |

| INVERSION                                                                                                               |

| FIGURE 5-5 – SCHEMATIC SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 12.5 % AT 400 MHz, IN-PHASE AND IN PHASE INVERSION |

| FIGURE 5-6 – SCHEMATIC SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 50 % AT 900 MHz, IN-PHASE AND IN PHASE             |

| INVERSION                                                                                                               |

| FIGURE 5-7 – SCHEMATIC SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 50 % AT 600 MHz, IN-PHASE AND IN PHASE             |

| INVERSION                                                                                                               |

| FIGURE 5-8 – SCHEMATIC SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 50 % AT 400 MHz, IN-PHASE AND IN PHASE             |

| INVERSION                                                                                                               |

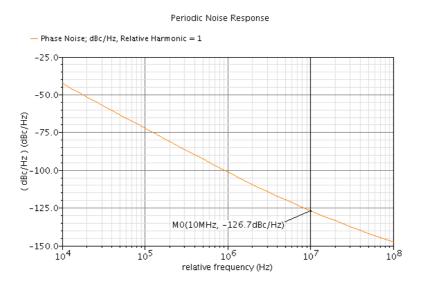

| FIGURA 5-9 PHASE NOISE OF THE OSCILLATOR AT 900MHz OSCILLATING FREQUENCY                                                |

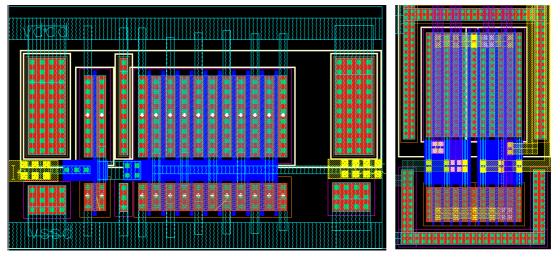

| FIGURE 5-10 – CURRENT MIRROR LAYOUT                                                                                     |

| Figure 5-11 – NAND Layout                                                                                               |

| FIGURE 5-12 – BUFFERS LAYOUT                                                                                            |

| FIGURE 5-13 – INVERTERS LAYOUT                                                                                          |

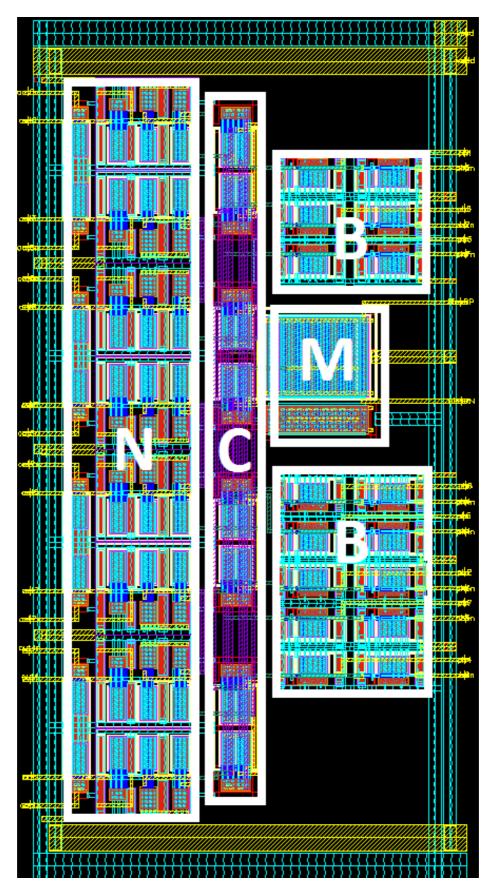

| Figure 5-14 – Layout of the 8-Phases Ring Oscillator (165 x 83 $\mu$ M <sup>2</sup> )55                                 |

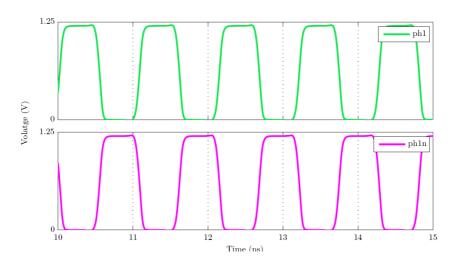

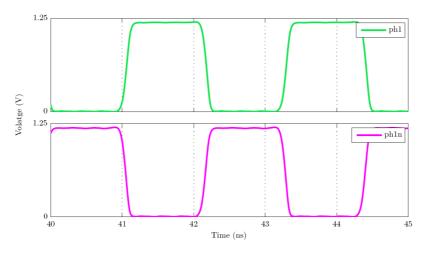

| FIGURE 5-15 – CALIBRE SEQUENTIAL SIGNALS WITH DUTY CYCLE OF 12.5 %.                                                     |

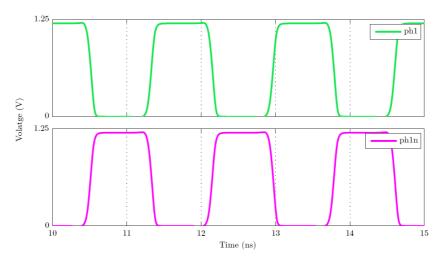

| FIGURE 5-16 – CALIBRE SEQUENTIAL SIGNALS WITH DUTY CYCLE OF 50 %.                                                       |

| FIGURE 5-17 – CALIBRE SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 12.5 % AT 900 MHz, IN-PHASE AND IN PHASE            |

| INVERSION                                                                                                               |

| FIGURE 5-18 – CALIBRE SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 12.5 % AT 600 MHz, IN-PHASE AND IN PHASE            |

| INVERSION                                                                                                               |

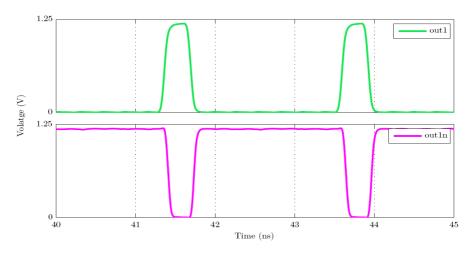

| FIGURE 5-19 – CALIBRE SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 12.5 % AT 400 MHz, IN-PHASE AND IN PHASE            |

| INVERSION                                                                                                               |

| FIGURE 5-20 – CALIBRE SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 50 % AT 900 MHz, IN-PHASE AND IN PHASE              |

| INVERSION                                                                                                               |

| FIGURE 5-21 – CALIBRE SIMULATIONS OF THE SIGNALS WITH DUTY CYCLE OF 50 % AT 600 MHz, IN-PHASE AND IN PHASE              |

| INVERSION                                                                                                               |

| Figure 5-22 – Calibre simulations of the signals with duty cycle of 50 % at 400 MHz, in-phase and in phase              |

| INVERSION                                                                                                               |

| FIGURE 5-23 - PHASE NOISE OF THE OSCILLATOR AT 900MHZ OSCILLATING FREQUENCY.                                            |

| FIGURE 5-24 – CORE CURRENT VERSUS OSCILLATION FREQUENCY FOR SCHEMATIC SIMULATIONS (SCHEMATIC ON THE LEFT,               |

| POST LAYOUT ON THE RIGHT)61                                                                                             |

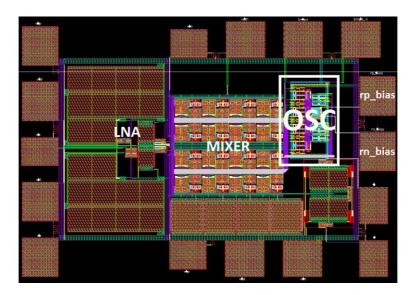

| Figure 5-25 – Layout of the front-end with the LNA with active loads (800 x 550 $\mu m^2).$               | 62 |

|-----------------------------------------------------------------------------------------------------------|----|

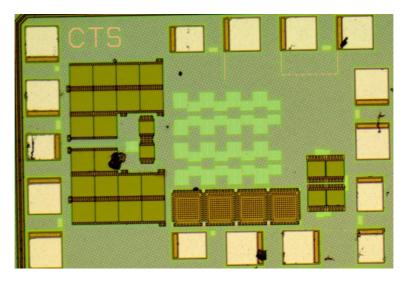

| Figure 5-26 – Die photo of the front-end with the LNA with active loads (800 x 550 $\mu$ m <sup>2</sup> ) | 63 |

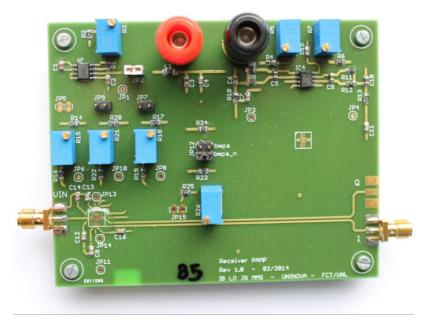

| FIGURE 5-27 – PROTOTYPE BOARD (ADOPTED FROM [12])                                                         | 63 |

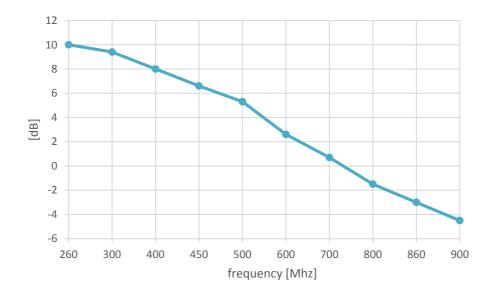

| FIGURE 5-28 – FRONT-END GAIN                                                                              | 64 |

# List of Tables

| TABLE 4.1 – TRUTH TABLE OF A NAND GATE                                   | 38 |

|--------------------------------------------------------------------------|----|

| TABLE 5.1 – SUMMARY OF SIGNAL CHARACTERISTICS FOR SCHEMATIC SIMULATIONS. | 51 |

| TABLE 5.2 – SUMMARY OF SIGNAL CHARACTERISTICS FOR CALIBRE SIMULATIONS.   | 60 |

# 1

# **1** Introduction

#### 1.1 Background and Motivation

Modern transceivers for wireless communications require circuits with low power consumption, size, cost, noise, while increasing the frequency and bandwidth. The successful travel of wireless communications led to new and more challenging requirements such as: low supply voltage, low cost, and low area circuits. The use of modern CMOS nanotechnologies allows, by adjusting old architectures or by employing new circuit designs, to find a way to reach these objectives [1].

The circuit between the antenna and the digital part, is generally defined as the RF frontend. Due to very tough specifications for RF blocks, the receiver front-end has a very important role in communications. Receiver architectures can be divided into: heterodyne and homodyne. The first converts the signal to an intermediate frequency (IF), while the second downconverts directly to the baseband. Combining the main advantages of both architectures, the Low-IF receiver is a modified version of the homodyne and is becoming a good alternative [1, 2].

Due to development of wireless receiver architectures, image-rejection topologies require accurate quadrature voltage-controlled oscillator (VCO). The way to keep an oscillator outputs stable in frequency and phase, is to connect two oscillators in a feedback structure, in order to be able to generate signals with a precise 90° phase shift. There's many ways to obtain accurate quadrature outputs. Due to this, new architectures have emerged using RC and LC oscillators, some of them have inherent quadrature outputs, for example the two integrator oscillator [1].

On the other hand, oscillators with wide operating range, they can provide different carrier frequencies and data rates for wireless transmissions in the existing variety of communication standards. A polyphase filter can produce quadrature signals using differential outputs of a VCO [3], [4]. Another technique to get quadrature output is to design a VCO, which works at double the desired frequency, followed by frequency division [5]. Coupled VCOs structure [6] and [7], coupled resonators in a ring structure [8], and multiphase ring oscillators [9] are other alternatives to produce quadrature outputs [10]. The architecture proposed in this thesis uses a combination of cross-coupled inverters and ring oscillators concept, for generating multiphase outputs.

#### 1.2 Thesis Organization

This thesis is presented into six chapters, including the present introduction. Since each chapter begins with a small introduction presenting that specific topics, here it is just a brief and general reference to each chapter.

**Chapter 2 - Receiver Architectures and RF Blocks:** this chapter is the literature review of the dissertation, introducing and describing the main architectures related to both receivers and the RF blocks.

**Chapter 3 - Oscillators:** is hereby continued the previous chapter, but with a more detailed view only on the RF block in which this thesis focuses properly. It is also included, in the final part, the chosen architecture for the oscillator design.

**Chapter 4 - 8 Phases Oscillator:** is dedicated to the context of the proposed circuit, that is, will be presented the actual topology where the oscillator in study came from. Following that first half, a more detailed study of the proposed topology and sizing of the projected oscillator and its most intimate blocks will also be presented.

**Chapter 5** - **Simulation and** Measurement Results: it is a chapter that, in addition to combine all types of simulations, either pre or post-layout, also includes presenting the designed layout. It is possible to finish all this experimental stage realizing, in a clear way, with the measurements carried out on the test board, that the oscillator behaved according to its initial premises.

**Chapter 6 - Conclusions and Future Work:** here are woven final considerations about the work, in kind of a summary of the main conclusions to be drawn. It also made the transposition into prospects and future work in order to improve the originated contribution.

#### **1.3** Main Contributions

The contributions of this thesis consist essentially in the redesign and layout of an architecture of 8-phases oscillator previously proposed [11]. The redesign allowed to evaluate the architecture made previously, which contributed to the confirmation by measurements of operating at 1 GHz with precise 8 phases with 12.5% and 50% duty cycle (The results have resulted in one submitted paper [12]).

2

## 2 Receiver Architectures and RF Blocks

The receivers are used in demodulating a signal sent by a transmitter, first the signal received by the antenna is amplified using an LNA, and then, downconverted to a lower frequency. In the end, it is possible to obtain at the outputs a demodulated signal. The receivers can be divided into two basic architectures: heterodyne or homodyne [13]. In the heterodyne one, signal is downconverted to an intermediate frequency (IF), in homodyne, a conversion is made directly to baseband. Today's favourite architecture is the homodyne for its simplicity, low power consumption and low cost [14]. In recent years new architectures have appeared that take clear advantage of the qualities of each of the aforementioned architectures. Low-IF receiver is precisely one that is being used in FM receivers [2].

The signal received by the antenna is processed by several receiver blocks, each with a specific function. One of the major blocks is LNA, since the intention involves amplifying the received signal in order to minimize noise. Another crucial block is the oscillator, this block generates a frequency, which combined with the mixer will change the signal frequency.

Modern receivers require quadrature outputs, because of this, the oscillator should be capable of generating more than one waveform. Thus, and for obvious reasons, will be dedicated one chapter just for literature review of the oscillators [13].

#### 2.1 Receiver Architectures

There are 3 very popular receivers architectures, they are: heterodyne, homodyne and Low-IF [2,14]. The first one is widely used and is characterized for taking the RF signal to an

Intermediate Frequency (IF) in a first stage and, just at a second plane, is that the signal is brought to baseband. The second type of receptor announced is also known as direct IF or zero-IF up, which results in a direct translation to RF baseband. The low-IF receiver architecture is similar to the heterodyne where the RF signal is brought to a low-IF frequency, and only brought to the baseband after being converted into the digital domain.

#### 2.1.1 Heterodyne or IF Receivers

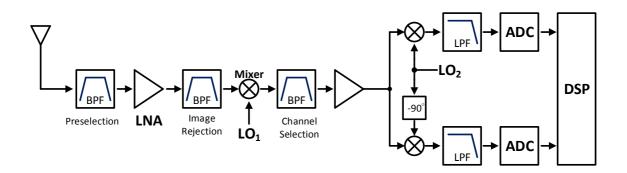

The block diagram of a heterodyne receiver is shown in Figure 2.1. Before being amplified by the LNA, the input signal undergoes the action of a bandpass filter to select the frequencies of interest. To mitigate the signs on the image frequency band outside the LNA, is used an image rejection filter. The mixer together with the oscillator, bring the signal to the IF, and thus, the signal again passes through a band pass filter to isolate the bandwidth of the IF and finally be amplified by an IF amplifier. For the mixer to bring the signal to baseband, and make downconversion, both in-phase (I) and quadrature (Q) components are necessary. Then, to be converted to digital domain, the signal passes through a low-pass filter.

In order to be possible to obtain a high quality factor (Q), used filters should be implemented off-chip, this is one of the reasons why this architecture is avoided in modern technology. The need for a high performance oscillator and the image frequency, are two main disadvantages of this architecture [13].

Figure 2-1 – Basic Heterodyne Architecture [1].

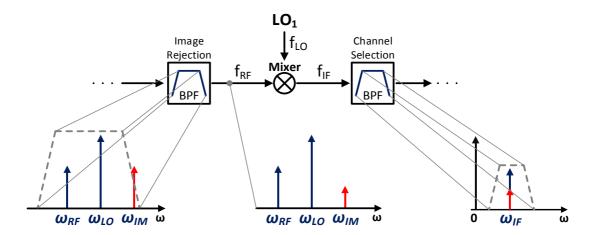

The mixer causes the problem of frequency image, moving both the sum and the difference frequencies, converting them for the same IF. If the downconvertion of a signal with a frequency  $\omega_{RF}$  has to be done to a frequency  $\omega_{IF}$ , but the frequency image in  $\omega_{IM}$  (as shown in Figure 2.2) is also downconverted. Even after the image rejection filter there is a small signal

at that frequency. When the signal is pushed into the mixer, both frequencies are downconverted to  $\omega_{IF}$ . A practical example to follow is assuming that:  $\omega_{IF}$  is 50 MHz,  $\omega_{RF}$  is 850 MHz,  $\omega_{LO}$  900 MHz and  $\omega_{IM}$  is a signal at the 950 MHz that will also be "downconverted" by the mixer to  $\omega_{IF}$ .

There is a trade-off about this architecture, related to the IF frequency. Some receiver blocks are influenced by the frequency chosen. With a higher frequency, it becomes easier to design an image rejection filter, because the image is far from the desired frequency. But the band-pass filter next to the mixer will necessarily be less demanding, making it easier to implement for a lower value of IF, the same applies to the IF amplifier.

Figure 2-2 – Image Rejection fundamentals [13].

#### 2.1.2 Homodyne or Zero-IF Receivers

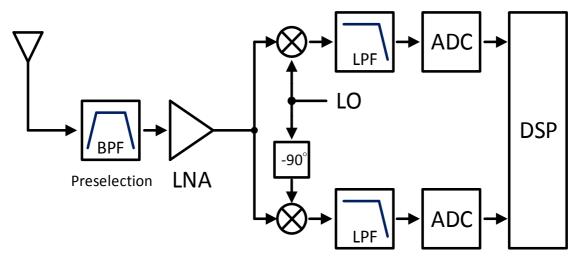

Zero-IF receivers are known for carrying the signal directly from RF to baseband. The lack of a first mixer, before downconvertion itself, is the most obvious difference between homodyne and heterodyne, which is why filters are implemented only for the signal before LNA and after the downconvertion.

In heterodyne, as already had the opportunity to check, the first mixer causes an overlap between two signals in IF, in this case, since the IF is zero, the desired frequency is the same as the image one, so there is no need for an image rejection filter. Another advantage lies in the amplification, as it is done in the baseband, the power consumption is reduced. Additionally, there is no need to use a bandpass filter, instead, only a low pass filter is used, after the downconvertion. Whereas there is no image rejection filter, the LNA does not need to be matched to 50 ohms at the output. This architecture has fewer blocks, as shown in Figure 2.3, therefore, has lower power consumption than the heterodyne receiver [1, 2, 14].

Figure 2-3 – Basic Homodyne Architecture [1].

When compared to heterodyne, this architecture have some disadvantages, but is still under research for more picky applications [1]. These disadvantages are:

- Named local oscillator leakage, this means that, between the local oscillator and the input port of the mixer and LNA, can be some kind of imperfect isolation. This leakage mixed with the original wave from the oscillator, create DC offsets in the mixer output. Antenna can also be the target of this leakage, which interferes with other receivers at the same frequency;

- DC offsets, because of the previous leakage from the oscillator, a voltage offset at mixer output appears and causes the saturation of the successive blocks.

- Flicker noise due to the spectrum close to DC from active devices, may corrupt the base band signals;

- Quadrature mismatch and error, the most critical aspect of direct-conversion receivers, where the main goal is to have equal I and Q branches with a phase difference of 90°, to create the ideal baseband signals. The mismatch between the branches contaminate the signal;

- Even order distortion (in intermodulation), creates a DC offset so the receiver shall have a high IIP2 (second-order intermodulation intercept point).

Once again, the low cost, low area, and low power consumption of this receiver, are the main reasons for this architecture to be used. Even though the performance is better than the

homodyne, the heterodyne needs external high quality components. The next architecture combines both receivers' advantages into one.

#### 2.1.3 Low-IF Receivers

Similar structure to the one of the homodyne type, but instead of downconverting to the baseband it converts to an IF close to the baseband. The signal path comprise, in first place, a band pass filter, then it is amplified and mixed in quadrature to a low IF. Finally, and before suffering the action of the ADC, the signal is amplified and filtered once again. To avoid the DC offset problems caused by LO leakage in the homodyne, but introducing the image frequency disadvantage of the heterodyne, IF must be once or twice the bandwidth of the desired signal.

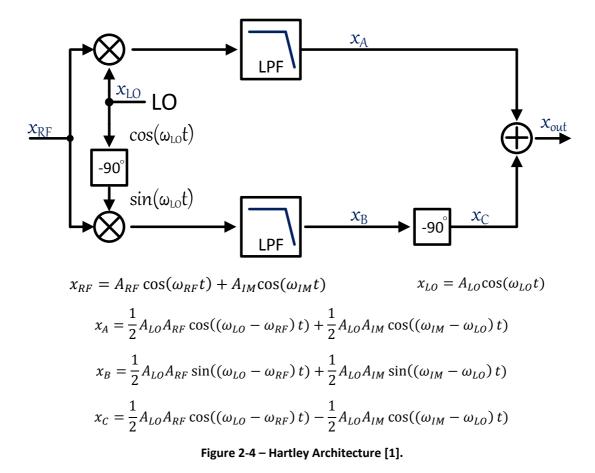

In opposite to the heterodyne, by the fact that it would require a filter with an extreme quality factor (Q) for the low IF, will be dropped the hypothesis of using an image rejection filter. Hartley and Weaver architectures have been proposed, as image reject techniques. These techniques only make sense implemented after the low pass filter, combining both outputs into a single one (variations of these architectures were also made for quadrature outputs).

The image rejection ratio (IIR) is the way to quantify the degree of image rejection in a receiver, which is given by (2.1).  $P_{IM}$  and  $P_s$  are the average power of the image and the signal respectively at the output,  $V_{IM}$  and  $V_s$  their amplitude at the input. The best of the cases would be where the image signal level is zero, making IRR =  $\infty$ .

$$IRR = \frac{\frac{P_{IM}}{P_S}}{\frac{V_{IM}^2}{V_S^2}}$$

(2.1)

We assume that the oscillator produces a phase difference of 90° with no mismatches. In Figure 2.4 is shown the Hartley solution that shifts the signal from Q branch another 90° and then both are summed. This solution works as follows, since there was already a shift of 90°, the image signal will be in opposition of the I channel, when adding both (Figure 2.4 shows in detail), the signal at  $\omega_{RF}$  is maintained and both images are cancelled mutually.

A shift of -45° on in-phase signal and 45° to the quadrature one, instead of using simply a single 90° shift, is a variation of this architecture, but the principle is the same [13].

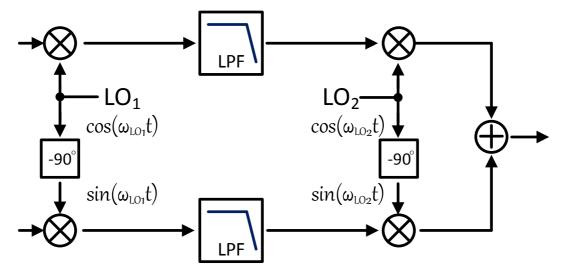

The simplified Weaver architecture does exactly the same as the Hartley architecture. Replicating the previous quadrature mixing stage after that, as shown in Figure 2.5, the same image cancelling effect is obtained. It is possible to use for quadrature outputs, if some changes to this architecture would be drawn. Anyways the Hartley architecture is more suitable for a single output, because a second mixing stage could produce more phase deviations.

Figure 2-5 – Weaver Architecture [1].

The remaining circuit is affected by a mismatch in phase and amplitude. The phase error is quite difficult to correct, but in the other hand, the amplitude imprecision is not so influential because, after the band pass filter, the signal is amplified. What can also take influence in both image and signal of interest average power, is the phase error. Assuming that actually there is a quadrature mismatch in the oscillator, (2.1) can lead us to (2.2), where ( $\theta$ ) represents the phase error. Then, it is possible to conclude that the main variable to image suppression success is the accuracy of the oscillator [13].

$$IRR = \frac{\theta^2}{4} \tag{2.2}$$

#### 2.2 LNA Basic Concepts

A crucial structure block for receivers of a wireless circuit, is the LNA, Low Noise Amplifier. The signals in the antennas are expected to be very weak, so there's a necessity to amplify them in order to be properly handled. However, this amplification must be done carefully, taking into account the reduction of the noise but amplifying to the maximum the wanted signal. In that regard the signal progresses in the best conditions to the rest of the circuit [15].

#### 2.2.1 S-Parameters

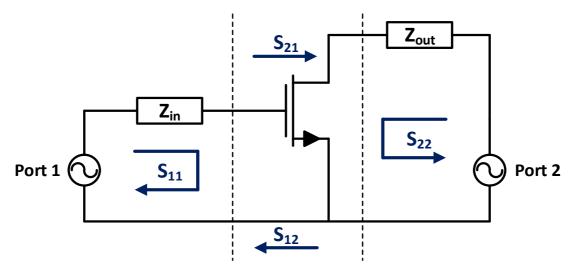

It is important to study some parameters defined by S11, S12, S21 and S22, to correctly analyse the performance of a LNA. S11 is the input port voltage reflection coefficient, S12 and S21 represent the reverse and forward voltage gain, respectively, and S22 the output port voltage reflection coefficient. An example on how these parameters are represented in a circuit of a LNA is shown in Figure 2.6 [2]. Usually when a LNA is developed, it is possible to assume if some simulated values corresponds to a decent circuit or not [2]. In other words, parameters S11 and S22 are important in this study and their values represent the input and output matching of the LNA. S12 is the reverse gain and it is a kind of response in relation to S21, therefore it is required to this parameter to be very small to grant good isolation. Finally, S21 is related to the capacity of a LNA to amplify the signal in good conditions, so the bigger this parameter is, the better is the performance of the LNA [16].

Figure 2-6 – S-Parameters [16].

In conclusion, the importance that the output, i.e., the parameters S21 and S22 have is reduced when talking about a complete global receiver architecture, makes sense only refer to the circuit input, which is the most critical. This will only occur upon the detailed and isolated LNA study from all other blocks.

First of all, before taking into account the LNA development itself, are the stability requirements. As it is possible to verify in the equations (2.3) and (2.4) [2], this factor takes advantage of the S-Parameters to calculate and verify the circuit stability.

$$\Delta = S_{11} * S_{22} - S_{12} * S_{21} \tag{2.3}$$

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2 * |S_{12} * S_{21}|^2}$$

(2.4)

#### 2.2.2 Stability

The premises that, when K > 1 and  $|\Delta| < 1$  lead to a conclusion of actual stability, are usually directed for bipolar transistors, but can also be noted for CMOS transistors. Important to say that S-parameters give the power gain, and it is possible to confirm with (2.5) and (2.6).

$$Power \ Gain = 10 * \log_{10} \left(\frac{P_{out}}{P_{in}}\right)$$

(2.5)

$$Voltage \ Gain = 20 * \log_{10} \left( \frac{V_{out}}{V_{in}} \right)$$

(2.6)

#### 2.2.3 Noise Figure

The other great and crucial parameter to rate the quality of a LNA is the Noise Factor. The lower the F, the lower will be the final F of the complete receiver, so it is extremely important to optimize it. Because of this value can depend on what application is measured, and also it has a close trade-off with the maximum gain reachable, usually, it is tough to define the best value for a circuit.

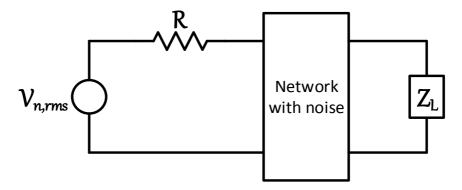

Figure 2-7 – Noise Network [16].

In general, and about this kind of noise, is common sense that it is related with thermal noise. Thus, the noise factor is defined as the ratio of the output noise power, of the LNA, to the portion thereof attributable to thermal noise in the input, at standard noise temperature  $T_0$ = 17°C (290 K), this ratio can be expressed by (2.7) [2].

$$F = \frac{P_{No}}{P_{Ni} * G_A} = \frac{P_{No}}{P_{Ni} * \frac{P_{So}}{P_{Si}}} = \frac{\frac{P_{Si}}{P_{Ni}}}{\frac{P_{So}}{P_{No}}} = \frac{SNR_{in}}{SNR_{out}}$$

(2.7)

The noise figure is simply the noise factor expressed in decibels (2.8).

$$NF = 10 * \log_{10} \left( \frac{SNR_{in}}{SNR_{out}} \right) = SNR_{in,dB} - SNR_{out,dB}$$

(2.8)

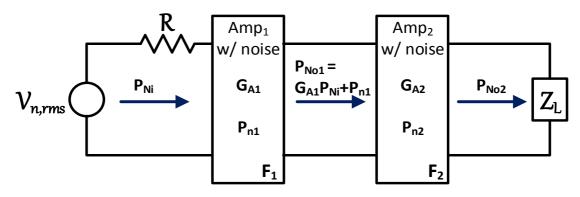

$P_{No}$  and  $P_{Ni}$  are the available noise power presented at the output and input, respectively.  $P_{Si}$  and  $P_{So}$  are the available signal power at the input and at the output too. At the start of this chapter the LNA was treated as one of the most important blocks in a receiver, and now it will be shown why. If (2.9) [2] can be take into account, it is easy to understand that the gain of the LNA is present in every block of the receiver, so it is extremely important to have a good gain in the first block (LNA) to compensate the others [2]. A basic configuration can be shown in Figure 2.7 [16] and Figure 2.8 [2].

Figure 2-8 – Noise Network [2].

$$F = \frac{P_{No2}}{P_{No1} * G_{A2}} = \frac{G_{A2} * (P_{Ni} * G_{A1} + P_{n1}) + P_{n2}}{P_{Ni} * G_{A1} * G_{A2}} = F1 + \frac{SNR_{in}}{SNR_{out}}$$

$$F = F1 + \frac{F2 - 1}{G_{A1}} + \frac{F3 - 1}{G_{A1} * G_{A2}} + \cdots$$

(2.9)

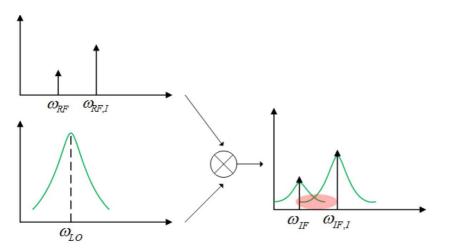

#### 2.3 Mixers

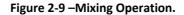

The responsibility for the process of translating the frequency to an Intermediate frequency (IF), or to baseband (known as down-conversion), belongs to one important receiver element. That important role is played by the mixer. In Figure 2.9 is possible to verify that it is just a multiplicative operation between two high frequency inputs. The inputs are the RF signal and the other is the LO signal. From this operation results two signals (shown in Figure 2.10 and considering the translations to IF only), the frequency of the signals are, respectively the sum and the difference of the frequencies from the input signals [1].

$$V_{RF} \sin(f_{RF}) \longrightarrow V_{IF} \frac{|f_{RF} - f_{LO}|}{(f_{RF} + f_{LO})} V_{IF} \frac{1}{2} V_{LO} V_{RF} \cdot \left[\cos((f_{RF} - f_{LO}) \cdot t) - \cos((f_{RF} + f_{LO}) \cdot t))\right]$$

$$V_{IF} \cos(f_{IF} t) = \frac{1}{2} V_{LO} V_{RF} \cdot \cos((f_{RF} - f_{LO}) \cdot t))$$

$$V_{LO} \sin(f_{LO})$$

Figure 2-10 – Down-Conversion Resulting Spectrum.

Having in mind that the mixing process have nonlinear behaviour so, it's natural to predict higher order effects and intermodulation issues, when using MOS transistors (which are nonlinear devices). This way, both phase and amplitude of the wanted signal, get compromised, thanks to those effects and issues mentioned before, complicating the design process.

Forward on this chapter will be possible to overview two kinds of MOS transistors mixers as well as their properties and characteristics.

#### 2.3.1 Performance Parameters of Mixers

#### **Conversion Gain**

As studied in the beginning of this chapter, for a mixer to be useful, it must be followed by a filter that removes the high frequency component. Assuming an ideal filter, the output is given by equation 2.10.

$$\frac{1}{2}V_{LO}V_{RF}\cos((f_{RF} - f_{LO})t)$$

(2.10)

Keeping an ideal scenario, the quotient between IF and RF signals define the gain (expressed in dB) and it is given by:

$$20\log\left(\frac{V_{LO}V_{RF}}{2V_{RF}}\right) = 20\log\left(\frac{V_{LO}}{2}\right)$$

(2.11)

The appearance of unwanted signals is originated by the fact that the mixer is implemented through a not so simple non-linear system [17]. A frequency dependent gain is lead to by the non-ideal filtering (less or greater than one). All of these effects together results in equation 2.11.

$$20\log_{10}\left(\frac{V_{LO}A}{2}\right) \tag{2.12}$$

#### Noise

The efficiency of the energy conversion from a mixer is the same either in the upper or lower sidebands. The same way as the original signal, every noise source will be replicated and translated up and down as well. In the IF band domain, the aliasing effect generated by both LO and LNA noise, will be noticeable at the output. This is a consequence of the wideband nature of the noise. The noise contributions decrease, can avoid some of these effects and lower the mixer noise as well (equation (2.8) and (2.9)).

A final note to this matter regards to the IF frequency selection. This must be done carefully. The flicker noise can be unpleasant if the IF frequency is below flicker noise corner frequency while the frequency translation of the noise occurs.

#### **Linearity and Intermodulation Products**

There is a need for an indication of the 3rd order products levels that a mixer is most likely to produce under multi-tone excitation. That spurious products in a mixer are harmonics that, when generated, can be difficult to filter without eradicating the wanted IF signal. This is problematic.

To describe this effect there is the necessity of IIP3 measurement. This named Input Referred Intercept Point is defined as the input power of the RF signal at which, the output power of the third order intermodulation products become equal or greater than the IF signal. With the intersection of the extrapolated IF response with the third-order intermodulation IF product, it becomes possible to achieve this abstract point shown in Figure 2.11.

Summarising, the higher intercept point will allow to handle more input power without causing undesired products, which would interfere with the desired IF output product, and, mainly, it will allow mixer to have a greater dynamic range [17].

Figure 2-11 – 3<sup>rd</sup> Order Intercept Point (IIP3).

These calculations gives an indication of the capability of the mixer, to handle the signal. That justifies why it is so important, in terms of performance measurements of a mixer, to calculate this parameter.

#### 2.3.2 Different Types of Mixers

#### **Passive Mixers**

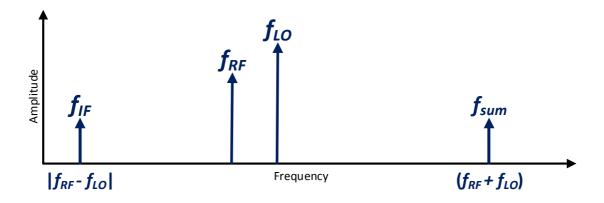

In order to produce the mixing operation, by the simplest way, the switching method can be used. This process consists of shifting the input RF signal to the output at lower frequency (IF). It also explains that LO signal at high level implies an open switch, consequently, the RF input signal is transferred, and at low level the switch is off and the input signal is not transferred.

The passive mixer, which implements the mentioned process, can be designed by using CMOS transistor, shown in Figure 2.12. The gate of the transistor is driven by the LO signal, the RF signal is applied at its source and the IF signal is taken at its drain [2].

Figure 2-12 – Passive Mixer Using Active Device [2].

The transistor presented operates as a switch, because the LO signal induces voltage variation on the gate, which changes the operation region of the transistor. More specifically, and with the help of the equation 2.13, whenever the voltage of LO exceeds the voltage of the RF by at least a threshold voltage ( $V_{TH}$ ) the transistor will conduct.

$$\left\{ \begin{array}{ll} V_{LO} - V_{RF} \geq V_{TH}, & Switch on \\ V_{LO} - V_{RF} < V_{TH}, & Switch of f \end{array} \right.$$

(2.13)

Basically, the transistor will swing between the cut-off region (transistor off) and triode region (transistor on).

#### **Active Mixers**

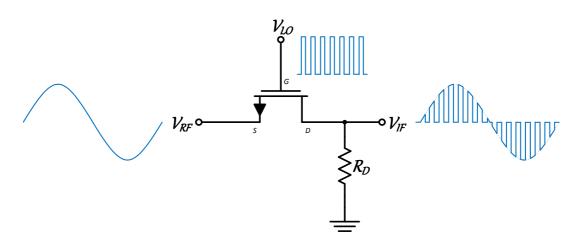

In the other hand, there are two other simple alternatives, which are inserted on the active type of mixers, that, contrary to the last one, provide gain and strength to the IF signal, and for that reason these are widely used in RF systems.

In this type of mixer, the mixing operation is achieved with the same commutation behaviour mentioned previously, yet a differential pair is used instead of using a single active device. These transistors operate in the saturation region (when active) and they acquire not only a current gain, but also a high output impedance, which allows to achieve gain. Not to mention that a differential output is retrieved and, consequently, the amplitude of the IF output is doubled [1, 17].

The alternatives, that are discussed here, are named as: Single-Balanced and Double-Balanced Mixers. The first architecture is represented in Figure 2.13.

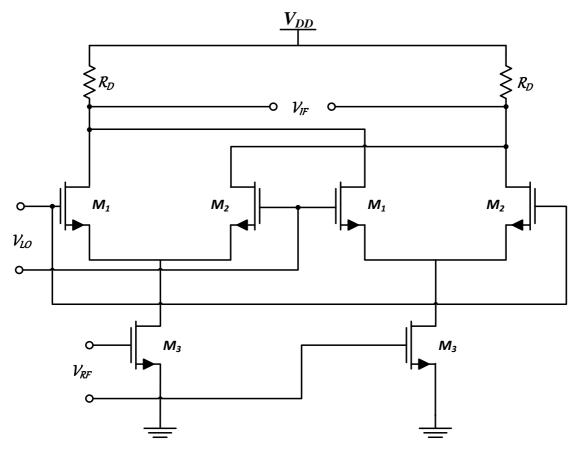

Figure 2-13 – Single Balanced Mixer [1].

This mixer has a differential pair of inputs driven by LO signal and also has a RF unbalanced input signal, which is converted into a current and this current is drawn alternately by the two sides of the differential pair. This mixer is a simple active mixer that allows to achieve a moderate gain and noise figure and high input impedance. As disadvantages, it has low 1dB compression point, low IIP3 and low isolation on port-to-port.

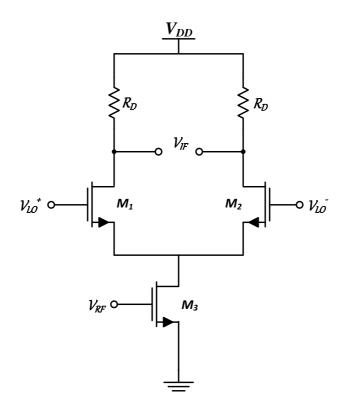

The double-balanced mixer is also called Gilbert Cell and is shown in Figure 2.14.

Figure 2-14 – Gilbert Cell.

This mixer is more complex because of having only differential inputs, even so, it achieves the same conversion gain as the single-balanced mixer, this can be explained by the circuit symmetry and phase shifts on the inputs and, for that reason, the extra differential pair does not enables gain doubling. Anyhow, it presents a lot of advantages, such as: a better linearity, better port-to-port isolation, it is less sensitive to even order distortion and, due to symmetry, the LO harmonic is removed from the output. The last advantage is useful to ensure a proper function of the following blocks, when considering a more complex RF structure like the receiver. However, these improvements increase the power consumption, the circuit area and its cost [1, 17].

# 3

# **3** Oscillators

At this particular chapter, it is plausible to begin the explanation related to one of the most important blocks in a receiver, since the quality of a down-conversion depends on the quality of his work. In this sense, it is the oscillator and it can be said that it converts a given DC level in pure sine or square-wave signal.

The performance and some other important parameters of the oscillator, in terms of measures, will be detailed and characterized in the present chapter [1, 18, 19].

### 3.1 Barkhausen Criterion

It is well known that the basic function of an oscillator is to convert a DC signal into a periodic signal. A sinusoidal oscillator generates a sinusoid with frequency  $\omega_0$  and amplitude  $V_0$ , that is:

$$v_{OUT}(t) = V_0 \cos(\omega_0 t + \theta_0) \tag{3.1}$$

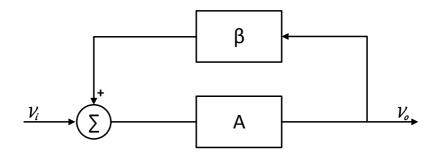

Regarding digital applications, it is fair to mention that oscillators generate a clock signal, which is a square-waveform with period  $T_0$ . Sinusoidal oscillators can be analyzed as feedback systems, shown in the next Figure, with the transfer function given by (3.2):

$$\frac{v_{out}(j\omega)}{v_{in}(j\omega)} = \frac{A(j\omega)}{1 - A(j\omega)\beta(j\omega)}$$

(3.2)

Figure 3-1 – Simple feedback system [1].

The necessary conditions regarding the loop gain for steady-state oscillation with frequency  $\omega_0$  are known as the Barkhausen conditions.

It is very important to highlight the aforementioned conditions, since they play a vital role in the field of electronics. The loop gain (as show in Figure 3.1) must be unity (gain condition), and the open-loop phase shift must be  $2k\pi$ , where k is an integer including zero as it can be seen at (3.3) (phase condition).

$$|A(j\omega_0)\beta(j\omega_0)| = 1$$

$$\arg[A(j\omega_0)\beta(j\omega_0)] = 2k\pi$$

(3.3)

The Barkhausen criterion gives the necessary conditions for stable oscillations, but not for start-up. For the oscillation to start, triggered by noise, when the system is switched on, it is mandatory that the loop gain must be larger than one,  $|A(j\omega_0)\beta(j\omega_0)| > 1$ .

#### 3.2 Phase-Noise

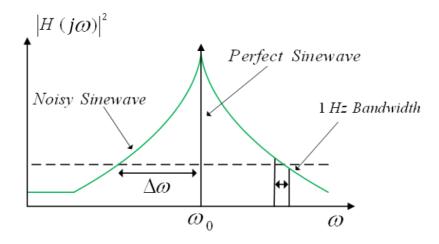

Phase noise is an important measure of performance of an oscillator. Ideally an oscillator should generate a perfect sine-wave which corresponds in the frequency domain to two Dirac signals. According to what we said above, the output signal presents a corruption of its spectrum (3.1).

Those undesired components (noise sidebands) that are now present in the spectrum can be quantified and will be reffered as phase-noise (Figure 3.2). This is represented by  $\mathcal{L}_{(\Delta\omega)}$  and can be expressed as the ratio between the power in a 1 Hz bandwidth at the offset frequency to the total power of the carrier hence specified in dBc/Hz. Equation 3.4 represents the aforementioned relation.

Figure 3-2 – Ideal Carrier and Carrier with Phase-Noise (adopted from [17]).

$$\mathcal{L}_{(\Delta\omega)} = \frac{P(\Delta\omega)}{P(\omega_0)} \tag{3.4}$$

The arising of the components previously indicated as noisy sidebands, can compromise the receiver performance. If the receiver mixer performs a down-conversion using an oscillator signal with a considerable amount of phase noise, it could happen that nearby frequencies from the signal of interest can be also down-converted (Figure 3.3). Clearly, this situation will result in overlapped signals (aliasing) which is not wanted [17]. This is the main reason why phasenoise measurement can be useful to quantify the receiver immunity level against nearby channels.

Figure 3-3 – Phase-Noise Effect in Down-Conversion (adopted from [17]).

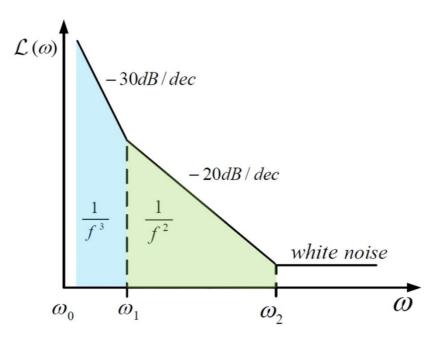

The phase noise can be divided, by considering the single side band (SSB) spectral density in three regions as shown in Figure 3.4. The very first region symbolizes the noise of the active

devices, the second region is the white noise within the oscillator and the last one is the white noise introduced by neighbor devices.

Figure 3-4 – Phase-Noise Single Side Band (adopted from [17]).

# 3.3 Quality Factor

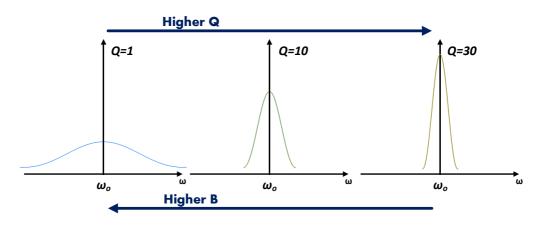

The quality factor is another way of characterizing the carrier spectrum, given the fact that it is related to the oscillator phase-noise (see Figure 3.5). Considering a second order system, there are three plausible designations or definitions for the quality factor.

Figure 3-5 – Carrier Spectrum Regarding Variations in The Quality Factor.

1. The first definition is related to a second order resonant circuit with bandwidth measured at -3db of the output signal and a carrier frequency  $\omega_0$ :

$$Q = \frac{\omega_0}{B} \tag{3.5}$$

This is applied to filters and oscillators characterized as second order resonator circuits [1].

2. The second designation is expressed as the measure of the rate of how the energy is lost, regarding to the oscillator stored energy (usually the loss of energy is related to resistive devices and the stored energy with the reactive devices). This is typically applied to a generic RLC circuit and the equation 3.6 expresses the ratio previously discussed:

$$Q = 2\pi \frac{Maximum\ energy\ stored\ in\ a\ period}{Energy\ dissipated\ in\ a\ period}$$

(3.6)

3. The third definition takes into consideration, not only the amplitude (A) but also the phase ( $\theta$ ) variations of the open-loop transfer function,  $H(j\omega)$ , of the oscillator (which is considered as a feedback system). This definition is often considered to calculate the quality factor of a two-integrator oscillator.

$$Q = \frac{\omega_0}{2} \sqrt{\left(\frac{dA}{d\omega}\right)^2 + \left(\frac{d\theta}{d\omega}\right)^2}$$

(3.7)

The quality factor has an inherent relation with the phase noise, that is, the higher the quality factor more the slopes  $1/f^3$  and  $1/f^2$  will come close to the carrier frequency which reflects on the decrease of the phase noise [17].

A high Q oscillator will be more difficult to tune and to design, given the fact that it requires several reactive elements (as a consequence, area consumption will increase). Regardless this aspect, it will be more stable and immune to nearby channels.

## 3.4 Examples of Oscillators

### 3.4.1 LC Oscillator

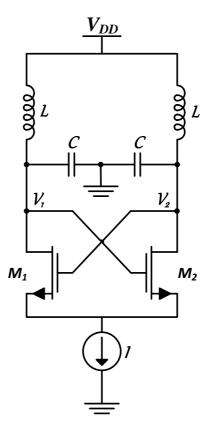

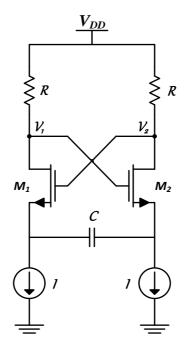

In Figure 3.6 it is possible to notice the first example presented. To assure the phase shift for oscillation, the LC Oscillator uses pure reactance feedback. Like the CMOS mixers, this circuit acts as a commutator, and is constituted by a differential pair that alternate the current conduction path through the feedback network. The alternate signal is created then.

Figure 3-6 – LC Oscillator [1].

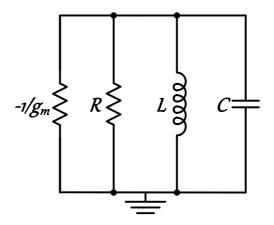

To meet the Barkhausen conditions, the differential pair presents cross-coupled outputs compensating the losses (installed by the feedback network). In Figure 3.7 is modelled the small signal equivalent of the differential pair, simulating the behaviour of a negative resistance.

Figure 3-7 – LC Oscillator Linear Model.

The main drawback of this kind of oscillator lies on its low frequency tuning capability, since the feedback network parameters are fixed (equation 3.10). On the other hand, a quasilinear behaviour, low phase-noise and usually a high quality factor represent some of the advantages of the LC oscillators.

$$\omega_0 = \frac{1}{\sqrt{LC}} \tag{3.10}$$

In terms of CMOS technology area consumption, LC oscillators integration have not the most desirable area consumption. Completing, modern receivers require quadrature outputs, which this oscillator alone is not able to provide. The solution lies in coupling an additional oscillator, which will increase even more the area used as well as it will degrade the frequency response due to the additional parasitic capacitances [17].

#### 3.4.2 Relaxation Oscillators

In the last years, most of the attention was held to another type of oscillators. Known as RC oscillators (the feedback network is now formed by a capacitor and a resistor) with very similar structure and behaviour to the ones studied in the LC oscillator. Equation 3.8 shows the integrator effect of the capacitor, transforming the DC current into voltage. The resistor is used for biasing purposes [17].

$$v(t) = \frac{1}{C} \int_{t_0}^{t} i(\tau) \, d\tau + v(t_0)$$

(3.8)

RC oscillators occupy far less area than a LC oscillator and are highly integrable due to the absence of the inductor which cause a lower quality factor. It has the same differential pair that

is responsible for the loss compensation and commutation behaviour. A common RC oscillator (Relaxation Oscillator) can be observed in Figure 3.8 and the resonant frequency is shown in equation 3.9, where it was given by [1] that this oscillator integration constant is I/C, and the amplitude is 4IR.

$$f = \frac{I}{2C(4RI)} = \frac{1}{8RC}$$

(3.9)

Figure 3-8 – Relaxation Oscillator [1].

#### 3.4.3 Coupled Ring Oscillators

The most basic CMOS ring oscillator employs an odd number of static single-ended inverters as delay cells ( as shown in Figure 3.9).

Figure 3-9 – 3-stage single-ended ring oscillator.

The transition travelling around the ring has to pass through each inverter twice to arrive at the initial state. Therefore, the oscillation frequency is given by Equation (3.10).

$$f_{osc} = \frac{1}{2 * \tau_{Chain}} = \frac{1}{2 * N * \tau_{Inverter}}$$

(3.10)

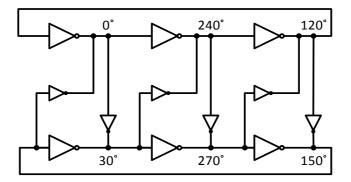

Unfortunately, quadrature outputs require a ring with an even number of stages [34]. Although coupled ring oscillators are not very conventional, they can provide high speed operations as well as multiphase quadrature outputs. This specially designed, single ended, inverter based coupled ring oscillators are also attractive for the capability of generating quadrature outputs in different variations. Before presenting different varieties of coupled oscillators, it is possible to say that this kind of oscillators may be useful in noisy environments. When compared with conventional ring oscillators, coupled ring oscillators have better phase noise and jitter performance, for a given power dissipation and oscillation frequency [20].

Figure 3-10 – Two sets of 3-stage ring oscillators coupled together [20].

In Figure 3.9 is shown two conventional, single ended, three stage ring oscillators [21]. In order to produce multi-phase outputs and high speed oscillation, they are coupled together. This simple linear model of the ring oscillator is used to predict the oscillation frequency of the coupled oscillator. Creating three sets of outputs with 30° phase difference between the neighbour vertical nodes can make this structure to oscillate. To be able to prove that this coupled oscillator is 1.57 times faster than conventional three-stage ring oscillator frequency, [20] were done analytical studies to find a valid function of the transfer matrix of the system. Moreover it is possible to say that compared to conventional ring oscillator, this coupled ring oscillator has double the area occupied by the conventional one and dissipates also the double of the energy supplied.

Another way to produce the quadrature outputs was reported by [10], using a three stage coupled ring oscillator. But this time, were added two delay cells to couple the conventional ring oscillators in Figure 3.9. This ring topology can produce two sets of quadrature outputs with 90°

phase shift as shown in Figure 3.10, and is considered as a Quadrature four-stage ring oscillator [34]. When comparing to conventional ring oscillators performance, it is possible to say that these coupled oscillators have better phase noise, and that the oscillation frequency turns to be just the same as the conventional, single ended, inverter based version of the ring oscillator. In the next chapter a particular coupled ring oscillator will be detailed, the 8-Phase Ring Oscillator, where more useful considerations will be made.

Figure 3-11 – Quadrature four-stage ring oscillator [34].

In contrast to a ring oscillator with an odd number of inverters, now two transitions are travelling through the ring. Therefore, the oscillation frequency in now given by Equation 3.11.

$$f_{osc} = \frac{1}{\tau_{Chain}} = \frac{1}{N * \tau_{Inverter}}$$

(3.11)

As there is a rising and falling transition ate any time, the single-ended quadrature ring oscillator draws a nearly constant supply current and minimises switching noise on supply lines.

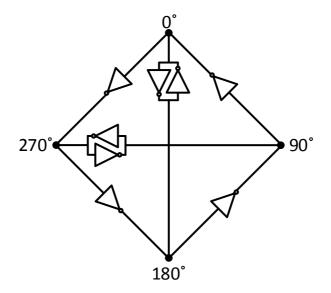

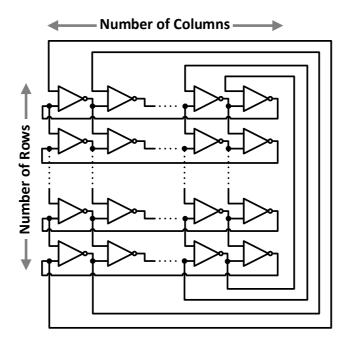

To finally settle this chapter, [22] describes a way to use coupled ring oscillators, to generate accurate delays (with a resolution equal to an inverting buffer delay, divided by the number of rings). Figure 3.11 shows what it a two-dimensional array oscillator. The concept is to force numerous rings to oscillate at the same frequency. This way, each frequency can be evenly shifted in phase by an exact fraction of a buffer delay. Nevertheless, the oscillation frequency is controlled mainly by the number of buffers per ring regardless to the number of rings in the array. Additional output phases can be introduced, and the delay resolution will

improve just by adding rings to the array. This kind of array oscillator can be realized using both single ended or differential inverting buffer.

Figure 3-12 – Two dimensional array oscillator [20].

# 4

# 4 8 Phases Oscillator

#### 4.1 Introduction

In order to describe and validate the 8 Phases Oscillator, there is a need to begin with a background introduction and the reason that led this work to be done. In [11] it was started to be developed a discrete-time (DT), harmonic rejection (HR) mixer with the objective of relaxing the RF filter requirements and reducing the noise folding, as seen in [23]. Contemporary CMOS technologies have allowed effective discrete-time, switched-capacitor (SC), applications of RF receiver front-ends. To obtain decent Image rejection, accurate I and Q quadrature signals are essential [2, 24] so, as already studied in Chapter 2, it is possible to consider low-IF front-ends, to overcome some of the restrictions of the zero-IF approach (mainly flicker noise and DC offset).

When compared to active mixers, the passive Mixer/IIR filter used in [23], have the benefits of low power consumption when dealing with RF signals, and considerable smaller flicker noise (as there isn't any DC current) [2, 24]. But the central drawbacks of passive mixers is the lack of conversion gain, which disturbs the global gain and entire noise budgets for the whole receiver. To beat this limitation, [11] suggest to apply the MOS Parametric Amplifier (PA) technique to the Mixer/IIR filter proposed in [23].

Analog and DT SC mixing receiver designs from [23] can combine quadrature mixing for I/Q demodulation and wideband HR. Although, its circuit suffers from signal attenuation and forces higher gain and linearity requirements on the LNA. A charge-transfer low-pass (LP) SC filter [2] can be used, which includes a passive SC amplifier cascaded with a recursive SC filter (IIR), in order to amplify the signal amplitude. The circuit projected in [11] alone consumes 4.2 mW and occupies 0.11 mm2, without having the mixing stage into account. It also uses PA to increase the gain with reduced power and much lower area.

## 4.2 Downconverter Architecture

The SC downconverter offered by [11] associates quadrature (I/Q) mixing and wideband HR in the VHF-III band (174 to 248 MHz). In Figure 4.1 is possible to see the block diagram of the IC from where the 8 Phases Oscillator in study, was adopted. An input-driver containing a low-gain RF amplifier and two enhanced voltage-followers (EVFs) drives the fully-passive SC core circuit. Once the objective of this IC is only to measure the SC core circuit performance, it's possible to say that it have about 0 dB conversion gain and provides 50  $\Omega$  input matching. The SC downconverter core consists of three stages:

- An oversampler with fs = 8 fc (fs is the sampling frequency and fc the carrier frequency);

- Two I/Q DT mixers for downconversion;

- Two LP IIR filters.