## Nuno Lemos Braamcamp de Mancelos

Licenciatura em Ciências da Engenharia Electrotécnica e de Computadores

# A Piezoelectric Based Energy Harvester Interface for a CMOS Wireless Sensor IC

Dissertação para obtenção do Grau de Mestre em Engenharia Electrotécnica e de Computadores

Orientador: Prof. Doutor João Pedro Abreu de Oliveira

Júri:

Presidente: Professor Doutor Luís Filipe Figueira de Brito Palma

Arguente: Professor Doutor Luís Augusto Bica Gomes de Oliveira

Vogais: Professor Doutor Fortunato Carlos Dualibe

Professor Doutor João Pedro Abreu de Oliveira

FACULDADE DE CIÊNCIAS E TECNOLOGIA UNIVERSIDADE NOVA DE LISBOA

Setembro, 2014

## A Piezoelectric Based Energy Harvester Interface for a CMOS Wireless Sensor IC

Copyright © Nuno Lemos Braamcamp de Mancelos, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa.

A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objectivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

# Acknowledgements

I would like to express my gratitude to my advisor, Prof. João Pedro Oliveira, for the interest he showed in my thesis right from the beginning, the patient advice and dedicated support he gave me, and for having accepted to help me in the particular subject that is approached in the thesis, which represents a growing interest of mine. As someone whose motivation is strongly enhanced by increased levels of personal interest, I truly value that acceptance.

I wish to express my appreciation to Prof. Fortunato Dualibe for his shared time and expertise, and for having assured a smooth and encouraging transition to a different department in a different country. His assertive guidance drove many crucial aspects of the thesis forward, and at full speed.

Prof. Luís Oliveira is also someone I want to thank. His classes helped me realise that my Master's degree should focus on Electronics. His willingness to assist and guide his students is tireless.

For all the much needed support, encouragement, affection and patience, I wholeheartedly thank my mother, father and sister. They are, and have always been, more than I could wish for. I am very proud to call them family.

My special thanks go to my girlfriend and colleague, Joana Correia, with whom I faced many challenges, side by side. With her I learned that a good team is something to be treasured and nurtured, and that there are no limits to the number of roles a person can fit in the life of another. Thank you for sharing this journey with me. Universidade Nova de Lisboa

## Resumo

# Faculdade de Ciências e Tecnologia Departamento de Engenharia Electrotécnica e de Computadores

Mestrado em Engenharia Electrotécnica de e Computadores

por Nuno Lemos Braamcamp de Mancelos

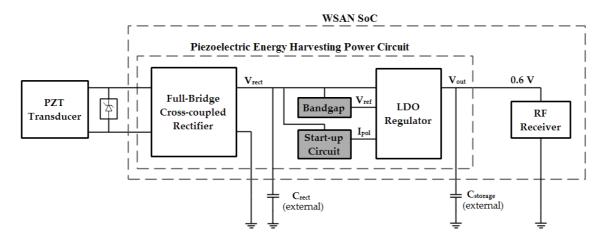

Esta tese apresenta a implementação de um sistema *energy harvesting* piezoeléctrico que tem o objectivo de alimentar um receptor RF com um consumo de 6 mW. Para tal é necessário que o sistema regule a saída de um transdutor piezoeléctrico submetido a vibração. A caracterização do transdutor escolhido é o ponto de partida do projecto, sendo que seguidamente é apresentado o rectificador responsável por rectificar a saída *AC* do transdutor, um *full-bridge crosscoupled rectifier*. O conversor DC-DC utilizado é um *low-dropout regulator*, que garante que a saída do sistema é mantida a um valor constante e com *ripple* reduzido. Este valor é 0,6 V, que corresponde à tensão de alimentação requisitada pelo receptor. O circuito é desenhado recorrendo à tecnologia CMOS 130 nm UMC, e apresenta uma arquitectura sem bobines, com reduzida área e custo. As simulações eléctricas feitas para o sistema completo levam a concluir que o circuito é uma solução plausível no que toca à alimentação do receptor RF, tendo em consideração níveis moderados de vibração do transdutor piezoeléctrico.

Palavras-chave: Energy Harvesting Piezoeléctrico, Rectificador Full-Bridge Cross-coupled, Conversor DC-DC, LDO Regulator, Wireless Sensor Networks.

Universidade Nova de Lisboa

# Abstract

# Faculdade de Ciências e Tecnologia Departamento de Engenharia Electrotécnica e de Computadores

Mestrado em Engenharia Electrotécnica de e Computadores

by Nuno Lemos Braamcamp de Mancelos

In this thesis a piezoelectric energy harvesting system, responsible for regulating the power output of a piezoelectric transducer subjected to ambient vibration, is designed to power an RF receiver with a 6 mW power consumption. The electrical characterisation of the chosen piezoelectric transducer is the starting point of the design, which subsequently presents a full-bridge cross-coupled rectifier that rectifies the *AC* output of the transducer and a low-dropout regulator responsible for delivering a constant voltage system output of 0.6 V, with low voltage ripple, which represents the receiver's required supply voltage. The circuit is designed using CMOS 130 nm UMC technology, and the system presents an inductorless architecture, with reduced area and cost. The electrical simulations run for the complete circuit lead to the conclusion that the proposed piezoelectric energy harvesting system is a plausible solution to power the RF receiver, provided that the chosen transducer is subjected to moderate levels of vibration.

Keywords: Piezoelectric energy harvesting, Full-Bridge Cross-coupled Rectifier, DC-DC Converter, LDO Regulator, Wireless Sensor Networks.

# Contents

| LIST OF TABLES                                                    | XIII    |

|-------------------------------------------------------------------|---------|

| ABBREVIATIONS                                                     | XV      |

|                                                                   |         |

| 1 - INTRODUCTION                                                  | 1       |

| 1.1 – BACKGROUND AND MOTIVATION                                   | 1       |

| 1.2 – Structure                                                   | 3       |

| 1.3 – Contributions                                               | 5       |

| 2 - TOWARDS SELF-POWERED WIRELESS SENSOR NODES                    | 7       |

| 2.1 – System Overview                                             | 8       |

| 2.2 – Energy Harvesting                                           | 14      |

| 2.2.1 – Electromechanical Energy Harvesting                       | 15      |

| 2.2.2 – Considerations regarding Energy Harvesting Applications   | 24      |

| 2.3 – LOW-VOLTAGE RF RECEIVER                                     | 25      |

| 2.3.1 – Transceivers designed for Wireless Sensor Networks        | 25      |

| 2.3.2 – RF Receiver to be powered by the Energy Harvesting System | 27      |

| 3 - ENERGY HARVESTING FROM PIEZOELECTRIC VIBRATION TRANSDU        | CERS 31 |

| 3.1 – PIEZOELECTRIC ENERGY HARVESTING OVERVIEW                    |         |

| 3.2 – The Piezoelectric Transducer                                |         |

| 3.3 – Rectifiers                                                  |         |

| 3.3.1 – Passive Rectifiers                                        | 38      |

| 3.3.2 – Active Rectifiers                                         | 45      |

| 3.4 – DC-DC CONVERTERS                                            | 50      |

| 3.4.1 – Linear Regulators                                         | 50      |

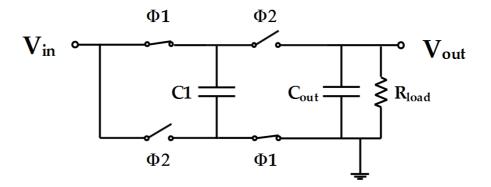

| 3.4.2 – Switched Capacitor Converters                             | 52      |

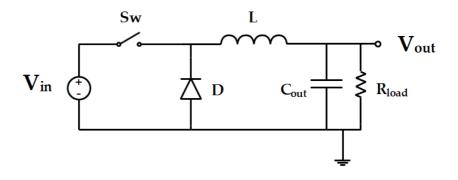

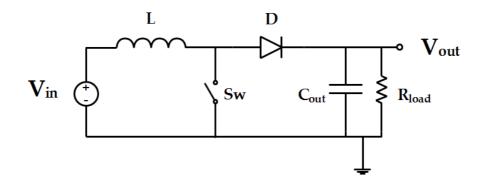

| 3.4.3 – Magnetic Converters                                       | 54      |

| 4 - PROPOSED SYSTEM AND CIRCUIT DESIGN                            | 59      |

| 4.1 - PIEZOELECTRIC ENERGY HARVESTING SYSTEM OVERVIEW             | 60      |

| 4.2 – ACTIVE FULL-BRIDGE CROSS-COUPLED RECTIFIER                  | 66      |

| 4.3 - LOW-DROPOUT REGULATOR                                       | 70      |

| 4.3.1 – PMOS Switch                                               | 71      |

| 4.3.2 – Comparator                                                | 74      |

LIST OF FIGURES ......XI

| 4.3.3 – Clock Generator                                                     | 82  |

|-----------------------------------------------------------------------------|-----|

| 5 - ELECTRICAL SIMULATIONS AND LAYOUT                                       | 87  |

| 5.1 – Electrical Simulations                                                |     |

| 5.1.1 – Piezoelectric transducer and Load circuits used for the simulations | 88  |

| 5.1.2 – Simulations regarding the Rectifier                                 | 90  |

| 5.1.3 – Simulations regarding the Complete Proposed System                  | 94  |

| 5.1.4 – Simulations regarding the Complete Proposed System and the RF       |     |

| receiver's LNA                                                              | 101 |

| 5.2 – LAYOUT                                                                | 104 |

| 5.2.1 – Layout considerations for the Power Circuit                         | 105 |

| 5.2.2 – Layout considerations for the Control Circuit                       | 105 |

| 6 - CONCLUSIONS                                                             | 107 |

| 6.1 – Conclusions                                                           | 107 |

| 6.2 – FUTURE WORK                                                           | 109 |

# List of Figures

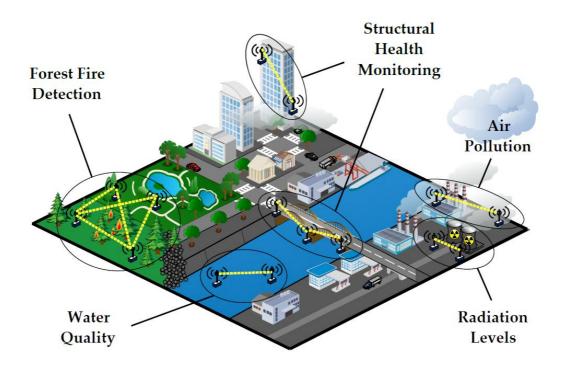

| 2.1: WIRELESS SENSOR NETWORK APPLICATIONS                                                        | 8   |

|--------------------------------------------------------------------------------------------------|-----|

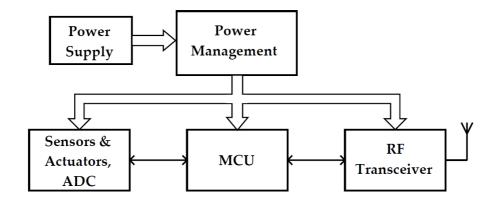

| 2.2: STRUCTURE OF A WIRELESS SENSOR ACTUATOR NODE                                                | 10  |

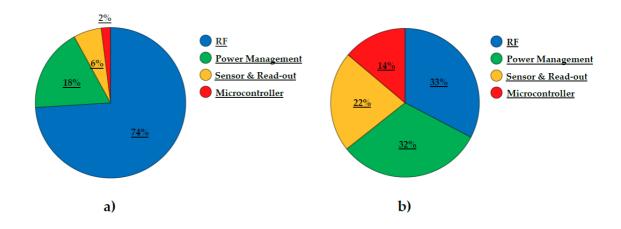

| 2.3: DISTRIBUTION OF POWER CONSUMPTION FOR TWO DIFFERENT WSANS, A) SENSOR NODE BASED ON THE      |     |

| Nordic RF24L01, b) sensor node based on the imec's ULP wireless, data from [2]                   | 11  |

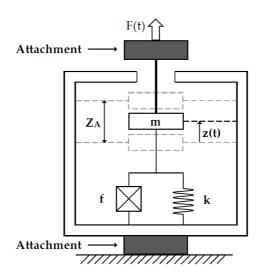

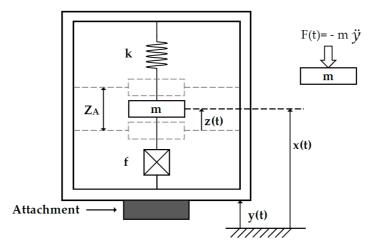

| 2.4: DIRECT-FORCE GENERATOR DIAGRAM, ADAPTED FROM [3]                                            | 16  |

| 2.5: INERTIAL-FORCE GENERATOR DIAGRAM, ADAPTED FROM [3]                                          | 17  |

| 2.6: MAGNETIC SPRING GENERATOR DIAGRAM, ADAPTED FROM [7]                                         | 18  |

| 2.7: RESONATOR ELECTROMAGNETIC GENERATOR, FIGURE TAKEN FROM [10]                                 | 19  |

| 2.8: THE DIRECT AND CONVERSE PIEZOELECTRIC EFFECTS                                               | 20  |

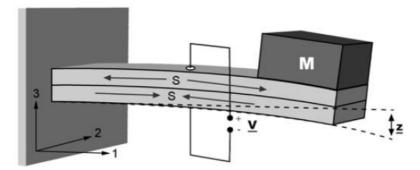

| 2.9: DIAGRAM OF A PIEZOELECTRIC TRANSDUCER WITH A BEAM STRUCTURE, FIGURE TAKEN FROM [12]         | 22  |

| 2.10: BLOCK DIAGRAM FOR A WSAN'S WIRELESS TRANSCEIVER                                            | 25  |

| 2.11: Low-IF Receiver Architecture                                                               | 27  |

| 2.12: Complete Receiver Circuit with all transistor sizes (W/L) in UM, taken from $[17]$         | 28  |

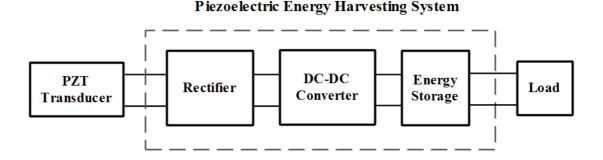

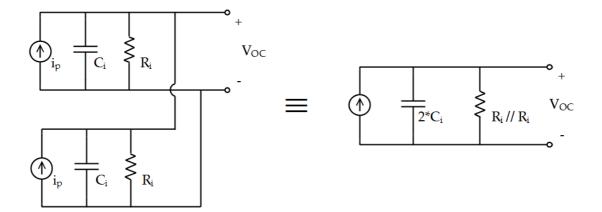

| 3.1: BLOCK DIAGRAM OF A GENERIC PIEZOELECTRIC ENERGY HARVESTING SYSTEM                           | 33  |

| 3.2: Equivalent Circuit of a single wafer on an inertial piezoelectric transducer vibrating near | THE |

| RESONANCE FREQUENCY                                                                              | 34  |

| 3.3: MIDÉ VOLTURE™ V21BL                                                                         | 35  |

| 3.4: Equivalent Circuit of a parallel configuration for a two-wafer piezoelectric transducer     | 36  |

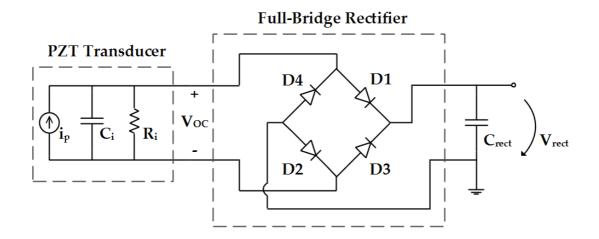

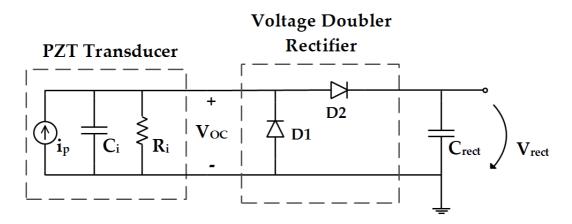

| 3.5: Full-Bridge Rectifier                                                                       | 38  |

| 3.6: Predicted Input current and voltage waveforms for the Full-Bridge rectifier, adapted from   | М   |

| [25]                                                                                             | 39  |

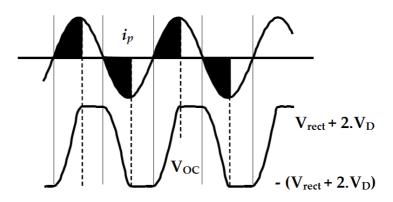

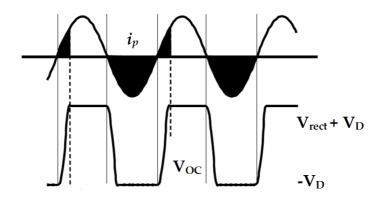

| 3.7: VOLTAGE DOUBLER RECTIFIER                                                                   | 42  |

| 3.8: PREDICTED INPUT CURRENT AND VOLTAGE WAVEFORMS FOR THE VOLTAGE DOUBLER RECTIFIER, ADAPTED    |     |

| FROM [25]                                                                                        | 43  |

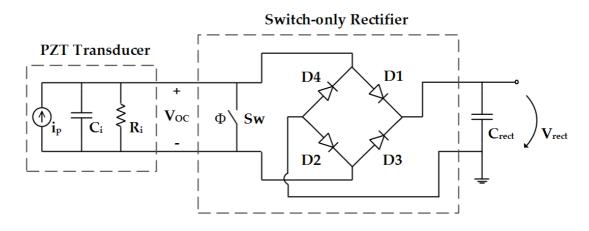

| 3.9: Switch-only Rectifier, [21]                                                                 | 45  |

| 3.10: Relevant current and voltage waveforms related to the Switch-only rectifier's operation    | N,  |

| ADAPTED FROM [21]                                                                                | 46  |

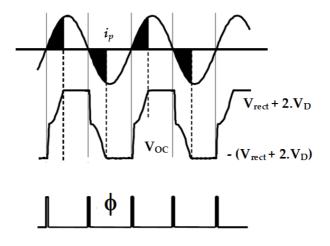

| 3.11: Full-Bridge Cross-coupled Rectifier                                                        | 48  |

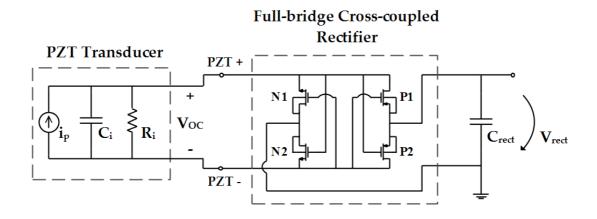

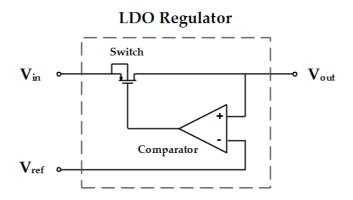

| 3.12: Low-dropout Regulator                                                                      | 51  |

| 3.13: Switched Capacitor Voltage Doubler                                                         | 53  |

| 3.14: TOPOLOGY OF A BUCK CONVERTER                                                               | 55  |

| 3.15: TOPOLOGY OF A BOOST CONVERTER                                                              | 56  |

|                                                                                                  |     |

| 4.1: BLOCK DIAGRAM OF THE PROPOSED PIEZOELECTRIC ENERGY HARVESTING POWER CIRCUIT, GREYED OUT   |      |

|------------------------------------------------------------------------------------------------|------|

| BLOCKS ARE NOT INCLUDED IN THE PROPOSED DESIGN                                                 | 60   |

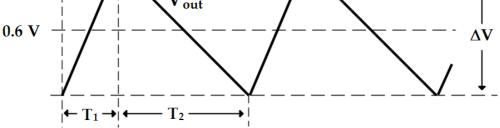

| 4.2: SIMPLIFIED VISUALISATION OF THE SYSTEM'S OUTPUT VOLTAGE RIPPLE                            | 64   |

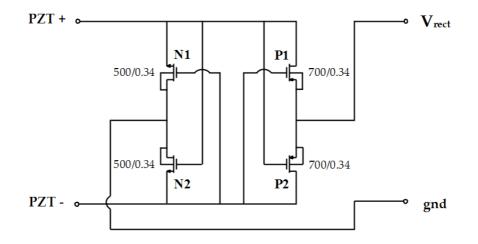

| 4.3: Full-Bridge Cross-coupled Rectifier Schematic, including transistor dimensions in UM (W/L | ).66 |

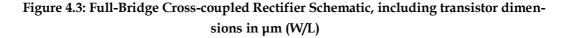

| 4.4: VARIATION OF THE PMOS DEVICE VOLTAGE DROP FOR DIFFERENT ASPECT RATIO VALUES               | 68   |

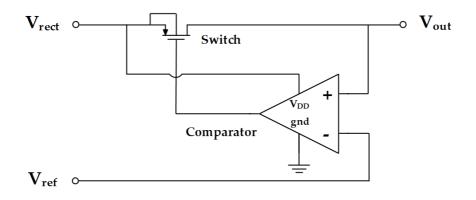

| 4.5: Low-dropout Regulator                                                                     | 70   |

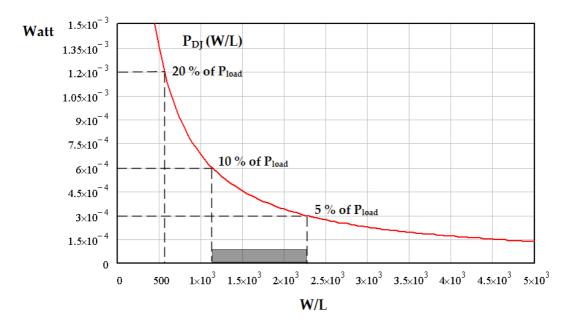

| 4.6: Variation of the power dissipated at the conducting switch by heating effect, with the    |      |

| TRANSISTOR'S ASPECT RATIO AS A VARIABLE (PLOAD=6MW)                                            | 72   |

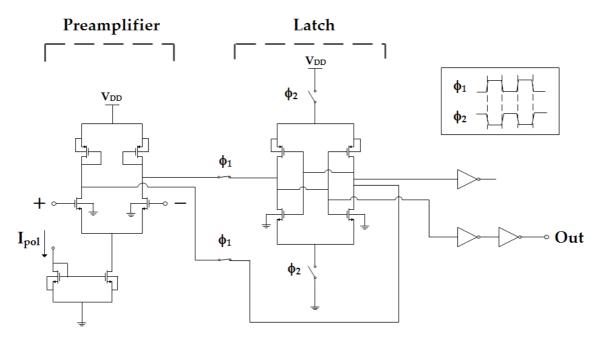

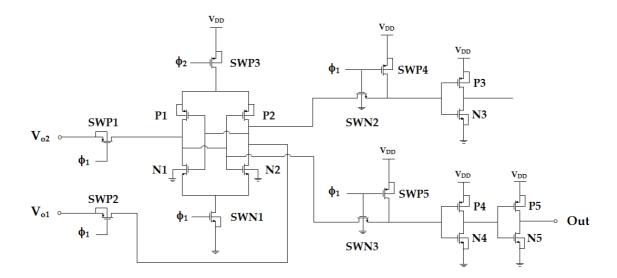

| 4.7: LATCH COMPARATOR'S SIMPLIFIED SCHEMATIC                                                   | 74   |

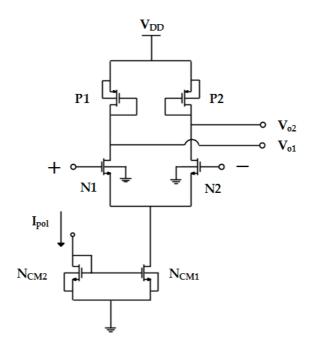

| 4.8: Preamplifier Stage of the Comparator                                                      | 76   |

| 4.9: LATCH CIRCUIT OF THE COMPARATOR, INCLUDING SWITCHES AND OUTPUT INVERTERS                  | 79   |

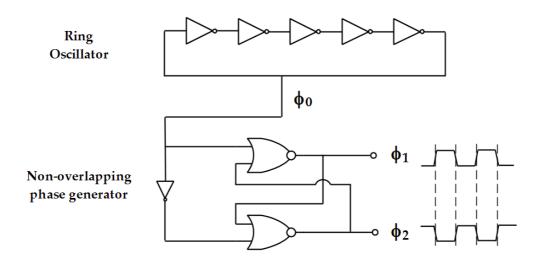

| 4.10: Clock Generator's Architecture                                                           | 82   |

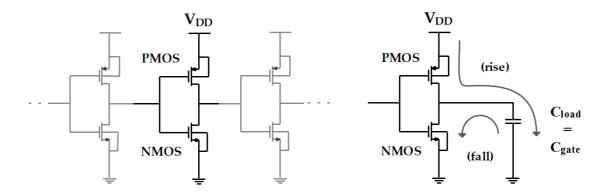

| 4.11: VISUALISATION OF THE OPERATION OF THE OSCILLATOR RING INVERTERS                          | 83   |

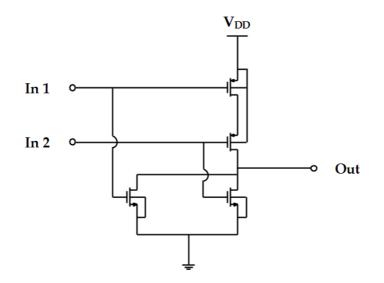

| 4.12: NOR GATE SCHEMATIC                                                                       | 86   |

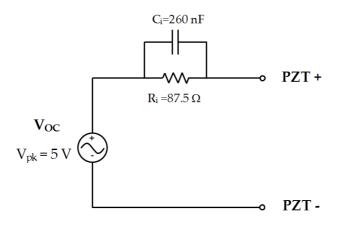

| 5.1: PIEZOELECTRIC TRANSDUCER'S EQUIVALENT CIRCUIT WITH THE CHOSEN DEFAULT SYSTEM INPUT VALUES88                    |

|---------------------------------------------------------------------------------------------------------------------|

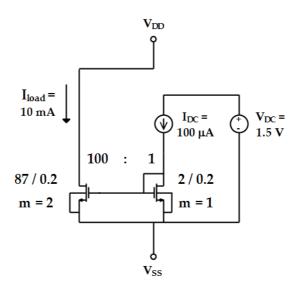

| 5.2: LOAD CIRCUIT USED FOR THE SIMULATIONS                                                                          |

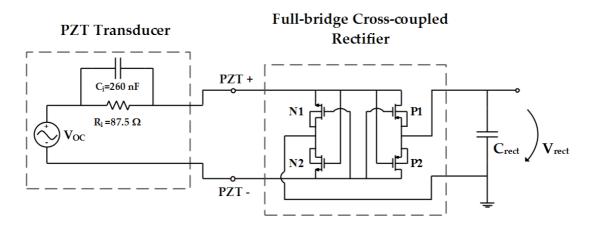

| 5.3: Schematic used for the simulations of the Rectifier module                                                     |

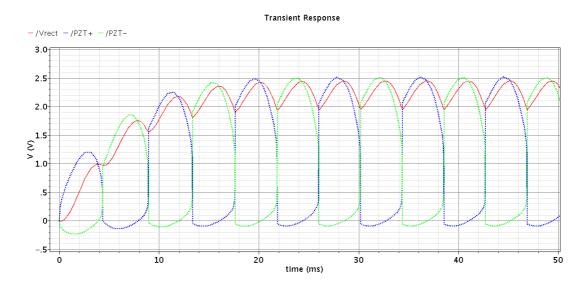

| 5.4: Simulations of the Rectifier module for the default system input, $Vpk = 5V$                                   |

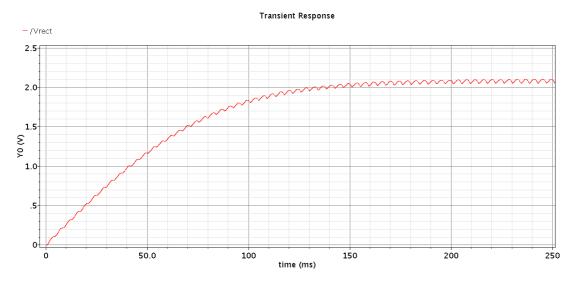

| 5.5: Simulation of the Rectifier module for the default system input, with $Crect = 1  mF$ 92                       |

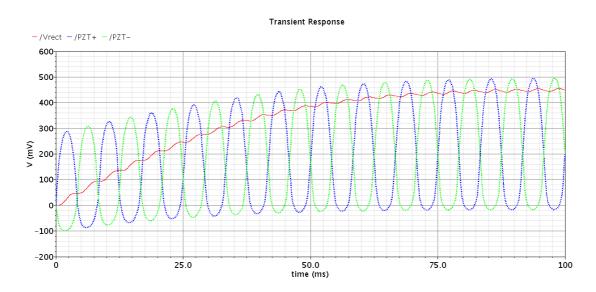

| 5.6: Simulation of the Rectifier module with $Vpk = 0.6 V$                                                          |

| 5.7: Schematic used for the simulations of the Complete Proposed Energy Harvesting System94                         |

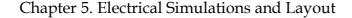

| 5.8: SIMULATION SHOWING THE COMPARATOR'S OUTPUT SIGNAL, Pgate, AND INPUT SIGNALS, Vout AND Vref.95                  |

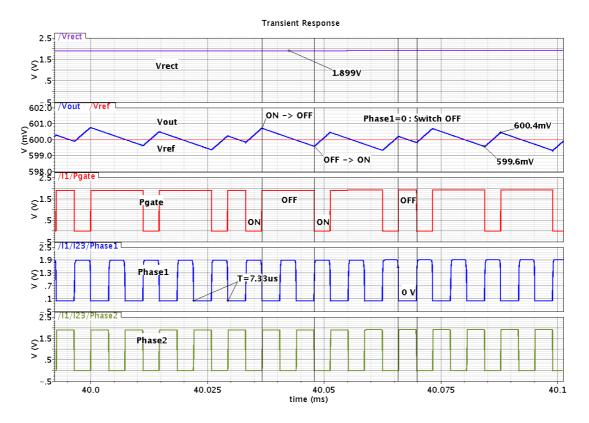

| 5.9: Simulation showing the clock signals $\Phi 1$ and $\Phi 2$ , generated by the Clock Generator Circuit 96       |

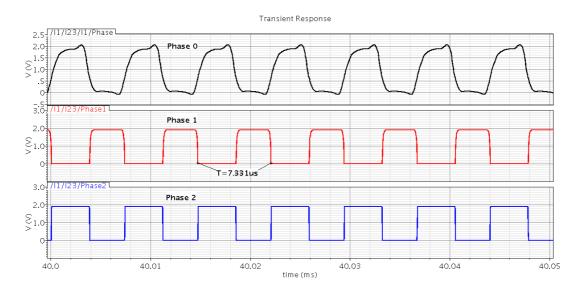

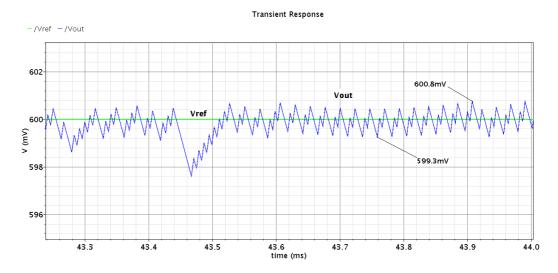

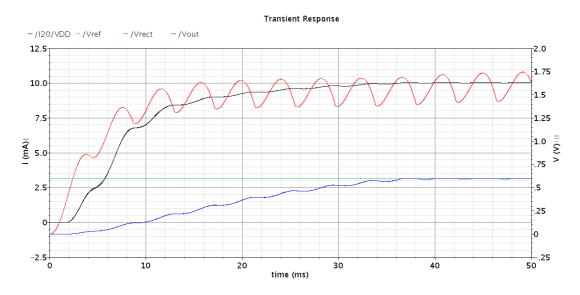

| 5.10: Simulation of the Complete Proposed System for the default system input, $Vpk=5~V$ , and the                  |

| default load requirements, $Vout = 0.6 V$ and $lload = 10 mA$                                                       |

| 5.11: Simulation of the Complete Proposed System for the default system input, zoomed in $Vout$                     |

| SIGNAL                                                                                                              |

| 5.12: Simulation of the Complete Proposed System for the minimum transducer output levels that                      |

| GUARANTEE THE APPLICATION'S POWER REQUIREMENTS, $Vpk=4.5V$                                                          |

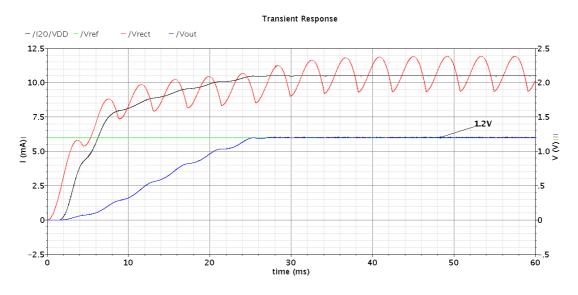

| 5.13: Simulation of the Complete Proposed System for $Vout = 1.2 V$ and $Iload = 10 m$ A, with                      |

| Vpk = 6V99                                                                                                          |

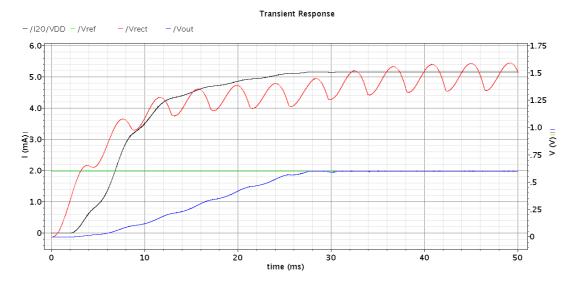

| 5.14: Simulations of the complete proposed system for $Vout = 0.6 V$ and $Iload = 5 m$ , with                       |

| Vpk = 3.5 V                                                                                                         |

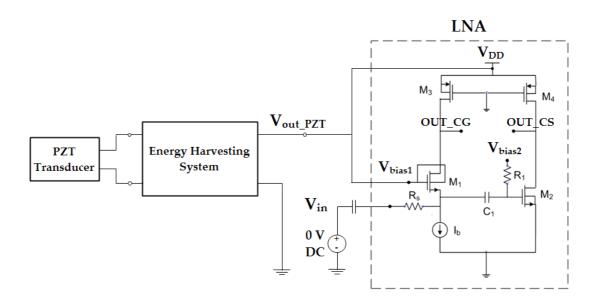

| $5.15: Circuit\ configuration\ for\ the\ simulation\ of\ the\ energy\ harvesting\ system\ and\ the\ RF\ receiver's$ |

| LNA101                                                                                                              |

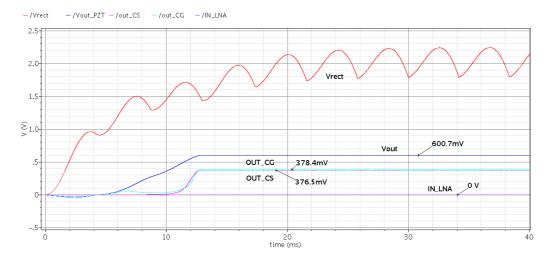

| 5.16: Simulation of the complete proposed system and the RF receiver's LNA, with a $0VDC$ input. $102$              |

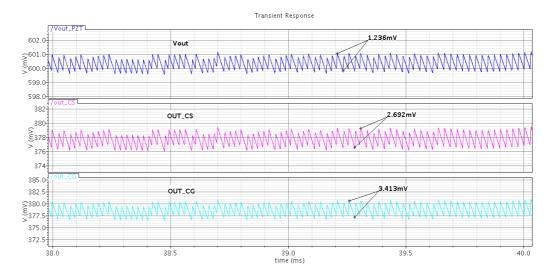

| 5.17: Zoomed in view of the simulation of the complete proposed system and the RF receiver's LNA                    |

|                                                                                                                     |

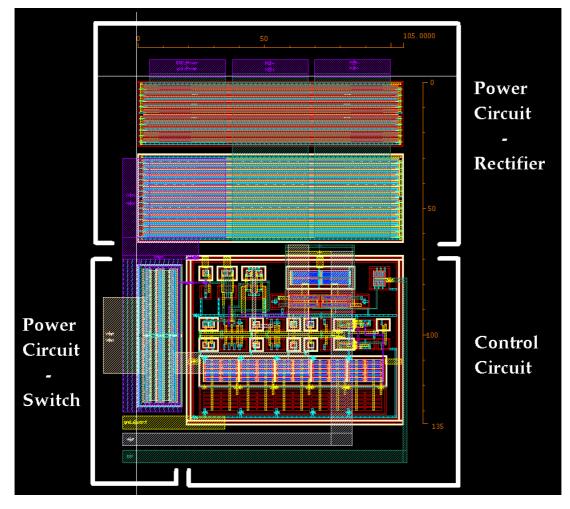

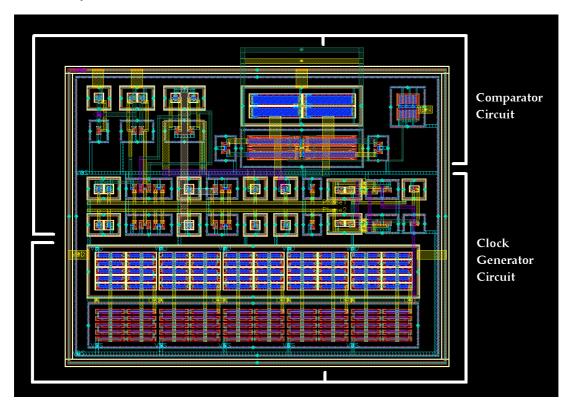

| 5.18: Complete Circuit Layout                                                                                       |

| 5.19: Control Circuit Layout                                                                                        |

# List of Tables

| 2.1: Power Consumption values for different commercial sensor nodes, [1]               | 10 |

|----------------------------------------------------------------------------------------|----|

| 2.2: TYPICAL POWER OUTPUT DENSITIES FOR DIFFERENT ENERGY HARVESTING SOLUTIONS          | 13 |

| 2.3: EXAMPLES OF DIFFERENT WSN TRANSCEIVERS AND CORRESPONDENT POWER CONSUMPTION VALUES | 26 |

| 2.4: SUMMARY OF THE RF RECEIVER'S POWER REQUIREMENTS                                   | 30 |

| 4.1: SUMMARY OF THE RF RECEIVER'S POWER REQUIREMENTS                                    | 61           |

|-----------------------------------------------------------------------------------------|--------------|

| 4.2: SUMMARY OF THE TRANSDUCERS' ELECTRICAL CHARACTERISTICS, [19]                       | 61           |

| 4.3: SUMMARY OF THE TRANSDUCERS' OPEN CIRCUIT VOLTAGE VALUES FOR DIFFERENT VIBRATION AM | IPLITUDES,   |

| [19]                                                                                    | 62           |

| 4.4: CHOSEN CAPACITANCE VALUES FOR THE SYSTEM'S EXTERNAL CAPACITORS                     |              |

| 4.5: Full-Bridge Cross-coupled rectifier transistor dimensions and characteristics      | 69           |

| 4.6: IMPORTANT TECHNOLOGY-RELATED VALUES CONSIDERED IN THE DIMENSIONING OF THE PROPOSEI | D CIRCUIT.69 |

| 4.7: PMOS Switch dimensions and conducting characteristics                              | 73           |

| 4.8: SUMMARY OF THE COMPARATOR'S OUTPUT-INPUT CORRESPONDENCE                            | 75           |

| 4.9: PREAMPLIFIER TRANSISTOR DIMENSIONS                                                 | 78           |

| 4.10: LATCH CIRCUIT TRANSISTOR DIMENSIONS                                               | 81           |

| 4.11: DIMENSIONS FOR THE INVERTER RING TRANSISTORS OF THE CLOCK GENERATOR               | 85           |

| 4.12: CLOCK GENERATOR'S SMALL DELAY INVERTER AND NOR GATE TRANSISTOR DIMENSIONS         | 85           |

|                                                                                         |              |

5.1: Summary of the minimum transducer output values for different sets of load requirements..  $100\,$

# Abbreviations

| AC   | Alternating Current                     |  |  |

|------|-----------------------------------------|--|--|

| ADC  | Analog-to-digital Converter             |  |  |

| CMOS | Complimentary Metal-Oxide-Semiconductor |  |  |

| DC   | Direct Current                          |  |  |

| LDO  | Low-dropout                             |  |  |

| LNA  | Low Noise Amplifier                     |  |  |

| MCU  | Microcontroller                         |  |  |

| NMOS | N-Channel Metal-Oxide-Semiconductor     |  |  |

| PMOS | P-Channel Metal-Oxide-Semiconductor     |  |  |

| PSRR | Power Supply Rejection Ratio            |  |  |

| PZT  | Lead Zirconate titanate                 |  |  |

| RF   | Radio Frequency                         |  |  |

| SHM  | Structural Health Monitoring            |  |  |

| SoC  | System on Chip                          |  |  |

| WSAN | Wireless Sensor Actuator Node           |  |  |

| WSN  | WSN Wireless Sensor Network             |  |  |

# 1

# Introduction

## 1.1 – Background and Motivation

Energy harvesting comprises a wide variety of techniques that make use of ambient energy to power different types of electronic devices. It differentiates itself from conventional renewable sources mainly due to its small scale, and is suitable to power devices like Wireless Sensor Actuator Nodes (WSAN), which are used to collect physical or environmental information, like temperature, humidity, radiation and other physical quantities, usually spread across vast or hardly accessible areas. These devices are commonly required to operate in locations surrounded by one or several sources of residual energy, which can be ambient light, thermal gradients, kinetic energy in the form of vibration or energy present in propagating radio waves, just to name a few. The WSAN devices are wirelessly connected in Wireless Sensor Networks (WSN) formed by several energy autonomous nodes. The common solution to independently power these nodes is the use of batteries, which demand periodic replacement and costly maintenance, since they generally store insufficient amounts of energy, when considering each node's life cycle duration.

Using energy harvesting techniques that are specifically designed to scavenge certain types of residual energy is a plausible answer to the energy demands of the devices that constitute some WSNs. By enabling the energy selfsufficiency of each node, these techniques enhance their wireless and widespread operations, allowing the devices to be installed in increasingly hard to reach or hazardous locations, and giving an incentive to the use of these wireless networks, since their reduced need for maintenance is likely to reduce their overall associated costs.

Some possible uses for WSNs are medical applications, in which the sensor nodes may be worn or implanted, environmental applications like forest fire detection, water quality and air pollution monitoring, structural health monitoring regarding buildings or different large-scale structures, industrial monitoring directed to factory environments or agriculture, and even military monitoring.

In terms of distribution and density values, kinetic energy is a relevant source of energy in some of the applications' environments. Vibration is a common source for this type of energy. One of the most interesting solutions to convert the energy contained in vibrations, in terms of typical power density values, is to use inertial piezoelectric transducers. These transducers explore the piezoelectricity of certain ceramics and crystalline materials, which is a property that is defined by the accumulation of charge inside the structure of piezoelectric materials when mechanical strains are applied to them.

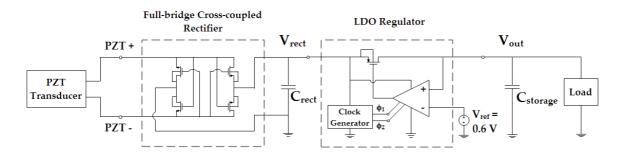

This work presents the design of a piezoelectric energy harvesting system, intended to supply a low-power RF receiver whose design is not part of this work but was the focus of another master's thesis, included in the same multidisciplinary project, a WSAN System on Chip (SoC). The energy harvesting system includes a full-bridge cross-coupled rectifier that rectifies the *AC* output of the inertial piezoelectric transducer. In order to convert the rectifier's output, a DC-DC converter is used, consisting in a low-dropout (LDO) regulator that is responsible for delivering a constant voltage supply, with reduced voltage ripple, to the RF receiver's voltage supply rail.

The mentioned RF receiver presents power demands that are known and serve as a goal to be achieved by the power output capabilities of the system. The design was adjusted to meet the power requirements having in mind the predicted outputs of different piezoelectric transducers, which vary with the vibration conditions to which they are subjected. These variations were taken into account in order to understand if typical vibration levels generate enough energy in the chosen piezoelectric transducers for the energy harvesting system to be able to meet the power demands of the RF receiver.

## 1.2 – Structure

After this introductory chapter, this thesis contains five chapters, with the contents that are summarised in this section.

## **Chapter 2 – Towards self-powered Wireless Sensor Nodes**

The second chapter approaches the concept of synergy between wireless sensor networks and energy harvesting. A comparison of typical WSN power demands and energy harvesting power outputs proves the relevance of this type of techniques as a solution to power these devices. The main energy harvesting techniques are briefly presented, with special focus on the piezoelectric case. The RF receiver that is to be powered by the designed system is briefly presented, along with its power requirements.

## **Chapter 3 – Energy Harvesting from Piezoelectric vibration transducers**

The particular case of energy harvesting from piezoelectric sources is explored in detail in this chapter. The equivalent circuit for the inertial piezoelectric transducer is presented, after which some examples of passive and active rectifiers are introduced. The chapter ends with the presentation of the several types of DC-DC converters and their main characteristics and operation principles.

### **Chapter 4 – Proposed System and Circuit Design**

This is the chapter where the proposed system is presented. A system overview is offered, in which the typical transducer output values are given for different vibration conditions, according to the chosen transducer family's datasheet. The system overview also includes the dimensioning of the system's external components. After this, the rectifier is presented, along with the dimensions of its devices and the considerations made for the sizing process. The presentation of the DC-DC converter is separated into three parts, each one including schematics and sizing: the switch, the comparator and the clock generator circuit.

#### **Chapter 5 – Electrical Simulations and Layout**

The electrical simulations, and the main conclusions they lead to, are presented in this chapter. These simulations are divided into two sections: related to the rectifier, and regarding the complete system. For those related to the complete system, some adjustments were tested in the load requirements and transducer predicted outputs, in order to test the system's versatility and overall performance under different conditions and requirements.

## **Chapter 6 – Conclusions**

Some conclusions are finally offered in the last chapter, followed by some future work suggestions.

## 1.3 – Contributions

This thesis originated from an experimental validation that was done for the operation of a commercially available piezoelectric transducer. This study provided insight related to piezoelectric energy harvesting and resulted in a publication in the 5<sup>th</sup> Doctoral Conference on Computing, Electrical and Industrial Systems (DoCEIS) 2014, entitled "Piezoelectric Energy Harvester for a CMOS Wireless Sensor".

The study of low-voltage techniques resulted in another publication in the same conference, entitled "Stability Improvements in a Rail-to-Rail Input/Output, Constant Gm Operational Amplifier, at 0.4 V Operation, Using the Low-Voltage DTMOS Technique".

The multidisciplinary project in which this thesis is integrated includes the design of an RF receiver that is to be supplied by the proposed energy harvesting system. The design of this receiver was done having in mind this type of power supply and its requisites became the energy harvesting system's power output goals. An article regarding this RF receiver, entitled "A Low-Voltage LNA and Current Mode Mixer Design for Energy Harvesting Sensor Node" was published in the 21<sup>st</sup> Mixed Design of Integrated Circuits & Systems (MIXDES) conference, 2014.

The previous paper resulted in an invitation to publish in the International Journal of Microelectronics and Computer Science. A new contribution entitled "Co-design of a Low-power RF Receiver and Piezoelectric Energy Harvesting Power Supply for a Wireless Sensor Node" was submitted for that purpose. This publication approaches a System on Chip concept that includes the RF receiver and the piezoelectric energy harvesting power supply.

2

# **Towards self-powered Wireless Sensor Nodes**

The concept of synergy between wireless sensor networks and energy harvesting is presented in this chapter.

In section 2.1, a system overview is offered, including an introduction to wireless sensor networks' applications, structure and typical power consumptions. The advantages of self-powered wireless sensor nodes in relation to battery-powered ones are emphasized, and energy harvesting is presented as a solution to guarantee energy self-sufficiency for the sensor nodes, with some typical power output values given for different energy harvesting solutions.

Section 2.2 gives an overall notion of the most important energy harvesting generators, focusing on piezoelectric energy harvesting. This section presents important considerations about the design of piezoelectric energy harvesting power supplies.

The structure and typical power consumption values of the transceivers used in wireless sensor nodes are introduced in section 2.3. The Low-voltage RF receiver that is intended to be supplied by the energy harvesting system is briefly presented, and its power requirements are highlighted.

## 2.1 – System Overview

There are many applications in which physical or environmental information is scattered and needs to be collected by sensors in order to be used and processed. Some examples may be catalogued in four main areas: environmental monitoring, industrial monitoring, health care monitoring and military monitoring. The sensors are usually connected by a wireless network, commonly referred to as a Wireless Sensor Network (WSN). Figure 2.1 presents some examples of applications for WSNs.

Figure 2.1: Wireless Sensor Network Applications

Concerning the environment, there are several physical conditions and quantities that are often measured, such as temperature, humidity, radiation and the presence of certain gases, just to name a few. The measurement of these quantities or properties over widely scattered areas allows forest fire detection, air pollution monitoring, weather sensing capabilities, water quality monitoring or even radiation levels monitoring in areas adjacent to nuclear power plants. Industrial environments often include restricted or hazardous areas containing important machinery that needs to be under constant supervision, in order to monitor equipment and operation conditions. That supervision is made possible by sensing and collecting particular physical parameters, in each situation, making use of strategically located devices, which can be subjected to extreme or hazardous environments. The agricultural sector also represents an example of widely scattered industrial areas where it is convenient to collect and process information regarding temperature, humidity and sunlight, for example. Structural Health Monitoring (SHM) is also an important field in which sensors are spread, in this case in structures or buildings, with the objective of monitoring their overall condition and conservation state, analysing changes to the materials, vibration patterns or alterations in geometry.

Health care monitoring consists in collecting physical information regarding a person's body that gives competent medical staff, or even the patient, the ability to define a realistic and real-time medical condition. This information might be, for example, body temperature, heart rate, respiratory rate or blood pressure and the sensors that enable the monitoring can be implanted inside the patient's body or simply be wearable devices.

Among military monitoring applications, measuring acoustic intensity in vast areas may help detect and map explosions or enemy fire, and chemical or biological sensing of the environment can be useful to prevent intoxication and serious damage caused by chemical weapons.

In order to create a WSN, several Wireless Sensor Actuator Nodes (WSAN) are wirelessly interconnected. These are autonomous sensor nodes that collect information making use of their sensors, process that information using their analog-to-digital converters (ADC), microcontrollers (MCU) and additional electronic circuitry and then wirelessly transmit that information through their radio transceivers. These nodes may also be equipped with actuators in order to interact with their environment. The transceivers allow the individual nodes of the network to receive and transmit information, thus connecting them all, forming a WSN.

A standard structure for a single WSAN is presented in Figure 2.2.

Figure 2.2: Structure of a Wireless Sensor Actuator Node

Depending on data rate, range of communication, number of sensors and actuators and processing requirements of each WSAN, just to give some relevant examples, the total power consumption varies for different devices. Table 2.1, [1], presents power consumption values for different commercial sensor nodes and includes some of their specifications.

|                                         | Crossbow MICAz      | Intel Mote 2 | Jennie JN5139       |

|-----------------------------------------|---------------------|--------------|---------------------|

| Radio standard                          | IEEE802.15.4/ZigBee | IEEE802.15.4 | IEEE802.15.4/ZigBee |

| Typical range                           | 100 m               | 30 m         | 1 km                |

| Data rate<br>(kbps)                     | 250                 | 250          | 250                 |

| Receiver con-<br>sumption               | 19.7 mA             | 44 mA        | 34 mA               |

| Transmitter<br>consumption              | 17.4 mA (+0 dbm)    | 44 mA        | 34 mA (+3 dbm)      |

| Minimum<br>supply voltage               | 2.7 V               | 3.2 V        | 2.7 V               |

| Average total<br>power con-<br>sumption | 2.8 mW              | 12 mW        | 3 mW                |

Table 2.1: Power Consumption values for different commercial sensor nodes, [1]

Each WSAN's total power consumption is the sum of the power consumption of all of its modules, which in turn have very different power demands among them. Even if distinct WSANs have different data rates for their wireless communications and their transceivers are not continuously communicating, the wireless transceiver is generally the module with the highest power consumption in the node. Modules like the power management, the microcontroller and the actual sensor also represent a relevant consumption value, as can be seen in Figure 2.3, [2], where the contribution of the most relevant modules in terms of power consumption is presented for two different WSAN devices.

Figure 2.3: Distribution of Power Consumption for two different WSANs, a) sensor node based on the Nordic RF24L01, b) sensor node based on the imec's ULP wireless, data from [2]

The sensor node with the power distribution described on the first graph in Figure 2.3 has an average power consumption of 1.3 mW, and 74% of that power consumption corresponds to the node's wireless transceiver. The second graph in Figure 2.3 presents the power consumption distribution for a wireless sensor node with an ultra low-power transceiver. This ultra low-power operation is achieved using duty cycling techniques, which consist in switching the transmitter or receiver on only when they need to be working, having them switched off the rest of the time. This is possible because the nodes do not have to be continuously transmitting or receiving information via the transceiver, which allows some energy saving techniques to be employed. The total average power consumption for this second approach is 362  $\mu$ W. Even with the reduction in the power consumption values of the transceiver, this module is still responsible for one third of the total power consumption. Having these two examples in mind, the main conclusion taken from the distribution of the power consumption of a WSAN is that the wireless transceiver is not only a very important module in terms of the creation of the network of nodes but also a crucial module to take into account when considering each node's power consumption. Further attention will be dedicated to these wireless transceivers in section 2.3.

Since the wireless sensor nodes must be energetically autonomous, they must be powered individually. Their wireless characteristics allow them to be installed in virtually any place inside a reasonably sized area, dependent on their communication range. The freedom of operation in a vast area given to the devices by their wireless capabilities would be compromised if they had to be powered by an external source, using wires, so the common solution to power these nodes is to use batteries. Even if they address the wireless operation issue, batteries have limited supplies of energy and must be replaced after they are depleted, which happens in a time interval that is much smaller than the typical lifetimes of the wireless sensor nodes they power. Replacing a battery for a WSAN can be a difficult and consequently expensive procedure, especially if the nodes are situated in hard-to-reach locations, as many of the WSN applications demand.

In terms of powering a wireless sensor node, the ideal situation is having a node that is self-sufficient in terms of energy, or self-powered. This means that the node is installed in its designed operations position and is able to remain there, autonomous and unattended, during its entire lifetime. This is often referred to as the place-and-forget concept, and it is made possible by energy harvesting.

There is residual energy present in many of the different environments where WSANs need to be installed. This energy can be present in many different forms and have numerous sources but, for the sake of definition, residual energy can be described as energy that is present and would otherwise not be used. Its origin may be light, thermal gradients, electromagnetic radiation or movement of different natures like rotation, vibration or water and air flow. Energy harvesting power supplies deal with the challenge of scavenging this residual energy and making it available to the circuits they supply. Table 2.2 presents some power supply capabilities of different types of energy harvesting generators, which will be explored with greater detail in section 2.2. Having its values compared with the ones presented in Table 2.1, this table leads to the conclusion that these harvesting power supplies have typical power densities that guarantee that they can provide sufficient power to be able to supply wireless sensor nodes, as long as the nodes and power supplies are carefully adjusted and matched.

| Source type                                   | Reference | Typical power density [3]   |

|-----------------------------------------------|-----------|-----------------------------|

| Solar                                         | [4]       | $10 \text{ mW/cm}^2$        |

| Thermal                                       | [5]       | $1 - 10 \text{ mW/cm}^3$    |

| Vibration; Piezoelectric                      | [6]       | 0.1 – 10 mW/cm <sup>3</sup> |

| Vibration, running person;<br>Electromagnetic | [7]       | $0.1 - 0.8 \text{ mW/cm}^3$ |

Table 2.2: Typical power output densities for different energy harvesting solutions

The typical power density values for the different energy harvesting techniques allow comparison by stating power output in terms of volume occupied by the transducer (for the solar energy harvesting type, the power density value is given for each square centimetre of solar cell).

There are many considerations that have to be made in order to fully characterise the power outputs of different energy harvesting generators. The examples given in Table 2.2 serve the purpose of demonstrating how the power outputs of several energy harvesting solutions may be matched with the power requirements of some wireless sensor nodes. However, the power output values depend, for example, on the loads that each implementation uses in order to test the generator, and these loads vary from one implementation to the other, making comparisons difficult and inequitable. Additionally, some values represent the power output after conditioning, suffering from a reduction due to the converter's efficiency; others are simply the power outputs of the transducers, directly connected to an optimal load. Moreover, it should be noted that for testing energy harvesting prototypes and solutions, the sources of energy are emulated in many different ways. Some authors test their prototypes with conditions that are as similar as possible to the real environments. Other authors prefer to optimise their energy source conditions in order to be able to maximise their prototype's conversion efficiency. For these reasons, the calculation of each generator's power output may be highly influenced by these differences in the approach to the tests.

## 2.2 – Energy Harvesting

Energy harvesting techniques have the goal to power small electronic devices, allowing them to be ever more mobile, self-sufficient in terms of power and increasingly maintenance-free. There are four main types of energy harvesting power supplies, and they are distinguished by their source of energy, which can either be solar (or light), thermal, electromagnetic or electromechanical, [8].

Solar energy harvesting uses photovoltaic cells to convert solar radiation into a flow of electrons in the form of direct current. It uses the photovoltaic effect, which consists in the absorption of photons by a semiconductor material that results in the increase in energy of its electrons. Given enough absorption, (superior to the band gap of the semiconductor material), these electrons transit from the valence band and become available to flow.

Energy harvesting from thermal sources is divided into two types, one that makes use of the thermoelectric effect and one of the pyroelectric effect. The thermoelectric effect includes three separate effects, the Seebeck effect, the Peltier effect and the Thomson effect. It consists in the creation of voltage in the terminals of a thermoelectric device when those terminals are subjected to different temperatures, and it is reversible, meaning that an applied voltage will create a thermal difference. It derives from the fact that different metals respond in distinct ways to the application of a thermal gradient, and for that reason create a current in a closed loop consisting of those adjacent metals. In its turn, the pyroelectric effect refers to the creation of a voltage when certain crystalline materials are heated or cooled, which is not the same as the thermoelectric effect, because in this case there is no temperature gradient in the material but rather a uniform distribution of temperature, at each instant, through the whole device.

Electromagnetic energy harvesting, or radio frequency (RF) energy harvesting, consists in scavenging the energy contained in propagating radio waves. This is possible with the use of antennas that receive these RF waves not to collect the information it carries but rather to harvest the energy it contains.

## 2.2.1 – Electromechanical Energy Harvesting

Different kinds of mechanical energy can also be scavenged to power small-scale devices, like the energy present in vibrations, relative movement of objects, airflow and pressure applied to certain structures, among others. This is called electromechanical energy harvesting and it is divided into three types of generators: the electromagnetic generators, the electrostatic generators and the piezoelectric generators.

Before presenting the characteristics of these three types of transducers, it should be noted that they fall into two categories: the ones that operate under direct application of force and those that exploit inertial forces acting on a proof mass, [3]. The concepts behind these two categories will be introduced before some examples are given, for both classifications, inside each of the three types of generators. Direct-force generators rely on mechanical contact with two structures that move relative to each other. By doing so, they apply force on a proof mass that is connected to one of the structures by a suspension with a spring behaviour, to which a damper element containing the transducer is also attached. When the proof mass moves, the damper opposes that motion and the mechanical energy involved is converted to electrical energy by the transducer. Figure 2.4 is a representation of the direct-force generator concept.

Figure 2.4: Direct-force Generator Diagram, adapted from [3]

In the figure, m relates to the actual proof mass, k represents the spring's stiffness, f is the transducer, z(t) is related to the proof mass displacement and  $Z_A$  is the amplitude of the inertial mass motion.

For the fact that direct-force transducers require two points of attachment to two different structures, their use in very small-scale energy harvesting solutions is less desirable in relation to the use of generators that make use of inertial forces acting on a proof mass, since these generators require the attachment to only one moving structure. Inertial generators can have their transducers contained inside compact and enclosed structures, favouring miniaturization, and include a proof mass, also connected to a spring-like suspension and a damper attached to the transducer. For inertial generators, however, the work done against the damper is not caused by the direct application of force to the proof mass, but rather by the relative displacement of the proof mass in relation to the rest of the moving structure, by means of the resistance to the change in its state of motion, *i.e.* its inertia. Figure 2.5 shows a model of a generic inertialforce generator.

Figure 2.5: Inertial-force Generator Diagram, adapted from [3]

For this case, x(t) is the absolute motion of the proof mass and y(t) the absolute motion of the structure. In its turn, z(t) relates to the relative motion between the proof mass and the structure.

#### **Electromagnetic Generators**

The principles that govern electromagnetic generators' operations make use of a direct application of Faraday's law of induction, which states that when subjected to a change in magnetic flux, a coil will have a voltage induced in its terminals. Therefore, they operate using the same principles that are in the core of large-scale electrical generators with synchronous and asynchronous machines.

Paradiso *et al.*, [9], have investigated three different methods of harvesting energy from the human gait, adapting energy harvesting transducers to different shoes. One of these approaches was the one presented in [9], where a rotating electromagnetic generator was installed in the heel of a shoe, and rotated by

the pressing of a lever for each step, as the heel touches the ground. This approach is one example of an electromagnetic generator designed to make use of direct application of force.

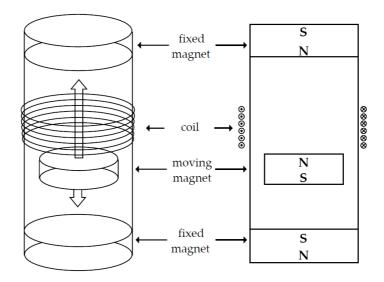

Two examples of electromagnetic generators that are inertial generators are the ones presented in [7] and [10]. The first is a magnetic spring generator and it is suitable for applications involving human walking or slow running. Figure 2.6 shows a conceptual model of the magnetic spring generator.

Figure 2.6: Magnetic Spring Generator Diagram, adapted from [7]

An unattached and free to move permanent magnet is placed inside a tube, with each of its magnetic poles facing one end of the tube. At each of these ends, two other permanent magnets are placed, each of them presenting a matching pole to the moving magnet, so that it is repelled by both ends. A coil is wrapped around the tube, allowing a voltage to be induced in it when the magnet moves inside, an occurrence that is provided by the magnet's relative movement to the tube, caused by its inertia, during the movement of the tube along its own axis.

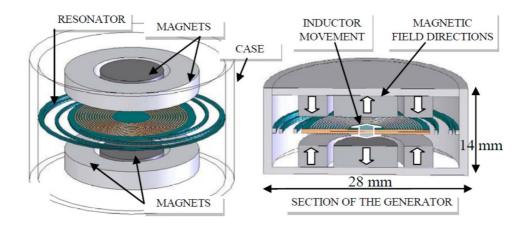

The second example is more suitable to vibrations and consists of a resonator with a movable planar inductor, a cylinder case and two sets of magnets, one at the top of the case and the other at the bottom. Attached to a vibrating object or structure, the cylinder case vibrates with it, making the magnets, which are fixed to it, also move. The planar inductor, which is free to move between the magnets, inertly resists the vibration and consequently exhibits movement relative to the magnets, which induces a voltage in the coil's terminals. Figure 2.7 is a representation of this generator.

Figure 2.7: Resonator Electromagnetic Generator, figure taken from [10]

## **Electrostatic Generators**

Electrostatic transducers use capacitor structures whose charged plates move in relation to one another, when subjected to movement, usually vibration. This relative movement of the charged plates changes the absolute values of the electric field in the capacitor's dielectric, thus guaranteeing energy storage capabilities. The relative movement of the plates can either be the separation and approximation of the plates or the lateral relative movement of two parallel plates, both cases resulting in the variation of the volume of the dielectric between them.

These transducers have two different principles of operation, one in which the charge of the plates is maintained during movement and the other where potential is maintained. In both cases, an electrostatic force generated by the opposition of the attraction of the plates and the relative movement they experience enables the conversion of mechanical energy into stored electrical energy, either by strengthening the electric field, in the constant charge case, or by forcing a flow of charge from the plates, creating a current, for the constant potential case.

Microelectromechanical Systems (MEMS) are very suitable for electrostatic transducer implementations, since they allow integration of the capacitor plates that can be produced at micrometre-scale dimensions. When integrated, these MEMS technology transducers can be included inside the integrated circuits they power, and are subjected to the same physical laws that govern their energy harvesting concepts in a larger scale, making the integration a very interesting possibility for electrostatic transducers.

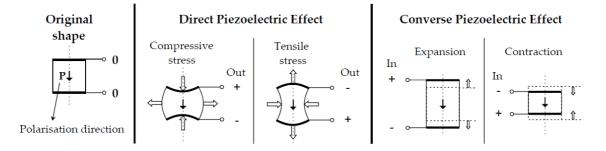

## **Piezoelectric Generators**

While electromagnetic transducers explore the technical implications of Faraday's law of induction and electrostatic transducers make extended use of the properties of mechanically variable capacitors, piezoelectric transducers rely on a property of some crystalline materials and certain ceramics, called piezoelectricity. The piezoelectric effect derives from this property, and refers to the accumulation of electrical charge in piezoelectric materials, when mechanical strains are applied to them. This is what makes piezoelectric materials an interesting prospect for energy harvesting purposes. The effect is reversible, meaning that a mechanical stress, *i.e.* movement, is generated in a piezoelectric material when an electrical field is applied to it. This is called the converse piezoelectric effect. Figure 2.8 shows a representation of these effects.

Figure 2.8: The Direct and Converse Piezoelectric Effects

The most common piezoelectric materials used in energy harvesting generators are lead zirconate titanate (PZT), barium titanate (BaTiO3) and polyvinylidene flouride (PVDF), [1]. PZT is commonly used in vibration energy harvesting because it exhibits high energy conversion efficiency from mechanical to electrical forms.

Piezoelectric generators are usually included in energy harvesting solutions that involve vibrations, so inertial generators are more common among piezoelectric energy harvesting systems than direct-force generators.

An example of a direct-force piezoelectric generator is developed in [11], where a piezoelectric material is placed in the heel of a shoe, inside the sole. Each time the shoe hits the floor, during the walking process, the piezoelectric material is pressed by the person's weight, and generates electric charge that is conveniently processed and stored by the associated power circuit. The same principle of operation has been studied for inclusion of piezoelectric materials under the steps of some busy public stairways or under the pavement of some public spaces with considerable movement, in order to generate electricity.

The most common way to make use of piezoelectric materials for energy harvesting purposes is to include them in inertial generators designed for vibration energy harvesting. These usually consist of a rectangular beam structure that bends in response to ambient vibration and that is clamped in one extremity and free to move in the other. The extremity that is free to vibrate usually has an attached proof mass. The piezoelectric material is added to each of the beam's surfaces, both the upper and the lower surfaces, in the shape of thin rectangular wafers that are completely fastened to the beam's structure. When the beam bends up and down, as a result of the ambient vibration, these wafers suffer mechanical strains that are complementary: if the beam bends upward, the upper wafer contracts, creating a certain potential at its terminals, and the lower wafer is stretched and expands, creating a potential with an opposite polarity. When the beam curves downward, the opposite occurs. Figure 2.9 exemplifies the process, presenting a conceptual diagram of a typical piezoelectric inertial transducer.

Figure 2.9: Diagram of a Piezoelectric Transducer with a beam structure, figure taken from [12]

This is the chosen type of piezoelectric transducer for the energy harvesting system developed in this thesis. For that reason, a detailed analysis of this type of transducer, including some important equations, is presented in section 3.1.

Examples of the use of piezoelectric materials as piezoelectric inertial generators designed to work with ambient vibrations are developed in [1, 13, 14]. Two of these implementations are designed to power wireless sensor nodes and the other is intended to give energetic autonomy to a wireless structural health monitoring system. Regardless of the level of complexity and optimisation of each of these piezoelectric generator developments, some considerations are common to all the works in the literature concerning this subject. One of the most important considerations to have in mind when developing this type of energy harvesting solution is that the vibration that represents the source of energy must be well characterised. The vibration characteristics that must be defined are its frequency, the acceleration and the type of vibration (which relates to whether it consists of sudden bursts, impacts or if it is more or less even and continuous). The knowledge of the characteristics of the source vibration is very important because the piezoelectric transducers of this kind have a natural frequency, or resonant frequency, that can be regulated, mainly by adjusting the proof mass, and that should be matched with the ambient frequency to which it is subjected, in order to maximise the power output. Additionally, piezoelectric transducers' datasheets present their open circuit voltage output values for the

transducers in terms of different vibration frequencies, matched with the regulated natural frequencies, but also in relation to the vibration's acceleration, which is directly related to the amount of physical displacement of the extremity of the beam that is free to move. The greater the acceleration, the greater the displacement of the tip, which results in a more substantial mechanical strain applied to each wafer. All of these considerations are very important in order to correctly design an energy harvesting system with a specific circuit to power, which in turn has its own requirements and specifications. For the three examples given above, a shaker table was used in order to create the vibrations necessary to test the energy harvesting system prototypes. These shaker tables create vibrations with frequency and acceleration values that are defined during tests, allowing a good testing setup for the prototypes.

A real concern for vibration-based piezoelectric energy harvesting design is the difficulty in defining the characteristics of the ambient vibration to which the generators are to be matched. Either way, the transducers present a certain power bandwidth, which corresponds to the bandwidth of frequency values around the resonant frequency to which the power output is still close to the desired value. The same is true for different values of acceleration. Even if the transducer is optimised to work for a certain acceleration value, other values might also guarantee satisfactory power output results. Summing-up, the better the vibration characteristics of the ambient source are defined, the better power output predictions can be made for the generator, after a careful dimensioning of both the transducer and the subsequent power circuit. For cases in which the vibration is less predictable, a piezoelectric energy harvesting solution may also be a good option, as long as it is considered a possibly intermittent power supply, which completely fits applications for some WSN, where nodes don't have to be constantly communicating with each other and can send and receive information only when they have sufficient power available to do so.

# 2.2.2 – Considerations regarding Energy Harvesting Applications

When designing any kind of energy harvesting generator, the target application should be considered from the beginning, not only because different applications are surrounded by different environments with different kinds of residual energy, but especially because the circuit that needs to be powered is the source of specific electrical requirements that need to be met.

Considering the present power output limitations of most energy harvesting solutions, related to the reduced residual amounts of energy that are available in certain environments and the sometimes low conversion efficiencies, the target applications for which they are considered as a potential power supply are generally low-power circuits, intended to operate in an intermittent way, meaning that the circuits operate only after sufficient energy is converted and stored. The integrated circuits that are part of WSANs have been recently developed in order to be less and less power-demanding, with a tendency to reduce supply voltage and current consumption as the integrated technology gets smaller and new power-aware integrated circuit designs are developed. This development has an increasing focus on reducing energy consumption, in part motivated by the interesting prospects given by the rising development of energy harvesting solutions.

The concept of synergy between WSANs and energy harvesting generators is therefore a very interesting and recent focus of several departments and investigators worldwide, in the field of microelectronics. It is fuelling the effort to increase the power outputs and conversion efficiencies of the energy harvesting solutions and also motivating the substantial reduction in integrated circuit power demand even further.

# 2.3 – Low-voltage RF Receiver

#### 2.3.1 – Transceivers designed for Wireless Sensor Networks

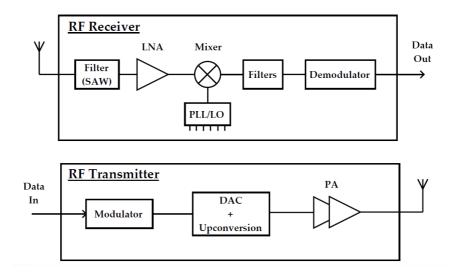

As previously stated in section 2.1, the wireless transceiver is a crucial module for a WSAN, not only because it guarantees the wireless network is created but also in terms of power consumption, since it is generally the module with the highest power consumption in the node. Figure 2.10 presents a generic architecture of a wireless transceiver used in a WSAN.

Figure 2.10: Block Diagram for a WSAN's Wireless Transceiver

The power consumption values of a wireless transceiver depend on some different requirements of the application it serves, like its data-rate, its communication range, its receiver sensitivity or (especially) its transmitter's needed output power, which is related to the communication range and directly influences the power consumption of the transmitter's power amplifier (PA), a block responsible for a considerable amount of power consumption in the transceiver. Transceivers that are intended to work with low-power consumption values are designed to be as simple as they can be, as long as the application's requirements are met. This effort leads to simpler modulation schemes, which in turn allow simpler receiver and transmitter architectures. For applications that involve close-range communications and low data-rates, for example, modulation schemes like the on-off keying (OOK) modulation are chosen, which employ a smaller number of electronic components and blocks. The overall reduction of the circuits' supply voltage also plays an important role in reducing the power consumption.

In order to have a sense of the typical power consumption values of recently developed wireless transceivers for WSN applications, some examples of wireless transceivers are presented in Table 2.3, which contains the power consumption values of their receivers and transmitters, as well as the supply voltage and modulation scheme.

| Block       | Parameters             | [2]    | [15]      | [16]    |

|-------------|------------------------|--------|-----------|---------|

|             | Power con-<br>sumption | 1.8 mW | 4.8 µW    | 0.88 mW |

| Receiver    | Supply voltage         | -      | 0.9 V     | 1 V     |

|             | Modulation             | OOK    | OOK       | ООК     |

| Transmitter | Power con-<br>sumption | 2.3 mW | 1.68 mW   | 2.5 mW  |

|             | Supply voltage         | -      | 1 – 1.2 V | 1 V     |

|             | Modulation             | OOK    | FSK       | ООК     |

Table 2.3: Examples of different WSN transceivers and correspondent power consumption values

# 2.3.2 – RF Receiver to be powered by the Energy Harvesting System

As previously stated in the first chapter, this work's goal is to design and simulate an energy harvesting system that is capable of converting the power output of an inertial piezoelectric transducer and supply a low-power RF receiver that was part of the same multidisciplinary project, with the analysis of a prospective WSAN System on Chip (SoC) as the final goal of the joint endeavour. For the reasons that have been explained in this chapter, especially in section 2.2.2, it is important to briefly present the main characteristics and power requirements of the RF receiver that is to be supplied by the energy harvesting system. In this section, the receiver will be briefly presented, having in mind that the most important characteristics that have to be considered are its power requirements.

#### **Receiver's Architecture**

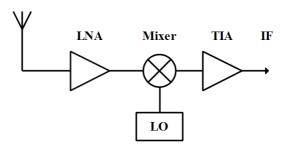

There are several classic RF receiver architectures with different complexities and performances. However, only some of them are suited for low-power applications, namely the Low-IF and the Direct conversion architectures. The receiver under discussion is the one presented in [17], and it follows a Low-IF architecture. Figure 2.11 presents a block diagram of this kind of receiver architecture.

Figure 2.11: Low-IF Receiver Architecture

## **Complete Receiver Circuit**

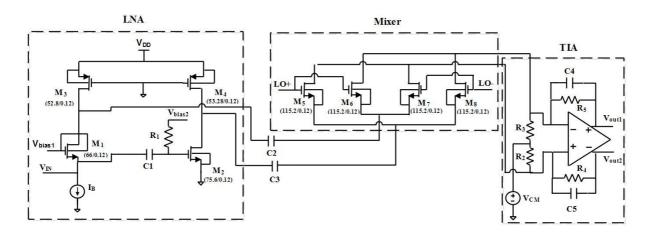

The complete schematic of the receiver implementation is shown in Figure 2.12. The design includes a MOSFET-only wideband balun Low-noise Amplifier (LNA), which includes noise and distortion cancelling capabilities. A passive mixer is also designed, intended to work in current mode. Although the design of the amplifier itself is not included, the system incorporates the transimpedance amplifier (TIA) module, which is essential for the current mode operation of the mixer, as explained in [17].

Figure 2.12: Complete Receiver Circuit with all transistor sizes (W/L) in µm, taken from [17]

Intended to work as a low-power receiver, targeting simple modulation schemes like OOK, the system design includes a passive mixer, which doesn't influence the overall power consumption. Since low power consumption was a major requirement for this receiver, as it was intended to work in an energy harvesting supplied WSAN, the design of the LNA was successfully optimised to work with a 0.6 V supply voltage, a value that represents half the supply voltage for which some important works in the literature were designed, namely the works that served as a starting point for the actual design of the LNA, like the one presented in [18].

#### **Receiver's Power Requirements**

The important considerations to have in mind in order to successfully design an energy harvesting power supply for this receiver circuit are directly related to its power consumption and its supply voltage.

As previously stated, the intended supply voltage is 0.6 V. This means that in order to be able to supply this circuit with satisfactory results, the power supply must guarantee a 0.6 V output to be connected to the receiver's power supply rail. Given the simplicity of the actual design and the precise optimisations that were made for the receiver to be able to work at a 0.6 V supply, the power supply must be designed to deliver a 0.6 V regulated output with as little ripple or variation as possible. This is a very important and decisive requirement, and it will be explored with more detail in the fourth chapter. This concern is directly related to the receiver's low Power Supply Rejection Ratio (PSRR), which is a consequence of the design's simplicity. For these reasons, the energy harvesting power supply's output must be regulated with considerable precision.

Regarding the power consumption, the receiver presents a 1.95 mW value for the joint operation of the LNA and mixer. This value represents the average power consumption of these two receiver modules. It is directly calculated as the sum of the currents flowing in the two LNA's stages, approximately 1.63 mA each, times the voltage supply. The mixer, being passive, does not contribute directly to this calculation. This 1.95 mW value refers to the consumption of the designed receiver modules. However, the calculation does not include the power consumption of the TIA or the local oscillator (LO). Nonetheless, an approximation of the receiver's total power consumption had to be made, because the goal is to eventually supply an entire receiver with the energy harvesting power supply. The estimation that was made was that the entire receiver would consume approximately 10 mA from the power supply, during operation. So that was the figure taken into consideration for the dimensioning of the power supply. During operation, the receiver would request 10 mA with a 0.6 V voltage supply, which results in an estimated power consumption of 6 mW.

Table 2.4 summarizes the receiver's power requirements.

|                   | LNA + Mixer | Complete Receiver |  |  |

|-------------------|-------------|-------------------|--|--|

| DC current        | 3.26 mA     | 10 mA             |  |  |

| V <sub>DD</sub>   | 0.6 V       | 0.6 V             |  |  |

| Power Consumption | 1.95 mW     | 6 mW              |  |  |

Table 2.4: Summary of the RF Receiver's Power Requirements

3

# Energy Harvesting from Piezoelectric vibration transducers

The main modules that constitute a piezoelectric energy harvesting power supply are presented in this chapter, including some relevant examples.

An overview of the piezoelectric energy harvesting power supply is offered in section 3.1. This overview introduces the system's modules.

Section 3.2 presents the equivalent circuit of the inertial piezoelectric transducer, as well as the most important equations that model its operation.

Different types of rectifiers are presented in section 3.3, divided by the passive and active categories. The rectifier designs and correspondent equations are presented, and each rectifier's operation is modelled having the piezo-electric transducer's equivalent circuit connected to its input.

The most important types of DC-DC converters are approached in section 3.4, giving special focus to linear regulators and offering the main concepts that govern the operation of switched capacitor converters and magnetic converters.

# 3.1 – Piezoelectric Energy Harvesting Overview

For the case of inertial piezoelectric energy harvesting, the piezoelectric transducer converts residual mechanical energy, present in vibrations, into electrical signals, by means of its piezoelectric properties. These electrical signals typically consist in a varying output voltage, usually in the form of irregular voltage bursts. These are *AC* periodic power signals, with the same frequency as the vibration source. As previously stated in subsection 2.2.1, the ambient vibration's most important characteristics are its frequency and acceleration. While the vibration frequency defines the output signal's frequency, the vibration's acceleration is what sets the output signal's magnitude, often characterised by the output voltage amplitude values. The piezoelectric transducer can be electrically modelled, meaning that it has an electrical model for which the internal parameter values can be changed, namely internal capacitance and impedance, in order to model transducers of different sizes and materials. The input vibration is also characterised in this model by adjusting the model's source, most commonly a current source, in terms of frequency and amplitude.

For the fact that the output of the transducer is an *AC* signal, an AC-DC converter is needed right after the transducer. This module is a rectifier, preferably a full-wave rectifier, so that the transducer's output energy can be scavenged to the full extent. Passive rectifiers rely on diodes connected in different configurations. Mainly because of the voltage drop at each diode's terminals, the passive rectifier's power efficiency is lower than the efficiency achieved with active rectifiers, which operate using actively controlled switches, usually MOSFET transistors or Bipolar Junction Transistors (BJT). These switches present a substantially lower voltage drop when compared to the diode case. The rectifier's output presents a *DC* signal, which means that there is unidirectional current flow, but not a constant voltage. In order to make this output voltage as constant as possible, a capacitor is usually added at the rectifier's output, so that an output voltage smoothing can be implemented. Even with the added capacitor, the output presents a voltage ripple that depends on the capacitance value and load current. Adding to the typically undesirable voltage ripple, this

rectifier's output presents an average voltage value that varies with the input's amplitude values, failing to guarantee a stable and constant output during voltage amplitude variations of the unstable *AC* input. For these reasons, and for the fact that the load circuits need to be fed at specific and regulated voltage values, a DC-DC converter is needed after the rectifier.

The DC-DC converter is responsible for converting the *DC* signal coming from the rectifier's output to a different voltage level. The converter's output is regulated, meaning that it delivers a constant voltage output value, with minimum voltage ripple. The converter's output requirements are set by the circuits that represent the energy harvesting system's load. The target output voltage is the load's required supply voltage, which should be as constant as possible, to ensure reliable operations. Electronic DC-DC converters used for piezoelectric energy harvesting systems may be linear regulators, switched capacitor converters (referred to as charge pumps), or magnetic converters, which rely on inductors (called step-down or buck and step-up or boost).

After rectification, DC-DC conversion and voltage regulation, the energy is then stored in the energy storage device, often chosen as a supercapacitor. Supercapacitors are double-layer capacitors with high capacitance values, that can be charged and discharged faster than batteries and store much more energy per unit mass than electrolytic capacitors. As previously mentioned, the load circuit is intended to operate only after enough energy is converted and stored. Typical WSAN applications present this intermittent operation.

Figure 3.1 presents a simple block diagram of a typical piezoelectric energy harvesting system.

# 3.2 – The Piezoelectric Transducer

Inertial piezoelectric transducers with a beam structure, introduced in subsection 2.2.1, are the type of transducer that is considered for the designed energy harvesting system that will be presented in the fourth chapter.

As previously stated, these transducers have a resonance frequency (also called natural frequency) that represents the optimal vibration frequency for scavenging mechanical energy contained in vibrations. This means that when the vibration to which the transducer is subjected has a frequency that is close to its resonance frequency, the power output is maximised. This resonance frequency is a characteristic of the piezoelectric transducer, and can be tuned by adjusting its proof (or tip) mass, as explained in [19]. From a mechanical energy conversion point of view, a transducer of this kind should have its tip mass adjusted so that its natural frequency matches the typical predicted vibrations frequencies to which it will be exposed in its destined environment.

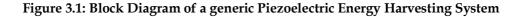

If the piezoelectric transducer vibrates at a frequency that is close to its resonance frequency, the piezoelectric wafer can be modelled by its equivalent circuit, shown in Figure 3.2, where  $i_p$  is the *AC* current source, C<sub>i</sub> the transducer's equivalent internal capacitor, R<sub>i</sub> the internal resistance and  $V_{oc}$  the open circuit voltage at the transducer's output, [20, 21].

Figure 3.2: Equivalent Circuit of a single wafer on an inertial piezoelectric transducer vibrating near the resonance frequency

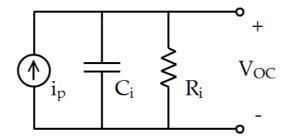

The equivalent circuit presented above refers to a single piezoelectric wafer. As discussed in the previous chapter, some beam structured piezoelectric transducers have two identical piezoelectric wafers, one for each surface of the beam. These wafers have two terminals each, which is why some specific transducers, namely the ones detailed in the datasheet for the Midé Volture<sup>™</sup> piezoelectric transducers family, [19], have four electrical leads. This accessibility to each of the two independent wafers allows two different connections: in parallel, in order to maximise current output, and in series, which maximises voltage output. The equivalent circuit for each of these configurations is given by the parallel or series connection of two of the single wafer equivalent circuits. A parallel configuration, chosen for maximum current output, was experimentally tested in [22], a work that is part of this thesis' contributions. The piezoelectric transducer used for the experimental validation in the referred work was the piezoelectric energy harvester Midé Volture<sup>™</sup> V21BL, presented in Figure 3.3.

Figure 3.3: Midé Volture<sup>TM</sup> V21BL

The parallel equivalent circuit used in [22] is presented in Figure 3.4.

Figure 3.4: Equivalent Circuit of a parallel configuration for a two-wafer piezoelectric transducer

The piezoelectric transducer presented above was a reference for the present work, as well as some of the devices included in its transducer family. The most important details regarding these devices that must be retrieved from their datasheet are their electrical characteristics and power output levels.

The internal characteristics of the piezoelectric transducer are modelled by the internal capacitance and resistance values. The *AC* current source generates a sine wave with the vibration's frequency and peak current values that are proportional to the vibration's amplitude, also called tip-to-tip displacement, which translates into how much the beam bends during vibration, a measure directly related to the vibration's acceleration. Equation (3.1) models the transducer's sinusoidal current source  $i_p(t)$ , where  $I_p$  is the current source amplitude and  $\omega = 2\pi f$ , with f as the vibration's frequency in hertz, [20].

$$i_p(t) = I_p \sin(\omega t) \tag{3.1}$$