#### **Edinei Santin**

Engenheiro Eletricista

## A Built-In Self-Test Technique for High Speed Analog-to-Digital Converters

Dissertação para obtenção do Grau de Doutor em Engenharia Electrotécnica e de Computadores

Orientador: João Carlos da Palma Goes, Professor Associado

com Agregação, Universidade Nova de Lisboa

Co-orientador: Luís A. Bica Gomes de Oliveira, Professor Auxiliar,

Universidade Nova de Lisboa

Júri:

Presidente: Prof. Doutor Paulo da Costa Luís da Fonseca Pinto

Arguentes: Prof. Doutor Gildas Léger

Prof. Doutor Jorge Manuel dos Santos Ribeiro Fernandes

Vogais: Prof. Doutor Francisco André Corrêa Alegria

Prof. Doutor Nuno Filipe Silva Veríssimo Paulino Prof. Doutor João Carlos da Palma Goes

Setembro 2014

| A Devile In Colf There The leading for High Council Application Divited Comments                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A Built-In Self-Test Technique for High Speed Analog-to-Digital Converters<br>Copyright © 2014 by Edinei Santin, Faculdade de Ciências e Tecnologia, and Universidade Nova de Lisboa                                                                                                                                                                                                                                                                                                                                     |

| A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objectivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor. |

| iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## Acknowledgments

During my PhD journey I received direct and indirect contributions, support, advices from many generous persons, to whom I would like to express my indebtedness. Since my memory is not perfect and it fades over time (not as much different as real capacitors and inductors lose their states), I would also like to sincerely apologize those forgotten. For those lucky, I would like to particularly thank:

- Professor João Goes, my supervisor, for his initial contacts, back in 2007, when I attended one semester of my undergraduate studies at Faculdade de Ciências e Tecnologia (FCT) of Universidade Nova de Lisboa (UNL). His strong commitment during that period was crucial for my decision of pursuing a PhD in his research group later.

- Professors João Goes and Luís B. Oliveira, my co-supervisor, for all their support, patience, and collaboration. Under their supervision, I was always treated with consideration and respect. I hope that our friendship continues and that we may collaborate again in the future.

- Professors Rui Tavares, Nuno Paulino, João P. Oliveira, and Adolfo Steiger Garção, all from the Electronics section of the Department of Electrical Engineering of FCT/UNL, for their collaboration and discussion about a diversified range of topics. Professor Rui Tavares was a close collaborator in several research papers, with his strong expertise in the optimization of analog circuits. Also, all laboratory users are in debt with him for all his dedication to keep the laboratory IT facilities (servers, CAD packages, licences, etc.) working properly almost uninterruptedly. Furthermore, he is a genuinely entertaining person, which make any interaction with him very enjoyable.

- Professors Jorge Fernandes and Manuel de Medeiros Silva, from Universidade Técnica de Lisboa. The former for accepting and being a member of my Thesis Accompanying Committee and for providing valuable suggestions for my PhD. The latter for being a passionate and dedicated educator, who proofread several of my initial papers and, with his unique skills, pointed out numerous improvements (e.g. to italicize all variables, to not italicize numbers, to be short and precise during argumentation, etc.). I only fully understood the uniqueness of Professor Manuel de Medeiros Silva when I leaned over the books Introdução aos Circuitos Eléctricos e Electrónicos and Circuitos com Transistores Bipolares e MOS (Fundação Calouste Gulbenkian) he gifted me.

- Professor Guiomar Evans, from Universidade de Lisboa, for collaboration in some research papers and for being a friendly person (with an admirable family).

- Professor Antonio Petraglia and Fernando Barúqui, from Universidade Federal do Rio de Janeiro (UFRJ), Brazil, for the warm reception in their research grout at UFRJ for the two one-week meetings in the scope of a cooperation project, and for the pleasant stay at Rio de Janeiro. One scientific outcome of this collaboration was a journal paper.

- Professor João Baptista dos Santos Martins, from Universidade Federal de Santa Maria (UFSM), Brazil, for accepting me in his Microelectronics research group at UFSM (right in the 2nd semester of my undergraduate studies!) and for being my supervisor and mentor until my graduation. Almost certainly, without that initial opportunity, I would have changed to another discipline other than Electronics/Microelectronis and, as a result, I would not be where I am now. Professor João Baptista was also who encouraged me to attend one semester of my undergraduate studies at FCT/UNL and, most importantly, introduced me to Professor João Goes (that was the "start" of this PhD).

- My colleagues (labmates) Michael Figueiredo, José Rui Custódio, João Ferreira, Blazej Nowacki, Rui Borrego, Ivan Bastos, João de Melo, Somayeh Abdollahvand, Hugo Serra, Carlos Carvalho, and João Casaleiro. It was a pleasure to share the laboratory rooms with them, besides of the numerous discussions we had on distinct subjects. From lunch times to all-night-long preceding days to tapeouts, we lived the extremes of our journey. I had a closer collaboration with Michael Figueiredo, to whom I would like to double thank all the precious help he gave me, from useful CAD tips to several in-depth and productive discussions. Our collaboration eventually resulted in some interesting achievements that were recognized with some international awards.

- My colleague Tiago Domingues for helping me in the layout of the preliminary version of the pipeline stages of the ADC. This help was essential to speed up the final layout of the ADC (one of the building blocks of the proposed system) and gave me more time for extraction simulations and correction of bad layout issues associated with that block.

- Pedro Faria, Rui Monteiro, and Arnaldo Guerreiro, from S3 Group, for providing help to specific issues of the pipeline stages' comparators and to the layout vs schematic verification of the Faraday's input/output cells.

- Francisco Ganhão, José Miguel Luzio, Miguel Pereira, Nuno Miguel Luís, Slavisa Tomic, and Rogério Campos Rebelo for their friendship, and also for many lunch and entertainment moments. Francisco Ganhão and José Miguel Luzio were brilliant colleagues I had the privilege to work with during the first year courses of the PhD program. We made together the acquisition of the "soft skills" more pleasant, with interesting projects, like the communication link between ESA and our hypothetical "Martian rover". Rogério Campos Rebelo was my housemate during more than three years, and during that time, besides of an (almost) harmonious living, I took dislike to his Benfica (always ruined by the referees in his unchanged opinion).

- My Brazilian colleagues Marcelo Dal Alba, Tiago da Silveira, and Taimur Gibran Rabuske for their friendship, dinners together, and some travels to discover Portugal.

- My Family, specially my mother Iracilde Bavaresco Santin, my bother Edgar Santin, and my grandparents João Santin and Teresa Durante, for all their support, encouragement, and love. Even with the yearly-surmountable physical distance between us, they were able to transmit me peace of mind, even when my grandfather had to be hospitalized and, even with speaking limitations, wanted to speak with me on the phone to say he was recovering well and would be recovered within some days (and fortunately it was what happened).

- The Centro de Tecnologias e Sistemas (CTS) of Instituto de Desenvolvimento de Novas Tecnologias (UNINOVA) for being my host institution. The CTS/UNINOVA staff, specially Magui Pereira, Paula Silva, Hugo Sousa, Mário Respeita, Francisco Ferro, and Rosa Rolo, were cooperative and diligent as much as possible.

- The Faculdade de Ciências e Tecnologia (FCT) of Universidade Nova de Lisboa (UNL) for accepting me as a PhD student, and also for providing all the academic facilities (Library, Cantina, etc.) I needed.

- And, finally, the Fundação para a Ciência e a Tecnologia (FCT) of Ministério da Educação e Ciência (MEC) for granting me a PhD grant (SFRH/BD/62568/2009) during four years of my PhD program.

Edinei Santin Caparica, September 2014

## Abstract

As the conversion rate trend of analog-to-digital converters (ADCs) keeps increasing, from the present state of few gigasamples per second range, their testing is becoming progressively more challenging, time-consuming, and costly. Aware to this fact, in this PhD work we investigate a novel solution to this problem. Specifically, we propose to use two small area oscillators inserted into two synchronized phase-locked loops (PLLs) to generate high frequency sinusoidal and clock signals and, on the digital side, to employ straightforward digital signal processing (DSP) techniques to dynamically and functionally test high speed and moderate resolution ADCs. Using this built-in self-test (BIST) approach, the only off-chip component required is a low frequency and stable reference signal (e.g., produced by a ubiquitous crystal oscillator). The DSP techniques for output response analysis rely primarily on spectral computations, which nowadays are available in most system-on-a-chip environment through optimized fast Fourier transform algorithms; hence, reusing of the DSP resources is usually possible. The proposed concept was implemented in an integrated circuit featuring two PLLs for test stimuli generation and an 8-bit 500 MS/s ADC as the device under test, and was validated with silicon measurements. In a 0.13  $\mu m$  CMOS technology, the area overhead introduced by the two PLLs is merely  $0.052 \text{ mm}^2$ .

KEYWORDS: Analog-to-digital converter (ADC), built-in self-test (BIST), high speed conversion, oscillator, phase-locked loop (PLL).

## Resumo

Seguindo a tendência do ritmo de amostragem de conversores analógico/digital (ADCs), que atualmente já adentra sobre a faixa de bilhões de amostras por segundo, o teste destes dispositivos está progressivamente se tornando mais complexo, demorado e custoso. Cientes desta problemática, neste trabalho de doutoramento investigou-se uma solução para tal questão. Especificamente, é proposta a utilização de dois osciladores compactos, controlados por duas malhas de captura de fase (PLLs) síncronas, para gerar sinais de sinusoide e de relógio de alta frequência e, na parte digital, empregar técnicas de processamento digital de sinais (DSP) simples para testar ADCs de elevado ritmo de conversão e moderada resolução dinamicamente e funcionalmente. Empregando esta abordagem de auto-teste (BIST), somente um componente externo para gerar um sinal de referência de baixa frequência e estável (e.g., por meio de um oscilador a cristal) é necessário. As técnicas de DSP para análise da resposta de saída recaem principalmente na computação do espectro, muito utilizada atualmente em sistemas completamente integrado em silício através de algoritmos de transformada rápida de Fourier otimizados. Portanto, a reutilização de recursos de DSP é geralmente possível. O conceito proposto foi implementado num circuito integrado, contendo duas PLLs para geração dos estímulos de teste e um ADC de 8-bit e 500 MS/s como dispositivo sob teste, e foi validado com medições em silício. Numa tecnologia CMOS de  $0.13~\mu m$ , o incremento de área introduzido pelas duas PLLs é de apenas 0.052 mm<sup>2</sup>.

PALAVRAS-CHAVE: Conversor analógico/digital (ADC), auto-teste (BIST), elevado ritmo de conversão, oscilador, malha de captura de fase (PLL).

# Contents

| Acknowledgments |                           |        | vii                                                   |                        |

|-----------------|---------------------------|--------|-------------------------------------------------------|------------------------|

| $\mathbf{A}$    | bstra                     | .ct    |                                                       | xi                     |

| Resumo          |                           |        | xiii                                                  |                        |

| C               | onter                     | nts    |                                                       | $\mathbf{x}\mathbf{v}$ |

| Li              | st of                     | Figure | es                                                    | xix                    |

| Li              | st of                     | Tables | 5                                                     | xxiii                  |

| Li              | st of                     | Abbre  | eviations and Symbols                                 | xxv                    |

| 1               | Intr<br>1.1<br>1.2<br>1.3 | Overv  | ation                                                 | . 2                    |

| 2               |                           | ic Con |                                                       | . o<br>5               |

| 4               | 2.1                       |        | g-to-Digital Conversion Principle                     |                        |

|                 | 2.2                       | `      | ADC Performance Metrics and Corresponding Testing     |                        |

|                 |                           | 2.2.1  | Gain and Offset                                       |                        |

|                 |                           | 2.2.2  | Differential Nonlinearity                             |                        |

|                 |                           | 2.2.3  | Integral Nonlinearity                                 |                        |

|                 | 2.3                       | Dynan  | nic ADC Performance Metrics and Corresponding Testing | . 9                    |

|                 |                           | 2.3.1  | Discrete Fourier Transform and Coherent Sampling      | . 10                   |

|                 |                           | 2.3.2  | Signal-to-Noise and Distortion Ratio                  | . 14                   |

|                 |                           | 2.3.3  | Total Harmonic Distortion                             | . 17                   |

|                 |                           | 2.3.4  | Signal-to-Noise Ratio                                 | . 18                   |

|                 |                           | 2.3.5  | Spurious Free Dynamic Range                           |                        |

|                 |                           | 2.3.6  | Effective Number of Bits                              |                        |

|                 | 2.4                       |        | f Testing                                             |                        |

|                 | 2.5                       | Chara  | cterization versus Production Testing                 | . 21                   |

|                 | 2.6                       | Struct | ural versus Functional Test Approaches                | 23                     |

| 3 | Res  | earch Question                                            | 25         |

|---|------|-----------------------------------------------------------|------------|

|   | 3.1  | Problem Introduction                                      | 25         |

|   | 3.2  | Research Question                                         | 27         |

|   | 3.3  | Preliminary Observations                                  | 27         |

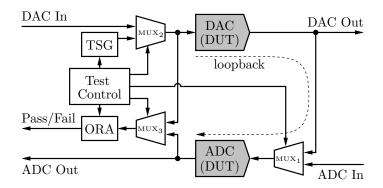

| 4 | Lite | erature Review                                            | <b>2</b> 9 |

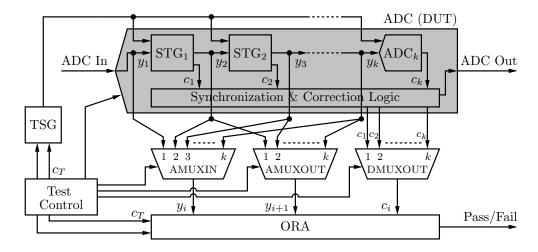

|   | 4.1  | Structural Built-In Self-Test for ADCs                    | 29         |

|   | 4.2  | Functional Built-In Self-Test for ADCs                    | 33         |

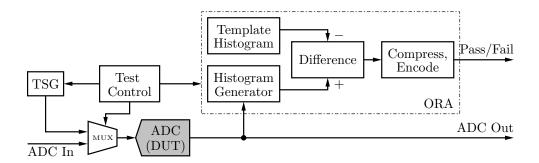

|   |      | 4.2.1 Static Performance BIST Methods                     | 33         |

|   |      | 4.2.2 Dynamic Performance BIST Methods                    | 37         |

|   | 4.3  | Discussion                                                | 45         |

| 5 | Pro  | posed Approach                                            | 47         |

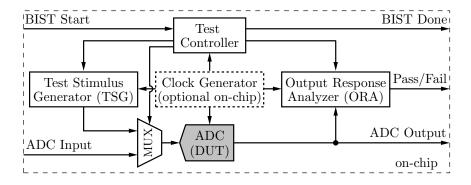

|   | 5.1  | Generic ADC BIST Architecture                             | 47         |

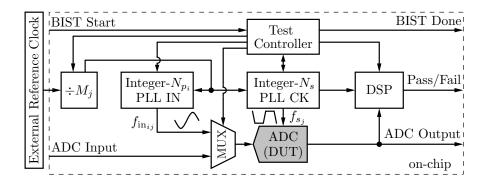

|   | 5.2  | Proposed ADC BIST Architecture                            | 48         |

| 6 | Pro  | totype Implementation                                     | 51         |

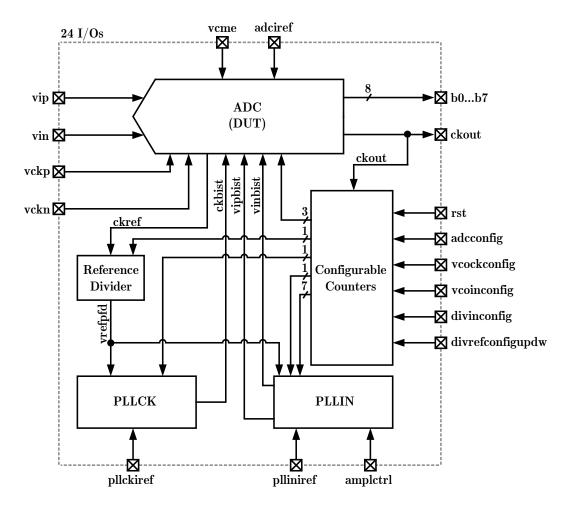

|   | 6.1  | Implemented System Overview                               | 51         |

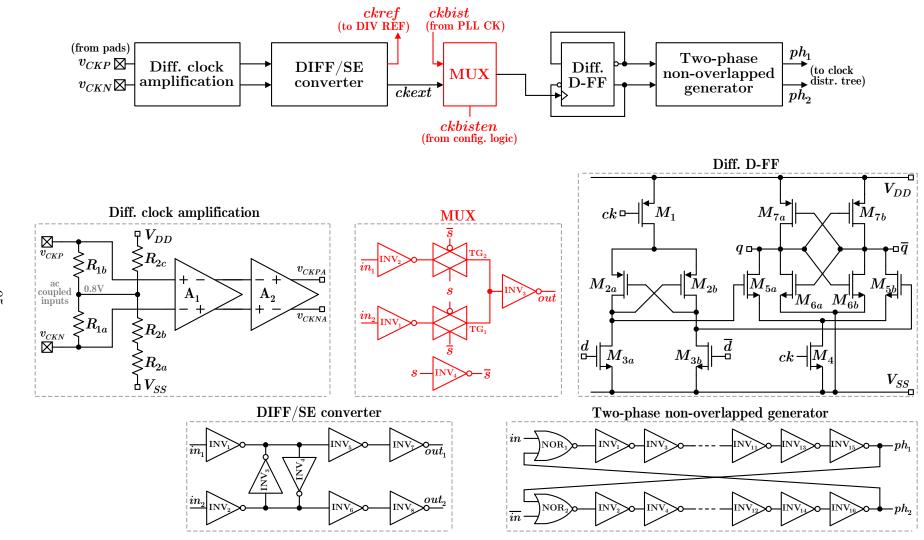

|   | 6.2  | BIST Circuitry: PLL IN, PLL CK, and Interfacing Circuits  | 54         |

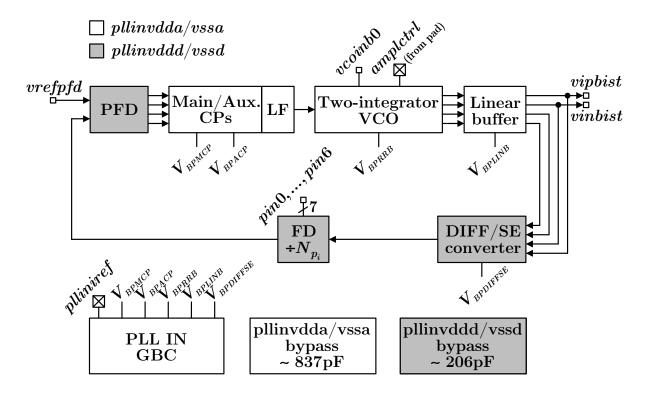

|   |      | 6.2.1 Analog Input Phase-Locked Loop (PLL IN) Overview    | 54         |

|   |      | 6.2.2 Clock Phase-Locked Loop (PLL CK) Overview           | 58         |

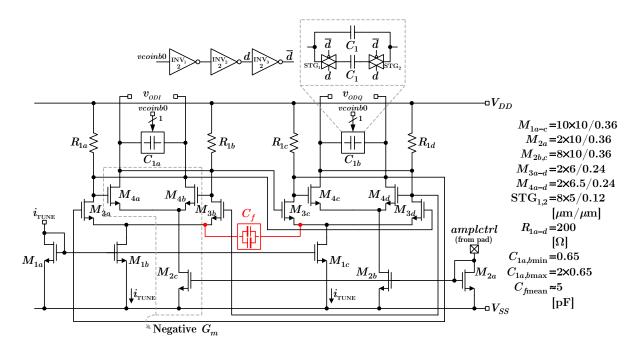

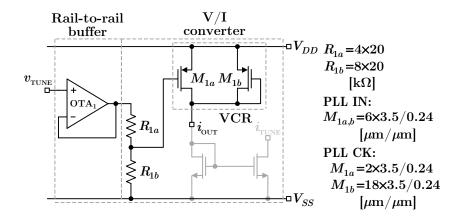

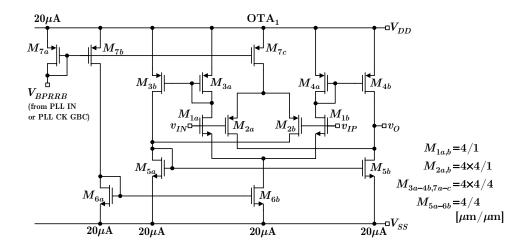

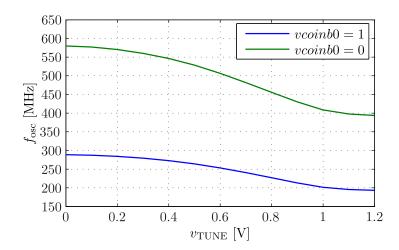

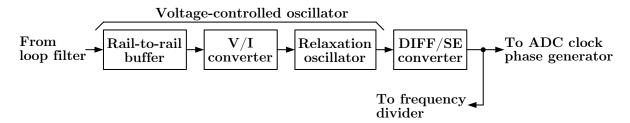

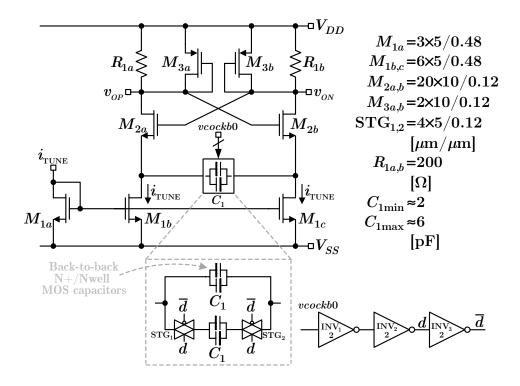

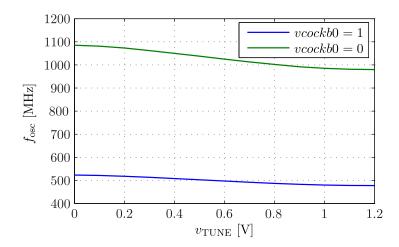

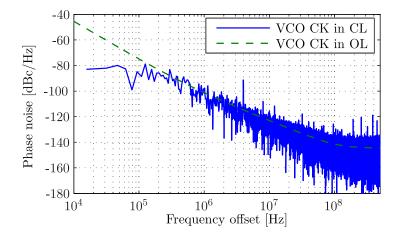

|   |      | 6.2.3 Voltage-Controlled Oscillators                      | 61         |

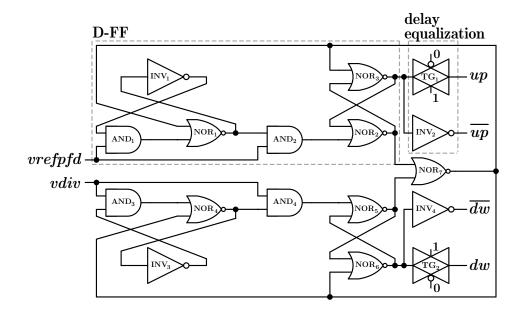

|   |      | 6.2.4 Phase/Frequency Detector                            | 73         |

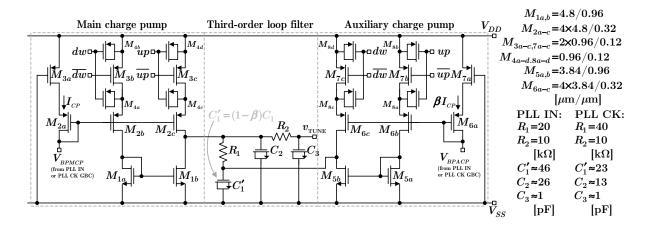

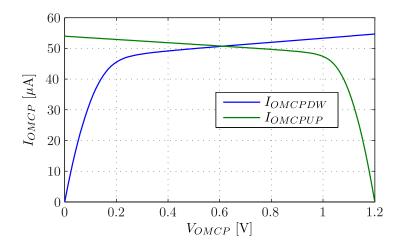

|   |      | 6.2.5 Charge Pumps and Loop Filter                        | 74         |

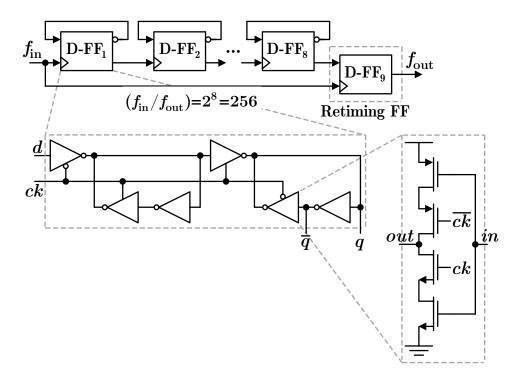

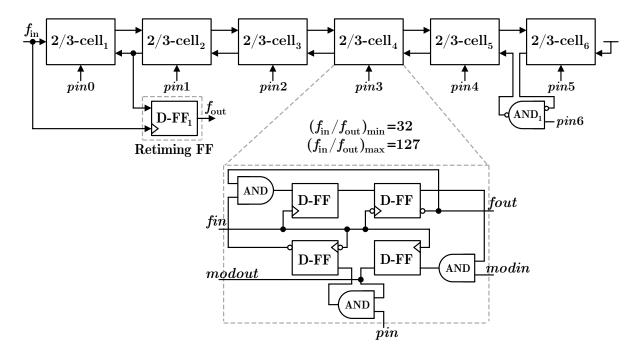

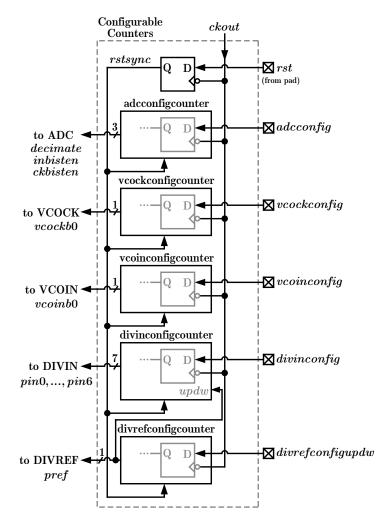

|   |      | 6.2.6 Frequency Dividers                                  | 77         |

|   |      | 6.2.7 Interfacing Circuits                                | 78         |

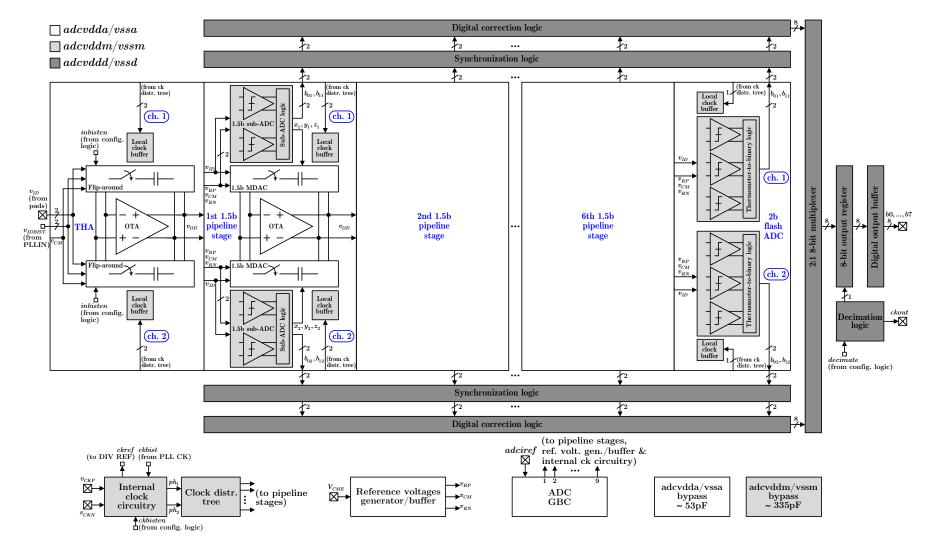

|   | 6.3  | DUT Circuitry: High Speed Pipelined ADC                   | 83         |

|   |      | 6.3.1 Pipelined ADC Overview                              | 83         |

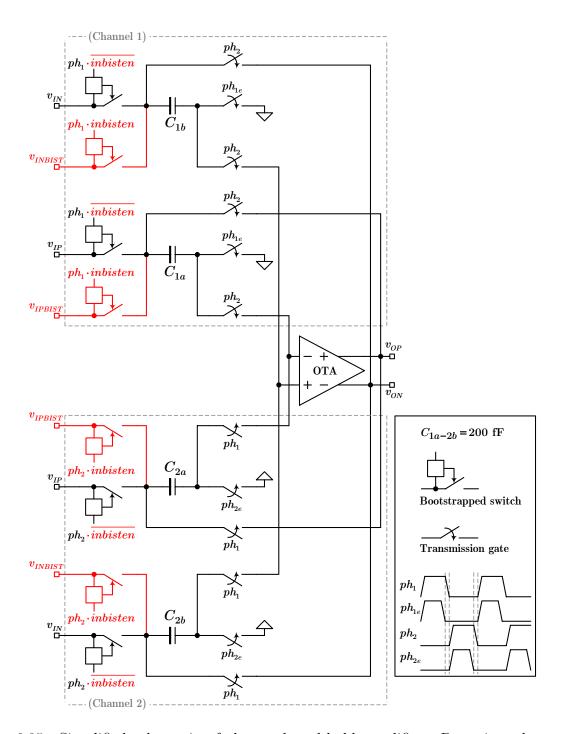

|   |      | 6.3.2 Interfacing Issues                                  | 93         |

| 7 | Exp  | perimental Results                                        | 97         |

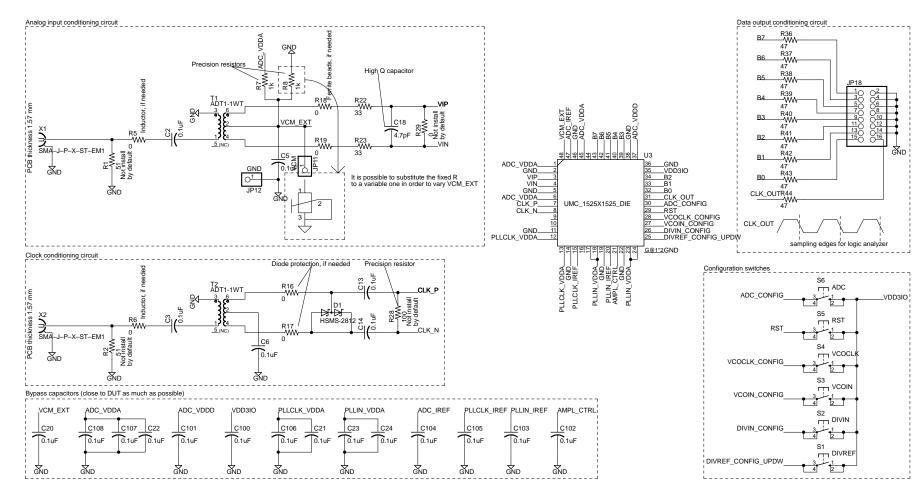

|   | 7.1  | Evaluation Board                                          | 97         |

|   |      | 7.1.1 On-board Analog Input Interface Circuitry           | 97         |

|   |      | U I / I                                                   | 99         |

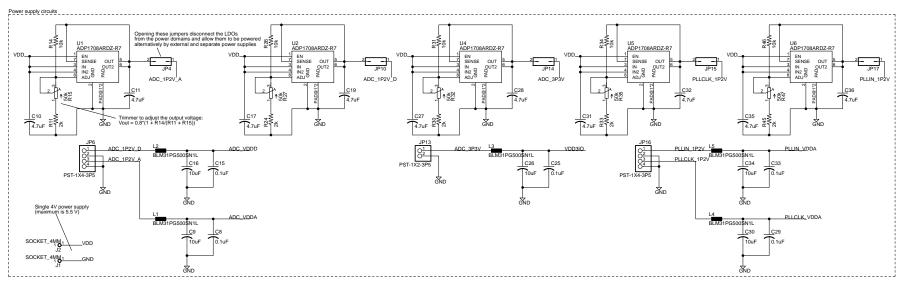

|   |      | 7.1.3 Power Supplies and Biasing Circuitry                | 00         |

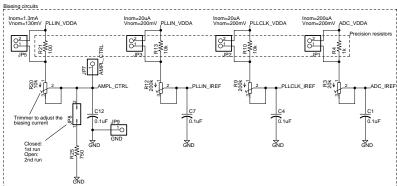

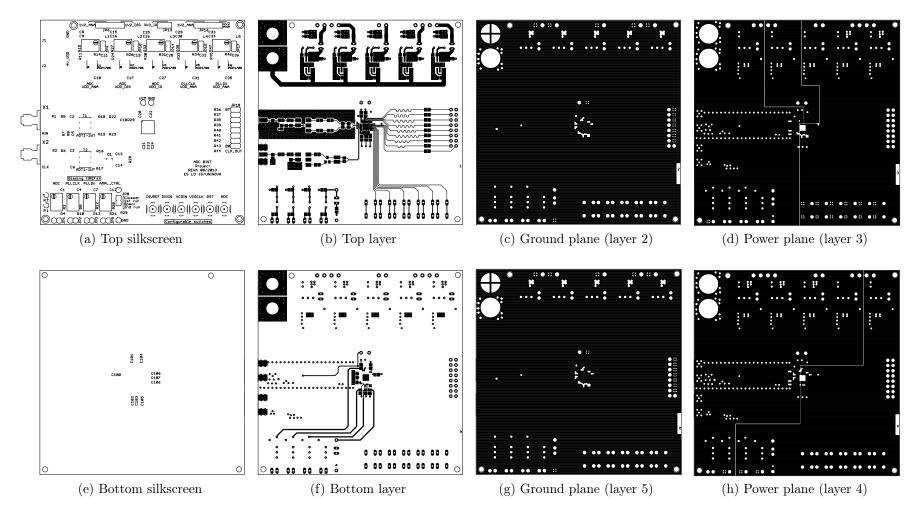

|   |      | 7.1.4 Printed Circuit Board Layout                        | 04         |

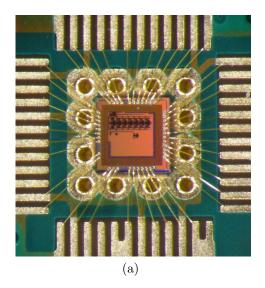

|   | 7.2  | Chip-on-Board Assembly                                    | 06         |

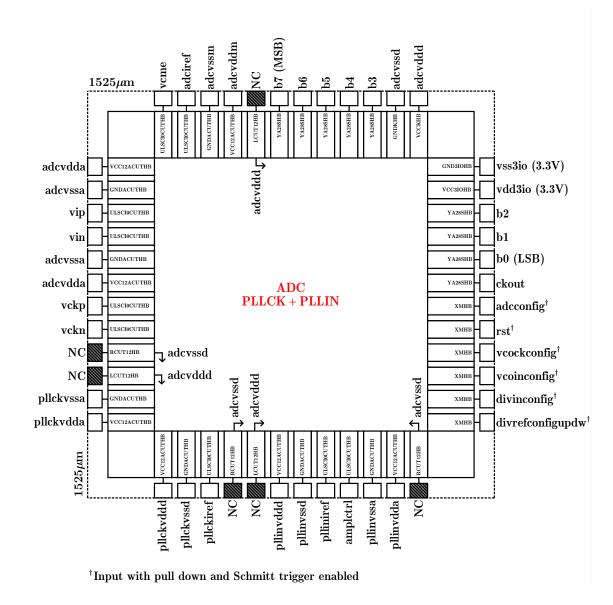

|   |      | 7.2.1 I/O Pad Ring                                        | 06         |

|   |      | 7.2.2 Chip-on-Board Process                               | 09         |

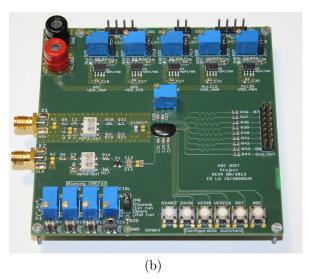

|   | 7.3  | Test Setup                                                | 09         |

|   | 7.4  | Measurement Results                                       | 13         |

|   |      | 7.4.1 DUT with External Analog Input and Clock            | 13         |

|   |      | 7.4.2 DUT with External Analog Input and Internal Clock 1 | 20         |

|   |      | 7.4.3 DUT with Internal Analog Input and Clock            | 26         |

|   |      | 7.4.4 Complementary DUT Measurements                      | 29         |

|   | 7.5  | Comparison and Discussion                                 | 35         |

| 8  | 8.1 Suggestions for Future Work | 137<br>138 |

|----|---------------------------------|------------|

| A  | System Configuration            | 141        |

| Bi | bliography                      | 147        |

# List of Figures

| 1.1  | Overview of the proposed idea                                               |

|------|-----------------------------------------------------------------------------|

| 2.1  | Ideal ADC model                                                             |

| 2.2  | Ideal ADC transfer curve and quantization error                             |

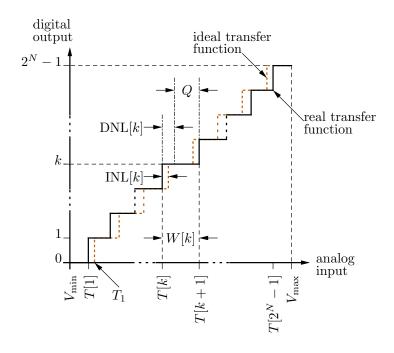

| 2.3  | Independently based DNL and INL definitions                                 |

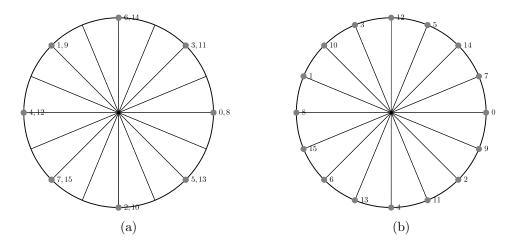

| 2.4  | Two sine phase distributions depending on $N_p$ and $N_s$                   |

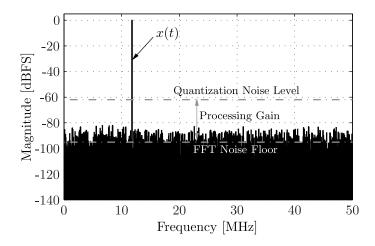

| 2.5  | DFT processing gain                                                         |

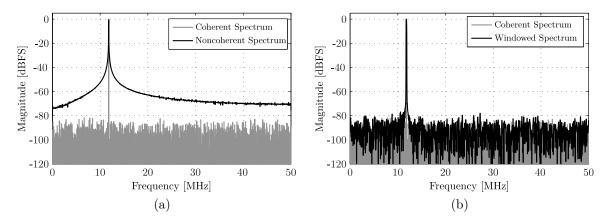

| 2.6  | Noncoherent spectrum versus windowed spectrum                               |

| 2.7  | Windowed sequence                                                           |

| 2.8  | Development cycle of an IC                                                  |

| 2.9  | Setup for characterization and production testing                           |

| 4.1  | DAC/ADC loopback BIST architecture                                          |

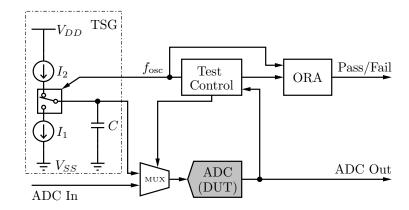

| 4.2  | Oscillation BIST architecture                                               |

| 4.3  | Structural BIST architecture for pipelined ADCs                             |

| 4.4  | HABIST architecture                                                         |

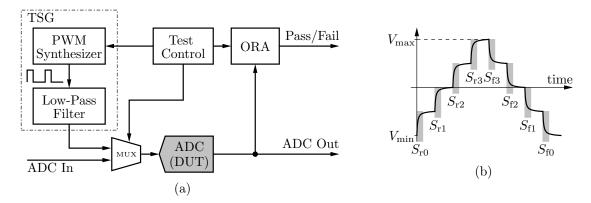

| 4.5  | Polynomial-fitting BIST architecture and low-pass filtered test stimulus 38 |

| 4.6  | OBIST architecture applied to functional testing                            |

| 4.7  | BIST architecture using low accuracy DACs for test stimulus generation. 36  |

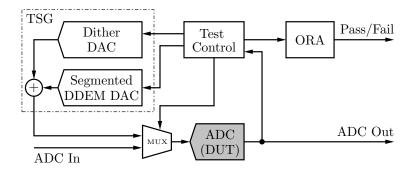

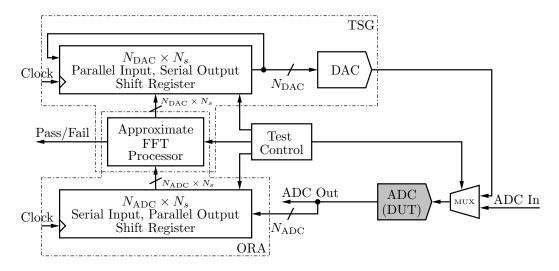

| 4.8  | Simplified MADBIST architecture for ADC testing                             |

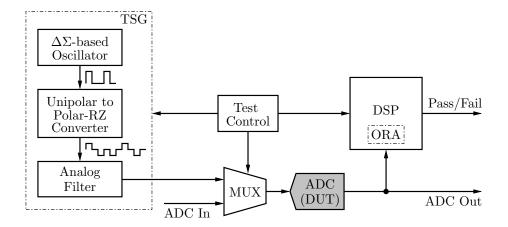

| 4.9  | Finite-length bitstream based test stimulus generator for BIST of ADCs. 40  |

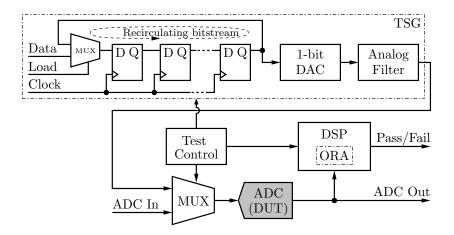

| 4.10 | Test stimulus generator based on ROM and DAC for ADC BIST 4                 |

| 4.11 | FFT-based built-in self-test architecture                                   |

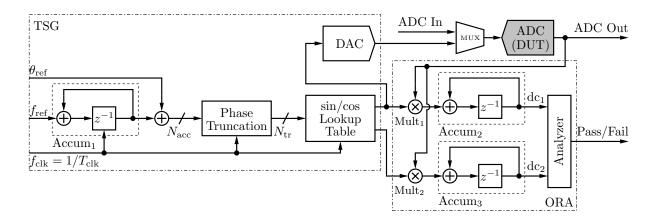

| 4.12 | DDS-based built-in self-test architecture                                   |

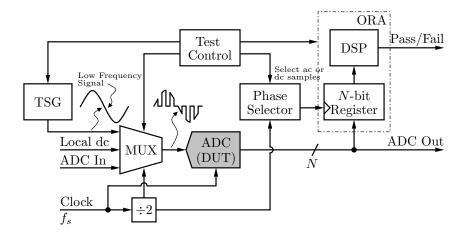

| 4.13 | Built-in self-test architecture with high frequency test stimulus generated |

|      | by mixing                                                                   |

| 5.1  | Generic BIST architecture for an ADC                                        |

| 5.2  | Proposed BIST architecture for coherent testing of high speed ADCs 48       |

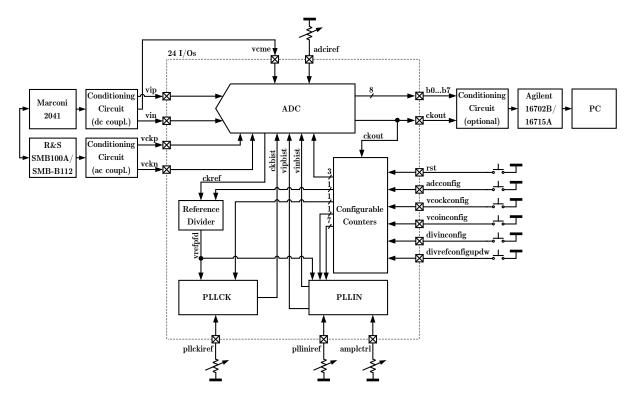

| 6.1  | Overview of the implemented system                                          |

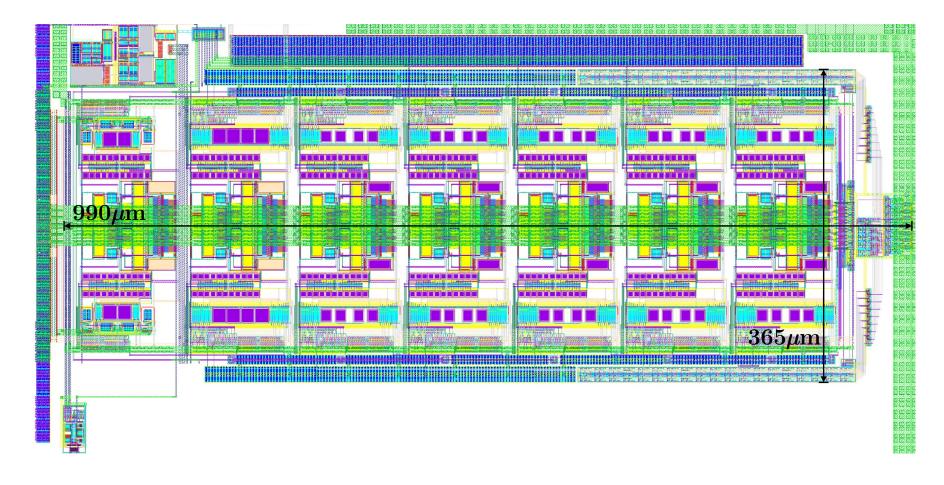

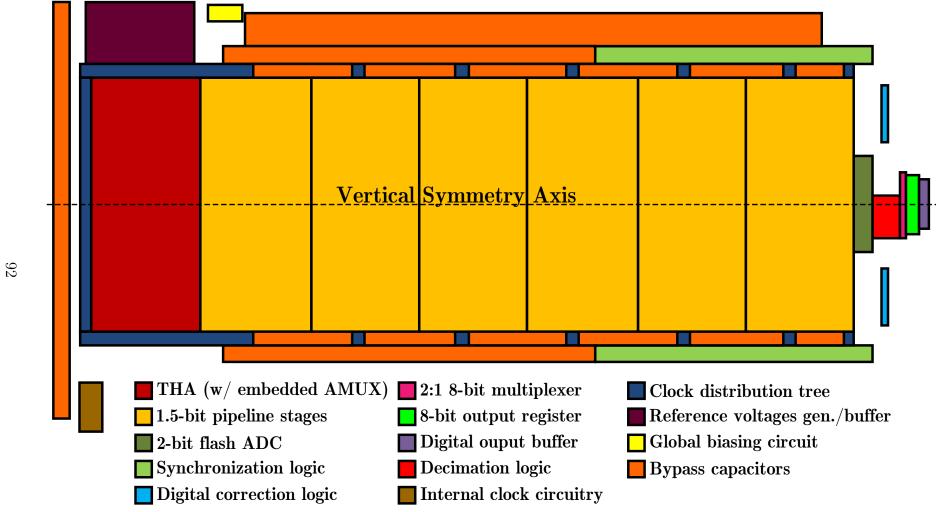

| 6.2  | Top layout view of the implemented system                                   |

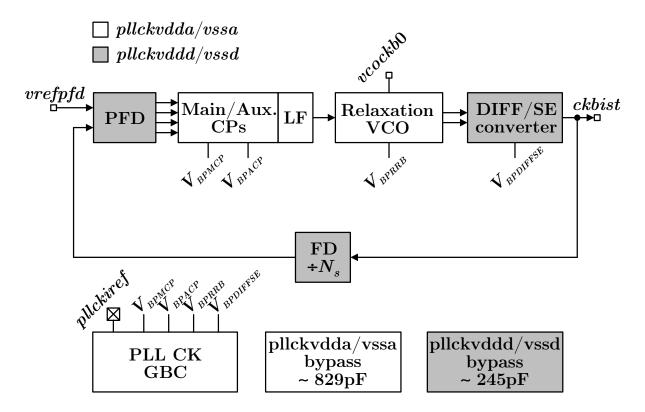

| 6.3  | Block diagram of the analog input PLL                                       |

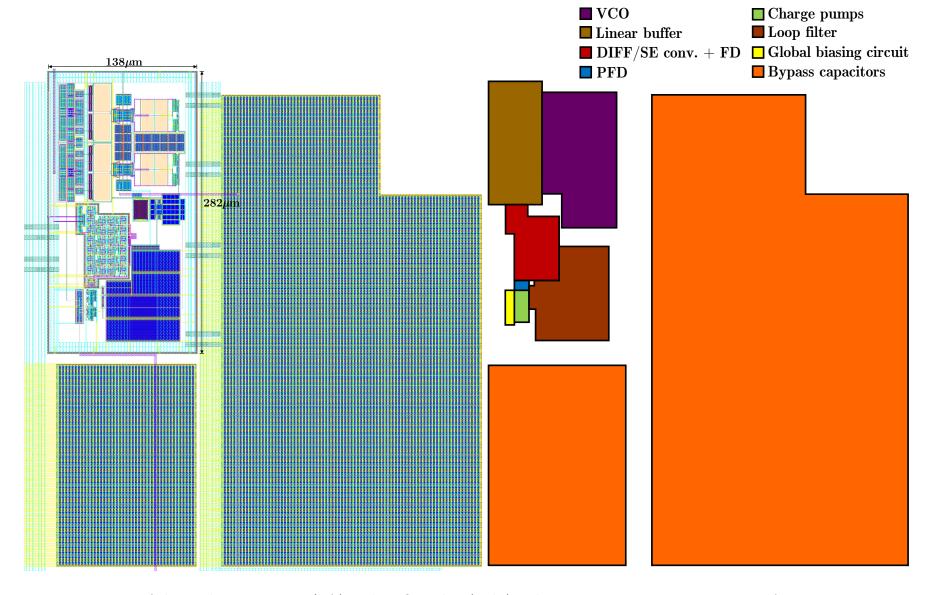

| 6.4  | Layout of the analog input PLL and its floorplan 5                          |

| 6.5  | Block diagram of the clock PLL                                              |

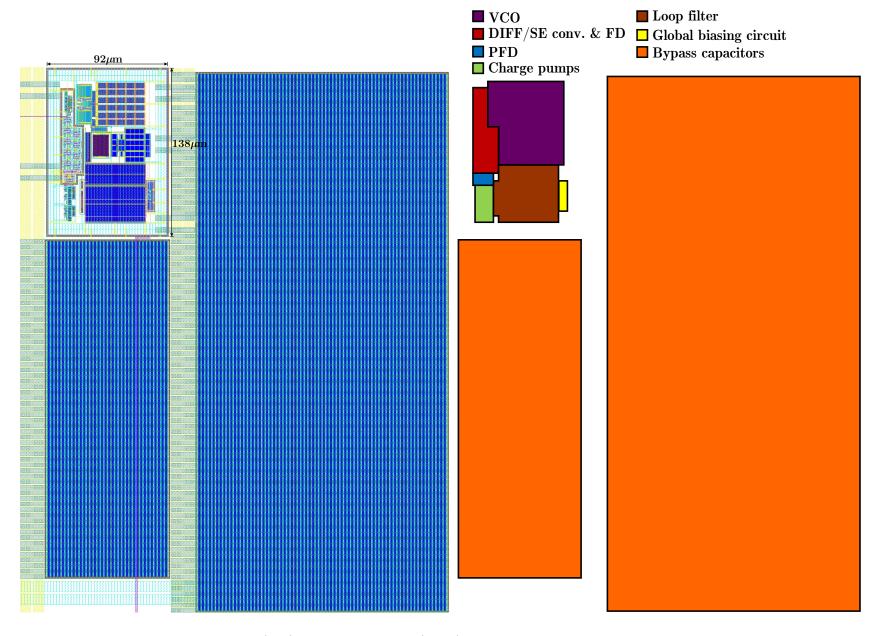

| 6.6  | Layout of the clock PLL and its floorplan                                   |

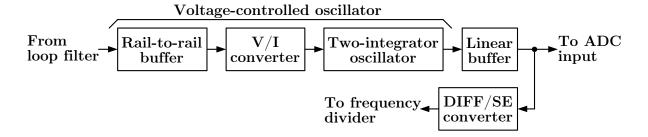

| 6.7  | Block diagram of the two-integrator VCO and related circuits 65             |

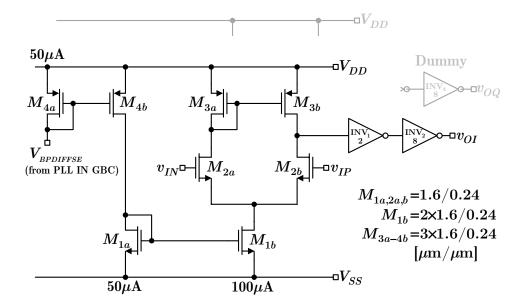

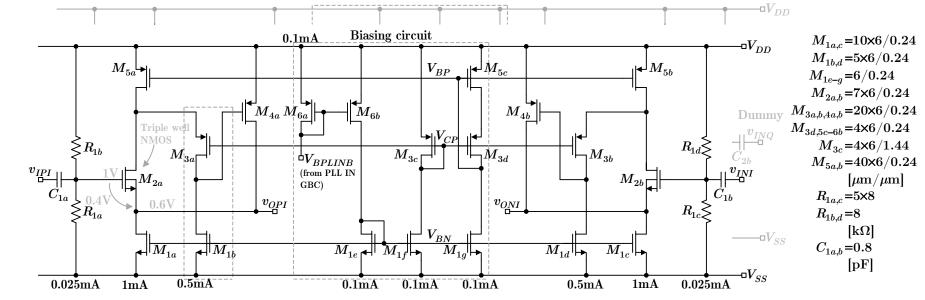

| 6.8  | Schematic of the two-integrator oscillator                                  |

| 6.9  | Schematic of the $V/I$ converter and rail-to-rail buffer                                                                 | j4            |

|------|--------------------------------------------------------------------------------------------------------------------------|---------------|

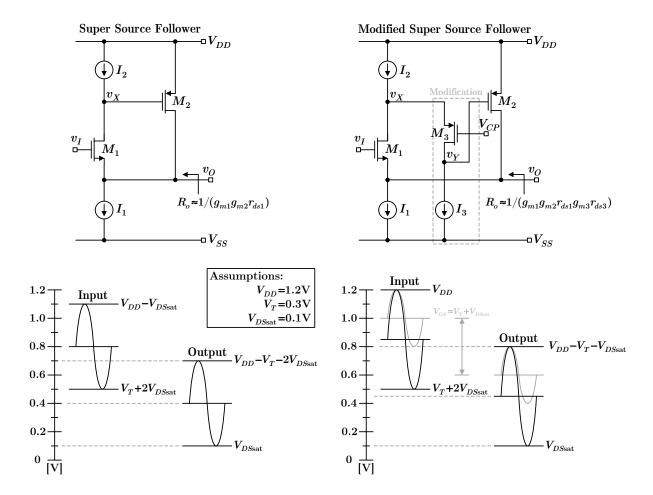

| 6.10 | Detailed schematic of the rail-to-rail buffer                                                                            | 35            |

| 6.11 | Simulated discrete tuning characteristics of the two-integrator VCO 6                                                    | 35            |

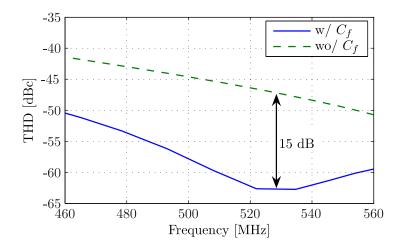

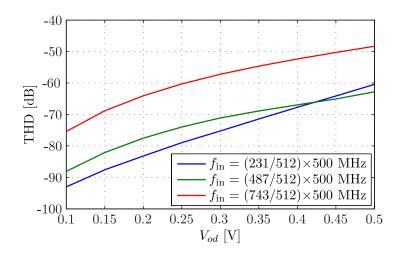

| 6.12 | Simulated output THD of the two-integrator oscillator with and without the filtering capacitor $C_f$                     | 66            |

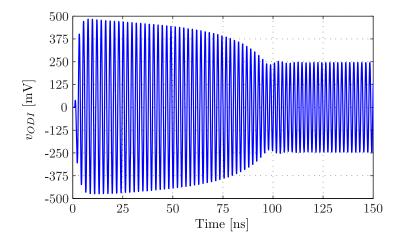

| 6.13 | Simulated start-up of the two-integrator oscillator showing the AAC re-                                                  | <sub>67</sub> |

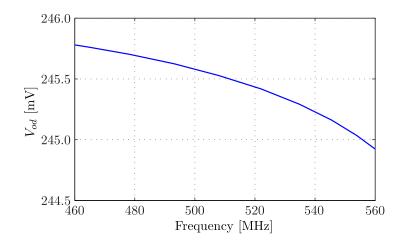

| 6.14 | 1                                                                                                                        | 38            |

|      |                                                                                                                          | 39            |

|      |                                                                                                                          | 39            |

|      |                                                                                                                          | 70            |

|      |                                                                                                                          | 71            |

|      | Simulated phase noise of the relaxation VCO running in open loop and in                                                  | 71            |

| 6.20 | •                                                                                                                        | 72            |

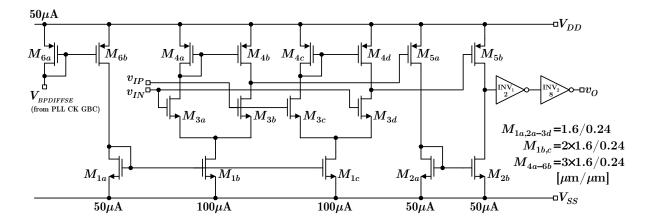

|      |                                                                                                                          | · -<br>73     |

|      |                                                                                                                          | 73            |

|      | Schematic of the phase/frequency detector employed either in PLL IN and                                                  | 74            |

| 6.24 | Schematic of the charge pumps and third-order passive loop filter employed                                               |               |

| e or |                                                                                                                          | 75<br>76      |

|      |                                                                                                                          | 76            |

|      |                                                                                                                          | 77<br>70      |

|      |                                                                                                                          | 78            |

|      |                                                                                                                          | 30<br>31      |

|      |                                                                                                                          | 31<br>32      |

|      |                                                                                                                          | 34<br>34      |

| 6.31 | •                                                                                                                        | 34<br>35      |

|      |                                                                                                                          | 91            |

|      |                                                                                                                          | 91<br>92      |

|      |                                                                                                                          | 94<br>94      |

|      | •                                                                                                                        | 95            |

| 7.1  | Test board schematic: input/output analog and digital signals circuitry 10                                               | )2            |

| 7.2  | Test board schematic: power supplies and biasing circuitry                                                               |               |

| 7.3  | Test board layout                                                                                                        |               |

| 7.4  | Pads distribution around the I/O ring                                                                                    |               |

| 7.5  | Photograph of a wire bonded die before glob top encapsulation and of a completely assembled test board                   |               |

| 7.6  | Test setup                                                                                                               |               |

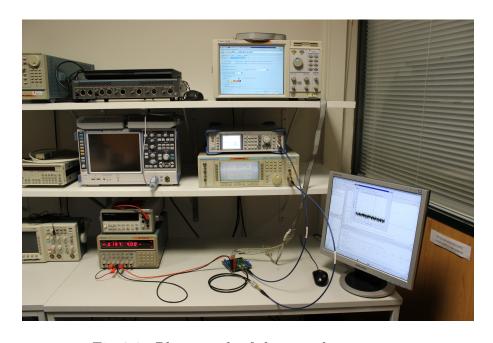

| 7.7  | Photograph of the actual test setup                                                                                      |               |

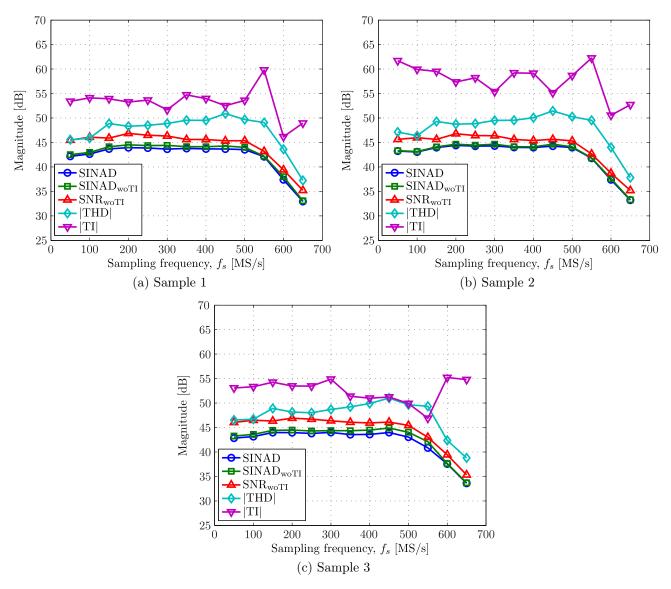

| 7.8  | Measured SINAD, SNR, THD, and TI spur versus $f_s$ at $f_{\rm in} \approx 10$ MHz and                                    |               |

| 7.0  | $V_{\rm in} \approx -0.1$ dBFS for three different samples                                                               | ГQ            |

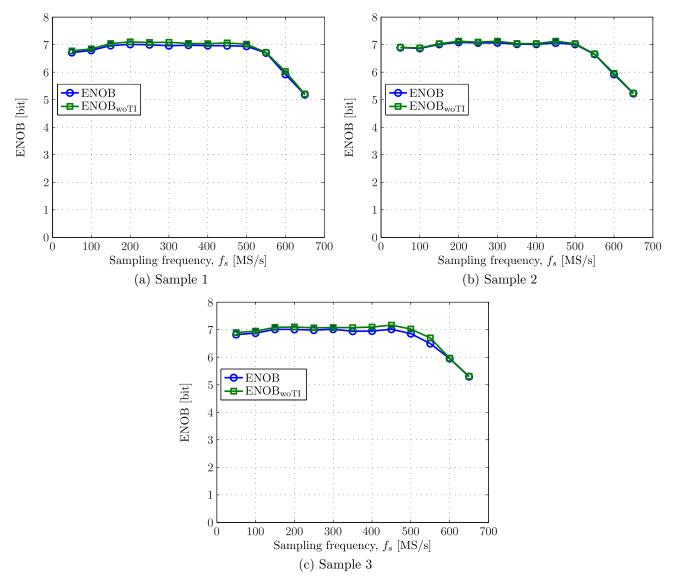

| 7.9  | Measured ENOB versus $f_s$ at $f_{\rm in} \approx 10$ MHz and $V_{\rm in} \approx -0.1$ dBFS for three different samples | 17            |

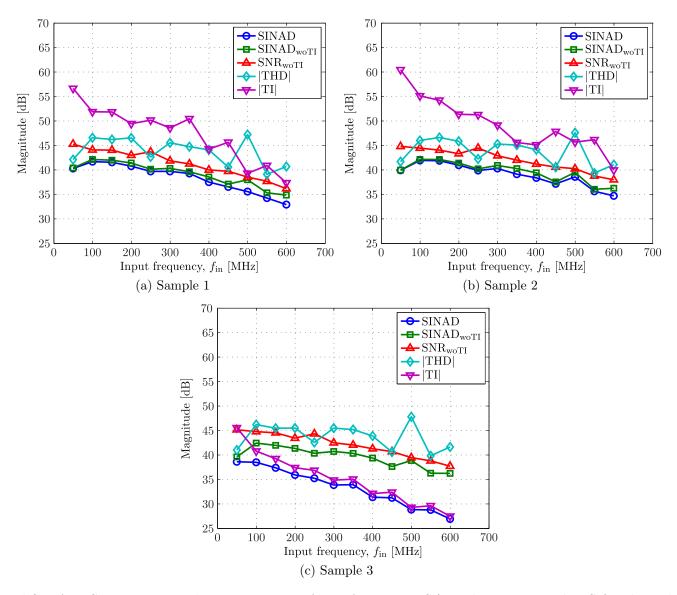

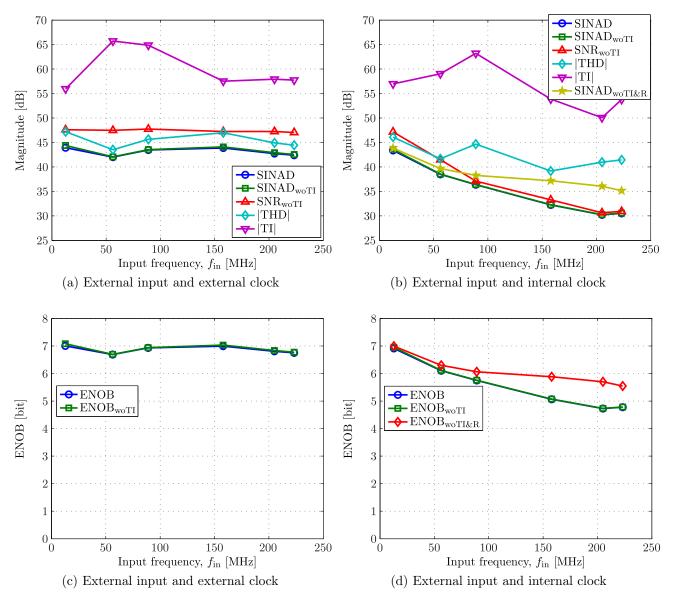

| 7.10 | Measured SINAD, SNR, THD, and TI spur versus $f_{\rm in}$ at $f_s = 500$ MS/s                               |              |

|------|-------------------------------------------------------------------------------------------------------------|--------------|

|      | and $V_{\rm in} \approx -0.1$ dBFS for three different samples                                              | 118          |

| 7.11 | Measured ENOB versus $f_{\rm in}$ at $f_s = 500$ MS/s and $V_{\rm in} \approx -0.1$ dBFS for                |              |

|      | three different samples                                                                                     | 119          |

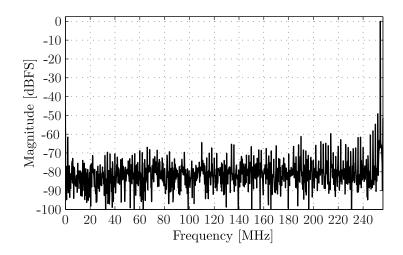

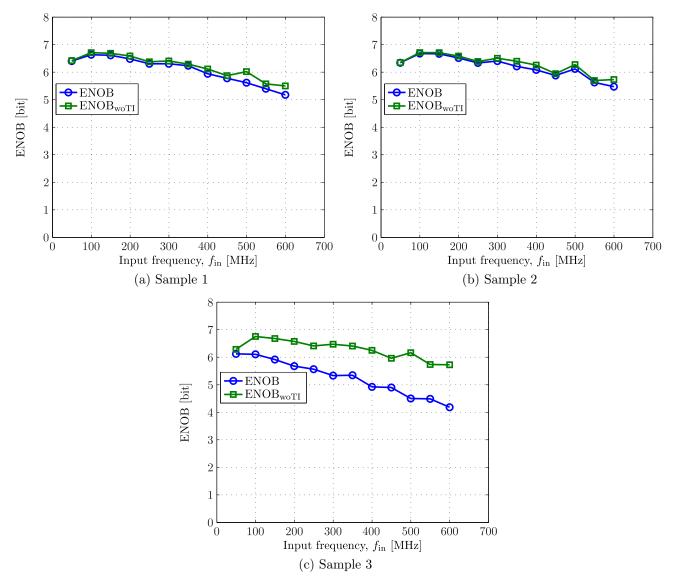

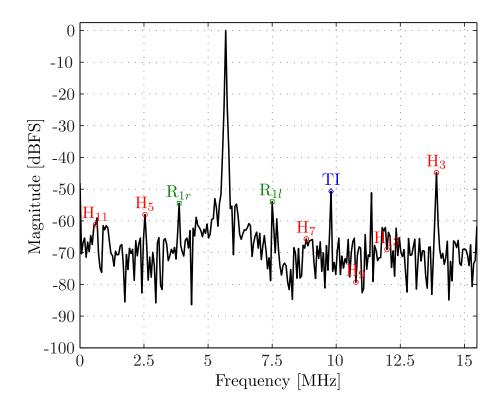

| 7.12 | Measured output spectrum of Sample 1 at $f_s = 464.64$ MS/s, $f_{\rm in} =$                                 |              |

|      | 56.265 MHz and $V_{\rm in} \approx -0.1$ dBFS                                                               | 121          |

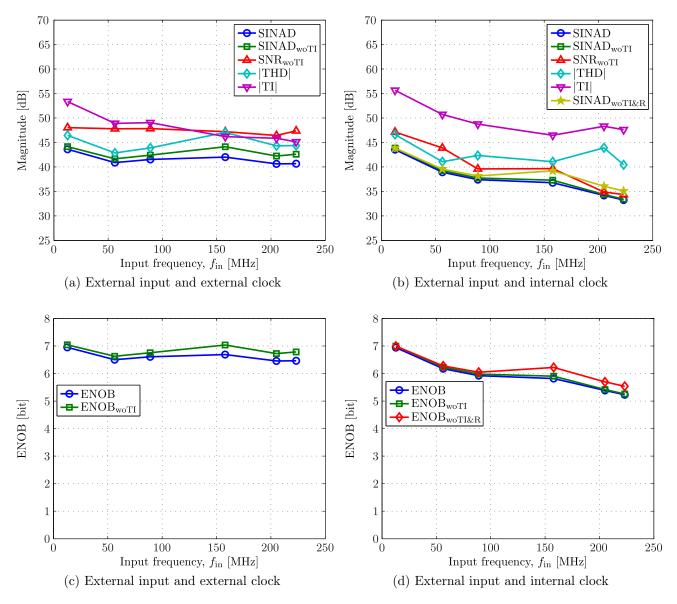

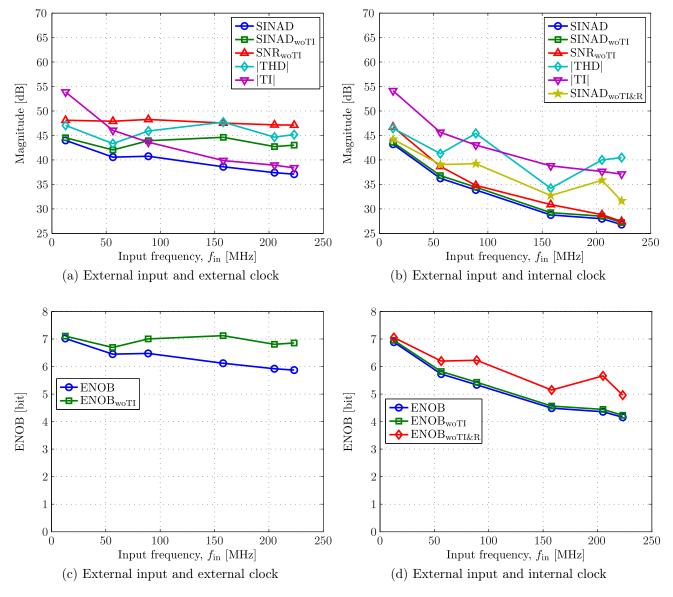

| 7.13 | Measured SINAD, SNR, THD, TI spur, and ENOB versus $f_{in}$ at $f_s =$                                      |              |

|      | 464.64 MS/s and $V_{\rm in} \approx -0.1$ dBFS for Sample 1                                                 | 123          |

| 7.14 | Measured SINAD, SNR, THD, TI spur, and ENOB versus $f_{in}$ at $f_s =$                                      |              |

|      | 464.64 MS/s and $V_{\rm in} \approx -0.1$ dBFS for Sample 2                                                 | 124          |

| 7.15 | Measured SINAD, SNR, THD, TI spur, and ENOB versus $f_{in}$ at $f_s =$                                      |              |

|      | 464.64 MS/s and $V_{\rm in} \approx -0.1$ dBFS for Sample 3                                                 |              |

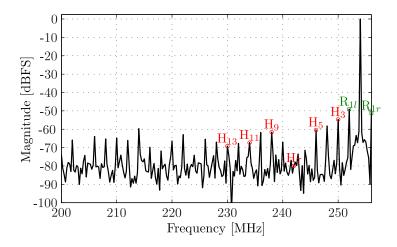

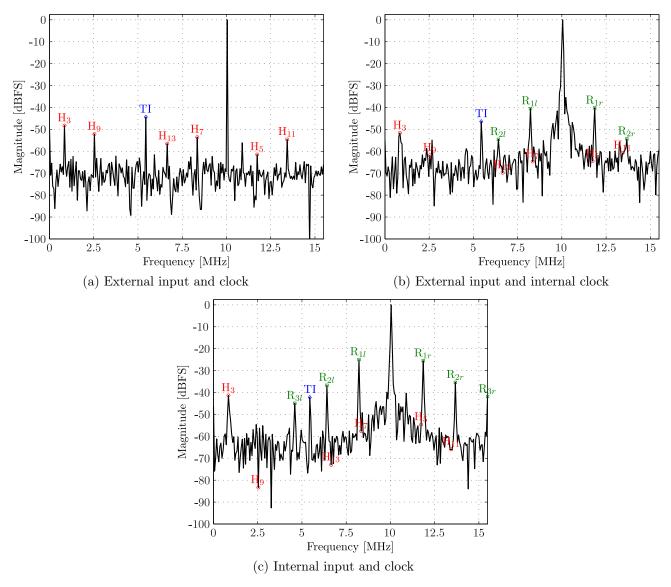

| 7.16 | Measured output spectra of Sample 1 at $f_s = 464.64 \mathrm{MS/s}, f_{\mathrm{in}} = 226.875 \mathrm{MHz}$ | $\mathbf{Z}$ |

|      | and $V_{\rm in} \approx -2.5$ dBFS for the three test scenarios                                             | 128          |

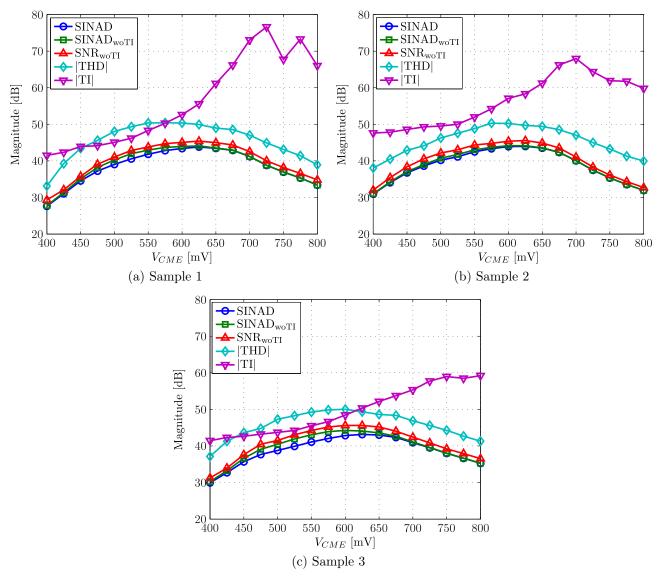

| 7.17 | Measured SINAD, SNR, THD, and TI spur versus $V_{CME}$ at $f_s = 500 \text{ MS/s}$ ,                        |              |

|      | $f_{\rm in} \approx 10$ MHz and $V_{\rm in} \approx -0.1$ dBFS for three different samples                  | 130          |

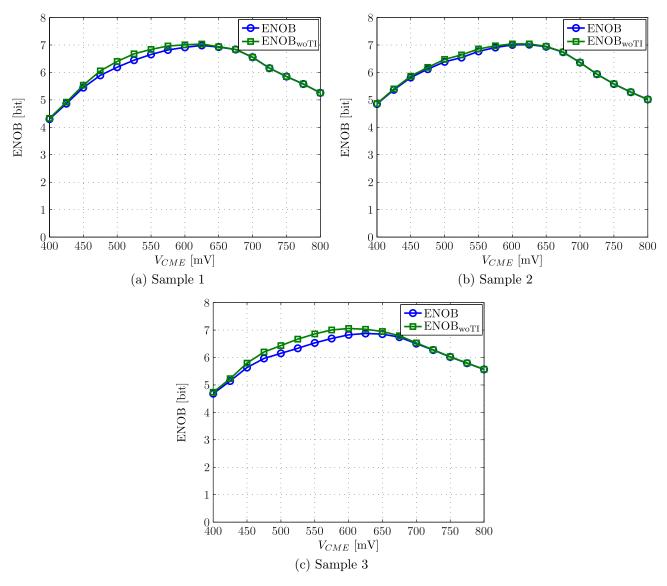

| 7.18 | Measured ENOB versus $V_{CME}$ at $f_s = 500$ MS/s, $f_{\rm in} \approx 10$ MHz and                         |              |

|      | $V_{\rm in} \approx -0.1$ dBFS for three different samples                                                  | 131          |

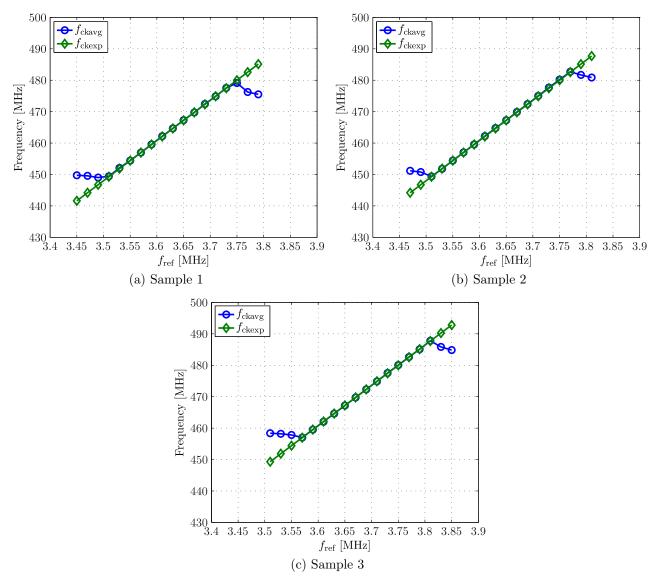

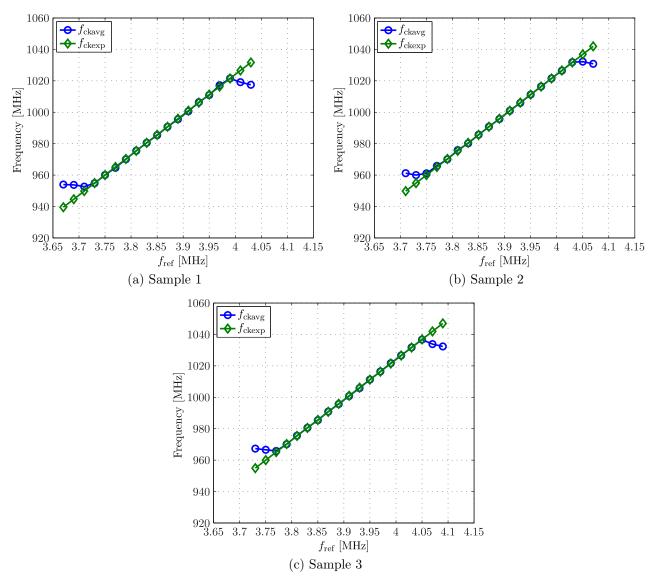

|      | Measured locking range of PLL CK for the slowest discrete tuning curve.                                     | 133          |

| 7.20 | Measured locking range of PLL CK for the fastest discrete tuning curve.                                     | 134          |

# List of Tables

| 3.1 | Summary of advantages and disadvantages of BIST                        | 28  |

|-----|------------------------------------------------------------------------|-----|

| 5.1 | Programmable parameters and frequency map for a 6-bit ADC              | 49  |

| 6.1 | Comparison of fully integrated CMOS oscillators                        | 61  |

| 7.1 | Bill of materials.                                                     | 106 |

| 7.2 | Description of the chip pads                                           | 110 |

| 7.3 | Summary of the key frequencies of the slowest locking range of PLL CK. | 132 |

| 7.4 | Summary of the key frequencies of the fastest locking range of PLL CK  | 132 |

| 7.5 | Performance summary and comparison with prior works                    | 135 |

| A.1 | ADC decimation, analog input, and clock configuration                  | 143 |

| A.2 | VCO CK discrete tuning configuration                                   | 144 |

| A.3 | VCO IN discrete tuning configuration                                   | 144 |

|     | DIV IN division value configuration                                    | 145 |

| A.5 | DIV REF division value configuration                                   | 145 |

# List of Abbreviations and Symbols

#### Abbreviations

- AAC Automatic Amplitude Control

- ac Alternating Current

- A/D Analog-to-Digital

- ADC Analog-to-Digital Converter

- AMUX Analog MUltipleXer

- ATE Automated Test Equipment

- BIST Built-In Self-Test

- CAD Computer-Aided Design

- CMOS Complementary Metal-Oxide-Semiconductor

- CODEC COder-DECoder

- CP Charge Pump

- DAC Digital-to-Analog Converter

- dc Direct Current

- DDEM Deterministic Dynamic Element Matching

- DDS Direct Digital Synthesis or Synthesizer

- DfT Design for Testability

- DFT Discrete Fourier Transform

- DIB Device Interface Board

- DIFF/SE DIFFerential-to-Single-Ended

- DNL Differential NonLinearity

- DSP Digital Signal Processing or Processor

- DUT Device Under Test

- ENIG Electroless Nickel Immersion Gold

- ENOB Effective Number Of Bits

- ESD ElectroStatic Discharge

- FD Frequency Divider

- FF Flip-Flop

- FFT Fast Fourier Transform

- FSR Full-Scale Range

- GBC Global Biasing Circuit

- HABIST Histogram-based Analog Built-In Self-Test

- HBIST Hybrid Built-In Self-Test

- IC Integrated Circuit

IDFT Inverse Discrete Fourier Transform

I<sup>2</sup>C Inter-Integrated Circuit

IMD InterModulation Distortion

INL Integral NonLinearity

I/O Input/Output

IP Intellectual Property

IQ In-phase and Quadrature-phase

LC Inductor-Capacitor

LF Loop Filter

LFSR Linear Feedback Shift Register

LSB Least Significant Bit

LVDS Low-Voltage Differential Signaling

MADBIST Mixed Analog-Digital Built-In Self-Test

MDAC Multiplying Digital-to-Analog Converter

MOM Metal-Oxide-Metal

MSB Most Significant Bit

MUX MUltipleXer

OBIST Oscillation Built-In Self-Test

ORA Output Response Analyzer

OTA Operational Transconductance Amplifier

PC Personal Computer

PCB Printed Circuit Board

PFD Phase/Frequency Detector

PG Processing Gain

PLL Phase-Locked Loop

ppm Parts Per Million

PVT Process, supply Voltage and Temperature

PWM Pulse Width Modulation

RAM Random-Access Memory

RC Resistor-Capacitor

RF Radio Frequency

rms Root-Mean-Square

ROM Read-Only Memory

rss Root-Sum-Square

RZ Return-to-Zero

SC Switched-Capacitor

SFDR Spurious Free Dynamic Range

SINAD Signal-to-Noise And Distortion ratio

SiP System-in-a-Package

SMA SubMiniature version A

SNR Signal-to-Noise Ratio

SoC System-on-a-Chip

SPI Serial Peripheral Interface

- SPICE Simulation Program with Integrated Circuit Emphasis

- SSO Simultaneous Switching Output

- STG Symmetrical Transmission Gate

- TG Transmission Gate

- THA Track-and-Hold Amplifier

- THD Total Harmonic Distortion

- TI Time-Interleaving

- TSG Test Stimulus Generator

- UMC United Microelectronics Corporation

- VCO Voltage-Controlled Oscillator

- VCR Voltage-Controlled Resistor

- V/I Voltage-to-Current

- 3D Three-Dimensional

#### **Symbols**

- f Signal frequency (f = 1/T) [cycles per second, Hz]

- $f_s$  Sampling frequency  $(f_s = 1/T_s)$  [samples per second, S/s]

- G Static gain of an ADC

- N Resolution of an ADC [bits, b]

- $N_p$  Number of integer periods of a periodic continuous-time signal

- $N_s$  Number of collected samples at ADC output

- $N_{\text{seq}}$  Number of collected sequences, each one with length  $N_s$

- Q Ideal code bin width of an ADC [e.g. volts, V]

- T[k] kth code transition level of an ADC [e.g. volts, V]

- T Signal period [seconds, s]

- $T_s$  Sampling period [seconds, s]

- $V_{\rm os}$  Static offset of an ADC [e.g. volts, V]

- x(t) Continuous-time signal at time instant t

- x[n] nth sample of a discrete-time signal

- X[k] kth DFT spectral component

- $X_{os}[k]$  kth one-sided spectral component

- $X_{\text{osm}}[k]$  Magnitude of  $X_{\text{os}}[k]$

- $X_{\text{osmav}}[k]$  Averaged magnitude of  $X_{\text{os}}[k]$

- $X_{\text{osmrms}}[k]$  rms magnitude of  $X_{\text{os}}[k]$

- $X_{\text{win}}[k]$  kth windowed DFT spectral component

- W[k] kth code bin width of an ADC [e.g. volts, V]

# Chapter 1

## Introduction

In this introductory chapter, we first discuss the motivations behind the research line pursued in this work in Sec. 1.1. Then, in Sec. 1.2, we give an overview of the proposed idea and state the main contributions. Finally, in Sec. 1.3, we present the organization of the chapters throughout this document.

#### 1.1 Motivation

The evolution of the complementary metal-oxide-semiconductor (CMOS) technology has been uninterrupted, allowing more efficient implementations of conventional digital-domain functions, and favoring the migration of other-domain functions to the digital domain at each new technology node. This efficiency gain and the innate advantages of the digital circuits (e.g. flexibility, robustness against surrounding noise, "unlimited" accuracy, etc.) are the main reasons behind the "never-ending" CMOS technology downscaling.

Despite of the interesting characteristics of the digital domain for implementing a variety of functions, most signals found in nature (e.g. sound, temperature, electromagnetic fields, etc.) cannot be directly processed by digital means. Therefore, after being represented into analog electrical signals (voltages or currents), these signals need to be converted to and from the digital domain through analog-to-digital and digital-to-analog converters (ADCs and DACs), respectively. ADCs and DACs are the most fundamental mixed-signal components, since they make the interfaces between the analog and digital domains possible.

The ADC interface, similarly as the DAC one<sup>1</sup>, assumes different forms depending on its specifications. For example, the ADC required to digitize the electrical signal representation of a human voice is completely distinct from the one required to digitize a high frequency modulated communication signal. Hence, there exist several ADC architectures and their design, fabrication, and test may vary considerably. The three key specifications of any ADC are the resolution, the conversion rate, and the dissipated power, which entail several trade-offs depending on the particular architecture chosen and the technology used.

For certain applications, commonly found in communication and measurement industries, high conversion rate (above 100 MS/s) ADCs play a crucial role in attaining faster

<sup>&</sup>lt;sup>1</sup>DAC interfaces are outside the scope of this work.

data processing, transmission, and usage. With the advances of the CMOS technology and the development of novel design techniques, the conversion rates of CMOS ADCs are now well beyond the gigasamples per second (GS/s) range [1–3]. Although the conversion rates for these applications are the highest possible, they generally require only moderate ADC resolutions (usually below 12 bits) [4]. These high conversion rate and moderate resolution ADCs are the ones we are primarily concerned in this work.

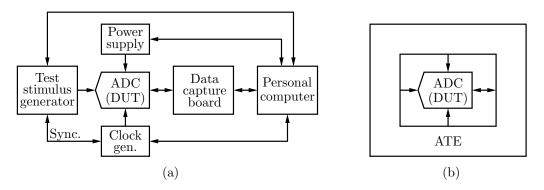

To ensure that these ADCs meet the specifications, and hence are qualified to be used in the envisaged applications, they need to be tested after fabrication and occasionally during in-field operation. The production test costs of such components represent today a very significant fraction of their production cost [5, p. 42], and these costs are perhaps the fastest-growing portion of the total manufacturing cost [6, p. 19] [5, p. 43]. These high testing costs are mainly due to lengthy test applications by means of extremely expensive automated test equipments (ATEs), which are required to apply specific test stimuli to the devices under test (DUTs) and collect and analyze their responses in the fastest possible way.

Since the conversion rates are foreseen to keep increasing [7], interfacing the ADCs to the test instruments raises new problems due to parasitics, trace mismatches, and interferences of either the printed circuit board (PCB) and the instrument test probes. This scenario becomes even more challenging with the today's trends of system-on-a-chip (SoC), system-in-a-package (SiP), and the still recent three-dimensional (3D) chips [8,9], where the accessability of the ADCs for testing purposes through external equipments is becoming more and more restricted. Currently, this accessability problem can only be alleviated when an ADC and a DAC coexist into the same system, where the two can be combined to implement a fully digital test [10]. If it is not the case, however, the testing of such an ADC is extremely challenging.

### 1.2 Overview and Contribution

It is clear from the preceding discussion that today's testing of high speed and moderate resolution ADCs poses remarkable challenges in terms of cost (due to expensive equipment and lengthy test applications), reliability (due to DUT and ATE interfacing issues), and also feasibility (due to restriction of pins for accessing the DUT).

To cope with these challenges, in this work we explore the possibility of using a dedicated built-in self-test (BIST) approach for testing these high speed and moderate resolution ADCs, either embedded into complex systems or as standalone components. This BIST approach is based on two compact and easy-to-integrate oscillators that generate high frequency test stimuli (either analog input and clock) to the DUT. Currently, CMOS oscillators are able to reach oscillation frequencies in excess of 300 GHz [11]; hence, they naturally fit to the purpose of high frequency signals generation. Instead of using free-running oscillators for generating the analog input and clock test stimuli, we propose to synchronize the two oscillators with the aid of two phase-locked loops. This synchronization improves the phase noise of the generated signals and, more importantly, allows coherent sampling.

The use of coherent sampling has a direct and beneficial impact on the output response analysis of the DUT, since it simplifies a lot the processing of the output data in terms of

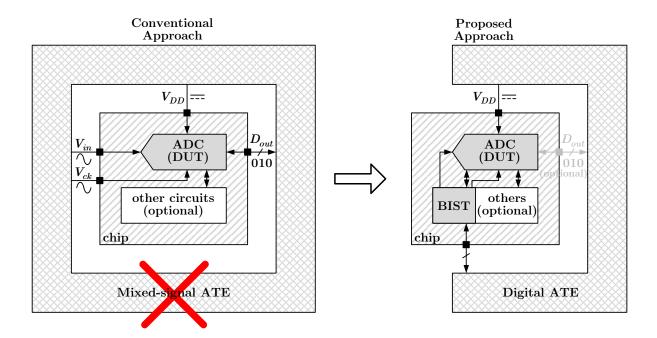

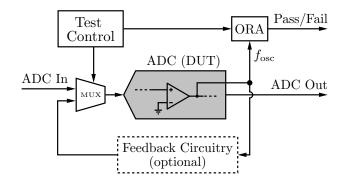

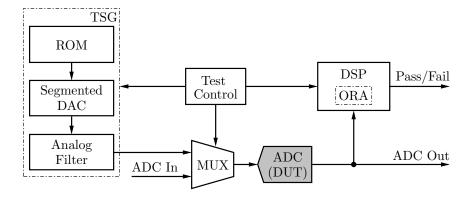

Fig. 1.1: Overview of the proposed idea.

execution time and complexity. Besides of that, and assuming spectral analysis is used to evaluate the raw output data, a coherent sampled signal translates directly to a coherent spectrum, which avoids undesirable artifacts like spectral leakage.

In the context of this work, we are primarily concerned about the ADCs' dynamic and functional performances, since ultimately they are what most matter in the testing of high speed ADCs [12, p. 241].

This fully integrated in CMOS technology BIST approach, which reduces test costs by avoiding the need of expensive mixed-signal ATEs, improves reliability by avoiding interfacing critical signals between the DUT and ATE, and enhances feasibility by carrying out the test procedure completely on-chip, is the main contribution of this work [13]. The conceptual overview of the proposed approach is shown in Fig. 1.1.

Even thought the DUT used in this work is based on a pipelined ADC topology, as it will be addressed later, the approach can be applied to other converter topologies with minimal effort, since it "sees" the device under test as an almost ideal "black box".

## 1.3 Chapters Organization

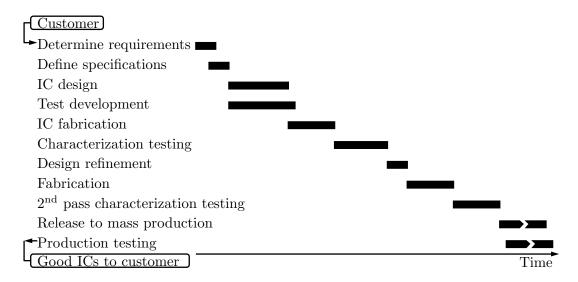

This dissertation is divided into eight chapters and one appendix. Following this introductory chapter, Chapter 2 introduces the basic concepts used throughout this work, namely: the static and dynamic performance metrics for ADCs and the standard test procedures used to determine them; the purpose of testing an integrated circuit; and the main differences between characterization and production tests and between structural and functional test approaches.

Chapter 3 deals specifically with the research question that guides this work. The investigated problem is detailed and preliminary observations, highlighting the strengths of built-in self-test methods, are given. Then, Chapter 4 is focused on the review of

structural and functional built-in self-test approaches, with emphasis on functional ones, which are further analyzed in terms of their applicability to static or dynamic performance testing. The chapter ends with a discussion of the reviewed solutions and identifies research gaps which are then considered within this work.

Chapter 5 presents the proposed built-in self-test architecture for high speed ADCs conceptually. It also indicates how the programmable parameters of the architecture could be selected based on the desired normalized analog input frequencies, desired clock frequencies, desired external reference frequency, and on the resolution of the ADC. Based on these parameters, a frequency map, which indicates all possible analog input and clock frequency combinations available to stimulate the device under test, is readily computed.

Chapter 6 contains the details of the proof-of-concept integrated circuit implementation. Special emphasis is given to the built-in self-test circuitry implementation, which may be ported to another ADC topology with minimal efforts, since the proposed approach considers the device under test as an almost ideal "black box" (except with regard to the interfacing input/output impedances). The device under test implementation, in this particular case a pipelined ADC, is also covered in this chapter.

Chapter 7 shows the silicon measurement results for distinct test scenarios, starting with the standalone ADC evaluation where the BIST circuitry is completely disabled. By means of on-chip configuration digital counters controlled by external push-button switches, other test modes are evaluated until the case where the BIST circuitry is fully operational. These results are compared and then confronted to those of other approaches available in the open literature. This chapter also discusses the implementation of the evaluation board and the test setup employed to make the measurements.

Chapter 8 summarizes the whole work and presents some suggestions for future research and development.

The dissertation is completed with Appendix A, which shows all system configuration possibilities.

## Chapter 2

# **Basic Concepts**

In this chapter, the background concepts related to this work are presented. First, in Sec. 2.1, the fundamental aspects of the A/D conversion are introduced since, throughout this work, we will deal with ADCs, in particular, with their testing. Secs. 2.2 and 2.3 discuss the most commonly used performance parameters for ADCs, classified into static and dynamic. Emphasis is given for dynamic parameters, since they are the most valuable in the context of high speed ADC testing. In Sec. 2.4, we briefly present the main need for evaluating a device, which is then complemented by Sec. 2.5, where two testing scenarios, characterization and production testing, depending on the device's development phase, are contrasted. The chapter ends with Sec. 2.6, which discusses the differences between functional and structural testing approaches, and points out why functional testing still maintains its predominance nowadays.

### 2.1 Analog-to-Digital Conversion Principle

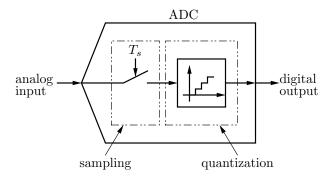

The function of an ADC is to convert a continuous-time and continuous-amplitude signal into a discrete sequence of digital words. It needs, therefore, to perform time discretization by means of a sampler (sampling operation) and amplitude discretization through a quantizer (quantization operation). The model for an ideal ADC is illustrated in Fig. 2.1. In general, quantization and sampling are nominally uniform [14, p. 1].

The input-output transfer curve of an ideal ADC, under the assumption of uniform quantization, can be represented by a staircase function and fitted with a straight line

Fig. 2.1: Ideal ADC model showing sampling and quantization operations.

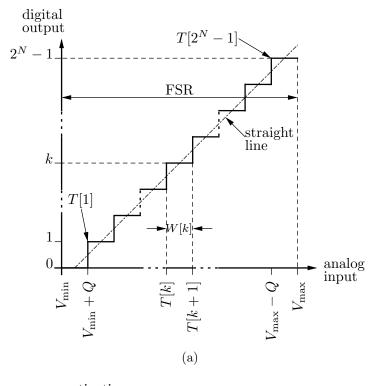

Fig. 2.2: Ideal ADC transfer curve, having full-scale range FSR and  $(2^N - 1)$  transition levels, which correspond to an N-bit quantization (a) and resulting quantization error (b).

as shown in Fig. 2.2a. The transfer curve maps the sampled input signal of the ADC (represented as a voltage, in this example) to a corresponding digital output (here, represented with the unsigned coding scheme). The input signal can range from a minimum to a maximum value,  $V_{\min}$  and  $V_{\max}$ , respectively, which is denoted as the input full-scale range (FSR) of the ADC. For a N-bit resolution ADC, the FSR is divided into  $2^N$  equally sized code bins with nominal width Q, hence

$$Q = \frac{\text{FSR}}{2^N} = \frac{V_{\text{max}} - V_{\text{min}}}{2^N} \tag{2.1}$$

By convention, the lowest code bin is numbered 0, the next is 1, and so on up to the highest code bin, numbered  $(2^N - 1)$  [14, p. 2]. Code bins are delimited by  $(2^N - 1)$  code transition levels represented by T[k]. The actual kth code bin width is W[k] = T[k+1] - T[k] for  $k = 1, 2, \ldots, (2^N - 2)$ . With this convention, therefore, the first and the last code bin widths are undefined. The code transition level T[k] corresponds to the

analog input magnitude where half of the digital outputs are greater or equal to code k while the other half are below code k [14, p. 34].

Since ADCs do not have a one-to-one input-output mapping (i.e., several input voltages are mapped to the same digital output), an inherent error denominated by quantization error exists. Referring to Fig. 2.2a, this error represents the difference between the staircase function and the fitted straight line, and is plotted in Fig. 2.2b. For specific input voltages (e.g., a ramp signal or a sine signal mixed with appropriate noise) the quantization error can be treated as a continuous random variable uniformly distributed between -Q/2 and +Q/2. In this situation, it is easy to show that the root-mean-square (rms) value of the quantization error will be [15, pp. 83-85]

rms quantization error =

$$\frac{Q}{\sqrt{12}}$$

(2.2)

Since the rms value of a full-scale input sine signal is  $FSR/(2\sqrt{2})$ , the maximum theoretical signal-to-noise and distortion ratio (SINAD) for an N-bit ADC is

$$SINAD_{max} = 20 \log_{10} \left( \frac{FSR/(2\sqrt{2})}{Q/\sqrt{12}} \right) = 6.02N + 1.76 \text{ [dB]}$$

(2.3)

The analog-to-digital (A/D) conversion of an actual ADC has other errors in addition to the quantization error shown in Fig. 2.2b. These errors can be classified into static and dynamic depending on the time derivative of the input signal observed at consecutive sampling instants. If the observed time derivatives are small, it means that the input signal slowly varies in time and its effects on the A/D conversion will be equivalent to a constant signal. Static and dynamic errors can be evaluated through several metrics which are discussed in the next sections (Secs. 2.2 and 2.3).

# 2.2 Static ADC Performance Metrics and Corresponding Testing

In this section, the most common ADC static metrics, i.e., offset, gain, differential and integral nonlinearities (DNL and INL), are discussed. We mention them briefly, since for high speed ADCs these parameters do not lead to useful conclusions about the devices' performance. The only exception is the integral and differential nonlinearities derived by sine wave histograms, where the frequency of the sine signal can be practically increased to reveal some dynamic limitations of the ADC. In this case, we call dynamic DNL and INL to oppose to their static counterparts, and the frequency of the sine wave as well as the sampling frequency must be specified.

The static parameters inform how accurate are the code transition levels of the actual ADC transfer characteristic with regard to the ideal one (see Fig. 2.2a). Hence, the first procedure in deriving the static ADC metrics is to obtain all code transition levels T[k] for  $k = 1, ..., 2^N - 1$ . For this purpose, there are basically three methods: the feedback loop, the ramp histogram, and the sine wave histogram [14, pp. 34-42].

For specific ADCs, e.g., very-high resolution or time-interleaved ADCs, the code transition levels are impractical or impossible to be defined. In these situations, there exist

an alternative method to obtain the ADC transfer curve by averaging the output codes related to a set of input signal levels. This method is explained in [14, pp. 42, 43].

#### 2.2.1 Gain and Offset

The static gain G and offset  $V_{os}$  of an ADC are defined as the quantities by which the code transition levels T[k] are multiplied and then added, respectively, in order to minimize the errors  $\varepsilon[k]$  defined in Eq. (2.4). Note that the right side of Eq. (2.4) represents the ideal code transition levels, with  $T_1$  corresponding to the ideal transition T[1] (see Fig. 2.3). This definition of G and  $V_{os}$  leads to the minimum difference between the input and the output signals, after the latter is converted to input units.

$$G \times T[k] + V_{os} + \varepsilon[k] = Q \times (k-1) + T_1 \qquad k = 1, \dots, 2^N - 1$$

(2.4)

Depending on how  $\varepsilon[k]$  is minimized, there are two definitions for gain and offset: terminal based and independently based [14, pp. 44, 45]. Terminal-based gain and offset are the values of G and  $V_{\rm os}$  in Eq. (2.4) that set the error  $\varepsilon[k]$  of the first and last code transition levels to zero , i.e.,  $\varepsilon[1] = \varepsilon[2^N - 1] = 0$ . Hence, by measuring the code transition levels T[1] and  $T[2^N - 1]$ , the terminal-based gain and offset are straightforwardly obtained.

When G and  $V_{os}$  in Eq. (2.4) are found by minimizing the mean squared value of  $\varepsilon[k]$ , the resulting gain and offset are denominated independently based. Using linear least-squares estimation techniques, the static gain and offset become, respectively, [14, p. 45]

$$G = \frac{Q(2^{N} - 1)\left(\sum_{k=1}^{2^{N} - 1} kT[k] - 2^{(N-1)} \sum_{k=1}^{2^{N} - 1} T[k]\right)}{(2^{N} - 1)\sum_{k=1}^{2^{N} - 1} T[k]^{2} - \left(\sum_{k=1}^{2^{N} - 1} T[k]\right)^{2}}$$

(2.5)

and

$$V_{\text{os}} = T_1 + Q\left(2^{(N-1)} - 1\right) - \frac{G}{(2^N - 1)} \sum_{k=1}^{2^N - 1} T[k]$$

(2.6)

Whichever of the two definitions is used, it must be clearly specified. The independently based approach is the most common in practice.

#### 2.2.2 Differential Nonlinearity

The differential nonlinearity is defined as the difference between the real and ideal code bin widths, W[k] and Q, respectively, divided by the ideal code bin width, after correcting for static gain. Mathematically, this becomes

$$DNL[k] = \frac{W[k] - Q}{Q} \qquad k = 1, \dots, 2^{N} - 2$$

(2.7)

Note that code bin widths W[0] and  $W[2^N - 1]$  are undefined, hence the corresponding DNLs do not exist. Furthermore, since we must adjust for static gain before computing

Fig. 2.3: Independently based DNL and INL definitions.

the DNL, we name the DNL according to the gain derivation procedure (i.e., terminal or independently based). The graphical representation of the kth independently based DNL value is shown in Fig. 2.3.

When the DNL is stated in a single value, it represents the maximum absolute value |DNL[k]| for all k. We say code k is a missing code when  $DNL[k] \le -0.9$  [14, pp. 47, 48].

### 2.2.3 Integral Nonlinearity

The integral nonlinearity is the difference between the ideal and actual code transition levels, normalized to the ideal code bin width, after correcting for static gain and offset. When expressed in units of least significant bits (LSBs), the INL becomes

$$INL[k] = \frac{\varepsilon[k]}{Q}$$

$k = 1, ..., 2^{N} - 1$  (2.8)

Similarly to the DNL, the INL may be terminal or independently based depending on the gain and offset estimation. Fig. 2.3 shows the kth independently based INL value.

A single INL value represents the maximum value of |INL[k]| for all codes k.

# 2.3 Dynamic ADC Performance Metrics and Corresponding Testing

Since the building blocks of any real ADC have finite bandwidths and can only process finite amplitude signals, generally swinging within a fraction of the supply rails ( $V_{DD}$  and  $V_{SS}$ ), the behavior of the ADC changes as either the amplitude or frequency of the input signal increases. Moreover, particularly when the ADC core circuitry is surrounded by

other circuitry, there exist a high likelihood of interferences from these circuits, which also modify the ADC's behavior. These changes are associated with intricate dynamical phenomena which pose limits on the performance of the ADCs and are quantified through several metrics discussed within this section. Given that most ADC performance parameters are derived from spectral analysis, we begin explaining the discrete Fourier transform (DFT) and a sampling technique called coherent sampling. For each metric, we discuss the most commonly used testing approaches.

### 2.3.1 Discrete Fourier Transform and Coherent Sampling

Suppose an ADC is digitizing an input signal x(t) with a sampling frequency  $f_s$ . After  $N_s \times T_s$  seconds, where  $N_s$  and  $T_s$  (= 1/ $f_s$ ) are the number of digitized samples and sampling period, respectively, we have a sequence x[n] with  $N_s$  samples. This timedomain sequence may be represented in the frequency-domain applying the DFT, which is defined as [16, p. 644]

$$X[k] = \sum_{n=0}^{N_s - 1} x[n]e^{-j2\pi kn/N_s} \qquad k = 0, \dots, N_s - 1$$

(2.9)

If we want to recover the sequence x[n] from its spectrum X[k], we can apply the inverse DFT (IDFT) as follows [16, p. 644]

$$x[n] = \frac{1}{N_s} \sum_{k=0}^{N_s - 1} X[k] e^{j2\pi nk/N_s} \qquad n = 0, \dots, N_s - 1$$

(2.10)

Note that a normalization factor  $1/N_s$  is used in Eq. (2.10). This means that each spectral component X[k] in Eq. (2.9) is scaled up by a factor  $N_s$ . This conclusion is easily confirmed if we calculate, for example, the direct current (dc) spectral component by means of Eq. (2.9), which is  $X[0] = x[0] + x[1] + \cdots + x[N_s - 1]$ , and compare it with the actual dc component value, which is the time average of x[n], i.e.,  $(x[0] + x[1] + \cdots + x[N_s - 1])/N_s$ .

The spectrum derived by Eq. (2.9) ranges from dc to  $f_s(1-1/N_s)$  with increments of  $f_s/N_s$ , which is the frequency resolution of the DFT. Furthermore, the spectrum so obtained is two-sided represented meaning that  $X[k] = X^*[N_s - k]$  for  $k = 1, \ldots, N_s - 1$ , where the symbol \* means complex conjugation. If  $N_s$  is an even integer, the spectral component  $X[N_s/2]$  does not have complex conjugation. In this case, the two-sided spectrum may be converted to the one-sided one (i.e., ranging from dc to  $f_s/2$ ) by multiplying the components X[k] by a factor of two for  $k = 1, \ldots, N_s/2 - 1$ . Therefore, the one-sided spectrum comprises a set of  $N_s/2 + 1$  spectral components as follows

$$X_{os}[k] = \begin{cases} X[k] & \text{for } k = 0\\ 2 \times X[k] & \text{for } 1 \le k \le N_s/2 - 1\\ X[k] & \text{for } k = N_s/2 \end{cases}$$

(2.11)

The magnitude of the one-sided spectrum after appropriate normalization is

$$X_{\text{osm}}[k] = \frac{|X_{\text{os}}[k]|}{N_s}$$

$k = 0, \dots, N_s/2$  (2.12)

where |x| means the absolute value of x. When  $N_s$  is an odd integer, slightly modifications are needed to make the two- to one-sided spectrum conversion, since now the component  $X[N_s/2]$  does not exist. In this work, otherwise explicitly stated, we assume even integer  $N_s$ .

Even though the one-sided spectrum contains only half the spectral components of the two-sided spectrum, both representations have the same spectral power. Hence, they can be used interchangeably, although the one-sided spectrum is the most used.

If we collect  $N_{\text{seq}}$  sequences x[n], each one with  $N_s$  samples, and apply the DFT over each of these sequences, the resulting  $N_{\text{seq}}$  spectrums will be slightly different due to inherent random artifacts (e.g. random noise, random interferers, etc.) present either in x(t) or introduced during the A/D conversion. Hence, the results obtained through the spectrums will vary accordingly, limiting the measurements' accuracy and repeatability. To reduce the spectral variance, the magnitudes of the spectrums can be averaged as follows [14, p. 52]

$$X_{\text{osmav}}[k] = \frac{1}{N_{\text{seq}}} \sum_{n=1}^{N_{\text{seq}}} X_{\text{osm}_n}[k]$$

$k = 0, \dots, N_s/2$  (2.13)

where  $X_{\text{osm}_n}[k]$  represents the kth one-sided spectrum magnitude related to the nth sequence. Eq. (2.13) is an ensemble average and represents the one-sided averaged magnitude spectrum. By concentrating on a given spectral component  $X_{\text{osm}_n}[k]$ , as n ranges from 1 to  $N_{\text{seq}}$ , the magnitudes fluctuate around a mean value with a certain standard deviation. It can be shown that this standard deviation is approximately  $\sqrt{N_{\text{seq}}}$  times higher than that obtained observing the fluctuations over several realizations of  $X_{\text{osmav}}[k]^1$ . Therefore, the spectral magnitudes given by Eq. (2.13) are more accurate than those given by Eq. (2.12).

The spectral magnitudes of Eqs. (2.12) and (2.13) may be represented in rms values. For Eq. (2.12), for instance, this becomes

$$X_{\text{osmrms}}[k] = \begin{cases} X_{\text{osm}}[k] & \text{for } k = 0\\ X_{\text{osm}}[k]/\sqrt{2} & \text{for } 1 \le k \le N_s/2 - 1\\ X_{\text{osm}}[k] & \text{for } k = N_s/2 \end{cases}$$

(2.14)

The average power of a real-value sequence x[n], with  $N_s$  samples, may be written in terms of the rms spectrum as follows

$$\frac{1}{N_s} \sum_{n=0}^{N_s - 1} x[n]^2 = \sum_{k=0}^{N_s / 2} X_{\text{osmrms}}[k]^2$$

(2.15)

where the Parseval's theorem [16, p. 707] is used.

Thus far, we have imposed no restrictions on the input signal x(t) being digitalized by the ADC and then processed by DFT. However, the spectrum computed by the DFT will be correct only if the signal x(t) can be frequency decomposed into integer multiples of the frequency resolution of the DFT, i.e.,  $kf_s/N_s$  for k=0,1,2,... This means that,

<sup>&</sup>lt;sup>1</sup>This is strictly true only if the random artifacts corrupting the collect sequences x[n] are uncorrelated.

when the DFT is applied, the spectral components of x[n] will lie exactly on the DFT bins, i.e.,  $kf_s/N_s$  for  $k = 0, 1, ..., N_s - 1$ . When this condition is satisfied, we say that signal x(t) is coherently sampled.

For the special case of a sine signal  $x(t) = A \sin(2\pi f_{\rm in}t)$ , with frequency  $f_{\rm in}$  (= 1/ $T_{\rm in}$ ), being sampled by a sample rate  $f_s$ , coherent sampling is achieved with [17, p. 45] [18]

$$f_{\rm in} = \frac{N_p f_s}{N_s} \tag{2.16}$$

where  $N_p$  is an integer number. Eq. (2.16) can be rearranged as follows:  $N_pT_{\rm in} = N_sT_s$ , where  $N_p$  may be interpreted as the number of input periods sampled during the sampling interval  $(N_sT_s)$ .

The computation of the DFT, exactly as defined in Eq. (2.9), requires a high computational cost, specifically,  $N_s^2$  complex multiplications and  $N_s(N_s-1)$  complex additions. In practice, however, there exist more efficient ways to compute the DFT, which are called fast Fourier transform (FFT) algorithms [16, chap. 9]. It can be shown that these algorithms reduce the implementation complexity of the DFT to  $N_s \log_2 N_s$  complex multiplications and  $N_s \log_2 N_s$  complex additions, if  $N_s$  is a power of two [16, p. 729]. Therefore, it is advisable and wise to collect a power of two number of samples to allow an efficient DFT computation. In this work, unless differently stated, we assume  $N_s = 2^p$  with a positive integer value p.

Sampling the sine signal x(t), with  $f_{in}$  defined as in Eq. (2.16), at instants  $t = nT_s$ , for n = 0, 1, ..., results

$$x[n] = A \sin\left(\frac{2\pi N_p n}{N_s}\right) \tag{2.17}$$

If we consider  $N_s=2^4=16$  and  $N_p=6$ , for instance, and collect  $N_s$  samples, the sine signal will assume discrete-phase values of  $2\pi(6/16)n$ ,  $n=0,1,\ldots,N_s-1$ . Distributing these phases on a circle produces Fig. 2.4a, where the index n for each sample is shown. It is clear from Fig. 2.4a that the sequence x[n] contains only 8 distinct values, since half of the samples overlap. In other words, the collected samples are somehow redundant. This occurs because  $N_p/N_s$  is not irreducible in this example, i.e.,  $N_p/N_s=6/16=3/8$ . Hence, the phases overlap after 8 samples, instead of  $N_s=16$ . By considering  $N_p$  any odd integer, the ratio  $N_p/N_s$  is irreducible since  $N_s$  is a power of two. In general,  $N_p$  and  $N_s$  must be mutually prime. Fig. 2.4b shows the phases distribution when  $N_s=16$  and  $N_p=7$ . Clearly, the  $N_s$  collected samples have distinct values.

From the ADC testing perspective, we want the minimum  $N_s$  that contains all possible ADC codes. Hence,  $N_p/N_s$  must be irreducible to avoid collecting redundant samples when the input signal is periodic. With this condition fulfilled and assuming an ideal ADC sampling a full-scale sinusoidal, the minimum  $N_s$  in order to get at least one sample from every ADC code is [13] [14, p. 30]

$$N_s > \pi 2^N \approx 2^{N+2} \tag{2.18}$$

The approximation in Eq. (2.18) gives some margin for nonidealities either in the ADC or in the input sinusoidal signal, though it cannot guarantee that all possible ADC codes are sampled in this nonideal scenario.

Fig. 2.4: Phases distribution of a sine signal with reducible (a) and irreducible  $N_p/N_s$  (b).  $N_s = 16$  for both cases and the circle is divided in  $N_s$  slices.

The number of samples,  $N_s$ , also influences the processing gain (PG) of the DFT, which is defined as [15, p. 88]

$$PG = 10\log_{10}\left(\frac{N_s}{2}\right) \text{ [dB]}$$

(2.19)

This gain defines how much the DFT noise floor is below the maximum signal-to-quantization noise ratio given by Eq. (2.3). As an example, Fig. 2.5 shows the one-sided magnitude spectrum obtained through Eq. (2.12) over  $N_s = 4096$  samples. The samples are derived from a 10-bit ADC with a FSR of one, which is sampling a full-scale sine signal, i.e.  $x(t) = (\text{FSR}/2) \sin(2\pi f_{\text{in}}t)$ , with  $f_s = 100 \text{ MS/s}$ . The frequency  $f_{\text{in}}$  is selected by Eq. (2.16) with  $N_p = 483$  and  $N_s$  given by Eq. (2.18), thus ensuring coherent sampling. (Note that the Nyquist criterion [16, p. 160] is not obeyed if  $N_p \geq N_s/2$ . In this case, the ADC is undersampling the input signal, which is commonly denoted sub-sampling operation mode.)

If Eq. (2.16) is not satisfied, the ADC samples the input signal noncoherently. In this situation, the signal will not be concentrated on a single DFT bin; instead, it will be spread among several bins, which is commonly known as spectral leakage. Fig. 2.6a superimposes the coherent spectrum of Fig. 2.5 with a noncoherent spectrum obtained choosing  $N_p = 483.5$ . It is noticeable that the resulting spectrum is unsuitable for practical use.

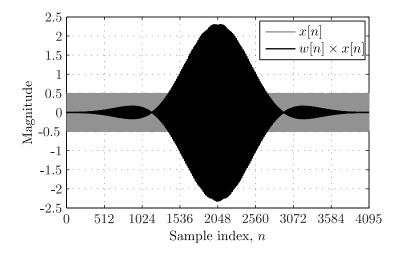

To minimize the undesirable effects produced by noncoherent sampling, we can apply a window over the digitized sequence x[n], and then compute the DFT. The purpose of any window is to progressively reduce the amplitude of the sequence x[n] from its intermediate to its extremes samples. This idea originates from the fact that the DFT, even processing a single sequence x[n] with  $N_s$  samples, implicitly assumes the sequence x[n], formed by a contiguous arrangement of an infinity number of sequences x[n], has no discontinuities between adjacent samples. When Eq. (2.16) is not fulfilled, these discontinuities are unavoidable. To reduce them, which are the cause of spectral leakage, the extreme samples of x[n] are attenuated (see Fig. 2.7).

Fig. 2.5: Output spectrum (4096-point FFT) of 10-bit ADC with FSR = 1,  $f_s$  = 100 MS/s, and input signal  $x(t) = 0.5 \times \sin(2\pi \times (483/4096) \times 10^8 t)$ . The FFT noise floor is  $\sim 33$  dB below the maximum theoretical SINAD for this converter, i.e.  $\sim 62$  dB, due to processing gain.

The spectrum of a windowed sequence is derived as follows

$$X_{\text{win}}[k] = \sum_{n=0}^{N_s - 1} w[n]x[n]e^{-j2\pi kn/N_s} \qquad k = 0, \dots, N_s - 1$$

(2.20)

which is similar to Eq. (2.9), despite now the sequence x[n] is multiplied by the window w[n].

Regarding the window selection, there are several options depending on the desired characteristics (see, e.g., [19, p. 55]). Perhaps the most used for ADC testing are the Flat Top and the Hann windows, which are defined, respectively, by Eqs. (2.21) and (2.22)

$$w[n] = 1 - 1.93 \cos\left(\frac{2\pi n}{N_s - 1}\right) + 1.29 \cos\left(\frac{4\pi n}{N_s - 1}\right) - 0.388 \cos\left(\frac{6\pi n}{N_s - 1}\right) + 0.0322 \cos\left(\frac{8\pi n}{N_s - 1}\right) \qquad n = 0, \dots, N_s - 1$$

$$w[n] = 0.5 \left(1 - \cos\left(\frac{2\pi n}{N_s - 1}\right)\right) \qquad n = 0, \dots, N_s - 1$$

(2.21)

$$w[n] = 0.5 \left(1 - \cos\left(\frac{2\pi n}{N_s - 1}\right)\right) \qquad n = 0, \dots, N_s - 1$$

(2.22)

The Flat Top window changes almost negligibly the amplitudes of the signal x(t), and since most measurements are based on spectrum magnitudes, this window is largely employed. However, the Flat Top window is not adequate for frequency discrimination, given that the energy of the components are spread over several DFT bins. In this particular case, the Hann window is more appropriate. Besides these two windows, there are many others, e.g., Hamming, Blackman, Blackman-Harris, etc. The windowed spectrum shown in Fig. 2.6b uses a Flat Top window.

#### 2.3.2 Signal-to-Noise and Distortion Ratio

Suppose an ADC is digitizing an input sine signal whose noise and distortion are negligible compared to those introduced by the ADC itself and other signals driving the ADC, e.g.,

Fig. 2.6: Noncoherent (a) and windowed (Flat Top window) (b) spectrums both overlaid with the coherent spectrum.

Fig. 2.7: Original x[n] and windowed  $w[n] \times x[n]$  sequences. The window attenuates the amplitudes of x[n] at its extreme samples.

the clock signal. For each amplitude and frequency of the sine wave, the signal-to-noise and distortion ratio (SINAD) is computed as the ratio of the rms value of the sine signal to the rms value of the total noise at the ADC output. Mathematically, this becomes

$$SINAD = 20 \log_{10} \left( \frac{rms \ signal}{rms \ total \ noise} \right) \ [dB]$$

(2.23)

The total noise is any deviation between the output of the ADC, converted to input units, and the input signal, except deviations caused by gain, phase, or dc level shifts. Therefore, the amplitude accuracy and dc offset of the sine signal do not affect the SINAD result. Nonetheless, random noise and distortion do affect it and, consequently, appropriate filtering may be required depending on the quality of the available sine wave generator. Also, the frequency stability of the generator is an important concern, and it should be able to generate a low phase noise signal.

The above outlined sine signal nonidealities must be insignificant contrasted to those introduced by the A/D conversion. If they are not, the ADC performance evaluation will

be misleading. Concerning the sine distortion, in practice, the amplitude of the dominant harmonic component of the sine signal should be at least 12 dB (or approximately 2 bits) below the amplitude of the dominant harmonic distortion of the ADC [14, pp. 69, 70]. A similar rule of thumb may be applied to the random noise corrupting the sine signal, i.e., 12 dB below the ADC rms quantization noise. For the frequency stability, a maximum limit may be found relating the time jitter standard deviation of the sine signal to its nominal period [14, pp. 68, 69].

The amplitude and frequency of the sine wave influence the SINAD, hence for each measurement their values must be clearly specified. The minimum amplitude that can be processed by the ADC is restricted by the ADC noise floor. As the amplitude of the sine signal increases, the SINAD also increases until the distortions become dominant. For greater magnitudes, the SINAD decreases sharply. The dependence on frequency is usually monotonic, with the SINAD decreasing as the frequency of the sine signal increases. The most informative SINAD value is obtained when either the frequency and amplitude of the sine signal are pushed close to the maximum allowed values, which rely on the ADC bandwidth and full-scale range.

There are, basically, two test methods used to derive the SINAD: one based on the frequency domain and other based on sine wave fitting. The frequency domain method uses the DFT to first derive the spectrum and then compute the rms values of the sine signal and the total noise. A coherent spectrum, when practically feasible, is preferable to a windowed spectrum, as explained in Sec. 2.3.1. Considering a one-sided rms magnitude spectrum (see Eq. (2.14)), the rms value of the total noise is given by

rms total noise =

$$\sqrt{\sum_{f_k \neq 0, f_{\text{in}}} X_{\text{osmrms}} [f_k]^2}$$

(2.24)

where  $f_k = kf_s/N_s$ ,  $k = 0, ..., N_s/2$ . In Eq. (2.24), we removed the dc and fundamental frequency  $(f_{in})$  components, and the remaining rms spectral components are combined in a root-sum-square (rss) basis. The rms value of the sine signal is found as follows

rms signal =

$$X_{\text{osmrms}}[f_{\text{in}}]$$

(2.25)

The SINAD is then obtained by substituting Eqs. (2.24) and (2.25) into Eq. (2.23).

If the measurement requires more accuracy, then the averaged spectrum defined by Eq. (2.13) can be applied. When a windowed spectrum is used to measure the SINAD, special attention must be paid to select the appropriate spectral components that form the rms signal and total noise values, since the energy of the signals are not confined in single DFT bins. In this situation, and depending on the characteristics of the window employed, adjacent bins should be considered for the dc and sine signal related spectral components [15, pp. 332, 333].

The sine fitting method is an alternative to the windowed spectrum to calculate the SINAD, since both approaches do not necessarily rely on the coherent sampling. Nevertheless, the fitting method entails more intensive computations than the DFT, specially when the latter is implemented using a FFT algorithm. This, in turn, entails more complex hardware/software implementations and longer testing procedures, which unavoidably limit the approach popularity. Following this method, the total noise rms

value is given by

rms total noise =

$$\sqrt{\frac{1}{N_s} \sum_{n=0}^{N_s-1} (x[n] - \hat{x}[n])^2}$$

(2.26)

where x[n] is the digital output of the ADC and  $\hat{x}[n]$  is its best fit sine wave. The sine wave rms value is simply the amplitude of the fitted sine divided by  $\sqrt{2}$ .

Two well-known approaches for sine wave fitting are the three- and four-parameters least-squares fitting. The former is used when the frequency of the sine is known a priori, but the offset, amplitude and phase are not. A discussion of both methods may be found in [14, pp. 28, 29].

#### 2.3.3 Total Harmonic Distortion

Differently from the SINAD, the total harmonic distortion (THD) accounts only for the harmonic components present in the ADC total noise. The harmonic components are a result of ADC nonlinearity and intricate dynamic phenomena when it is digitizing a periodic signal.