UNIVERSIDADE NOVA DE LISBOA

Março, 2014

#### Heterogeneous Computing with an Algorithmic Skeleton Framework

Copyright © Fábio Miguel Cardoso Soldado, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa

A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objectivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor. iv

To my parents and my sister, for all this awesome years so far

vi

## Acknowledgements

I would like to thank, in first place, to my adviser Hervé Paulino, for all the support during the time we worked together, and for always being available to help me at any time. Secondly, I want to thank the FCT/UNL, for providing a good environment and working conditions.

A special thanks goes to my course friends, specially André Alves, Pedro Leonardo, Paulo Dias and Carlos Loureiro, for the mutual emotional support in the harder times.

I could not finish without thanking my family, specially my parents and grandparents, for being able to fully support me during my studies, both economically and emotionally. viii

## Abstract

The Graphics Processing Unit (GPU) is present in almost every modern day personal computer. Despite its specific purpose design, they have been increasingly used for general computations with very good results. Hence, there is a growing effort from the community to seamlessly integrate this kind of devices in everyday computing. However, to fully exploit the potential of a system comprising GPUs and CPUs, these devices should be presented to the programmer as a single platform.

The efficient combination of the power of CPU and GPU devices is highly dependent on each device's characteristics, resulting in platform specific applications that cannot be ported to different systems. Also, the most efficient work balance among devices is highly dependable on the computations to be performed and respective data sizes.

In this work, we propose a solution for heterogeneous environments based on the abstraction level provided by algorithmic skeletons. Our goal is to take full advantage of the power of all CPU and GPU devices present in a system, without the need for different kernel implementations nor explicit work-distribution. To that end, we extended Marrow, an algorithmic skeleton framework for multi-GPUs, to support CPU computations and efficiently balance the work-load between devices. Our approach is based on an offline training execution that identifies the ideal work balance and platform configurations for a given application and input data size.

The evaluation of this work shows that the combination of CPU and GPU devices can significantly boost the performance of our benchmarks in the tested environments, when compared to GPU-only executions.

Keywords: Algorithmic Skeletons, OpenCL, GPGPU, Heterogeneous Computing.

x

### Resumo

O GPU (Graphics Processing Unit) está presente em praticamente todos os computadores actuais. Apesar da sua finalidade específica, este processador tem sido alvo de crescente uso em computação de carácter mais geral, com resultados bastante promissores. Como tal, tem havido um crescente esforço para integrar este dispositivo na programação mais geral. No entanto, para que o potencial de sistemas constituidos por CPUs e GPUs possa ser explorado ao máximo, estes dispositivos devem ser apresentados ao programador como uma plataforma única.

Uma combinação eficiente do poder de CPUs e GPUs depende muito das características de cada um destes dispositivos, resultando em aplicações específicas para uma plataforma que não manterão a mesma eficiência quando portadas para sistemas diferentes. Além disso, o balanceamento de carga entre estes dois dispositivos depende também das computações executadas assim como dos respectivos tamanhos dos dados.

Neste trabalho, propomos uma solução para ambientes heterogéneos baseada no nível de abstracção fornecido pelos *Algorithmic Skeletons*. O nosso objectivo é tirar partido do poder de todos os CPUs e GPUs presentes num sistema sem que haja a necessidade de definir diferentes *kernels* ou dividir a carga explicitamente. Deste modo, estendemos o Marrow, uma *framework* de *Algorithmic Skeletons* para multi-GPUs, para suportar computações OpenCL no CPU e balancear a carga do trabalho entre os dispositivos de forma eficiente. A nossa abordagem é baseada num treino *offline*, que identifica o balanceamento de carga e a configuração da plataforma ideais para uma dada aplicação.

A avaliação deste trabalho mostra que a combinação do CPU e do GPU foi capaz de melhorar significativamente os resultados dos nossos testes nos ambientes de execução em que foram corridos, quando comparados com execuções apenas nos GPUs.

Palavras-chave: Padrões Algorítmicos, GPGPU, OpenCL, Computação Heterogénea.

xii

## Contents

| 1 | Intr                                              | oductic           | )n                                                         | 1  |  |

|---|---------------------------------------------------|-------------------|------------------------------------------------------------|----|--|

|   | 1.1                                               | Motiv             | ation                                                      | 1  |  |

|   | 1.2                                               | Proble            | em                                                         | 2  |  |

|   | 1.3                                               | Proposal          |                                                            |    |  |

|   | 1.4                                               | Contri            | ibutions                                                   | 4  |  |

|   | 1.5                                               | ment Organization | 4                                                          |    |  |

| 2 | Stat                                              | e of the          | e Art                                                      | 7  |  |

|   | 2.1                                               | Algori            | ithmic Skeletons                                           | 7  |  |

|   | 2.2                                               | Hetero            | ogeneous Computing                                         | 10 |  |

|   |                                                   | 2.2.1             | On the programming of Heterogeneous Systems                | 11 |  |

|   |                                                   | 2.2.2             | GPU offloading tools                                       | 12 |  |

|   |                                                   | 2.2.3             | Multi-backend with single or explicit offloading           | 15 |  |

|   |                                                   | 2.2.4             | Automatic Backend Selection                                | 17 |  |

|   | 2.3                                               | Skelet            | ons and Template-based Frameworks for Multi-core Computing | 21 |  |

|   | 2.4                                               | Summ              | nary                                                       | 22 |  |

| 3 | The                                               | Marro             | w Algorithmic Skeleton Framework                           | 25 |  |

|   | 3.1                                               | Skelet            | on Library                                                 | 25 |  |

|   |                                                   | 3.1.1             | Skeleton Nesting                                           | 26 |  |

|   |                                                   | 3.1.2             | Multi-GPU support                                          | 27 |  |

|   |                                                   | 3.1.3             | Supported Skeletons                                        | 28 |  |

|   |                                                   | 3.1.4             | Programming example                                        | 30 |  |

|   | 3.2                                               | Runtii            | me System                                                  | 31 |  |

|   |                                                   | 3.2.1             | Execution Model                                            | 31 |  |

| 4 | Integrating the CPU in the Marrow Execution Model |                   |                                                            |    |  |

|   | 4.1                                               | Gener             | al Overview                                                | 35 |  |

|   | 4.2                                               | Skelet            | on Library                                                 | 37 |  |

|   |     | 4.2.1 Programming example                              | 39 |  |  |  |

|---|-----|--------------------------------------------------------|----|--|--|--|

|   | 4.3 | Runtime System                                         | 41 |  |  |  |

|   | 4.4 | Execution Model                                        |    |  |  |  |

|   | 4.5 | Work-load Distribution                                 |    |  |  |  |

|   |     | 4.5.1 Training                                         | 47 |  |  |  |

|   |     | 4.5.2 Partitioning Derivation                          | 56 |  |  |  |

|   | 4.6 | Summary                                                | 57 |  |  |  |

| 5 | Eva | luation                                                | 59 |  |  |  |

|   | 5.1 | Methodology and Metrics                                | 59 |  |  |  |

|   | 5.2 | Case-Studies                                           | 60 |  |  |  |

|   | 5.3 | Systems                                                | 61 |  |  |  |

|   | 5.4 | CPU-only Execution                                     | 62 |  |  |  |

|   | 5.5 | Comparison against GPU-only executions                 | 63 |  |  |  |

|   | 5.6 | Training Evaluation                                    | 69 |  |  |  |

|   | 5.7 | Work-load Derivation and Dynamic Balancing             | 70 |  |  |  |

|   |     | 5.7.1 Image Pipeline work-load distribution derivation | 70 |  |  |  |

|   |     | 5.7.2 Reaction to system's load changes                | 71 |  |  |  |

|   | 5.8 | Final Remarks                                          | 73 |  |  |  |

| 6 | Con | clusion                                                | 75 |  |  |  |

|   | 6.1 | Goals and Results                                      | 75 |  |  |  |

|   | 6.2 | Future Work                                            | 76 |  |  |  |

# List of Figures

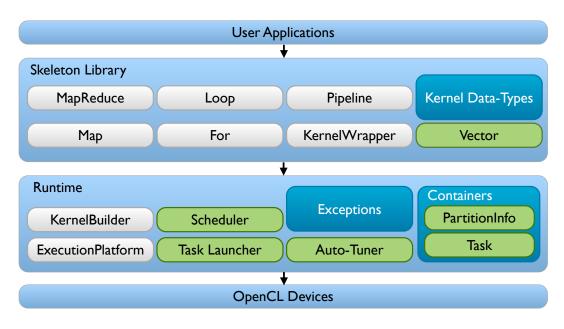

| 3.1  | Marrow's System Architecture                                                     | 26 |

|------|----------------------------------------------------------------------------------|----|

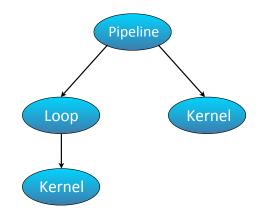

| 3.2  | Example of a computational tree                                                  | 27 |

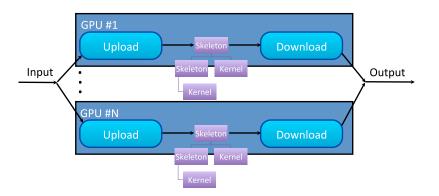

| 3.3  | Computational tree replication                                                   | 28 |

| 3.4  | Map skeleton execution                                                           | 28 |

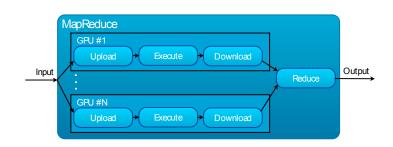

| 3.5  | MapReduce skeleton execution                                                     | 29 |

| 3.6  | Pipeline skeleton execution                                                      | 29 |

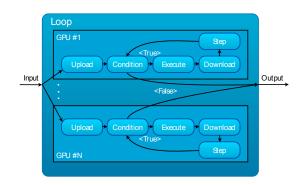

| 3.7  | Loop skeleton with parallel step computation                                     | 30 |

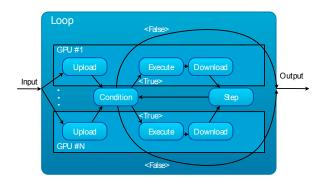

| 3.8  | Loop skeleton with synchronized step computation                                 | 30 |

| 3.9  | Skeleton Initialization                                                          | 33 |

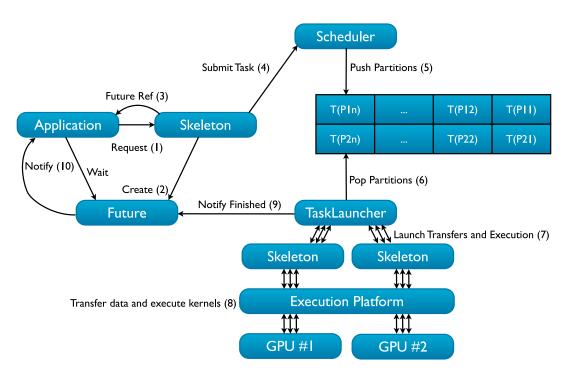

| 3.10 | Skeleton Execution Request                                                       | 34 |

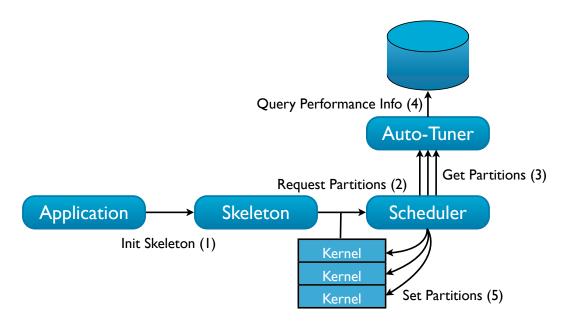

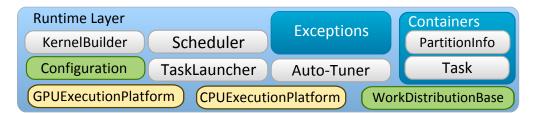

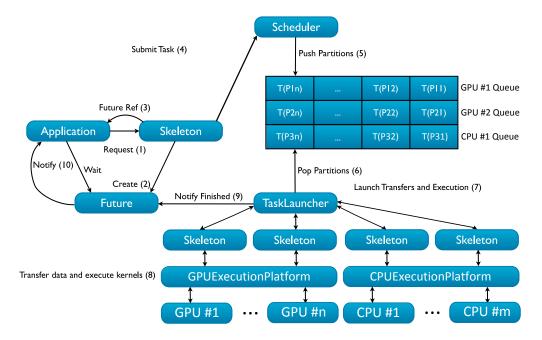

| 4.1  | Marrow's new Runtime Layer                                                       | 41 |

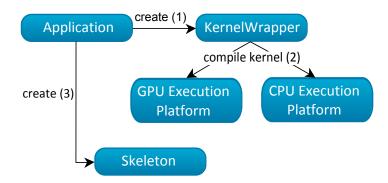

| 4.2  | Skeleton Creating stage                                                          | 45 |

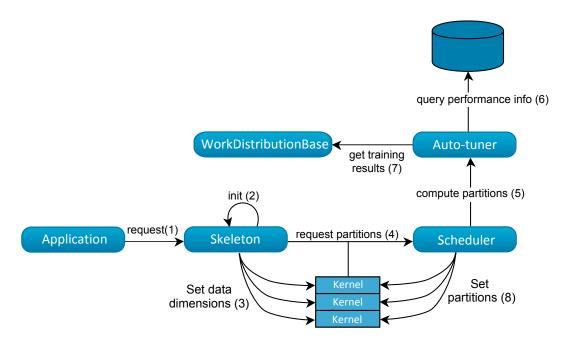

| 4.3  | Skeleton Work Partitionging stage                                                | 46 |

| 4.4  | Skeleton Request Execution stage                                                 | 47 |

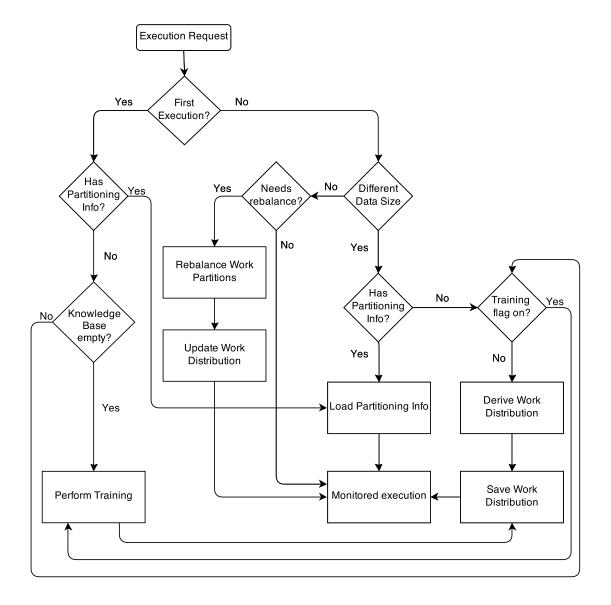

| 4.5  | Work distribution decision process                                               | 48 |

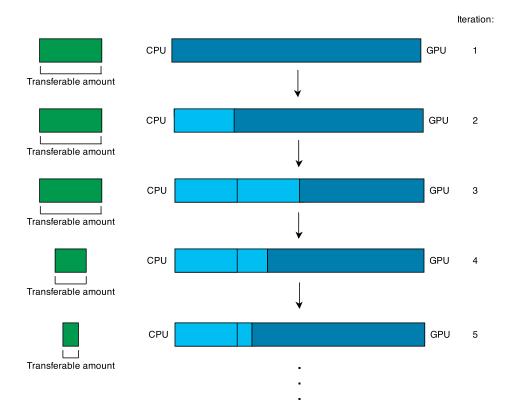

| 4.6  | 50/50 split training example                                                     | 52 |

| 4.7  | CPU assisted GPU execution training example                                      | 53 |

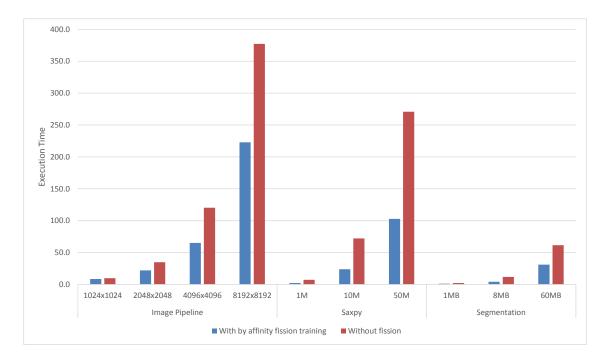

| 5.1  | Comparison of the execution times with and without fission for Image             |    |

|      | Pipeline, Saxpy and Segmentation benchmarks on system $S_1 \ldots \ldots \ldots$ | 63 |

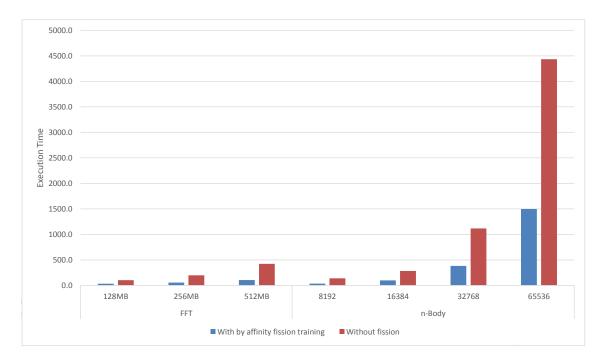

| 5.2  | Comparison of the execution times with and without fission for FFT and           |    |

|      | N-Body benchmarks on system $S_1$                                                | 64 |

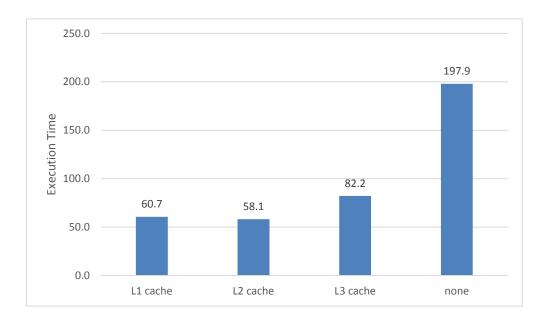

| 5.3  | Execution times measured during the training of FFT with 256 MB input .          | 66 |

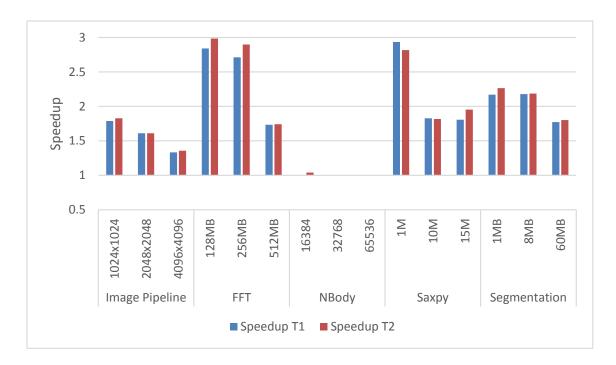

| 5.4  | Speedup for 1 GPU executions                                                     | 67 |

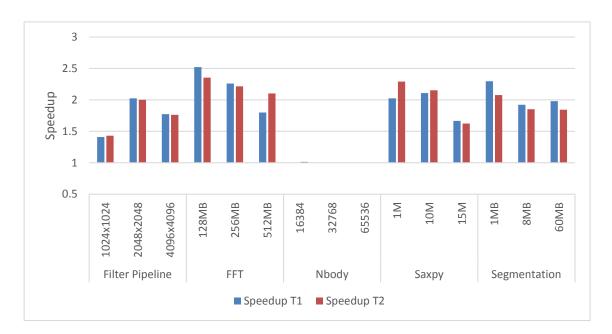

| 5.5  | Speedup for 2 GPU executions                                                     | 68 |

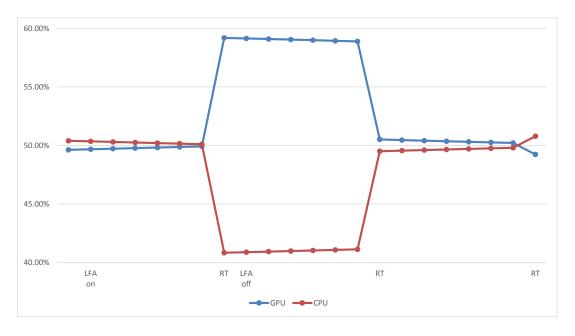

| 5.6  | Dynamic rebalance to system's load fluctuations                                  | 72 |

|      |                                                                                  |    |

# **List of Tables**

| 2.1 | Skeleton support by analyzed frameworks                                                     | 22 |

|-----|---------------------------------------------------------------------------------------------|----|

| 4.1 | Example of the evolution of <i>lbl</i> for $weight = 2/3$                                   | 55 |

| 5.1 | Systems characteristics                                                                     | 62 |

| 5.2 | CPU only executions in system $S_1$                                                         | 62 |

| 5.3 | Benchmark execution on system $S_2$ using 1 GPU $\ldots \ldots \ldots \ldots \ldots \ldots$ | 65 |

| 5.4 | Benchmark execution on system $S_2$ using 2 GPU $\ldots \ldots \ldots \ldots \ldots$        | 65 |

| 5.5 | Average benchmark duration for each                                                         | 70 |

| 5.6 | Filter Pipeline: performance obtained from the training's results                           | 71 |

| 5.7 | Filter Pipeline: performance obtained from the derivation of the work-load                  |    |

|     | distribution from past executions                                                           | 71 |

xviii

# Listings

| 3.1 | BufferData constructor                            | 28 |

|-----|---------------------------------------------------|----|

| 3.2 | Image Pipeline implementation in multi-GPU Marrow | 32 |

| 4.1 | BufferData constructor alterations                | 38 |

| 4.2 | Vector constructor alterations                    | 38 |

| 4.3 | KernelWrapper constructor alterations             | 39 |

| 4.4 | Image Pipeline implementation in Marrow           | 40 |

| 4.5 | Configuration File example                        | 42 |

# 1

## Introduction

#### 1.1 Motivation

The Graphic Processing Unit (GPU) is a common component found in virtually every modern computer. Over the past years, this kind of processors experienced a great evolution, mainly driven by the gaming industry, reaching a point where they can deliver high levels of performance, unachievable with modern Central Processing Units (CPUs), when executing graphics-related computations. These performance levels grow from the particular characteristics of GPU hardware, formed by many streaming processors, with clock frequencies generally lower. By being a common component found in today's personal computer's system, and because of its purpose specific architecture, the cost of this processors are often labeled as low-priced, considering the performance levels they can output [1]. Also, due to their lower clock frequencies, they are also energy-efficient solutions, all characteristics that make this units desirable to use in fields other than graphics processing.

Using the GPU in general purpose computations (GPGPU), although desirable, raises several challenges related to its parallel and graphics targeted architecture. Nonetheless, the potential of this hardware has driven a lot of research with the goal of providing a friendlier way to program this kind of processors, by implicitly taking care of intricacies related to memory management and work parallelization (for example [2, 3, 4, 5]), leading to a more general acceptance and recognition of GPGPU.

The emergence of higher level programming tools to deal with GPUs, obfuscate some of the low level details exposed by the base GPGPU programming frameworks, OpenCL and CUDA. As such, this processor became available to a wider range of programmers. However, GPU programming still requires much more effort from the programmer than the tools available for its CPU counterpart. Firstly, most of the current proposals only focus on providing a higher level interface for the GPU, leaving it to the programmer to identify which computations should be offloaded to the GPU and which ones should stay on the CPU. This will have an heavy impact on the system's overall performance as it will be dependent on the programmer's ability to identify and efficiently schedule computations on both processors, considering the intricacies of each of them. The offloading of an execution to the GPU must take into account the overhead introduced by the data transfers between the memory of both devices. On the other hand, when considering multi-core CPU computations, the memory is shared between different threads but there is still a need to partition the work among those threads, while avoiding race conditions.

Given the increasing utilization of the GPU in general purpose computing, our motivation grows from the belief that there is a need for tools that allow the programmer to address this heterogeneous system as a whole, delegating the work scheduling and efficiency concerns to the compiler/runtime system, providing a friendlier and generalized way to fully harness the available computing power of the underlying computational infrastructure.

#### 1.2 Problem

Programming GPUs, even with the support of high-level programming platforms, is still a more complex task than addressing sequential or even multi-core CPU processors. This complexity increases when there is a need to address both CPUs and GPUs, due to their different execution models. For this reason, it is desirable for these processors to be presented to the programmer as a part of a single computing platform. In our opinion, CPU/GPU heterogeneity should be handled at system level, being it by the language's compiler, a dedicated run-time system or, even, by the operating system. However, to accomplish such grounds, some challenges have to be surpassed.

The CPU and the GPU have different associated execution models due to their different architectures. For them to be presented as a single platform, there is a need to find a suitable model to address both this processors. This problem is only partially addressed by most of the current proposals, as their focus is on the GPU programmability. Some solutions support both GPUs and multi-core CPUs, but these must be used in mutual exclusion, or the device scheduling and work distribution is left to the programmer.

There is, however, a new trend of platforms that aim to address the system's underlying heterogeneity internally, providing the user with a unified programming platform. Some of these solutions simply pick the best performing device to execute a computation, without achieving device cooperation. On the other hand, the solutions that do achieve device cooperation, they either require different implementations of the parallelizable computation for the various devices, or they are too purpose specific and cannot be used in a wider range of applications. We believe that there is still work to be done, targeting implicitly schedule of different computations into the different processors in an efficient way, and without requiring extra work from the programmer to prepare the application to be executed on multiple devices.

In this work, we aim to exploit the abstraction power of the Algorithmic Skeletons to address this challenges. Skeletons, by definition, hide the implementation details of commonly found algorithmic patterns, providing a parameterizable interface to the programmer. Furthermore, since the skeletons encompass all the computation, they can convey, to the runtime system, all the information the latter requires to make the right decisions regarding work-load partitioning and work scheduling.

#### 1.3 Proposal

Our proposal grows from Marrow[6, 7], an Algorithmic Skeleton Framework (ASkF) for the orchestration of complex OpenCL-based GPGPU computations. Among its most notorious features, there are the skeleton nesting and the task-parallel skeletons, features not found in other GPU ASkF. Also, it implements a set of optimizations for performance improvement, including communication and computation overlapping.

The main goal of this thesis is to extend the Marrow framework so that it may take advantage of both the multiple CPU and the multiple GPU devices present in a single node architecture. Our motivation is to fully exploit the computational power available, in an efficient way, while maintaining the current level of abstraction provided by the supported skeletons.

In order to achieve this goal, we have to start by introducing the support for CPU computations in Marrow and subsequently guarantee the cooperation and work-load between CPU and GPU devices without the programmers' intervention. The current version of Marrow already supports multi-GPU devices, being that the division of the work is performed when the skeleton tree is created, restricting the data dimensions to the values defined upon creation. We propose to lift this restriction by creating a more dynamic solution where the system can adapt itself to the dimension of the inputted data and also to the current system's work-load.

Like in the current version of Marrow, in the solution we propose, the work partitioning will be achieved prior to the execution offload, avoiding the need for work transfers during runtime. However, the current work distribution method is based on performance values acquired prior to the applications execution that are used to calculate a performance ratio between devices. This approach is not suitable for work distribution among CPU and GPU devices, due to the huge differences in their architecture and execution model. Therefore, we propose a solution based on an offline training where different work distribution configurations are tested, to find the ideal work-balance for each different application. To address the possible work-load fluctuations of the CPU device, we aim to implement a lightweight monitoring of the running executions, comparing the performance of CPU and GPU devices and adjusting the work-balance when a significant performance gap is detected. Finally, we intend to explore the OpenCL device fission functionality to leverage locality in CPUs.

Our goal is to take advantage of the abstraction level provided by Algorithmic Skeletons to provide support for programming in heterogeneous systems, composed by multiple CPUs and GPUs, an approach that, as far as we know, is not addressed by the state of the art.

#### 1.4 Contributions

The main contributions of this work are:

- The introduction of support for multiple OpenCL device types in Marrow;

- Backend for CPU OpenCL executions;

- A framework that combines offline application training with online performance monitoring with specific algorithms for both stages.

- An evaluation of the performance gains of this implementation when compared to GPU-only executions, as well as an evaluation of the execution of Marrow in a CPU-only environment.

The work also makes two secondary contributions which are:

- Dynamic adjustment of work distribution in successive executions of a given Marrow computation. This implied modifications on the execution model and on the frameworks API;

- An evaluation of the OpenCL device fission functionality.

#### 1.5 Document Organization

The remainder of The remainder of this document is organized as follows:

- In Chapter 2, we analyze the current state of the art with a focus on GPU offloading frameworks, skeleton frameworks and automatic backend selection solutions;

- Chapter 3 describes the Marrow framework, in its multi-GPU version, which was the state of this framework prior to our work;

- In Chapter 4 we describe the modifications we implemented over Marrow in order to meet our goals.

- The evaluation of our work is presented in Chapter 5, focusing on the performance gains achieved by using both CPU and GPU devices, when compared to GPU-only executions;

- Finally, in Chapter 6, we revisit the our goals and introduce some ideas on how the Marrow framework could be further extended.

6

# 2

## State of the Art

Algorithmic skeletons have been a recurrent solution for abstracting parallelization intricacies in homogeneous and heterogeneous environments. The abstraction layer provided by skeletons has proved to be useful under different system configurations, from single node computers to clusters and grids. In this chapter, we analyze the existing work regarding skeleton frameworks (and similar solutions, like language templates), with a focus on tools directed to GPU and/or CPU parallel programming.

Before describing the existing tools related to our work, we start by introducing the concept of algorithmic skeletons and describing the skeletons more commonly found in the existing frameworks. We also introduce the concept of heterogeneous computing and characterize the most common approaches to this paradigm. Given our focus on both CPU and GPU programming, we also include some tools that target multi-core CPU computing through algorithmic skeletons.

#### 2.1 Algorithmic Skeletons

The concept of algorithmic skeletons was proposed by Murray Cole, in 1989 [8]. The algorithmic skeletons model tries to identify commonly used patterns in parallel programming, namely concerning computation, communication and interaction [9], to provide a higher level of abstraction. Software developers need only to choose the skeleton that better fits the problem at hand. This greater level of abstraction enhances portability since the particularities of each architecture will be internally handled by the skeletons. This allows for each skeleton to be extensively optimized for each different architecture, resulting in levels of performance hard to achieve without this level of abstraction. Moreover, by abstracting the programmer of the parallel programming concerns, this model also prevents typical programming errors derived from its extra complexity, resulting in a more efficient way to develop software.

Algorithmic skeletons were firstly thought as a solution for cluster computing. The distributed nature and hardware diversity of cluster computing demanded programmers to be aware of the underlying hardware's characteristics. This resulted in hardware-specific programs, with hard portability and probably poor performance in different systems, with distinct hardware specifications, since they were only optimized for the system they were developed to. Also, determining which part of a program could and should be parallelized was not always a trivial task and could also be dependent on the underlying hardware's idiosyncrasies, resulting in a solution that may not be optimal for that particular system. Moreover, the behavior of a system comprising several parts that work in parallel is harder to predict than the behavior of a system that works sequentially. As soon as general purpose computers began to incorporate parallel hardware, the concept was adopted to single machine computations, not only for multi-core CPUs, but also for GPUs.

Skeletons can be divided in three main categories: Data-parallel, Task-parallel and Resolution skeletons. Data-parallel skeletons handle problems with large data structures, dealing with challenges such as splitting the data among all running threads and merging the results after a routine is applied. Examples are *Map*, *Reduce* and *Zip*. Task-parallel skeletons deal with problems related to task interaction, like communication and synchronization. Examples are the *Pipeline*, *Farm* (also know as *Master-Slave*), *For* and *While*. Finally we have the Resolution skeletons, which define algorithms to solve a family of problems. Two examples are the *Divide & Conquer* and the *Branch & Bound*. We now describe the most popular skeletons included in these categories.

- Data-parallel

- Map Applies a function or a sub-skeleton to all elements of a set of data. This skeleton can be conceived as a Single Instruction, Multiple Data (SIMD) skeleton as parallel threads running the same instructions can be applied concurrently over different data elements.

- Reduce Scans a data-set from left to right applying a function to each pair of elements, resulting in a single element being produced. The concurrency potential will depend on the associativity property of the function applied. This skeleton is also called *Fold* by some frameworks.

- Scan This skeleton has a behavior similar to Reduce, the difference laying in the resulting type. Instead of a single element, Scan returns a data-set of the same size as the input, where each element is the result of applying the reduction function to all the elements in the input set with lower or equal indexes. This intermediate results are important to a subset of algorithms and that is why some frameworks support this skeleton.

- Zip This skeleton receives two data-sets and an operator as input, and outputs the resulting set of applying the operator over the input elements with the same position.

- Fork This skeletons works similar to map but a different function is applied to each element of the data-set, making it into a Multiple Instruction, Multiple Data skeleton.

- Task-Parallel

- Farm Also known as *Master-Slave*, consists in the creation of independent tasks, achieving parallelism through scheduling different tasks to distinct resource, so they can be simultaneously computed.

- Pipeline This skeletons consists in the notion of staged computations where the output of one stage is the input on the next one. Since each stage is dependent on the termination of the previous stage, parallelism can only be achieved through executing different stages simultaneously on different inputs.

- For Executes a sub-skeleton or a function for a specified number of times.

Parallelism can only be achieved if the result of one iteration is independent of the result of the previous one.

- While Behaves like For but instead of iterating a fixed number of times, the cycle termination is decided by a condition.

- Resolution Skeletons

- Divide & Conquer (D&C) This skeleton can be viewed as a generalization of the Map skeleton. It works by recursively splitting the problem into subproblems and calculating partial solutions in parallel, merging the results in the upper levels of the recursion, ultimately reaching the global solution.

- Branch & Bound (B&B) B&B algorithms are applied on NP-hard problems where reaching the optimal solution is only possible with algorithms with exponential complexity because it requires all the possible solutions to be tested. Instead of looking for the ultimate optimal solution, B&B skeletons try to reach the best solution by recursively test several possible solutions until a bound is met. It works by finding an initial possible solution, calculate its optimality value (known as *fitness*) and generate alternative possible solutions based on that one. The same process will be recursively applied to every possible solution, but only the solutions with the best fitness value will be further explored. The algorithm will terminate when a determined bound is met. That bound can be either time-based, cycle-based or when a solution with a fitness value over some pre-established limit is met.

#### 2.2 Heterogeneous Computing

Heterogeneous computing systems are not a new concept. For a long time, purposespecific processors have been used to assist the CPU in some particular operations. The most notorious example of a purpose-specific processor is the GPU, a processing unit in charge of graphics processing in almost every nowadays computer. This kind of processors are very optimized for graphics related operations, outputting high performance levels, generally not achievable by the general-purpose processor when performing this type of tasks. GPUs were firstly design as fixed function pipelines [10], meaning that a pre-determined set of functions were specified in the hardware, and implementing a new function was only possible through hardware modifications. Nonetheless, the scientific simulation community identified an untapped computation source that could be leveraged in their highly resource demanding computations. The downside of these processors was that, being design with specific intents, it was really hard or even impossible for programmers to implement operations that differed from the processors original purpose. However, this new interest, conjoined with the evolution of GPU hardware, potentiated this kind of processors to become increasingly more programmable, allowing them to be applicable on a wider range of fields, ultimately leading to the rise of the GPGPU (General-Purpose Computing on GPU) concept. GPGPU is the designation of using the GPU for computations involving non-graphical tasks.

Despite being programmable, the existing APIs for GPUs (like OpenGL), were targeted to graphics processing and all the operations had to be addressed as graphical problems, meaning it was still really hard to program and take full advantage of this processors, when addressing problems other than graphical ones. This lead to an effort to reach more generic APIs. Brooks [11] was the first attempt, and although it was not adopted by the industry, it was an important proof of concept to show the potential of GPUs in different grounds. Consequently, it was not long until the industry itself recognized that potential and in 2006, NVIDIA, one of the main GPU manufacturers, unveiled CUDA [12], the first actual solution to GPGPU.

After NVIDIA released CUDA, other manufacturers wanted to join the race. Being created by NVIDIA, CUDA was only supported by NVIDIA graphical cards and the community craved for the specification of an open standard for GPGPU. Such necessity spawned the OpenCL [13] proposal, a standard specified by the Khronos Group and today is implemented by a large list of manufacturers, including NVIDIA, Intel, AMD and Apple.

The existence of an open standard further paved the path for the continuous growth of GPGPU field, but some challenges are yet to overcome, namely the increasing of the abstraction level. CUDA and OpenCL are too close to the hardware and the programmers still need to have some insight about the GPUs architecture to take full advantage of the parallelism they offer. This difficulty, together with the necessity to support other programming languages other than C or C++ (the languages supported by CUDA

and OpenCL), let to numerous independent efforts to bring GPGPU programming to an higher abstraction level. Our focus is on tools that allow orchestration of GPU and CPU computing, instead of just making GPU computations available to the programmer.

#### 2.2.1 On the programming of Heterogeneous Systems

The popularization of the GPGPU led to the proliferation of GPU programming frameworks. On one hand, pre-existing parallel programming frameworks have been extended to benefit from the power of this processors. On the other, this device propelled the rise of new solutions developed from scratch with the GPU programming in mind. GPGPU has been tackled from different angles. Regarding the programming support, the most popular approaches are the directive-based frameworks, programming languages and high-level libraries.

**Directive-based frameworks** are tools that convert source code written in the host programming language (like C or Fortran) into code of another language (like CUDA or OpenCL). These, tools, also known as source-to-source compilers, aim to have a minimal impact on the sequential version of the code, requiring little to no modifications to the source, other than the directive annotations (also known as pragmas) on the parts of the code that can be parallelized. Therefore, despite providing a unified programming model, it still relies on the programmer to identify the parallelizable parts of the program and to specify how the compiler must interpret such code. Also, additional options can be specified, in order to increase the program's performance. Two examples of such compilers are hiCUDA [14](C-to-CUDA) and Bones [15] (C-to-CUDA and C-to-OpenCL).

Another way to provide GPU support in a higher level is through **native language level support**. Some programming languages directed to cluster computing, like X10 [16, 17] and Chapel [18, 19], have been adapted to keep up with the GPGPU trend, others, like Lime [20], have been design from scratch with GPU programming in mind.

GPU support can also be provided through **high-level libraries** that hide certain lower level aspects of GPU programming, like device communication and computation offloading. A common way to provide abstraction over the GPU parallelization is through algorithmic skeletons, or templates (like SkePU [3] and SkelCL [2]), identifying common parallelization patterns and providing a generalized implementation of such patterns, leaving it to the programmer to just parameterize them according to the specificities of the application.

In the context of our work we are more interested in classifying these frameworks according to their support for heterogeneous computing. Accordingly, we will divide them into three categories, which will drive the structure of remainder of this section:

- **GPU offloading tools:** These are the tools that focus solely on offloading computations to one or more GPU devices, without support for other backends;

- Multi-backend with single or explicit offloading: In this category we include

frameworks that provide support for both GPUs and multi-core CPUs (and possibly other backends), but each computation is explicitly offloaded by the programmer, or when only one backend is active at a time, the remaining working as a fallback in case the primary backend cannot execute the computation;

• Automatic Backend Selection: This category contains the tools that not only provide support for multiple backends (GPUs, CPUs and possibly other devices), but also provide mechanisms to implicitly distribute work-load among such devices.

#### 2.2.2 GPU offloading tools

**SkelCL** [2] is a C++ skeleton framework that provides support for multi-GPU executions through OpenCL. SkelCL provides implicit data exchange through an abstract vector data type and lazy copying to minimize communication overhead between devices. Every skeleton in SkelCL receives a vector as input and produces a vector as output. To generate an OpenCL kernel, every skeleton receives a function as a string parameter that will be merged with the skeleton's own source to form the OpenCL code. The kernel is compiled during runtime, but since it can be a time-consuming task, after compiled, the compiled kernel is stored on disk for future utilizations. To pass more arguments to the kernel function than the number defined by each skeleton, every skeleton can receive an additional argument, an object of the type Arguments. All the additional arguments must be packed inside this object and passed to the skeleton. When multiple GPUs are present, a vector can be distributed through all the available devices, either by completely copying them to every device, or evenly splitting the vector into different parts, to perform executions over the array simultaneously by all the the devices. SkelCL provides skeleton-specific distribution so the vector can be divided implicitly, although, the programmer can take control and explicitly set the Vector's distribution. Also, data exchanges between multiple devices is automatically performed by the library. The skeletons supported are Map, Zip, Reduce and Scan, without nesting capabilities.

**Marrow** [6, 7] is a C++ skeleton framework focused on orchestration and execution of OpenCL kernels on multiple heterogeneous GPU devices, as well as introducing optimizations to the overall execution. Besides the typical data-parallel skeletons, like Map and Reduce, provided by most of the skeleton frameworks, it also provides support for some task-parallel skeletons like Pipeline and Loop (While and For). Another advantage over other libraries, is that Marrow offers support for skeleton nesting, allowing for more complex algorithmic structures to be specified. The parallel computations are defined and submitted as native OpenCL kernels, although, low-level functionalities like error-handling and memory management are abstracted from the programmer. This skeletons are encapsulated in an object called KernelWrapper allowing skeletons to easily access them when orchestrating an execution.

The Marrow framework takes advantage of the modern GPU's capacity to perform

simultaneous bi-directional data transfers between host and device, while executing computations and applies a technique called overlap between communication and computation. This technique reduces GPU's idle time by optimizing the scheduling and issuing of operations with memory transfers between the host and the device.

The execution model in Marrow can be viewed as a Master-Slave pattern, where a task is submitted for execution and the application is allowed to continue to perform additional computations. When an execution is requested, it is queued and an associated *future* object is created and referenced to the application. This object allows the application to query the state of the execution as well as waiting for the execution to finish.

**OpenACC** [21] is an open standard for parallel programming, resultant of the effort of a group of vendors to improve code portability between different implementations. This standard defines directives similar to those found in OpenMP, an already well-accepted standard for parallel programming with multi-core CPUs. There are several compilers implementations of OpenACC, both commercial (PGI [22] and CAPS [23]) and opensource (accULL[24]), but since they all obey to the same specification, the same code can be compiled with the different compilers with no need for code modifications.

**X10 [16, 17] and Chapel [18, 19]** are two programming languages that use the APGAS (Asynchronous Partitioned Global Address space) [25] model, an extension of the PGAS model. The PGAS model tries to create a level of abstraction over the global address space of a distributed system, making any data (local or remote) directly accessible by any process regardless of its location, without never completely suppressing the notion of local and remote data. By being aware of the data location, it is possible to reduce the performance problems associated with the GAS solutions, where the programmer was completely abstracted from the data locality. The APGAS, as the X10 team as defined it, introduces two new concepts: *places* and *asyncs*. A place is the abstraction of an entity on which computations are executed. A place can be mapped to an x86 core, a multi-core processor or even a GPU. Places are not required to be single-threaded and a place can be defined hierarchically, allowing for the exploitation of the hierarchical design of an architecture. A place can be stored in a variable and passed to functions as an argument. This model allows for explicitly requesting an execution to take place on a determined place. The APGAS model goes even further and allows for that execution to be asynchronous, through the async statement.

X10 is a programming language developed by IBM as a solution for clusters of multicore CPUs and has later been extended to support GPUs. In X10, a GPU is represented by a subplace of the hosting place. The memory allocation on the GPU is done in a way similar to CUDA or OpenCL. For memory transfers between the GPU and the host, X10 provides an API that mirrors Java's System.arrayCopy (Array.asyncCopy), but it allows one of the arrays to be a remote reference and the copy is made asynchronously. The native X10 synchronization mechanism, clocks, is also usable inside a GPU to provide a barrier mechanism to synchronize shared memory access. In practice, the programming of the computation offloaded to the GPU is not very distant from the abstraction level of CUDA or OpenCL. The programmer must explicitly express which asynchronous activities must be executed on GPUs. Also, in such cases, the execution of said activities is specified inside two nested loops, iterating over each block and then over each thread of the GPU, requiring the programmer to be aware of the adjacent execution model.

Chapel is a programming language developed by Cray that aims to provide a higher level of parallel programming while allowing the programmer to drop to a lower-level specification allowing for specific algorithm tunes to be performed. Unlike X10, the GPU is not represented as a subplace of the host, it is however, an integrated parted of the host's *locale* (a place in Chapel). When allocating memory in Chapel, the *dmapped* keyword is used, followed by the keyword to specify the domain where the memory is to be mapped. Allocating a variable on the GPU memory is achieved by using the GPUDist as the domain keyword. Data parallelism is achieved through the *forall* loop declaration. If a forall loop is applied over a variable mapped to the GPU, the compiler will automatically generate a CUDA kernel with the body of that loop and that will execute that computation on the GPU. The memory transmissions between the host and the GPU is implicit by default but can be set to explicit when the memory is mapped by using the GPU-*ExplicitDist* keyword. Chapel also offers explicit access to specialized memory spaces of the GPU, like shared memory, constant cache memory and texture cache, by simply mapping the memory with respective keywords. Besides the forall operator, Chapel also offers support for the higher level operators *reduction* and *scan*, allowing those operators to also be defined by the programmers. Although GPU computing in Chapel is much more abstract than in X10, the programmer still has to decide what must the executed in each processing unit.

**Lime [20]** is a programming language for hybrid computation, comprising architectures involving multi-core CPUs, GPUs and also FPGAs. It is a language inspired in the Java programming language and attempts to achieve maximum compatibility with Java, in a way that code compilable with the Java compiler can also be compiled with the Lime compiler. The reverse can also happen if the Lime code does not make use of Lime exclusive features that do not exist in Java.

Lime allows for the creation of workflows that can be described as a direct graph of computations where each edge represent a task and the output of each task is the input of the next task in the graph. That being said, the two most important operators in Lime are the connect operator (=>) and the task operator (*task*). Each task represents a computational unit, equivalent to an OpenCL kernel, while each connector denotes the flow of the data between two tasks. In Lime, a task can be either *isolated* or *non-isolated*. An isolated task (also called *filter*) is a task that can only access its own address space and has no access to the global state. The job of each task is to apply a method (called *worker method*) as long as there is still input to be processed, and enqueue the result into

an output stream. Also, by explicitly declaring the communication between tasks (using the connect operator), it is possible for the compiler to optimize and synchronize the communication between tasks automatically, without the programmers intervention.

Lime also has support for the map-reduce model. The map function is represented by the @ token and applies a function to each element of an aggregate data structure, returning another aggregate data structure. On the other end, by using the token ! after an operator or method, the Lime compiler will treat it as a combinator to execute a reduction, as long as the method applies the computations to two arguments of the same type and returns a result of that type.

The Lime compiler implicitly determines a partitioning of the program between the CPU and the GPU. For a task to be electable to be offloaded to the GPU, it must not be the first nor the last task in the stream and it must be an isolated task, guaranteeing that it does not perform globally side-effecting operations. The compiler also searches for map and reduce operations within each filter to identify kernel-level data-parallelism opportunities. For a map function to be compiled for the GPU, it has to be static and local, and the arguments must be value types, guaranteeing that the function is side-effect free.

#### 2.2.3 Multi-backend with single or explicit offloading

**Muesli [26]** is a skeleton library that started with a focus on multi-node clusters and has been continuously adapted to support multi-core processors and more recently, GPU processors, combining MPI, OpenMP and CUDA. Although it supports both multi-core CPUs and GPUs, Muesli does not support the combination of CUDA with OpenMP. Also, the platform does not choose where the execution will take place, meaning that it has to be specified in the code whether the execution will take place in the CPU or in the GPU. Like most of the skeleton libraries, Muesli takes care of memory transfers implicitly, through lazy-copy mechanisms to reduce the communication overhead. Kernels are defined in a CUDA-like way, without no higher level abstraction. Muesli implements both Data (Map, Zip, Fold and Scan) and Task-parallel skeletons (Farm, Pipe, D&C and B&B), although, GPU offloading is only available for Data-parallel skeletons. The same goes for skeleton nesting, as the library supports skeleton nesting but since you cannot nest skeletons inside data-parallel skeletons, it can be concluded that skeleton nesting is not supported for GPU computations.

**Thrust [27]** is a C++ template library of parallel algorithms and data structures for CUDA. In Thrust, memory management is explicitly declared, although, it is greatly simplified by vector containers. When specifying a vector container, either a host\_vector or a device\_vector, the memory will be automatically allocated in the specific device. Also, deallocation and dynamic resize will be taken care by the library. Memory transfers can easily be specified by using the = operator or the copy function. Kernel launching is abstracted by Thrust's interface as the programmer only has to call the template function. Thrust already provides most of the built-in arithmetic and comparison operators to be

used in the template calls, but it is also possible for the programmer to declare his own. Thrust also provides an OpenMP and a TBB backend that can be specified during compilation, without any modifications to the code, although, two different backends cannot coexist.

**Bolt** [4] is also a C++ template library, developed by AMD on top of OpenCL. Bolt is in many ways similar to Thrust. Device and host memory is also explicitly declared through a vector container (std::vector or device\_vector), providing a simpler way to manage memory than in OpenCL declarations. Unlike Thrust, however, if the data is allocated in the CPU memory space and the computation will take place in the GPU, the data will be automatically copied to the GPU memory. Besides OpenCL, Bolt functions can also be executed with a TBB backend or in a serial way in the CPU, although, and like Thrust, it provides no support for different backends to coexist. By default, Bolt functions will try to run computations on the GPU with OpenCL, if it fails it will fall back to TBB and then to serial execution.

**Aparapi** [28] is the result of an effort aimed towards providing GPU computations using the Java programming language, by converting Java bytecode into OpenCL. It also aims to maintain the Java's principle of "Write Once Run Anywhere", meaning that if a GPU is not available, does not support OpenCL or, for some reason, the OpenCL code cannot be generated, the computation will be carried out by a Java thread pool. This characteristic makes Aparapi an interesting platform since code suitable for the execution on GPUs can also be executed on CPUs. Although, the sections of the program that are meant to be run on the GPU have to be explicitly declared meaning that the platform has no mechanism to implicitly schedule the working load to the different processors. Also, Aparapi offers no abstraction level over the kernel code. The code is written in Java, but the abstraction level is the same of an OpenCL kernel, as the programmers are aware that they are writting the code with the partial vision of each thread.

**Bones** [15] is a source-to-source compiler in which the compilation is achieved through algorithmic skeletons. In Bones, algorithms are classified into different classes and when the programmer is declaring a pragma to signal parallelizable code, it defines the class in which the algorithm falls into. This will allow the compiler to merge the programmer defined code with the generic code of the skeleton for that class. The resulting code already takes care of memory allocation and data transmission between devices. Bones has no support for multiple GPUs nor skeleton nesting. Supported backends are CUDA and OpenCL (both for GPU and CPU), although, not all the skeletons supported by the CUDA backend are supported by the OpenCL one.

A Flexible Shared Library Profiler for Early Estimation of Performance Gains in Heterogeneous Systems [29] is a work that addresses heterogeneous architectures through

a shared library interposing technique, that replaces shared library calls, by calls to a wrapper library that will choose among alternative implementations of the shared library, based on a performance prediction model. Given that the wrapper library and the alternative implementations have the same ABI (Application Binary Interface) of the original library, one of the advantages of this technique is that it does not require any modifications to the original application, nor to the original library.

The framework starts by analyzing the application's executable file in order to identify the shared library calls. It then generates a wrapper library that calls the original shared library functions and traces all the calls to each function while collecting profiling data. The next step is to execute the application with the wrapper library preloaded, for a significant number of operating conditions, so the profiling information can be collected. This profiling information is then combined with the performance models for each of the alternative implementations, allowing for a performance prediction during runtime, depending on the operating conditions like the input work size.

The downsides of this model are the need for the existence of different shared library implementations, and the fact that only one implementation is selected to execute, not taking advantage of possible performance gains by distributing the work-load between different implementations (that execute on different devices).

## 2.2.4 Automatic Backend Selection

**SkePU** [3] is a skeleton library that was originaly built with multi-core CPUs and multi-GPUs in mind. Like Muesli, memory transfers are achieved through lazy-copying mechanisms and memory locality is abstracted through a vector interface. The library supports both OpenCL and CUDA backends, for GPU executions, as well as an OpenMP backend for multi-core executions. All backends have the same interface, meaning that the programmer does not have to be aware of where the execution will take place while programming. Kernels are also not explicitly declared, instead, the programmer only defines the function to be applied by the skeleton via a small set of predefined C macros.

This framework has recently evolved to integrate automatic backend selection support[30]. Although there is no cooperation between the different devices, as only one implementation is selected to perform an execution, the control of which backend to offload an execution is no longer left upon the user. Instead, the platform implicitly determines the best performing device, based on the received data size and the performance information gathered during an offline training.

SkePU's offline training is based upon the premise that if an implementation is the best performing for a data size i and for a data size j, then, all data sizes between i and j will also perform best with said implementation. The training algorithm starts by evaluating the best performance for the lower and the upper bound data sizes (default or user-specified). This information is stored on the root node of a tree. The remaining of the tree is then constructed by recursively dividing each dimension's subspace, until equal

winners of a subspace are found, considering the respective leaf node, a *closed node*. The training terminates when all the leafs of the tree are closed, or upon reaching a maximum tree depth or training timeout, specified by the user.

In parallel to the training project, there's a parallel project aiming to integrate SkePU with StarPU [31]. StarPU is itself a heterogeneous computing library that pays close attention to the efficient scheduling of tasks through the several available CPUs and GPUs, which combined with SkePU, gives the programmer the abstraction level of the skeletons as well as a dynamic scheduling of the tasks, resulting in lighter burden over the programmer and more efficient final results. However, there is still no work-load distributions among different devices, meaning that device concurrency is only possible with the submission of multiple tasks. SkePU only has support for data-parallel skeletons like Map, Reduce and some variants of those two and does not support skeleton nesting.

**StreamIt [32, 33]** is a programming language that was developed as a response to the crescent increase of parallel streaming applications. It attempts to provide the programmers with a more natural way to define a stream, while it performs stream-specific optimizations, achieving levels of performance close to optimized code written in a lower-level language. The basic unit of computation in StreamIt is the *filter*, which represents a computation that is executed over a stream of data. Each filter holds two types of communication channels, the input by which the data is received, and the output, where the results of the computations are sent to. A stream can be represented by a hierarchically organized graph and the constructs can be of three types: *pipelines, split-joins* or *feedback loops*. The pipeline is the most basic construct where each filter is connected to the next one. In a split-join construct, the flow of the data is divided into independent substreams by the *splitter* and later is rejoined by the *joiner*. A splitter can either apply each element to every of its substreams, to allow for different filters to be applied over the same data but it, can also apply each element to only one substream, allowing for weight distribution. A feedback loop allows for the existence of cycles in the stream flow graph.

StreamIt is another example of a language that has evolved to support GPU computations, although in this case, only the compiler was modified to be GPU aware. The stream application can be represented as directed acyclic graph (given that in this version, some advanced features like feedback loops are not supported). The platform processes the stream graph through a coarsening and a uncoarsening phase, grouping nodes (*filters*) into partitions, taking into account performance and communication time estimations, while also taking advantage of the on-chip GPU shared memory, in the most efficient way.

After the partitions are created, they are distributed among the present GPUs, with the exception of the partitions that maintain an internal state, that are pre-mapped to the CPU. Besides this exceptions, the CPU is used to control the GPU's execution (one dedicated thread per GPU device). The framework internally manages communications between partitions inside each GPU device, as well as inter-GPU communication. Adaptive Runtime Selection for GPU [34] is a work addressing online performance prediction, based on an offline profiling stage. This solution consists in converting C source code, identified by pragmas, to CUDA code, through a source-to-source polyhedral compiler. During this code conversion, various optimizations are performed, like identifying data reusability, to take advantage of the GPU's shared memory. When the CUDA code is compiled, various versions of the code are generated, differing in some parameters, like tile and block sizes.

The next step is to perform an offline profiling stage. This profiling stage is divided into two stages. During the first stage, data communication between the host and the GPUs is evaluated, building a table that matches message sizes with the expected communication times. The second stage consists in the simulation of the different generated versions of the CUDA kernel, under different execution contexts.

Finally, at runtime, the framework estimates the total execution time of each kernel implementation, considering the execution and communication information gathered during the offline profiling stage. The version with the best predicted global execution time is selected to run. Simultaneously, the same computation is prompt at the CPU as well. When one of the executions finishes, it signals the other one to interrupt its execution. Although this solution performs concurrent executions in the CPU and GPU devices, there is still no cooperation between the devices, as the results of one of the executions will be discarded.

Accelerating MapReduce on a Coupled CPU-GPU Architecture [35] is a work that addresses the execution of MapReduce computations in nodes comprising CPUs with integrated GPU. This work proposes two approaches for using both these devices in a cooperative way: one where both the Map and the Reduce stages are executed by both processors (*Map-dividing Scheme*), and another, where each of those stages is executed in a different device (*Pipelining Scheme*). Both these devices rely upon a dynamic work distribution approach and implement continuous reduction.

In the *Map-dividing Scheme*, the scheduler is responsible for dispatching the input data to each worker. In a GPU, a worker corresponds to a workgroup. In the CPU, each core is a worker, except for the first one that is responsible for the dynamic schedule, based on the master-worker model. Inside each worker, the input data is divided among the working threads to execute the map function. Each worker has also a reduction object, responsible for the partial reduction of the output of each of its belonging thread. When the end message is received by the workers, one reduction object per device will perform a reduction of the reduction objects of its workers. In the end, these intermediate results are combined to produce the final result.

The *Pipelining Scheme* is based on a producer-consumer model. In this case, the map device performs the map function over the input data, in the same fashion as it happens in the *Map-dividing Scheme*, but instead of local reduction objects, the output of the map function is placed on a circular buffer (one for each worker), placed in the zero copy

buffers, as they are accessed by both devices. The reduction device is also composed by multiple workers, that perform a partial reduction function. When the scheduler identifies an idle reduce worker, it will assign it a full key-value block from one of the circular buffers. At the end, a global reduction object will reduce the results of all the partial reduction objects.

There is also a static load balancing approach for this scheme. This approach eliminates the need for a scheduler and therefore, all the CPU cores will work as workers. The input is evenly distributed among the map workers and the output is stored on the circular buffers (also one for each worker). Since there is no scheduler, the key-value blocks present in the circular buffers are evenly distributed among the reduction workers.

**Transparent application acceleration by intelligent scheduling of shared library calls on heterogeneous systems [36]** continues the work presented in [29], described previously. In this work, the authors extend the previously proposed framework, so, when not limited by the data/control dependencies, the system automatically distributes the work-load among different devices (through different library implementations).

Unlike their previous work, this works follows a dynamic performance model construction during runtime, instead of during an offline profiling. The task scheduling follows one of two policies: the *Best Performance Selection* policy, when the working data cannot be divided among different devices; and the *Load Balancing* policy, when work partitioning is possible.

In the *Best Performance Selection* policy, when the best performing implementation is not known for the given work size, the performance model is constructed by executing the application using all the implementations (simultaneously). The following executions will only be executed by the fastest implementation. Every time the application is executed, the performance model is updated so it may adapt to eventual alterations in the running environment, such as a system's load variation.

The *Load Balance* policy follows a load balancing approach that tries to balance the work-load in a way that all executing devices finish their execution at the same time. This process is also dynamic and based on a Functional Performance Model principle. For the first iteration, since there is no performance information, the work-load is evenly distributed among the devices. In the following iterations, the FPM of each device is updated and a new load distribution is calculated, gradually getting closer to the ideal work distribution.

**Transparent CPU-GPU Collaboration for Data-Parallel Kernels on Heterogeneous Systems [37]** is a solution for transparent orchestration of CPU and GPU OpenCL computations. They address device heterogeneity by executing a different number of work-groups in each device to achieve work-load balance. The work partitioning is performed by a dynamic compiler composed by three modules: the *kernel transformer*, the *buffer manager* and the *partitioner*.

The kernel transformer is responsible for converting the original kernel, preparing it to work only over a subset of work-groups. After this step, the buffer manager analyses the memory access patterns of each work-group. If the memory accesses can be determined statically, only the necessary data is transferred to each device. Otherwise, the input is replicated through all the devices and the output will be merged. The partitioner is responsible for deciding the number of work-groups to execute in each device, based on profiling information. That profiling information is gathered in a single time basis, by launching executions with s different number of work-groups to each device, while gathering performance results.

# 2.3 Skeletons and Template-based Frameworks for Multi-core Computing

In this section, we will visit some multi-core framework solutions that use algorithmic patterns.

**Skandium [38]** is a Java algorithmic skeletons framework (ASkF). It stands as a reimplementation of Calcium [39], a Java ASkF for cluster environments, but targeting multi-core computers instead. Skandium provides support for both Data (Map and Fork) and Task-parallel skeletons (Farm, Pipeline, for and while) as well as the resolution skeleton D&C. Skandium also allows for skeleton nesting. Besides skeletons, there is another important concept called *muscle blocks*. Muscle blocks are sequential blocks of code that provide the logical needed to transform a general skeleton into a specific application. Muscle blocks can be viewed as black boxes that are invoked by the skeletons and depending on the skeleton they can be executed either sequentially or in parallel.

In Skandium, all the communications between devices are implicit, however, it does not provide any higher level shared-memory protection mechanism, meaning that the programmer has to be aware that the muscle blocks may execute concurrently, and take the right measures to avoid race conditions, guaranteeing the correct results. This may have an impact on performance, since a part of the program has to be serialized and it is up to the programmer to identify the critical section.

Skandium offers a dynamic scheduling, based on a producer/consumer scheme. The initial task is inserted into a task queue. Multiple threads will consume and compute tasks from the ready queue. A task can generate sub-tasks that will be inserted into the task queue, and can be kept in a waiting state until all its generated subtasks have finished executing, allowing for other tasks to be executed. When the task exits its waiting state, it is re-introduced into the task queue to be scheduled to continue its computations.

**Intel Threading Building Blocks [40]** (TBB) is a C++ template library developed by Intel for parallel programming on multi-core processors. Although it does not label itself as a skeleton framework, its pattern-based abstraction approach has evident similarities

|          | GPU          |              |              | CPU          |              | GPU/CPU      |              |              |

|----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

|          | SkelCL       | Bolt         | Thrust       | Marrow       | Skandium     | TBB          | Muesli       | SkePU        |

| Map      | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | X            | $\checkmark$ | $\checkmark$ |

| Reduce   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | X            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Zip      | $\checkmark$ | X            | X            | X            | X            | X            | $\checkmark$ | X            |

| Scan     | $\checkmark$ | $\checkmark$ | $\checkmark$ | X            | X            | $\checkmark$ | $\checkmark$ | X            |

| Fork     | ×            | X            | X            | X            | $\checkmark$ | X            | X            | X            |

| Pipeline | ×            | X            | X            | $\checkmark$ | $\checkmark$ | $\checkmark$ | CPU          | X            |

| Farm     | ×            | X            | X            | X            | $\checkmark$ | X            | CPU          | X            |

| For      | X            | X            | X            | $\checkmark$ | $\checkmark$ | $\checkmark$ | X            | X            |

| While    | X            | X            | X            | $\checkmark$ | $\checkmark$ | $\checkmark$ | X            | X            |

| D&C      | X            | X            | X            | X            | $\checkmark$ | X            | CPU          | X            |

| B&B      | ×            | X            | X            | X            | ×            | X            | CPU          | X            |

| Sort     | ×            | $\checkmark$ | $\checkmark$ | X            | ×            | $\checkmark$ | X            | ×            |

Table 2.1: Skeleton support by analyzed frameworks

with skeleton programming. TBB offers both implicit and explicit parallelism. Explicit parallelism is based on the notion of a task, a sequential blocks of code that can be executed in parallel with other tasks. A task may spawn additional tasks, allowing the creation of complex task hierarchies with specified task dependencies. For more common types of parallelism, TBB provides a set of templates (For, Reduce, Skan, While and Sort) that offer the same pattern-based abstraction as skeletons. These templates are implicitly converted into tasks.

All tasks are executed through a dynamic scheduler based on local task queues and task stealing, a scheduling strategy popularized by Cilk[41]. Each working thread has its own task queue, avoiding race conditions to a global task queue, maximizing concurrency. The problem with local task queues is that the work distribution between threads may be unbalanced, reaching a point in the execution when some threads become idle, waiting for other working threads to finish computations, not fully exploiting the parallelism. To work around this weakness, TBB implements a task stealing mechanism. When a working thread has no more tasks in its task queue, it selects a random working thread and tries to steal a task from it. Although this mechanism will keep more threads busy, ultimately improving performance, the random nature of the victim thread selections may not select the best victim to steal from, and since each steal will introduce an overhead on the execution, it would be desirable to steal a task from the busiest thread, reducing the overall number of steals.

# 2.4 Summary

Table 2.1 summarizes the skeletons implemented by the skeleton frameworks analyzed in this chapter.

Some of the GPU skeleton frameworks, like skeletons, are based on OpenCL, which means that they are able to execute on CPUs as well. However, given its GPU focus, there

is no reason to do it from a performance point-of-view, as all the framework was design with only OpenCL GPU executions.

Concluding, the current state of the art around the abstraction of a system composed by CPUs and GPUs as a whole is still very preliminarily. In the context of CPU and GPU skeleton frameworks, we did not find any proposal with the characteristics of the solution we are proposing.

24

# 3

# The Marrow Algorithmic Skeleton Framework

The work presented in this document aims to extend Marrow [6, 7], to offer support for CPU OpenCL computations along with the current support for multiple heterogeneous GPUs. As introduced in Section 2.2.2, Marrow is a C++ algorithmic skeleton framework that stands out for its focus on kernel orchestration and communication, rather than just focusing on the partitioning and distribution of data, like most of the current skeleton frameworks for GPU programming. This chapter presents the latest version of the framework that includes support for multiple heterogeneous GPUs.

Marrow's architecture is divided into four layers: *User Applications, Skeleton Library, Runtime* and *OpenCL Enabled Devices,* as shown in Figure 3.1. The flow of the communication goes downwards, meaning that each layer only has vision of itself and the layer immediately bellow. The upmost layer is the User Application layer and it represents the C++ applications that make use of Marrow's skeletal API. The downmost layer symbolizes the OpenCL enabled devices where the kernel computations are to be run, in this case, GPU devices. A more comprehensive description of the remaining two follows.

# 3.1 Skeleton Library

The skeleton Library encloses all the components of the Marrow framework that are accessible to the programmer. It includes the implementation of each skeleton offered by the platform, the *Kernel Data-types* and the Vector and KernelWrapper classes. The Kernel Data-Types enable the specification of a kernel regarding its type, size, whether or not it is partitionable (for data partitioning purposes) and the minimum size for a

Figure 3.1: Marrow's System Architecture (taken from [7])

partition (*indivisible size*). The currently supported data-types are:

BufferData represents a contiguous memory region;

**FinalData** a constant single-element data defined on its creation and valid for all the executions;

SingletonData a single-element data but the value is defined for each execution;

LocalData represents a memory region allocated in the GPU memory.

The KernelWrapper object is an enclosure for an OpenCL kernel to be executed. The Vector represents a contiguous memory region and wraps any data buffer to be submitted to a skeleton, concealing any intrinsic memory management, namely data-partitioning, memory allocation and data-transmission between the host and the OpenCL devices.

# 3.1.1 Skeleton Nesting

When Marrow was introduced in Section 2.2.2, we highlighted the feature that allows the creation of structured computational trees (exemplified in Figure 3.2) by nesting skeletons inside each other, defining a complex behavior comprising the behavior of all the nested skeletons. The nodes of this trees can be divided into three categories: *root nodes, inner nodes* and *leaf nodes*.

In Marrow, a computational tree is composed by: exactly one root node, at least one leaf node and any amount of inner nodes. Any of the skeletons supported by the framework can become the root node of the computational tree but only the Pipeline, Loop and For skeletons are eligible to be inner nodes (the explanation follows in the

Figure 3.2: Example of a computational tree (adapted from [42])