### José Alberto Martins de Carvalho

## Transimpedance Amplifier for Integrated SpO2 Optic Sensor

Dissertação para obtenção do Grau de Mestre em Engenharia Electrotécnica e de Computadores

| Orientador :    | Luís Augusto Bica Gomes de Oliveira,        |  |  |  |

|-----------------|---------------------------------------------|--|--|--|

|                 | Prof. Auxiliar, Universidade Nova de Lisboa |  |  |  |

| Co-orientador : | João Carlos da Palma Goes, Prof. Associado, |  |  |  |

|                 | Universidade Nova de Lisboa                 |  |  |  |

Júri: Presidente: Prof. Doutor Nuno Filipe Silva Veríssimo Paulino Arguente: Prof. Doutor João Pedro Abreu de Oliveira Vogal: Prof. Doutora Maria Manuela de Almeida Carvalho Vieira

FACULDADE DE CIÊNCIAS E TECNOLOGIA UNIVERSIDADE NOVA DE LISBOA

Setembro, 2012

### Transimpedance Amplifier for Integrated SpO2 Optic Sensor

Copyright © José Alberto Martins de Carvalho, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa

A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objectivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

#### UNIVERSIDADE NOVA DE LISBOA

# Resumo

Faculdade de Ciências e Tecnologia Departamento de Engenharia Electrotécnica e de Computadores

Mestre em Engenharia Electrotécnica e de Computadores

por José Alberto Martins de Carvalho

O nível de oxigenação do sangue, ou SpO2 (saturação de hemoglobina arterial como é medida pelo oxímetro de pulso) é um sinal vital essencial para o diagnostico médico e a sua medição por métodos não invasivos é uma das grandes inovações da medicina moderna. Esta medição pode ser efectuada pelo processamento da luz vermelha e infravermelha reflectida no dedo do paciente e recebida num fotorreceptor. Antes deste sinal ser aplicado a um conversor analógico-digital (ADC), a corrente gerada no fotorreceptor tem de ser convertida para um sinal em tensão, e a sua amplitude ajustada por forma a usar totalmente a gama dinâmica do ADC. Uma vez que o fotorreceptor gera um sinal em corrente de amplitude variável, é necessário um amplificador de transimpedância (TIA) de ganho controlável. O TIA de dois andares proposto nesta tese utiliza um andar de porta comum com regulação (RCG) no primeiro andar, ao mesmo tempo que utiliza técnicas de cancelamento de ruído e de conversão de sinal single-end para diferencial, com recurso a um andar fonte comum adicional. Um segundo andar de ganho regulável é implementado, baseado no amplificador MOS paramétrico (MPA), idealmente sem ruído. O MPA é um amplificador em tempo discreto, eliminando portanto a necessidade de um circuito de amostragem (S & H), na entrada do ADC. O circuito proposto foi dimensionado em tecnologia CMOS standard de 130 nm com 1.2 V de tensão de alimentação e o consumo total do circuito é inferior a 350  $\mu$ W.

Palavras Chave: SpO2; Amplificador de Transimpedância; Cancelamento de Ruído; Amplificador Parametrico; Baixa Potência

#### UNIVERSIDADE NOVA DE LISBOA

# Abstract

Faculdade de Ciências e Tecnologia Departamento de Engenharia Electrotécnica e de Computadores

Mestre em Engenharia Electrotécnica e de Computadores

por José Alberto Martins de Carvalho

The oxygen level in blood, usually referred as SpO2 (Saturation of hemoglobin with oxygen as measured by pulse oximetry) is an essential medical information. Measuring the oxygen level of the human blood using non- intrusive techniques is a vital achievement in modern medicine. This can be performed by processing the infrared and red light transmitted through the patient's finger and received by a photoreceptor. Before being applied to an analog-to-digital converter (ADC), the incoming light has to be converted to a voltage and the range should be dynamically adjusted in order to use the full input range of the ADC. Since the photoreceptor generates an output current, a transimpedance amplifier (TIA) with gain control is required. The two-stage TIA proposed in this paper, uses a regulated common-gate (RCG), in the first stage, employing noise cancellation and balun operation using an additional common-source (CS) stage, while the adjustable gain is implemented in the second-stage, which is based on an intrinsically noiseless MOS parametric amplifier (MPA). This MPA operates in the discrete-time domain, thus, eliminating the need of an input sample-and-hold (S&H) block in the ADC. The proposed circuit has been designed in a 130 nm digital 1.2 V CMOS technology with a power consumption lower than 350  $\mu W.$

# Contents

| Re       | esum  | 0                                                    | 3  |

|----------|-------|------------------------------------------------------|----|

| Al       | ostra | $\mathbf{ct}$                                        | 5  |

| Li       | st of | Figures                                              | 9  |

| A۱       | brev  | viations                                             | 11 |

| 1        | Intr  | oduction                                             | 13 |

|          | 1.1   | Background and Motivation                            | 13 |

|          | 1.2   | Thesis Organization                                  | 14 |

|          | 1.3   | Contributions                                        | 15 |

| <b>2</b> | Stat  | e of the art                                         | 17 |

|          | 2.1   | Principles of Pulse Oximetry                         | 17 |

|          | 2.2   | Pulse Oxymeters                                      | 19 |

|          | 2.3   | Proposed Pulse Oximeter Architecture                 | 20 |

|          |       | 2.3.1 Integrated Photodiode                          | 21 |

|          |       | 2.3.2 Transimpedance Amplifiers                      | 22 |

|          |       | 2.3.3 Discrete Time Parametric Amplifier             | 22 |

|          | 2.4   | Noise                                                | 23 |

|          |       | 2.4.1 Thermal Noise                                  | 23 |

|          |       | 2.4.2 Flicker Noise                                  | 24 |

|          | 2.5   | Transimpedance Amplifier Topologies                  | 25 |

|          |       | 2.5.1 Feedback Transimpedance Amplifier              | 25 |

|          |       | 2.5.2 Common-gate Trasimpedance amplifier            | 28 |

|          |       | 2.5.3 Regulated Common Gate Transimpedance Amplifier | 30 |

| 3        | Reg   | ulated Common Gate Stage                             | 33 |

|          | 3.1   | Working Principle                                    | 34 |

|          | 3.2   | Frequency Response of the RCG                        | 35 |

|          |       | 3.2.1 Input Impedance                                | 36 |

|          |       | 3.2.2 Transfer Function                              | 37 |

|          | <u></u> | 3.2.3                       | Considerations abo   | v             |            |           |    |         |      |

|----------|---------|-----------------------------|----------------------|---------------|------------|-----------|----|---------|------|

|          | 3.3     | 3.3.1                       | Thermal Noise        |               |            |           |    |         |      |

|          |         |                             |                      | t source      |            |           |    |         |      |

|          |         |                             |                      | transistor an |            |           |    |         |      |

|          |         |                             | 0                    | nsistor       |            |           |    |         |      |

| 4        | Bal     | un ope                      | ration and noise o   | ancellation   | techniqu   | es        |    |         | 43   |

|          | 4.1     | Comm                        | on-Source Stage      |               |            |           |    | <br>    | . 44 |

|          | 4.2     | LNA's                       |                      |               |            |           |    | <br>    | . 45 |

|          |         | 4.2.1                       | Balun Operation .    |               |            |           |    | <br>    | . 45 |

|          |         | 4.2.2                       | Noise Cancellation   |               |            |           |    | <br>    | . 46 |

|          |         | 4.2.3                       | Distortion Cancellin | ng            |            |           |    | <br>    | . 47 |

|          |         | 4.2.4                       | Design Consideration | ons           |            |           |    | <br>    | . 47 |

|          | 4.3     | TIA's                       |                      |               |            |           |    | <br>    | . 47 |

|          |         | 4.3.1                       | Balun Operation .    |               |            |           |    |         |      |

|          |         | 4.3.2                       | Noise Cancelling .   |               |            |           |    | <br>    | . 48 |

|          | 4.4     | Regula                      | ted Common-Gate S    | Stage with No | ise Cancel | lling     |    | <br>    | . 48 |

|          |         | 4.4.1                       | Balun Operation .    |               |            |           |    | <br>    | . 49 |

|          |         | 4.4.2                       | Noise Cancelling .   |               |            |           |    | <br>• • | . 50 |

| <b>5</b> | Dise    | crete T                     | ime Parametric A     | Amplifier wit | h Adjust   | table Gai | in |         | 51   |

|          | 5.1     | Basic 1                     | rinciples of the DT  | MPA           |            |           |    | <br>    | . 51 |

|          | 5.2     | The M                       | OSCAP and the thr    | ee terminal M | IOS varac  | tor       |    | <br>    | . 53 |

|          | 5.3     | The D                       | Г МРА                |               |            |           |    | <br>    | . 55 |

|          | 5.4     | Propos                      | ed DT MPA            |               |            |           |    | <br>••• | . 57 |

| 6        | Circ    | cuit Im                     | plementation         |               |            |           |    |         | 59   |

|          | 6.1     | Balun                       | RCG TIA              |               |            |           |    | <br>    | . 59 |

|          | 6.2     | TIA a                       | d DTPA               |               |            |           |    | <br>••• | . 62 |

| 7        | Con     | Conclusions and Future Work |                      |               |            |           | 63 |         |      |

|          | 7.1     | Conclu                      | sions                |               |            |           |    | <br>••• | . 63 |

|          | 7.2     | Future                      | Work                 |               |            |           |    | <br>••• | . 64 |

|          |         |                             |                      |               |            |           |    |         |      |

| A        | թու     | olished                     | Paper                |               |            |           |    |         | 65   |

| A Published Paper | 65 |

|-------------------|----|

| Bibliography      | 73 |

# List of Figures

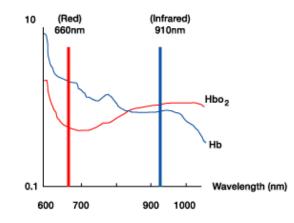

| 2.1 | Absorption spectra of $Hb$ and $HbO_2$                                                                                             | 18 |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----|

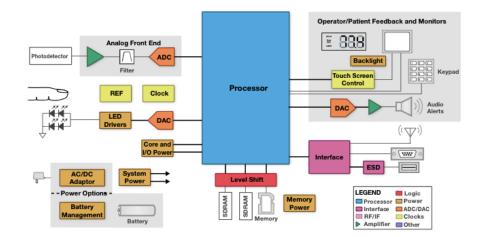

| 2.2 | Pulse oximeter system block diagram from [1]                                                                                       | 19 |

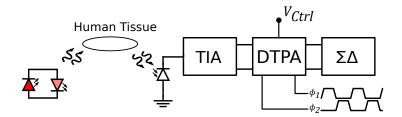

| 2.3 | Pulse oximeter architecture.                                                                                                       | 20 |

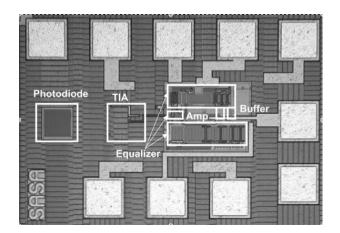

| 2.4 | Chip microphotograph of integrated photodiode and preamplifier in stan-                                                            |    |

|     | dard CMOS [2]                                                                                                                      | 22 |

| 2.5 | Models of thermal noise                                                                                                            | 24 |

| 2.6 | PSD of the total noise in a transistor (flicker noise and thermal noise)                                                           | 25 |

| 2.7 | Shunt feedback transimpedance amplifier.                                                                                           | 26 |

| 2.8 | CG transimpedance amplifier stage                                                                                                  | 28 |

| 2.9 | CG transimpedance amplifier stage small signal model                                                                               | 29 |

| 3.1 | Regulated Common Gate Stage                                                                                                        | 33 |

| 3.2 | Feedback mechanism in source degeneration                                                                                          | 34 |

| 3.3 | (a) Common Gate stage with local feedback and (b) it's small signal equiv-                                                         |    |

|     | alent                                                                                                                              | 35 |

| 3.4 | RCG stage small signal equivalent circuit.                                                                                         | 36 |

| 3.5 | RCG stage with noise sources                                                                                                       | 38 |

| 3.6 | Small signal equivalent with $I_{B2}$ and $M_2$ noise source                                                                       | 39 |

| 3.7 | Small signal equivalent with $M_1$ noise source                                                                                    | 40 |

| 4.1 | Basic CG-CS topology exploiting the input transistor thermal noise can-                                                            | 10 |

| 4.0 | celling                                                                                                                            | 43 |

| 4.2 | Common-source amplifier topology.                                                                                                  | 44 |

| 4.3 | Balun RCG exploiting thermal noise cancelling.                                                                                     | 49 |

| 5.1 | Principle of operation of the discrete time MOS parametric amplifier                                                               | 52 |

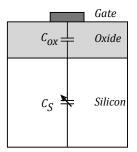

| 5.2 | Simplified cross section of a MOS Capacitor showing a simple equivalent                                                            |    |

|     | circuit                                                                                                                            | 53 |

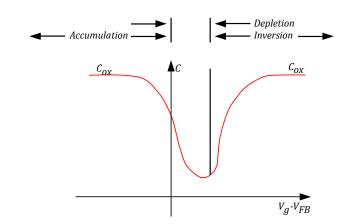

| 5.3 | Typical capacitance/voltage characteristic of a NMOS capacitor                                                                     | 54 |

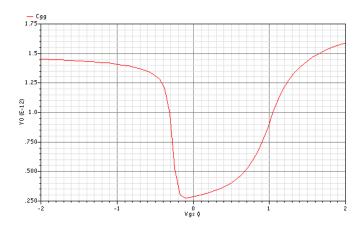

| 5.4 | Simulated Capacitance/voltage characteristic of a PMOS 3 terminal varactor.                                                        |    |

| 5.5 | DT MPA cell based on [3]                                                                                                           | 56 |

| 5.6 | Proposed DT MPA circuit.                                                                                                           | 57 |

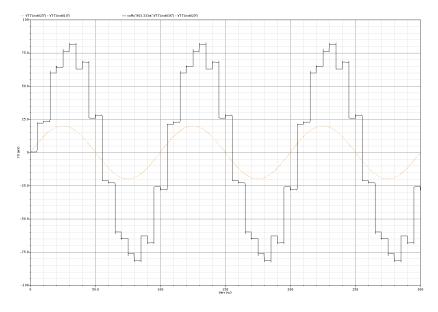

| 5.7 | DT MPA simulation with $V_{gs} = 0.3 \text{ V}$ , $V_{in} = 20 \text{ mV}$ , $f_{in} = 10 \text{ kHz}$ , $F_s = 100 \text{ kHz}$ . | 58 |

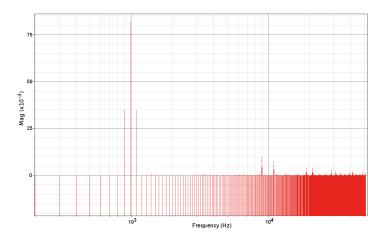

| 5.8 | Hamming window FFT with 1024 points for DT MPA with $V_{qs} = 0.3$ V,                                                              | 00 |

| 0.0 | $f_{in} = 10 \text{ kHz}$ , $F_s = 100 \text{ kHz}$ .                                                                              | 58 |

|     |                                                                                                                                    |    |

| 6.1 | Balun RCG exploiting thermal noise cancelling               | 59 |

|-----|-------------------------------------------------------------|----|

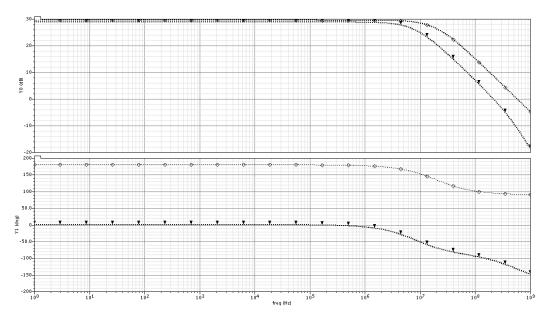

| 6.2 | Frequency response of the RCG (circles) and CS (triangles). | 60 |

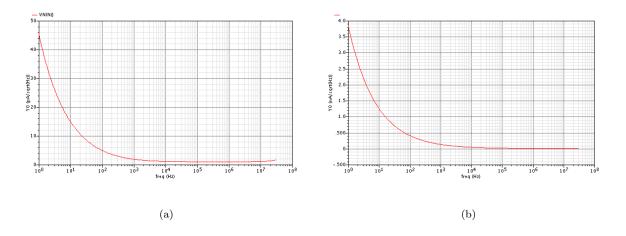

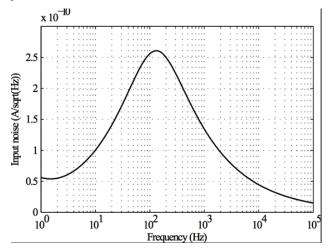

| 6.3 | Simulated input referred noise                              | 61 |

| 6.4 | Simulated transient output                                  | 62 |

# Abbreviations

| AC            | Alternating Current                                                                                                                                         |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC           | Analog to Digital Converter                                                                                                                                 |

| $\mathbf{CG}$ | Common Gate                                                                                                                                                 |

| CMOS          | $\mathbf{C} \mathbf{o} \mathbf{m} \mathbf{p} \mathbf{e} \mathbf{m} \mathbf{n} \mathbf{n} \mathbf{n} \mathbf{n} \mathbf{n} \mathbf{n} \mathbf{n} n$          |

| $\mathbf{CS}$ | Common Source                                                                                                                                               |

| DC            | Direct Current                                                                                                                                              |

| DTPA          | Discrete Time Parametric Amplifier                                                                                                                          |

| IC            | Integrated Circuits                                                                                                                                         |

| IR            | $\mathbf{I}$ nfra $\mathbf{R}$ ed                                                                                                                           |

| KCL           | Kirchhoff's Current Law                                                                                                                                     |

| LED           | $\mathbf{L} ight \ \mathbf{E} mitting \ \mathbf{D} iode$                                                                                                    |

| LNA           | $\mathbf{L}$ ow $\mathbf{N}$ oise $\mathbf{A}$ mplifier                                                                                                     |

| MOSFET        | $\mathbf{M} \mathrm{etal}~\mathbf{O} \mathrm{xide}~\mathbf{S} \mathrm{emiconductor}~\mathbf{Field}~\mathbf{E} \mathrm{ffect}~\mathbf{T} \mathrm{ransistor}$ |

| NEF           | Noise Excess Factor                                                                                                                                         |

| PCB           | Printed Circuit Board                                                                                                                                       |

| PSD           | Power Spectral Density                                                                                                                                      |

| RCG           | Regulated Common Gate                                                                                                                                       |

| RGC           | $\mathbf{ReG}$ ulated $\mathbf{C}$ ascode                                                                                                                   |

| $\mathbf{RF}$ | $\mathbf{R}$ adio $\mathbf{F}$ requency                                                                                                                     |

| S&H           | $\mathbf{S}$ ample and $\mathbf{H}$ old                                                                                                                     |

| SoC           | System on Chip                                                                                                                                              |

| TIA           | $\mathbf{T}$ rans $\mathbf{I}$ mpedance $\mathbf{A}$ mplifier                                                                                               |

| VCCS          | Voltage Controlled Current Source                                                                                                                           |

|               |                                                                                                                                                             |

# Chapter 1

# Introduction

## 1.1 Background and Motivation

Nowadays, with the increased population demand, there is a need for better and more economic health care. It's in this context that the need for economical and reliable devices to continuously and remotely monitor the health of a patient arises, in order for actions to be taken as soon as a change in a patients status is observed, and thus, improving the health care quality and saving costs, on the long run, by dealing with illnesses and critical conditions on it's early stages. In modern medicine the blood oxygen level is considered to be one of the important vital signs (alongside blood pressure, heart rate, breathing rate and body temperature) and its constant monitoring can give early insight on problems in the circulatory and respiratory system.

Pulse oximeters are a non-invasive method to measure the percentage of oxygenated hemoglobin in a patients blood, and as such are ubiquitous in modern medicine, as such pulse oximeters are widely used in intensive care, operating rooms, emergency care, birth and delivery, neonatal and pediatric care, sleep studies, among others.

In traditional pulse oxymeters the transducer is usually clipped or taped to a translucent area of the patient, such as an earlobe or a finger, and wires extend from the transducer to the central processing unit, making this system not very practical for portable and wearable applications and limiting it's usefulness. Besides the traditional applications, there is a growing demand for a new type of devices, which focus on the remote monitoring of the patients, and so the need for novel architectures built around cheap and portable solutions arises. This new devices will make possible applications, such as, home care monitoring for the elderly or chronically ill, wireless medical sensing, remote monitoring of the health status of military personnel in the battlefield as well as fire-fighters engaging in fire control, and rescue missions. It's in this context that reducing size and power consumption is critical. Power consumption is directly related to price and size, because it directly influences battery life. More compact approaches comprising the whole transducer and analog front-end could potentially lead to cheaper and easier to use disposable systems, boosting even further the applications of this systems.

In this work a CMOS differential transimpedance amplifier (TIA) with adjustable gain that also doubles as a sample and hold (S&H) is proposed in order to be implemented in the same die as a photo-detector and ADC (Analog-To-Digital Converter) in order to build a full SoC pulse oximeter analog front end. To accommodate for different photo-sensor's, variations in light sources and transducer positioning a controllable gain is desirable. The goal is to design a TIA that is both low power, and has a high dynamic range with controllable gain.

### 1.2 Thesis Organization

This thesis has been organized in six chapters, including this introductory chapter.

Chapter 2 consists of a brief overview of the pulse oximetry principles. This includes a brief explanation of the phisical aspects of the pulse oximetri measurment as well as a breif explanation of the basic blocks in the architecture. A basic overview of noise in CMOS circuits is then presented, as well as an introduction to two of the most common TIA topologies, and the principles of parametric amplification.

In Chapter 3, a more in depth analysis is given for the RCG TIA. Starting with a very simple and intuitive explanation of the working principle of the RCG circuit we start from the CG and then introduce the gm boosting mechanism characteristic of this topology. After having some insight into the basics of the RCG, teoretical equations for input impedance, transimpedance function and noise are presented as well as some considerations regarding the stability of the RCG. Chapter 4 presents a noise cancelling and balun operation principle. First, the known equations for the LNA CG/CS circuit are shown, and then a parallelism between the LNA and the TIA is demonstrated, and equations to guarantee simultaneous noise cancelling and balun operation are presented. From the analysis of the RCG, the proposed RCG/CS circuit is then presented with the matching conditions to assure noise cancelling and balun operation.

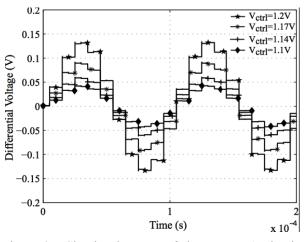

Chapter 5 is dedicated to the DTPA, which is the second stage of the proposed architecture. First a brief analysis of the working principle of the DTPA is made. The MOS varactor that constitutes the heart of the DTPA is then presented, as well as a technique that enables the gain to be varied. The proposed DTPA is then presented with simulation results the corroborate the proposed variable gain aspect of the circuit.

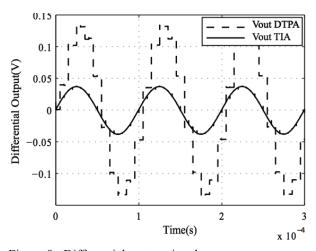

Chapter 6 starts with implementation considerations for the proposed circuit. Simulation results are provided for the TIA and the complete architecture. It's shown that the TIA has a good performance compared to other circuits with similar purposes in the literature. The DPTA is shown to work as expected in simultaneous with the TIA.

Chapter 7 comprises the overall conclusions on the work developed, as well as suggestions for further research work.

### **1.3** Contributions

The main contributions of this thesis are:

A novel integrated architecture for a front end amplifier for application in  $SpO_2$  sensors is presented. The presented architecture aims at being booth low power, and low noise. The architecture comprises two main blocks, namely a transimpedance amplifier and a discrete time parametric amplifier with gain control.

A new topology is proposed for the transimpedance amplifier based on the regulated common gate, and the well known common-gate/common-source topologies. The proposed circuit exploits booth thermal and flicker noise cancelling, while offering balun operation.

A new controllable gain amplifier is proposed based on the discrete time MOS parametric amplifier. A circuit is designed and validated by simulation. This work also originated a paper accepted for oral presentation at the 2012 IEEE International Conference Mixed Design of Integrated Circuits Systems (MIXDES)[4].

# Chapter 2

# State of the art

In the following sections, the physics behind the working principles of a pulse oximeter are presented in order to give a better insight on the challenges of the its design. Then the proposed pulse oximeter architecture is presented, as well as its constituting blocks.

### 2.1 Principles of Pulse Oximetry

The percentage of oxygen in blood as measured by the pulse oximeter  $(SpO_2)$  is given by the ratio between oxygenated hemoglobin and the total hemoglobin, as given by 2.1, where  $HbO_2$  is refers to the oxygenated hemoblogin, and Hb refers to hemoglobin with reduced oxygen.

$$SpO_2 = \frac{HbO_2}{Hb + HbO_2} \tag{2.1}$$

Oxygenated hemoblogin  $(HbO_2)$ , which is bright red absorbs more IR light, and let's more red light pass through it than its de-oxygenated counter part, the dark red hemoglobin (Hb), as can be observed in Fig.2.1. It's this different absorption characteristics for red light (660 nm) and infra-red light (940 nm) that make possible to measure the blood oxygenation by measuring the ratio of absorption of red and IR light.

The light sources, usually light-emitting diodes (LED's) shine red and IR light through a translucent part of patients body such as an earlobe or a finger or toe. The light passes through the patients tissue, and is then measured with a photo-sensor, usually a

FIGURE 2.1: Absorption spectra of Hb and  $HbO_2$ .

photo-diode. Light has to travel through other tissues, such as skin, bones and muscle, but fortunately blood vessels expand and contract with the heart beat so the oximeter signal appears modulated, making it possible to effectively separate the blood transmission characteristics, an AC signal, from the transmission characteristics of the unmodulated tissue in the background, a DC signal.

The physics behind the working principle of the pulse oximeter are based on the Beer-Lambert law. Beer's law relates the transmitted and incident light through a medium that contains an absorving substance of concentration C and lenght l acording to 2.2, where  $I_{TRANS}$  and  $I_{INC}$  are the intensity of the transmitted and incident light respectively.

$$I_{TRANS}(t) = I_{INC} e^{-\varepsilon(\lambda)CL}$$

(2.2)

We can define the transmittance T as  $I_{TRANS}/I_{INC}$  and the absorbance A as -ln(T), and we obtain the total light absorbance of blood that is given by

$$A_{bld}(t) = [\varepsilon_{HbO2}(\lambda_R)C_{HbO2} + \varepsilon_{Hb}(\lambda_R)C_{Hb}]L$$

(2.3)

We have stated before that the blood vessels expand and contract, so it can be established that their thickness varies, and so does the observance of the blood in them with L in 2.3. If we define R to be the ratio of relative absorbances at the red and IR wavelenghts we get,

$$R = \frac{\ln(i_{H,R}/i_{L,R})}{\ln(i_{H,R}/i_{L,R})} \approx \frac{i_{ac}^{R}/i_{DC}^{R}}{i_{ac}^{IR}/I_{DC}^{IR}}$$

$$= \frac{\varepsilon_{HbO2}(\lambda_{R})C_{HbO2} + \varepsilon_{Hb}(\lambda_{R})C_{Hb}}{\varepsilon_{HbO2}(\lambda_{IR})C_{HbO2} + \varepsilon_{Hb}(\lambda_{IR})C_{Hb}}$$

(2.4)

It's known that the right-hand side of equation 2.4 is a good approximation of the left-hand side, considering that the ac signals are very small when compared to the dc component. Whe can then combinine equations 2.1 and 2.4 to obtain

$$SpO_2 = \frac{\varepsilon_{Hb}(\lambda_R) - \varepsilon_{Hb}(\lambda_{IR})R}{\varepsilon_{Hb}(\lambda_R) - \varepsilon_{HbO2}(\lambda_R) + [\varepsilon_{HbO2}\lambda_{(IR}) - \varepsilon_{Hb}(\lambda_{IR})]R} \times 100\%$$

(2.5)

The absorbances for Hb and  $HbO_2$  are know for the red and IR wavelenghts, so it's now clear that the value that the pulse oxymeter measures is the ratio R, wich relates to  $SpO_2$  by means of equation 2.5.

### 2.2 Pulse Oxymeters

Pulse oxymeters usually are comprised of two parts, a sensing probe, and a control unit. Usually the sensing probe consists of the transducer and the light sources, while the control unit takes care of the signal conditioning, data acquisition, signal processing and data display. A typical system level architecture is depicted in Fig. 2.2[1].

FIGURE 2.2: Pulse oximeter system block diagram from [1].

The LED's are pulsed in order to save power, while the signal of interest (the light absorbed by the patients tissue), is measured at the photodector. It's then conditioned in the analog front end, where the current signal coming from the photodetector is converted into a voltage signal, which is then filtered and converted into the digital domain in the analog to digital converter (ADC). After converted into the digital domain, discrete time digital processing clears the signal, and computes the  $SpO_2$  by computing the ratios of absorbance according to the principles explained in the previous section. Note that most of the power consumption can be traced back to the the user interface and signal processing.

One big inconvenience of this type of traditional systems is that the sensing probe has to be connected via a wire to the main unit. Albeit being perfectly useful in a situation where a patient is in a hospital bed, for applications such as home care monitoring for the elderly or chronically ill, wireless medical sensing, remote monitoring of the health status of military personnel in the battlefield as well as fire-fighters engaging in fire control, and rescue missions among others, proves to be a severe constraint.

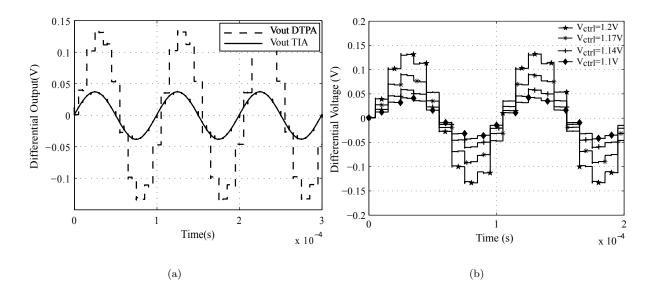

### 2.3 Proposed Pulse Oximeter Architecture

In contrast to the traditional pulse oxymeter architectures, the proposed work is based on an architecture where the photodetector and analog front end are separated from the data display and signal processing. This way, we can have a low power probe, that uses a small battery attached to the patient, while a device such as a smart phone is connected wirelessly to the probe and handles the power consuming signal processing and data display. The architecture for the proposed pulse oxymeter front-end is depicted on Fig. 2.3. By decoupling the analog front end from the rest of the circuit, a low power solution can be obtained, while it's expected that by integrating the photodetector with the analog front end might lead to reduced cost's, and greater usability. This comes from the fact that no wires are needed for the sensor itself.

FIGURE 2.3: Pulse oximeter architecture.

The light sources to be used are two LED's, one IR and one red, in anti-parallel so that they can be easily switched on one at a time. The transducer is a photodiode that converts the incident red an IR lights into a current. This current is then amplified and converted into a voltage in the TIA, and then further amplified while being sampled and held in the discrete time parametric amplifier (DTPA). The output of the DPTA is then fed to the ADC, and once the signal is in the digital domain it can finally be sent wirelessly to a remote device for signal processing. This device can be a bluetooth capable smart phone, that can easily log the patients status for a long time. By using this architecture, several other sensors can be used to create wearable integrated remote monitoring device for medical applications by using time division multiplexing in order for the ADC and wireless module to be shared with the rest of the sensors.

#### 2.3.1 Integrated Photodiode

In order to convert light signal into an electrical signal some sort of transducer must be used. The photodiode is a type of photodetector that converts a light signal into a current signal. Like a normal diode a photodiode consists of a p-n junction. When a photon of sufficient energy is absorbed in the photodiodes p and n regions an electronhole pair is generated. Although in the bulk region these electron hole pairs have a high chance of recombining, in the depletion region and a diffusion width on either side of it, the existing electric field quickly sweeps the electrons to the n side and the holes to the p side. This creates a photocurrent, which is proportional to the incident light. Any p-n junction is a potential photodiode, this is the reason why devices containing p-n junctions are encapsulated in opaque packages in order to prevent any photocurrent induced malfunctions. With careful design, one can implement a photodiode in the same die as the rest of the circuit, resulting in a more compact and cheaper monolithic approach. In the past several work has been done in the area of integrated photodiodes in standard CMOS technologies, namely for CMOS image sensors [5], optic communications [2], and others. One example of an integrated photodiode can be seen in Fig. 2.4 [2], where a photiode for optical comunications is integrated in the same die as the TIA.

Typically a photodiode can be modelled as a current source in parallel with a capacitance [6]. This capacitance is usually high, and is biasing dependent. Typical values for capacitances are in the order of pF for a device of  $50 \ \mu m \times 50 \ \mu m$  [7]. Although this capacitance is dependent on the technology used, PD size and biasing [7], for this work a input capacitance of 1 pF is assumed for design and simulation, knowing that although this it is not an accurate value, is of the expected order of magnitude of the real capacitance according to the literature [7][8]. The current output of the photodiode is also highly dependent on its surface area [7]. For this work it's assumed that the photodiode outputs a current between  $0.1 - 10 \ \mu A$ . The sizing of the photodiode is outside the scope of this work, and it should be done according to this output current specification.

FIGURE 2.4: Chip microphotograph of integrated photodiode and preamplifier in standard CMOS [2].

### 2.3.2 Transimpedance Amplifiers

Traditionally amplifiers sense voltages at their input and amplify them in their output. Other types of amplifiers also exist, namely amplifiers that sense currents and output voltages. This "current-voltage" amplifiers are effectively a current controlled voltage source (CCVS) and are commonly know as transimpedance (TIA) amplifiers. Ideally the input impedance should be zero much like an ideal current meter. Likewise the output impedance should also be zero as in a ideal voltage source. The transimpedance gain is then defined as  $R_o = v_{out}/i_{in}$ .

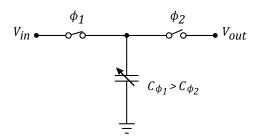

#### 2.3.3 Discrete Time Parametric Amplifier

Parametric amplifiers work by the change of a parameter within the amplifier. In this particular case, amplification is made through the variation of a sampling capacitor. This can be simply described by taking the equation for the charge in a capacitor, given by  $Q = C \cdot V$ . If we can vary the capacitance from an initial value  $C_1$ , to a lower value  $C_2$  while conserving the charge in the capacitor we can obtain a gain expressed as:

$$A_v = \frac{V_o}{V_{in}} = \frac{C_1}{C_2} \tag{2.6}$$

In [3] an aproach is proposed, where the capacitor can be replaced by MOS transistor connected to work as a varactor. Note that besides the noise involved in the sampling process the amplification itself is ideally noiseless [9]. Theoretically, if the value of the initial or final capacitance could be varied, one could obtain a variable gain. In the proposed circuit presented in the next chapters this possibility is pursued further.

### 2.4 Noise

In electronic circuits, we consider noise to be a random unwanted signals. This signals are generated in electronic devices due to different physical phenomena. Noise in electronic circuits comes from the fact that charge is carried in discrete amounts equal to an electrons charge [10][11]. These small fluctuations of charge create small fluctuations in the current and voltage at the macroscopic level that are perceived as noise. Although the presence of noise in electronic circuits can be desired and useful, such as in some oscillators, usually noise limits the circuits performance. When dealing with low power signals, it's crucial that the noise is not of the same order of magnitude as the signal itself, otherwise that would make the two signals indistinct. Noise also limits the upper limit of an amplifiers gain to  $V_{dd}/v_n$  where  $V_{dd}$  is the supply voltage and  $v_n$  is the noise floor at the input of the amplifier [11]. A gain larger then  $V_{dd}/v_n$  would simply saturate the transistor, leaving no output dynamic range for the input signal. Although noise is by definition a random signal in the time domain, its average power and frequency spectrum can be quantified. In this section two of the most common noise sources in CMOS transistors are described.

#### 2.4.1 Thermal Noise

In every conductor at a temperature different then 0 K there is a random motion of electrons. This random motion creates what is usually referred to as thermal noise. In a resistor the noise generated by thermal noise can be expressed as [12][10]

$$\overline{v_n^2}_{Res} = 4kTR\Delta f \tag{2.7}$$

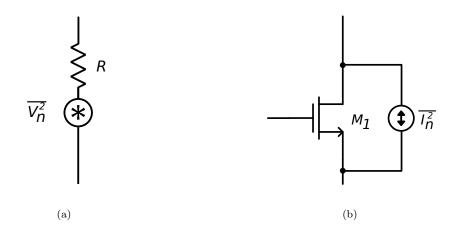

where T is the absolute temperature in Kelvin, k is the Boltzmann constant and  $\Delta f$  is the bandwidth of the system. Note that noise power is usually referred to a normalize 1 Hz bandwidth, so the  $\Delta f$  term is sometimes omitted. The thermal noise power is frequency invariant, so the thermal noise has a flat power spectral density (PSD). It's because of this flat PSD that thermal noise is also referred to as white noise. As shown in Fig.2.5(a) (a) thermal noise in a resistor can be modelled by a voltage source in series with the resistor.

FIGURE 2.5: Models of the thermal noise in a resistor (a) and a MOS transistor (b).

The same phenomena that occurs in resistors, also occurs in a MOS transistor conducting channel. Usually thermal noise in a MOS transistor is modelled with a current source between drain and source as can be seen inf Fig.2.5(b) (b). It can be proved that for long channel MOS devices in the saturation region the thermal noise in the transistor channel can be expressed as [12],

$$\overline{v_n^2}_{MOS} = 4kTgm\gamma\Delta f \tag{2.8}$$

where T and k are the absolute temperature and Boltzmann constant respectively,  $\Delta f$  is the bandwidth of the system, gm is the transistors transconductance and  $\gamma$  is the noise excess factor (NEF). For long channel devices the NEF can be derived to be equal to 2/3 but it's higher for submicron transistors [12].

#### 2.4.2 Flicker Noise

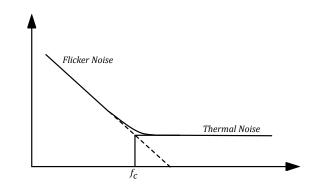

Another type of noise is also present in MOS transistors. Flicker noise is thought to be caused by the impurities in the interface between the gate oxide and the silicon substrate. Unlike the thermal noise flicker noise power can't be predicted easily [12], and it's quantification is still largely based on empirical considerations [11]. Flicker noise has a PSD of  $1/f^n$  with  $n \approx 1$ . In Fig.2.6 the total noise power (flicker and thermal noise) of a MOS transistor is presented. One can see that until the corner frequency  $f_c$  the flicker noise is dominant, but for higher frequencies it can be neglected.

FIGURE 2.6: PSD of the total noise in a transistor (flicker noise and thermal noise)

Flicker noise is modelled by a voltage source in series with the transistor gate with a power roughly given by [12]

$$\overline{v_{nf}^2}_{MOS} = \frac{K}{C_{ox}WL} \frac{1}{f^n}$$

(2.9)

where K is a process dependent constant,  $C_{ox}$  is the gate oxide capacitance per unity area, and W and L are the transistors width and length respectively. Cleaner fabrication processes result in lower values for K, and thus in lower flicker noise values. Also PMOS transistors have lower K values then NMOS transistors, and thus have less flicker noise.

### 2.5 Transimpedance Amplifier Topologies

In this section, a brief analysis of three common TIA's is presented. Simple equations for the transimpedance gain, input impedance are derived, as well as equations relating to the noise performance of the TIA's.

#### 2.5.1 Feedback Transimpedance Amplifier

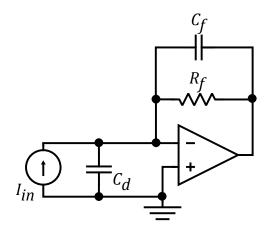

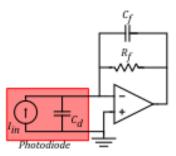

The feedback TIA is commonly used in optoelectronic integrated circuits [13]. It consists of an operational amplifier (OA) with feedback shunt-shunt feedback topology as illustrated in Fig. 2.7.

If we assume the op-amp in Fig. 2.7 to be ideal, we know that it's negative input voltages tends to zero. This translates into a very low input impedance (ideally zero). Considering

FIGURE 2.7: Shunt feedback transimpedance amplifier.

that the gain of the opamp is very high and frequency independent we can write

$$\frac{V_o}{Z_f} = I_{in} \tag{2.10}$$

where  $Z_f$  is the feedback impedance given by  $R_f / \frac{1}{sC_f}$ . By this means we can achieve a high transmodulate gain, while maintaining a very low input impedance. Considering that the OA has a dominant pole as in [14] it's transfer function is given by equation 2.11. and it's GBW is given by equation 2.12

$$A(s) = \frac{A_0}{1 + s\tau_a} \tag{2.11}$$

$$B = A_0 \omega_a = \frac{A_0}{\tau_a} \tag{2.12}$$

We know that the voltage in the negative input of the op-amp is given by  $V_o(s)/A(s)$  we can write the Kirchhoff current law (KCL) to the input node thus obtaining

$$\frac{V_o(s) - \frac{V_o(s)}{A(s)}}{Z_f} + I_{in}(s) - \frac{\frac{V_o(s)}{A(s)}}{s}C_d = 0$$

(2.13)

Rearranging equation 2.13 and rewriting the op-amp transfer function A(s) with equations 2.11 and 2.12 we can then obtain the transimpedance function of the feedback TIA.

$$\frac{V_o(s)}{I_{in}(s)} = -\frac{R_f}{s^2 R_f C_d B^{-1} + s R_f (C_f + \frac{C_d}{A_0}) + 1}$$

(2.14)

Since we know that the voltage at the input node is given by  $\frac{V_o(s)}{A(s)}$  we can derive the input impedance.

$$\frac{V_o(s)}{V_{in}(s)} = A(s) \Leftrightarrow \frac{V_o(s)}{I_{in}(s)Z_{in}(s)} = A(s) \Leftrightarrow Z_{in} = \frac{V_o(s)}{I_{in}(s)}\frac{1}{A(s)}$$

(2.15)

$$Z_{in}(s) = -\frac{R_f}{s^2 R_f C_d B^{-1} + s R_f (C_f + \frac{C_d}{A_0}) + 1} \cdot \frac{1}{A_0} + s B^{-1}$$

(2.16)

While studying the feedback TIA it's also important to have some insight into it's noise performance. For this study we will assume that the noise generated in the opamp can be modelled by a voltage source in series with the input of the amplifier. Note that the opamp can be designed in a way that dominant noise contribution is originated in the input transistor and that it's contribution to the total noise can be shown to be dominant over the feedback resistors noise [14]. Thermal noise in a MOS transistor can be modelled by a current source between source and drain and flicker noise by a voltage source in series with the gate [12]. In order to simplify the analysis we can transform the thermal noise current into a equivalent voltage in series with the gate. Taking the equations for thermal and flicker noise already presented in the previous section, we get the equivalent input noise voltage of the opamp to be,

$$\overline{v_{na}^2} = 4kT\gamma gm^- 1 + \frac{K}{C_{ox}WL} \cdot \frac{1}{f},$$

(2.17)

where k is the Boltzmann constant,  $\gamma$  is a channel length dependant coefficient, K is a process dependent constant, and  $C_{ox}WL$  is the gate capacitance [12].

The noise transfer function for the feedback is derived in [14] and is given by

$$N(s) = \frac{V_{no}}{V_{na}} = -\frac{1 + sR_fC_d}{s^2R_fC_dB^{-1} + sR_f(C_f + \frac{C_d}{A_o}) + 1}$$

(2.18)

In order to minimize the thermal noise high values of gm are required according to equation 2.17. This can be obtained at the cost of either die area, using very wide transistors (high W/L) or high currents. Note that high area transistors also lower the flicker noise. Since the application devised in this work is battery operated, a low current design is preferred.

Note that the complexity and area needed for a good performance opamp could lead to an increased cost.

#### 2.5.2 Common-gate Trasimpedance amplifier

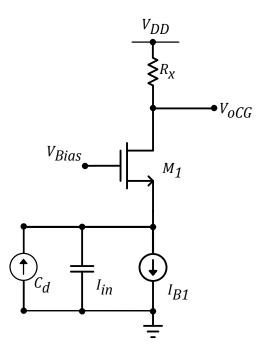

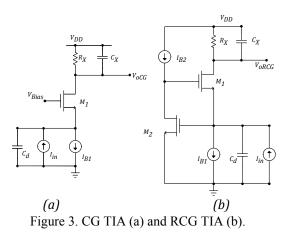

Another basic TIA topology commonly used is the common-gate (CG) stage presented in Fig. 2.8, where  $I_{B1}$  and  $V_{Bias}$  are a bias current and voltage, respectively. This topology is know for it's low input impedance and broadband [6]. Since the input current at the transistors source equals the output current at the transistors drain, ideally the transimpedance gain would be equal to  $R_x$ . Intuitively the common-gate stage acts as a current buffer, while the I-V conversion is performed at the output by the load resistor  $R_x$ . It's then important to know it's input impedance.

FIGURE 2.8: CG transimpedance amplifier stage.

By observing the small signal equivalent in Fig. 2.9 and disregarding the parasitic capacitances, noting that the bulk and gate are tied to ground we can write

$$V_{in} = -v_{gs} = v_{sb} = v_s \tag{2.19}$$

$$I_{in} = \frac{V_{in} - I_{out}R_x}{r_o} - (gm + gm_b)v_{gs}$$

(2.20)

FIGURE 2.9: CG transimpedance amplifier stage small signal model.

By combining equations 2.19 and 2.20 and having  $Z_{in} = V_{in}/I_{in}$  we obtain the input impedance for low frequencies to be given by

$$Z_{in} = \frac{r_o + R_x}{1 + (gm + gm_b)r_o} = \frac{1}{\frac{1}{r_o} + gm + gm_b} \left(1 + \frac{R_x}{r_o}\right)$$

(2.21)

From equation 2.21 some considerations can be made. First, note that input impedance depends on the load  $R_x$ , divided by  $r_o$ . Since  $r_o$  is usually very high, for low gain amplifiers where  $R_x$  is relatively small we can approximate  $Z_{in} = 1/(gm + gm_B)$  as in [14]. For high gain amplifiers and sub-micron technologies, where  $r_o$  and  $R_X$  can be of the same order of magnitude this relation between gain and input impedance must be taken into account. The body effect effectively lowers the input impedance. Also note that the output impedance of the biasing current source wasn't considered because it's high compared with the CG input impedance, with which it's in parallel. Since the gate and bulk are booth tied to ground, one can easily generalize equation 2.21 for high frequencies. By replacing  $R_x$  with  $R_x//\frac{1}{sC_D}$  where  $C_D$  is the total capacitance in the drain node ( $C_D = C_{db} + C_{gd} + C_X$ ) and then making the parallel of this modified input impedance with  $\frac{1}{sC_S}$  where  $C_S$  equal to the total capacitance in the source node ( $C_S = C_s + C_{gs} + C_{sb}$ ) we obtaining equation 2.22.

$$Z_{in}(s) = \frac{sR_xr_oC_D + R_x + r_o}{s^2R_xr_oC_DC_S + sR_x(C_D + C_S + (gm + gm_b)r_oC_D) + sr_oC_S + (gm + gm_b)r_o + 1}$$

(2.22)

By combining the voltage gain and the input impedance, the transimpedance function can be obtained. Equation 2.23 is the common-gate voltage gain  $V_{out}(s)/V_{in}(s)$  derived from [12].

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{R_x(r_o(gm + gm_b) + 1)}{sR_x r_o C_D + R_x + r_o}$$

(2.23)

Since the numerator of 2.22 and denominator of 2.23 cancel out, it's straightforward to obtain the transimpedance function A(s) in equation 2.24. Note that as stated before, for low frequencies the transmedance gain equals  $R_x$ ,

$$A(s) = \frac{R_x(r_o(gm + gm_b) + 1)}{s^2 R_x r_o C_D C_S + s R_x (C_D + C_S + (gm + gm_b) r_o C_D) + s r_o C_S + (gm + gm_b) r_o + 1}.$$

(2.24)

In the common-gate TIA there are three noise current sources relating to the thermal noise of the common-gate transistor, the noise in the drain resistor  $R_x$  and the noise of the bias current  $I_B$ . It can be shown that the noise contribution of the common-gate transistor is dominant and has a noise transfer function given by [14]

$$\frac{V_{no}}{I_n(s)} = -\frac{R_x}{gm * R_{ob}} \frac{1 + sR_{oB}}{(1 + sgm^{-1}C_S)(1 + sR_xC_D)}$$

(2.25)

Although from equation 2.25 the noise might appear to decrease with gm because it's in the denominator, if we consider the total integrated output noise the effect of the reduction of the bandwith with a decrease in gm is actually dominant as proved in [14]. So in order to decrease the total output noise a lower gm is required, which conflicts with the need to have a high gm in order to obtain a low input impedance.

#### 2.5.3 Regulated Common Gate Transimpedance Amplifier

The regulated common gate (RCG) stage presented in subsequent Chapter is a widely known TIA, with applications in many optical receivers [8]. Note that the RCG is also referred to as Regulated Cascode (RGC) in the literature. Although the RCG and RGC are effectively the same circuit, the same way that single-stage amplifiers have different names depending on where the input/output is taken so should this circuit. The RCG name will be used trough out this work since it better reflects the working principle of this amplifier.

The RCG consists of a common-gate stage with gm boosting [15] which, boost's the transconductance of the input transistor by a factor of (A + 1), where A is the gain of the feedback loop. Compared to the CG stage, the RCG allows for a lower input impedance for the same bias current in the input transistor, which relates to a higher bandwidth, and potentially a better noise performance. Because the input transistor dominant noise source, which depends on its gm, is no longer tied to the input impedance/bandwidth determination as in the common-gate TIA, an extra degree of freedom is given to the designer to optimize the circuit. Since the proposed TIA is based on the RCG topology, it will be studied in detail in the following Chapter.

# Chapter 3

# Regulated Common Gate Stage

The regulated common gate (RCG) stage presented in Fig. 3.1 is a widely known TIA. It derives from the CG, in which, a *gm* boosting technique that consists of a local feedback loop is applied. In this Chapter, an intuitive explanation of how the RCG works is done besides a more in depth analysis of the key parameters of the RCG TIA. Transimpedance gain, input impedance and noise performance is studied. The derived equations are validated by simulation.

FIGURE 3.1: Regulated Common Gate Stage.

## 3.1 Working Principle

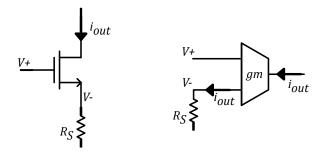

The RCG TIA, derives from the CG TIA. By applying a local feedback loop the RCG is capable of a lower input impedance then the CG stage with the same input transistor bias current and thus the same gm. This effectively increases the bandwidth by moving the input pole into higher frequencies while maintaining a good noise performance.

The effect that the source degeneration has in increasing both input and output impedance by a factor of  $1 + gmR_S$  is well known. This feedback mechanism can be intuitively understood if ones thinks of a transistor as a transconductance amplifier as in Fig.3.2, where the output current is equal to the negative input current.

FIGURE 3.2: Feedback mechanism in source degeneration.

The source resistance effectively generates a series-series feedback loop by converting the output current into a voltage, while it's applied to the negative input of the transconductance amplifier. By using this principle with an active load we obtain the regular cascode circuit. This same concept can be applied to the common gate amplifier using an active feedback loop as depicted in Fig.3.3(a). This feedback loop then has the effect of decreasing the input impedance. In order to obtain negative feedback, a CS stage is used thus obtaining the circuit in Fig. 3.1.

By taking the simplified small signal equivalent in Fig.3.3(b) we can derive the approximate input impedance and transimpedance gain of the RCG. By observing the small signal circuit we can write

$$v_{gs} = -A \cdot v_{in} - v_{in} = -(A+1)v_{in} \tag{3.1}$$

$$i_{in} = i_{in} = (A+1)v_{in}gm_1 \tag{3.2}$$

Since  $R_{in} = v_{in} i_{in}$  we obtain

FIGURE 3.3: (a) Common Gate stage with local feedback and (b) it's small signal equivalent.

$$Z_{in} = \frac{1}{(A+1)gm_1}.$$

(3.3)

Compared to the CG stage, the input impedance is now A times smaller. In regards to the transimpedance gain, it's easy to see that the input current is the same as the output current. Like the CG stage the RCG effectively works as a current conveyor, where the current-voltage conversion is accomplished in the load resistor  $R_x$ .

# 3.2 Frequency Response of the RCG

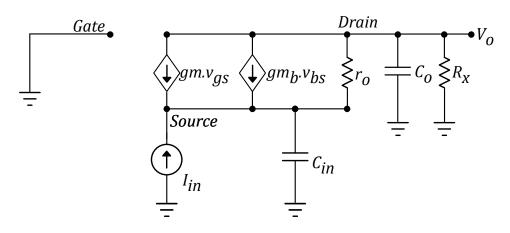

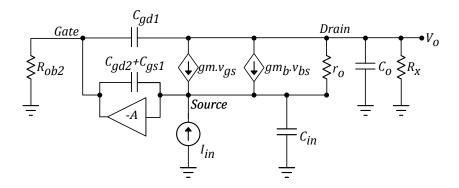

In the small signal equivalent circuit in the previous chapter, the transistors output resistance was discarded, as well as all the capacities present. If we take into account all the capacities involved we obtain the small circuits circuit in Fig. 3.4 where  $C_{in}$  is the sum of the photodiode capacitance and the transistors parasitic capacitance  $C_{sb}$ , and  $C_o$  is equal to a load capacitance plus  $C_{db}$ .

The gain -A in the Fig. 3.4 is obtained via a CS gain stage so for low frequencies it is approximately equal to

$$A_{vCS} = -gm_2 \frac{r_{o2}R_{ob2}}{r_{o2} + R_{ob2}}$$

(3.4)

FIGURE 3.4: RCG stage small signal equivalent circuit.

If we look into the small signal equivalent we can write the total input capacitance by taking the miller effect into acount, and thus obtaining

$$C'_{in} = C_{in} + (1+A)(C_{gs} + C_{gd2} + C_{gs1}) = C_d + C_{sb} + (1+A)(C_{gs} + C_{gd2} + C_{gs1}) \quad (3.5)$$

#### 3.2.1 Input Impedance

The impedance of the total input capacitance,  $C'_{in}$ , is in parallel with the input impedance for small signals. For simplicity we will disregard the input capacitor, and then add its contribution in the end. We can then write the input current to be given by equation

$$I_{in} = -gm_1 V_{gs} - gm_b V_{bs} + \frac{1}{r_o 1} (V_{in} - (R_x / /C_o) I_{in})$$

(3.6)

We can then write  $V_{gs} = -(A+1)V_{in}$ , so comparing to the CG stage, where  $V_{gs} = V_{sb}$ , in the RCG  $V_{gs}$  is (A+1) times bigger then  $V_{sb}$ . Since  $gm_b$  is already smaller then gm, the current caused by the body effect can be neglected. We can now write

$$I_{in}\left(1 + \frac{R_x}{(sR_xC_o + 1)r_o}\right) = V_{in}\left[(A+1)gm_1 + \frac{1}{r_o}\right]$$

(3.7)

and from there obtain the following equation for the input impedance without considering the input capacitance

$$Z_{in}' = \frac{V_{in}}{I_{in}} = \frac{1}{(A+1)gm_1 + \frac{1}{r_o}} + \frac{\frac{R_x}{(sR_xC_o+1)r_o}}{(A+1)gm_1 + \frac{1}{r_o}}$$

(3.8)

Now we just have to make  $Z'_{in}//\frac{1}{sC'_{in}}$  to obtain the input impedance.

## 3.2.2 Transfer Function

As noted before, the input current is divided between the input impedance, and  $C'_{in}$ . Noting that we are dealing with a current divider, the incremental source current in  $M_1$  can then be expressed as

$$I_{s1} = \frac{1/sC'_{in}}{Z'_{in} + 1/sC'_{in}} I_{in} = \frac{1}{1 + sZ'_{in}C'_{in}} I_{in}$$

(3.9)

which can be written in the form  $\frac{1}{1+s\tau_1}I_{in}$  where  $\tau_1 = Z'_{in}C'_{in}$ . This current flows through the output impedance  $Z_x = \frac{R_x}{1+sR_xC_o}$ . Whe can then write the approximate transimpedance function to be given by

$$\frac{V_o}{I_d} \approx \frac{R_x}{(1 + sC_{in}' \frac{1 + \frac{R_x}{(sR_xC_o + 1)r_o}}{(A + 1)gm_1 + \frac{1}{r_o}})(1 + sR_xC_o)}$$

(3.10)

#### 3.2.3 Considerations about stability

The approximate transfer function derived before could lead one to believe that this RCG is always stable, but because it has a feedback loop, the stability of the amplifier should be studied. From the approximations made, the transfer function has two poles, at the input and output, while the loop gain only has one pole. This might lead one to believe that the system is intrinsically stable, because the maximum phase shift in a 1 pole system is 90°, thus meeting the criteria for a stable system that the loop gain must be lower then unity when the phase has shifted by 180°. However the common-source stage used in the loop gain has two poles. This third pole can be traced back to the node at the gate of the input transistor. This pole is approximately given by

$$\tau = (R_{ob2}//r_{o2}) \cdot \left[ (C_{gd2} + C_{gs1})(1 - A^{-1}) + C_{db2} \right]$$

(3.11)

where some capacities are multiplied by the Miller effect.

In [16] it's suggested that this pole has to be in a frequency at least three times higher then the frequency in which the loop gain is lower then one. This should allow for a phase margin of  $72^{\circ}$ , which should guarantee there is not any overshoot in the time domain [16].

## 3.3 Noise

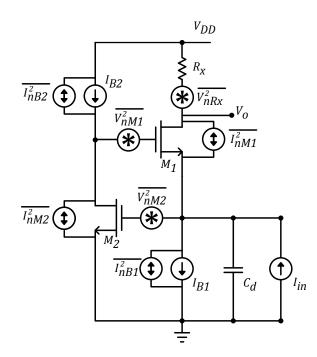

For the noise analysis we will first determine the noise voltage spectral density at the output. For wideband circuits the flicker noise can be neglected [14]. Since in pulse oximetry the signals involved are low frequency by nature, flicker noise should be considered. In Fig. 3.5 all the noise sources of the RCG stage are represented.

FIGURE 3.5: RCG stage with noise sources.

#### 3.3.1 Thermal Noise

The noise sources present in Fig. 3.5 are related to the thermal and flicker noise. We will first consider the thermal noise sources, generated by the current sources  $\overline{I_{nB1}^2}$ ,  $\overline{I_{nB2}^2}$ ,  $\overline{I_{nM2}^2}$  and  $\overline{I_{nM1}^2}$ , and voltage source  $\overline{V_{nRx}^2}$ .

#### **3.3.1.1** $I_{B1}$ current source

The noise contribution of the input transistor biasing current source is given by  $\overline{I_{nB1}^2}$ . It can be seen in Fig. 3.5 that it is in parallel with the input current, so it's noise transfer function,  $V_{no}/I_{nB1}$  is equal to the RCG transfer function given by 3.10. The noise contribution to the total output noise can then be expressed as

$$\overline{V_n^2 Out, B1} = \overline{I_{nB1}^2} \cdot \left| \frac{R_x}{(1 + sC_{in}' \frac{1 + \frac{R_x}{(sR_x C_o + 1)r_o}}{(A+1)gm_1 + \frac{1}{r_o}})(1 + sR_x C_o)} \right|^2$$

(3.12)

#### **3.3.1.2** Regulaton transistor and $I_{B2}$ current source

In the small signal equivalent, where  $V_{dd}$  is short-circuited to ground, the noise currents generated by the regulation transistor,  $M_2$ , and given by  $\overline{I_{nM2}^2}$ , and the noise from the biasing current source  $I_{B2}$ , given by  $\overline{I_{nB2}^2}$  are in parallel, so they share the same noise transfer function.

FIGURE 3.6: Small signal equivalent with  $I_{B2}$  and  $M_2$  noise source.

By taking the simplified small signal circuit in Fig. 3.6 we can derive the noise transfer function. We start by writing the straightforward voltages at the gate, source and drain of the transistor thus obtaining the following equations.

$$V_g = -AV_s + I_n R_{ob2} / / r_{o2} ag{3.13}$$

$$V_s = gm V_{gs} \frac{1}{sCin} \tag{3.14}$$

$$V_o = gm V_{gs} \frac{R_x}{sR_x C_o} \tag{3.15}$$

Combining equations 3.13 and 3.14 we can write  $I_n$  as follows

$$I_n = \frac{V_{gs} s C_{in} + g m V_{gs} (A+1)}{s C_{in} R_x}$$

(3.16)

We can obtain the noise transfer function by dividing equations 3.15 by 3.16 thus obtaining the noise transfer function  $V_{no}/I_n$  below.

$$\frac{V_{no}}{I_n} = \frac{s \frac{R_{ob2}//r_{o2}R_x C_{in}}{(A+1)}}{(s \frac{C_{in}}{gm(A+1)} + 1)(sR_x C_o + 1)}$$

(3.17)

#### 3.3.1.3 Input transistor

We will now analyse the effect of the input transistors thermal noise. Note that in the common-gate stage, this was the dominant noise source.

FIGURE 3.7: Small signal equivalent with  $M_1$  noise source.

Using the small signal circuit in Fig. 3.7 we will now derive the noise transfer function. We can write the voltage at the output node as

$$V_o = \frac{R_x}{sR_xC_o + 1} \left[ gm_1(A+1)V_s + \frac{V_s - V_o}{r_{o1}} + I_n \right]$$

(3.18)

$$V_o\left(1 + \frac{R_x}{(1 + sR_xC_o)r_{o1}}\right) = \frac{R_x}{1 + sR_xC_o} \cdot (I_n + gm_1(A+1)V_s)$$

(3.19)

where  $V_s$  is the voltage at the source node, and in equation 3.19 we have taken into acount that  $gm_1(A+1) >> 1/r_{o1}$ . Since the current at the output node is the same as the current in the input, we can write  $V_s$  in terms of  $V_o$  so we have

$$V_s = V_o \cdot \frac{sR_xC_o + 1}{R_x} \cdot \frac{R_{ob1}}{sR_{ob1}C_{in} + 1}$$

(3.20)

Combining equations 3.19 and 3.20 with then obtain

$$V_o\left(1 + \frac{R_x}{(sR_xC_o + 1)r_{o1}} - gm_1(A+1)\frac{R_{ob1}}{sR_{ob1}C_{in} + 1}\right) = \frac{R_x}{1 + sR_xC_o}I_n$$

(3.21)

We know simplify the multiplying factor of  $V_o$  in the left-hand side of equation 3.21 o obtain the factorized equation in 3.22.

$$\frac{(sR_xC_o+1)(sR_{ob1}C_{in}+1) + R_x/r_{o1}(sR_{ob1}C_{in}+1) + gm1(A+1)R_{ob1}(sR_xC_o+1)}{(sR_xC_o+1)(sR_{ob1}C_{in}+1)}$$

(3.22)

In order to further simplify 3.22, we will assume that  $gm_1(A+1)R_{ob1} >> R_x$  and  $gm(A+1)C_x >> C_{in}/r_{o1}$ . With this simplifications, and equations 3.20 and 3.21 we can then write the noise transfer function below.

$$\frac{V_o}{I_n} = \frac{R_x}{gm_1(A+1)R_{ob1}} \frac{1 + sR_{ob1}C_{in}}{(s\frac{Cin}{gm_1(A+1)} + 1)(sR_xC_o)}$$

(3.23)

# Chapter 4

# Balun operation and noise cancellation techniques

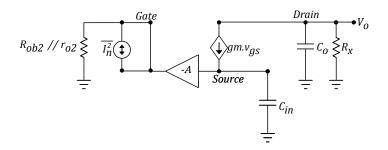

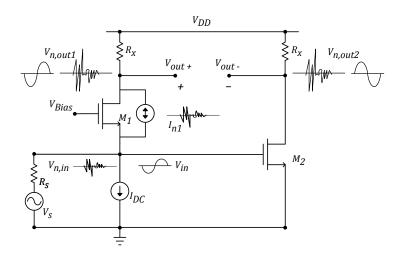

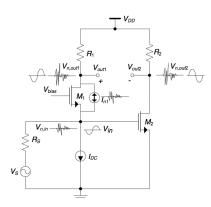

Differential operation has many benefits, such as reducing second-order distorion and rejection of power supply and substrate noise[17]. Many RF wideband LNA circuits have been publishing integrating the LNA and balun in the same circuit, while exploiting the noise cancellation technique proposed in [18]. This consists of a CG stage in parallel with a CS stage, as depicted in Fig. 4.1.

FIGURE 4.1: Basic CG-CS topology exploiting the input transistor thermal noise cancelling.

The basic principle is clearly illustrated in Fig. 4.1. The input current,  $I_{in}$ , generates a voltage,  $V_{in}$  at the input node. This voltage is given by the product of the input current and the input impedance. This voltage is then amplified on the CG stage, thus creating

a in phase output voltage  $V_{out+}$ . Since  $V_{in}$  is also amplified by the CS, at the CS output we have  $V_{out-}$  in phase opposition to  $V_{in}$  and  $V_{out+}$ . The gain can then be expressed as

$$A_{vCS} = A_{vCG} + A_{vCS} \tag{4.1}$$

which is the sum of the gain of the CG stage and the CS stage. Assuming both the CG and CS gains are matched, by taking the output as  $V_{out+} - V_{out-}$  we achieve our differential output, and consequently increase the gain by 6 dB. In a analogous way, the thermal noise, represented by the current source between the source and drain of the input transistor,  $M_1$ , generates a noise voltage  $V_{nCG}$  at the output node, and an anti-phase noise voltage,  $V_{nIN}$ . When  $V_{nIN}$  is amplified by the CS stage, we obtain a noise voltage,  $V_{nCS}$ , which is in phase with  $V_{nCG}$ . The noise cancels because it becomes a common-mode signal at the differential output. Comparatively to other noise cancelling techniques employing feedback, this is a strictly feed-forward technique, so instability risks are greatly relaxed [18].

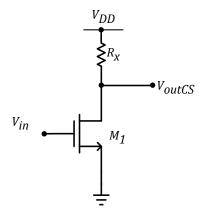

## 4.1 Common-Source Stage

Some considerations must be made in regards to the common-source stage being added to the circuit. The basic common-source topology is presented in Fig. 4.2.

FIGURE 4.2: Common-source amplifier topology.

One of the first aspects that we should study in the CS stage is its gain. If we take the small signal model for low frequencies we can write the gain as:

$$A_{vCS} = -gm \frac{r_o R_x}{r_o + R_x} \approx -gm R_x \tag{4.2}$$

Since the photodiodes input capacitance is high and we are interested in low frequencies, the CS transistor parasitic capacitances aren't expected to degrade the bandwidth and input impedance significantly. Unfortunately, in order to obtain differential operation and noise cancelling, we are adding new noise sources which should be considered.

The flicker and thermal noise of the transistor, can be expressed as 4.3 and 4.4

$$\overline{v_{nf}^2}_{CS} = \frac{K}{C_{ox}WL} \frac{1}{f^n} \cdot (gmR_x)^2 \tag{4.3}$$

$$\overline{v_{nt}^2}_{CS} = 4kT\gamma R_x^2 \tag{4.4}$$

Note that booth of these noise sources will be added to the total output noise in order to obtain the differential gain. Since the gain is doubled, a better noise factor can be achieved in some situations. Careful design should guarantee that the benefits of adding the CS stage aren't surpassed by the additional noise introduced.

## 4.2 LNA's

As said earlier, the CG-CS topology has been reported in a multiple applications for wide-band LNA's. We will now show some simple equations that allow both a balanced differential output and noise cancelling.

#### 4.2.1 Balun Operation

To achieve the balun operation, it's crucial that booth stages have the same gain. Simple equations for the conditions in which the gain is balanced can be derived. For CG stage, we know from our previous analysis that the input and output current are the same, and as such, the output voltage is given by  $V_o = R_x I_{in}$ . We can then write

$$I_{in} = I_o = \frac{V_{out+}}{R_x} = \frac{R_x}{A_{vCG}}$$

$$\tag{4.5}$$

where  $A_{vCG}$  is the voltage gain of the CG amplifier stage and is approximately equal to  $gm \cdot R_x$ . Since the input impedance is also known to be approximately given by  $1/gm_{CG}$ , and for a LNA the equal the source resistance,  $R_S$  we get that the gain of the CG stage to be given by [17]

$$A_{vCG} = \frac{R_x}{Z_{in}} = \frac{R_x}{R_S} \tag{4.6}$$

Since the gain has to be balanced, but in phase opposition, the gain of the CS stage is then given by

$$A_{vCS} = -\frac{R_x}{R_S} \tag{4.7}$$

If the condition in 4.7 is met, then the LNA will have a balanced balun operation. We shall now derive the equations that guarantee that we can also cancel the thermal noise. We will now study the conditions required to cancel the thermal noise produced by the CG input transistor, modelled by the current source  $I_n$  in Fig. 4.1.

#### 4.2.2 Noise Cancellation

In the CG-CS, the thermal noise current generates a voltage at the input node, and a fully correlated anti-phase voltage at the CG output [17]. The voltage at the input can be expressed as  $V_{nIN} = \alpha_1 \cdot I_n \cdot R_S$  while the output voltage can be written as  $V_{nCG} = -\alpha_1 \cdot I_n \cdot R_x$ , where  $\alpha_1$  accounts for the the voltage division between  $R_S$  and  $Z_{in}$ , which is 1/2 when the input is matched. In order for the noise to cancel, we must have  $V_{nCG} = V_{nCS}$ . We can write the output noise voltage at the CS stage as 4.8 bellow.

$$V_{nCS} = V_{nIN} \cdot A_{vCS} = \alpha_1 \cdot I_n \cdot R_S \cdot A_{vCS} \tag{4.8}$$

By replacing equation 4.7 in 4.8 we guarantee that noise cancelling and balanced balun operation are achieved simultaneously.

### 4.2.3 Distortion Cancelling

The proposed technique cancels all signals that can be modelled as a current source between the drain and source as such, in [18] it's shown that this can effectively cancel the nonlinearity of the input transistor, assuming it's modeled as a current source controlled by the gate. In [17] further proof is presented that all the noise and distortion currents generated by the input transistor can be cancelled. It's also shown that the gain of the CS required for the distortion products of the CG is the same required to guarantee noise cancelling and output balancing.

#### 4.2.4 Design Considerations

From the equations derived in the previous subsections two different design options can be considered while maintaining balanced balun operation and noise cancelling.

- 1) The traditional way to implement the CG-CS amplifier is with balanced gains on the CG and CS. For simplicity  $gm_{CS} = gm_{CG}$  and  $R_{CS} = R_{CG}$

- 2) The transconductance of the CS stage is sized to be n times bigger than the transconductance of the CG stage, while the load resistor of the CG stage is n times smaller. This was the design option chosen in [17] to minimize the noise contribution of the CS stage. Note that for LNA applications, the CG transconductance is imposed because the input match depends on it.

In [17] it's shown that option 2) has an improved noise figure compared to option 1), as it reduces the noise of the CS stage, thus reducing the total output noise (the CG noise is already considered to be cancelled).

## 4.3 TIA's

Although extensively used in LNA's, the CG-CS topology hasn't, to the authors knowledge, been used in TIA's. We will know show that the same considerations made for the LNA amplifier, also apply to the TIA.

## 4.3.1 Balun Operation

For TIA's, we can write  $V_{in}$  as the voltage at the input node to be the product of  $I_{in}$  and  $Z_{in}$ , while  $V_{out+} = R_x I_{in}$  still holds. Thus, we obtain

$$I_{in}R_x = V_{in}A_{vCS} = I_{in}ZinA_{vCS} \tag{4.9}$$

$$R_x = \frac{1}{gm_{CG}} A_{vCS} \tag{4.10}$$

If the condition in 4.10 is true, then we achieve balanced balun operation in the CG TIA.

#### 4.3.2 Noise Cancelling

Simultaneous output balancing and noise cancellation can also be obtained in the CG TIA. It's straightforward to obtain the equality for  $V_{nCG}$  and  $V_{nCS}$

$$A_{vCS} \cdot \frac{I_{nIN}}{gm_{CG}} = I_n \cdot R_x \tag{4.11}$$

If we replace equation 4.10 in 4.11 it's always true, so as in the LNA operation, balanced operation and noise cancelling are achieved simultaneously.

We have thus proved that any signal that can be modelled as a current source between the drain and source of the input transistor in the CG LNA or TIA can be cancelled. Although flicker noise is usually modelled as a voltage source connected in series with the gate of the transistor it can be modelled as a current source because the current in the MOS transistor is dependent on the  $V_{gs}$ . So in this circuit, besides thermal noise cancelling, we also achieve flicker noise cancelling.

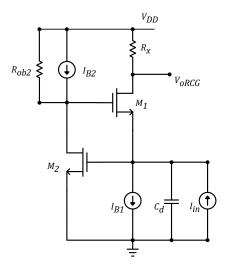

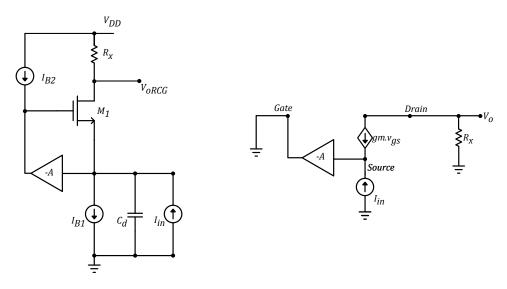

# 4.4 Regulated Common-Gate Stage with Noise Cancelling

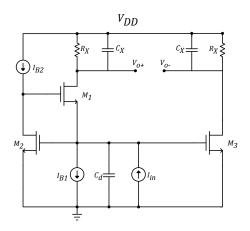

From the previous analysis we have shown that the RCG topology has a lower input impedance, and can be designed in order to obtain a better noise performance then the CG stage. It's then a natural step to employ the technique explained earlier in this chapter to the RCG topology. In order to harness the benefits of differential operation, a CS stage is added in parallel to the RCG, as can be seen in Fig. 4.3. By means of the CS stage, balun operation and potential noise cancelling of the input transistor,  $M_1$  can be achieved.

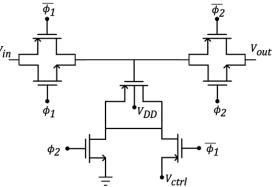

FIGURE 4.3: Balun RCG exploiting thermal noise cancelling.

#### 4.4.1 Balun Operation

In order to guarantee a balanced balun operation, booth the voltage gains of the RCG and CS must be matched. From our previous analysis of the RCG stage, we now that the input impedance of the RCG stage can be written as  $Z_{in} = 1/gm_1(A + 1)$ . In an analogue case to the CG-CS, for low to moderate frequencies, the RCG provides a purely resistive input impedance and we can say that the input current is equal to the RCG output current. We can then write

$$I_{in}R_x = V_{in}A_{vCS} = I_{in}\frac{1}{gm_1(A+1)}A_{vCS}$$

(4.12)

$$R_x g m_1 (A+1) = g m_3 R_X \tag{4.13}$$

Equation 4.13 lays the condition to guarantee balanced balun operation, when booth the output resistance of the RCG and CS are equal.

## 4.4.2 Noise Cancelling

In the CG-CS case, simultaneous output balancing and noise cancellation could be obtained. Because the RCG is effectively a CG stage with gm boosting, the same principle applies. The thermal noise current between the drain and source of the  $M_1$  transistor generates a voltage at the input node, and a anti-phase voltage at the RCG output. We can write these voltages as The  $V_{nIN} = I_n \cdot Z_{in}$  while the output voltage can be written as  $V_{nCG} = -I_n \cdot R_x$ . Since  $V_{nCS} = -V_{nIN}gm_3R_x$  we can write

$$-I_n R_x = -V_{nIN}gm_3R_x \Leftrightarrow \tag{4.14}$$

$$\Leftrightarrow gm_1(A+1)R_x = gm_3R_x \tag{4.15}$$

So the same way that output balancing and noise cancelling where achieved simultaneously in the CG-CS, the same proves to be true for the RCG-CS topology. The same way that thermal noise cancelling of  $M_1$  is achieved, so is any signal that can be be modelled by a current source between it's gate and source.

# Chapter 5

# Discrete Time Parametric Amplifier with Adjustable Gain

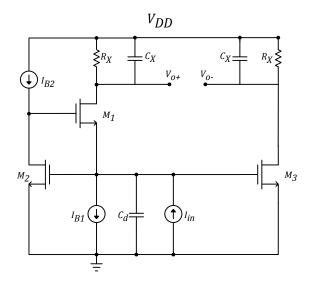

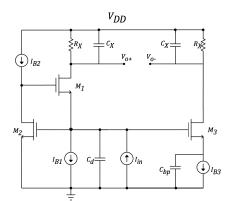

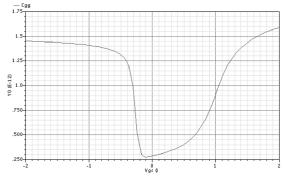

In this chapter the working principle of the Discrete Time (DT) MOS Parametric Amplifier (MPA) is discussed, as well as a brief explanation of the variable MOS capacitors (varactor) which is the basic building block of the DT MPA. The use of the DT MPA in the proposed architecture will cover the need of an extra sample-and-hold (S&H) block between the TIA and ADC while providing a virtually noiseless and controllable amplification stage.

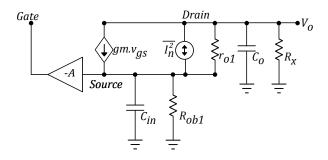

# 5.1 Basic Principles of the DT MPA

A parametric amplifier is a circuit in which the amplification is achieved by using a variable (time-dependent) parameter or circuit element [9]. In this work, the variable element used is a variable capacitor or varactor. While at a first glance, the idea of varying a capacitance to achieve an amplification might sound odd, the basic working principle of the parametric amplifier is actually quite simple. It's known that the charge stored in a capacitor is given by the well known equation

$$Q = C \cdot V \tag{5.1}$$

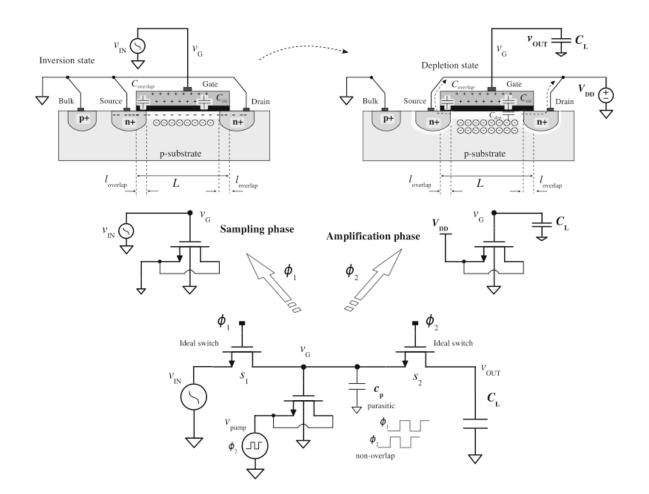

where Q is the charge, C the capacitance and V the voltage applied to the capacitor. Then, if charge is preserved, by varying the capacity of a device, a higher or lower voltage can be obtained. The principle operation of the circuit can be seen in Fig. 5.1. In  $\phi_1$  the input voltage is sampled. Then the top plate of the capacitor is disconnected and left floating while it's capacity is decreased. Finally, during  $\phi_2$ , the amplified voltage is then passed to the output. Note that it's very important the  $\phi_1$  and  $\phi_2$  are non overlapping phases to guarantee that when the capacity is reduced, the capacitor node is floating. This is required to guarantee charge conservation from  $\phi_1$  to  $\phi_2$ .

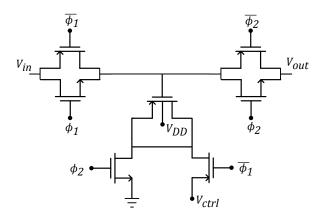

FIGURE 5.1: Principle of operation of the discrete time MOS parametric amplifier.

A first approach reveals that the gain of the amplifier might then be expressed as

$$A_{v} = \frac{V_{o}}{V_{in}} = \frac{C_{\phi 1}}{C_{\phi 2}}$$

(5.2)