#### **Ricardo Jorge dos Santos Marques**

Computer Science Graduate

## Algorithmic Skeleton Framework for the Orchestration of GPU Computations

Dissertação para obtenção do Grau de Mestre em Engenharia Informática

Orientador: Hervé Paulino, Prof. Assistente, Universidade Nova

de Lisboa

Júri:

Presidente: Pedro Barahona

Arguente: Leonel Sousa

Vogal: Hervé Paulino

#### Algorithmic Skeleton Framework for the Orchestration of GPU Computations

Copyright © Ricardo Jorge dos Santos Marques, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa

A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objectivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

Eu dedico esta tese a todos aqueles que, de uma forma ou de outra, contribuiram para que ela se torna-se possível. Esta tese não é so minha, é também vossa.

## Acknowledgements

I would like to start by thanking Professor Hervé Paulino, without whom this work would not be possible. His dedication, his patience, and his constant availability were absolutely fundamental to my thesis. I would also like to thank Professor Pedro Medeiros for his assistance in numerous occasions throughout my thesis. I extend my gratitude towards FCT-MCTES for financing the equipment, namely the GPUs, I used in this project. I thank the department of computer science of Faculdade de Ciências e Tecnologias, da Universidade Nova de Lisboa, (DI FCT UNL) for providing me with conditions to carry out this project.

My thesis also had indirect contributions, by certain individuals. My thanks to Pedro Severino for all the countless hours spent discussing solutions and sharing ideas. Similarly my thanks to André Mourão for providing so many hilarious moments, that helped relive the stress and, consequently, think more clearly. A big thanks to Tania Leitão and Filipe Carvalho for providing a friendly smile, when needed most.

A huge Thank You to Soraia Assis, whose friendship got me by the rough times, and whose smile warmed my own. Without you this thesis would be but a dream.

I thank my parents for all the sacrifices that they endured, so that I would be fortunate enough to study, and eventually reach this mark in my life.

Thank you to all my family members and friends, whose names were not mention so far. They are the silent heroes, whose word is spoken throughout this thesis.

Obrigado a todos!

## **Abstract**

The Graphics Processing Unit (GPU) is gaining popularity as a co-processor to the Central Processing Unit (CPU), due to its ability to surpass the latter's performance in certain application fields. Nonetheless, harnessing the GPU's capabilities is a non-trivial exercise that requires good knowledge of parallel programming. Thus, providing ways to extract such computational power has become an emerging research topic.

In this context, there have been several proposals in the field of GPGPU (General-purpose Computation on Graphics Processing Unit) development. However, most of these still offer a low-level abstraction of the GPU computing model, forcing the developer to adapt application computations in accordance with the SPMD model, as well as to orchestrate the low-level details of the execution. On the other hand, the higher-level approaches have limitations that prevent the full exploitation of GPUs when the purpose goes beyond the simple offloading of a kernel.

To this extent, our proposal builds on the recent trend of applying the notion of algorithmic patterns (skeletons) to GPU computing. We propose Marrow, a high-level algorithmic skeleton framework that expands the set of skeletons currently available in this field. Marrow's skeletons orchestrate the execution of OpenCL computations and introduce optimizations that overlap communication and computation, thus conjoining programming simplicity with performance gains in many application scenarios. Additionally, these skeletons can be combined (nested) to create more complex applications.

We evaluated the proposed constructs by confronting them against the comparable skeleton libraries for GPGPU, as well as against hand-tuned OpenCL programs. The results are favourable, indicating that Marrow's skeletons are both flexible and efficient in the context of GPU computing.

Keywords: Algorithmic Patterns (Skeletons), GPU Computing, OpenCL

## Resumo

A Unidade de Processamento Gráfico (*GPU*) tem vindo a ganhar popularidade como co-processador à Unidade de Processamento Central (*CPU*), devido à sua capacidade de ultrapassar o último em termos de desempenho em certas classes de aplicação. No entanto, aproveitar as capacidades do *GPU* não é uma tarefa trivial, requerendo bons conhecimentos de programação paralela. Assim, fornecer maneiras de extrair tal poder computacional tornou-se um tópico de investigação imergente.

Neste contexto, tem surgido várias propostas na área do desenvolvimento *GPGPU* (Computações de uso geral em Unidades de Processamento Gráfico). Contudo, muitas destas ainda oferecem um abstração de baixo-nível ao modelo de computação *GPU*, obrigando a que os programadores tenham que adaptar as computações das aplicações de acordo com o modelo *SPMD*, bem como em orquestrar os detalhes de baixo-nível inerentes à execução. Por outro lado, as aproximações de alto-nível possuem limitações que impedem o aproveitamento dos *GPUs* quando não se pretende só executar um *kernel*.

Neste sentido, a nossa proposta baseia-se na recente prática de aplicar a noção de padrões algorítmicos (skeletons) à computação *GPU*. Propomos Marrow, uma biblioteca de padrões algorítmicos, que expande o conjunto de *skeletons* atualmente disponíveis neste campo. Os *skeletons* da Marrow orquestram a execução de computações OpenCL e introduzem optimizações que sobrepõe comunicação com computação, agrupando simplicidade de programação com aumento de desempenho em várias aplicações. Além disso, estes *skeletons* podem ser combinados (*nested*) de forma a criar aplicações mais complexas.

Nós avaliámos as construções propostas comparando-as com bibliotecas para *GPGPU* semelhantes, bem como com programas OpenCL base. Os resultados são favoráveis, indicando que os *skeletons* da Marrow são flexíveis e eficientes no contexto *GPGPU*.

Palavras-chave: Padrões Algorítmicos (Skeletons), Computação GPU, OpenCL

## **Contents**

| 1 | Intr | oduction                                          | 1  |

|---|------|---------------------------------------------------|----|

|   | 1.1  | Motivation                                        | 1  |

|   | 1.2  | The Challenges of GPGPU                           | 3  |

|   | 1.3  | A High-Level Skeleton Framework for GPU Computing | 4  |

|   | 1.4  | Contributions                                     | 5  |

|   | 1.5  | Document Structure                                | 6  |

| 2 | Stat | e Of The Art                                      | 7  |

|   | 2.1  | GPU Architecture Evolution                        | 7  |

|   | 2.2  | General Purpose Programming on GPUs               | 10 |

|   |      | 2.2.1 Brook                                       | 11 |

|   |      | 2.2.2 Compute Unified Device Architecture         | 11 |

|   |      | 2.2.3 Open Computing Language                     | 13 |

|   | 2.3  | High Level GPGPU                                  | 19 |

|   |      | 2.3.1 Libraries                                   | 20 |

|   |      | 2.3.2 Programming Language Support                | 22 |

|   | 2.4  | Algorithmic Patterns and GPGPU                    | 28 |

|   |      | 2.4.1 Overview of Patterns for Parallel Computing | 29 |

|   |      | 2.4.2 Skeletons Libraries for GPGPU               | 35 |

|   | 2.5  | Final Remarks                                     | 41 |

| 3 | The  | Marrow Skeleton Library                           | 43 |

|   | 3.1  | Execution Model and API                           | 43 |

|   | 3.2  | Kernels                                           | 45 |

|   | 3.3  | Overlap Between Communication and Computation     | 47 |

|   | 3.4  | Nesting                                           | 49 |

|   | 3.5  | Skeletons                                         | 50 |

|   |      | 3.5.1 Stream                                      | 50 |

|   |      | 3.5.2 MapReduce                                   | 51 |

xiv CONTENTS

|                            |      | 3.5.3              | Pipeline                                        | 52  |

|----------------------------|------|--------------------|-------------------------------------------------|-----|

|                            |      | 3.5.4              | Loop and For                                    | 53  |

|                            | 3.6  | Progra             | amming Model                                    | 55  |

|                            |      | 3.6.1              | Programming Model Structure                     | 55  |

|                            |      | 3.6.2              | Comparison between Marrow's and OpenCL's models | 56  |

|                            |      | 3.6.3              | Programming examples                            | 57  |

| 4                          | Arcl | hitectu            | re and Implementation                           | 67  |

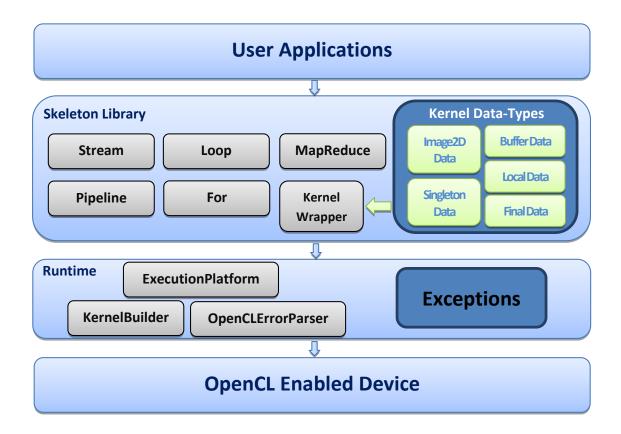

|                            | 4.1  | Archit             | tecture                                         | 67  |

|                            | 4.2  | Imple              | mentation                                       | 70  |

|                            |      | 4.2.1              | Execution Model Specificities                   | 70  |

|                            |      | 4.2.2              | Nesting                                         | 72  |

|                            |      | 4.2.3              | Skeleton Implementation                         | 74  |

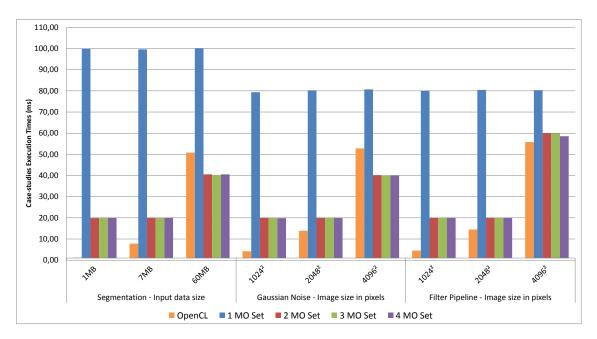

|                            | 4.3  | Addit              | ional Approaches                                | 78  |

| 5                          | Eval | luation            |                                                 | 81  |

| 5.1 Comparison with OpenCL |      | arison with OpenCL | 82                                              |     |

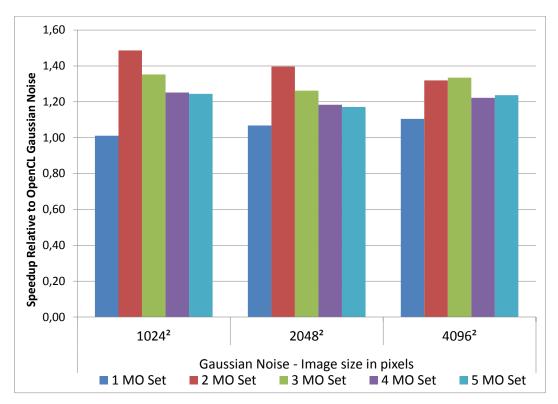

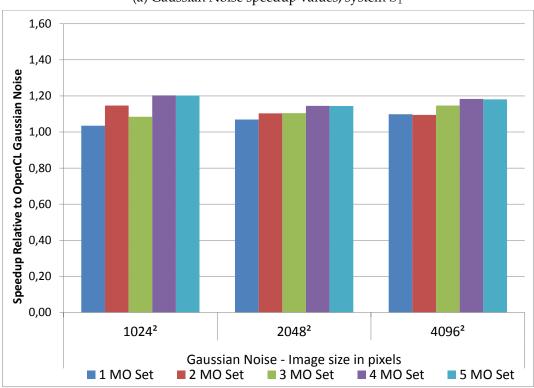

|                            |      | 5.1.1              | Performance Evaluation                          | 84  |

|                            |      | 5.1.2              | Programming Model Evaluation                    | 90  |

|                            | 5.2  | Comp               | arison with SkePU and SkelCL                    | 90  |

|                            |      | 5.2.1              | Performance Evaluation                          | 93  |

|                            |      | 5.2.2              | Programming Model Evaluation                    | 100 |

| 6                          | Con  | clusior            | 1                                               | 105 |

|                            | 6.1  | Object             | tives and Results                               | 105 |

|                            | 6.2  | Future             | e Work                                          | 106 |

# **List of Figures**

| 2.1  | The architecture of the NVIDIA Fermi. Edited from figures in [Cor09]   | 9  |

|------|------------------------------------------------------------------------|----|

| 2.2  | Linear memory segments and threads in a half warp, taken from [NVI09]  | 10 |

| 2.3  | Coalesced access in which all threads but one access the corresponding |    |

|      | work in a segment, taken from [NVI09]                                  | 10 |

| 2.4  | CUDA's software stack, taken from [NVI]                                | 12 |

| 2.5  | CUDA's memory management, taken from [NVI]                             | 13 |

| 2.6  | An OpenCL 2-dimensional index space, taken from [Mun+09]               | 16 |

| 2.7  | Pallas layered hierarchy of patterns, taken from [KMMS10]              | 31 |

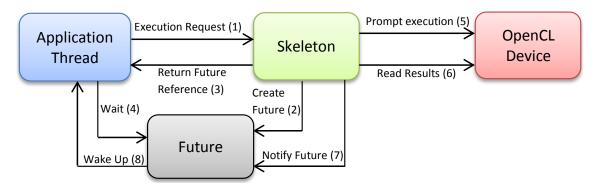

| 3.1  | Marrow's execution model                                               | 45 |

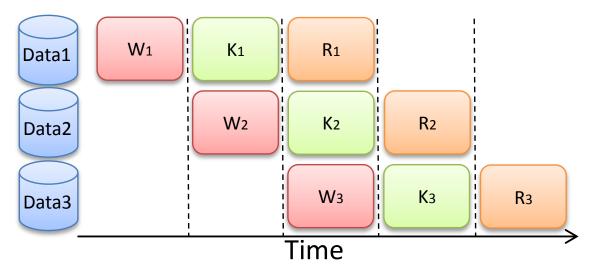

| 3.2  | An overlapped execution order                                          | 48 |

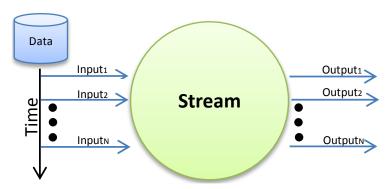

| 3.3  | The Stream skeleton                                                    | 50 |

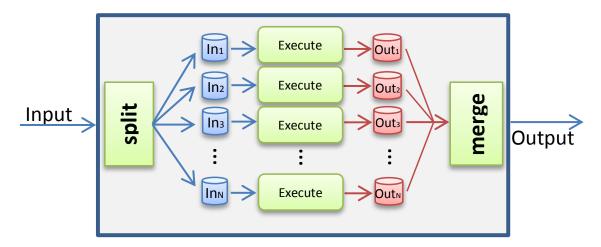

| 3.4  | The MapReduce skeleton                                                 | 51 |

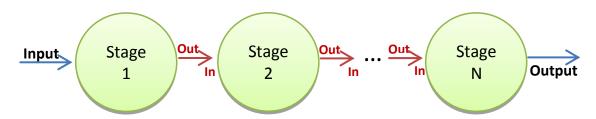

| 3.5  | The Pipeline skeleton                                                  | 52 |

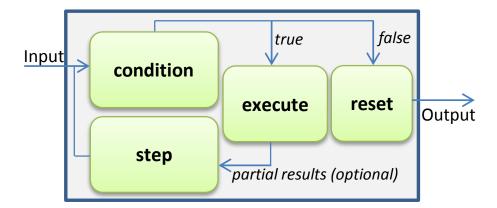

| 3.6  | The <i>Loop</i> skeleton                                               | 54 |

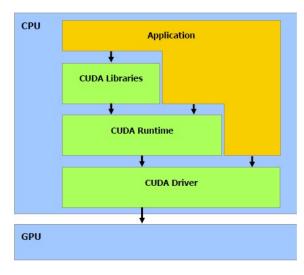

| 4.1  | The Marrow software stack                                              | 68 |

| 4.2  | Execution times for a set of applications                              | 79 |

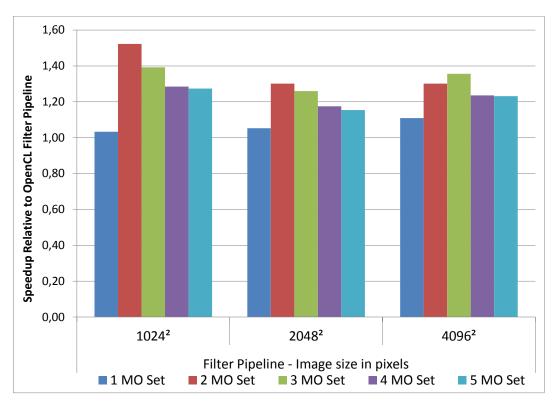

| 5.1  | Gaussian Noise Marrow Speedup Values                                   | 86 |

| 5.2  | Pipeline Marrow Speedup Values                                         | 87 |

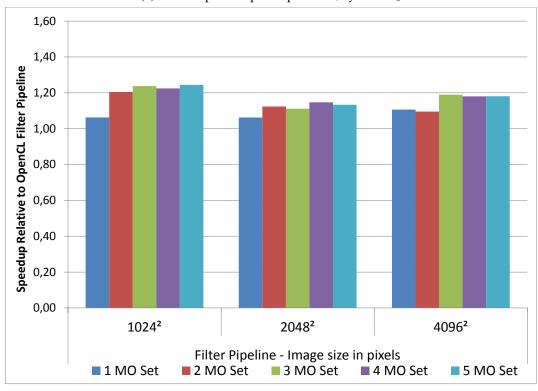

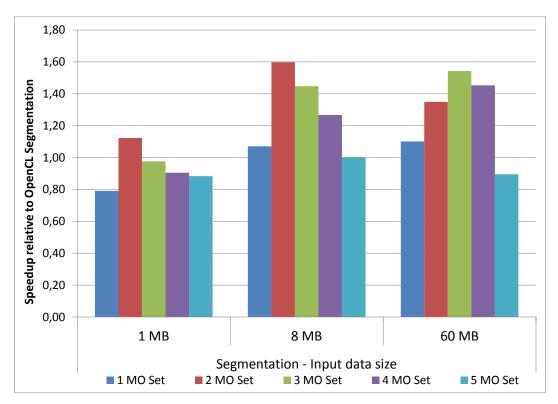

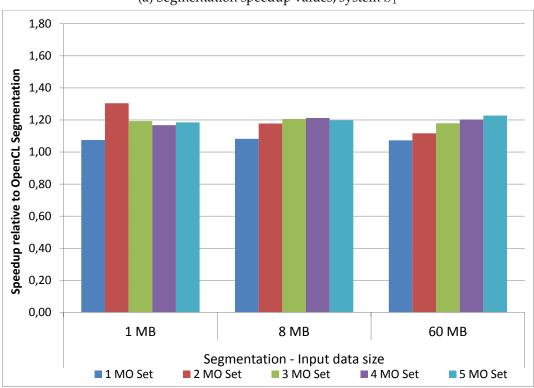

| 5.3  | Segmentation Marrow Speedup values                                     | 88 |

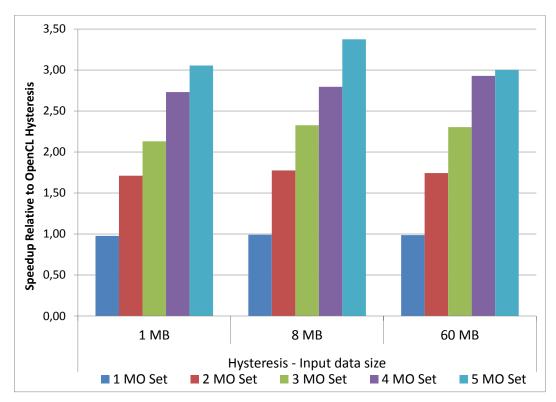

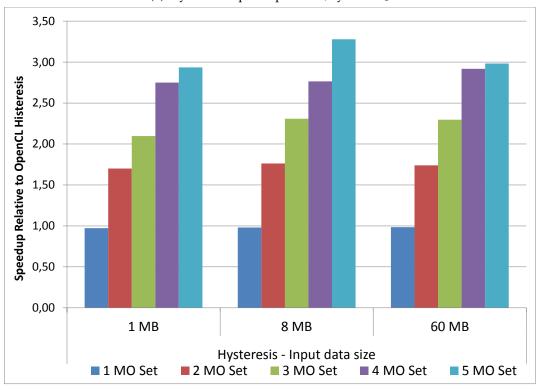

| 5.4  | Hysteresis Marrow Speedup Values                                       | 89 |

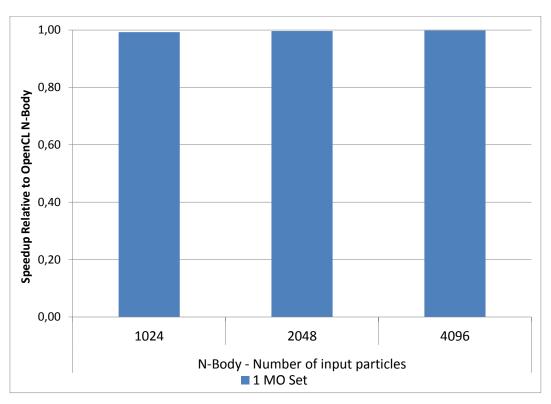

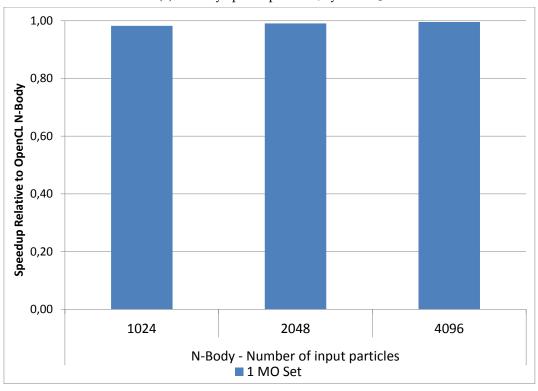

| 5.5  | N-Body Marrow Speedup values                                           | 91 |

| 5.6  | Productivity comparison between distinct application versions          | 92 |

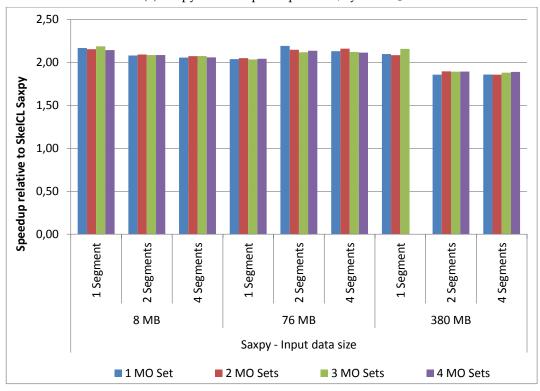

| 5.7  | Saxpy SkePU Speedup Values                                             | 95 |

| 5.8  | Saxpy SkelCL Speedup Values                                            | 96 |

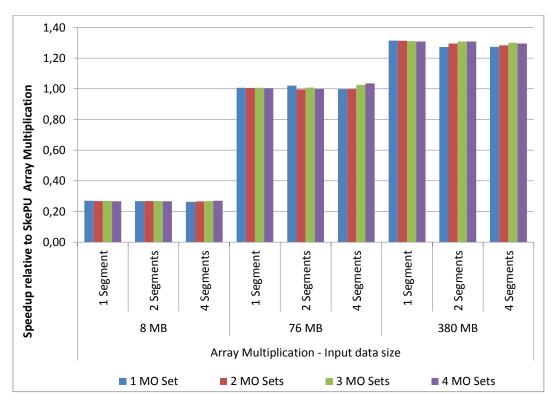

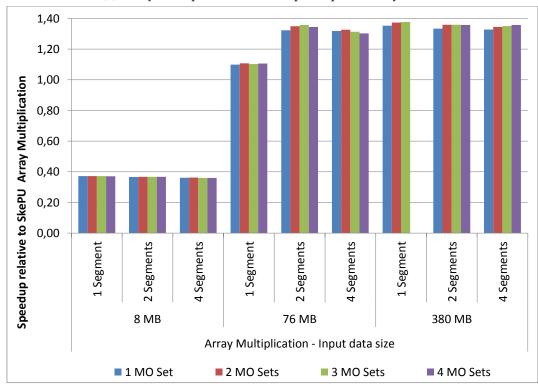

| 5.9  | Array Multiplication SkePU Speedup Values                              | 97 |

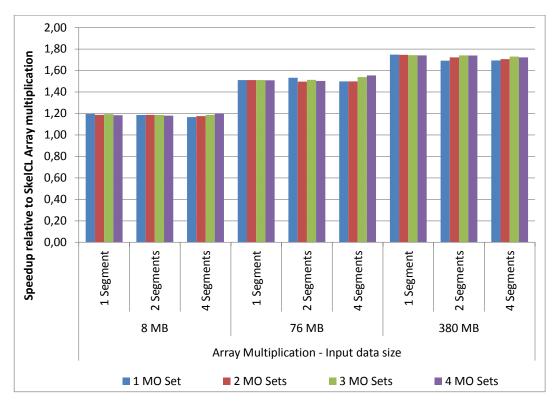

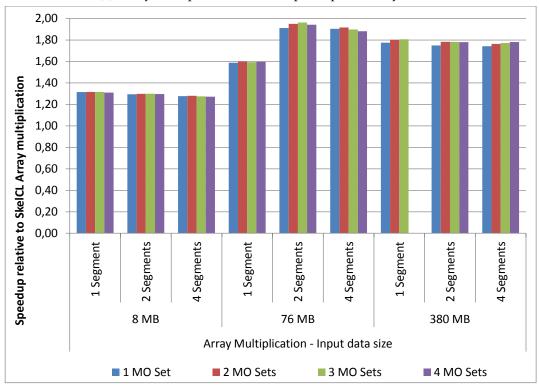

| 5.10 | Array Multiplication SkelCL Speedup Values                             | 98 |

| •   |                 |

|-----|-----------------|

| XV1 | LIST OF FIGURES |

| XVI | LIST OF TIGURES |

|     |                 |

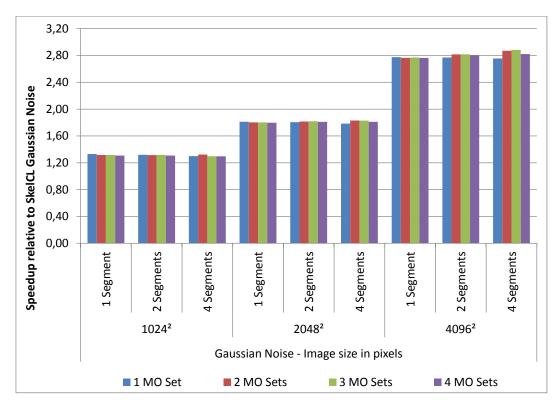

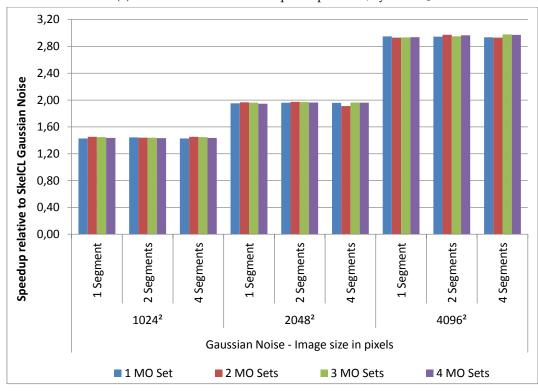

| 5.11 | Gaussian Noise SkelCL Speedup Values | 99  |

|------|--------------------------------------|-----|

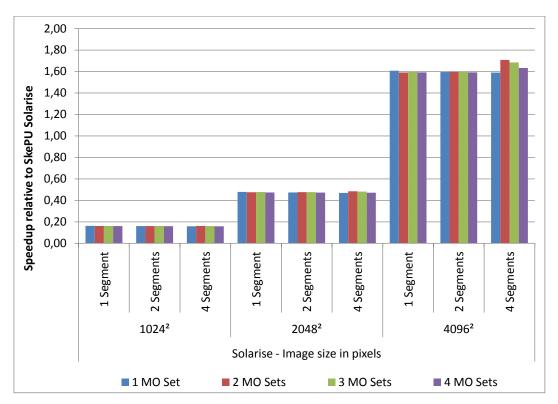

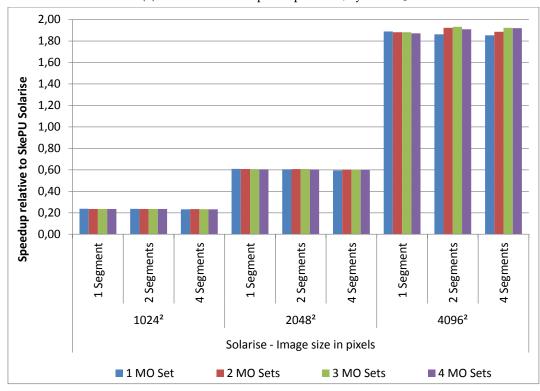

| 5.12 | Solarise SkePU Speedup Values        | 101 |

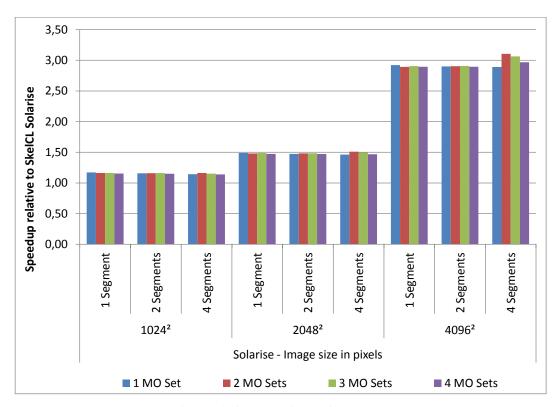

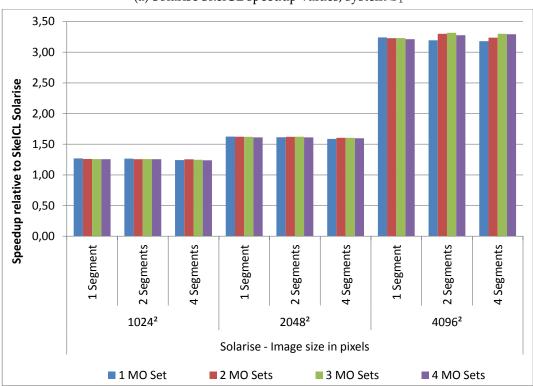

| 5.13 | Solarise SkelCL Speedup Values       | 102 |

|      |                                      |     |

## **List of Tables**

| 2.1 | Comparative table of the algorithmic skeleton frameworks, taken from [GVL]                                             | 10] 33   |

|-----|------------------------------------------------------------------------------------------------------------------------|----------|

|     | Association between argument data-type and memory address space Execution pattern of OpenCL and the proposed skeletons |          |

|     | OpenCL versions execution times in milliseconds                                                                        | 84<br>94 |

xviii LIST OF TABLES

# Listings

| 2.1 | OpenCL code that multiplies two square matrices                          | 18 |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | The kernel function                                                      | 19 |

| 2.3 | SkePU macros, taken from [EK10]                                          | 36 |

| 2.4 | SkePU map reduce example, taken from [EK10]                              | 37 |

| 2.5 | SkelCL computation of the dot product of two vectors, taken from [SKG11] | 39 |

| 3.1 | Initialization of a basic composition tree                               | 57 |

| 3.2 | Declaring a <i>Loop</i> state class                                      | 59 |

| 3.3 | Initialization of a <i>Loop</i>                                          | 60 |

| 3.4 | Initialization of a <i>MapReduce</i>                                     | 61 |

| 3.5 | Nesting exemplification                                                  | 63 |

| 3.6 | Execution example                                                        | 64 |

| 3.7 | Execution example                                                        | 65 |

| 4.1 | ISkeleton class member function definition                               | 71 |

| 4.2 | IExecutable class member function definition                             | 72 |

XX LISTINGS

## Introduction

#### 1.1 Motivation

The future of computing befalls upon parallelism. As transistors continuously get smaller, following Moore's Law [Moo65], today's microprocessor development is mainly concentrated on the addition of execution cores, rather than on the increase of single-thread performance through higher clock speeds. Examples of this trend are the latest CPUs released by Intel, codename Sandy Bridge, that feature up to six physical cores<sup>1</sup>.

Another form of parallel processor is the graphics processing unit (GPU) that, despite starting off as a solution to a very domain specific problem (computer graphics), has been maturing into a powerful general processing unit. Recent GPUs surpass even the CPU in parallel performance and throughput in some particular classes of applications, not necessarily related to graphics processing. Hence, the use of GPUs as co-processors to the CPU is, more and more, a popular computation strategy, that even motivated other approaches aimed at introducing heterogeneity in the CPU's architecture. For instance, the Accelerated Processing Units (APUs) are processors that have both GPU and CPU cores on the same dye. An example of such an architecture is AMD's Fusion [Bro10] processor.

Nevertheless, the GPUs were not always viewed as general purpose co-processors. In the late 1980s all the graphical computations were simple 2D vectorial operations, with great performance concerns in terms of screen drawing speed. Originally, these computations were performed by the CPU, with poor performance results, due to the inadequacy of the latter's architecture. This inefficiency dictated that the evolution of

<sup>&</sup>lt;sup>1</sup>Information taken from http://ark.intel.com/products/codename/29900/Sandy-Bridge

1. Introduction 1.1. Motivation

computer architectures was directed to a path of offloading demanding and domain specific computations to a dedicated processor, giving birth to the GPU. Towards the end of the twentieth century, as 3D accelerated applications gained popularity, due to the gaming market, new graphics APIs with 3D support were proposed (e.g., OpenGL [NDW97], and DirectX [BD98]). With time, the popularity of these APIs caused a relocation of an increasing number of calculation steps to the GPU.

Nowadays, the use of the GPU has crossed the boundaries of graphical computations. Scientific researchers embraced the GPU as an important support beam on which they build complex scientific models that require TeraFlops of computational power, an area commonly referred to as High-Performance Computing (HPC). Besides scientific computations, today the GPU is gaining popularity as a possible way of improving the performance of many general-purpose applications, that run in everyone's computers (e.g., databases [BS10], anti-virus [Kas09], so on and so forth).

GPU architecture differs a lot from the usual CPU design, as it is designed to take advantage of applications that fit well in the data-parallel computing model (expatiated below), where throughput is more important than latency. However, early attempts to harness the computational power of these processors for non-graphic applications meant mapping them to a graphics API, and structuring them in terms of the graphics pipeline. In most cases these tasks were not at all trivial, driving away most inexperienced programmers. Such attempts were recognised by Mark Harris in 2002, subsequently coining this trend as general-purpose computation on graphics processing units (GPGPU) [Har05].

As the GPU evolved into the general-purpose fully programmable processors of today, there was an emergence of some general-purpose programming languages that were more programmer friendly, and allowed for a greater control over the execution of the graphics pipeline. The first popular GPGPU language was NVIDIA's CUDA [NVI]. Because of its C-like syntax, it introduced a smaller learning curve to those who wished to create applications that executed on GPUs. This made CUDA very popular among scientific researchers because it allowed the use of NVIDIA graphics cards for computing scientific models, thus, increasing their efficiency by removing limitations imposed by computational power. However, CUDA is not an industrial standard, and its code is not portable to architectures that are equipped with chips not manufactured by NVIDIA. Later on, as the need for such a standard in GPGPU programming architectures grew, Khronos (a consortium of corporations - whose members feature Intel, AMD, NVIDIA, Google, and many others - bent on creating open standard APIs) saw fit to create the first standard language for GPGPU development. The result was OpenCL [Mun+09], today's standard for GPGPU APIs. It provides a broad set of programming APIs based on past successes. Moreover, it defines core functionality, supported by all platforms, as well as optional functionalities for high-function devices.

The previous GPGPU languages provide a programming model that abstracts the underlying platform model (GPU). They divide the computation in two categories: host,

and device. The host computations, usually processed by a primary unit such as the CPU, orchestrate and issue device executions. In turn, the device runs kernel functions, which are the parallel computations executed by one or more compute units (e.g., CPU cores, cores on a stream multiprocessor). This model will be further elaborated in Chapter 2. As it stands, the execution models of these GPGPU APIs gives support to the following parallel computing models:

- **Data-parallel** Where concurrency is expressed as instructions from a single program applied to multiple independent partitions of a data structure.

- Task-parallel Where computations are expressed in terms of multiple concurrent tasks that have independent instruction locksteps.

#### 1.2 The Challenges of GPGPU

GPGPU APIs were a major development in GPU computing, giving developers a simpler way to use the resources available in GPUs. Nevertheless, using the previously mentioned GPGPU APIs is still a challenging exercise, since not only does the parallel part of the application needs to be structured according to the SMPD model (as described in Section 2.1), but also, the developer has to oversee many low-level programming concerns. The latter range from memory/resource management, to performing data transfers between host and device memories, or even synchronizing the host execution with the auxiliary computing device. On the other hand, if the developer decides to use a non-standard API, such as CUDA, he or she should be aware of the lack of portability attached to such an API. The acknowledgement of these limitations led to the proposal of several high-level GPGPU APIs (e.g., Aparapi [AMD11], Accelerator [TPO06], Rapid-Mind [McC06]), covered in Section 2.3.

Even though these high-level frameworks provide a good level of abstraction relative to the underline platform model (GPUs), they only offer basic building blocks with which to build parallel applications, remaining still significantly close to the underline computing model (parallel computing), and/or not being able to extract the full potential of the architecture. For instance, although Accelerator's execution model is highly oriented towards arrays, it does not support more complex operations than simple element-wise arithmetic combinations (e.g., addition, subtraction, division) of arrays. Even worse, some platforms (e.g., Aparapi) do not even guarantee that the code created by the developer will in fact be executed on a GPU, since this execution is only supported if a transformation from source code to OpenCL code is feasible. These and other particular issues are discussed in more detail in Chapter 2.

It would be advantageous to software developers to have a framework that would provide them with guidelines, that would steer the design process towards good design models. At the same time, the framework would take care of any concerns native to parallel programming (e.g., synchronization, communication), and still be able to harness the

full potential of the architecture. These ideas are some of the main purposes of the recent approach that centres on the application of algorithmic patterns [Col91] (also known as skeletons) to the context of GPGPU development. Skeletons are essentially abstractions of commonly used parallel patterns, like the *MapReduce* or the *master-worker* skeletons (as described in Subsection 2.4). They are provided as algorithmic skeleton frameworks (ASkFs), that contain recurring structures, and behaviours, associated to parallel programming.

To the best of our knowledge, only three platforms that support this type of abstraction on GPUs have been released, namely SkelCL [SKG11], SkePU [EK10], and Muesli [EK12]. Nonetheless, this work is still very preliminary and does not go much beyond supporting the *MapReduce* skeleton and some variants, leaving out skeletons like *Pipeline*, and *Loops*. These types of skeletons have been successfully implemented in other areas (e.g., clusters [CL07], multi-core CPUs [LP10]), and are useful in GPUs since they aggregate multiple computational steps within a persistent memory utilization scheme, not requiring memory transfers between steps. On the other hand, the mechanisms that these libraries provide for the developer to adapt a skeleton's execution are somewhat limiting – in SkePU developers use a macro language, in SkelCL executions are defined and issued as strings, and in Muesli developers are limited to pre-defined data types. In the end of Section 2.4 we give more detail about these and other issues.

When using any of the previous skeleton platforms, developers have no control over how the communication is overlapped with the computations. This obviously simplifies application development, although, if the developer intends to increase general performance by controlling this overlap, it is not possible. For example, a developer may intend to create an application that applies the same execution successively to multiple different data-sets. Given that, the decoupling of the CPU's and GPU's address spaces implies memory transfers, the best executional strategy would be to concurrently send new input data-sets to the device, as it computes upon an older data-set. This would enable the GPU to begin processing the next input immediately after finishing its previous execution, consequently reducing its idle time. However, this is not a particularly easy technique to apply and only Muesli supports this kind of optimization, although is is not parametrizable. On the other hand, none the previous platforms supports nesting of GPU skeletons.

### 1.3 A High-Level Skeleton Framework for GPU Computing

Our proposal builds on the idea of applying the notion of skeletons to the context of GPGPU development. We intend to solve some of the previously mentioned issues by developing an ASkF that is mainly focussed on orchestrating the execution of OpenCL kernels, and offers a varied set of data- and task-parallel skeletons. By not delving into the domain of the parallel computations (kernels) we were able to propose a framework that has a rich set of constructs, that can still support the major functionalities offered

1. INTRODUCTION 1.4. Contributions

by the OpenCL language. The set of proposed skeletons include some that are already present in the context of CPUs and clusters (e.g., *Pipeline*), and others there are completely new to this context (e.g., *Stream*), as far as we know. Also, only in the interests of completeness, our ASkF supports common GPU skeletons, like the *MapReduce*. We were primary interested in skeletons whose execution behaviour was not hampered by the logical, and physical, division between the host and device address spaces. Skeletons whose execution is based on persistent data schemes are attractive to us because they do not require data-transfers when combining distinct execution instances. In this way, they avoid the overheads associated to transfers between disjunct memory spaces. For example, consider a N-staged *Pipeline*. If executed on the GPU, the results of stage i, where 0 < i < N, do not have to be transferred back to main memory in order to be available to the subsequent stage (i+1). There are other examples of such skeletons. The entire set supported by our ASkF is presented in Chapter 3.

We deemed as very important to allow the combination, or nesting, of skeletons as it enables developers to build complex executional structures, possibly containing very distinct behaviours, in a very simply and efficient manner. This technique is also beneficial in terms of performance, in that it is compatible with a disjoint memory scheme. An application may apply a successive collection of computations, in the form of skeletons, to an input data-set, and only carry out memory transfers when: writing the input to device memory, and reading the results to main memory. Furthermore, the nesting mechanisms helps the skeleton design to remain simple. A skeleton may only provide a very specific behaviour, since more complex structures are created by nesting multiple skeletons.

We also sought to allow the developer to seamlessly introduce performance gains by having the skeletons overlap communication and computation. By doing so, the skeletons can make better use of the parallelism qualities of modern GPUs, and increase overall productivity. Having the skeletons transparently apply this execution strategy obviously facilitates the developer's job. He or she can develop efficient applications without having a large degree of knowledge in both, parallel programming, and the OpenCL language features.

In essence, our approach is to design and implement a high-level skeleton framework for the orchestration of GPU computations that encompasses the above concerns: performance (by overlapping communication with computation) and modularity (by supporting nesting of skeletons).

#### 1.4 Contributions

The main contribution is C++ ASkF, named *Marrow*, for the orchestration of OpenCL kernels, that introduces new skeleton constructs within that scope. Marrow is supported by a OpenCL runtime, that provides a standard execution model across multiple heterogeneous parallel architectures, despite our main focus being in GPUs. Additionally,

1. Introduction 1.5. Document Structure

Marrow's constructs can be nested, which to the best of our knowledge is a functionality not supported by any GPGPU ASkF. The nesting enables the development of intricate parallel applications without having to manually connect distinct computational models, and implicitly avoiding heavy memory transfers. These resulting applications transparently use overlap between communication and computation as a way to increase overall performance. Overlap reduces the overhead introduced by constant memory transfers and gives a virtual sense of persistence to the computations. Moreover, it enables us to exploit concurrency between computations and memory data transfers, increasing the application's parallel factor.

Another key contribution is fact that Marrow has an OpenCL based implementation. This highly increases the portability of the code produced when using Marrow, considering that if the underlying platform supports OpenCL, then it is very likely that it fully supports Marrow. Naturally, there are other portability concerns derived from the use of the C++ language, namely using a compiler that fully supports C++11. However, this issue does not significantly impair our library's portability.

Yet another contribution is the comparative evaluation that we performed. We compared Marrow in terms of performance and programming model productivity, against OpenCL, SkePU, and SkelCL. We left out Muesli, since the latter enables GPU executions through CUDA, consequently distancing itself from our direct research focus.

#### 1.5 Document Structure

The remainder of this document is structured as follows:

- **Chapter 2** Presents the state of the art associated to our research area. Naturally, our research area is associated to GPGPU technologies at different levels (e.g., low-level, high-level, algorithmic patterns), so the most relevant technologies at each level are described. Additionally, an overview about GPU architecture is given.

- **Chapter 3** Expatiates on the developed C++ ASkF, Marrow. The chapter discusses all of Marrow's core features and functionalities, namely: the supported skeletons, nesting mechanism, overlap between communication and computation, and others.

- **Chapter 4** Presents Marrow's architecture, as well as its most relevant implementation details.

- **Chapter 5** Validates the developed library, by presenting and discussing experimental results that evaluate Marrow's performance and programming model against technologies of lower and higher abstraction level.

- **Chapter 6** Summarises key aspects about the work carried out in this dissertation. Particularly, it reflects on the achievement of the proposed objectives; on the contribution of Marrow to the current state of the art on GPU computing; and discusses possible future research topics, within Marrow's context.

## State Of The Art

To better understand the GPU's potential for general-purpose computing, and what kind of attempts have been made to exploit its capabilities, this chapter presents a description of the most relevant GPGPU technologies in general GPU computing, and particularly in regards to our proposal. This chapter begins by providing a brief overview about the evolution of GPU architecture (Section 2.1), based on [OHLGSP08]. Then, GPGPU technologies are presented, from lowest (Section 2.2) to highest (Section 2.3) level. Subsequently, an alternative to the common methodologies of high-level GPGPU platforms is presented, in the form of computational patterns (Section 2.4). Lastly, our final considerations about the current state of the art, in regards to GPGPU development, are given in (Section 2.5). Should be noted that only the platforms that have a direct impact in our work, either by development support or by intellectual contribution, are provided with programming examples.

#### 2.1 **GPU** Architecture Evolution

It all begins at the graphics pipeline, the basis for the GPU's architecture. It is where the input, a list of geometric primitives, is shaded and mapped onto the screen. The steps in the canonical pipeline are:

- 1. **Vertex Operations** Each vertex from the input primitives is transformed from a 3D position into a 2D screen coordinate (referred to as *the shading process*). Since vertices can be computed independently, this stage is well suited for parallel hardware.

- 2. **Primitive Assembly** The vertices are assembled into triangles, that is the fundamental primitive in current GPU architectures.

- 3. **Rasterization** This is the process of determining which screen-space pixel locations are covered by each triangle. Every triangle generates a primitive called a *fragment* at each screen-space pixel location that it covers.

- 4. **Fragment Operations** Determines the final color of each *fragment* by using the color information from the vertices and/or textures. Even though the elements in this step can be computed in parallel, this is typically the most computationally demanding stage in the graphics pipeline.

- 5. **Composition** Finally, fragments are assembled into a final image, with one color per pixel.

First GPUs were composed of highly specialized function units, however, as they became faster in rendering basic computer graphics, demand for more sophisticated techniques grew. Most functionalities, supported by these early GPUs, were fixed functions. That is to say, if a new technique was developed and was not supported by the graphics API, the hardware had to be directly modified so that the API could be extended to support such functionality. There was not much room for the API to grow on top of the hardware because the latter had very specific and limiting functionalities, which greatly limit the possibilities of software developers.

The overcoming of these limitations required a major architectural switch of GPUs. Highly specialized function units were replaced by smaller and simpler processors, transforming the GPU's architecture into a SIMD architecture. A SIMD (Single Instruction Multiple Data) architecture is composed of multiple processing elements capable of executing the same operation on multiple data streams simultaneously, as defined by Flynn in [Fly72]. The GPU's hardware was composed of large amounts of processors for vertex and pixel specific calculations, increasing the flexibility of the hardware and providing the vendors with a scalable architecture.

Further refinements were made to the architecture over the years, like the unification of the vertex and pixels specialized processors into a single less specialized type with only one instruction set, capable of handling all the previous tasks. This increased the complexity of the processors, but also made them more flexible. That refinement is to-day denominated as the Unified Shader Model 4.0 [Bly06]. Also, modern GPUs provide a SPMD (Single Program Multiple Data) computing model where multiple processing elements execute the same program, having a synchronization lockstep at program level instead of at instruction level, as happens in a SIMD model. This means that the execution path between processing elements may differ.

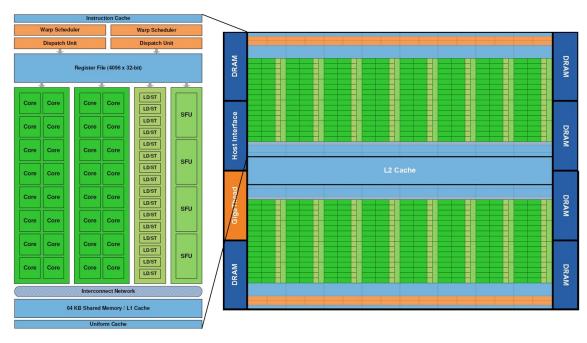

Modern GPUs feature a big parallel pipeline with a high data throughput, also having programmable components as opposed to the original fixed function components. A good example of a unified and massively parallel programmable unit is the architecture of the NVIDIA Fermi, depicted in Figure 2.1. It features sixteen stream multiprocessors of thirty-two cores each, summing up to five-hundred and twelve processing cores. Each

Figure 2.1: The architecture of the NVIDIA Fermi. Edited from figures in [Cor09]

stream multiprocessor has its own 64 KB L1 cache, shared by its thread processors, as well as a 16 KB register file. There is also a L2 cache that is shared by the stream multiprocessors.

Fully utilizing the potential of the modern GPU architecture is complex endeavour. The differences from the usual parallel programming methodology (CPU) are such, that there is a high probability of creating an inefficient GPU program, if the developer does not pay close attention to specifications of the underlying hardware. Considering only NVIDIA GPUs, and their terminology, one such difference is the fact that the smallest executable unit of parallelism on a device, a warp, comprises 32 threads. Stating that every modern NVIDIA GPU can support a minimum of 768 threads per multiprocessor [NVI09], a device that has 30 multiprocessors can have more than 30000 active threads. This parallel capability can be easily wasted if the number of threads is not sufficient to fill every available multiprocessor. Thus, executing a very small number of threads may present more overheads than actual performance benefits.

Typically, hundreds of threads are queued up for work (in warps). These GPU threads are extremely lightweight, in contrast with CPU threads. If a processor must wait on one warp of threads, it simply begins executing work on another. Because register are allocated to active threads, no swapping of registers and state occurs between GPU threads, and resources stay allocated to a thread until it completes its executions. This efficient warp swapping is usually beneficial, although very sensitive to the memory access patterns of threads. If the accesses to principal GPU memory (global memory) by threads within a warp are not coalesced, then general performance will be significantly reduced.

GPU global memory loads/stores by threads of a half warp (16 threads) are coalesced by the device in as few as one transaction, when certain access requirements are met. To

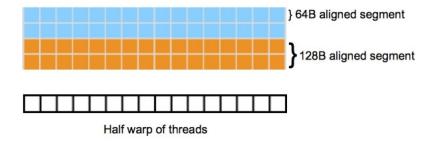

Figure 2.2: Linear memory segments and threads in a half warp, taken from [NVI09]

Figure 2.3: Coalesced access in which all threads but one access the corresponding work in a segment, taken from [NVI09]

understand these memory access recommendations, global memory should be viewed in terms of aligned segments of 16 and 32 words, as in Figure 2.2. It shows global memory as of 64-byte aligned segments. Two rows of the same color depict a 128-byte aligned segment. At the bottom of the figure is indicated a half warp of threads that accesses the global memory.

A simple coalesced access pattern is represented in Figure 2.3. The *k*-th thread accesses the *k*-th word in a segment, though it is not necessary that every thread participates. This access pattern results in a single 64-byte transaction (highlighted by the red rectangle). Even the unnecessary word is fetched from global memory. If just one of these threads, for example the one that did not participate, accessed a data value that was not stored in the first 16 words, then the half warp would required two full transactions before beginning its execution. Logically, increasing the number of transactions reduces performance, since the warps are left waiting rather then executing.

### 2.2 General Purpose Programming on GPUs

As the computational power of GPUs (and CPUs) grew it was noticed that for certain domains of computation, like data-parallel oriented applications, the use of GPUs outperformed even the most extremely optimized CPU versions of the algorithms. This reality fostered the proposal of new APIs, which were not exclusively for graphics programming: Instead, they allowed the development of more general-purpose applications. The

most relevant GPGPU APIs are subsequently presented.

#### 2.2.1 Brook

Brook [BFHSFHH04] is a language that was designed to provide programmers with native support for data-parallelism, while still being efficient enough to allow the development of arithmetic intensive applications. Furthermore, it had portability concerns, enabling programs to run in various heterogeneous architectures. To accomplish these goals Brook provides various features, of whom the most important are: Streams, Kernels and Reductions.

**Streams** are the basic building blocks of Brook. They define a collection of data which can be operated in parallel. Each stream is composed of elements, whose domain falls in the primitive types provided by the language, such as floats. A similarity can be traced between streams and C arrays, although, access to a stream is restricted to a kernel.

**Kernels** are functions which are applied to every element of a stream. In order to obtain a data-parallel application of the kernels to the streams, programmers are forced to distinguish between the input data of a kernel, used as read-only, and the respective output data, used as read-write.

**Reductions** are the inverse of a kernel, that is, they provide a mechanism for calculating a single value from a collection of records. Reductions accept a single stream and output either a smaller stream of the same type, or a single element value. An example of reduction is summing all the integer elements of a stream. Reductions are still data-parallel.

Brook was the first effective approach to GPGPU development. However, due to the release of other GPGPU APIs, namely CUDA, it was never really adopted in the industry, being remitted as a case study for research activities.

#### 2.2.2 Compute Unified Device Architecture

Compute Unified Device Architecture (CUDA) [NVI] was created by NVIDIA and released in 2007. It is a hardware and software architecture for issuing and managing data-parallel oriented computations on the GPU, without the need of mapping them to a graphics API.

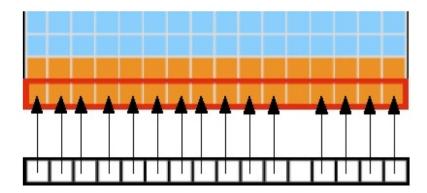

#### Architecture overview

The CUDA software stack is composed of three layers, as shown in Figure 2.4. An important aspect of CUDA is that it provides general memory addressing, that is, from a programming perspective the application can read and write data at any memory address, equivalent to a CPU and system RAM.

Figure 2.4: CUDA's software stack, taken from [NVI]

- 1. Two high-level mathematical libraries CUFFT and CUBLAS.

- API and its runtime The API comprises an extension to the C programming language.

- Hardware driver Being designed by NVIDIA, CUDA relies on hardware specific drivers, created for their own graphics cards.

#### **Programming Model**

In CUDA, the GPU is viewed as a data-parallel co-processor, capable of executing a huge number of threads in parallel. To get the desired effect, a function that operates on each of the data independent partitions is compiled to the instruction set of the device. At runtime the resulting program, a kernel, is downloaded to the device and mapped onto one or more threads. Both the host (CPU) and the device (GPU) maintain their own memory, allowing the programmer to issue data transfers between them as needed.

To organize the different threads running the same kernel in the device, CUDA joins together batches of threads, as thread blocks, allowing them to cooperate and synchronize by sharing data through fast shared memory. Each thread is assigned a thread identifier, which is the thread's number within its block.

There is a limited maximum number of threads that a block can contain. Nevertheless, blocks of equal dimensionality and size that execute the same kernel can be grouped together into what is known as a grid of blocks. This is done at the expense of thread cooperation, because threads in different blocks inside a grid cannot communicate or synchronize. Yet, this mechanism allows devices to run all the blocks of a grid sequentially, in parallel, or even a combination of both, boasting the parallel factor of the device. The block's identifier is its number within the grid.

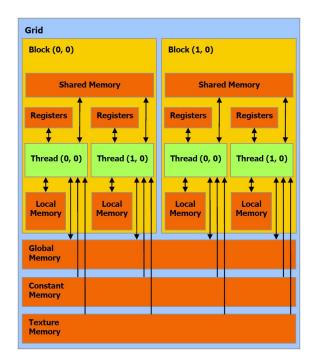

CUDA's memory management coordinates the memory access per-thread, per-block and per-grid, dividing the memory between grids, and structuring the memory spaces as illustrated in Figure 2.5. In this memory coordination scheme, the host has full access to the global, constant, and texture memories.

Figure 2.5: CUDA's memory management, taken from [NVI]

- **Registers** Read-write per-threads.

- Local memory Read-write perthreads.

- **Shared memory** Read-write perblock.

- Global memory Read-write pergrid.

- Constant memory Read-only pergrid.

- Texture memory Read-only pergrid.

#### 2.2.3 Open Computing Language

As the GPUs evolved into programmable parallel processors, it became important to provide software developers the means to easily use these powerful processing platforms. Furthermore, the need for software developers to take full advantage of heterogeneous processing platforms (e.g., servers, desktop computers, hand-held devices) has grown.

This lead to the proposal of some platforms on which software developers could build applications that used both CPUs and GPUs as main computational devices, giving developers a simple yet efficient way to control and use them. However, these platforms were usually associated to a specific vendor or hardware and were not standard from an industry perspective. As a result, they hampered the development of applications that harnessed the computational power of these processors, from a single or multi-platform source code base.

With these prospects in mind, a consortium of corporations, known as Khronos, joined efforts to create an industrial open standard language for general-purpose parallel programming, across multiple hardware platforms. The result is a language known as OpenCL [Mun+09].

"OpenCL (Open Computing Language) is an open royalty-free standard for general purpose parallel programming across CPUs, GPUs and other processors, giving software developers portable and efficient access to the power of these heterogeneous processing platforms." [Mun+09]

Being launched in 2008, it supports a wide range of applications, from consumer software, to HPC solutions. It is particularly suited to play a key role in emerging interactive

graphics applications that combine graphics rendering pipelines with general parallel compute algorithms.

Structurally, OpenCL is a cross-platform programming language, featuring an API that enables the coordination of parallel computations across multiple heterogeneous processing devices. However, it is more than just a language. It is a framework on which software developers can build general-purpose programs that execute on GPUs without the need to map their algorithms into a 3D graphics API such as OpenGL [NDW97] or DirectX [BD98]. Its architectural details will be subsequently outlined.

#### **Platform Model**

OpenCL's platform model if fairly straightforward. Nevertheless, first we must define a common terminology that is going to be used throughout the rest of the thesis.

- **Host** Formally, the host is the entity that uses the OpenCL API. Usually, it is a processing unit such as a CPU.

- **OpenCL device** An OpenCL device is a collection of compute units, that execute commands issued by the host. Typically, these devices correspond to GPUs, multicore CPUs, or other forms of parallel architectures.

- Compute Units A compute unit is composed of one or more processing elements. In most modern GPUs, for example, a correspondence to a compute unit is a stream multiprocessor, composed of a very large number of small processing units.

- **Processing Elements** It is a virtual scalar processor. It is the basic computational structure, on which the commands issued by the host are computed. For example, it is and ALU (arithmetic logic unit) inside a stream multiprocessor, in a GPU.

OpenCL's platform model consists of a host connected to one or more OpenCL devices, which in turn are divided into one or more compute units. These compute units are further divided into one or more processing elements.

An OpenCL application runs on a host according to its platform model. The application submits commands from the host to the device, prompting the execution of computations on the processing elements. On the other hand, these processing elements execute a single stream of instructions as SIMD units.

#### **Execution Model**

Firstly we must expand the terminology defined previously.

Context – The environment within which the kernels execute. It includes, for example, a set of devices, the memory objects accessible to those devices, and one or more command-queues associated each device.

- Command-queue An object that holds commands that will be executed on a specific device, of a particular context. Commands to a command-queue are queued in-order but may be executed in-order or out-of-order.

- Kernel A kernel is a function declared in an OpenCL program. It is executed by an OpenCL device.

- Work-item It is an instance of a kernel, executed by one or more processing elements.

- Work-group It is a collection of work-items that execute concurrently on the processing elements of a single compute unit. All the work-items inside a work-group execute the same kernel and share local memory.

- **Program Objects** The program source and executable that implements a specific kernel.

- Memory Objects A set of objects visible to both the host and the OpenCL devices.

The execution of an OpenCL program is divided into two parts: kernels that execute on OpenCL devices, and host program that executes on the host. This model is very close to CUDA's execution model, differing mostly in the terminology - CUDA has threads instead of work-items, and thread blocks instead of work-groups.

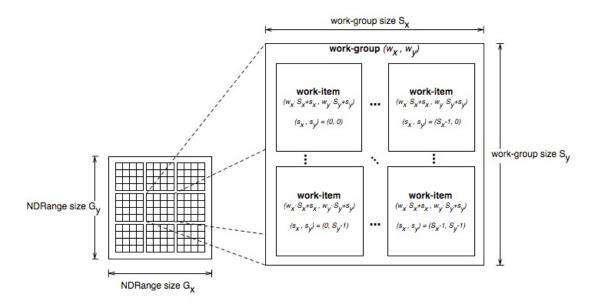

When the host submits a kernel for the device to execute an index space is defined. This index space is called NDRange and it is a N-dimensional index space, where N is either one, two, or three. It is defined by an integer array of length N, that specifies the length of each dimension. Each point of this index space is called a work-item, and each work-item is assigned a global identifier that constitutes a N-dimensional tuple, whose components range from zero to the number of elements in that dimension minus one, that corresponds to its position within the index.

In order to provide a more coarse-grained decomposition of the index space, workitems are joined together to form work-groups. To define the number of work-groups in each dimension, an array of length N is created. Each work-group is then assigned a unique global identifier with the same dimensionality as the work-items index space. Additionally, work-items are assigned a local identifier in order to uniquely identify them within a work-group. Again, we have similarities to CUDA's execution model since a NDRange index space is analogous to a grid of thread blocks.

To exemplify the manner in which a work-item can be identified within the index, lets consider Figure 2.6. The host inputs the index space for the work-items  $(G_x, G_y)$  and the number of work-items per work-group  $(S_x, S_y)$ , in each dimensions. This defines a global  $G_x$  by  $G_y$  index space where the number of work-items is  $G_x \times G_y$ , and a work-group  $S_x$  by  $S_y$  local index space where the number of work-items per work-group can be given by  $S_x \times S_y$ . Hence, the number of work-groups can be given by  $(G_x/S_x) \times (G_y/S_y)$ .

A work-item global identifier  $(g_x, g_y)$  is obtained directly form its position within the index space, or by combining its local identifier  $(s_x, s_y)$  and work-group identifier  $(w_x, y_y)$  as:  $(g_x, g_y) = (w_x \times S_x + s_x, w_y \times S_y + s_y)$

Figure 2.6: An OpenCL 2-dimensional index space, taken from [Mun+09]

The OpenCL execution model explicitly supports both data-parallel and task parallel programming models. To do so, a host program must define a context for the execution of the kernel and its resources (e.g., devices, command-queues, kernels, program objects, memory objects). This context is manipulated by the host through the use of functions from the OpenCL API. The host then places commands into a data structure called a command-queue, which are then scheduled onto the respective device.

#### **Memory Model**

In OpenCL's architecture the memory is divided into four distinct regions:

- **Global Memory** This memory region allows read/write access to all the workitems in the index space, as well as to the host.

- Constant Memory This region allows read/write access to the host, but only read

access to the work-items.

- Local Memory A memory region local to work-group, therefore it can be used to

allocate memory objects shared by all the work-items of that specific group. The

host has no access to it.

- Private Memory A region of memory private to a work-item. Logically, variables stored in one work-item's private memory are not visible to another work-item. The host has no access to it.

This memory scheme is parallel to CUDA's, except in the absence of texture memory. The host's memory is usually independent from the OpenCL device's memory, however, they often need to interact. This interaction occurs either by direct copy between memories, or by mapping and unmapping regions of a memory object. To map objects to the device, the host's program uses the OpenCL API to create memory objects in global memory, and also to enqueue memory commands in order to operate on these objects. In similar fashion, to copy data explicitly the host enqueues commands to transfer data between memories.

When it comes to memory consistency, OpenCL uses a relaxed consistency model. So, the state of memory visible to a work-item may not be consistent across a collection of work-items at a given point. Only private memory has load/store consistency, the local memory is only consistent across work-items in a single work-group at a work-group barrier (a barrier is a standard synchronization mechanism in parallel computing). This is also valid for global memory, but there are no guarantees of memory consistency between work-items in different work-groups.

#### **Programming Model**

To better understand the fundamentals of the OpenCL language, a simple OpenCL program, that illustrates its basic functionalities and properties, is depicted in Listing 2.1. This example presents a program that multiplies two square matrices, A and B, and stores the results in matrix C. Nonetheless, to simplify this exemplification, the code only contemplates the essential parts related to OpenCL. Therefore, all the error checks, possible optimizations, and auxiliary functions are left out.

Before the kernel is executed by the OpenCL device some aspects relative to the execution environment must be configured, by following some common steps. First the devices that are able to run the kernel must be obtained (line 19). The type of the desired device can be selected, provided it exists in the given platform. A context must be created and associated with the devices obtained previously (line 21). It is possible to choose and use more than one device, although, in this example only one is used. Nonetheless, the need to submit orders to the device still remains. This can be accomplished by creating a *command-queue*, associated to the device and the context (line 22).

Now that the configuration of the platform is complete, the memory objects that the kernel can access must be initialized, along with their respective access permissions (lines 23 to 28). In this example, the memory objects are initialized and, at the same time, filled with the values from the matrices A and B.

Subsequently, the kernel function source (Listing 2.2) must be read, compiled, and used to create a kernel object (lines 29 to 31). There are several ways to obtain the source, so the procedure used in this example is not important. Now that kernel has been created it must bet pointed to needed arguments, for example the matrices (lines 33 to 37).

A NDRange index space is defined in order for OpenCL to map the kernel onto the

work-items. This initialization requires the number of dimensions, of work-items per dimension, and optionally, of work-items per work-group (line 38). Then, the OpenCL device is ordered to run the kernel (line 39).

Lastly, the results are read, and the resources are freed (lines 42 to 50). Note that this example is not at all optimized, since our focus in this description is readability and ease of understanding.

Listing 2.1: OpenCL code that multiplies two square matrices

```

int main(int argc, char** argv) {

int matrix_width = atoi(argv[1]);

2

int matrix_size = matrix_width*matrix_width;

int mem_size = sizeof(int)*matrix_size;

int *A = (int*) malloc(mem_size);

int *B = (int*) malloc(mem_size);

int *C = (int*) malloc(mem_size);

randomInit(A, matrix_size); randomInit(B, matrix_size);

cl_platform_id platform_id;

cl_device_id device_id;

10

cl_context clContext;

cl_command_queue clCommandQueue;

12

cl_program clProgram;

13

cl_kernel clKernel;

14

cl_int errcode;

15

cl_mem cl_A, cl_B, cl_C;

16

clGetPlatformIDs(1, &platform_id, NULL);

17

18

int is_gpu = atoi(argv[2]);

errcode = clGetDeviceIDs(platform_id, is_gpu ? CL_DEVICE_TYPE_GPU :

19

CL_DEVICE_TYPE_CPU, 1, &device_id, NULL);

20

clContext = clCreateContext(0, 1, &device_id, NULL, NULL, &errcode);

21

22

clCommandQueue = clCreateCommandQueue(clContext, device_id, 0, &errcode);

cl_C = clCreateBuffer(clContext, CL_MEM_READ_WRITE, mem_size,

23

NULL, &errcode);

24

cl A = clCreateBuffer(clContext, CL MEM READ WRITE | CL MEM COPY HOST PTR,

25

mem_size, A, &errcode);

cl_B = clCreateBuffer(clContext, CL_MEM_READ_WRITE | CL_MEM_COPY_HOST_PTR,

27

mem_size, B, &errcode);

28

clProgram = getKernelSource(argv[3],clContext);

29

errcode = clBuildProgram(clProgram, 0, NULL, NULL, NULL, NULL);

clKernel = clCreateKernel(clProgram, "matrixMul", &errcode);

31

int cl_matrix_width = matrix_width;

32

errcode = clSetKernelArg(clKernel, 0, sizeof(cl_mem), (void *)&cl_C);

33

errcode |= clSetKernelArg(clKernel, 1, sizeof(cl_mem), (void *)&cl_A);

errcode |= clSetKernelArg(clKernel, 2, sizeof(cl_mem), (void *)&cl_B);

35

errcode |= clSetKernelArg(clKernel, 3, sizeof(int),

36

37

(void *)&cl_matrix_width);

size_t globalWorkSize[2] = {matrix_width, matrix_width};

38

errcode = clEnqueueNDRangeKernel(clCommandQueue, clKernel, 2,

39

NULL, globalWorkSize, NULL, 0, NULL, NULL);

40

clFinish(clCommandQueue);

```

2. STATE OF THE ART 2.3. High Level GPGPU

```

errcode = clEnqueueReadBuffer(clCommandQueue, cl_C, CL_TRUE, 0,

42

mem_size, C, 0, NULL, NULL);

43

free (A); free (B); free (C);

44

clReleaseMemObject(cl_A); clReleaseMemObject(cl_B);

45

clReleaseMemObject(cl_C);

46

clReleaseContext (clContext);

47

clReleaseKernel(clKernel);

clReleaseProgram(clProgram);

49

clReleaseCommandQueue (clCommandQueue);

50

51

```

Listing 2.2: The kernel function

```

__kernel void matrixMul(

__global int* C,__global int* A,__global int* B, int width){

int px = get_global_id(0);//x-dimension

int py = get_global_id(1);//y-dimension

int value = 0;

for (int i = 0; i < width; i++) {

int elementA = A[py * width + i];

int elementB = B[i * width + px];

value += elementA * elementB;

}

C[py * width + px] = value;

}</pre>

```

OpenCL features two domains of synchronization, not used in the example: work-items in a single work-group, and commands enqueued to command-queue(s) in a single context. Synchronization between work-items of a single work-group is done by using a work-group barrier. Every work-item, in a work-group, must execute the barrier before any are allowed to continue subsequent computations. Still, there is no mechanism for synchronization between work-groups.

In regard to command queues there are two synchronization points: command-queue barriers, and events. The first ensures that all previously queued commands have been completed and any resulting memory updates are visible to subsequent commands. The latter, are returned by every API function that enqueues commands. A next command waiting on that event certainly views consistent memory objects.

# 2.3 High Level GPGPU

GPGPU APIs, like OpenCL and CUDA, are popular among software developers that intend to make use of the GPU's parallel computing qualities. Regardless, these APIs do not provide a good abstraction from the underlying execution model since, for instance,

they require an explicit management and interconnection of both host and device memories by the programmer, as well as other low-level responsibilities. It comes without surprise that efforts were made towards equipping software developers with higher-level GPGPU development tools, mostly driven towards an object-oriented paradigm. These tools provides an additional abstraction layer to the underline platform, letting developers focus on the data-parallel structures and operations, rather than on how to translate the computations to a lower level syntax.

Subsequently are presented the high-level GPGPU platforms and APIs most relevant to our work.

#### 2.3.1 Libraries

# RapidMind

RapidMind [McC06] was a C++ platform, inspired in SH [MQP02], for expressing data-parallel computations on GPUs. It was released in 2006, being the real first high-level GPGPU API.

It provided three main C++ types: Value< N, T>, Array< D, T> and Program. All the three types are containers: the first two for data and the last for operations. Parallel computations are invoked by applying either programs or parallel collective operations (reductions) to arrays, which generate new arrays or scalar values, respectively.

The Value< N, T > type is a N-tuple, holding N values of type T. T can be a basic numerical type (e.g., single/double-precision floating point, signed/unsigned integers).

The Array<D,T> type is a data container like Value<N,T>, although, it is multidimensional and variable in size. Thus, D is the dimensionality (can take the value of one, two or three), and the type T gives the type of the element, similarly to T of Value<N,T>.

Lastly, the Program type stores a sequence of operations on specific structures. Its declaration starts by the BEGIN macro and ends with the END macro, encapsulating variable declaration, and operations. The variables declared inside a Program are declared either as input or output parameters, using the IN < T > and OUT < T > template wrappers.

RapidMind was acquired by Intel in 2009, being used in the development of the Intel ArBB platform [NSLMGTWDCW+11]. At the time of writing of this document, Intel's ArBB did not support GPU executions, however, according to Intel, efforts were being made in that direction.

#### **Aparapi**

Aparapi [AMD11] is AMD's solution for high-level GPGPU. It was presented in June 2011, as an API for expressing data-parallel workloads in Java, that may execute either on OpenCL or on the Java Thread Pool. The developer creates an application where the data-parallel executions are implemented inside an extension of a Kernel base class. Upon the invocation of the Kernel's execute method the runtime decides on which platform should the the operations be executed.

If its the first execution of the kernel, Aparapi tries to convert the Java Bytecode of the kernel function into OpenCL. If the platform supports OpenCL, and the Bytecode is convertible, the conversion is carried out and the kernel executes on an OpenCL device. Otherwise, the kernel executes on a Java Thread Pool. This conversion is only done once, since the consequent executions will skip this process and go immediately to execution on the available back-end, either OpenCL or Java Thread Pool depending on the previous conclusions.

The Aparapi source code is part of an open source project and it is currently only capable of executing kernels on recent AMD GPUs. Therefore is is still bound to a specific set of hardware devices.

#### Accelerator and PeakStream

Accelerator [TPO06] is a C++ library with a managed API wrapper, created by Microsoft and currently in its second version, for implementing array-processing operations on multi-threaded systems, such as multi-core processors or GPUs.

It features a parallel array (PA) namespace that offers various API functions, that carry out operations (e.g., subtractions, divisions) in, and in between, arrays in parallel. These parallel executions are transparent to the programmer, and carried out on a CPU or a GPU. Nonetheless, the types of the arrays received as argument in the API functions have to be associated to the Accelerator runtime (e.g., IntParallelArray, FloatParallelArray).

To select the hardware on which the operations are executed, an appropriate target must first be created. For example, a DirectX 9 or a multi-core target. From this point on, array operations can be submitted for evaluation. These are performed in the declared order, and execute on the respective target.

In order to execute on a GPU, Accelerator automatically translates the structures and operations issued by the programmer into GPU machine code, by using the DirectX 9 API. Hence, GPUs that do not support the DirectX 9 API are unable to execute Accelerator workloads.

On the other hand, if the developer issues a multi-core target, Accelerator takes care of thread creation and synchronization. The number of threads is automatically determined, depending on the available CPUs and workload size. One limitation is that only CPUs that have an 64 bit instruction set are compatible to Accelerator.

PeakStream [Pap07] is somewhat similar to the Accelerator platform, as it also provided a C++ array-oriented data-parallelism abstraction. It uses C++ operator overloading, instead of API functions, in order to execute operations between arrays. It was bought by Google in 2007, and is currently only for internal usage.

#### **Critical Analysis**

The semantics gap between these high-level APIs and the underlying GPU programming model is considerable. Thus, they offer a decent abstraction when developing applications that are to be computed, either totally or partially, on the GPU. However, these platforms are not free of issues. In fact, they have a varied set of limitations, in regards to distinct concepts. These include, portability concerns, an over simplified execution model, and others problems.

Aparapi's approach has the advantage of providing a high degree of abstraction, although the developer is oblivious of the code's sustainability for GPU execution until it is just-in-time compiled to OpenCL, at runtime. Its programming model does not provide the same capabilities of OpenCL's, since programmers are reduced to using unidimensional arrays in kernel executions, besides normal singleton values (e.g., integers, floats). In addition, at the time of writing, it only supported GPU executions in AMD chips, analogously to CUDA. Therefore, this is a convenient tool to leverage from the existence of a GPU, when the required conditions are met, but not for actual GPGPU development.

More often than not, the scope of the application context is narrowed to a set of operations known to be supported by the target programming model. For instance, Accelerator, is a good tool for applying a sequence of element-wise arithmetic operations to a set of arrays, but is not powerful enough for general-purpose computing. On top of that, it has problems related to portability, specifically, it may only execute on GPUs that support, at minimum, DirectX 9.

# 2.3.2 Programming Language Support

#### **GPGPU Programming Languages**

**Lime** is a Java-compatible language, proposed in 2012, that exports a high-level GPU programming model. It provides a high-level object-oriented paradigm, that offers task, data, and pipeline parallelism. It extends Java with several constructs designed for programming heterogeneous architectures with GPU accelerators.

Lime represents the main computation as a task graph data structure, in which values flow between tasks over edges in the graph. To compose a task graph, the programmer uses Lime-specific operators, such as the task operator, or the => (connect) operator. The former creates a computational unit equivalent to a OpenCL kernel, while the latter represents the flow of data between tasks. Another operator is the finish, that initiates the computations and forces completion.

A Lime task repeatedly applies a *worker* method, as long as the input data is presented to the task through an input port, and enqueues its output (the result of a method application) to an output stream. These methods are task agnostic, i.e. they may be invoked as conventional static or instance methods, only becoming worker methods by applying the task operator. Moreover, tasks are either *isolated* or *non-isolated*. An isolated task (a filter)

has its own address space and may not access mutable global state. Consequently, the *worker* method of an isolated task inputs immutable (value types) arguments, and must return values.

A value type, represents a deeply immutable object (e.g., array, or a data structure) declared using the value modifier on a type. As a result, a float bi-dimensional value array (matrix) would be declared as float[ [] [N]], where N>0. This would instantiate a matrix in which the outer dimension is unbounded, and the inner dimension is bounded to size N.

The => operator is used to connect two tasks, when the output type of the upstream task matches the input type of the downstream task. This is explicitly exposed in order to enable the compiler, and runtime, to automatically optimize the I/O, as well as synchronization, between tasks.

Lime offers a *map* and *reduce* model for fine-grained data parallelism. The map operator is represented by the @ token. It applies a worker function to each element of a value type, and returns the respective output (depending on the input value type). In its turn, the reduction is expressed using an operator, or method, followed by !. This indicates to the compiler that the method should be treated as a combinator. Lime permits instance or static methods to serve as reduction operators, as long as they apply the computations to two arguments of the same type, and consequently produce a result of that type.

The Lime compiler performs several optimizations to the applications, such as in regards to kernels, or even to data memory placement. However, it does not optimize how the communication is overlapped with the computation.

**X10** [CGSDKEPSS05] is an instantiation of the APGAS [SABCCGKPT10] programming model on top of a base sequential language, with Java-style productivity. X10 was developed by IBM in the last few years. The design of the APGAS model was aimed at programming for clusters of multi-core nodes. X10's instantiation of the previous model, according to IBM, can be used to write efficient code for some heterogeneous parallel architectures (e.g., multi-cores, SMPs, Cell-accelerated nodes). To achieve GPU execution X10 has to support GPU programming idioms such as threads, blocks, barriers, constant memory, etc [CBS11]. Is accomplishes these challenges with an extension to the X10-to-C++ compiler, that recognizes such idioms and generates CUDA kernel code.

Before we can understand the mechanisms by which X10 allows the development of GPU executable code we must introduce some key concepts of the APGAS model. Firstly, APGAS is organized into four simple and independent concepts: *locality*, *asynchrony*, *conditional atomicity* and *order*.

• Places – A place is an computational entity on which executions take place (e.g., x86 core, SMP, GPU). Places can be joined together and are reified, i.e. can be stored in variables, passed into functions, etc. In this model, a unit of serial execution

(thread) can be denominated as an *activity*, and an activity is only located in a specific place for its lifetime. Given a place p the statement at(p) S can be used to request the execution of S at place p.

- Asynchrony An activity may utilize the statement async S to launch a new activity to execute S. S may reference variables in the surrounding lexical environment.

- Conditional Atomicity An activity may use the statement when (c) S, where c is a boolean valued expression. The execution of this statement in a state s terminates in a single step, and yields the state s' if and only if the condition c is true in s, and that the execution of S in s yields s'.

- **Order** The statement finish S imposes partial order on the state changes provoked by individual activities. After *S* is executed it waits for all activities spawned during the execution of *S* to terminate. Thus, ensuring that subsequent activities see the effect of the state changes that resulted from the execution of finish.

The async, finish and at statements can be nested arbitrarily, providing an increased flexibility to the APGAS model.

Using APGAS' constructs a programmer is able to create applications that use one or more GPUs as their execution platform. Though APGAS offers a higher abstraction of the GPU programming model than low-level GPGPU APIs, its execution model is not unlike CUDA's or OpenCL's. Since X10 compiles CUDA code, we will use CUDA's terminology for the rest of the description. In that sense, it is natural that APGAS' constructs are organized in such way that clearly separates memory domains. For example, global memory is represented as heap memory for a place, since it outlives the execution of a kernel. Local and private memories are finer-grain memory locations, associated to either a block, or a thread, respectively. Given that the latter two do not outlive kernel execution, in APGAS they are described as stack memory. This memory hierarchy is more easily unified with the notion that an individual GPU is a single place, rather than viewed as several interconnected places.

In X10, remote memory allocation is accomplished with the new construct, analogous to Java. However, the GPU programming model did not allow memory allocation inside a kernel until very late in the development process of X10, so this functionality was left out. Rather, the host part of the application calls API functions (in similar fashion to CUDA or OpenCL) to allocate desired memory spaces. An example of this mechanism is the following primitive: CUDAUtilities.makeRemoteArray[T] (p, sz,  $single_value$ );. This creates an array of type T in GPU at place P, with its corresponding size and values.

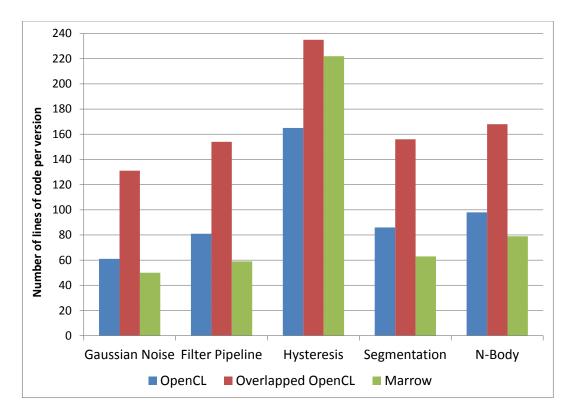

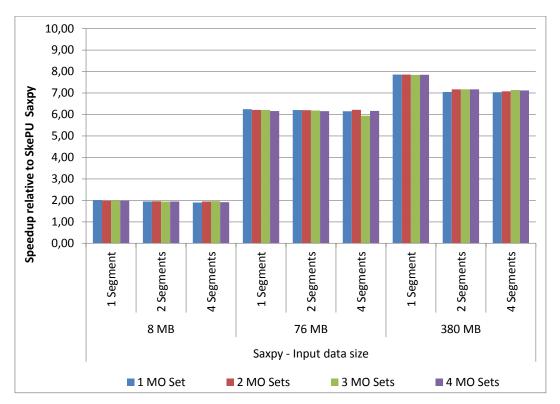

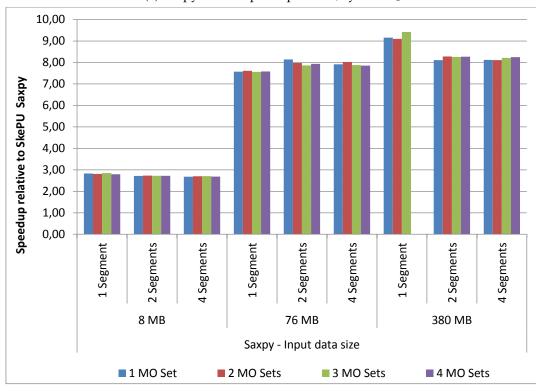

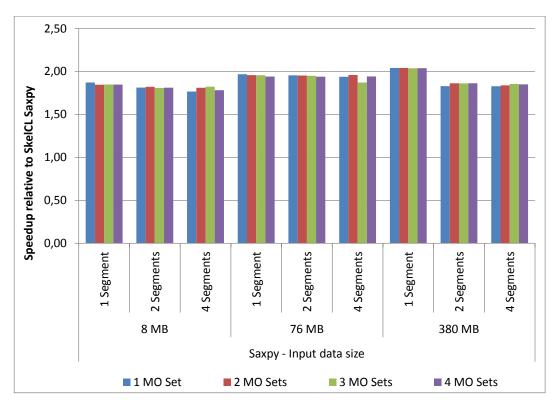

To copy data to/from the GPU X10 provides an API that mirrors Java's System.arrayCopy, although being asynchronous, and allowing one of the arrays to be a remote reference. The following example depicts the copying of data between arrays r and l, remote and local respectively: finish Array.asyncCopy(r, r\_off, l, l\_off, len);