# Constraint Solving over Multi-valued Logics - Application to Digital Circuits -

Dissertação apresentada para obtenção do Grau de Doutor em Informática na especialidade de Informática pela Universidade Nova de Lisboa, Faculdade de Ciências e Tecnologia.

## **ACKNOWLEDGMENTS**

First of all, I would like to thank my family, my parents and my sister for all the help, support and, specially, love they provided me during my whole life and through the hard but stimulating times of my Ph.D. studies with all their ups and downs. To them, I owe my education and my longing for Truth, wisdom, knowledge and intelligence (even if artificial). I also remember my late grandparents with all their care.

As to this research work, I had the honour of having Pedro Barahona as my supervisor and friend. I cannot thank him enough for all the patience in reading, understanding and proposing improvements to my writings, amidst all his works. He introduced and pushed me to this field where he has taught me so much.

Thank you to Paulo Flores and his supervisor João Paulo Marques Silva of the INESC team, for getting me acquainted with the problems of the ECAD area, and for sending me precious data and tools even in troubled times.

I also would like to thank the IC-Parc team, especially Mark Wallace, Carmen Gervet, and Joachim Schimpf, for the warm welcome, hospitality, friendship, and fruitful discussions during my stay there, which reflected in this dissertation.

My acknowledgements to the Department of Computer Science and CENTRIA for providing all needed equipment and working conditions, to my colleagues such as Carlos Damásio, João Leite, António Ribeiro, Rui Marques or Jorge Cruz for the help and for being there, and to the secretary staff for the support and general help.

Naturally, I thank the financial support of "Sub-Programa Ciência e Tecnologia do 2º Quadro Comunitário de Apoio" that always arrived on time.

And, of course, thanks be to God, for without Him no thanks would be possible!

# Universidade Nova de Lisboa Faculdade de Ciências e Tecnologia

# **Abstract**

# CONSTRAINT SOLVING OVER MULTI-VALUED LOGICS — APPLICATION TO DIGITAL CIRCUITS

by Francisco de Moura e Castro Ascensão de Azevedo

Supervisor: Professor Pedro M. C. C. Barahona Departamento de Informática

Due to usage conditions, hazardous environments or intentional causes, physical and virtual systems are subject to faults in their components, which may affect their overall behaviour. In a 'black-box' agent modelled by a set of propositional logic rules, in which just a subset of components is externally visible, such faults may only be recognised by examining some output function of the agent. A (fault-free) model of the agent's system provides the expected output given some input. If the real output differs from that predicted output, then the system is faulty. However, some faults may only become apparent in the system output when appropriate inputs are given. A number of problems regarding both testing and diagnosis thus arise, such as testing a fault, testing the whole system, finding possible faults and differentiating them to locate the correct one. The corresponding optimisation problems of finding solutions that require minimum resources are also very relevant in industry, as is minimal diagnosis.

In this dissertation we use a well established set of benchmark circuits to address such diagnostic related problems and propose and develop models with different logics that we formalise and generalise as much as possible. We also prove that all techniques generalise to agents and to multiple faults. The developed multi-valued logics extend the usual Boolean logic (suitable for fault-free models) by encoding values with some dependency (usually on faults). Such logics thus allow modelling an arbitrary number of diagnostic theories. Each problem is subsequently solved with CLP solvers that we implement and discuss, together with a new efficient search technique that we present. We compare our results with other approaches such as SAT (that require substantial duplication of circuits), showing the effectiveness of constraints over multi-valued logics, and also the adequacy of a general set constraint solver (with special inferences over set functions such as cardinality) on other problems. In addition, for an optimisation problem, we integrate local search with a constructive approach (branch-and-bound) using a variety of logics to improve an existing efficient tool based on SAT and ILP.

# Universidade Nova de Lisboa Faculdade de Ciências e Tecnologia

# Sumário

# RESOLUÇÃO DE RESTRIÇÕES SOBRE LÓGICAS MULTI-VALOR – APLICAÇÃO EM CIRCUITOS DIGITAIS

por Francisco de Moura e Castro Ascensão de Azevedo

Orientador: Professor Doutor Pedro M. C. C. Barahona Departamento de Informática

Os sistemas físicos como os circuitos digitais estão sujeitos a falhas nos seus componentes devido a erros de fabrico, uso intenso ou ambientes hostis, entre outras causas. Tais falhas podem afectar o comportamento global do sistema mas apenas serem discerníveis em certas condições, uma vez que comummente este se apresenta como uma 'caixa negra' onde apenas um sub-conjunto de componentes é observável. Nesses casos, o efeito da falha torna-se vísivel por uma função de saída do sistema quando sujeito a uma certa entrada. Se a saída prevista pelo modelo do sistema sem falhas difere da real, então o sistema está defeituoso. O facto de nem todas as entradas possíveis garantirem a verificação de uma falha coloca vários problemas de teste e diagnóstico destes sistemas que, em geral, são agentes (eventualmente virtuais) modelados por um conjunto de regras em lógica proposicional. Esses problemas incluem o teste de uma falha e de todo o sistema, procura de falhas possíveis, distingui-las e localizar a correcta. Os problemas de optimização correspondentes (encontrar soluções requerendo recursos mínimos) são também extremamente relevantes na indústria, como é o problema do diagnóstico mínimo.

Nesta dissertação, utilizamos um conhecido conjunto de circuitos de teste para abordar estes problemas, desenvolvendo modelos com lógicas multi-valor que estendem a tradicional lógica boleana (suficiente para modelar teorias normais, sem falhas) ao introduzir valores extra que denotam alguma dependência (normalmente, de falhas). Assim, um número arbitrário de teorias de diagnóstico pode ser codificado para modelar os diversos problemas que são então solucionados por resolvedores de restrições que também desenvolvemos. Também provamos que as técnicas desenvolvidas se generalizam a agentes e a falhas múltiplas e, adicionalmente, apresentamos uma nova e eficiente técnica de pesquisa. Comparamos os resultados com outras abordagens como SAT, mostrando a aplicabilidade de resolução de restrições sobre as lógicas multi-valor. Nomeadamente, desenvolvemos um eficiente resolvedor de restrições sobre conjuntos, onde funções como a cardinalidade são particularmente exploradas, e para o qual mostramos a aplicabilidade e declaratividade para modelação e resolução destes e de outros problemas. Adicionalmente, para um problema de optimização, usámos várias lógicas multi-valor e integrámos uma *pesquisa local* num método construtivo de procura do óptimo, melhorando uma ferramenta baseada em SAT e ILP.

# GLOSSARY OF ACRONYMS

AC Arc ConsistencyAI Artificial Intelligence

ATG Automatic Test Generation

ATMS Assumption-Based TMS

BAC Bounded Arc Consistency

BB Branch and Bound BIST Built-In Self-Test Bit Binary Digit

CLP Constraint Logic ProgrammingCNF Conjunctive Normal FormCSP Constraint Satisfaction Problem

CP Constraint ProgrammingCPU Central Processing UnitCUT Circuit Under Test

DAC Directional Arc ConsistencyDTG Differential Test Generation

**ECAD** Electronic Computer-Aided Design

FC Forward Checking

FD Finite Domain

FF First-Fail

GHz Giga Hertz

HCLP Hierarchical CLP

I/O Input/Output

**ILP** Integer Linear Programming

**ISCAS** International Symposium on Circuits and Applied Systems

ITBS Iterative Time-Bounded Search

**LP** Logic Programming

**LS** Local Search

**MAC** Maintaining Arc Consistency

Mb Mega bytesMHz Mega Hertz

MSF Multiple Stuck Fault

MTP Minimum Test Pattern

PC Path Consistency

PI Primary Input

PO Primary Output

**RAM** Random Access Memory

**RISC** Reduced Instruction-Set Computer

**s-a-0** Stuck at 0 **s-a-1** Stuck at 1

**SAT** Propositional Satisfiability

SSF Single Stuck FaultTG Test Generation

TMS Truth Maintenance SystemVLSI Very Large Scale Integration

**XOR** Exclusive OR

# TABLE OF CONTENTS

| CHAPTER 1 INTRODUCTION                                     | 1  |

|------------------------------------------------------------|----|

| 1.1 Scope                                                  | 3  |

| 1.2 Truth Maintenance Systems                              | 3  |

| 1.3 Constraint Reasoning                                   | 4  |

| 1.3.1 Consistency Techniques                               |    |

| 1.3.2 Maintaining Consistency                              |    |

| 1.3.3 Advanced Techniques                                  | 7  |

| 1.4 Contributions and Limitations                          | 9  |

| 1.4.1 Limitations                                          |    |

| 1.5 Overview                                               | 11 |

| CHAPTER 2 CIRCUIT MODELLING                                | 13 |

| 2.1 Introduction                                           | 13 |

| 2.2 Logic Simulation                                       | 14 |

| 2.3 Fault Modelling                                        | 17 |

| 2.4 Benchmarks                                             | 18 |

| 2.5 Our Modelling Approach                                 | 21 |

| 2.6 Summary                                                | 26 |

| CHAPTER 3 TEST PATTERNS                                    | 27 |

| 3.1 What are Test Patterns?                                | 27 |

| 3.2 Test Generation                                        | 28 |

| 3.3 TG Modelling Approaches and Algorithms                 |    |

| 3.3.1 Algebraic Models / Algorithms                        |    |

| 3.3.2 Topological Methods                                  |    |

| 3.3.3 Multi-valued Logics  3.3.4 TG Specialised Algorithms |    |

| 3.4 Constraint Reasoning                                   |    |

| 3.4.1 CLP(B)                                               |    |

| 3.4.2 CLP(FD)                                              |    |

| 3.5 Heuristics                                             | 45 |

| 3.5.1 Discussion and Potential Improvements                | 47 |

| 3.6 Iterative Time-Bounded Search                          | 48 |

| 3.6.1 Conclusion                                           |    |

| 3.7 Summary                                                | 51 |

| C H A P T E R 4 DIFFERENTIAL DIAGNOSIS                              | 53 |

|---------------------------------------------------------------------|----|

| 4.1 Introduction                                                    | 53 |

| 4.2 Diagnosis Approaches                                            | 54 |

| 4.3 Differential Diagnosis and Test Patterns                        | 56 |

| 4.4 The 8-valued Logic                                              | 57 |

| 4.4.1 Boolean operations                                            | 59 |

| 4.4.2 Modelling Alternative Diagnostic Theories in Digital Circuits | 60 |

| 4.5 A 4-valued logic for Differentiation                            | 62 |

| 4.6 A Constraint Solver for the 8-Valued Logic                      | 63 |

| 4.6.1 Domain Representation                                         | 64 |

| 4.6.2 Not-Gates                                                     | 65 |

| 4.6.3 Xor-Gates                                                     | 66 |

| 4.6.4 Normal And-Gates                                              | 67 |

| 4.6.5 S-Buffers                                                     |    |

| 4.6.6 Heuristics to Find Differential Patterns                      | 71 |

| 4.7 Benchmarks                                                      | 72 |

| 4.7.1 Generating a Benchmark                                        | 72 |

| 4.7.2 Set of Benchmarks Used                                        | 73 |

| 4.8 Differentiating Multiple Diagnoses                              | 73 |

| 4.9 Experimental Results                                            | 76 |

| 4.9.1 Choosing the Heuristic                                        | 76 |

| 4.9.2 Discussion                                                    | 77 |

| 4.9.3 Complete Results                                              | 78 |

| 4.9.4 Comparison of Results and Approaches                          | 80 |

| 4.10 Conclusions                                                    | 83 |

| C H A P T E R 5 PROBLEMS WITH MULTIPLE DIAGNOSES                    | 85 |

| 5.1 Satisfaction Problems                                           | 86 |

| 5.1.1 Fault Simulation                                              |    |

| 5.1.2 Test Generation                                               | 86 |

| 5.1.3 Fault Covering                                                |    |

| 5.1.4 Covered Diagnoses                                             |    |

| 5.1.5 Diagnosis                                                     | 87 |

| 5.1.6 Fault Location                                                | 87 |

| 5.2 Optimisation Problems                                           | 88 |

| 5.2.1 Minimal Set of Test Patterns                                  | 88 |

| 5.2.2 Maximal Test Patterns                                         |    |

| 5.2.3 Minimal Diagnosis                                             | 89 |

| 5.2.4 Maximal Fault Resolution                                      | 89 |

| 5.3 Logic over Booleans and Sets                                    | 89 |

| 5.3.1 Signal Representation                                         | 90 |

| 5.3.2 Normal Gates                                    | 90  |

|-------------------------------------------------------|-----|

| 5.3.3 S-Buffers                                       |     |

| 5.4 Modelling and Solving                             | 92  |

| 5.4.1 Diagnosis                                       |     |

| 5.4.2 Differentiation                                 |     |

| 5.4.3 Optimisation Problems                           |     |

| 5.5 Reduction to Set Algebra                          | 90  |

| 5.5.1 Motivation                                      |     |

| 5.5.2 Transformation                                  |     |

| 5.5.3 Modelling                                       |     |

| 5.6 Summary                                           | 100 |

| C H A P T E R 6 A NEW SET CONSTRAINT SOLVER: CARDINAL | 101 |

| 6.1 Set Constraint Solving and Cardinality Inferences | 101 |

| 6.2 Intervals and Lattices                            | 103 |

| 6.3 Operational Semantics                             | 105 |

| 6.3.1 Set Variable                                    | 106 |

| 6.3.2 Membership Constraints                          | 107 |

| 6.3.3 Set Complement                                  | 107 |

| 6.3.4 Set Equality                                    | 108 |

| 6.3.5 Set Inequality                                  | 108 |

| 6.3.6 Disjointness                                    | 109 |

| 6.3.7 Set Inclusion                                   | 109 |

| 6.3.8 Set Intersection                                |     |

| 6.3.9 Set Union                                       | 114 |

| 6.3.10 Set Difference                                 | 116 |

| 6.4 Implementation                                    | 119 |

| 6.4.1 Set Labelling                                   | 119 |

| 6.5 Results                                           | 120 |

| 6.6 Other Applications                                | 121 |

| 6.6.1 Steiner Triples                                 | 121 |

| 6.6.2 Golfers                                         | 122 |

| 6.6.3 Warehouse                                       | 123 |

| 6.6.4 Differential Diagnosis                          | 124 |

| 6.7 Cardinal Extensions                               | 120 |

| 6.7.1 Sets Union                                      | 127 |

| 6.7.2 Generalisation to Sets Functions                | 127 |

| 6.7.3 Set Covering                                    | 127 |

| 6.7.4 Results                                         |     |

| 6.7.5 Future Research                                 | 130 |

| 6.8 Conclusions                                       | 131 |

| CHAPTER 7 TEST PATTERN OPTIMISATION                   | 133 |

| 7.1 Description                                           | 133 |

|-----------------------------------------------------------|-----|

| 7.2 SAT Approach                                          | 134 |

| 7.3 5-valued Logic                                        | 135 |

| 7.4 Completeness                                          | 137 |

| 7.5 Naming Unspecified Values for an Extended Logic       | 138 |

| 7.5.1 Fault Detection Conditions                          | 141 |

| 7.6 Local Search                                          | 143 |

| 7.6.1 A Multiple Extended Logic for Local Search          |     |

| 7.6.2 Operational Semantics                               | 145 |

| 7.6.3 Improving Local Search                              | 148 |

| 7.6.4 Multiple unspecification                            | 149 |

| 7.7 Solution Spaces                                       | 151 |

| 7.8 Combining Logics                                      | 153 |

| 7.9 Results                                               | 156 |

| 7.10 Conclusions                                          | 163 |

| C H A P T E R 8 GENERALISATION, DISCUSSION AND CONCLUSION | 165 |

| 8.1 Agents                                                | 165 |

| 8.2 Conclusion and Research Directions                    | 168 |

| REFERENCES                                                | 171 |

| Appendix A: ISCAS Circuits                                | 183 |

| Annendix R. Logics                                        | 213 |

# LIST OF FIGURES

| Number                                                                                                                       | Page |

|------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.1. Fanout node                                                                                                      | 14   |

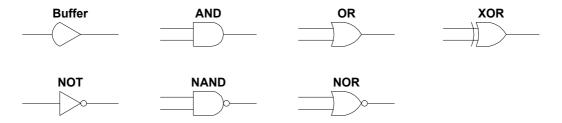

| Figure 2.2. Basic gates                                                                                                      | 15   |

| Figure 2.3. Boolean logic truth tables                                                                                       | 15   |

| Figure 2.4. And-gate truth table                                                                                             | 15   |

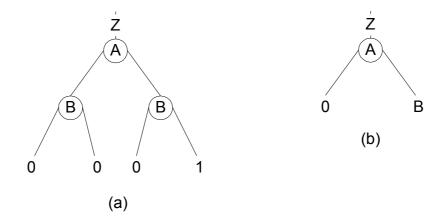

| Figure 2.5. Binary decision diagrams for the and-gate                                                                        | 16   |

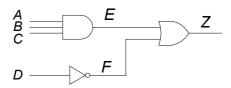

| Figure 2.6. Example circuit to model as code                                                                                 |      |

| Figure 2.7. Boolean logic extended with unspecified values                                                                   |      |

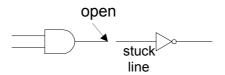

| Figure 2.8. Stuck fault caused by an open                                                                                    | 18   |

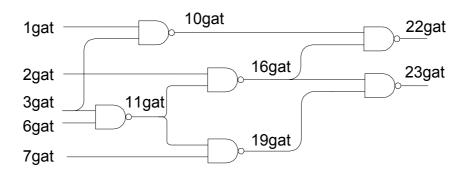

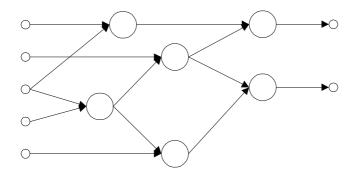

| Figure 2.9. c17 ISCAS'85 example circuit                                                                                     | 19   |

| Figure 2.10. Graph representation of c17                                                                                     | 20   |

| Figure 2.11. C17 circuit with added buffers                                                                                  |      |

| Figure 2.12. circuit/4 predicate for c17                                                                                     | 22   |

| Figure 2.13. Gate predicate for Boolean simulation                                                                           | 23   |

| Figure 2.14. Gate in a multi-valued logic                                                                                    | 23   |

| Figure 2.15. Possible faulty gate                                                                                            | 23   |

| Figure 2.16. Gate as a constraint                                                                                            | 24   |

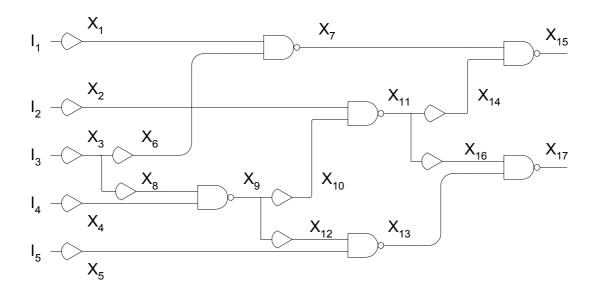

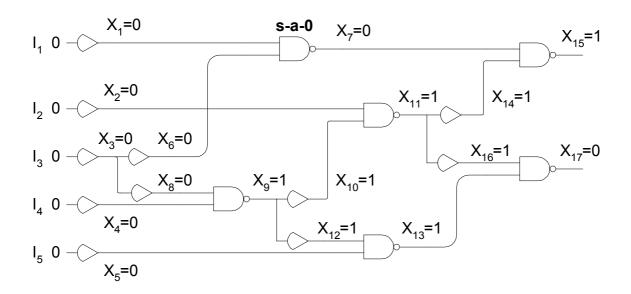

| Figure 2.17. C17 circuit with a stuck gate                                                                                   | 24   |

| Figure 2.18. Introduction of an S-buffer B s-a-0                                                                             | 26   |

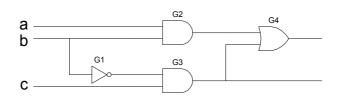

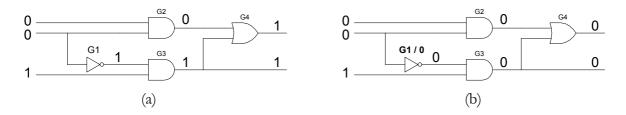

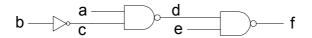

| Figure 3.1. Example CUT                                                                                                      | 27   |

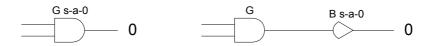

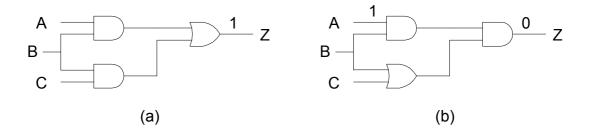

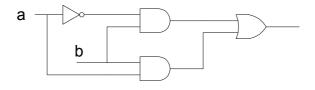

| Figure 3.2. Expected circuit behaviour (a); and circuit response with G1 s-a-0 (b)                                           | 28   |

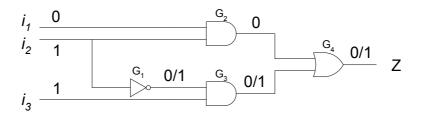

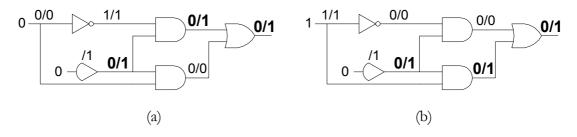

| Figure 3.3. Test for SSF $G_1$ s-a-1                                                                                         | 29   |

| Figure 3.4. Justifying values for line k                                                                                     | 31   |

| Figure 3.5. 4-valued logic                                                                                                   | 31   |

| Figure 3.6. 5-valued logic                                                                                                   | 31   |

| Figure 3.7. Some backward and forward implications using 5-valued logic                                                      | 32   |

| Figure 3.8. Target fault: $G_I$ s-a-1                                                                                        | 32   |

| Figure 3.9. Multiple-path sensitisation                                                                                      | 33   |

| Figure 3.10. Impossible single-path sensitisation                                                                            | 33   |

| Figure 3.11. Objective: $f = 1$                                                                                              | 35   |

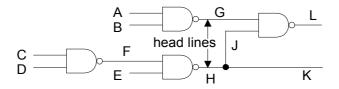

| Figure 3.12. Head lines                                                                                                      |      |

| Figure 3.13. Global implications: the value of Z determines the value of B                                                   |      |

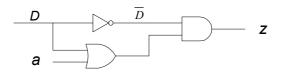

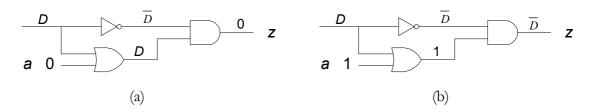

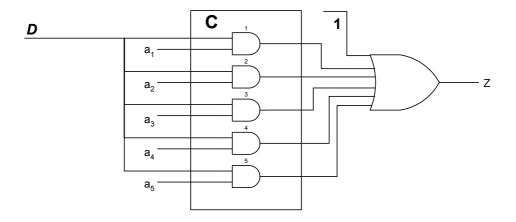

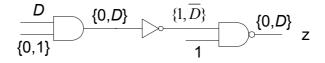

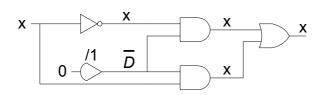

| Figure 3.14. How to assign a to have a d-signal at z?                                                                        | 39   |

| Figure 3.15. To have a d-signal at z, D must be masked at the or-gate by $a=1$                                               | 39   |

| Figure 3.16. Drawback of creating choice points                                                                              | 40   |

| Figure 3.17. Global implication: D must pass through z                                                                       |      |

| Figure 3.18. Impossible error propagation                                                                                    | 45   |

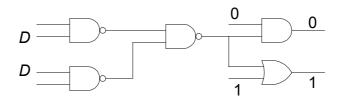

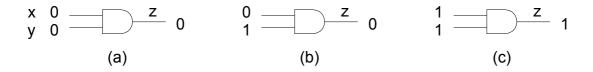

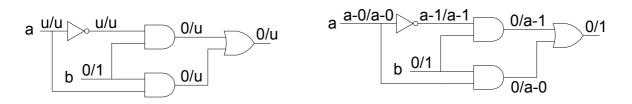

| Figure 3.19. Inverter constraint propagations                                                                                |      |

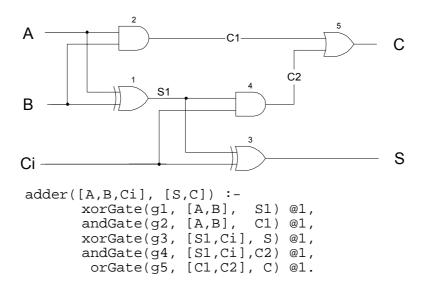

| Figure 4.1. Full adder circuit and its specification                                                                         | 55   |

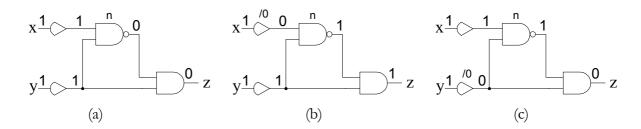

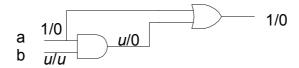

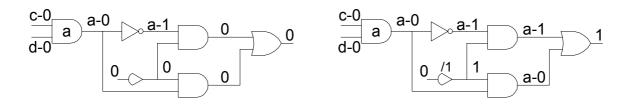

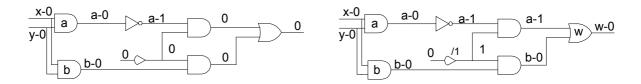

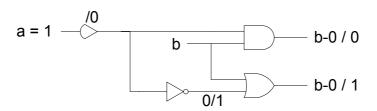

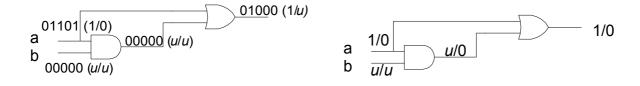

| <b>Figure 4.2.</b> Differential test for $x/0$ and $y/0$ ; a) normal circuit $N$ ; b) $F_1$ with $x/0$ ; c) $F_2$ with $y/0$ | 59   |

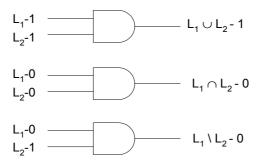

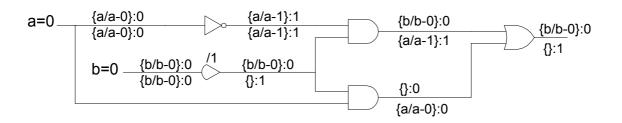

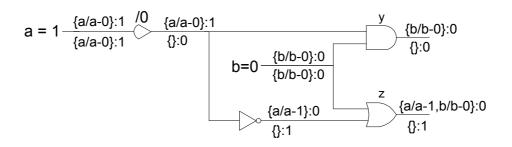

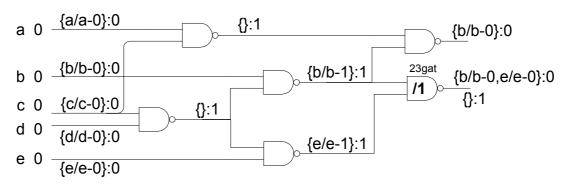

| Figure 4.3. Circuit with 8-valued logic for x/0 or y/0                                                                       | 59   |

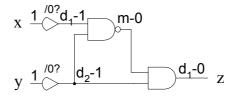

| Figure 4.4. Logic operations over a 4-valued logic for diagnosis                                                             | 62   |

| Figure 4.5. Algorithm to partition a set into classes of indistinguishable diagnoses                                         | 74   |

| Figure 4.6. Algorithm to obtain a set of indistinguishable diagnoses                                                         | 75   |

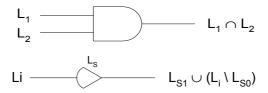

| Figure 5.1. And-gate                                                                               | 9  |

|----------------------------------------------------------------------------------------------------|----|

| Figure 5.2. S-buffer                                                                               | 9  |

| Figure 5.3. Improved algorithm to obtain a set of indistinguishable diagnoses                      | 9  |

| Figure 5.4. Improved algorithm to partition a set into classes of indistinguishable diagnoses      | 9  |

| Figure 5.5. And-gate and S-buffer over sets                                                        | 9  |

| Figure 5.6. Other gates over sets                                                                  | 9  |

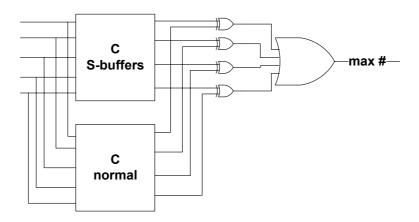

| Figure 5.7. Modelling the maximisation problem with sets                                           | 9  |

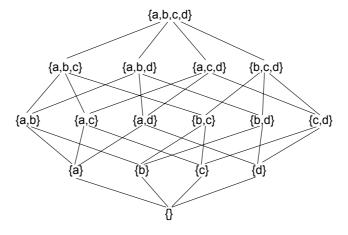

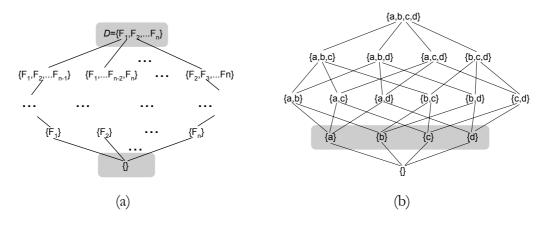

| Figure 6.1. Powerset lattice for $\mathcal{U} = \{a,b,c,d\}$ , with set inclusion as partial order | 10 |

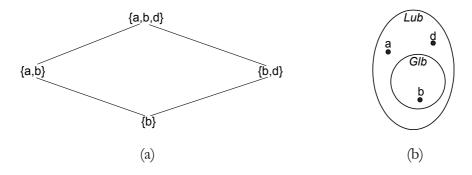

| Figure 6.2. Set interval [{b},{a,b,d}]: a) Sub-lattice; b) Venn diagram                            | 10 |

| Figure 6.3. Powerset lattices with cardinalities: a) circuit PI; b) singleton                      | 10 |

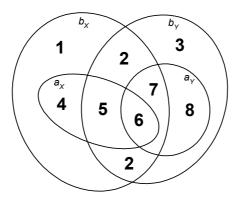

| Figure 6.4. Two sets, X, Y, define 8 different zones                                               | 11 |

| Figure 6.5. Minimum intersection cardinality                                                       | 11 |

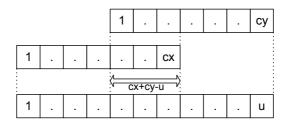

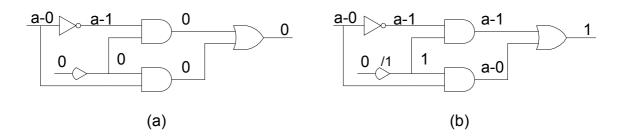

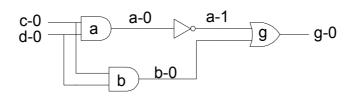

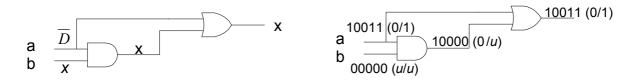

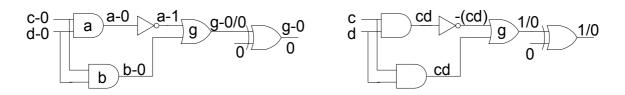

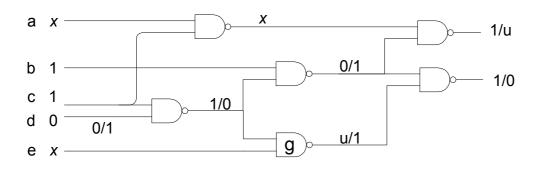

| Figure 7.1. Counter-example to a SAT model assumption                                              | 13 |

| Figure 7.2. Test x0 detects b s-a-1                                                                | 13 |

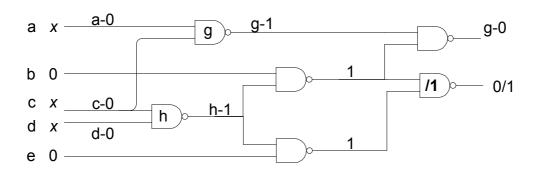

| Figure 7.3. Different sensitised paths for different assignments of PI: a) $a=0$ ; and b) $a=1$    | 13 |

| Figure 7.4. 5-valued logic cannot detect test x0                                                   | 13 |

| Figure 7.5. 9-valued logic cannot detect test x0                                                   | 13 |

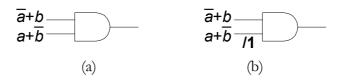

| Figure 7.6. Extended logic considering the inversion parity of an unspecified value                | 13 |

| Figure 7.7. Normal and faulty circuits with extended logic                                         | 13 |

| Figure 7.8. Anding unspecified values of different sources                                         | 14 |

| Figure 7.9. Normal and faulty extended circuits                                                    | 14 |

| Figure 7.10. Limitation of the extended logic: faulty circuit output should have value 1           | 14 |

| Figure 7.11. Limitation of the extended logic: final output should have value 1                    | 14 |

| Figure 7.12. Possible Boolean reasoning for unspecified values                                     | 14 |

| Figure 7.13. Output is sensitised regardless of b                                                  | 14 |

| Figure 7.14. Different values of b sensitise different POs                                         | 14 |

| Figure 7.15. Dependencies on a) 0, b) 1 and c) 2 specified values                                  | 14 |

| Figure 7.16. Sets of dependencies                                                                  | 14 |

| Figure 7.17. And-operation procedure for local search                                              | 14 |

| Figure 7.18. Local search logic: PI a may be made unspecified                                      | 14 |

| Figure 7.19. PI b can be made unspecified since either y or z will be sensitised                   | 14 |

| Figure 7.20. PIs b and e cannot be made unspecified in test t=00000                                | 14 |

| Figure 7.21. Verification of improved test $t'=x0xx0$                                              |    |

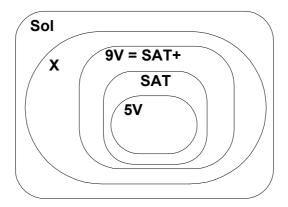

| Figure 7.22. Relative solution spaces                                                              |    |

| Figure 7.23. Test t=0x belongs to Sol(SAT)\Sol(5V)                                                 | 15 |

| Figure 7.24. Test $t=1x$ belongs to $Sol(9V)\backslash Sol(SAT)$                                   |    |

| Figure 7.25. Test $t=x0$ belongs to $Sol(X)\backslash Sol(9V)$                                     |    |

| Figure 7.26. Valid test t=xx0 does not belong to Sol(X)                                            |    |

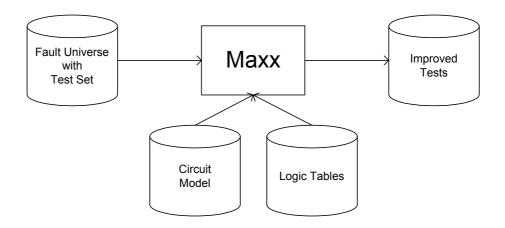

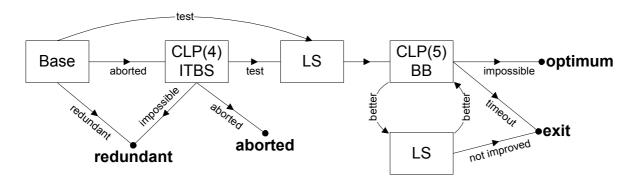

| Figure 7.27. Maxx system                                                                           |    |

| Figure 7.28. Maxx flowchart                                                                        |    |

| Figure 7.29. Maxx optimal test not recognised by MTP                                               |    |

| Figure 8.1. (a) Equivalence function: (b) altered (implication) function by an SSF                 |    |

# LIST OF TABLES

| Number                                                                                               | Page |

|------------------------------------------------------------------------------------------------------|------|

| Table 2.1. And-gate s-a-0 truth table                                                                | 18   |

| Table 2.2. Lines' statistics of ISCAS benchmarks                                                     | 20   |

| Table 2.3. Gates' statistics of ISCAS benchmarks                                                     | 21   |

| Table 2.4. ISCAS circuits: Fault sets                                                                | 21   |

| Table 2.5. Translation of c17 fault set into stuck gates                                             |      |

| Table 2.6.   C17 graph information                                                                   |      |

| Table 3.1. Tests for possible stuck gates                                                            |      |

| Table 3.2. Partially specified composite values                                                      | 34   |

| Table 3.3. NOT-operation in 9-valued logic                                                           |      |

| Table 3.4. Results of Simonis' ATG system                                                            |      |

| Table 3.5. S-buffers logic table                                                                     | 42   |

| Table 3.6. Implicit 16-valued logic conjunction                                                      | 43   |

| Table 3.7. Some constraint propagation examples in 4-valued logic                                    | 43   |

| Table 3.8. ATG results with cardinality constraint                                                   | 46   |

| Table 3.9. ATG results with ITBS over sensitised POs                                                 | 50   |

| Table 3.10. ATG results with ITBS over specified sensitised POs                                      | 51   |

| Table 4.1. Truth-value of a signal with a normal model and two different diagnoses                   | 59   |

| Table 4.2. XOR truth table in 8-valued logic                                                         | 60   |

| <b>Table 4.3.</b> Physical output of an xor-gate with inputs $m-1$ and $d_1-0$                       | 60   |

| Table 4.4. Truth table for the 8 different types of S-buffer                                         | 61   |

| <b>Table 4.5.</b> Output of an S-buffer (stuck-at-0 in $F_1$ and stuck-at-1 in $F_2$ ) for input m-0 | 61   |

| Table 4.6. Condensation of 8-valued logic into a 4-valued logic for differentiation                  | 62   |

| Table 4.7. XOR for encoded domain {-41, 14}                                                          | 64   |

| Table 4.8. Output of xor-gate implies relation between arguments                                     | 65   |

| Table 4.9. Adopted 8-valued domain encoding                                                          | 65   |

| Table 4.10.   8-valued logic table for NOT                                                           | 66   |

| Table 4.11. 8-valued logic encoded table for NOT                                                     | 66   |

| Table 4.12. XOR possible input pairs for each output                                                 | 66   |

| Table 4.13. XOR possible encoded input pairs for each output                                         | 66   |

| Table 4.14. Relation between output of an xor-gate and its arguments                                 | 67   |

| Table 4.15. AND (8-valued) logic table                                                               | 67   |

| <b>Table 4.16.</b> Constraints when input $X$ of $A = X \wedge Y$ is known                           | 68   |

| Table 4.17. 'And' encoded logic table and constraints                                                | 68   |

| Table 4.18. Constraints to post when output of and-gate becomes instantiated                         | 69   |

| Table 4.19. Truth table and constraints for the 8 different types of S-buffer                        | 70   |

| Table 4.20. Random inputs generated for circuit c432, and corresponding outputs                      | 72   |

| Table 4.21. Benchmarks attempts for c432                                                             | 73   |

| Table 4.22. Differentiation results with the different heuristics                                    |      |

| Table 4.23. Complete results for differentiation benchmarks                                          | 79   |

| Table 4.24. DIATEST results                                                                          |      |

| Table 4.25. Comparison of DTG results                                                                | 82   |

| Table 5.1. S-buffer output                                                                           | 91   |

| Table 5.2. Total times for 3.2 incorrect outputs                                                     | 93   |

| Table 5.3. Application of transf function to the inputs and output of an and-gate | 98  |

|-----------------------------------------------------------------------------------|-----|

| Table 5.4. Application of transf function to the input and output of an S-buffer  | 98  |

| Table 6.1. Set intersection: cause-effect rules on set bounds                     | 113 |

| Table 6.2. Set union: cause-effect rules on set bounds                            | 116 |

| Table 6.3. Set difference: cause-effect rules on set bounds                       | 118 |

| Table 6.4. Experimental Results                                                   | 120 |

| Table 6.5. Steiner triples results                                                |     |

| Table 6.6. Delivery costs of warehouse problem                                    | 123 |

| Table 6.7. Differentiation results over different set libraries                   |     |

| Table 6.8. Differentiation results with different solvers                         | 126 |

| Table 6.9. Optimum bounds                                                         | 129 |

| Table 6.10. Obtained ranges with or without union function                        | 129 |

| Table 7.1. Double Boolean variables                                               | 134 |

| Table 7.2. Comparison with 9-valued logic                                         |     |

| Table 7.3. S-buffers logic table                                                  |     |

| Table 7.4. Comparison with SAT encoding                                           |     |

| Table 7.5. Conjunction of named unspecified values                                | 140 |

| Table 7.6. Not-operation for local search                                         | 146 |

| Table 7.7. $Z = X$ and $Y$ in local search                                        | 147 |

| Table 7.8. ISCAS circuits: PIs, Gates and Faults                                  | 156 |

| Table 7.9. Maxx results from scratch (empty base test set)                        | 157 |

| Table 7.10. Atalanta results                                                      | 158 |

| Table 7.11. Maxx results with Atalanta as base                                    |     |

| Table 7.12. MTP <sub>100</sub> results over Atalanta                              | 159 |

| Table 7.13.   MTP and Maxx improvements on Atalanta                               |     |

| Table 7.14. Maxx results with MTP as base                                         | 161 |

| Table 7.15.   MTP <sub>1000</sub> results over Atalanta                           |     |

| Table 7.16.   MTP and Maxx improvements on MTP <sub>100</sub>                     | 162 |

| Table 7.17. Breakdown of Maxx improvements                                        | 162 |

| Table 8.1. Altered agent function                                                 | 166 |

#### INTRODUCTION

Due to manufacturing errors, long-usage, hazardous environment, or some other cause, physical systems are subject to *faults* in their components, which may affect the overall system behaviour. In a system modelled by a set of *propositional rules*, but with just a subset of components externally visible (thus behaving like a 'black-box'), such faults may only be recognised by examining some *output function* of the system. By knowing the *input* given to the system, its initial (fault-free) *model* provides the expected output. If the real output differs from that predicted output, then the system is faulty. However, some faults may only become apparent in the system output under certain conditions, i.e. when appropriate inputs are given. This fact poses a number of problems regarding both the **testing** and **diagnosis** of systems. For example (to name just a few):

- How to test a system? What is the smallest amount of effort required for that?

- How to test a fault? What are the minimum resources required?

- What are the possible faults?

- How to differentiate between possible faults and locate the correct one?

Agents in general are the systems of interest to this dissertation. In particular, logical-based agents are indeed modelled by a set of propositional rules in a 'black-box' with some controllable inputs and some visible outputs, all Boolean. An output bit may unveil a fault if, when given some input to the agent, its value is dependent on the presence (or absence) of the fault. Such fault is not restricted to be a physical fault since it can also be applied to virtual agents (e.g. on the internet). Virtual agents may also have a known (or expected) model and behave as faulty due to some (possibly intentional) change of belief or some relaxed rule, for instance. This is particularly relevant in the emerging field of electronic transactions in a society of agents, where rules for bids in an auction depend on knowledge acquired on competitors and their actions. It is thus very important to predict the behaviour of the agent with whom some contract is being negotiated, after some unexpected output is detected. Hence, it is crucial to test the agent, formulate hypotheses for its unexpected behaviour, refine them in order to obtain a minimal set of hypotheses (possibly by performing additional tests), and model them. Having modelled the competitors, an optimal 'bid' (the one that is expected to generate the best 'price') can be found.

A number of problems concerning agents have been deserving especial attention by the scientific community. In particular, digital circuits in the Electronics Computer Aided Design (ECAD) area have traditionally established several problems, for which widely used benchmarks are available. The use of digital circuits has known a great expansion for many years and they are now present virtually everywhere. Reflecting the economic importance of this area, such problems have been widely

studied and they are still the subject of active research, with a variety of approaches. The evolution of the area, with new technologies and continuous new requirements and needs, makes it a suitable application field for Constraint Logic Programming (CLP) [Jaffar and Lassez 1987, Jaffar and Maher 1994], which combines the declarativity of logic programming with the power and efficiency of constraint reasoning (see section 1.3). Such suitability was already exemplified and discussed in this area [Simonis 1992] and we reckon that the expressive power and flexibility of the constraint programming approach makes it very attractive to tackle additional problems over circuits in particular, and agents in general.

The traditional Boolean domain and corresponding logic is sufficient to model a normal digital circuit, by representing each gate as a Boolean operation. However, since physical circuits may be faulty, such model needs to be extended somehow in order to model circuits that may exhibit a different behaviour than that predicted by a model of the normal circuit. While this may be simple when all gates are accessible, it is not so when the circuit is, in practice, a 'black-box' in which only a set of inputs and a set of outputs are visible. Since it is not known *a priori* whether a gate is normal or faulty, such fact may be modelled as a disjunction to represent the alternative choices. Such simple modelling has however the drawback of possibly leading to excessive backtracking in problem solving.

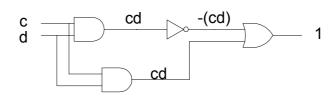

The use of extra symbolic values in conjunction with the usual Boolean  $\{0,1\}$  was proposed in a D-calculus [Roth 1966] to reflect the dependency of values in physical lines on some faulty gate. When the gate is stuck at some Boolean value v (i.e. its output is always v, regardless of the inputs), the physical value of its output depends in general on whether it is really faulty or not. Moreover, gates that take that value as input can also be affected, and hence propagate the fault effect. Two extra values are then used in the model of the circuit to denote that the normal (expected) value 0 or 1 in some line is inverted if the fault is present. Hence, multi-valued logics are introduced to model circuits in which signal values may depend on faults affecting the circuit. In this case, a 4-valued logic is defined to model dependencies on a single fault. Gate operations involve four values and their semantics have to be defined by extended 'truth' tables that, implicitly, consider two (normal and faulty) circuits.

The use of multi-valued logics is not new in computer science, with successful application in several domains such as temporal logics [Prior 1957, Galton 1987, van Benthem 1995] or in qualitative reasoning [Forbus 1984, Davis 1984, Kuipers 1989]. Modelling dependencies with such logics relates to *truth maintenance systems* (TMSs) [Doyle 1979], as discussed in section 1.2, and has possible applications for generic agents (and for circuits in particular) for tasks such as diagnosis or general modelling to predict behaviour.

The introduction of multi-valued logics induces problem variables (signal lines) with finite domains, thus suggesting the use of CLP(FD) for efficient solving. Instead, separate circuit models with Boolean variables can be considered and subsequently solved by propositional satisfiability (SAT) approaches [Marques-Silva 1995].

In this dissertation we address a number of diagnostic related problems (in the sense that faults are taken into account) and propose and develop models with different logics that we formalise and

generalise as much as possible. In addition, we try to solve each problem with CLP solvers that we implement and discuss, comparing with other approaches. The adequacy of the proposed approaches is illustrated with examples and results, pointing to other applications (where appropriate) and possible research directions.

# 1.1 Scope

This dissertation covers a number of satisfaction and optimisation problems, such as modelling of circuits and faults, simulation of normal and faulty behaviour, test generation, minimal and differential diagnosis, generation and minimisation of test sets, unveiling and maximising faults detected by a test, and maximisation of unspecified inputs of a test. Techniques developed apply to these and other related problems over circuits in particular and agents in general.

While such problems concern general 'black-box' agents modelled as propositional theories, examples throughout this dissertation consider only the particular but representative case of combinational digital circuits, for which a well established set of benchmarks [ISCAS 1985] exist, thus allowing comprehensive comparisons of results with different approaches for those problems. Applicability of developed techniques to general agents is trivially proven in the last chapter.

Some examples and notation concerning circuits are taken from [Abramovici *et al.* 1990], where a thourough study of digital systems testing can be found and where it is also shown that the consideration of combinational circuits alone is not too restrictive, since problems over sequential circuits are usually best handled with techniques developed for combinational circuits (often by transforming those circuits into combinational).

The types of faults considered are the usual stuck-at faults, where a gate is stuck at some Boolean value v thus always outputting v regardless of its input. Again, [Abramovici et al. 1990] shows that such faults are not too restrictive since other types of faults can often be considered through these simpler stuck-at faults, and such (apparent) restriction allows for more efficient techniques to be developed. Furthermore, when talking about virtual agents modelled as a set of propositional rules, these faults are the only ones that need to be considered.

# 1.2 Truth Maintenance Systems

Truth maintenance systems (TMSs) [Doyle 1979] reason about logical statements in order to maintain global consistency. Inferences are justified by a set of supporting statements that are recorded as dependencies. Such systems support nonmonotonic reasoning since assumptions derived from default reasoning may be revised due to contradictory new information (inferred statements). For that, TMSs refer to a statement as a node that may be at any point in either of two states: IN or OUT. If a node is believed to be true then it is IN, otherwise it is OUT either because there is no justification for it to be true or because justifications for it are currently not valid.

Each node n then has a list of justifications attached, which basically are support lists mentioning nodes that must be IN and nodes that must be OUT for n to be believed to be true (IN).

When a contradiction arises, a dependency-directed backtracking procedure is invoked on the

contradiction node created, looking at its justification nodes and recursively at their justifications until a set of inconsistent assumptions is found, which is then recorded as a *nogood* node to avoid further computations based on it.

To model circuits problems, a digital gate is assumed to be either normal or with a specific fault. Inspection of the output may then reveal a contradiction that leads to a set of inconsistent assumptions, which are however found only indirectly since dependency on assumptions is not explicitly expressed (in fact, the system has to search recursively through justifications to find such dependencies).

In conventional *justification-based* TMSs, a particular datum is believed in an implicit context given by the set of all IN nodes. Context switching is performed for truth maintenance by dependency-directed backtracking to move inside the search space. To avoid most backtracking and easily switch between contexts, Johan de Kleer proposed [1986] an *assumption-based* TMS (ATMS), where data are labelled with the sets of assumptions (representing contexts) under which they hold. Such sets are kept as general as possible in order to more easily derive data (for example, if context *C* includes context *B*, then all derivations of *B* remain valid under *C*). Similarly, contradictions are recorded in the most general form to rule out as much of the search space as possible. Thus, multiple solutions can be explored simultaneously without the need for the global database to be consistent. For this, ATMSs spend most computation time in determining most general forms.

While conventional TMSs are oriented towards finding one solution, the ATMS is oriented to finding all solutions. Hence, ATMSs are best suited only for problems with many solutions and where all of them are required.

The multi-valued logics that we develop in this dissertation allow more efficient tools to be developed by encoding direct dependency on the assumptions that care for each problem. Hence, overhead of searching dependencies with TMS is avoided. And since, in general, solving 'circuit' problems requires finding a solution rather than all of them, overhead of considering all contexts as in ATMSs is also avoided. Furthermore, for such cases where all solutions are required, such as in diagnosis, it is often possible to be more efficient using a multi-valued logic as reported in [Alferes et al. 2001], where a model using a logic over Boolean and set values generates all possible diagnoses (for an incorrect circuit behaviour) in a single step with no backtracking at all!

# 1.3 Constraint Reasoning

A problem where relations between variables (to which values must be assigned) are restricted by a number of constraints that must be satisfied, is referred to as a Constraint Satisfaction Problem (CSP) [Montanari 1974, Mackworth 1977]. The goal is to assign values to all the variables without violating any constraint, or to prove this to be impossible. The space formed by all possible combinations of assignments is referred to as the search space. Such combinatorial search problems have been widely studied in *Artificial Intelligence* (AI) and *Operations Research*.

CLP(FD) integrates constraints in logic programming, where variables may be restricted to

explicitly range over finite subsets of the universe of values, thus defining finite domain variables [Van Hentenryck and Dincbas 1986]. Search for solutions involve assigning variables with values from their domain and, when a contradiction is found due to some violated constraint, perform some form of backtracking [Golomb and Baumert 1965] (usually chronological) to undo choices made and try other yet unexplored branch of the search tree.

Since the search space of combinatorial problems is usually intractable [Garey and Johnson 1979], a naïve *generate-and-test* approach, in which each combination of possible assignments is generated and then tested for a solution, until one is found, is unsuitable. Hence, *constraint reasoning* techniques are usually applied in AI to (often, drastically) reduce search space by discarding impossible solutions [Mackworth 1977, Nadel 1989, Dincbas *et al.* 1990, Dechter 1992, Mackworth 1992, Kumar 1992]. In this section, we briefly describe the basics of such local consistency techniques that look ahead at logical predicates defined as constraints to discard impossible values from the domain of individual variables.

# 1.3.1 Consistency Techniques

Constraint solvers apply constraint propagation or consistency techniques [Van Hentenryck 1989] in order to remove redundant (i.e. impossible) values from the domains of variables involved in stored constraints. If the domain of some variable becomes empty after the application of such techniques, then the CSP is insoluble. Otherwise, the CSP is said to be **consistent** (with regard to some properties) and there may be a solution, which has to be found to definitely prove one exists. In general, solvers using such techniques are incomplete, which means that reaching a consistent state for the CSP is not a sufficient condition for its satisfiability. Hence, a search phase must still occur to find a possible assignment of values to all the variables. Consistency techniques are interleaved during this search phase to constantly reduce search space, aiming at saving computation time. Notice that there is a trade-off between the level of consistency applied and the amount of pruning (of the search tree) obtained. Usually, greater levels of consistency produce decreasingly larger improvements on pruning and require increasingly larger amounts of CPU time, thus becoming counter-productive at some stage.

In this section we briefly describe the most common consistency techniques, each guaranteeing a different property. Definitions are taken from [Tsang 1993], where a thorough study on these concepts can be found.

Before introducing such concepts we first recall that a CSP is composed of a set of variables (each with some domain) related by a set of constraints that restrict the values they can simultaneously take. A **binary** CSP is one such problem where constraints are just unary or binary (i.e. each constraint involves just one or two variables). It can be represented as a graph where nodes are variables and edges are constraints relating two nodes. A CSP not limited to such constraints is referred to as a **general** CSP and defines a hypergraph where hyperedges are constraints relating (connecting) an arbitrary number of variables (nodes). Notice, however, that any CSP has a **dual** binary CSP (as described in [Tsang 1993]).

To solve a CSP, variables have to be assigned values from their domains (i.e. labelled). An assignment of value v to variable x is denoted by a **label** in the form  $\langle x, v \rangle$ . A **compound label** is a

set of labels representing a simultaneous assignment of values to different variables.

With these notions we may now define some consistency techniques.

A CSP is **node-consistent** (NC) if and only if for all variables, all values in its domain satisfy the constraints on that variable (i.e. unary constraints).

Node consistency is usually applied in CLP(FD) since the finite enumeration of possible values allows an efficient removal of values that do not satisfy a constraint.

A CSP is **arc-consistent** if and only if for every variable x, for every label  $\langle x,a \rangle$  that satisfies the constraints on x, there exists a value b for every variable y such that the compound label  $(\langle x,a \rangle \langle y,b \rangle)$  satisfies all the constraints on x and y.

For n-ary constraints, *generalised arc consistency* can also be defined and applied by checking compatible labels among all variables related by each constraint. However, this is generally too expensive.

To keep a CSP arc-consistent there are a number of algorithms that go through the variables to remove incompatible values (with some other variable) from their domains. These algorithms vary on the number of steps and tests required to achieve AC, i.e. on their time and space complexity. We may refer, for binary constraints, the naïve AC-1 algorithm, which considers all constraints and for each value removed from a domain, it will go through all constraints again to check if some other value can be removed. AC-1 was then improved to AC-2 and AC-3, which would add the notion of supporting values to avoid checking all constraints again, but rather only those constraints that could be affected by the removal of some value from the domain of a variable. These algorithms were later further improved by the (considered optimal) AC-4, which extends the notion of support to conclude that although removing a value from the domain of x may affect y, the particular removal of y does not. Nevertheless, other algorithms were still developed [Bessière and Cordier 1994, Bessière y and y does not. Nevertheless, other algorithms were still developed [Bessière and Cordier 1994, Bessière y and y does not. Nevertheless, other algorithms were still developed [Bessière and Cordier 1994, Bessière y and y does not. Nevertheless, other algorithms were still developed [Bessière and Cordier 1994, Bessière y and y does not.

# Beyond AC one may still define **Path Consistency** (PC):

A CSP is path-consistent if and only if for all variables x and y, whenever a compound label  $(\langle x,a \rangle \langle y,b \rangle)$  satisfies the constraints on both x and y, there exists a label  $\langle z,c \rangle$  for every variable z such that  $(\langle x,a \rangle \langle y,b \rangle \langle z,c \rangle)$  satisfies all the constraints on x, y and z.

Path consistency (or any variant or simplification) is rarely used due to its computational complexity. In practice, such kind of consistency may only be considered for binary CSPs or when constraints are few and domains are very small.

Since full AC is, in general, already too costly computationally, some consistency techniques try to approximate it by relaxing some properties. This implies that values incompatible with other variables may remain in some domain, but often it is worth that 'risk' since the relaxed technique is

much simpler than full AC, and the pruning achieved is similar. Below we describe some of these techniques.

If there is a total ordering of variables, consistency techniques such as AC (and PC) can be directional. **Directional Arc-Consistency** (DAC) [Dechter and Pearl 1988] is thus defined when the constraint graph is in fact a tree:

A CSP is *directional arc-consistent* under an ordering of the variables if and only if for every label  $\langle x,a \rangle$  that satisfies the constraints on x, there exists a compatible label  $\langle y,b \rangle$  for every variable y that is <u>after</u> x according to the ordering.

A weaker but often more efficient consistency technique than AC is that of **Bounded Arc-Consistency** (BAC) [Van Hentenryck 1989] in which only the two bounds of each variable (domain) are verified and possibly updated (tightened) to remove impossible values between two variables by restricting their domains. This is particularly used in CLP(*Intervals*), often for modelling domains over real numbers or sets, for example. In such cases, domains are expressed by a range in the form *lower-bound. upper-bound*.

# 1.3.2 Maintaining Consistency

**Forward Checking** (FC) is a search strategy that assumes node consistency and approximates arcconsistency by removing from domains of variables, those values that are incompatible with each assignment. I.e. whenever there is a commitment to a label  $\langle x,a \rangle$ , FC removes all values from the domains of variables (other than x) that are incompatible with value a for x. If some domain becomes empty, unsatisfiability for the current set of assignments is detected and backtracking is forced. **Constraint propagation** is thus performed on instantiation of some variable. Arc consistency is forced between two variables only when one of them is labelled, thus being effectively reduced to node consistency.

The algorithm of **Maintaining Arc Consistency**, MAC [Sabin and Freuder 1994], is a combination of FC and AC in that the constraint network is made arc consistent initially and whenever there is a commitment to a label  $\langle x,a \rangle$ , the effects of removing values (other than a) from the domain of x are propagated through the constraint network as necessary to restore full arc consistency. The particular usefulness of MAC in random binary CSPs is shown in [Sabin and Freuder 1994, Bessière and Régin 1996].

# 1.3.3 Advanced Techniques

In this section we mention different advanced techniques that CLP solvers may also apply. Such techniques will be referred along this dissertation to solve different problems.

The techniques described above use a local consistency criterion to remove impossible values from domains of variables by examining directly a constraint that relates them. However, often a set of basic constraints relating a set of variables can be seen as a **global constraint** [Beldiceanu 1990] over them, which allows specialised information to be used for further pruning of the search tree.

For instance, let us assume that four variables  $X_1$ ,  $X_2$ ,  $X_3$ ,  $X_4$ , with domain  $\{1,2,3\}$ , are constrained to be pairwise different (i.e.  $X_1 \neq X_2 \land X_1 \neq X_3 \land X_1 \neq X_4 \land X_2 \neq X_3 \land X_2 \neq X_4 \land X_3 \neq X_4$ ), to express that all four variables are different. Clearly, there is no solution that satisfies those constraints since there are only 3 possible values for 4 different variables. Nevertheless, it can be verified that the CSP is path-consistent, since for any assignment to two variables, there is still one possible value left for a third variable. For such cases, a global constraint such as *all\_different*( $\{X_1, X_2, X_3, X_4\}$ ) may be used to decide for unsatisfiability due to shortage of resources (number of different values to assign). An efficient algorithm for such constraint is described in [Régin 1994].

A global constraint may be either user-defined or provided as built-in of a CLP solver (a number of such built-in global constraints exist, e.g. [Beldiceanu and Contejean 1994]).

Similarly, a *meta-constraint* such as the *cardinality* operator [Van Hentenryck and Deville 1991] may be used for a more global reasoning. The cardinality constraint is given a set of goals, of which at least *n* and at most *m* must be satisfied. It may thus represent a disjunctive constraint, which allows delaying choices (the disjuncts) by reasoning globally on the disjunction to, when some goals become known to be impossible or trivially satisfied (during search or upon new constraints posted), infer that the remaining goals must be either true or false.

A yet more powerful technique to handle disjunctions consists of *constructive disjunction* [le Provost and Wallace 1993] which may restrict domains of variables by reasoning globally on the disjunction (enforcing AC).

In general, interleaved with the maintenance of some form of consistency, a *labelling* phase for enumeration of the CSP variables must still occur to prove whether a solution exists and find it. There are different ways to go through the search space, with possible dramatic differences in efficiency. Hence, in addition to constraint propagation techniques, it is also important to pay attention on guiding search.

Instantiating variables with values from their domains sequentially in a depth-first search, with chronological backtracking of Prolog, is often unsatisfactory. **Heuristics** (functions to rank candidates) may thus be used to choose what variable to instantiate next and what value should be tried first. The difference in ordering may be critical since there may be labels much more likely to belong to a solution than others, and because some variables may be harder to instantiate. This is the case considered by the popular *first-fail* (FF) heuristic [Haralick and Elliott 1980], which selects variables with smaller domains first.

To avoid being "stuck" at an incorrect early choice of a depth-first search, randomisation techniques may also be applied to "jump" to a different point in the search space. This allows other branches to be explored before some defined threshold is reached, which contributes to a "fairer" distribution of search and, consequently, to increase probability of finding a solution faster. Existing such techniques include iterative broadening [Ginsberg and Harvey 1990], iterative deepening [Meseguer 1997], and limited discrepancy search [Harvey and Ginsberg 1995, Walsh 1997]. A new search technique based on randomisation is presented in Chapter 3 and is subsequently applied to solve more complex problems addressed in following chapters.

For an optimisation goal, one is not interested just in finding a solution but rather in finding the best one. For that, once some solution is found, only better solutions (according to some measure function) are sought. Hence, partial solutions already known to have no possibilities of improving the current optimal solution can be discarded, and other branches of the remaining search tree can be explored. Such pruning and branching technique according to a current bound is referred to as **branch-and-bound** [Papadimitriou and Steiglitz 1982, Balas and Toth 1985].

Often, a solution found can be improved more efficiently by performing some form of **local** search, in which small changes to the current solution are explored to find a local optimum.

In Chapter 7 we combine branch-and-bound and local search techniques to solve an optimisation problem using models with different multi-valued logics.

#### 1.4 Contributions and Limitations

The contributions of this dissertation are not restricted to a single domain bur rather aim at different aspects of computer science in general, and AI in particular. The areas potentially benefited involve *Constraint Reasoning*, formal *Multi-valued Logics*, ECAD *problem modelling and solving* (namely simulation, test generation, optimisation, basic and differential diagnosis) and *Agents* (to which paradigm all developed techniques are generalised).

In this dissertation we extend the standard Boolean logic by formalising a number of logics that encode simultaneously different theories (of a circuit/agent model), which represents an alternative to the classical approach of modelling each theory with Boolean variables and then relating the encoded theories with constraints over those variables. The logics developed typically have 2<sup>n</sup> values, where n is the number of encoded theories, but other logics are also presented to explicitly consider unspecified values. The development of such logics culminates with the set algebra, thus generalising the encoding of an arbitrary number of theories in a single logic. All logics aim at modelling fault dependencies, as did the basic D-calculus of the ECAD area [Abramovici et al. 1990], already used in constraint programming [Simonis 1989]. We generalise not only the number of encoded theories, as explained, but also the number of faults a theory can have, thus, being no more restricted to single faults.

For each logic, we show how to model and solve different satisfaction and optimisation problems and we implement specialised constraint solvers, showing their applicability. All these implementations contributed to a workbench for a practical study of different consistency techniques. In addition, when implementing search strategies, a new technique, **iterative time-bounded search** (Chapter 3), was formalised and developed with significant results.

One such implemented constraint solver, *Cardinal* (Chapter 6), is a general set constraint solver which improves on existing solvers by adding *cardinality inferences*, which prove to be extremely useful by obtaining execution times orders of magnitude smaller on a number of problems. To such set solvers, we also show how attaching to set variables set functions other than cardinality, may turn general problems more declarative and efficient, by reasoning on such functions. We use an extended *Cardinal* for practical results over some benchmark problems.

In addition to the constructive approach of constraint programming we use a repairing approach in a tool, *Maxx* (Chapter 7), that we developed to solve the optimisation problem of maximising the number of unspecified bits in an input test vector. Since models with the developed logics and other approaches are not complete (in the sense that optimal tests can be unrecognised), we developed yet another logic to which we refer as **extended logic**. This logic takes into account the sources of unspecified values, in order to approach completeness in a practical way. Again, sets were used to denote dependencies on specified values in a **local search** method to improve solutions. Altogether, *Maxx* incorporates a number of multi-valued logics with branch-and-bound and local search. By obtaining better results than an efficient tool based on SAT and ILP, we show and discuss the usefulness of integrating branch-and-bound with local search.

In summary, the main contributions include:

- □ Development and formalisation of a number of multi-valued logics to model different problems, together with specialised CLP tools to solve them;

- □ Development and formalisation of a new efficient search technique: ITBS;

- □ Proposal of new benchmarks, namely for differential diagnosis;

- Generalisation of several logics into a single logic over sets, to encode an arbitrary number of theories;

- □ Formalisation of models for the different satisfaction and optimisation diagnostic-related problems;

- Generalisation of all problems to theories with multiple faults;

- ☐ Generalisation of all circuit problems to agents;

- □ Development and formalisation of a new efficient general set constraint solver, *Cardinal*, with especial inferences on sets cardinality;

- □ Presentation of extensions to *Cardinal*, generalising inferences over sets functions, with discussion and application over general combinatorial problems;

- □ Formalisation of an *extended logic*, more complete when handling unspecified values, by keeping track of their sources;

- □ Development of *Maxx*, a constraint tool incorporating different multi-valued logics developed, to optimise test vectors and beat an existing efficient tool based on SAT and ILP;

- □ Integration of *local search* with *branch-and-bound* using another logic based on sets, with exemplification of the usefulness of such an approach on optimisation problems.

All in all, a number of research topics are open and we believe that the results and generalisations we obtain in several areas promise a wide research with many possible directions.

## 1.4.1 Limitations

While we show that the techniques developed in this dissertation generalise to agents, we restrict our examples to problems over digital combinational circuits with well-known benchmarks. The ECAD industry is very competitive and has many specialised and optimised tools devoted to solving each industry problem. It is already a very mature area; hence it is not our purpose to solve their specific problems or improve their solutions (although we present some competitive results, as recognised in the ECAD community, e.g. [Azevedo and Barahona 2000a, 2002]). Rather, we want to show the effectiveness of our approach, to these and other problems, by showing its potential and generalise it so that the already specialised techniques developed can be used in other domains. Also, we present new ideas and techniques that the industry may like to introduce in their systems in order to possibly improve them.

Therefore, we did not concentrate on heuristics, which are crucial for solving circuit problems. Also, during search, we relied on chronological backtracking of Prolog (usually the graphical Tcl/Tk version [Ousterhout 1994] of ECLiPSe over Windows). Some intelligent backtracking scheme such as dependency-directed backtracking [Stallman and Sussman 1977] would probably be much more efficient when trying to label a number of circuit input bits. Moreover, the underlying Prolog tool is not the best suited in terms of efficiency.

Problems and models presented throughout this dissertation assume that circuits are combinational. Nevertheless, solving problems over sequential circuits often involves some transformation into equivalent combinational circuits [Abramovici *et al.* 1990], which allows using the developed techniques for such circuits.

A limitation regarding fault modelling is that we only consider stuck-at faults. Although other types of permanent physical faults can be modelled with just stuck-at faults [Abramovici et al. 1990], circuits with intermittent and transient faults require extra techniques not dealt with in this dissertation. Nevertheless, the usual stuck-at faults are enough to represent any kind of fault in theoretical agents modelled by a set of propositional rules.

#### 1.5 Overview

Since the practical examples of this dissertation are concentrated on circuit problems, we start by discussing circuit modelling in Chapter 2. A first problem is presented in Chapter 3, where we describe, model and solve the basic problem of generating tests (input vectors) for a circuit (particularly, for a specific fault) and discuss and compare our approach with competing alternatives. For this problem, we develop a CLP solver over a 4-valued logic (encoding fault dependencies) that uses a new search technique, namely, iterative time-bounded search. Such logic is then extended to an 8-valued logic that we formalise in Chapter 4 for the problem of differential diagnosis of two sets of faults.

In Chapter 5, we present different satisfaction and optimisation problems concerning multiple diagnoses (each a set of faults) showing how to model them with a logic over values formed by a pair of a set and a Boolean value (the particular problem of diagnosis is efficiently solved with such logic, as the experimental results document). We also show a transformation of such value pairs into single set values, that produce elegant models over a set algebra. To solve problems described by these and other models, we developed a general set constraint solver, *Cardinal*, formally described in Chapter 6, that is able to perform a number of especial inferences over sets cardinality. We present experimental results for general set problems and for the particular problem of differential diagnosis, where the superiority of *Cardinal* over existing solvers is especially evident. *Cardinal*

extensions are also presented and discussed in this chapter by considering other set functions to solve other general problems, such as set covering.

Inspired in the reasoning over sets and over dependencies, in Chapter 7 we tackle another test optimisation problem by developing an extended logic and using local search (with sets of dependencies on specified values) together with a constructive approach to improve on an existing efficient tool to solve this problem. We incorporated a number of multi-valued logics to develop the new tool, *Maxx*, for which we present the improved results.

Finally, in Chapter 8 we show that all techniques generalise to consider agents (modelled by a set of propositional rules) instead of circuits. In addition to this important and desired result, we discuss the overall work covered in this dissertation together with possible future research, and present some final conclusions.

We organised this dissertation in a way that the multi-valued logics are presented in successive chapters in increasing order of the number of their values, as a consequence of encoding successively more theories. Often a described logic is a generalisation of a previous one; hence chapters should be read sequentially, although we try to keep each chapter with a reasonable amount of autonomy by having clear distinct objectives and referring related work described in more detail elsewhere in the dissertation (or outside it).

We add two appendices, basically with raw data, for ease of consultation and to obtain more detail on the most used sources of knowledge of this dissertation. Appendix A describes in more detail the circuit benchmarks used throughout the dissertation (an information made available on the internet via world wide web). Appendix B describes the multi-valued logics that were developed, with their purpose, meaning of values, and "truth" tables for the usual operations.

#### CIRCUIT MODELLING

To support all the stages of the life cycle of a digital system, it is convenient to have a model of it. Design, production and testing of a digital circuit largely depend on modelling, for it is the model that allows one to simulate the logical circuit with or without faults, to verify its correctness and generate tests for it. Hence, the way a circuit is *internally modelled* in a computer influences the application of algorithms for it.

This chapter addresses circuit- and fault-modelling approaches starting with a brief introduction in section 2.1, where we present general terminology and features of combinational circuits. In section 2.2 we discuss modelling of normal digital circuits for simulation of behaviour, and in section 2.3 possible circuit faults that may affect it are taken into account. Then, in section 2.4 we present a set of widely used circuit benchmarks and their characteristics, and in section 2.5 we describe our general modelling approach for such circuits and for the faults that may affect their behaviour.

## 2.1 Introduction