# **Experimental Studies on Germanium-Tin P-Channel Tunneling Field Effect Transistors**

Von der Fakultät Informatik, Elektrotechnik und Informationstechnik der Universität Stuttgart zur Erlangung der Würde eines Doktors der Ingenieurwissenschaften (Dr.-Ing.) genehmigte Abhandlung

Vorgelegt von

Erlend Granbo Rolseth

aus Trondheim, Norwegen

Hauptberichter: Prof. Dr. habil. Jörg Schulze

Mitberichter: Prof. Dr. rer. nat. Joachim Knoch

Tag der mündlichen Prüfung: 22.08.2017

Institut für Halbleitertechnik der Universität Stuttgart 2017

## Contents

| Zusammen    | fassung                                                                       | 10 |

|-------------|-------------------------------------------------------------------------------|----|

| Summary .   |                                                                               | 13 |

| Chapter 1   | Introduction                                                                  | 15 |

| 1.1 Se      | arching for a New Energy Efficient Switch                                     | 15 |

| 1.2 A       | Brief History of Germanium in Complementary Metal-Oxide-Semiconductor         |    |

| Technolo    | gy                                                                            | 16 |

| 1.3 Hi      | story of the Tunneling Field Effect Transistor                                | 18 |

| 1.4 Th      | eoretical Background                                                          | 20 |

| 1.4.1       | Power Consumption of a Logic Element                                          | 21 |

| 1.4.2       | Tunneling Field Effect Transistor: Operating Principles                       | 23 |

| 1.4.3       | Zener Tunneling Current                                                       | 24 |

| 1.4.4       | Subthreshold Swing of Tunneling Field Effect Transistors                      | 26 |

| 1.4.5       | Leakage Current Mechanisms in Tunneling Field Effect Transistors              | 28 |

| 1.5 Tu      | nneling Field Effect Transistors: State-of-the-Art                            | 32 |

| 1.5.1       | Material System Considerations for Tunneling Field Effect Transistor Design 3 | 32 |

| 1.5.2       | Geometry Considerations for Tunneling Field Effect Transistor Design          | 35 |

| 1.6 Th      | esis Overview                                                                 | 36 |

| Chapter 2   | Vertical Tunneling Field Effect Transistor Device Fabrication and Data        |    |

| Acquisition | n 40                                                                          |    |

| 2.1 Mo      | olecular Beam Epitaxy                                                         | 40 |

| 2.1.1       | Molecular Beam Epitaxy Growth Process                                         | 41 |

| 2.1.2       | Doping in Molecular Beam Epitaxy Systems                                      | 42 |

| 2.1.3       | Molecular Beam Epitaxy Growth of Germanium on Silicon                         | 43 |

| 2.1.4       | Molecular Beam Epitaxy Growth of Germanium-Tin                                | 45 |

| 2.1.5       | Molecular Beam Epitaxy Growth of Germanium/Germanium-Tin P-Channel            |    |

| Tunnel      | ing Field Effect Transistors                                                  | 46 |

| 2.2     | Vei    | rtical Gate-All-Around Device Fabrication of Germanium Based Tunneling   |    |

|---------|--------|--------------------------------------------------------------------------|----|

| Field   | d Effe | ct Transistors                                                           | 48 |

| 2.      | 2.1    | Mesa Structuring in Gate-All-Around Fabrication Process of Germanium     |    |

| В       | ased T | Cunneling Field Effect Transistors                                       | 49 |

| 2.      | 2.2    | Gate Formation in Gate-All-Around Fabrication Process of Germanium Based |    |

| Ti      | unneli | ng Field Effect Transistors                                              | 50 |

| 2.      | 2.3    | Isolation and Contacting in Gate-All-Around Fabrication Process of       |    |

| G       | erman  | ium Based Tunneling Field Effect Transistors                             | 52 |

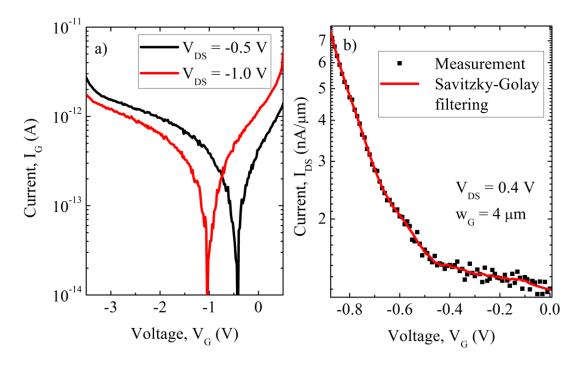

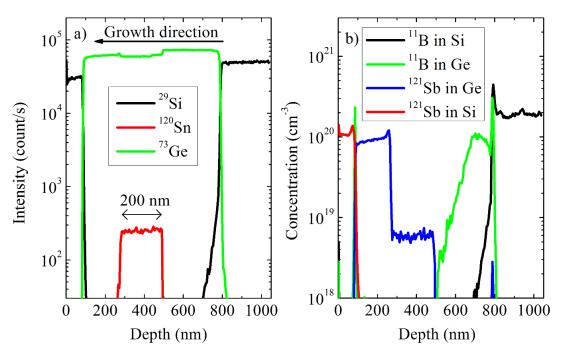

| 2.3     | Dat    | ta Acquisition and Processing                                            | 53 |

| Chapt   | er 3   | Germanium-Tin P-Channel Tunneling Field Effect Transistors: the          |    |

| Effect  | of Ti  | n-Content in Germanium-Tin Channel                                       | 56 |

| 3.1     | Inti   | roduction                                                                | 56 |

| 3.2     | Lay    | yer Growth and Device Fabrication                                        | 57 |

| 3.3     | Res    | sults and Discussion                                                     | 59 |

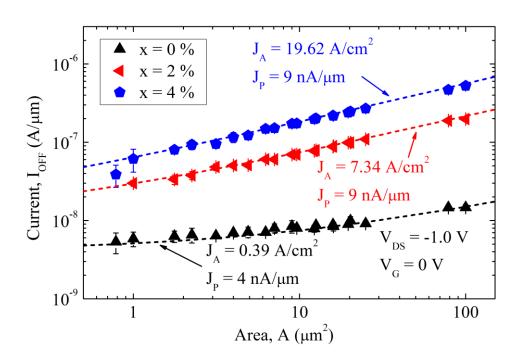

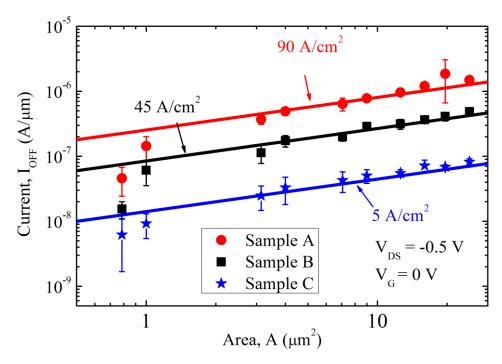

| 3.      | 3.1    | Influence of Tin-Content in Channel on Leakage Current in Germanium-Tin  |    |

| Ti      | unneli | ng Field Effect Transistors                                              | 60 |

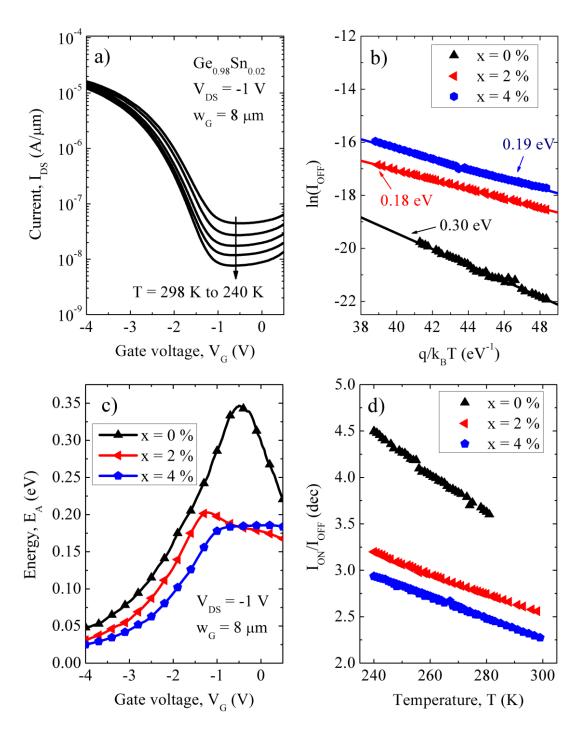

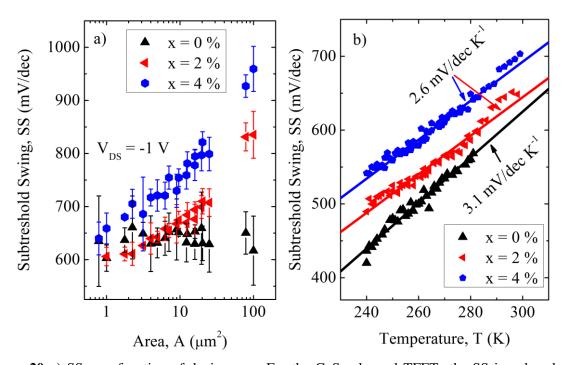

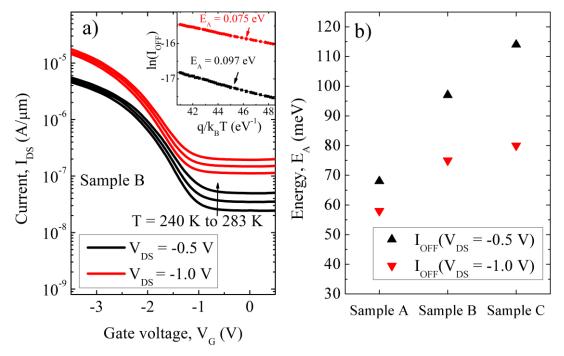

| 3.      | 3.2    | Influence of Tin-Content in Channel on Subthreshold Swing of Germanium-  |    |

| Ti      | in Tun | nneling Field Effect Transistors                                         | 66 |

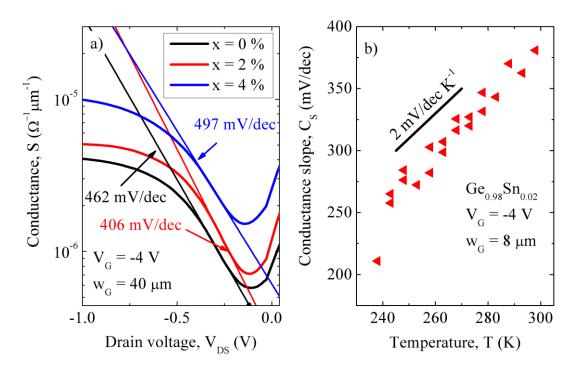

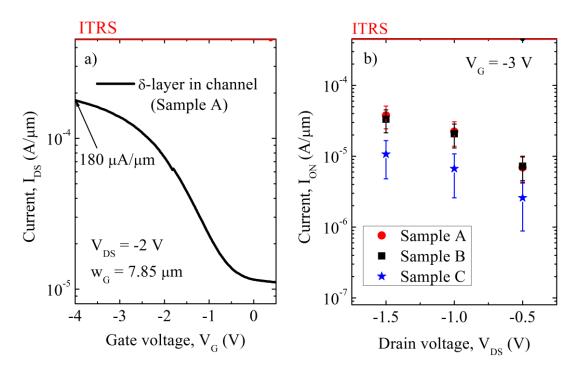

| 3.      | 3.3    | Influence of Tin-Content in Channel on Drive Current of Germanium-Tin    |    |

| T       | unneli | ng Field Effect Transistors                                              | 68 |

| 3.4     | Co     | nclusion                                                                 | 71 |

| Chapt   | er 4   | Germanium-Tin P-Channel Tunneling Field Effect Transistors:              |    |

| Positio | onal D | Dependence of Germanium-Tin-Delta-Layer at Source-Channel Interface      | 72 |

| 4.1     | Inti   | roduction                                                                | 72 |

| 4.2     | Lay    | yer Growth and Device Fabrication                                        | 73 |

| 4.3     | Res    | sults and Discussion                                                     | 74 |

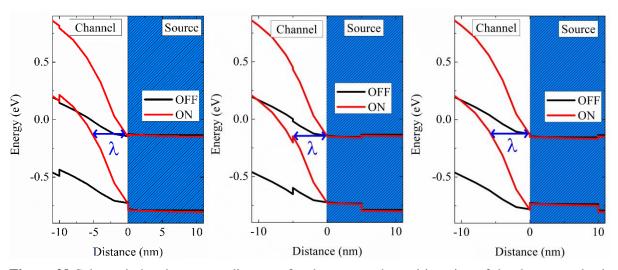

| 4.      | 3.1    | Positional Dependence of Germanium-Tin-Delta-Layer at Source-Channel     |    |

| In      | terfac | e on Leakage Current                                                     | 75 |

| 4.      | 3.2    | Positional Dependence of Germanium-Tin-Delta-Layer at Source-Channel     |    |

| In      | terfac | e on Drive Current                                                       | 78 |

| 4.4    | Conclusion80                                                                                                                 |

|--------|------------------------------------------------------------------------------------------------------------------------------|

| Chapt  | er 5 Source Doping Concentration Variation in Germanium P-Channel                                                            |

| Tunne  | eling Field Effect Transistors82                                                                                             |

| 5.1    | Introduction                                                                                                                 |

| 5.2    | Layer Growth and Device Fabrication                                                                                          |

| 5.3    | Results and Discussion                                                                                                       |

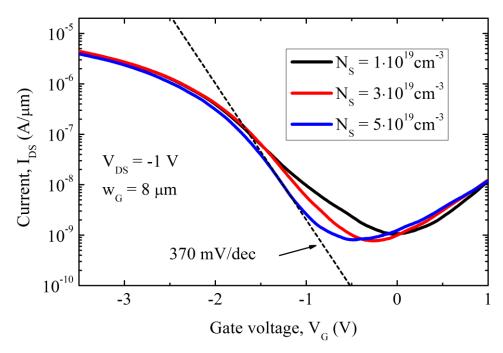

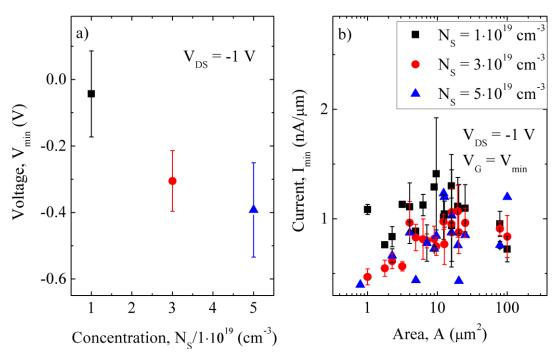

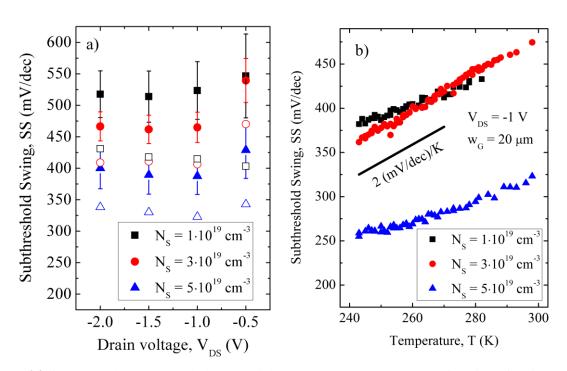

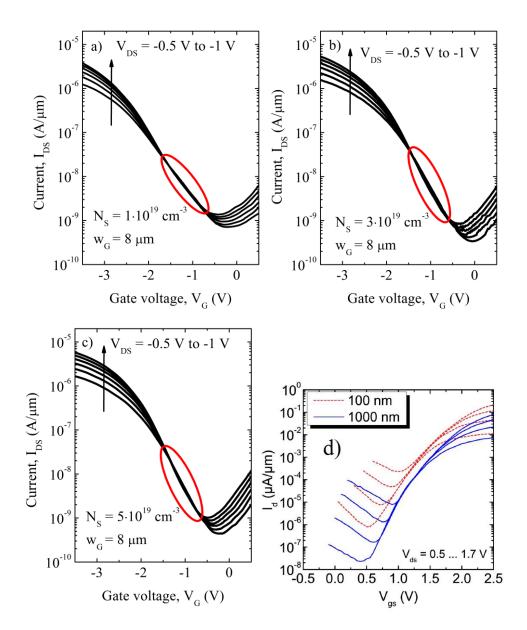

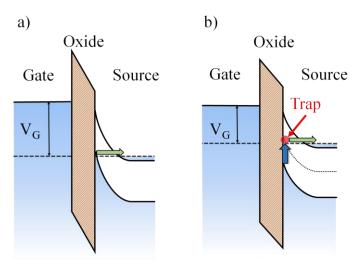

|        | 3.1 Influence of Source Doping Concentration on Leakage Current in Germanium unneling Field Effect Transistors               |

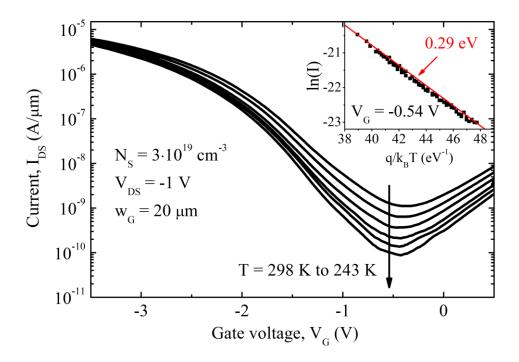

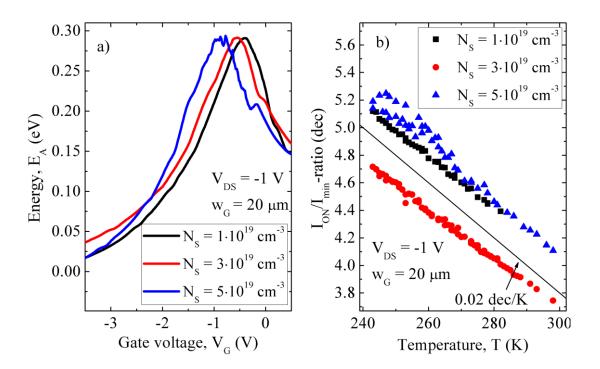

|        | 3.2 Temperature Dependence of Germanium P-Channel Tunneling Field Effect ransistors with Varying Source Doping Concentration |

|        | 3.3 Influence of Source Doping Concentration on Subthreshold Swing in ermanium P-Channel Tunneling Field Effect Transistors  |

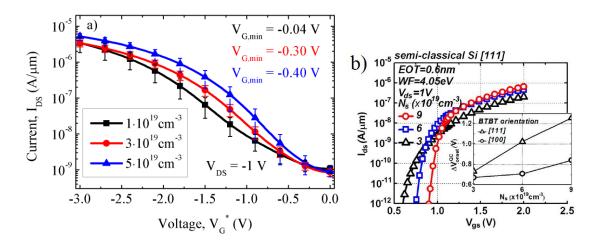

| 5.3    | 3.4 Influence of Source Doping Concentration on Drive Current in Germanium P-                                                |

| Cł     | hannel Tunneling Field Effect Transistors                                                                                    |

| 5.4    | Conclusion95                                                                                                                 |

| Chapt  | er 6 Source Doping Profile Tuning in Germanium P-Channel Tunneling Field                                                     |

| Effect | Transistors through Molecular Beam Epitaxy Antimony Pre-Buildup97                                                            |

| 6.1    | Introduction                                                                                                                 |

| 6.2    | Layer Growth and Device Fabrication                                                                                          |

| 6.3    | Results and Discussion                                                                                                       |

| 6.4    | Conclusion                                                                                                                   |

| Chapt  | er 7 Electrical Characterization of Germanium/Aluminum                                                                       |

| Oxide/ | Aluminum Metal-Oxide-Semiconductor Capacitors Passivated through Post                                                        |

| Plasma | a Oxidation104                                                                                                               |

| 7.1    | Introduction                                                                                                                 |

| 7.2    | Layer Growth and Device Fabrication                                                                                          |

| 7.3    | Results and Discussion                                                                                                       |

| 7.3    | 3.1 Capacitance-Voltage Characteristics of Post Plasma Oxidized                                                              |

| Ge     | ermanium/Aluminum Oxide/Aluminum Metal-Oxide-Semiconductor Capacitors 106                                                    |

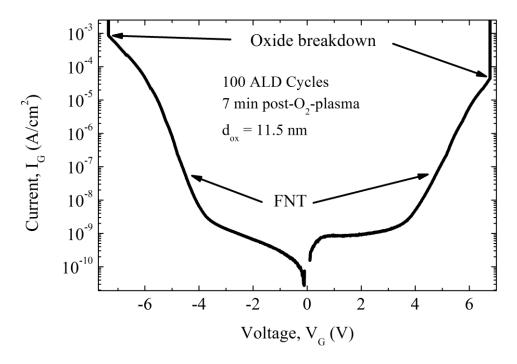

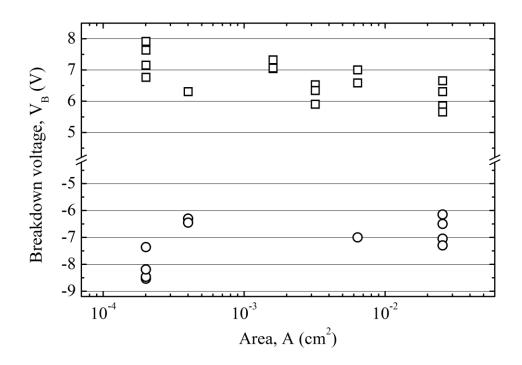

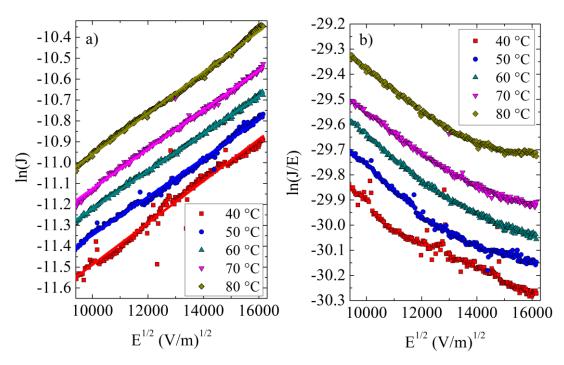

| 7.3.2        | Current-Voltage Characteristics of Po              | ost Plasma Oxidized           |

|--------------|----------------------------------------------------|-------------------------------|

| German       | nium/Aluminum Oxide/Aluminum Metal-Oxide-Se        | miconductor Capacitors 113    |

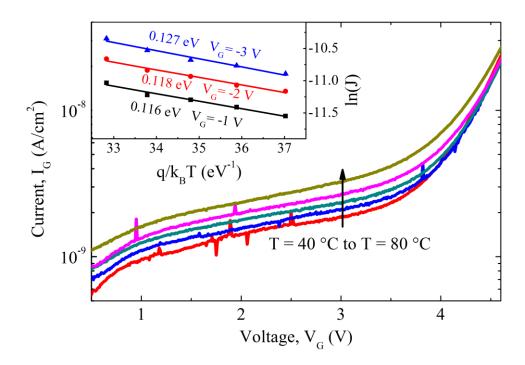

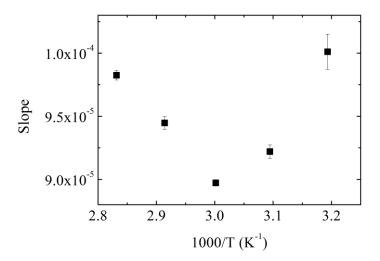

| 7.3.3        | Temperature Dependency of the Current-Volta        | age Characteristics of Post   |

| Plasma       | Oxidized Germanium/Aluminum Oxide/                 | Aluminum Metal-Oxide-         |

| Semicor      | nductor Capacitors                                 | 116                           |

| 7.4 Cor      | nclusion                                           | 119                           |

| Chapter 8    | Impact of Sulfur Passivation on the E              | lectric Characteristics of    |

| Germanium    | n/Aluminum Oxide/Aluminum Metal-Oxide-Sen          | niconductor Capacitors 121    |

| 8.1 Intr     | roduction                                          | 121                           |

| 8.2 Lay      | yer Growth and Device Fabrication                  | 121                           |

| 8.3 Res      | sults and Discussion                               | 122                           |

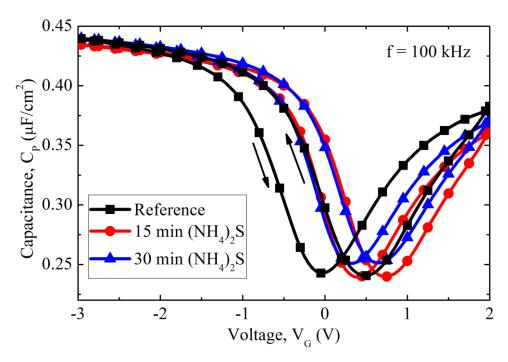

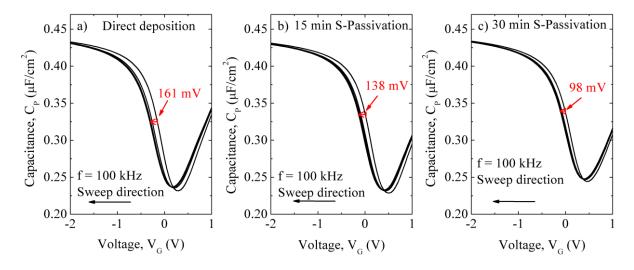

| 8.3.1        | Influence of Sulfur-Passivation on the Capacitance | ce-Voltage Characteristics of |

| German       | nium/Aluminum Oxide/Aluminum Metal-Oxide-Se        | miconductor Capacitors 122    |

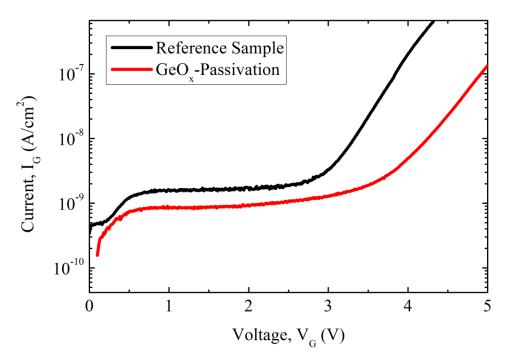

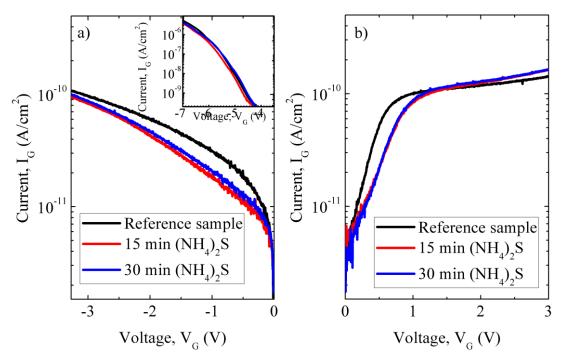

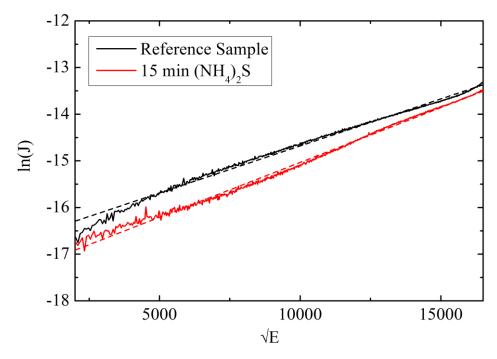

| 8.3.2        | Influence of Sulfur-Passivation on the Current     | -Voltage Characteristics of   |

| German       | nium/Aluminum Oxide/Aluminum Metal-Oxide-Se        | miconductor Capacitors 125    |

| 8.4 Cor      | nclusion                                           | 127                           |

| Concluding   | g Remarks                                          | 129                           |

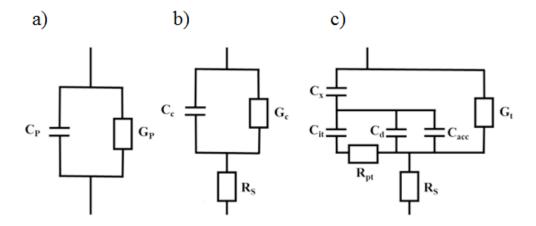

| Appendix: 7  | The Metal-Oxide-Semiconductor System               | 132                           |

| References . |                                                    | 144                           |

| Acknowledg   | gements                                            | 155                           |

| Curriculum   | 1 Vitae                                            |                               |

### **Acronyms and abbreviations**

ALD Atomic layer deposition

BHF Buffered hydrofluoric acid

BTBT Band-to-band tunneling

DIBT Drain induced barrier thinning

EOT Equivalent oxide thickness

FGA Forming gas annealing

GIDL Gate induced drain leakage

HF High frequency

ICP-RIE Induced coupled plasma-reactive ion etching

IHT Institut für Halbleitertechnik

IL Interfacial layer

ITRS International technology roadmap for semiconductors

LF Low Frequency

MBE Molecular beam epitaxy

ML Monolayer

MOS Metal-oxide-semiconductor

MOSFET Metal-oxide-semiconductor field effect transistor

NDR Negative-differential-resistance

QCE quantum confinement effect

RT Room temperature

SEM Scanning electron microscopy

SIMS Secondary ion mass spectrometry

SRH Shockley-Read-Hall

TAT Trap-assisted tunneling

TMA Tri-methyl-aluminum

VS Virtual substrate

A Device area

C<sub>D</sub> Depletion capacitance

C<sub>M</sub> MOS capacitance

C<sub>P</sub> Measured capacitance

C<sub>S</sub> Semiconductor capacitance

D Mesa diameter

D<sub>it</sub> Interface state density

d<sub>channel</sub> Channel thickness

d<sub>ox</sub> Oxide thickness

E<sub>G</sub> Bandgap

I<sub>ON</sub> Drive current

I<sub>OFF</sub> Leakage current

J<sub>A</sub> Area leakage current density

J<sub>P</sub> Perimeter leakage current density

k<sub>B</sub> Boltzmann constant

$N_A$  Acceptor doping concentration

N<sub>D</sub> Donor doping concentration

$N_S$  Source doping concentration

n<sub>i</sub> Intrinsic carrier concentration

P Device perimeter

p<sub>i</sub> Background doping concentration

q Elementary charge

R<sub>S</sub> Series resistance

SS Subthreshold swing

T Measurement temperature

T<sub>sub</sub> Substrate temperature

V<sub>DS</sub> Drain-Source voltage

V<sub>FB</sub> Flatband voltage

V<sub>G</sub> Gate-source voltage

V<sub>stress</sub> Presoaking voltage

W<sub>D</sub> Depletion width

w<sub>G</sub> Gate width

x Sn-content

ξ Electric field

ε<sub>o</sub> Vacuum permittivity

$\varepsilon_{\rm r}$  Relative permittivity

$\epsilon_{S}$  Semiconductor permittivity

τ Lifetime

$\lambda \hspace{1cm} \text{Tunneling barrier width}$

Al Aluminum

Al<sub>2</sub>O<sub>3</sub> Aluminum oxide

B Boron

Ge Germanium

$GeO_x$  Germanium oxide GeSn Germanium-tin

H<sub>2</sub>O<sub>2</sub> Hydrogen peroxide

S Sulfur Si Silicon

SiO<sub>2</sub> Silicon oxide

SiGe Silicon-germanium

Sb Antimony

Sn Tin

### Zusammenfassung

In den letzten Jahren zeigte sich ein wachsendes Interesse an Bauelementkonzepten wie Tunnel-Feldeffekttransistoren (TFETs), die auf dem quantenmechanischen Tunneln basieren. Der TFET konkurriert in Bezug auf Geschwindigkeit, Leistung und Fläche direkt mit dem Metall-Oxid-Halbleiter-Feldeffekttransistor (MOSFET). Der Injektionsmechanismus in TFET ist ein Band-zu-Band-Tunnel- (BTBT-) Strom, und der potentielle Vorteil des TFET liegt in seinen steilen Strom-Spannungs (IV) -Unterschwellwertcharakteristiken, die nicht wie im MOSFET durch die 60 mV / Dekade bei Raumtemperatur begrenzt sind. TFETs könnten bei niedrigen Versorgungsspannungen zwar potentiell besser arbeiten, aber die experimentellen Realisierungen dieses Bauelements bleiben noch hinter den Erwartungen zurück. Insbesondere ist eine Verbesserung des On-Stroms notwendig, um den MOSFET hinsichtlich seiner Leistungsfähigkeit zu übertreffen.

In dieser Arbeit wurden verschiedene Strategien zur Verbesserung der Leistungsfähigkeit von p-Kanal Germanium (Ge) TFETs experimentell untersucht. Modifikationen des Halbleitermaterials und Dotierungsprofile werden mit dem Ziel, die Tunnelwahrscheinlichkeit zu erhöhen und hohe On-Ströme zu erreichen, untersucht. Hierzu wurden vertikale TFETs konzipiert, hergestellt und charakterisiert. Die vertikalen Halbleiterstrukturen selbst wurden mittels Molekularstrahlepitaxie (MBE) hergestellt, und die vertikalen Bauelemente wurden unter Verwendung eines GAA- (Gate-all-around) -Geometrie-Herstellungsprozesses hergestellt.

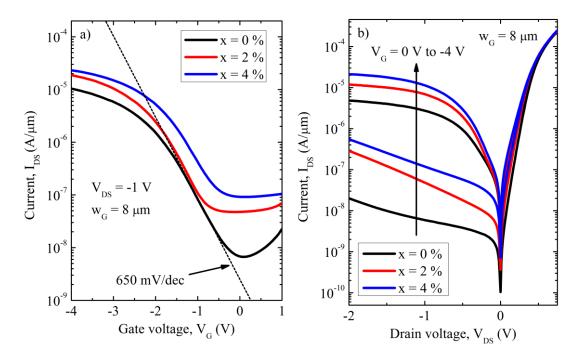

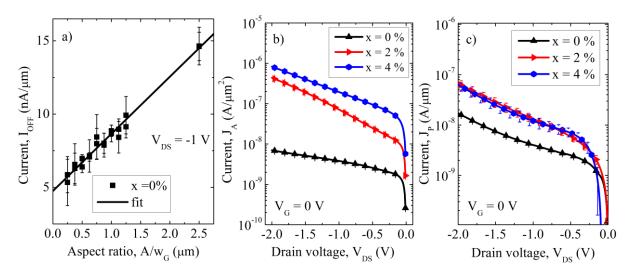

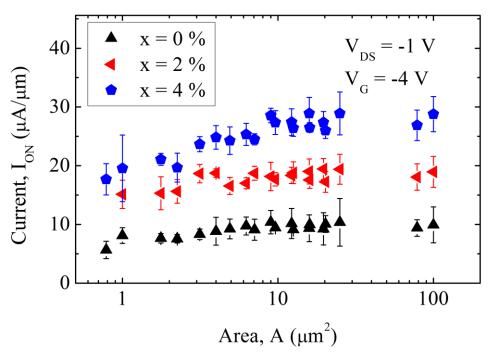

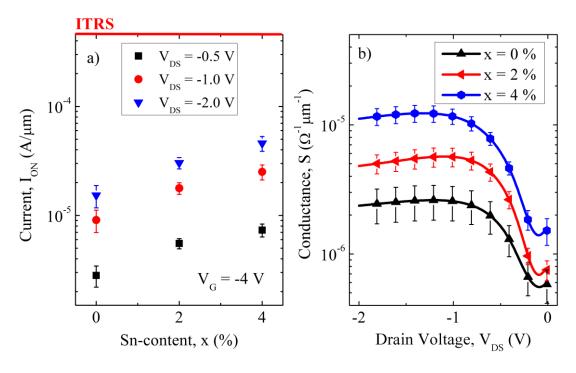

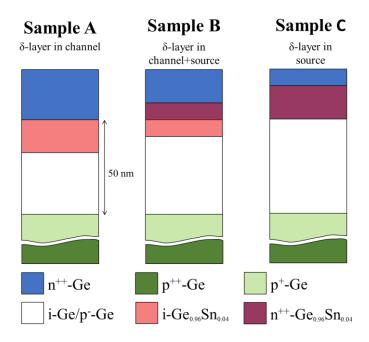

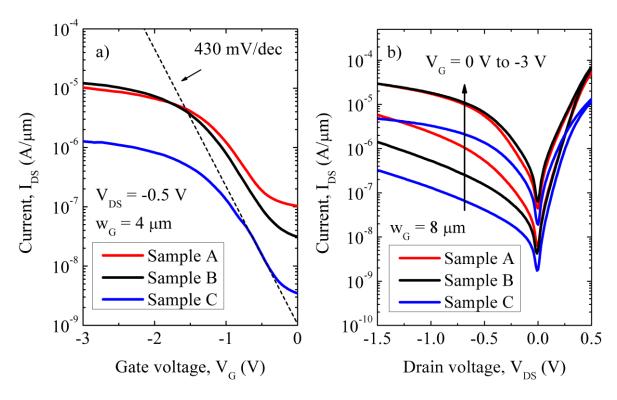

Es wird gezeigt, dass der On-Strom (Ion) effektiv durch die Einführung von Germanium-Zinn (GeSn) in den Kanal erhöht werden kann. Ein sukzessiver Anstieg von Ion wird beobachtet, wenn der Zinn (Sn) -Gehalt x in einem Germanium-Zinn (Ge1-xSnx) -Kanal von x = 0 % auf x = 2 % und x = 4 % erhöht wird. Dies liegt an der Verringerung der Bandlücke in Ge1-xSnx mit steigendem Sn-Gehalt, was die Tunnelwahrscheinlichkeit effektiv erhöht. Ferner wurde experimentell ermittel, dass, wenn die Schichtdicke von Ge0,96Sn0,04 auf 10 nm begrenzt ist, die genaue Positionierung dieser Ge0,96Sn0,04-Schicht relativ zum Source-Kanal-Übergang des TFETs deutliche Auswirkungen auf die Kennlinien des Bauelements hat: Ein hoher Ion wird erreicht, wenn sich diese Schicht vollständig innerhalb des Kanals befindet, während der Leckstrom (IOFF) reduziert wird, wenn diese Schicht vom Kanal in die Source verschoben wird. Eine Schwierigkeit beim Einbau von Ge1-xSnx in die p-Kanal-Ge-TFETs ist, eine hohe epitaxiale Qualität beizubehalten, wenn der Sn-Gehalt erhöht wird. Zusammen mit der Verringerung der Bandlücke wird gezeigt, dass das Einbringen von Sn die IoFF- und

Subschwellenschwingung (SS) der Bauelemente durch erhöhte Shockley-Read-Hall (SRH) - Erzeugung und Trap-Assisted-Tunneling (TAT) -Ströme verschlechtert. Dies stellt die Machbarkeit einer akzeptablen Leistung mit GeSn als Kanalmaterial in Frage. Basierend auf den Ergebnissen werden einige Verbesserungsstrategien diskutiert.

Es wurde herausgefunden, dass die Variation der Source-Dotierungskonzentration in p-Kanal-Ge-TFETs mit Gate-Source-Überlappung hauptsächlich die Unterschwellencharakteristika der Bauelemente beeinflusst. Eine höhere Steilheit wird mit zunehmender Dotierstoffkonzentration in der Source-Region erzielt. Es wird angenommen, dass diese Korrelation ein Ergebnis von TAT in der Source-Gate-Überlappungsregion ist. Im Gegensatz zu Ergebnissen aus veröffentlichten Simulationsstudien konnte für die untersuchten Dotierungsgrade keine Auswirkung der Dotierstoffkonzentration auf I<sub>ON</sub> identifiziert werden.

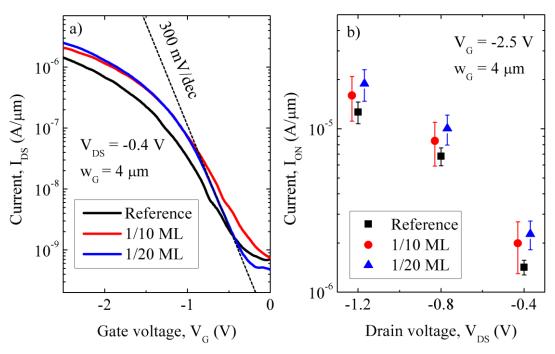

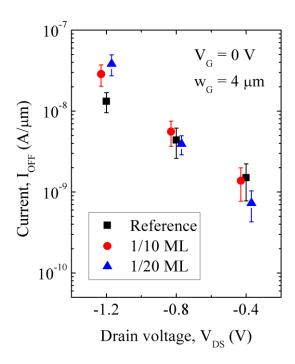

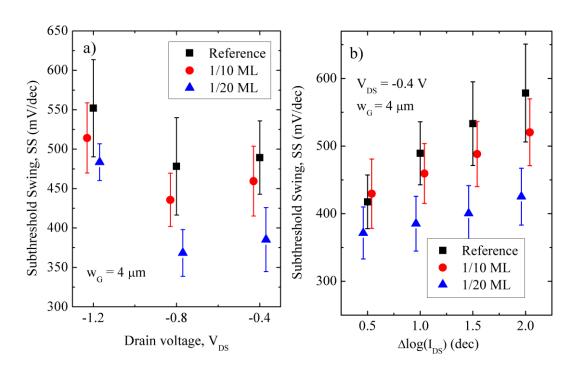

Eine MBE-Vorbelegungsstrategie von Antimon (Sb) wird untersucht, um steile Source-Dotierungsprofile in vertikalen p-Kanal-Ge-TFETs zu erhalten. Es ist ersichtlich, dass für eine Sb-Vorbelegung von 1/20 Monolagen (ML) sowohl I<sub>ON</sub> als auch SS verbessert sind. Dies wird dadurch erklärt, dass die Ausbreitung der Tunnelbarriere in die Source-Region reduziert wird, was zu einer Erhöhung der Tunnelwahrscheinlichkeit und Verbesserung der Bandpassfilterung führt. Die Verstärkung von I<sub>ON</sub> ist gering, aber die Vorbelegung lässt sich ohne Mehraufwand in den TFET-Herstellungsprozess integrieren und kann leicht mit anderen Strategien zur Verstärkung der On-Ströme von TFETs kombiniert werden. Die Ergebnisse deuten auch darauf hin, dass eine optimale Vor-Aufbau-Dotierung existiert.

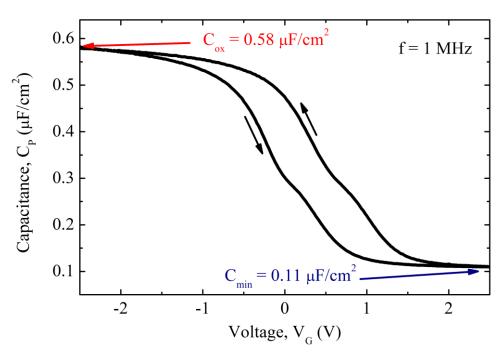

In dieser Arbeit werden auch das Aluminiumoxid (Al<sub>2</sub>O<sub>3</sub>), das als Gateoxid verwendet wird, und das Ge / Al<sub>2</sub>O<sub>3</sub> / Al-System untersucht. Eine Germaniumoxid (GeOx) -Passivierung durch Post-Plasma-Oxidation und eine Schwefel (S) -Passivierung durch wässrige Ammoniumsulfit-Lösungsbehandlung werden durch die Herstellung und elektrische Charakterisierung von MOS-Kondensatoren untersucht. Für die mit GeO<sub>x</sub> passivierte Probe wird eine Hysterese und eine Verschiebung der Flachbandspannung durch Akzeptor-Traps im Oxid erklärt. Eine allgemeine Parallelverschiebung der Kapazitäts-Spannungs- (C-V) -Kurve zu positiven Gate-Spannungen ist Indikator für ortsfeste negative Ladungen und ein O-reiches Al<sub>2</sub>O<sub>3</sub>. Es wird vorgeschlagen, dass diese O-reichen Regionen durch die Nach-Plasma-Oxidationsbehandlung induziert werden könnten. Temperaturabhängige Strom-Spannungs (I-V) -Kennlinien zeigen einen Schottky-Emissionsprozess als Haupttransportmechanismus durch das Oxid bei niedrigen elektrischen Feldern an.

Es wird beobachtet, dass der Effekt der S-Passivierung der Ge-Oberfläche sowohl die C-V-Hysterese als auch den Leckstrom in der Region mit niedrigem E-Feld reduziert. Die gemessenen Oxidkapazitäten zeigen auch, dass dies nicht auf Kosten einer Oxidverdickung geht.

### **Summary**

Recent years have shown a growing interest in device concepts based on quantum mechanical tunneling. The tunneling field effect transistor (TFET) is a device that competes directly with the metal-oxide-semiconductor field effect transistor (MOSFET) in terms of speed, power and area. The drive current injection mechanism in TFETs is a band-to-band tunneling (BTBT) current and the promise of the TFET lies in its steep subtreshold current-voltage (I-V) characteristics, which is not restricted by the MOSFET's 60 mV/dec limit at room temperature. TFETs could perform better at low supply voltages, but improvement of the drive current is necessary to outperform the MOSFET.

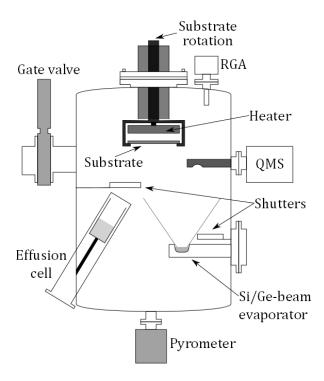

In this work different device tuning strategies for the p-channel germanium (Ge) TFET are studied. Modifications involving the semiconductor material and doping profiles are investigated with the aim of increasing the tunneling probability and achieving high drive currents. This investigation has been conducted through designing, fabricating and characterizing the vertical TFET structures. Vertical semiconductor structures were grown by means of molecular beam epitaxy (MBE), and the vertical devices were fabricated using a gate-all-around (GAA) geometry fabrication process.

It is shown that the drive current ( $I_{ON}$ ) can be effectively increased by the introduction of germanium-tin (GeSn) in the channel. A successive increase in  $I_{ON}$  is seen when increasing the tin (Sn)-content, x, in a germanium-tin (Ge<sub>1-x</sub>Sn<sub>x</sub>) channel from x = 0 % to x = 2 % and x = 4 %. This is due to the lowering of the bandgap, which effectively increases the tunneling probability. Furthermore, it is found that when  $Ge_{0.96}Sn_{0.04}$  is confined within a 10 nm delta-layer, TFET device performance can be tuned by shifting the position of this layer at the source-channel interface. A high  $I_{ON}$  is achieved when this layer is completely inside the channel, while the leakage current ( $I_{OFF}$ ) is reduced when this layer is shifted from the channel and into the source. A complicating factor with incorporating  $Ge_{1-x}Sn_x$  in the p-channel Ge TFETs is found to be the difficulty of maintaining a high epitaxial quality when increasing the Sn-content. Together with the lowering of the bandgap, this is shown to degrade the  $I_{OFF}$  and subthreshold swing (SS) of the device through increased Shockley-Read-Hall (SRH) generation and trap-assisted tunneling (TAT) currents. This further calls into question the feasibility of achieving acceptable performance with GeSn as channel material. Based on the results, some device performance strategies are discussed.

Varying the source doping concentration in p-channel Ge TFETs with gate-source overlap is found to mainly influence the subthreshold characteristics of the devices. Steeper

subthreshold characteristics is found with increasing source doping concentration. This correlation is believed to be a result of TAT in the source-gate overlap region. Contrary to results from published simulation studies, no effect of varying the source doping concentration on I<sub>ON</sub> could be distinguished for the doping levels investigated.

A MBE pre-buildup technique of antimony (Sb) is investigated as a means to achieve steep source doping profiles in vertical p-channel Ge TFETs. It is seen that for a Sb pre-buildup concentration of 1/20 monolayer (ML), both I<sub>ON</sub> and SS is improved. This is explained by that the extent of the tunneling barrier into the source region is reduced, leading to an increase of the tunneling probability and improvement of the band pass filtering. The boost in I<sub>ON</sub> is small, but the pre-buildup technique imposes no extra load onto the TFET fabrication process and can easily be combined with other strategies for boosting the drive current for TFETs. The results also suggests that an optimal pre-buildup doping exists.

In this work also the aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), which is used as gate oxide, and the Ge/Al<sub>2</sub>O<sub>3</sub>/Al system is studied. A germanium oxide (GeO<sub>x</sub>)-passivation achieved through postplasma oxidation and a sulfur (S)-passivation achieved through an aqueous Ammonium sulfite solution treatment, are both investigated through the fabrication and electrical characterization of MOS-capacitors. For the sample passivated with GeO<sub>x</sub>, a hysteresis and a shift in the flatband voltage is explained by acceptor traps in the oxide. A general parallel shift of the capacitance-voltage (C-V)-curve towards positive gate voltages indicates fixed negative charges and an O-rich Al<sub>2</sub>O<sub>3</sub>. It is suggested that these O-rich regions could be induced by the post plasma oxidation treatment. Temperature dependent current-voltage (I-V)-characteristics indicate a Schottky emission process as the main transport mechanism through the oxide at low electric fields.

The effect of S-passivation of the Ge surface is seen to reduce both the C-V hysteresis and the leakage current in the low E-field region. The measured oxide capacitances also reveal that this does not come at the expense of a thicker equivalent oxide thickness (EOT).

# **Chapter 1** Introduction

#### 1.1 Searching for a New Energy Efficient Switch

At the time of writing there are over 3 billion smartphone users in the world. Projections are made that those numbers will exceed 6.4 billion by the year 2021[1]. It is no exaggeration to say that the market of electronic devices has, and is continuing to, exhibit a unique growth, not seen the likes of in many other industries. The growth is partly a result of the improvement achieved for each new electronic device generation. Due to the new features and capabilities of the newest device generation, electronic devices are often acquired at a more frequent rate than the actual service lifetime of the devices. To keep up with this rapid development, however, considerable requirements are forced onto the electronic switches i.e. transistors, responsible for doing the job. Scaling down the transistors dimensions, has been the successful strategy used for over five decades to accomplish this task. This strategy has allowed to increase the transistor count on the chip, and hence increasing a processors computational power. For a long time scaling did also result in more energy efficient as well as faster switches. This made miniaturization a very advantageous approach. As the nanometer technology needed to realize these switches has grown extremely complex and expensive, we are now also seeing other reasons for why the scaling is becoming less advantageous than before. The devices are being pushed hard against their theoretical limits. This has made increasing the transistor count, but at the same time reducing the power consumption of each single transistor, a very difficult task. For a consumer this leads to some worrisome outlooks if not taken care of. Imagine if your portable electronic device needs constant recharging. It takes away its intended practicality. If the device, due to excessive power dissipation, is too hot to handle, this also limits its usefulness. In trying to solve this problem, scientific virtue and engineering ingenuity is called for. A new energy efficient switch is needed.

In this thesis an electronic switch that is based on quantum mechanical tunneling is presented. This device, the tunneling field effect transistor (TFET), takes advantage of the peculiar phenomenon that electrons can pass through a barrier if it is made sufficiently thin. Switching between on and off with the aid of tunneling has been shown to consume much less energy than other devices. A TFET could hence potentially outperform the existing and transistor era's long lived work horse, the metal-oxide-semiconductor field effect transistor (MOSFET), in terms of both speed and power as well as area. The TFET has, however, its own challenges to overcome before it can be accepted by the industry. Although the current flow

can be controlled in a very energy efficient way, the existence of a barrier still significantly reduces the current carrying-capacity. As a result the drive currents of TFETs is inferior to today's transistors. Solving this problem sets the backdrop for this thesis.

### 1.2 A Brief History of Germanium in Complementary Metal-Oxide-Semiconductor Technology

Germanium (Ge) is considered an exciting candidate for high-performance scaled complementary metal-oxide-semiconductor (CMOS) technology. Compared to silicon (Si), Ge has a smaller bandgap and higher and better balanced bulk hole and electron mobilities (see Table 1). This gives Ge the potential of replacing Si as the material of choice, as the computer technology is pushed up against the physical limitations of miniaturization. Although attracting much interest in the last decades for its exciting attributes, the emergence of Ge in the semiconductor technology is more of a revival. Ge actually has a history in the semiconductor industry as long as the industry itself. It was the earliest semiconductor pursued by the Bell Laboratories at the beginning of the transistor era [2]. Numerous breakthroughs in the field of semiconductor engineering have Ge in the leading role: the first commercial transistor [3], the first integrated circuit [4] and the first demonstration of a tunneling diode [5] to mention a few. However, in the history of the MOSFET and what evolved into the successful CMOS technology, Si has played the instrumental role. In addition to its abundance, one of the most important reasons for pursuing Si was because of the superior interface it formed with silicon oxide (SiO<sub>2</sub>) and the high quality thermal oxide [6]. Due to the thermal instability and chemical reactivity of germanium oxide (GeO<sub>2</sub>) with water, the Ge/GeO<sub>2</sub> system on the other hand was considered unfit for field effect devices. Ge was hence sidelined in the beginning years of the CMOS technology. Looking back at the computer chip era and dominance of the CMOS technology in the electronics industry today, one can understand the Si choice.

**Table 1** Properties of Si and Ge at 300 K. After [31].

| Semiconductor | Lattice  | Indirect | Direct  | Mobility    |         | Relative                                  | Intrinsic           |

|---------------|----------|----------|---------|-------------|---------|-------------------------------------------|---------------------|

|               | constant | bandgap  | bandgap | $(cm^2/Vs)$ |         | permittivity                              | carrier             |

|               | (Å)      | (eV)     | (eV)    | μn          | $\mu_p$ | $\varepsilon/\varepsilon_0=\varepsilon_r$ | concentration       |

|               |          |          |         |             |         |                                           | (cm <sup>-3</sup> ) |

| Si            | 5.43     | 1.12     | 3.4     | 1450        | 500     | 11.9                                      | 1.1010              |

| Ge            | 5.65     | 0.66     | 0.8     | 3900        | 1900    | 16.0                                      | 2·10 <sup>13</sup>  |

Between the 60's and beginning of the 80's the main focus of the CMOS technology was scaling down the well-functioning Si/SiO<sub>2</sub> system, rigorously following the scaling trend predicted by Gordon E. Moore [7]. Little attention was therefore given to alternative materials investigations during this period. This was, however, about to change. Although the scaling and miniaturization strategy was immensely fruitful and effective, concern were being voiced [8] about the physical and geometrical limitations awaiting in the near future. Also the cost due to the demands and constraints on the production facilities that came with the continued scaling, was growing with a worrisome rate [9]. This eventually led to the appearance of Ge in the field in the mid 80's. The accomplishment of low-temperature (< 700 °C) epitaxial growth of Si, allowed the effective joining of Si and Ge into silicon-germanium (SiGe) alloys [10]. SiGe alloys found its uses as channel material [11], but first and foremost as relaxed SiGe buffers for strained Si MOSFETS [12, 13]. Through strain or through alloying with Ge, an effectiv increase in carrier mobility compared to unaltered Si is achieved. SiGe therefore represented an alternative approach to improving device performance other than device dimension shrinking. Noteworthy industry breakthroughs followed. IBM was first out, revealing their SiGe technology in 1989, and a decade later introducing it into the industry's first standard, highvolume SiGe chip [14]. Intel followed soon after by introducing SiGe in their 90 nm process generation [15]. At the time SiGe had been introduced and accepted by the somewhat conservative semiconductor industry, the research community was eager to investigate the next natural step. Due to the high mobility of charge carriers, all Ge devices could potentially provide improved performance even compared to advanced strained Si and SiGe layers [2]. All Ge FETs devices were fabricated, characterized and reported [16, 17, 18]. Now, an extra focus was put on the major problem facing Ge based field effect devices in the first place: the unfavorable surface properties.

Simultaneously as Ge was being introduced into the field, the CMOS scaling and device shrinking also started demanding very thin  $SiO_2$  gate oxides thicknesses,  $t_{ox}$ . For very thin oxides,  $t_{ox} < 4$  nm, however, quantum mechanical tunneling through the oxide becomes a serious issue. In the beginning of the 2000's the leakage current through the  $SiO_2$  gate oxide started increasing 100 fold for each process generation [19]. The solution to this problem was found in high- $\kappa$  dielectrics, which in this context are defined as insulators that have a higher relative permittivity than  $SiO_2$ . They could offer a larger physical thickness, but with the same equivalent capacitance as that of a much thinner  $SiO_2$  layer. Although concern were voiced about introducing a new high- $\kappa$  material into the gate stack and the CMOS technology, by 2007 both Intel [19] and IBM [20] had announced that they would replace  $SiO_2$  with the high- $\kappa$

material hafnium oxide (HfO<sub>2</sub>) for the 45 nm process generation. Now with the departure from SiO<sub>2</sub> as gate oxide of choice, the importance of the superior Si/SiO<sub>2</sub> semiconductor-oxide system became redundant. From this point of view, the argument of sticking with Si as a channel material lost its significance.

Which material system and device concept will eventually replace the Si MOSFET, is yet to be determined, as many exciting device concepts and new materials have entered the race [21]. The first experimental demonstration of an all Ge CMOS circuit with an Al<sub>2</sub>O<sub>3</sub> gate oxide has recently been reported [22]. But also a recently presented TFET using Ge as a source material has gained attention due to its extremely steep turn-on characteristics [23]. Both of these two maybe marking, in separate ways, the beginning for a new or alternative era for the CMOS technology. However, one can expect Ge to be a major influential player, as creative scientist and engineers struggle to sustain Moore's Law in the years that lie ahead.

#### 1.3 History of the Tunneling Field Effect Transistor

The history of the tunneling field effect transistor, can be traced all the way back to 1952 and a work conducted by O. M. Stuetzer [24]. In an experimental study, he demonstrated a surface conductivity control when an electrode (Gate) was placed in the neighborhood of a pnjunction. The device, which he named *junction fieldistor*, contained the basic elements of a TFET. This device also demonstrated both n-type and p-type transistor behavior, depending on the positioning of the gate electrode with respect to the pn-junction. This is a unique characteristic of the TFET. The reported surface conductivity control was, however, not attributed to quantum mechanical tunneling. This having the natural explanation that tunneling in semiconductors at the time was not yet an established concept. It is true that the idea of electrons traveling from one energy band to another, had been theorized by Clarence Zener already in 1934 [25]. However, the theory of Zener was derived to explain the electrical breakdown of dielectrics. It was later found that Zener's breakdown theory was applicable also for semiconductors. *Zener tunneling* and *Zener effect* were later introduced and are today commonly used terms to describe the tunneling in reverse biased pn-junctions.

A tunneling breakthrough came in 1958, when Leo Esaki reported on a new phenomenon in heavily doped Ge pn-junctions [5]. He discovered an anomalous current-voltage (I-V) characteristic in the forward direction. A negative differential resistance (NDR) region was observed, were the current decreased with increasing voltage bias. Esaki was able to explain the behavior by electron band-to-band tunneling (BTBT). Simplified band diagram schematics explaining the I-V characteristics of such a junction are shown in Figure 1. The discovery later

earned Esaki the 1973 Nobel Prize in physics [26]. Together with the theoretical work of Evan O. Kane [27, 28], Esaki's discovery laid the foundation for a better understanding of tunneling in semiconductor structures.

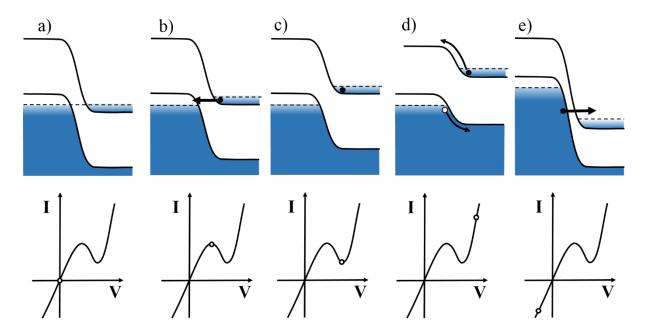

**Figure 1** Simplified band diagrams and the corresponding I-V characteristics explaining the current flow in a tunnel diode for different voltage biases. **a)** Thermal equilibrium, zero bias. No current is flowing. **b)** For a small forward voltage bias, electrons in the conduction band of the degenerate nregion tunnel into empty states in the valence band of the p-region. **c)** At higher positive bias the tunneling current decreases as the overlap of the energy bands is reduced and leading to a NDR. **d)** Diffusion current dominate at high forward bias. **e)** For negative bias electrons tunnel from valence band and into the conduction band. This is often referred to as Zener tunneling. After [29].

The tunnel diode, sometimes referred to as *Esaki diode*, was also introduced into the industry. It showed great promise as an oscillator and switching element at high frequencies [30]. Other conventional semiconductor devices would, however, in the course of time outperform and replace the tunnel diode for these functional areas [31]. The tunnel diode was therefore pushed into niche markets. In the fields of semiconductor science and engineering, the BTBT phenomenon continued to fascinate. Although it took some time, this eventually led to the appearance of new device concepts. The first three terminal devices actively addressing and taking advantage of the BTBT phenomenon was proposed by Quinn et al. in 1978 [32]. Their n-MOSFET structure with a heavily doped p-source was designed to yield information about subband splittings of the surface inversion layer. A transistor device concept, with the similar structure as that of Quinn was proposed by Baba [33]. This device was given the name *surface tunnel transistor* (STT). In addition to gallium-arsenide (GaAs) which was used in the

first STT, also Si [34], Si-on-insulator [35] and indium-gallium-arsenide (In<sub>0.53</sub>Ga<sub>0.47</sub>As) [36] STTs were demonstrated in the course of the 1990's. Many of the early three terminal tunneling devices were focusing on the forward characteristics, and controlling the NDR of the tunnel diode with a gate. However, the Si STT demonstrated by Reddick and Amartunga in 1995 [37], also showed the BTBT current under reverse bias could be controlled. The first vertical Si TFET was proposed and fabricated by Hansch et al. in 2000[38].

In the early 2000's the TFET's potential as a low-power switch became recognized. This followed the realization that the I-V characteristics in the subthreshold region of a TFET was not restricted by the MOSFET's 60 mV/dec subthreshold swing limit at room temperature [39]. This interest got further vitalized by the experimental demonstrations of a devices surpassing this limit by Appenzeller et al. in 2004 [40]. Many groups had at this time directed their focus on the TFET, and soon after more sub 60 mV/dec TFETs were demonstrated [41, 42].

With the attention given due to the obvious potential of the TFET, the challenges of the device became more and more evident towards the end of the 2000's. Although showing great off-state and turn-on characteristics, the drive current was still inferior to that of a MOSFET. The favorable steep turn-on characteristics were also only demonstrated in a narrow and low current regime. The recent years of TFET research, has been revolving around how best to tackle these problems. As with most scientific and engineering challenges, many different solutions have been proposed. In this rapidly advancing field, a wide variety of TFETs, with different material systems and device geometries, are represented in the published TFET studies.

The current status and state-of-the-art of TFETs, is given in the end of this chapter. Some theoretical background will, however, first be given. This can be useful in order to better understand the ideas behind the different TFET concepts, as well as the work presented in this thesis.

#### 1.4 Theoretical Background

The TFET, like the MOSFET, is a three terminal electronic switch. When a voltage is applied between the drain and source contacts, the current flow between them is controlled by the voltage applied to a third terminal, the gate. Both p- and n-channel TFETs are realizable. This offers complementary TFET technology for logic operations, analogous to CMOS technology. TFETs can also be incorporated in industrial CMOS process flow, without additional process steps. The TFET bears a strong resemblance to the MOSFET in this regard. A fundamental difference, with respect to the MOSFET can, however, be found in the mechanism with which

the gate controlled current is flowing and turned on and off. This gives the TFET some unique advantages. In this chapter the operating principles of a TFET will be explained. Both the TFETs potential and challenges will be highlighted.

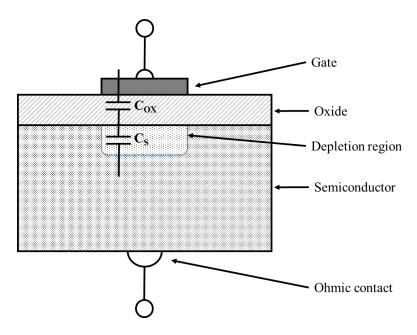

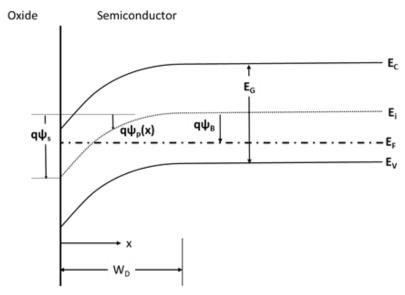

Understanding the function of a TFET require some basic understanding of energy band theory for semiconductors. The reader is directed to introductory books on the topic like those of Sze and Ng [31] and Schroeder [43], as this topic is too extensive to cover here. Information about the MOS capacitor system and the field effect is contained in Appendix.

#### 1.4.1 Power Consumption of a Logic Element

The TFET is regarded as a candidate for replacing the MOSFET due to its low power operation capabilities. It is therefore natural to start by looking at the power dissipation in digital CMOS circuit, which is given by the following expression [44]:

$$P_{tot} = C_L \cdot V_D^2 \cdot f \cdot \alpha + I_{SC} \cdot V_D + V_D \cdot I_{OFF}.$$

(1)

Here, the first term represents the switching component and describes the power dissipated when switching between the on and off state. It is the product of a load capacitance,  $C_L$ , the supply voltage,  $V_D$ , the clock frequency, f, and an activity factor,  $\alpha$ . The second term is the short circuit term when both p-MOSFET and n-MOSFET are simultaneously active and a short circuit current  $I_{SC}$  is flowing. The third term is the static power consumption. This term describes the power dissipated due to the presence of a non-zero leakage current,  $I_{OFF}$ , when the transistor is turned off. When examining (1) it is clear that the most effective way of reducing the power dissipation would be to reduce  $V_D$ . A reduction of  $V_D$  should, however, not compromise the drive current in the on-state of the transistor,  $I_{ON}$ . Transistors in integrated circuits work together, and the output of one stage of transistors can be used as input of the next stage. In this case the time it takes to charge  $C_L$  depends directly on  $I_{ON}$ .  $I_{ON}$  therefore determines the maximum speed of the circuit. This means that reducing  $I_{ON}$  in most cases leads to unacceptable increase in delay time and result in slow operation.

From these requirements an important characteristic of the transistor should be introduced: its rate of current change with respect of the applied gate voltage. This figure of merit is often quantified by the subthreshold swing (SS). The SS is a measure of how much voltage needs to be applied to the gate terminal to induce a change in drain current by one order of magnitude. The average SS of a transistor can be defined as [45]:

$$S_{\text{avg}} = \frac{V_{\text{D}}}{\log\left(\frac{I_{\text{ON}}}{I_{\text{OFF}}}\right)}.$$

(2)

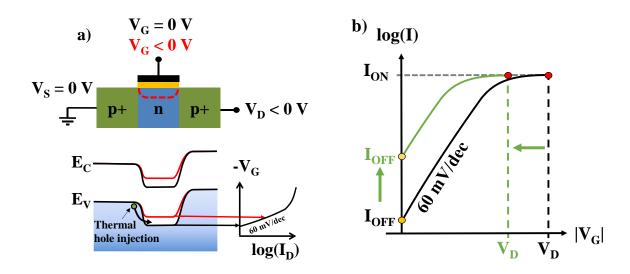

The ideal switch would have a step function response, where  $SS \rightarrow 0$  mV/dec. However, the physics involved in the switching process, in addition to the technological challenges incurred when fabricating an ideal device, prevents this limit from being reached. For a MOSFET, a theoretical limit exist for the lowest achievable SS. This limit originates from the switching mechanism and the thermal injection process of charge carriers over the gate controlled barrier (see Figure 2a). At room temperature this limit is 60 mV/dec [31]. The consequence of this limit for the SS when scaling the voltage  $V_D$  is seen in Figure 2 b. As  $I_{ON}$  should remain constant,  $V_D$ -scaling of a MOSFET leads to a parallel shift of the transfer characteristics (green) with respect to the initial characteristics (black). This leads to at least a tenfold increase in  $I_{OFF}$  for every 60 mV of  $V_D$  reduction. The static power dissipation in (1) therefore increases when reducing  $V_D$ .

**Figure 2 a)** Schematic illustration of a p-type MOSFET. The energy band diagrams are shown below for two different gate biases. The thermal injection of holes from source into the channel, limits the SS to 60 mV/dec at room temperature. **b)** V<sub>D</sub> scaling of the MOSFET. A tenfold increase in I<sub>OFF</sub> results for every 60 mV reduction of V<sub>D</sub>. The static power dissipation as a results increases.

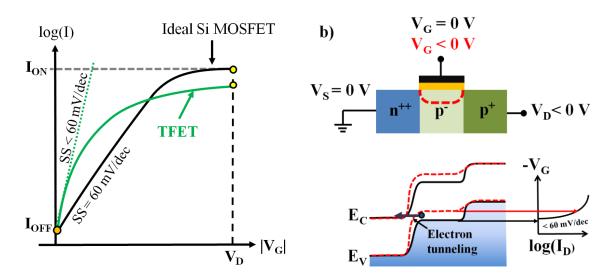

The inability to surpass this limit is starting to make its presence, as MOSFETs approaching the 60 mV/dec SS limit are already in the market. This has intensified the search for what is referred to as *steep slope* switches: switches with SS < 60 mV/dec (see Figure 3a). One of these proposed switches is the TFET.

#### 1.4.2 Tunneling Field Effect Transistor: Operating Principles

The TFET as a device concept is based on a reversed biased pin diode and the tunneling phenomenon, which was briefly introduced in section 1.3. When the TFET is turned on, the TFET behaves like a tunneling diode in reverse bias mode. A current flows when electrons tunnel from valence band and into the conduction band. This BTBT mechanism, often referred to as *Zener tunneling*, is hence used to attain a drive current in TFETs. However, to prevent this current from flowing in the off-state, the TFET structure differs from the tunneling diode by an intrinsic or lightly doped region which is sandwiched between the high n- and p-doped regions. This region blocks the tunneling current by widening the tunneling barrier. It therefore ensures a low Ioff. To enable to switch between the on and off states, the intrinsic region is gated and serves as the channel region. When applying a gate bias, the energy bands in the channel region are manipulated through the field effect. At sufficient gate bias the energy bands overlap and Zener tunneling is engaged. A p-channel TFET with the corresponding band diagram schematics is shown in Figure 3b. At the onset of tunneling, an ideal TFET shows a very steep I-V relationship which is not physically limited to the 60 mV/dec MOSFET limit at room temperature.

**Figure 3 a)** A TFET can have a SS < 60 mV/dec at room temperature and therefore offer the possibility of scaling the supply voltage without increasing the leakage current. The  $I_{ON}$  of today's TFETs are, however, still inferior to the MOSFET. b) Schematic illustration of a p-channel TFET structure. The energy band diagrams are shown below for two different gate biases. The injection mechanism for a TFET is BTBT of electrons (indicated with an arrow). The BTBT current is activated above a certain gate voltage corresponding to when the channel valence band is above the source conduction band. This switching mechanism offers the potential of steep slope IV-characteristics.

Both p-channel and n-channel TFET have similar pin diode structures. Asymmetric doping profiles, where source doping is higher than the drain doping, should however be used to suppress tunneling at the drain-channel interface [46]. A TFET with symmetric doped pin layer will exhibit ambipolar behavior, since applying a gate bias with opposite polarity can create a tunneling junction and induce current flow at the drain-channel interface. This ambipolarity can also lead to increased leakage current also for zero gate bias. Other suggested device strategies for reducing the tunneling at the drain-channel interface includes structures with gate-drain underlap [47], heterogeneous gate oxide [48] and heterojunction TFETs [49].

#### **1.4.3** Zener Tunneling Current

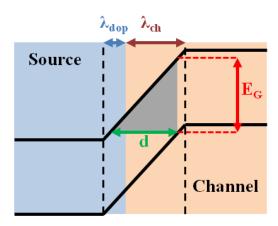

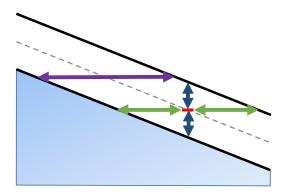

To analyze the Zener tunneling current in a TFET, one first has to find an expression for the BTBT probability at the channel-source interface. Tunneling of an electron through the forbidden energy gap is analogous to a particle tunneling through a potential barrier. The potential barrier across a pn-junction can be approximated by a triangle, see Figure 4. The height of the barrier equals the bandgap  $E_G$  of the semiconductor and tunneling width d is proportional to the tunneling screening length,  $\lambda$ . The tunneling screening length is composed of two components,  $\lambda = \lambda_{dop} + \lambda_{ch}$ . The length  $\lambda_{dop}$  is the part which is extended into the source region.  $\lambda_{dop}$  therefore depends on the doping abruptness as well as the doping level.

**Figure 4** The tunneling barrier at the channel-source interface can be approximated by a triangular barrier (gray area). The height of the tunneling barrier equals the materials bandgap  $E_G$ . The spatial width of the tunneling junction is determined by the sum of the screening length in the source  $\lambda_{dop}$  and the channel  $\lambda_{ch}$ , respectively.

In general a high source doping will reduce  $\lambda_{dop}$ . The length  $\lambda_{ch}$  is the part of the width of  $\lambda$  extended into the channel and is strongly dependent on the electrostatic control of the gate. The

tunneling probability through a triangular barrier with a uniform electric field  $\xi$  can be given by the Wentzel-Kramers-Brillouin (WKB) approximation [31]:

$$T_{WKB} \approx \exp\left(-\frac{4\cdot\sqrt{2\cdot m^*\cdot E_G^3}}{3\cdot q\cdot \hbar\cdot \xi}\right).$$

(3)

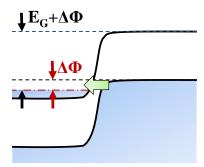

Here  $m^*$  is the reduced effective mass, which averages both the electron and hole effective masses. In (3) a high electric field, low effective mass and narrow bandgap is assumed so that the effect of the transverse energy states on the tunneling probability can be neglected [50]. Only electrons within a certain energetic interval,  $\Delta\Phi$ , contribute to current flow (see Figure 5). The TFET is therefore said to work as an energy filter, only allowing electrons within  $\Delta\Phi$  to flow.

**Figure 5** Band diagram of a p-channel TFET with a degenerate n-type source doping in the on-state. Only electrons within the interval  $\Delta\Phi$  contribute to the current flow. From the figure one can see that the degeneracy in the n-region, although reducing the tunnel barrier, also reduces  $\Delta\Phi$  and can hence limit the current flow.

Now with an expression for the tunneling probability, the total current density can be found by integrating over the energy interval  $\Delta\Phi$ :

$$J = \frac{2 \cdot q}{h} \cdot T_{WKB} \int_0^{\Delta \Phi} [f_S(E) \cdot f_D(E)] dE.$$

(4)

Here  $f_{S,D}(E)$  is the source and drain fermi-dirac distribution functions, respectively. Through rigorous manipulation of (4) the following result is obtained for the tunneling current [28, 31, 50]:

$$J = \frac{\sqrt{2 \cdot m^*} \cdot q^3 \cdot \xi \cdot \Delta \Phi}{8 \cdot \pi^2 \cdot \hbar^2 \cdot \sqrt{E_G}} \exp\left(-\frac{4 \cdot \sqrt{2 \cdot m^* \cdot E_G^3}}{3 \cdot q \cdot \hbar \cdot \xi}\right). \tag{5}$$

The electric field  $\xi$  in this expression can be approximated by:

$$\xi \approx \frac{E_G}{q \cdot d} \approx \frac{E_G + \Delta \Phi}{q \cdot \lambda}.$$

(6)

As a major challenge for TFETs is its low tunneling current, the expression in (5) is used as the starting point for many of the TFET performance tuning strategies and state-of-the-art TFETs, which will be reviewed at the end of this chapter. In general, we see from (5), that to increase the current, the exponential term should be made close to unity. With respect to material properties, this necessitates a low bandgap as well as low effective mass. Similarly, the tunneling width  $\lambda$  should be minimized in order to ensure a high transparency of the tunneling barrier.

The indirect tunneling from band-to-band in semiconductors like Si and Ge, requires phonon-assistance to conserve the momentum of the process. Although derived for direct semiconductors, the analytical expression in (5) has been shown to be in good agreement with measured reverse biased heavily doped Ge pn-junctions [51]. The phonon assistance needed for indirect semiconductors, however, significantly lowers the tunneling probability.

Note that (5) does not contain any thermal energy term  $(k_B \cdot T/q)$ , and has therefore a weak temperature dependence, mainly originating from the temperature dependence of  $E_G$ . The phonon-assistance needed for indirect tunneling, however, introduces an additional temperature dependence in indirect semiconductors compared to direct semiconductors.

#### 1.4.4 Subthreshold Swing of Tunneling Field Effect Transistors

The SS has already been briefly introduced, and is the parameter most often used to quantify the steepness of the transfer characteristics for a field effect devices. It is defined as:

$$SS = \left(\frac{dlog(I_{DS})}{dV_G}\right)^{-1},\tag{7}$$

where  $I_{DS}$  is the drain-source current,  $V_G$  the gate voltage and SS is given in mV/dec. The SS of a TFET is one of the attributes which makes it such an interesting device concept. For a MOSFET the  $I_{DS}$ - $V_G$  relationship is well known and SS is given by [31]:

$$SS_{MOSFET} = ln(10) \cdot \left(\frac{k_B \cdot T}{q}\right) \cdot \left(1 + \frac{C_D}{C_{OX}}\right). \tag{8}$$

Here  $C_D$  is the depletion layer capacitance and  $C_{OX}$  the oxide capacitance. (8) represents the ideal SS, where interface defects and other unidealities degrading the SS are not considered. The  $C_D/C_{OX}$  term can be minimized by reducing the oxide thickness. If excellent electrostatic control of the gate is achieved, this term can be neglected, and the minimum obtainable SS for a MOSFET becomes:

$$SS_{MOSFET} = ln(10) \cdot \left(\frac{k_B \cdot T}{q}\right) \sim 60 \text{ mV/dec}$$

(9)

at room temperature.

An expression for the SS of a TFET can be found through taking the derivative of (5):

$$SS = \left(\frac{\partial \log(J_{DS})}{\partial V_{G}}\right)^{-1} = \ln(10) \cdot \left(\frac{1}{\Delta \Phi} \cdot \frac{\partial \Delta \Phi}{\partial V_{G}} + \frac{\xi + b}{\xi^{2}} \cdot \frac{\partial \xi}{\partial V_{G}}\right)^{-1}.$$

(10)

Where:

$$b = \frac{4 \cdot m^{*1/2} \cdot E_G^{3/2}}{3 \cdot q \cdot \hbar}.$$

(11)

We see that there are two terms in the denominator of (10) which should be maximized to achieve a low SS. These terms can be thought to represent two different switching mechanisms [52]. The first term is dominant if the tunneling probability is close to unity and changes little with respect to gate voltage. For a TFET with good electrostatic control we have:

$$\frac{\partial \Delta \Phi}{\partial V_G} \sim q. \tag{12}$$

The SS originating from this term therefore reduces to:

$$SS \approx \frac{\ln(10)}{g} \cdot \Delta\Phi. \tag{13}$$

In this expression, SS increases linearly with  $V_G$  and allow for vanishing SS for  $\Delta\Phi \to 0$ . This is in contrast to the MOSFET, where SS is almost completely independent of gate voltage.

When having an energy band diagram in mind, this switching mechanism can be thought of as the vertical shift of the energy bands and the band overlap dependence of  $V_G$ .

The second term in (10) is dominating if the tunneling probability is small, but varying rapidly with gate voltage. In this case, the switching mechanism is due to gate voltage manipulation of the tunneling width and the junction electrical field (horizontal movement of energy bands). This can be calculated to [53]:

$$SS \approx \ln(10) \cdot \frac{3 \cdot q \cdot \hbar \cdot (\Delta \Phi + E_G)^2}{4 \cdot \lambda \cdot \sqrt{2 \cdot m^*} \cdot E_G^{3/2}}.$$

(14)

Due to the quadratic ( $\Delta\Phi$ +E<sub>G</sub>) dependence, we can see that the expression for SS in (14) changes more rapidly with gate voltage than the term in (13). It also does not vanish for  $\Delta\Phi \rightarrow 0$ , but can be made small through tuning the parameters  $\lambda$ , E<sub>G</sub> and m\*. Comparing (14) and (5) we, however, see that there exists a tradeoff between achieving steep SS and high I<sub>ON</sub>, with respect to  $\lambda$  and m\*.

The SS in (13) allows for a larger gate voltage range for which SS < 60 mV/dec, compared to (14). When designing a device, this type of switching is therefore the more attractive of the two. In practice, however, the two contributions are coupled and cannot be engineered independently.

#### 1.4.5 Leakage Current Mechanisms in Tunneling Field Effect Transistors

In an ideal switch, no current flows when it is in the off-state. Real devices, on the other hand, will always exhibit some degree of carrier conduction. Different types of transport mechanisms can contribute to leakage currents in TFETs. The type of contributions present and their magnitude depend on the material, device structure and geometry as well as temperature and biasing conditions. In the following section the most common leakage current mechanisms will be introduced.

#### 1.4.5.1 Diffusion Current

Ideally the leakage current of a TFET should be dictated by the diffusion current of the reverse biased diode. An expression for the saturated diffusion current is given by [31]:

$$J_0 = q \cdot \left(\frac{D_p}{L_p \cdot N_D} + \frac{D_n}{L_n \cdot N_A}\right) \cdot n_i^2. \tag{15}$$

Here  $D_p$  and  $L_p$  are the diffusion constant and diffusion length for holes in the n-region, and  $D_n$  and  $L_n$  are the diffusion constant and diffusion length for electrons in the p-region. The diffusion current under reverse bias is almost completely independent of drain-source bias. As both source and drain doping levels are high, the diffusion barrier for a TFET is very high. This usually ensures a very low diffusion current at room temperature for TFETs. The quantities D, L and  $n_i$  are all temperature dependent, and the temperature dependence of the diffusion current is given by [31]:

$$J(T) \propto T^{\gamma/2} \cdot \left[ T^{3/2} \cdot \exp\left( -\frac{E_G(T)}{2 \cdot k_B \cdot T} \right) \right]^2 = T^{3+\gamma/2} \cdot \exp\left( -\frac{E_G(T)}{k_B \cdot T} \right). \tag{16}$$

Here  $\gamma$  is an integer. In the last expression in (16) the temperature dependence of the polynomial term is negligible compared to the exponential term. Diffusion currents therefore have a temperature dependence with activation energy close to bandgap,  $E_A \sim E_G$ . At high temperatures diffusion currents usually become dominant due to this strong temperature dependence.

#### 1.4.5.2 Shockley-Read-Hall Generation Current

Crystal defects either in the bulk or at the surface can constitute trap states within the forbidden bandgap of the semiconductor. These trap states allow generation of electron-hole pairs to take place within the depletion region (see Figure 6) and contribute to a current flow. The generation rate,  $U_{SRH}$ , can be described by Shockley-Read-Hall theory [54, 55].  $U_{SRH}$  is maximized for trap levels with energy  $E_t$  close to the intrinsic fermi level  $E_i$ ,  $E_t = E_i$ . These midgap trap states are therefore the most effective generation centers. Considering only these traps an expression for the generation rate is given by [31]:

$$U_{SRH} = -\left(\frac{\sigma_p \cdot \sigma_n \cdot v_{th} \cdot N_t}{\sigma_n \cdot (1 + n/n_i) + \sigma_p \cdot (1 + p/n_i)}\right) \cdot n_i = -\frac{n_i}{\tau_g}.$$

(17)

Here  $N_t$  is the number of traps,  $v_{th}$  is the thermal velocity and  $\sigma_{p,n}$  is the electron and hole capture cross sections, respectively.  $\tau_g$  is the expression inside the brackets and is the generation carrier lifetime. The total generation current is proportional to the diode depletion layer width  $W_D$ :

$$J_{ge} \approx q \cdot U_{SRH} \cdot W_{D} = -\frac{q \cdot n_{i}}{\tau_{g}} \cdot W_{D}.$$

(18)

As W<sub>D</sub> is dependent on the applied reverse bias, it is expected that:

$$J_{ge} \propto \sqrt{\Psi_{bi} - V} , \qquad (19)$$

for abrupt junctions. Here  $\Psi_{bi}$  is the junction built in potential. The temperature dependence of SRH generation current is governed by the temperature dependence of  $n_i$ , if the generation lifetime is a slowly varying function of temperature:

$$J_{ge}(T) \propto n_i(T) \sim T^{3/2} \cdot \exp\left(-\frac{E_G(T)}{2 \cdot k_B \cdot T}\right). \tag{20}$$

The activation energy of a SRH leakage current is therefore close to half the materials bandgap  $E_{G.}$

#### 1.4.5.3 Tunneling Leakage Currents

The tunneling of electron through the bandgap used as drive current mechanism in TFET can also contribute to significant carrier transport in the off state, especially for devices with short intrinsic channel region and poor electrostatic gate control of the body. Leakage current due to Zener tunneling can be described by a similar expression as to that given in (5).

**Figure 6** Band diagram showing different leakage current mechanisms. When traps are present in the bandgap, both SRH scattering processes involving mid gap traps (blue arrow), and TAT events (green arrow) increases. A SRH process has a strong temperature dependence, while tunneling process has a strong electric field dependence. When the channel width is small and the electrostatic gate control of the body is poor, BTBT (purple arrow) can take place even in the off state of the transistor.

Traps can also lead to increased tunneling currents due to trap assisted tunneling (TAT). TAT is the tunneling between energy bands and trap states within the bandgap (see Figure 6). The two leakage mechanisms, SRH and TAT, often take place simultaneously. The combined leakage current due to these two mechanism can be described by the Hurkx model [56]. In this model the SRH constant,  $U_{SRH}$ , in (18) is replaced by  $U_{trap}$ :

$$U_{\text{trap}} = (1+\Gamma) \cdot U_{\text{SRH}}. \tag{21}$$

Here  $\Gamma$  is the electric field enhancement factor, which is given by the integral:

$$\Gamma = \frac{E_{\mathrm{T}}}{k_{\mathrm{B}} \cdot \mathrm{T}} \int_{0}^{1} \exp\left(\frac{E_{\mathrm{T}}}{k_{\mathrm{B}} \cdot \mathrm{T}} \cdot \mathbf{u} - \frac{4}{3} \cdot \frac{\sqrt{2 \cdot \mathbf{m}^{*} \cdot E_{\mathrm{T}}^{3/2}}}{q \cdot \hbar \cdot |\xi|} \cdot \mathbf{u}^{3/2}\right) d\mathbf{u}. \tag{22}$$

Here  $\xi$  is the electric field and  $E_T$  is the trap energy level, which equals  $E_G/2$  for midgap traps. At low electric fields  $\Gamma$  is close to zero and the current is simply given by (18). At high electric fields the tunneling events will dominate as  $\Gamma$  increases.

The temperature dependence of a TAT process is dependent on which of the two processes, tunneling or SRH, is dominating. At low electric fields, the SRH mechanism is usually dominating which as explained above results in an activation energy equal to  $E_G/2$ . It can, however, become significantly lower when tunneling is dominating at higher electric fields.

As tunneling has a strong electrical field dependence, everything that modulates the electrical field can alter the leakage tunneling rate. For TFETs with short channels and poor electrostatic control of the gate, a dependence of tunneling leakage with the drain-source bias can be seen. This effect is often referred to as drain induced barrier thinning (DIBT), and is due to the modulation of the drain-to-source tunneling barrier width with respect to the drain-source bias.

#### 1.4.5.4 Gate Oxide Leakage Currents

Gate oxide leakage is a shared problem for most field effect devices with aggressively scaled MOS systems. Ideally the energy barrier by the insulating gate oxide should be so large that they prevent the free flow of carriers from the metal to the semiconductor or vice versa. In real insulators on the other hand some degree of carrier conduction will be present at sufficiently high electrical field or temperature. Especially tunneling through the oxide has become a problem as the oxide thickness is scaled down to meet the requirements of modern CMOS technology. The gate oxide leakage can be suppressed by increasing the physical oxide thickness. This however degrades the gate control, as it reduces the total MOS gate capacitance. To omit this problem high- $\kappa$  materials, materials with dielectric constant larger than that of SiO<sub>2</sub>,  $\kappa > \kappa_{SiO2} = 3.9$ , have become standard in CMOS technology. More information of the leakage current in a MOS-capacitor system is given in Appendix.

#### 1.4.5.5 Gate Induced Leakage Currents and Ambipolarity

Gate induced leakage currents are due to tunneling events taking place in the drain region or at the drain-channel interface of the device. Tunneling at the drain-channel interface, is a unique and often encountered problem for the TFET. This is often referred to as *ambipolar leakage* and is a consequence of the similar pin structures of p- and n-channel TFETs. The gate voltage does not only modulate the source-channel barrier, but also the drain-channel barrier can be altered to the extent where tunneling is allowed.

For devices with a gate-drain overlap, tunneling can also take place in the accumulation layer formed inside the drain. For a certain gate bias the energy bands in this region are bent to the extent that tunneling is allowed. Tunneling taking place in this region is often referred to as gate induced drain leakage (GIDL). GIDL is not unique for the TFET, and has for a long time been known to contribute to leakage current in MOSFETs[57, 58]. Gate induced leakage currents, both ambipolar leakage and GIDL, leads to a distinct *ambipolar* behavior. For a p-type device this means that the drain current increases with positive voltage, and that the drain current increases for negative voltage for an n-type device, respectively. Gate induced leakage currents can also lead to an elevated leakage floor when no gate bias is applied.

The terms ambipolar leakage and GIDL are often used interchangeably, as they both refer to leakage currents induced by the gate. It can however be useful to differ between them as different design approaches might be needed to suppress the two.

#### 1.5 Tunneling Field Effect Transistors: State-of-the-Art

In the above sections the operating principles of a TFET was explained, and expressions for the BTBT drive current, SS and different leakage current mechanisms was given. It is now time to take a look at how one, with this knowledge, best should proceed when engineering a TFET to meet the requirements of the international technology roadmap for semiconductors (ITRS)[59]. At the moment there exists no scientific consensus with regards to this, and a large variety of strategies and TFET concepts have evolved. What follows is therefore an overview of some performance boosters and the state-of-the-art TFETs.

# 1.5.1 Material System Considerations for Tunneling Field Effect Transistor Design

As has been previously stated, the potential of the TFET lies in its steep subthreshold characteristics. This allows for a much needed supply voltage reduction for the next generations of electronic devices. The gate voltage dependence of the SS for a TFET (see (13) and (14) in

section 1.4.4), leads to that the tunneling current exhibit an early saturation at higher gate voltages. As a consequence I<sub>ON</sub> of TFETs are, to date, low compared to those of MOSFETs. Increasing I<sub>ON</sub>, without degrading SS and I<sub>OFF</sub>, is therefore the TFETs biggest challenge, and a major obstacle for realizing TFETs as viable candidates to replacing MOSFETs.

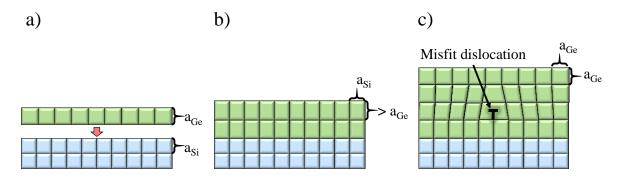

When focusing on increasing I<sub>ON</sub>, the expression for the BTBT current (see (5) in section 1.4.3), can be used as a starting point for finding an optimal TFET semiconductor material. This expression states that the materials energy bandgap, E<sub>G</sub>, and the reduced effective mass,  $m^*$ , and tunneling width  $\lambda$  should be minimized to increase the tunneling current. The first two parameters depend solely on the material system, while  $\lambda$  can be influenced by several parameter, like doping profiles, geometry and gate capacitance [60]. Due to the large bandgap and large carrier mass, Si can in this regard be considered an unideal TFET material. Si TFETs are, however, still the most studied. The know-how, excellent quality and availability of Si is superior to that of any other semiconductor. Of the TFETs that experimentally have demonstrated SS < 60 mV/dec, Si TFET, stands for the largest portion of these reported devices[61]. Experimental studies do however agree with predictions, as Si TFETs exhibit overall low I<sub>ON</sub>[62, 63, 64]. Of the group IV materials, SiGe and Ge are more interesting. They can easily be integrated on a Si-platform and make it into mass production, but have a reduced bandgap and reduced effective mass with respect to Si. Demonstrated SiGe TFETs[65] and Ge TFETs [66] also show considerably higher I<sub>ON</sub> compared to Si TFETs. These materials still suffer the same major problem as Si, namely that they are indirect semiconductor materials. In order for electrons to tunnel between bands misaligned in momentum-space, they must also absorb energy from vibrations in the crystal. This significantly lowers the tunneling probability. Potential of group IV materials for TFET, however, lies in direct bandgap transition engineering through strain[67] or through alloying with Sn[68].

Group III-V semiconductors materials such as InGaAs[69], have the advantage that they are direct semiconductors and as a result show considerably higher tunneling currents than those of Si TFETs. Using the mix of two group III-V compounds creating staggered gap heterojunctions, like InGaAs/GaAsSb[70] and AlGaSb/InAs[71], have demonstrated the highest tunneling currents so far, with IoN comparable to that of current MOSFETs. The high currents is a result of the natural overlap between bands which leads to that less voltage is needed to turn these devices on. Group III-V materials are still a bit too exotic for mass production in logic chips. That larger companies like Intel are looking into these materials for the use in MOSFETs [72], is, however, a sign for that this might only be a temporary showstopper.

Although a bias toward group III-V seems to have evolved for the n-channel TFET, this is not the case for the less studied p-channel TFET. Here the low conduction band density of states is a limiting factor for III-V materials [73]. Finding one single material that is suited for complementary TFET, which is a must if TFETs should be implemented in logic chips, is therefore another problem facing TFETs. Some have suggested that a future complimentary TFET element can consists of both types of material, i.e. group IV material for a p-channel and a group III-V material for n-channel TFET, respectively [74].

Materials that have attracted recent interest are 2D materials like transition metal dichalcogenides and graphene [75]. These offer high electron tunneling efficiency through a broken-gap band alignment and a low I<sub>OFF</sub> through band gap engineering of drain material. Even though these materials are at a very early stage, TFETs have already been demonstrated [23, 76].

When choosing a material with the sole purpose of increasing the tunneling current, one can run into trouble. Especially with bandgap engineering, the tradeoff due to increase of leakage current with lowering of the bandgap becomes a problem. The above referred to III-V staggered bandgap heterojunction TFETs and also low bandgap Ge and GeSn TFETs [77], which show high IoN, also exhibit high leakage currents and poor IoN/IoFF-ratio. These devices have not been able to demonstrate SS < 60 mV/dec. This is not only due to low bandgap, but also a consequence of the low quality of these material. Crystal defects, both in the bulk at the surface, increase SRH and TAT leakage currents. With respect to material quality, TFETs are said to require a much higher degree of perfection than previous electronic devices [78]. Novel materials, that are predicted to show excellent TFET characteristics, often lack technological experience. This is thought to be the main reason for the large gap between the experiments and the much more optimistic theoretical predictions of TFETs, which often neglects nonidealities [61].

The drain and source doping profiles are other material parameters which can be tuned to improve device performance. The source doping profile and level determines the tunneling barrier width  $\lambda$ , while the drain doping profile affects the electrical field and ambipolarity. A high and abrupt source doping is needed to ensure a small depletion width in the source. A source doping abruptness of less than 4 nm/dec is needed to maximize  $I_{ON}$  [50]. However, degeneracy limits the number of electrons available for tunneling and can reduce  $I_{ON}$ .

The gate oxide material is important to ensure a good electrostatic control of the gate. Both a higher I<sub>ON</sub> and a lower SS can be obtained by increasing the gate oxide capacitance[79]. The problem of having a high oxide capacitance, but on the same time preventing gate oxide

leakage, is thanks to the advances in MOSFET technology, solved by implementing high-κ oxides. Some common high-κ oxides are HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub>. Many semiconductor/high-κ surfaces, however, suffer from very high interface trap densities (D<sub>it</sub>), which prevents low SS of being achieved [48]. Surface passivation chemistry has therefore become an essential part of the work in improving future TFETs.

#### 1.5.2 Geometry Considerations for Tunneling Field Effect Transistor Design

In order to improve TFET performance, geometry and device design is also important in order to utilize the material system at hand. In bulk TFETs, a trade-off exist between achieving high on-currents and small values for SS. 1D systems, achieved with nanowire geometries, and 2D crystals have been proposed as ideally suited for realizing TFETs with high I<sub>ON</sub> and low SS [53, 80]. In nanowire geometries the electrical gate field penetrate the entire body and therefore represents the ideal electrostatic gate control. In this devices a pn-structure is often used and the positional dependence of the gate with respect to the junction is used to separate the p-channel and n-channel TFETs. The gate metal is chosen to deplete the channel in the off state, an *intrinsic* region is then achieved electrostatically. Achieving 1D and 2D systems is, however, technologically challenging, and not realizable for all materials. Scaling down to the atomic level also introduces a problem of variability, where placement and concentration of dopant atoms and interface roughness can significantly change the electrical properties [81].

In addition to reducing body thickness, well aligned gates are a key technological challenge. Both unintentional gate-underlap and overlap can have serious deteriorating effects on the TFET performance [82].

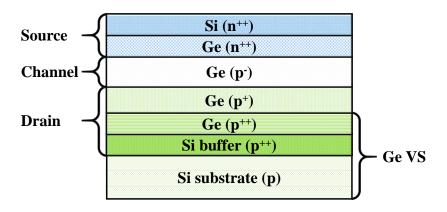

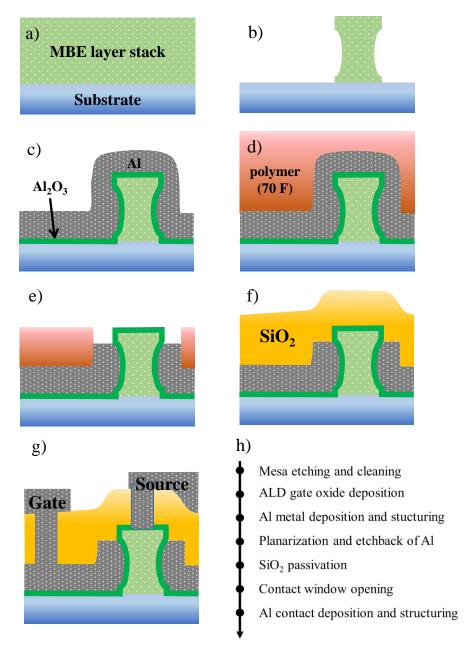

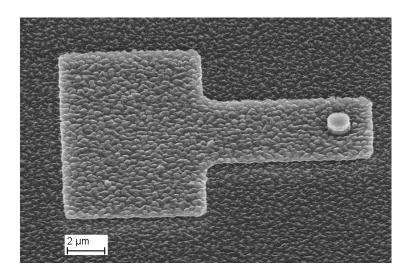

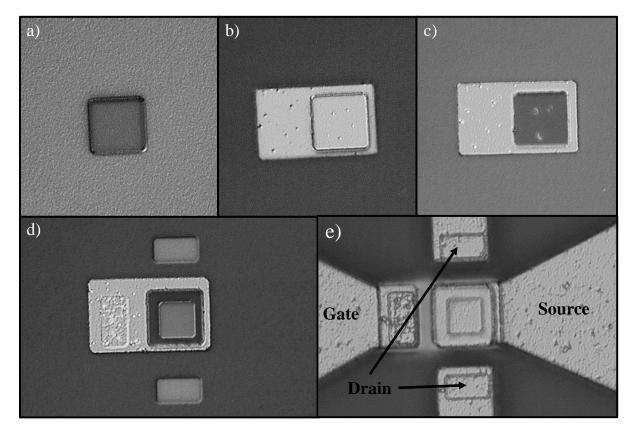

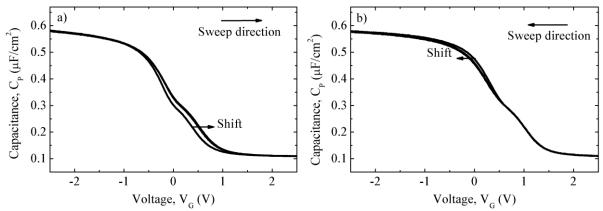

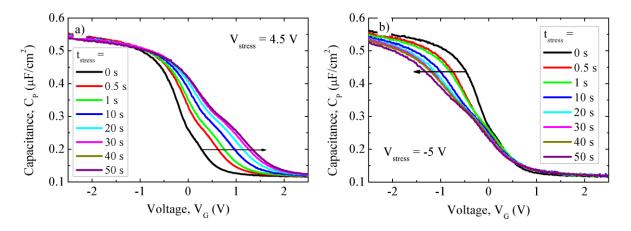

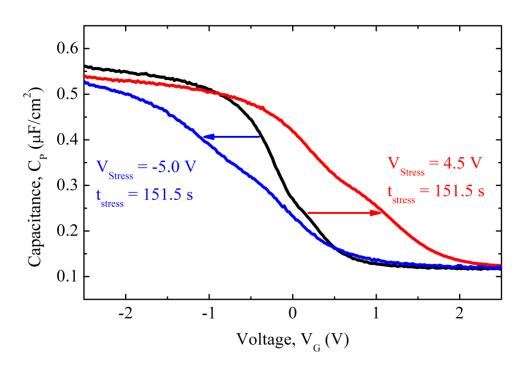

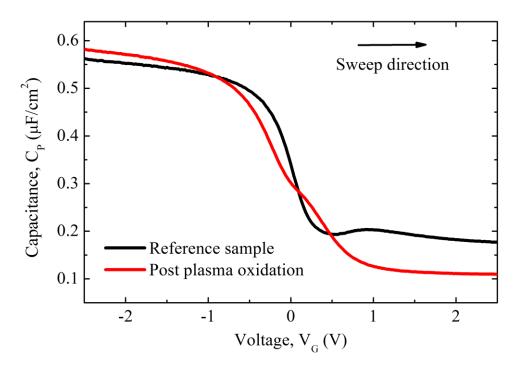

Having an intentional source-gate overlap has been shown to boost drive currents in Si [83] and SiGe [84] TFETs. In this case tunneling does not only takes place at the source channel interface, but also inside the gate overlapped source region.