# GaN-on-Silicon HEMTs and Schottky diodes for high voltage applications

### Loizos Efthymiou

Department of Engineering University of Cambridge

This dissertation is submitted for the degree of  $Doctor \ of \ Philosophy$

Churchill College

April 2018

### Declaration

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other University. This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration, except where specifically indicated in the text. This dissertation contains approximately 42,000 words including appendices, bibliography, footnotes, tables and equations and has 89 figures.

Loizos Efthymiou April 2018

#### Acknowledgements

Firstly, I would like to thank my supervisor Prof. Florin Udrea for his help and expert guidance throughout my PhD. His enthusiasm for the topic of power devices was a constant source of motivation.

I would like to give a very special thanks to Giorgia Longobardi and Gianluca Camuso for all their help and patience when assisting me with the initial understanding of the topic and the different experimental activities involved in this line of work. I would also like to thank Alice Pei-Shan Hsieh for her support and encouragement when I first joined the lab. I would also like to express my gratitude to Nishad Udugambola for his invaluable assistance with anything measurement-related.

I would like to thank the team from Vishay Taiwan (Max Chen, Terry Chien and Evelyn Lin) for a very fruitful and enjoyable collaboration as well as the team from Vishay Siliconix (Kyle Terrill and Ayman Shibib) for their contributions towards the final stages of this PhD.

I would like to thank the members of the HVMS lab, past and present, for creating a very friendly and enjoyable working environment. It has been a great pleasure working with you all. I would also like to express my gratitude to all my friends outside the lab, in Cambridge and beyond, that supported me and offered words of encouragement throughout my PhD.

A special thanks goes to my girlfriend, Penelope, for her patience and kindness. I am very grateful for everything you do to support me. Finally, I would like to thank my family, my parents and my two brothers, for their unconditional support and belief in me. I would not have managed this without them.

#### Abstract

Gallium Nitride (GaN) is considered a very promising material for use in the field of power devices as its application in power systems would result in a significant increase in the power density, reduced power losses, and the potential to operate at high frequencies. The wide bandgap of the material allows a high critical electric field to be sustained which can lead to the design of devices with a shorter drift region, and therefore with lower on-state resistance, if compared to a silicon-based device with the same breakdown voltage. The use of an AlGaN/GaN heterostructure allows the formation of a two-dimensional electron gas (2DEG) at the heterointerface where carriers can reach very high mobility values. These properties can lead to the production of High Electron Mobility Transistors (HEMTs) and Schottky barrier diodes with superior performance, even when compared to devices based on state-of-the-art technologies such as Silicon Carbide or superjunctions. Furthermore, epitaxial growth of GaN layers on silicon wafers allows a significant reduction in the production cost and makes these devices competitive from a price perspective. This thesis will deal with a variety of topics concerning the characterization, design and optimization of AlGaN/GaN HEMTs and Schottky diodes with a 600 to 650V rating. Discussion will span several topics from device cross-section physics to circuit implementation and will be based on both experimental results and advanced modelling.

More specifically, the thesis is concerned with the characterization of AlGaN/GaN Schottky diodes and extraction of their main parameters such as ideality factor, barrier height and series resistance. A thorough investigation of their reverse recovery performance and a comparison to competing technologies is also given. Several topics which concern the operation of AlGaN/GaN HEMTs are then discussed. The underlying physics of p-gate enhancement mode transistors are analysed followed by a discussion of the challenges associated with the implementation of these devices at a circuit level. Finally, a comparison of the performance of a specific area-saving layout (Bonding pad over active area) and a conventional design is given.

The thesis aims to significantly enhance the understanding of the behaviour of these devices to enable better or new commercial designs to emerge.

## Table of contents

| Li            | st of | figures xi                                                                                                | ii |

|---------------|-------|-----------------------------------------------------------------------------------------------------------|----|

| $\mathbf{Li}$ | st of | tables xi                                                                                                 | x  |

| N             | omei  | nclature xi                                                                                               | x  |

| 1             | Inti  | roduction                                                                                                 | 3  |

|               | 1.1   | Overview of the field                                                                                     | 3  |

|               | 1.2   | Brief history of power devices                                                                            | 4  |

|               | 1.3   | Comparison between GaN and other materials $\ldots \ldots \ldots \ldots \ldots$                           | 6  |

|               | 1.4   | Applications of GaN power devices                                                                         | 2  |

|               | 1.5   | Overview of the thesis 1                                                                                  | 4  |

| <b>2</b>      | Gal   | N device physics and state of the art 1                                                                   | 7  |

|               | 2.1   | Wafer processing 1                                                                                        | 17 |

|               | 2.2   | Physical properties of the AlGaN/GaN heterojunction                                                       | 8  |

|               | 2.3   | Typical AlGaN/GaN Schottky diode structure                                                                | 22 |

|               | 2.4   | AlGaN/GaN High Electron mobility transistor                                                               | 23 |

|               |       | 2.4.1 Enhancement mode HEMT                                                                               | 24 |

|               | 2.5   | Brief discussion of issues related to GaN-based devices                                                   | 27 |

|               |       | 2.5.1 Off-state leakage and breakdown                                                                     | 28 |

|               |       | 2.5.2 Current Degradation                                                                                 | 29 |

|               |       | 2.5.3 Passivation $\ldots \ldots 3$ | 32 |

|               |       | 2.5.4 Field plate design                                                                                  | 32 |

|               |       | 2.5.5 Cap layer $\ldots$ | 32 |

|               | 2.6   | Switching of GaN HEMTs and Schottky diodes                                                                | 33 |

|               | 2.7   | Device layout                                                                                             | 33 |

| 3        | $\operatorname{Sim}$ | ulation tools                                                                                                    | 35        |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------|-----------|

|          | 3.1                  | Sentaurus TCAD                                                                                                   | 35        |

|          |                      | 3.1.1 Spontaneous and Polarization Effects                                                                       | 36        |

|          |                      | 3.1.2 Traps                                                                                                      | 36        |

|          |                      | 3.1.3 Fermi - Dirac statistics                                                                                   | 37        |

|          |                      | 3.1.4 Contacts                                                                                                   | 38        |

|          |                      | 3.1.5 Transport models $\ldots$ | 38        |

|          |                      | 3.1.6 Mobility models                                                                                            | 40        |

|          |                      | 3.1.7 Mesh                                                                                                       | 42        |

|          | 3.2                  | LTspice                                                                                                          | 42        |

|          | 3.3                  | Mixed mode simulations                                                                                           | 44        |

| 4        | Mo                   | delling of an AlGaN/GaN Schottky diode and extraction of main                                                    |           |

|          | par                  | ameters                                                                                                          | <b>45</b> |

|          | 4.1                  | Introduction                                                                                                     | 45        |

|          | 4.2                  | Device Structure and Methods                                                                                     | 46        |

|          |                      | 4.2.1 Device Structure                                                                                           | 46        |

|          |                      | 4.2.2 Literature Background and methods for parameter extraction .                                               | 46        |

|          |                      | 4.2.3 Outline of extraction method used in this study                                                            | 48        |

|          | 4.3                  | Results and Discussion                                                                                           | 50        |

|          | 4.4                  | Conclusions                                                                                                      | 54        |

| <b>5</b> | Ove                  | erview of the operation of AlGaN/GaN Schottky diode and com-                                                     |           |

|          | par                  | ison with competing technologies                                                                                 | 55        |

|          | 5.1                  | Motivation                                                                                                       | 55        |

|          | 5.2                  | Device Structure                                                                                                 | 56        |

|          | 5.3                  | Experimental methods                                                                                             | 57        |

|          | 5.4                  | TCAD model                                                                                                       | 57        |

|          |                      | 5.4.1 Model matching                                                                                             | 57        |

|          |                      | 5.4.2 Effect of substrate connection on GaN device performance $\ldots$                                          | 61        |

|          |                      | 5.4.3 AlGaN/GaN Schottky diode turn-off                                                                          | 64        |

|          | 5.5                  | Comparison with competing technologies                                                                           | 68        |

|          |                      | 5.5.1 Experimental Measurements                                                                                  | 68        |

|          |                      | 5.5.2 TCAD model comparison                                                                                      | 71        |

|          | 5.6                  | TCAD model limitations and future work                                                                           | 73        |

|          | 5.7                  | Conclusions                                                                                                      | 75        |

| 6 | On            | the physical operation and optimization of the p-GaN gate in                                                         | 1   |

|---|---------------|----------------------------------------------------------------------------------------------------------------------|-----|

|   | nor           | mally-off GaN HEMT devices                                                                                           | 77  |

|   | 6.1           | Introduction                                                                                                         | 77  |

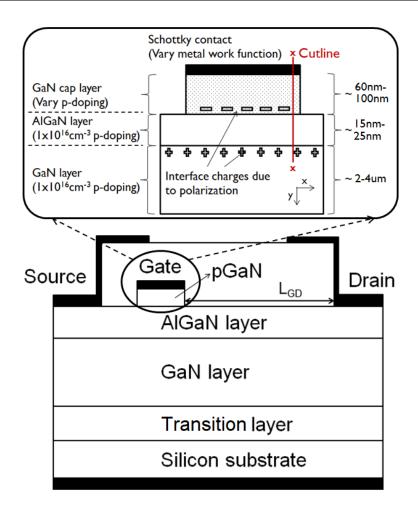

|   | 6.2           | Device Structure and TCAD models                                                                                     | 78  |

|   | 6.3           | TCAD results and discussion                                                                                          | 81  |

|   |               | 6.3.1 Variation of p-GaN doping and Schottky gate work function                                                      | 81  |

|   |               | 6.3.2 Gate turn-on                                                                                                   | 84  |

|   | 6.4           | Conclusions                                                                                                          | 87  |

| 7 | Osc           | cillatory Behaviour during Switching of normally-off GaN HEMTs                                                       | 89  |

|   | 7.1           | Introduction                                                                                                         | 89  |

|   | 7.2           | Device structure and characteristics                                                                                 | 90  |

|   | 7.3           | Experimental method                                                                                                  | 92  |

|   | 7.4           | Results and Discussion                                                                                               | 95  |

|   |               | 7.4.1 dV/dt related effect                                                                                           | 96  |

|   |               | 7.4.2 dI/dt related effect $\ldots$ | 98  |

|   |               | 7.4.3 Good design suggestions                                                                                        | 101 |

|   | 7.5           | Effect of internal parasitics                                                                                        | 103 |

|   |               | 7.5.1 Switching capability                                                                                           | 107 |

|   | 7.6           | Conclusions                                                                                                          | 108 |

| 8 | Bor           | nding pad over active area (BPOA) layout for lateral AlGaN/GaN                                                       | 1   |

|   | $\mathbf{HE}$ | MTs : a critical view                                                                                                | 109 |

|   | 8.1           | Introduction                                                                                                         | 109 |

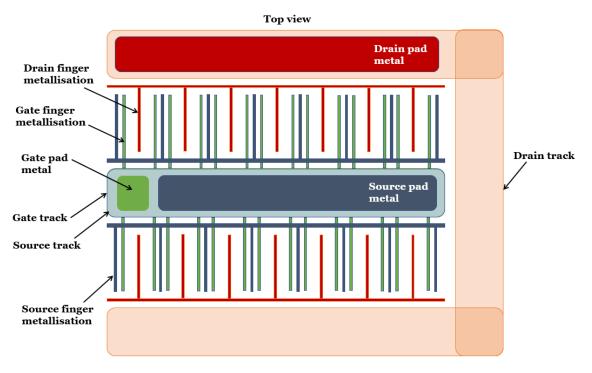

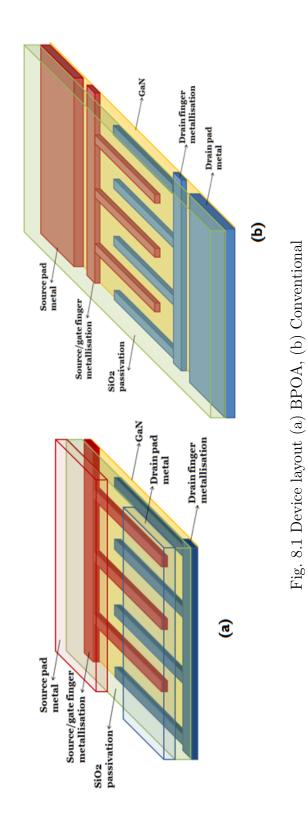

|   | 8.2           | Device Structure                                                                                                     | 110 |

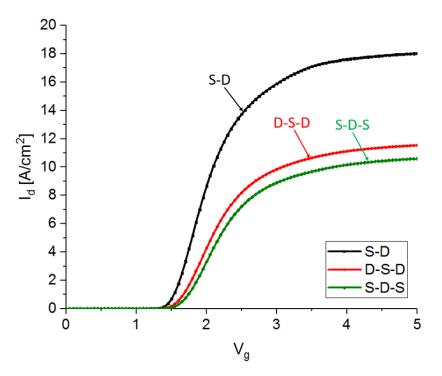

|   | 8.3           | Experimental Results                                                                                                 | 112 |

|   | 8.4           | Reliability analysis                                                                                                 | 115 |

|   |               | 8.4.1 TCAD Model                                                                                                     | 115 |

|   |               | 8.4.2 Off-state simulations                                                                                          | 116 |

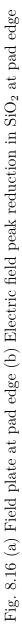

|   |               | 8.4.3 Electric field peak at pad edge                                                                                | 123 |

|   | 8.5           | Conclusions                                                                                                          | 126 |

| 9 | Cor           | nclusions and Future work                                                                                            | 127 |

|   | 9.1           | Conclusions                                                                                                          | 127 |

|   | 9.2           | Future work                                                                                                          | 133 |

| R | efere         | ences                                                                                                                | 137 |

# List of figures

| 1.1  | Applications of power devices                                                             | 4  |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | $\mathrm{R}_{\mathrm{on}}$ vs breakdown: Comparison of intrinsic and demonstrated perfor- |    |

|      | mance of different technologies                                                           | 11 |

| 1.3  | Commercially available GaN devices                                                        | 12 |

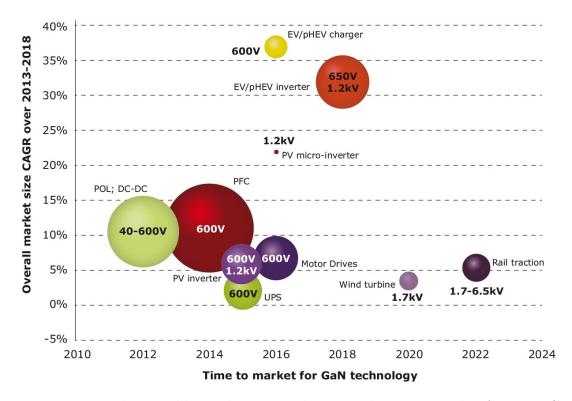

| 1.4  | Estimated accessible markets, growth rate and time-to-market for main                     |    |

|      | GaN applications                                                                          | 13 |

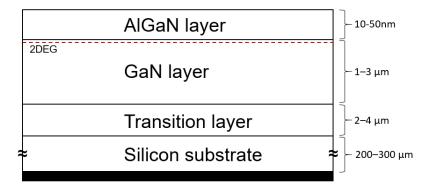

| 2.1  | Typical structure with several GaN-based layers grown on a Silicon                        |    |

|      | substrate                                                                                 | 18 |

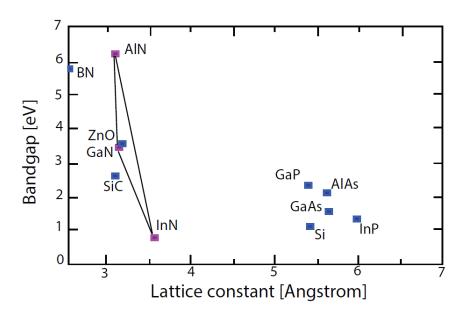

| 2.2  | Band Diagram vs Lattice constant for different semiconductors                             | 19 |

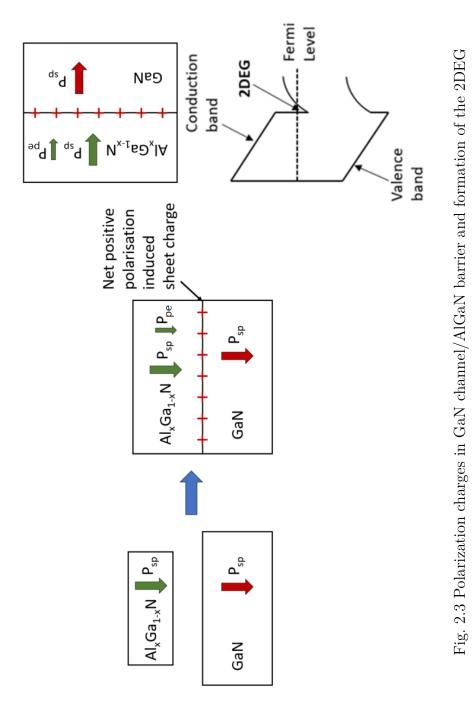

| 2.3  | Polarization charges in GaN channel/AlGaN barrier and formation of                        |    |

|      | the 2DEG                                                                                  | 21 |

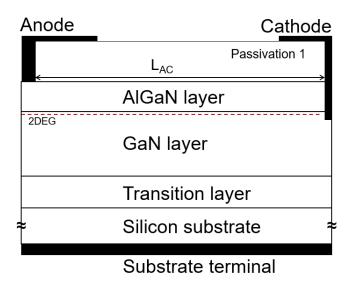

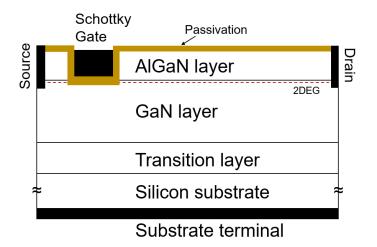

| 2.4  | Typical lateral AlGaN/GaN Schottky diode structure                                        | 22 |

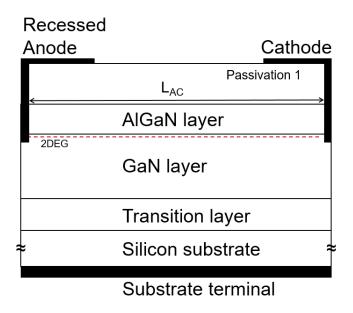

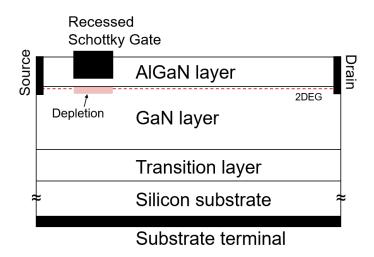

| 2.5  | Typical lateral AlGaN/GaN recessed Schottky diode structure $\ . \ . \ .$                 | 23 |

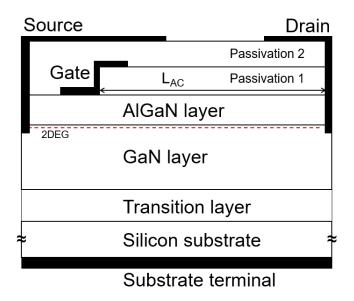

| 2.6  | Typical lateral AlGaN/GaN HEMT transistor structure                                       | 24 |

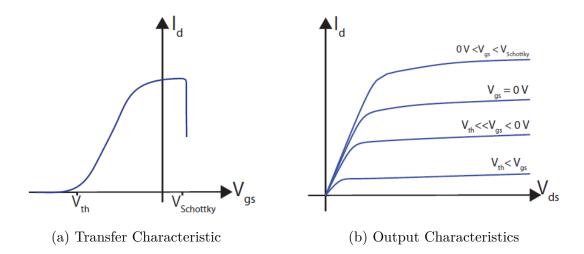

| 2.7  | Typical lateral AlGaN/GaN depletion mode HEMT characteristics                             | 25 |

| 2.8  | Typical lateral AlGaN/GaN enhancement mode MISHEMT $\ .\ .\ .$ .                          | 26 |

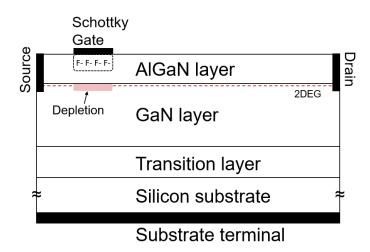

| 2.9  | Typical lateral AlGaN/GaN enhancement mode HEMT using recessed                            |    |

|      | Schottky gate                                                                             | 26 |

| 2.10 | Typical lateral AlGaN/GaN enhancement mode HEMT using fluorine                            |    |

|      | treatment                                                                                 | 27 |

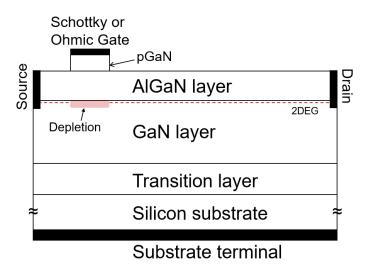

| 2.11 | Typical lateral AlGaN/GaN enhancement mode HEMT using p-GaN gate $% \mathcal{A}$          | 28 |

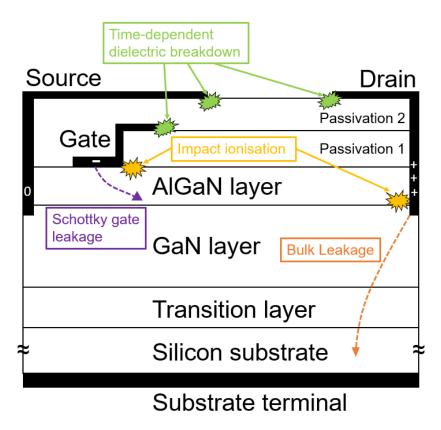

| 2.12 | Common off-state leakage and breakdown mechanisms associated with                         |    |

|      | AlGaN/GaN HEMTs and Schottky diodes                                                       | 29 |

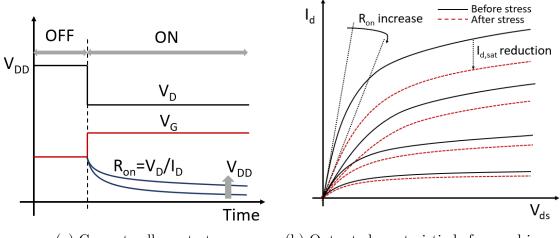

| 2.13 | Current collapse or Dynamic $R_{on}$ phenomenon                                           | 30 |

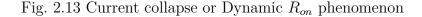

| 2.14 | Trapping mechanisms responsible for current collapse                                      | 31 |

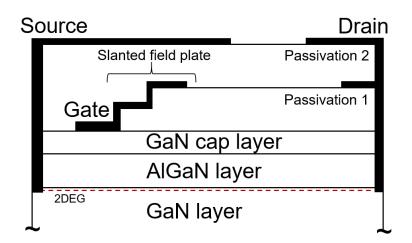

| 2.15 | Slanted field plate and GaN cap layer device example                                      | 33 |

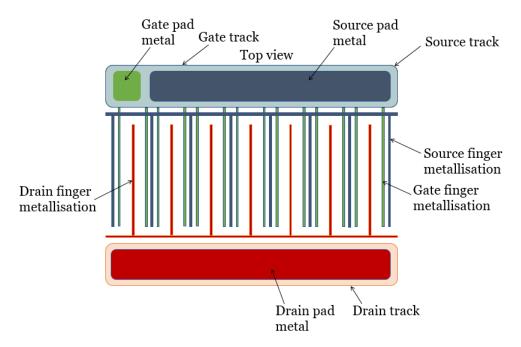

| 2.16 | Typical lateral AlGaN/GaN HEMT inter-digitated layout                                     | 34 |

| 3.1 | Location and polarity of the theoretically predicted interface charges for     |    |

|-----|--------------------------------------------------------------------------------|----|

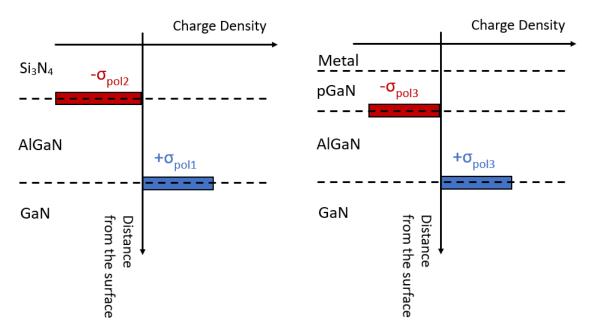

|     | different structures                                                           | 37 |

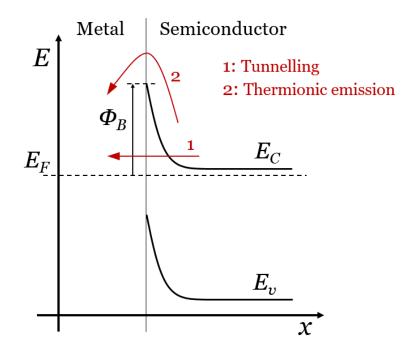

| 3.2 | Conduction mechanisms at a Schottky junction                                   | 41 |

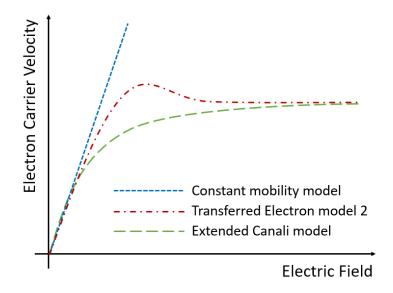

| 3.3 | Illustration of different velocity saturation models available in Sentaurus    |    |

|     | TCAD software                                                                  | 42 |

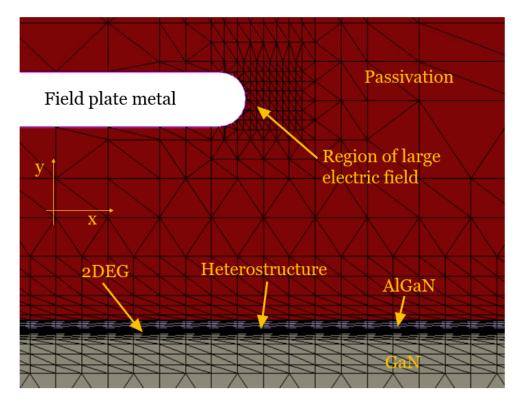

| 3.4 | Example of mesh definition in a TCAD model                                     | 43 |

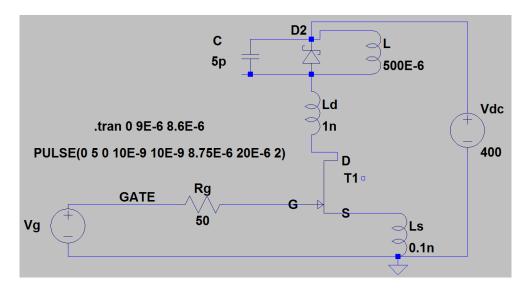

| 3.5 | Example of a simple clamped inductive switching circuit in LT<br>spice $\ .$ . | 43 |

| 3.6 | Example of a netlist defining a simple clamped inductive switching             |    |

|     | circuit for mixed mode simulations                                             | 44 |

| 4.1 | Device structure (a) Cross section, (b) Band diagram schematic at the          |    |

|     | Schottky/GaN/AlGaN/GaN interface                                               | 47 |

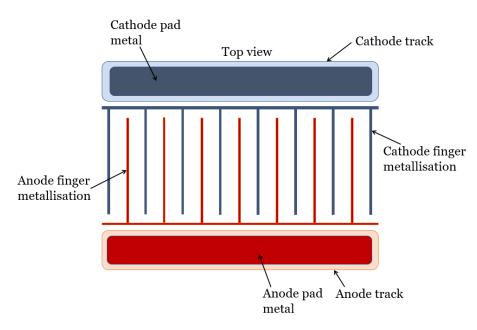

| 4.2 | AlGaN/GaN Schottky diode layout                                                | 48 |

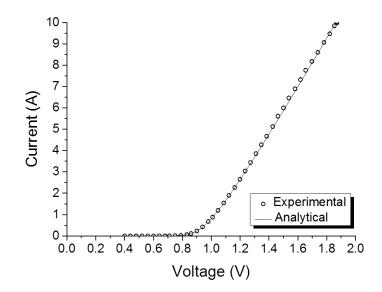

| 4.3 | Experimental and analytical on - state I-V characteristic for device           |    |

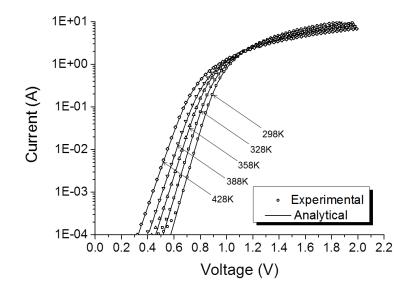

|     | shown in Fig. 4.1                                                              | 51 |

| 4.4 | Sub - threshold experimental and analytical on - state I-V characteristic      |    |

|     | for device shown in Fig. 4.1                                                   | 51 |

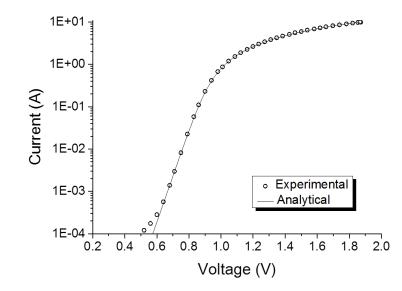

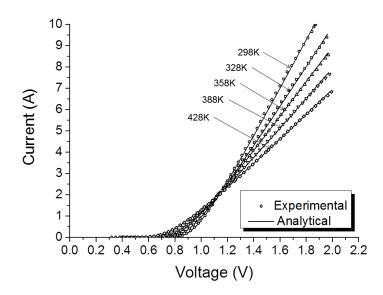

| 4.5 | Experimental and analytical on-state I-V characteristic for device shown       |    |

|     | in Fig. 4.1 at increased temperatures                                          | 52 |

| 4.6 | Sub-threshold experimental and analytical on-state I-V characteristic          |    |

|     | for device shown in Fig. 4.1 at increased temperatures                         | 52 |

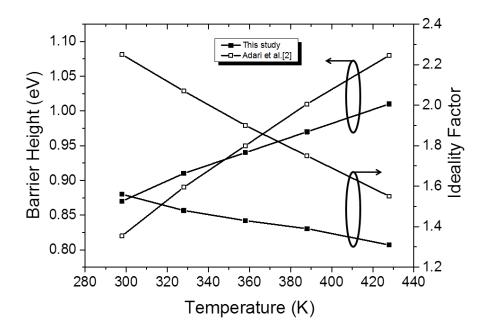

| 4.7 | Extracted ideality factor and barrier height as a function of temperature      |    |

|     | for device shown in Fig.4.1                                                    | 53 |

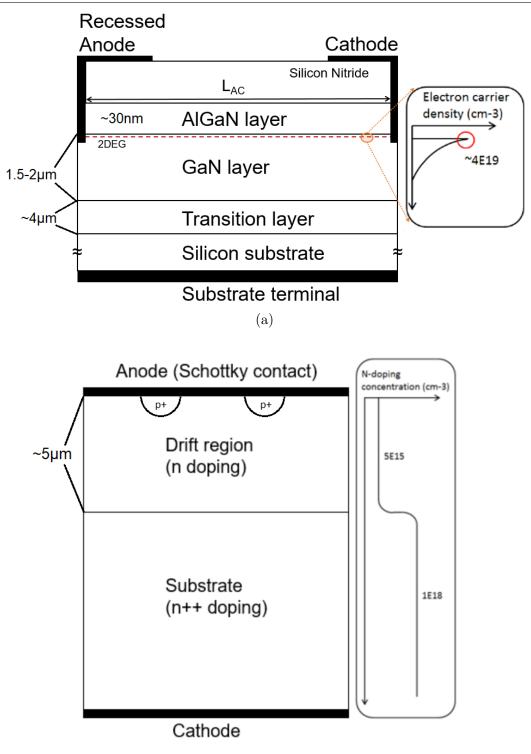

| 5.1 | Cross section of (a) AlGaN/GaN device and (b) SiC device used for              |    |

|     | experimental measurements and TCAD model                                       | 58 |

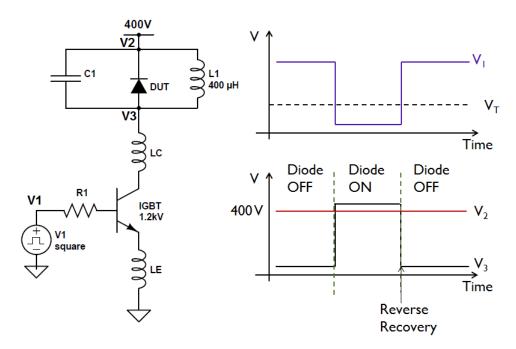

| 5.2 | Experimental and simulation reverse recovery test circuit                      | 59 |

| 5.3 | Experimental measurement and TCAD model simulation on-state match-             |    |

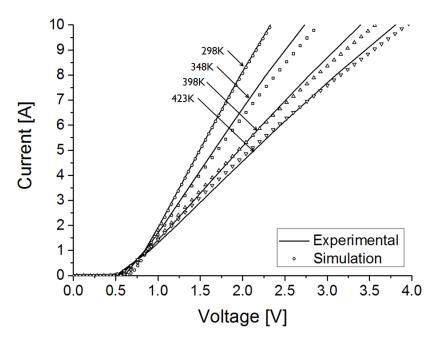

|     | ing at a range of temperatures                                                 | 60 |

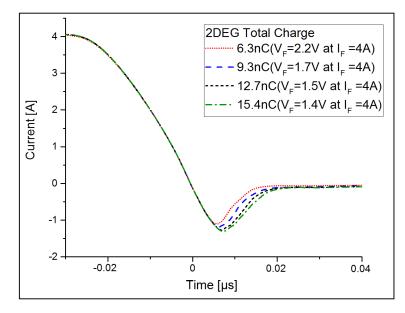

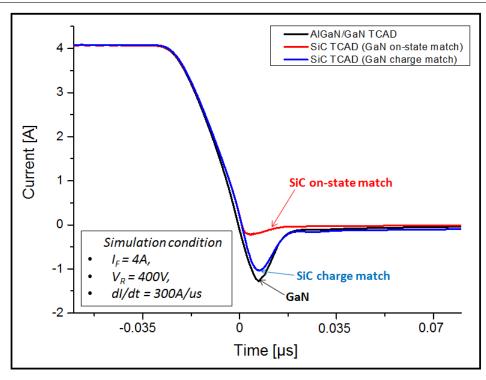

| 5.4 | Effects of 2DEG charge level on TCAD model reverse recovery charac-            |    |

|     | teristic for AlGaN/GaN Schottky diode device shown in Fig. 5.1a                | 61 |

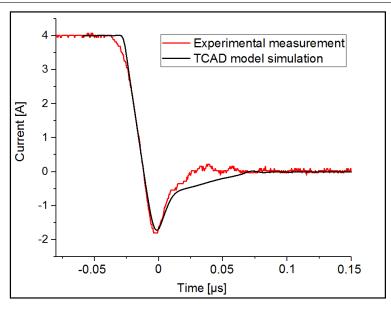

| 5.5 | AlGaN/GaN Schottky diode reverse recovery characteristic match be-             |    |

|     | tween TCAD model simulation and experimental result at room tem-               |    |

|     | perature                                                                       | 62 |

| 5.6 | (a) Experimental and simulation reverse recovery test circuit (b) Elec-        | -  |

|     | trostatic potential at points V1, V2, V3 during reverse recovery test          | 63 |

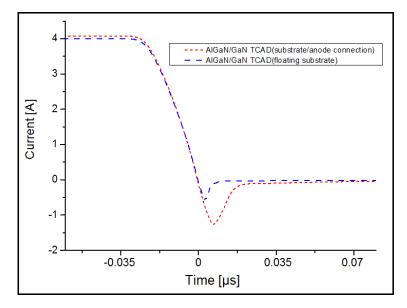

| 5.7  | Effects of substrate connection on TCAD model reverse recovery char-                                                                                  |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | acteristic for AlGaN/GaN Schottky diode device shown in Fig. 5.1a                                                                                     | 65 |

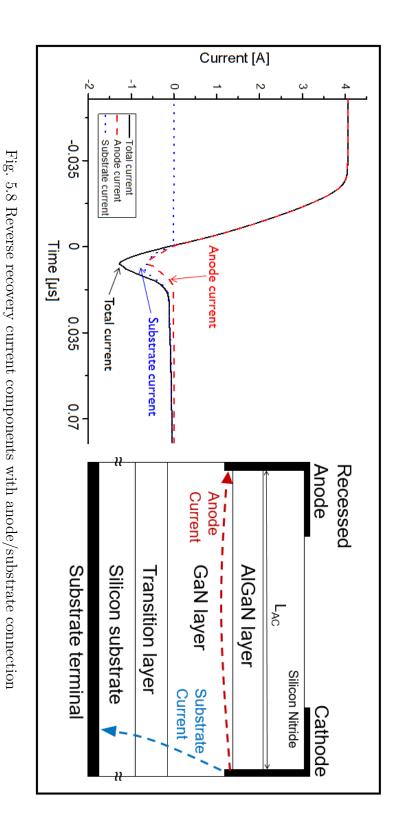

| 5.8  | Reverse recovery current components with anode/substrate connection                                                                                   | 66 |

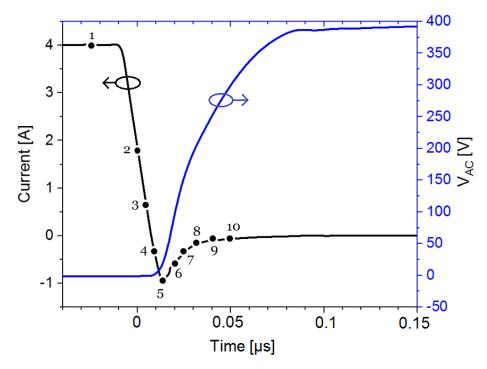

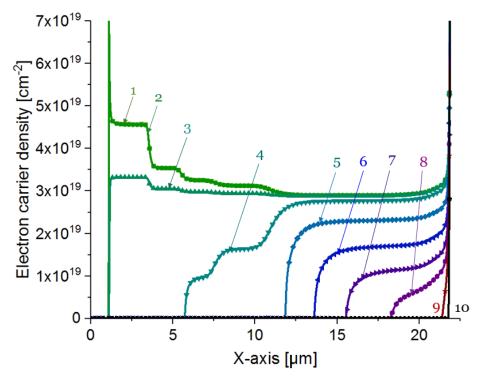

| 5.9  | Illustration of depletion of 2DEG carrier denisty with time during turn-off                                                                           | 67 |

| 5.10 | Experimental reverse recovery characteristic of AlGaN/GaN diode com-                                                                                  |    |

|      | pared with SiC Schottky diodes and fast recovery Si diodes of similar                                                                                 |    |

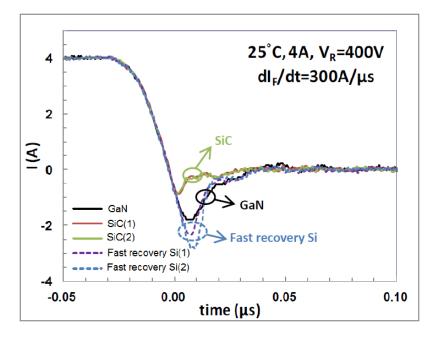

|      | rating at room temperature                                                                                                                            | 69 |

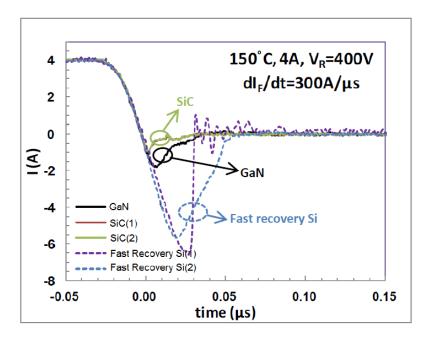

| 5.11 | Experimental reverse recovery characteristic of AlGaN/GaN diode com-                                                                                  |    |

|      | pared with SiC Schottky diodes and fast recovery Si diodes of similar                                                                                 |    |

|      | rating at room temperature                                                                                                                            | 69 |

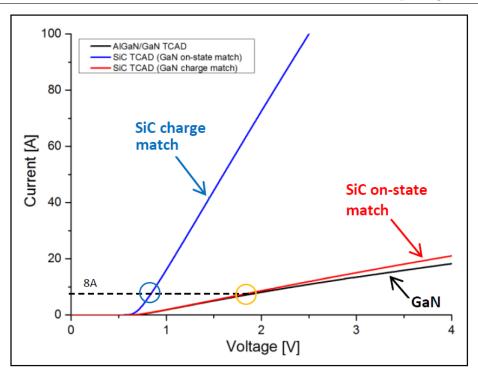

| 5.12 | Simulated on-state I-V characteristic of AlGaN/GaN diode model matched                                                                                |    |

|      | with SiC diode model. The on-state I-V characteristic comparison be-                                                                                  |    |

|      | tween the two devices is also shown with equal drift region charge                                                                                    | 72 |

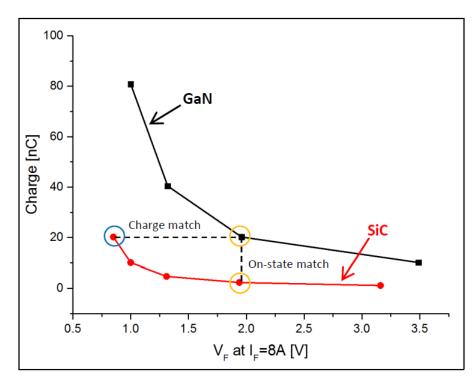

| 5.13 | Comparison of drift region charge for SiC and 2DEG charge for GaN $$                                                                                  |    |

|      | vs forward voltage drop for a current rating of 8A for GaN and SiC $$                                                                                 |    |

|      | Schottky diode TCAD models                                                                                                                            | 73 |

| 5.14 | Simulated reverse recovery characteristic of AlGaN/GaN diode model $$                                                                                 |    |

|      | compared with SiC Schottky diodes of equal on-state current character-                                                                                |    |

|      | istic and equal drift region charge                                                                                                                   | 74 |

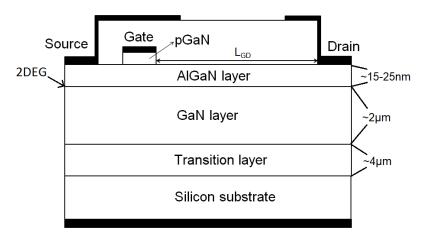

| 6.1  | Cross-section of p-GaN/AlGaN/GaN HEMT device modelled                                                                                                 | 79 |

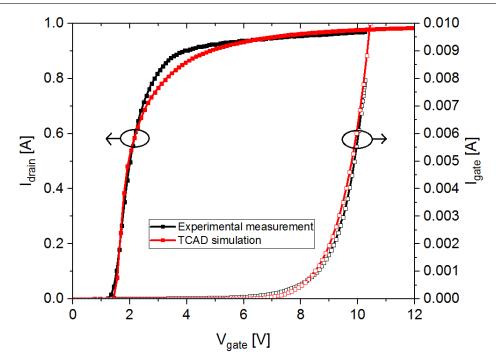

| 6.2  | Experimental measurements and TCAD simulations of $I_d V_q$ and $I_q V_q$                                                                             |    |

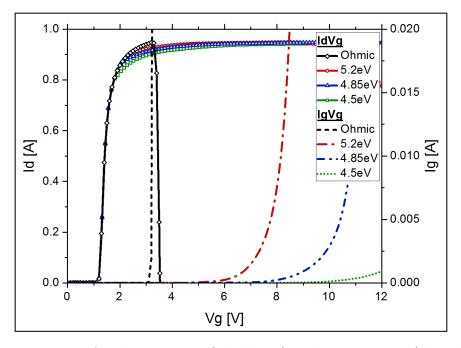

| 0    | characteristic $\ldots \ldots \ldots$ | 80 |

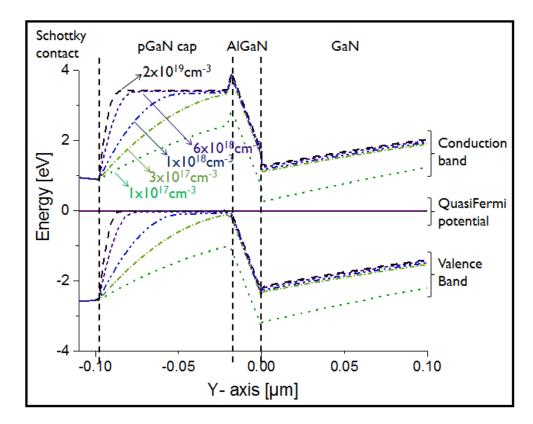

| 6.3  | Effect of p-GaN gate doping variation on band diagram at zero bias                                                                                    | 81 |

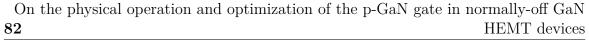

| 6.4  | $I_D - V_G$ transfer characteristic with variation in p-GaN gate doping                                                                               |    |

| 0.1  | (Inset: Device threshold voltage, $V_{th}$ vs p-GaN acceptor doping)                                                                                  | 82 |

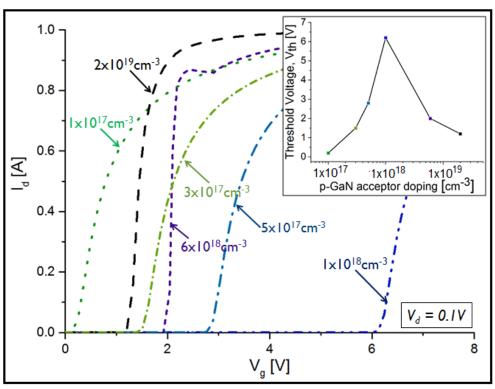

| 6.5  | Effect of gate bias on different sections of the gate structure band                                                                                  |    |

|      | diagram (i) Schottky junction, (ii) AlGaN/GaN Heterojunction                                                                                          | 83 |

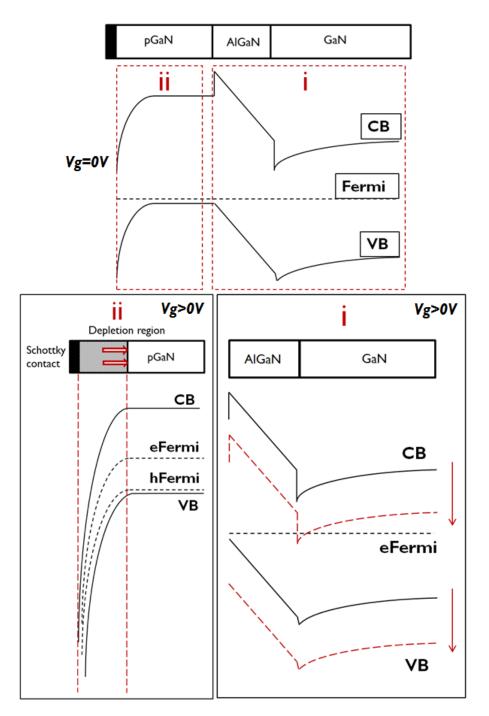

| 6.6  | Gate structure band diagram at gate bias of 3V for p-GaN doping of                                                                                    |    |

|      | $1 \times 10^{18} \text{cm}^{-3}$ (negligible hole tunnelling) and $2 \times 10^{19} \text{cm}^{-3}$ (considerable hole                               |    |

|      | tunnelling)                                                                                                                                           | 85 |

| 6.7  | $I_D - V_G$ transfer characteristic (solid lines) and gate turn-on (dotted                                                                            |    |

|      | lines) as gate metal work function is varied                                                                                                          | 85 |

| 6.8  | Gate structure band diagram at gate bias of $Vg = 3V$ , $9V > Vth$ for                                                                                |    |

|      | TCAD model with p-GaN doping of $2 \times 10^{19} \text{ cm}^{-3}$ (Inset: Conduction                                                                 |    |

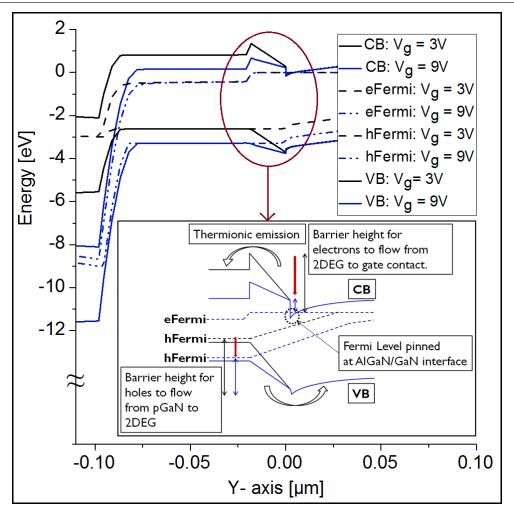

|      | mechanism at the heterojunction barrier)                                                                                                              | 86 |

| 7.1  | AlGaN/GaN heterostructure p-gate enhancement mode HEMT cross-                                                |      |

|------|--------------------------------------------------------------------------------------------------------------|------|

|      | section                                                                                                      | 91   |

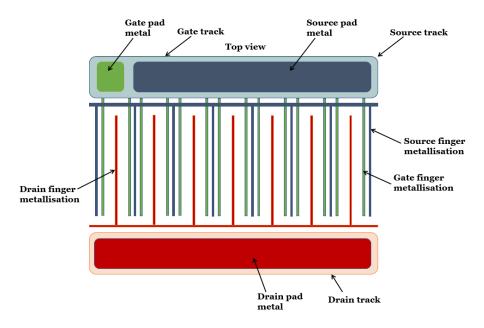

| 7.2  | AlGaN/GaN HEMT Inter - digitated layout                                                                      | 91   |

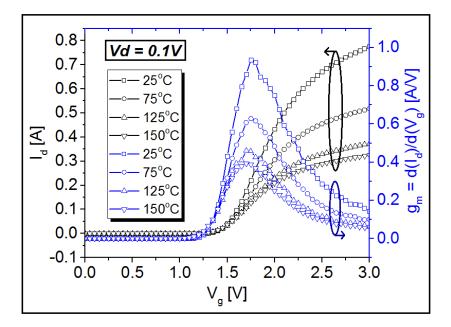

| 7.3  | GaN HEMT transfer characteristic and transconductance at room and                                            |      |

|      | increased temperatures                                                                                       | 92   |

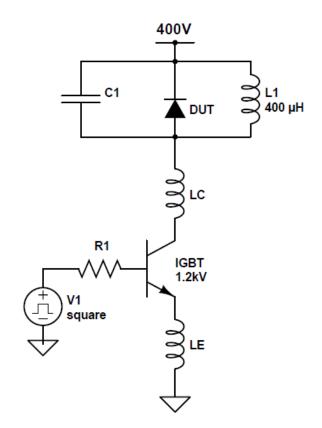

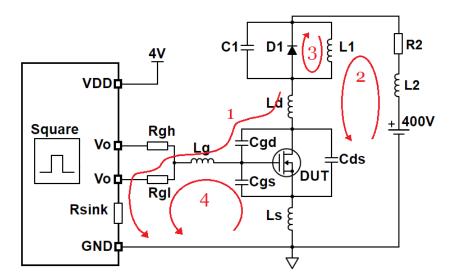

| 7.4  | Clamped inductive swithing circuit                                                                           | 93   |

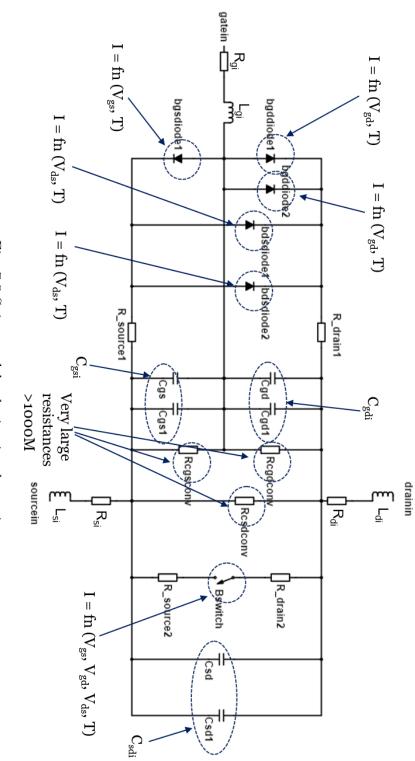

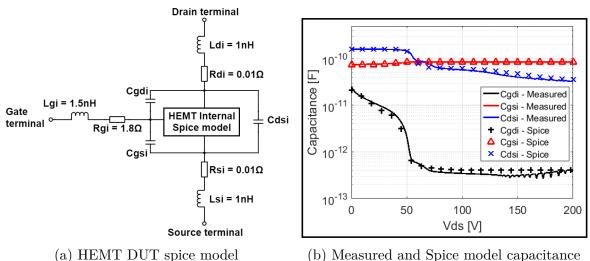

| 7.5  | Spice model sub-circuit schematic                                                                            | 94   |

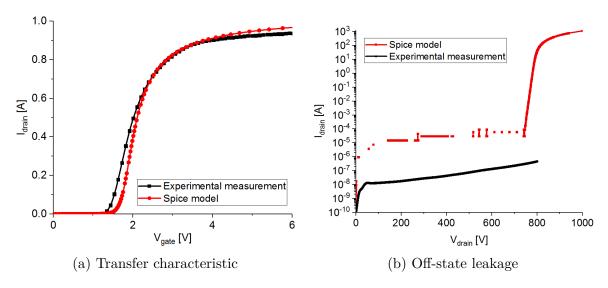

| 7.6  | GaN HEMT measured and Spice model characteristics                                                            | 95   |

| 7.7  | SPICE model parameters adjusted                                                                              | 96   |

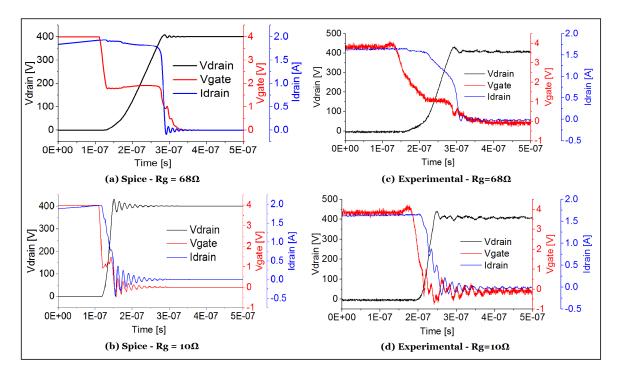

| 7.8  | Spice simulated and experimental HEMT turn-off waveforms: (a) Spice                                          |      |

|      | - $Rg = 68\Omega$ , (b) Spice - $Rg = 10\Omega$ , (c) Experimental - $Rg = 68\Omega$ , (d)                   |      |

|      | Experimental - $Rg = 10\Omega$                                                                               | 97   |

| 7.9  | HEMT turn-on waveforms with $Rg = 10\Omega$ (a) Spice simulation, (b)                                        |      |

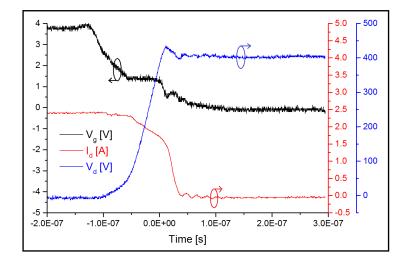

|      | Experimental                                                                                                 | 98   |

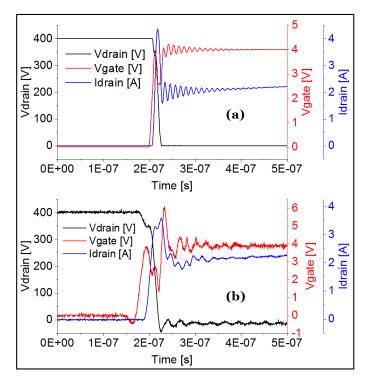

| 7.10 | dI/dt related oscillations in Spice simulated and experimental HEMT                                          |      |

|      | turn-off and turn-on waveforms: (a) Spice turn-off, (b) Experimental                                         |      |

|      | turn-off, (c) Spice turn-on, (d) Experimental turn-on $\ldots \ldots \ldots \ldots$                          | 99   |

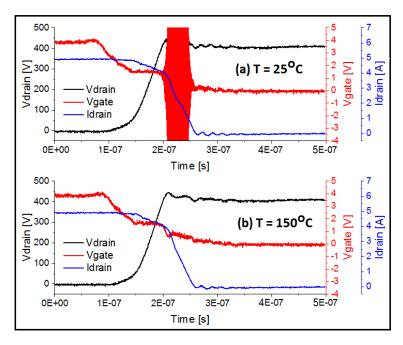

| 7.11 | Effect of temperature on experimental turn-off waveforms of HEMT device                                      | e101 |

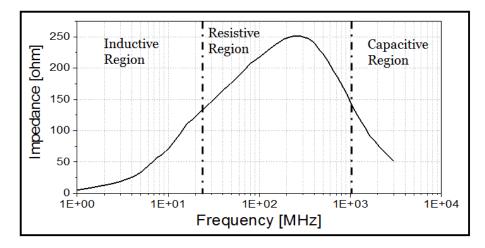

| 7.12 | Ferrite bead impedance against signal frequency $\ldots \ldots \ldots \ldots \ldots$                         | 102  |

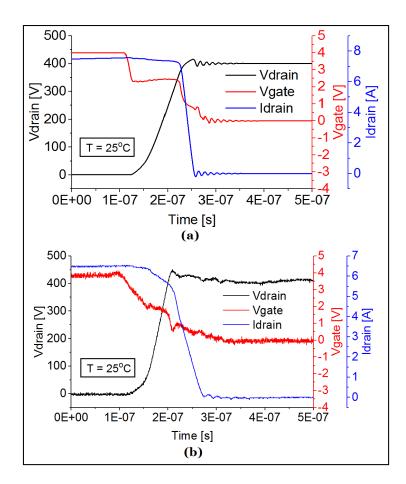

| 7.13 | Effect of ferrite bead on ringing observed in (a) Spice simulated and (b)                                    |      |

|      | experimental circuit turn-off waveforms seen in Figs. 7.10a and 7.10b $$ .                                   | 103  |

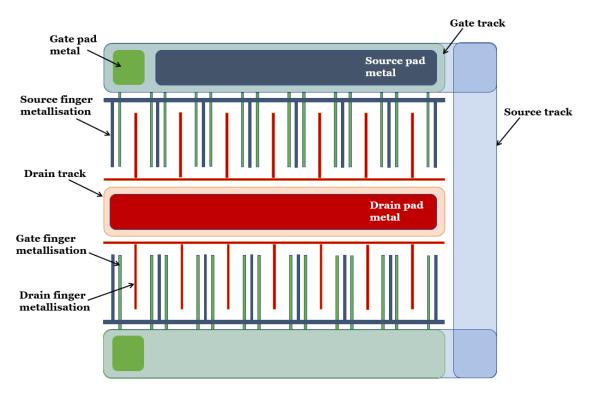

| 7.14 | Source-Drain-Source layout of a high voltage HEMT                                                            | 105  |

| 7.15 | Drain-Source-Drain layout of a high voltage HEMT $\hdots$                                                    | 105  |

| 7.16 | Transfer characteristic comparison of different layouts with y-axis as                                       |      |

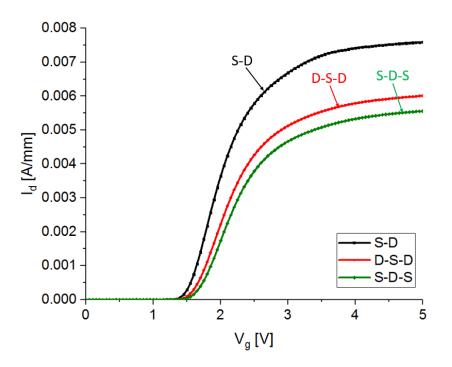

|      | current per unit gate width $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 106  |

| 7.17 | Transfer Characteristic comparison of different layouts with y-axis as                                       |      |

|      | current per unit area                                                                                        | 106  |

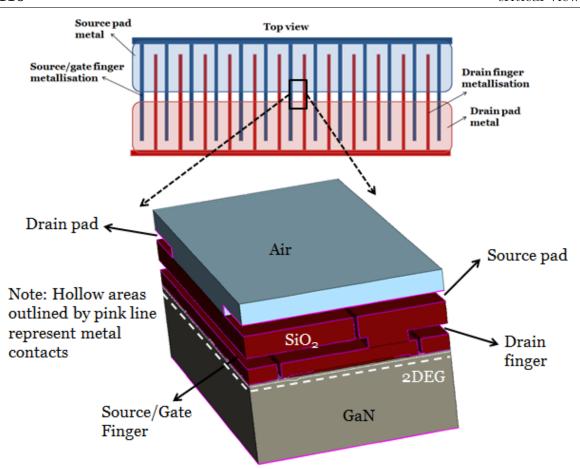

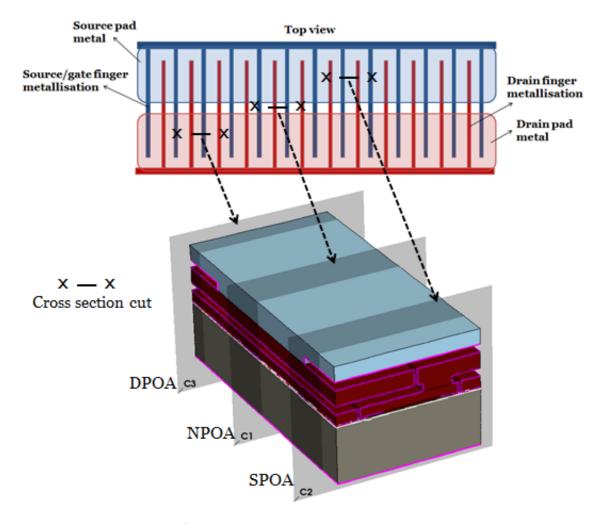

| 8.1  | Device layout (a) BPOA, (b) Conventional                                                                     | 111  |

| 8.2  | On-state comparison between AlGaN/GaN heterostructure p-gate en-                                             |      |

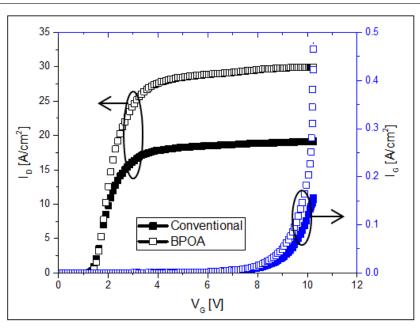

| 0.2  | hancement mode HEMT with BPOA vs conventional design                                                         | 112  |

| 8.3  | Leakage comparison between AlGaN/GaN heterostructure p-gate en-                                              | 112  |

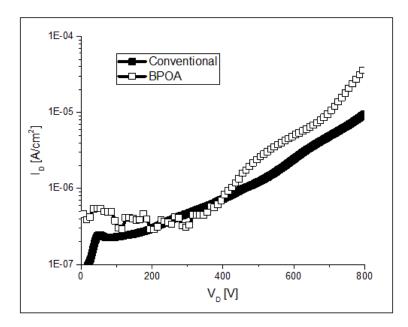

| 0.0  | hancement mode HEMT with BPOA vs conventional design                                                         | 113  |

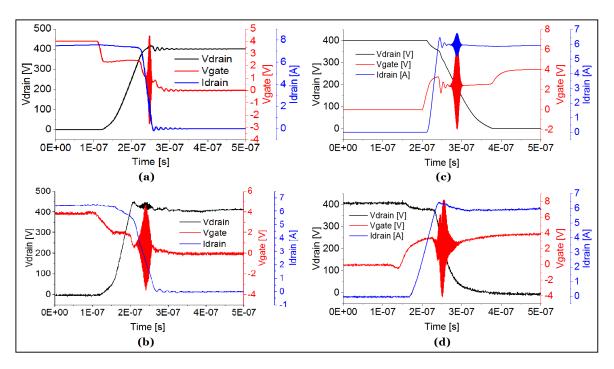

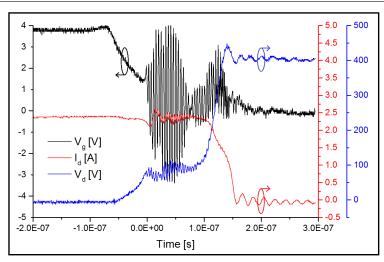

| 8.4  | BPOA layout HEMT clamped inductive switching. (400V, 3A)                                                     |      |

| 8.5  | Conventional layout HEMT clamped inductive switching. (400V, 3A) .                                           |      |

| 8.6  | 3D TCAD model of bonding pad over active (BPOA) structure                                                    |      |

| 0.0  | SE I CHE INCOURT FORMING PAR OVER ACTIVE (DI OTI) SULLCUITE                                                  | TTO  |

| 8.7  | Three locations (no pad - NPOA, source pad over active - SPOA, drain                                                                                                              |   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|      | pad over active - DPOA) in the active area of the layout that give                                                                                                                |   |

|      | different cross-sections $\ldots \ldots \ldots$                   | 7 |

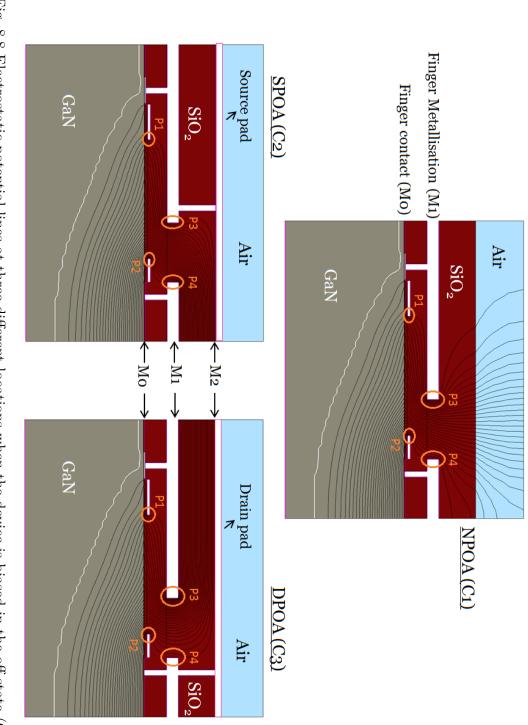

| 8.8  | Electrostatic potential lines at three different locations when the device                                                                                                        |   |

|      | is biased in the off-state (650V) $\ldots \ldots \ldots$          | 8 |

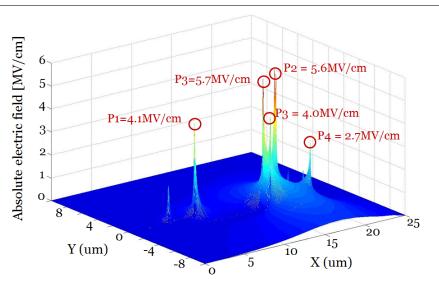

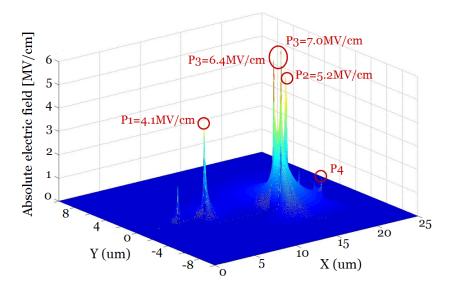

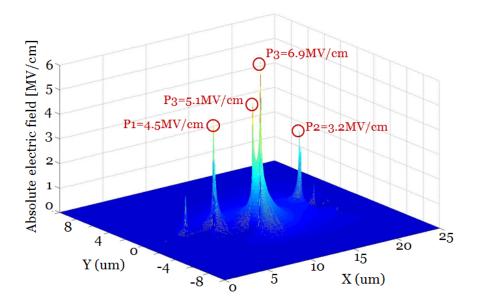

| 8.9  | Electric field peaks in SiO <sub>2</sub> at NP section of the structure                                                                                                           | 0 |

| 8.10 | Electric field peaks in SiO <sub>2</sub> at DPOA section of the structure 120 $$                                                                                                  | 0 |

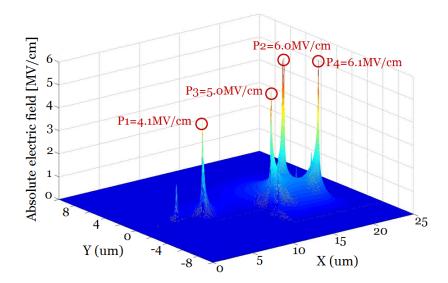

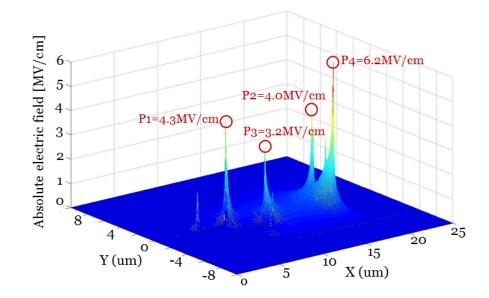

| 8.11 | Electric field peaks in SiO <sub>2</sub> at SPOA section of the structure $\ldots$ $\ldots$ 12                                                                                    | 1 |

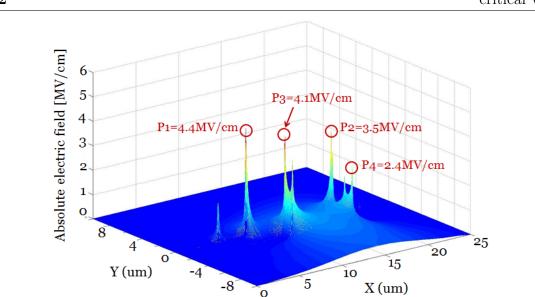

| 8.12 | Electric field peaks in $SiO_2$ at NP section of the structure after optimization 12                                                                                              | 2 |

| 8.13 | Electric field peaks in $SiO_2$ at DPOA section of the structure after                                                                                                            |   |

|      | optimization                                                                                                                                                                      | 2 |

| 8.14 | Electric field peaks in $SiO_2$ at SPOA section of the structure after                                                                                                            |   |

|      | optimization                                                                                                                                                                      | 3 |

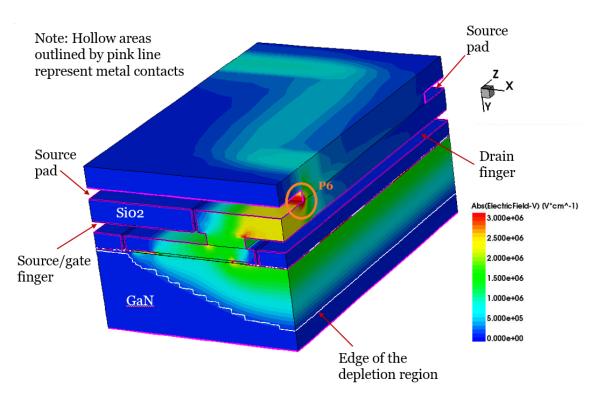

| 8.15 | Electric field peak in $SiO_2$ at pad edge $\ldots \ldots \ldots$ | 4 |

| 8.16 | (a) Field plate at pad edge (b) Electric field peak reduction in $SiO_2$ at                                                                                                       |   |

|      | pad edge                                                                                                                                                                          | 5 |

## List of tables

| 1.1 | Material properties of wide bandgap semiconductors compared to Silicon                 | 7   |

|-----|----------------------------------------------------------------------------------------|-----|

| 1.2 | Implications of the usual substrate materials for the GaN epitaxy                      | 9   |

| 4.1 | Extracted Schottky Parameters                                                          | 50  |

| 5.1 | Comparison of off-state leakage observed in experimental measurements                  |     |

|     | and TCAD model simulations                                                             | 60  |

| 5.2 | Effect of substrate connection on on-state and switching performance $% \mathcal{A}$ . | 64  |

| 5.3 | Effect of substrate connection on terminal potential in TCAD simulations               | 64  |

| 5.4 | Forward voltage drop of tested devices at room temperature and in-                     |     |

|     | creased temperatures                                                                   | 68  |

| 5.5 | Reverse recovery parameters of AlGaN/GaN Schottky diode at room                        |     |

|     | temperature and increased temperature compared with SiC Schottky                       |     |

|     | diodes and fast recovery Si diodes of similar rating                                   | 70  |

| 7.1 | State of the art Specific $R_{on}$ of different technologies for a 650V device         | 90  |

| 7.2 | HEMT switching                                                                         | 107 |

| 8.1 | Summary of electric field peaks observed in different regions of the                   |     |

|     | BPOA device                                                                            | 121 |

## List of Publications

- L. Efthymiou, G. Longobardi, G. Camuso, A. P. S. Hsieh and F. Udrea, Modelling of an AlGaN/GaN Schottky diode and extraction of main parameters, 2015 International Semiconductor Conference (CAS), Sinaia, 2015, pp. 211-214.

- L. Efthymiou et al., Zero reverse recovery in SiC and GaN Schottky diodes: A comparison, 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, 2016, pp. 71-74.

- L. Efthymiou et al., On the source of oscillatory behaviour during switching of power enhancement mode GaN HEMTs, Energies Journal, vol. 10, no. 3, 2017.

- L. Efthymiou, G. Longobardi, G. Camuso, T. Chien, M. Chen and F. Udrea, On the physical operation and optimization of the p-GaN gate in normally-off GaN HEMT devices, Applied Physics Letters, vol. 110, no. 12, 2017, pp 123502.

- F. Udrea, L. Efthymiou and G. Longobardi, Fast dV/dt and dI/dt in GaN Devices, European Centre for Power Electronics (ECPE) Workshop, March 2017.

- L. Efthymiou et al., Effect of device layout on the switching of enhancement mode GaN HEMTs, International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, 2018 (accepted).

- L. Efthymiou et al, Bonding pad over active area (BPOA) layout for lateral AlGaN/GaN power HEMTs and diodes : a critical view (under review).

#### List of Patent applications

• Field plate structure for bonding pad over active area (BPOA) layout for lateral AlGaN/GaN power HEMTs.

### Chapter 1

### Introduction

#### 1.1 Overview of the field

Power electronics is the branch of electronics that deals with processing the voltage, current, frequency and phase from a particular source into specific forms which are optimal for the desired load to be powered.

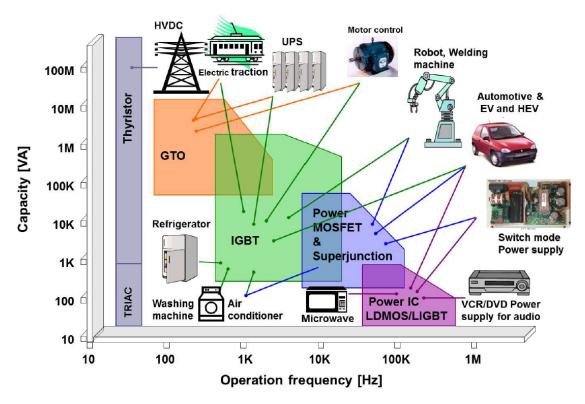

Power devices are semiconductor devices used as rectifiers or switches in power electronics systems. Applications of power semiconductor devices are quite diverse and are required in systems with a range of power ratings and operating frequencies. A good illustration of this diversity can be seen in Fig. 1.1 [1].

Power electronics is an important field of research in aspiring low-carbon economies as estimations suggest that 50% [2][3] of electrical power consumed goes through some form of power conversion before it is utilized. Power devices lay at the heart of any power electronics circuit in such a way that enhanced specifications of power devices can lead to new possibilities in the power electronics sector.

Improved power electronics technologies can enable high penetration levels of renewable energy resources, large energy savings in high voltage direct current (HVDC) transmission systems, increases in efficiency of variable speed drives for electric motors and also pave the path for widespread use of electric vehicles. Progress in the field of power electronics is therefore very important in the attempt to achieve energy savings both domestically and in industrial applications both for commercial incentives and to contribute to the reduction of carbon dioxide emissions.

The aims of research in the field of power devices is to fulfil objectives such as increasing power density, reducing the size of devices, achieving improved high temperature performance, higher frequency response, lower leakage, and lower onresistance all of which would add up to greater operating efficiency.

Fig. 1.1 Applications of power devices

#### **1.2** Brief history of power devices

Research in the field of power devices originated with the invention of the bipolar transistor at Bell labs in 1948. Power rectifiers based on germanium were reported in the 1950s [4] with a switch to Silicon as the favoured material as the decade progressed. Silicon devices have dominated the field ever since with several different concepts being introduced. The thyristor structure was proposed in 1956 [5], followed by the gate turn-off thyristor in 1961[6]. A thyristor is a solid-state semiconductor device with four layers of alternating P- and N-type materials. It acts exclusively as a bistable switch, conducting when the gate receives a current trigger, and continuing to conduct while the voltage across the device is not reversed (forward-biased). Originally, thyristors relied only on current reversal to turn them off, making them difficult to apply for direct current; newer device types can be turned on and off through the control gate signal. The latter is known as a gate turn-off thyristor, or GTO thyristor.

The introduction of the power metal-oxide-semiconductor field effect transistor (MOSFET) in 1980 [7] was an important step in the growth of the power electronics market observed at this time due to its voltage controlled gate and high input impedance. A device which combines the voltage controlled gate of the MOSFET and the bipolar

on-state conduction seen in earlier devices was introduced in the mid 80s and named the insulated gate bipolar transistor (IGBT) [8][9]. Conductivity modulation in the drift region of IGBTs allows a reduction in on-state resistance and led to devices with higher current capability. Some compromise is however needed in the maximum achievable switching frequency and the transient losses due to the charge removal required when switching. This illustrates that, depending on the application requirements, different concepts appear more suitable.

At this point an important trade-off consideration in the field of power MOSFETs can be introduced. This trade off relates to the maximum breakdown voltage which can be achieved versus the on-state resistance observed in vertical power MOSFETs. This arises when the electric field distribution in an ideal planar p-n junction is considered. The reverse bias voltage needed to reach a critical electric field relates to the length and doping of the drift region. Reduced doping or increased drift region length can lead to higher breakdown but can also lead to greater on-state resistance thus the trade-off arises. This relationship is often referred to as the limit of silicon. However, a more accurate description would identify this as the limit of the specific technology of vertical power FETs. The relationship between specific on-resistance and breakdown voltage of an ideal drift region is given by:

$$R_{on} = 4BV^2/\epsilon_0\epsilon_r\mu_n\xi_c^{\ 3} \tag{1.1}$$

The denominator in the expression above is defined as Baliga figure of merit (BFOM) [10] and is based on minimizing conduction losses in vertical power FETs. It is worth mentioning that this assumes power losses to be solely due to on-state power dissipation and applies best to operation at lower frequencies where conduction losses dominate. It is clear that this figure of merit can be used to an extent to compare the capabilities of different materials as it contains terms which are linked to the intrinsic properties of a material. This will be discussed in more detail in the following section.

The concept for a device which can surpass the limit of Silicon was first presented in literature in 1997-1998 [11][12][13]. This concept is known as the super-junction and consists of highly n-doped and p-doped pillars in the device drift region. This offers a more optimized distribution of electric field in the drift region compared to conventional devices. While conduction occurs through only one of the pillars the increase in doping is such that a significant reduction in on-state resistance can still be observed. The superjunction concept has been implemented in different technologies (MOSFETs, IGBTs) leading to significant improvements in all round performance. In conjunction with the vertical devices described so far another class of devices has received a lot of attention. These are lateral devices where the conduction path is parallel to the wafer surface rather than perpendicular. The advantage of these devices relates to their ability to be integrated monolithically with gate drive circuitry leading to the design of power integrated circuits. Similar concepts to the ones described for vertical devices are used in the design of these lateral devices with the lateral IGBT holding considerable market interest [14] and the superjunction concept applied in the lateral double diffused metal-oxide semiconductor (LDDMOS) [15].

While clever engineering has allowed the capabilities of silicon devices to be redefined for several decades, there is a case to be made for wide band-gap materials. The main materials which have received considerable attention as an alternative to silicon in power device applications are silicon carbide (SiC), gallium nitride (GaN) and diamond.

Research into wide bandgap materials for power electronics application can be traced back to the early 1990s [16][17]. The first wide bandgap device to be made commercially available was a SiC Schottky diode introduced by Infineon in 2001 [18]. Indeed that is where SiC devices have had most commercial success. In terms of three terminal devices, SiC JFETs, BJTs and MOSFETs have been introduced and are looking to compete in high voltage, high power applications [18]. The leading structures for the commercialization of GaN-based devices are high electron mobility transistors (HEMTs), metal-insulator-semiconductor FETs (MISFETs) and hetero-junction lateral Schottky diodes. For diamond devices most efforts are focused on the development of Schottky diodes however they still appear to be a long way from reaching the market. The suitability of wide bandgap materials for power device applications relates to their intrinsic properties which shall be discussed in more detail in the next section.

#### **1.3** Comparison between GaN and other materials

As mentioned earlier, when referring to power devices we refer to two types of devices; switches and rectifiers. The field in both of those disciplines is currently dominated by silicon devices. In the field of switches a variety of different device structures exist (power MOSFET, IGBT, thyristor) depending on the particular requirements of the specific application for which the device is used. Silicon rectifiers are equally important in power electronics as they find use in equipment such as boost converters and are used as free wheeling diodes in bridge inverter topologies. In the field of rectifiers the latest in silicon technology comes in the form of ultrafast recovery P-I-N diodes that utilize techniques such as carrier lifetime reduction and silicon-on insulator technologies to achieve operation at higher frequencies [19].

The dominance of silicon in the power devices industry arises from the maturity in the manufacturing process of silicon which is very reliable and low in cost. In addition to processing advantages, design of silicon devices has gone through decades of optimization allowing the best performance of the material to be extracted. However it is becoming increasingly challenging to improve the performance of silicon devices and the cost of advancements has increased dramatically.

To that effect there is very much a case of looking at alternative semiconductors with better intrinsic physical properties for use in power electronics applications. In this pursuit of new materials emphasis has been given to wide bandgap semiconductors such as Silicon Carbide (SiC) and Gallium Nitride (GaN). These materials can theoretically offer significant improvements in the areas of specific on-resistance, blocking voltage, operation at increased temperatures and switching both in terms of losses and switching frequency. A comparison of some of the most important properties of the candidate materials which can affect performance are given in Table 1.1 which has been reproduced from [18].

| Parameter                           | Silicon       | 4H - SiC      | GaN                 | Diamond        |

|-------------------------------------|---------------|---------------|---------------------|----------------|

|                                     |               |               |                     |                |

| $W_g,  \mathrm{eV}$                 | 1.12          | 3.26          | 3.39                | 5.47           |

| $E_{crit},  \mathrm{MV/cm}$         | 0.23          | 2.2           | 3.3                 | 5.6            |

| $\epsilon_r$                        | 11.8          | 9.7           | 9.0                 | 5.7            |

| $\mu_n,  \mathrm{cm}^2/\mathrm{Vs}$ | 1400          | 950           | $800/1700^{\rm b}$  | 1800           |

| BFoM <sup>a</sup> relative to Si    | 1             | 500           | $1300/2700^{\rm b}$ | 9000           |

| $n_i,  \mathrm{cm}^{-3}$            | $1 * 10^{10}$ | $8 * 10^{-9}$ | $2 * 10^{-10}$      | $1 * 10^{-20}$ |

| $\lambda$                           | 1.5           | 3.8           | $1.3/3^{c}$         | 20             |

Table 1.1 Material properties of wide bandgap semiconductors compared to Silicon

<sup>a</sup>Baliga's figure of merit for the power devices:  $\epsilon_r * \mu_n * E_{crit}^3$ <sup>b</sup>Significant difference between the bulk and the 2DEG <sup>c</sup>Difference between the epitaxial layers and the bulk material

A wider bandgap is desirable as it theoretically allows for a higher breakdown voltage per unit length of device (breakdown field,  $E_{crit}$ ). As can be seen in Table 1.1 the performance of GaN and 4H-SiC<sup>1</sup> exceed the performance of silicon by an

<sup>&</sup>lt;sup>1</sup>The prefix 4H- refers to a specific polymorph of SiC used for comparison purposes. Other polymorphs exist which are suitable for the development of power devices e.g. 6H-SiC, 3C-SiC. These may have different bandgap, mobility, saturation velocity etc. due to their different crystal structure.

order of magnitude in that respect. A wide bandgap also allows lower intrinsic carrier concentration which can affect off-state leakage. The possibility of shorter devices for the same blocking voltage as well as increased carrier mobility  $(\mu_n)$  can allow a lower on-resistance to be achieved. Furthermore, high mobility and high saturation velocity allow higher switching frequencies to be achieved and therefore a reduction in the size and weight of magnetic components used in power electronic modules. The theoretically superior nature of wide bandgap materials such as SiC and GaN to silicon is seen when calculating figures of merit used to compare the suitability of materials for power device applications.

It can be seen in Table 1.1 that using the Baliga figure of merit (BFOM) introduced earlier, GaN has a distinctive advantage over other materials, other than diamond. One area in which GaN is not as competitive is that of thermal conductivity  $(\lambda)$ .

Other than intrinsic advantages of the material there are numerous other factors which need to be considered before a commercial power device can be produced. Issues such as ease of doping, mass production capability, wafer quality, ease of processing techniques, number of masks required and production costs in general need to be taken into account. These factors provide significant challenges in utilizing new materials. That is why diamond, despite its exceptional properties, is still at very early stages of development due to difficulties in mass production, doping (in particular n-doping) and cost. SiC devices also deal with certain technology issues. For example, SiC MOSFETs have traditionally suffered from poor oxide semiconductor interface quality, which has led to large threshold voltage instability. Furthermore, use of normally-on SiC JFETs and SiC BJTs requires the design of more challenging gate driving [20].

GaN is considered a very promising material as it has several advantages over other wide bandgap semiconductors in the aspects just mentioned. One major advantage is that high quality GaN layers can be grown epitaxially on several substrates, the most significant of which being silicon. This can be done using standard silicon production lines and hetero-epitaxy on upto 8-inch wafers has been demonstrated already. On the other hand, SiC devices can only be produced on SiC substrates which are costly to produce and are only made up to 6-inch wafers, leaving SiC only able to satisfy sections of the market which require top performance at a price. Table 1.2 reproduced from [18] clearly illustrates the point discussed with GaN-on-Si costing 1/100th of the price of GaN on SiC. This thesis will thus consider the development of lateral rather than vertical GaN devices. The main drawback of a vertical device would be cost, as even though vertical GaN rectifiers with very good properties have been reported in literature [21][22], the cost of such devices makes them unrealistic in a commercial environment due to the need of a bulk GaN wafer [18].

| Substrate             | Bulk GaN | SiC          | Sapphire   | Silicon          |

|-----------------------|----------|--------------|------------|------------------|

| <b>T</b>              |          | - <b>-</b> ~ | 1.00       | ~                |

| Lattice mismatch      | none     | +3.5%        | -16%       | -17%             |

| Thermal mismatch      | none     | +33%         | -25%       | +116%            |

| Electrical resistance | low      | $low^{a}$    | $\infty$   | very $low^a$     |

| Thermal resistance    | same     | $0.3x^{a}$   | 3x         | $0.9 \mathrm{x}$ |

| Available wafer size  | 2"(3")   | 4"(6")       | up to $8"$ | any              |

| $Cost, Euro/cm^2$     | 100      | 10           | 1          | 0.1              |

Table 1.2 Implications of the usual substrate materials for the GaN epitaxy

<sup>a</sup>Only non-conductive interfaces yet

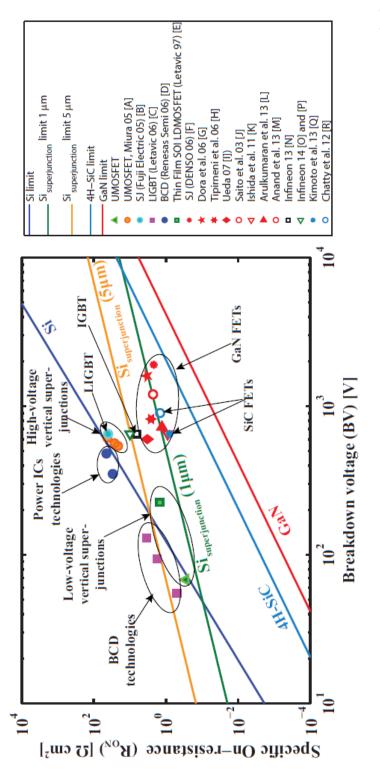

A second major advantage of GaN is that it allows the formation of hetero-structures through the use of aluminium. The formation of a heterostructure comprising of a layer of GaN and a layer of AlGaN allows a two dimensional electron gas layer to be formed close to the interface of the heterojunction; this is referred to as a 2DEG. This is a region of high carrier concentration as well as high mobility due to no additional doping being necessary for the formation of the 2DEG. The use of the 2DEG as a channel can result in low on-state resistance and fast switching. The physics behind this are explained in more detail in Chapter 2. Given the intrinsic and practical advantages of GaN for use in power devices the motivation for research in the development of GaN-based power switches and rectifiers becomes apparent. Nonetheless, while GaN devices appear to be promising due to the advantages discussed above it is worth considering for which breakdown voltage capabilities, current capabilities and frequencies of operation these advantages will best be exploited. In this respect it is again worth considering the trade-off between on-state resistance and breakdown voltage capability. The discussion earlier considered vertical MOSFET devices however the relationship given by equation 1.2 does not apply to lateral devices or superjunction devices. Therefore, the relationship does not apply to the lateral AlGaN/GaN heterojunction devices that are discussed in this thesis. It has indeed been derived that the relationship between  $R_{on}$  and BV for high voltage lateral FETs is:

$$R_{on} = BV^2/q\mu_n n_s \xi_c^2 \tag{1.2}$$

where  $n_s$  is the electron sheet charge density at the channel of the device. Note that this equation assumes a uniform electric field distribution at the surface of the drift region and thus presents an ideal case. A plot showing the relationship between specific  $R_{on}$  and BV for the different technologies is shown in Fig. 1.2 [23]. It is important to note the slope of the line for the different materials/technologies. The plot illustrates the intrinsic advantage that wide bandgap semiconductors have over Silicon devices in an ideal device. Nonetheless, it is observed that as breakdown voltage rating rises, the improvement in performance which can be achieved by using WBG materials over the Silicon SJ is reduced, with possible improvements which can be achieved being more stark at lower voltages. It is worth stating that, while this is a useful indicator, it relies on theory and thus does not take into consideration a variety of challenges which can be presented for the different technologies when attempting to increase the breakdown capability. The figure illustrates some state of the art devices for each technology to give a better comparison of where the performance of each technology currently lies. Finally, it is important to note that performance is not the only measure when considering a device for a given application with cost often being a prohibiting factor an example of which being why SiC FET devices have had a hard time displacing their Silicon counterparts.

#### 1.4 Applications of GaN power devices

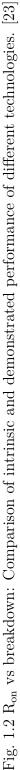

Taking into consideration the comparison between GaN and its competitors, a clearer picture appears of applications in which new GaN devices can displace the technologies which currently dominate the market. A number of devices have made an appearance in the market in recent years. A summary of the available devices is illustrated in Fig. 1.3 [24].

Fig. 1.3 Commercially available GaN devices

The majority of devices target the 100-200V voltage range and the 600-650V range. In terms of current capabilities the majority of devices are available for currents below 60A. The lower voltage capability devices would be suitable for point-of-load applications i.e. low voltage DC-DC converters for IT or consumer electronics applications. Large market potential however exists at the 600V range for applications such as power factor correction (PFC), uninterrupted power supplies (UPS), motor drives, and photovoltaic (PV) system inverters. 600V GaN devices can also find use as chargers in hybrid electric vehicles (HEV) and electric vehicles (EV), a market which is growing at an enormous pace. Future development of devices with breakdown capabilities up to 1.2kV and power ratings which can reach 7.2kW can lead to GaN devices being used in EV and HEV converters where the high frequency of operation will allow a reduction in system size, a parameter which is significant when considering mobile systems. Ultimately, if the power rating is extended enough GaN devices could find application in wind turbines (1.7kV) and rail traction systems (1.7kV-6.5kV). Nonetheless, this would be a hard market to penetrate with 60kW + systems being more suited to the use of the latest generation of Si IGBTs and even SiC MOSFETs.

Regarding applications for GaN-based Schottky diodes the starting point for market penetration would be 600-650V devices targeted for use in server and telecommunications switch mode power supplies (SMPS), PC power and lighting applications, as well as solar inverters and UPS systems. GaN Shottky diodes face a challenging market to compete in, considering the performance of the latest generation of SiC Schottky diodes which achieve very low on-state and switching losses. The advantage of GaN-based devices could be price and the ability to be included in power integrated circuits monolithically with GaN HEMTs. A more thorough comparison of AlGaN/GaN Schottky diodes against SiC Schottky diodes will be given in Chapter 4.

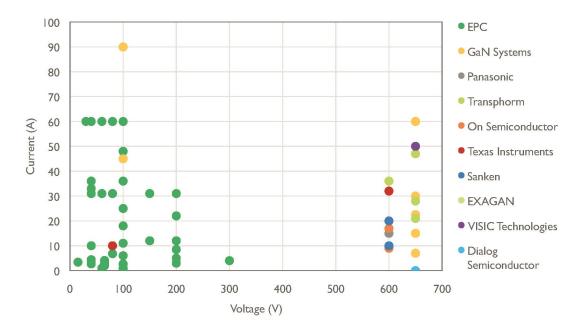

A report by *Yole development* [25] makes a prediction about the time to market of the GaN technologies and the compound annual growth rate (CAGR) that might be observed. These predictions are illustrated in Fig. 1.4. The CAGR is the mean annual growth rate of an investment over a specified period of time longer than one year. The time-line extends to 2024 and suggests a very encouraging picture with growth in large segments of the power electronics industry, especially in the mid-voltage range.

Fig. 1.4 Estimated accessible markets, growth rate and time-to-market for main GaN applications

#### 1.5 Overview of the thesis

This thesis will deal with a variety of topics concerning the design and optimization of AlGaN/GaN HEMTs and Schottky diodes with a 650V rating. Discussion will span several topics from device cross-section physics to circuit implementation and will be based on both experimental results and advanced modelling.

- In Chapter 2, the physics of the AlGaN/GaN heterojunction will be presented in more detail. Furthermore, the state of the art in AlGaN/GaN HEMTs and diodes will be presented and a discussion of the challenges that these devices face will also be discussed.

- In Chapter 3, an overview of the simulation tools used in this thesis will be given with the discussion focusing mostly on important considerations when setting up TCAD simulations of GaN-based devices.

- Chapter 4 will describe a method to extract the ideality factor, barrier height and series resistance of a lateral AlGaN/GaN heterostructure power Schottky diode using a simple I-V measurement in on-state and sub-threshold domains. An analytical model previously developed for Gallium Arsenide (GaAs) and Silicon vertical diodes [26] is applied to lateral AlGaN/GaN Schottky diodes and calibrated using extensive experimental results both at room and increased temperature.

- Chapter 5 will discuss the development of a TCAD model for a lateral AlGaN/GaN Schottky diode and offer an in depth investigation of the operation of such a device during switching. A comparison of the switching capability of the GaNbased diode with its main competitors (SiC Schottky diode, Si fast recovery diode) will then be given both experimentally and supported by simulations.

- Chapter 6 will discuss the development of the TCAD model of a p-gate enhancement mode HEMT. Through the variation of some of the gate parameters an improved understanding of the operation of the p-gate will be achieved offering the ability to optimize the design of these devices.

- Chapter 7 will discuss the switching of GaN HEMTs and the concerns that arise due to their fast switching capability. These are revealed to be both circuit and device layout related.

- Chapter 8 will offer a critical view of bonding pad over active area layouts for use in GaN HEMT devices compared with conventional layouts for both on-state and off-state performance, switching capability and reliability concerns.

- Chapter 9 will summarize and provide some conclusions for the work done as well as provide a discussion on the possible continuation of this work.

Several fabricated devices will be discussed in this thesis. It is important to note that these devices were provided by the commercial partner involved in this project, Vishay Intertechnology Inc., an American manufacturer of discrete semiconductors and passive electronic components. The devices described have not necessarily been fabricated or processed by Vishay and at times have been produced on its behalf at commercial foundry partners. Some activities in this project are subject to a nondisclosure agreement and as such certain information (e.g. precise device cross-section dimensions) will not be disclosed in this thesis. A range of reasonable values will be given where possible to aid understanding.

## Chapter 2

## GaN device physics and state of the art

This chapter deals with the device physics of GaN devices starting with a short discussion of the wafer processing challenges faced in the development of GaN-on-Si devices. This will be followed by a discussion of the AlGaN/GaN heterojunction to achieve a better understanding of the mechanisms which lead to the formation of the two dimensional electron gas that gives these devices their unique properties. Furthermore, a review of the state of the art AlGaN/GaN HEMTs and Schottky diodes will be given to provide some insight into the challenges and trade-offs faced when attempting to improve their performance.

## 2.1 Wafer processing

Epitaxial layers of GaN are most commonly grown on a silicon substrate using metalorganic chemical vapour deposition (MOCVD). MOCVD is a method used to produce single or polycrystalline thin films. It is a highly complex process for growing crystalline layers to create semiconductor multilayer structures. In contrast to molecular beam epitaxy (MBE) the growth of crystals is by chemical reaction and not physical deposition. This takes place not in a vacuum, but from the gas phase at moderate pressures. A discussion of the technical and commercial considerations associated with the two methods can be found in [27].

A typical GaN-on-Si wafer can be seen in Fig. 2.1. GaN-on-Si is far from a straightforward process and the production of high quality, crack-free GaN layers on silicon substrates is faced with many challenges [28]. These arise from the large lattice mismatch between Si and GaN which causes a large number of dislocations to appear

in the GaN channel layer. To mitigate this problem a transition layer is used before the deposition of the GaN channel layer as seen in Fig 2.1.

Fig. 2.1 Typical structure with several GaN-based layers grown on a Silicon substrate

The transition layer often consists of either a single layer of AlN/AlGaN [29] or a superlattice structure composed of several GaN/AlGaN/AlN layers [30] [31]. The quality of the epitaxial layers is of great importance as it affects bulk leakage in the off-state and the severity of current degradation mechanisms. Another major obstacle in obtaining high quality wafers is the difference in the thermal expansion coefficients of Si and GaN which causes stresses to develop during processing and film cracking to occur. It has been suggested that to effectively compensate for the tensile stress induced into the sample during cooling down, it is better to build up sufficient compressive stresses in the nitride heterostructures at the growth temperatures [32]. Other than material quality the doping of the GaN layer is of great importance. Carbon doping in the range of  $10^{16} - 10^{17}$  is often included during growth. This has been demonstrated to enhance reverse blocking capability and to suppress the vertical leakage current [33]. Nonetheless, Carbon which has a complex set of acceptor trap levels in the lower half of the bandgap [34], has also been linked with current-collapse [35][36].

## 2.2 Physical properties of the AlGaN/GaN heterojunction

A heterojunction is defined as the interface that occurs between two layers of dissimilar crystalline semiconductors. These semiconducting materials have unequal band gaps. To be able to obtain a heterostructure without compromising the quality of the crystalline structure of the two layers, the lattice constants of the two materials must be close to each other. The lattice constant of GaN and AlN is very similar as can be

Fig. 2.2 Bandgap vs Lattice constant for different semiconductors [37]

seen in Fig. 2.2. Incorporating an aluminium mole fraction, x (between x=0 and x=1) in the GaN layer leads to the formation of  $Al_xGaN_{x-1}$  with electrical and mechanical properties between those of GaN and AlN.

The difference in the band gaps of the two materials leads to band discontinuity when the two layers are brought together and this band discontinuity leads to the formation of a quantum well. The 2DEG layer is formed at the interface between the GaN channel layer and AlGaN barrier. A thorough study on the formation of the 2DEG layer was given in a highly cited paper by Ambacher et al. [38] which focuses on the electrical and structural characterization of AlGaN/GaN/AlGaN heterostructures grown by MOCVD. The study describes, in detail, other contributing factors which lead to the formation of the 2DEG other than the band discontinuity at the interface. The confinement of a high concentration of electrons at the interface to create the 2DEG can be explained further by the compensation of a positive polarization induced sheet charge. This sheet charge is caused by different spontaneous and piezoelectric polarizations of the GaN layer and the AlGaN layer. Gallium Nitride can exist in three different crystal structures: Wurtzite, Zinc blende, and Rock salt. At room temperature the most stable structure for GaN and AlN is Wurzite and is the one most commonly used. Wurzite crystalline structure exhibits spontaneous polarization. Based on its aluminium content, the AlGaN layer has a greater spontaneous polarisation  ${\cal P}_{sp}$  than GaN. Additionally, both GaN and AlN are piezoelectric materials. The piezoelectric effect is the ability of certain materials to generate an electric charge in response to

applied mechanical stress. AlN and therefore AlGaN has a smaller lattice constant than GaN therefore if AlGaN is grown on a relaxed GaN layer a piezoelectric polarisation charge ( $P_{pe}$ ) is also formed due to the strain in the AlGaN layer. These charges form a net positive charge at the AlGaN/GaN interface which is compensated by a large concentration of electrons which forms the 2DEG. A schematic illustration of these polarization charges along with the resulting hetero-junction band diagram is shown in Fig. 2.3. Note that the polarisation induced sheet charge densities and directions of the spontaneous and piezoelectric polarisations are dependent on the crystal structure so Fig. 2.3 applies to the Wurzite structure.

The density of the positive polarization charge at the AlGaN/GaN interface is in excess of  $10^{13}cm^{-2}$  in a strained  $Al_{0.3}GaN_{0.7}$ /relaxed GaN system [38]. Thus, a large concentration of carriers can be present in the 2DEG channel without any additional doping. This leads to very limited scattering in the channel and allows very high mobility values to be reached. As described, the aluminium mole fraction is an important parameter in the device as it affects the size of the polarization charge at the interface and thus the number of carriers in the 2DEG channel.

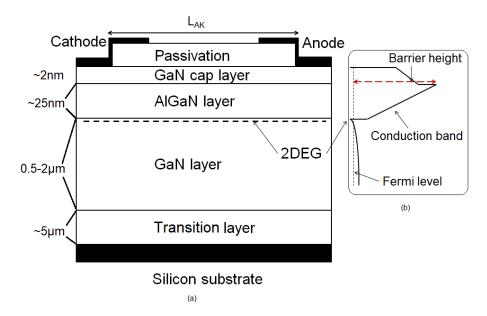

## 2.3 Typical AlGaN/GaN Schottky diode structure

The typical structure of a lateral AlGaN/GaN Schottky diode will be presented as well as a brief overview of the operation of such a device. Figure 2.4 shows a typical lateral AlGaN/GaN Schottky diode. The device consists of a Silicon substrate and GaN-based epitaxial layers mentioned in section 2.1 as well as three terminals; the anode, cathode and substrate. The cathode and substrate terminals are Ohmic contacts and the anode is a Schottky contact.

Fig. 2.4 Typical lateral AlGaN/GaN Schottky diode structure

The rectifying characteristics of the device come from the anode Schottky contact. Depending on the metal used for the contact, a potential barrier forms which blocks current flow from cathode to anode when the device is reverse biased. When a forward bias voltage is applied current flows from the anode though the 2DEG to the cathode. It is important that the threshold voltage is low to limit on-state losses. A popular design characteristic with lateral topology GaN SBDs is the use of a recessed anode [39][40][41] as seen in Fig. 2.5.

In this structure, the anode Schottky contact is made directly to the 2DEG by etching through the AlGaN barrier before depositing the contact. This causes a decrease in the turn-on voltage of the device thus limiting on-state losses but can lead to higher leakage in the off-state. Tunnelling at the Schottky contact which is dependent on the magnitude and spatial distribution of the electric field peak at the edge of the anode contact [42] is one of the major concerns. An example of such a recessed anode device is reported in [39] with an onset voltage as low as 0.43V and a

Fig. 2.5 Typical lateral AlGaN/GaN recessed Schottky diode structure

reverse blocking capability greater than 1000V. Nonetheless, the leakage observed is considerable despite the use of carbon doping in the GaN layer to suppress it. One of the most important arguments for the development of GaN heterostructure diodes is their unipolar nature which can allow negligible reverse recovery to be achieved during switching compared to the bipolar Silicon PIN diodes. Chapter 5 will focus on specific issues concerning the operation of AlGaN/GaN Schottky diodes including their switching capability through the development of a TCAD model of a test device and experimental comparison to other state of the art technologies. A brief overview of several other aspects which concern the design of lateral AlGaN/GaN diodes (field plate design, passivation, bulk leakage, current collapse) which are also encountered in HEMTs will be discussed in the next section.

## 2.4 AlGaN/GaN High Electron mobility transistor