### Daniel Filipe Simões Malafaia

Frontend em tempo real para Cognitive Radio inspirado na Cóclea Humana

Real Time Front-end for Cognitive Radio Inspired by the Human Cochlea

"Any radio with the capacity to jump around the spectrum optimising for power, range and required data rates, will, at the very least, require an extremely flexible RF front end."

— John Walko

### Daniel Filipe Simões Malafaia

### Frontend em tempo real para Cognitive Radio inspirado na Cóclea Humana

# Real Time Front-end for Cognitive Radio Inspired by the Human Cochlea

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requesitos necessários à obtenção do grau de Mestre em Engenharia Eletrónica e Telecomunicações, realizada sob a orientação científica de José Manuel Neto Vieira, Professor do Departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro

### o júri / the jury

| presidente / president       | Professor Doutor Tomás António Mendes Oliveira e Silva<br>Professor Associado da Universidade de Aveiro (por delegação da Reitora da Uni-<br>versidade de Aveiro) |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vogais / examiners committee | <b>Professor Doutor Roberto Gómez Garcia</b><br>Professor Associado, Universidad de Alcalá                                                                        |

|                              | <b>Professor Doutor José Manuel Neto Vieira</b><br>Professor Auxiliar, Universidade de Aveiro (orientador)                                                        |

|                              | Professor Doutor Nuno Miguel Gonçalves Borges de Carvalho<br>Professor Associado com Agregação, Universidade de Aveiro (co-orientador)                            |

### agradecimentos / acknowledgements

O autor deseja agradecer ao orientador José Neto Vieira, que sempre prestou toda a ajuda necessária para o avanço e conclusão desta tese. Ao coorientador Nuno Borges por todas as suas informações e disponibilidade prestada. Ao José Pedro Magalhães que não só criou alicerces para tornar esta tese possível, como trabalhou comigo para o progresso da mesma. Ao Teófilo Monteiro que também teve um papel importante neste projecto. Diogo Ribeiro, que me ajudou com os equipamentos do laboratório de RF. Ao Arnaldo Oliveira e Nelson Silva por toda a ajuda prestada na área da computação reconfigurável. Ao Hugo Mostardinha por todo o apoio no laboratório de RF. Aos meus amigos Pedro Costa e Bruno Pereira que me acompanharam desde o início do curso até à conclusão da tese. Aos meus pais e irmão que me têm acompanhado desde sempre, aos meus primos que espero que tenham a hipótese de também agradecer aos familiares quando acabarem a sua tese, e ao resto da minha família, tias, tio e aos meus avós que me criaram. A todos os outros que não couberam neste agradecimento mas que de alguma forma me ajudaram, o meu obrigado.

| Palavras-chave | Bancos de Filtros Híbridos, Rádio Cognitivo, Rádio Definido por Software,<br>FPGA, Engenharia Reversa, Medições em RF, Processamento de Sinal<br>Digital em Tempo Real                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Resumo         | Nesta tese vamos discutir a implementação e desenvolvimento de um front-<br>end inspirado na cóclea humana que é capaz de amostrar sinais RF com uma<br>larga largura de banda e gama dinâmica. Este front-end usa um multiplexer<br>de RF de 8 canais amostrado por uma placa com 8 ADCs a funcionar a<br>250MSPS. Uma placa de desenvolvimento com uma FPGA controla a ADC<br>e implementa os filtros de síntese digitais e liga a um computador pessoal<br>para transferir toda a informação e mudar os coeficientes dos filtros em<br>tempo real. |  |  |  |

| Keywords | Hybrid Filter Banks, Cognitive Radio, Software Defined Radio, FPGA,<br>Reverse Engineering, RF Measurements, Real-time Digital Signal Processing                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abstract | In this thesis it will be discussed the real time implementation and develop-<br>ment of a front-end inspired by the Human Cochlea that is able to sample RF<br>signals with a large bandwidth and dynamic range. This front-end uses an 8<br>channel RF multiplexer sampled by an 8 channel 250MSPS ADC board. A<br>FPGA board controls the ADC, implements the digital synthesis filter bank<br>and connects to a personal computer to transfer the data and to change the<br>filters in real-time. |

# Contents

| $\mathbf{C}$ | onter                                  | nts                                                                                                                                                                                                                                                              | 1                                                                                              |

|--------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| N            | omer                                   | nclature                                                                                                                                                                                                                                                         | 4                                                                                              |

| Ι            | $\mathbf{Int}$                         | roduction                                                                                                                                                                                                                                                        | 6                                                                                              |

| 1            | Rad<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | lio - State of the art         The radio technology         Software Defined Radio         Cognitive Radio         Analog to Digital Converters         Author publications                                                                                      | 7<br>7<br>8<br>9<br>10<br>10                                                                   |

| II           | Bi                                     | o-Inspired front-end                                                                                                                                                                                                                                             | 11                                                                                             |

| 2            | Coc<br>2.1<br>2.2<br>2.3<br>2.4        | Hear radio         Human Auditory System         Proposal for an SDR front-end based on hybrid filter banks         2.2.1         Front-End proposal         2.2.2         Hybrid Filter Banks         Digital Signal Processing         Reconfigurable Hardware | <b>12</b><br>12<br>14<br>14<br>16<br>16<br>16                                                  |

|              | 2.5<br>2.6                             | 2.4.1FPGA2.4.2VHDLFML605 board based in Virtex6 XILINX FPGA2.5.1Integrated synthesis environment2.5.2ML605 board4DSP FMC108 8-ADC 250MSamples board                                                                                                              | 16<br>17<br>18<br>18<br>18<br>18<br>19                                                         |

|              | 2.7<br>2.8<br>2.9                      | The Cochlea analog filter bank                                                                                                                                                                                                                                   | <ul> <li>21</li> <li>23</li> <li>25</li> <li>25</li> <li>26</li> <li>28</li> <li>29</li> </ul> |

|          |                                               | 2.9.4.1       Test 1                                                                                                                                                                                                                                                    | 32                               |

|----------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| II       | IA                                            | Accurate Measurements in RF                                                                                                                                                                                                                                             | 35                               |

| 3        | Acc                                           | 8                                                                                                                                                                                                                                                                       | 36                               |

|          | 3.1                                           | Matlab code development for interaction with a GPIB Oscilloscope and Signal                                                                                                                                                                                             |                                  |

|          | 3.2                                           | Generator                                                                                                                                                                                                                                                               | 36                               |

|          |                                               | function                                                                                                                                                                                                                                                                | 36                               |

|          | 3.3                                           | Characterization of the Oscilloscope                                                                                                                                                                                                                                    | 37                               |

|          |                                               | 3.3.1 Used material                                                                                                                                                                                                                                                     | 38                               |

|          |                                               | 3.3.2 Experimental assembly                                                                                                                                                                                                                                             | 38                               |

|          |                                               | 3.3.3 Procedure to the first experiment                                                                                                                                                                                                                                 | 40                               |

|          |                                               | 3.3.4 Procedure to the second experiment                                                                                                                                                                                                                                | 41                               |

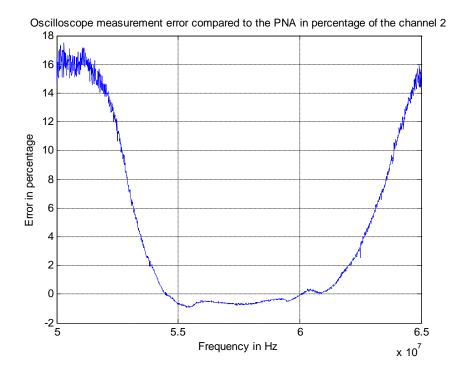

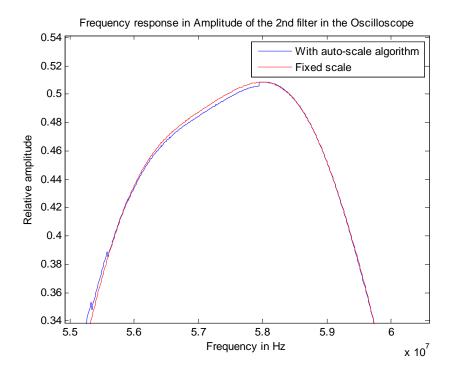

|          |                                               | 3.3.5 Result analysis                                                                                                                                                                                                                                                   | 41                               |

|          |                                               | 3.3.6 Results                                                                                                                                                                                                                                                           | 41                               |

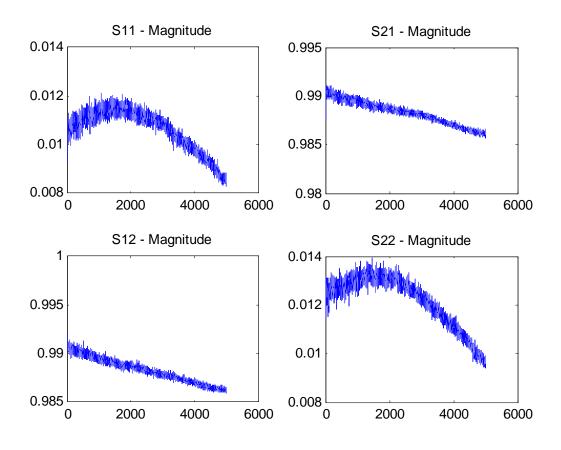

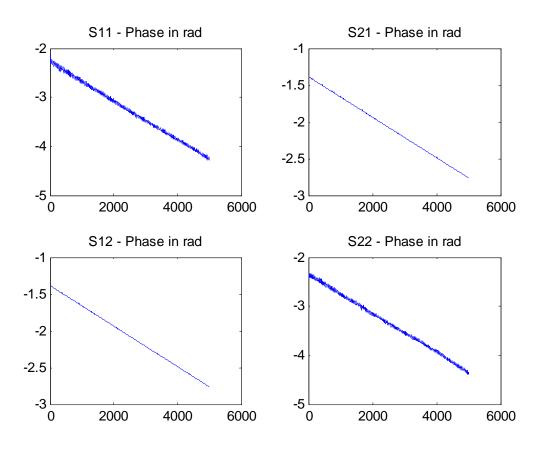

|          | 3.4                                           | Characterization of the cables                                                                                                                                                                                                                                          | 44                               |

|          |                                               |                                                                                                                                                                                                                                                                         | 44                               |

|          |                                               | 3.4.2 Experiment                                                                                                                                                                                                                                                        | 45                               |

| I۱       | / R                                           | Realtime Cochlear Front-End                                                                                                                                                                                                                                             | 49                               |

| <b>4</b> | Har                                           | dware development and characterization                                                                                                                                                                                                                                  | 50                               |

|          | 4.1                                           | 4.1.1 Performance and Resource Utilization Benchmark for realtime imple-                                                                                                                                                                                                | 50                               |

|          |                                               | mentation of FIR filters                                                                                                                                                                                                                                                | 50                               |

|          |                                               | 4.1.2 Creating firmware to interact with a laptop via serial port for a future                                                                                                                                                                                          |                                  |

|          |                                               | change in the coefficients of FIR filters in real-time                                                                                                                                                                                                                  | 52                               |

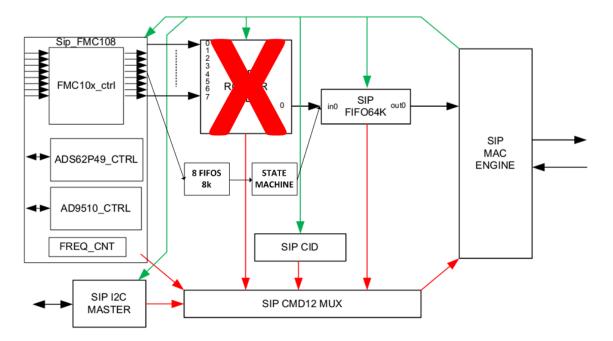

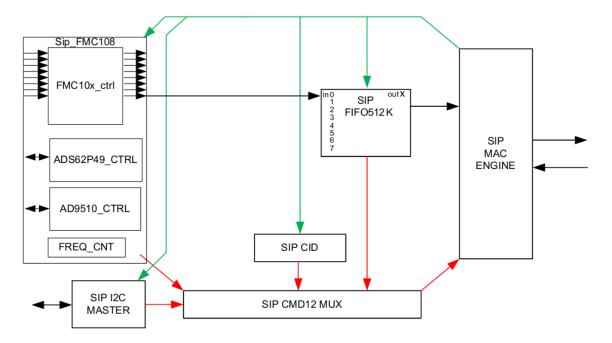

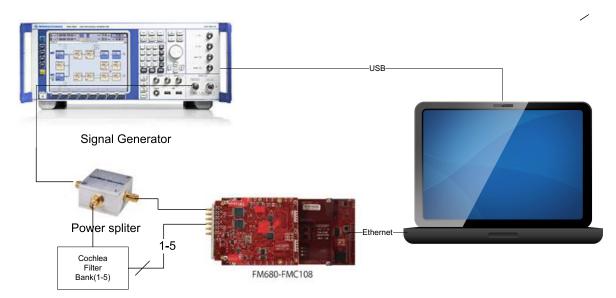

|          | 4.2                                           | 4DSP solution overview                                                                                                                                                                                                                                                  | 52                               |

|          | 4.0                                           |                                                                                                                                                                                                                                                                         |                                  |

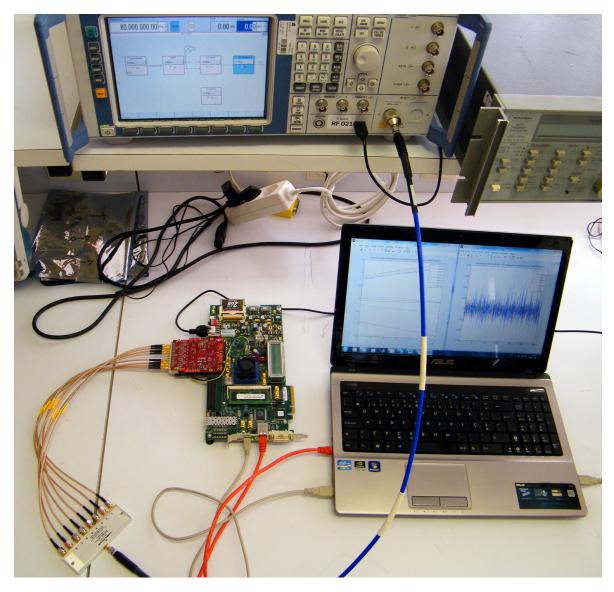

|          | 4.3                                           | Initial tests with the firmware                                                                                                                                                                                                                                         | 53                               |

|          | $\begin{array}{c} 4.3\\ 4.4\end{array}$       | Initial tests with the firmware $\dots \dots \dots$                                                                                                                     | 53                               |

|          | 4.4                                           | Initial tests with the firmware                                                                                                                                                                                                                                         |                                  |

|          |                                               | Initial tests with the firmware $\dots \dots \dots$                                                                                                                     | 53<br>53                         |

|          | 4.4                                           | Initial tests with the firmware                                                                                                                                                                                                                                         | 53<br>53<br>55                   |

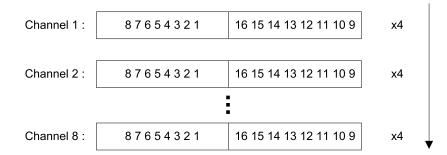

|          | 4.4                                           | Initial tests with the firmwareCreation of a protocol to communicate between Matlab and the C++ programreceiving the ADC dataReview and amendment of the code C + + and VHDL to support simultaneoussampling of the 8 ADCs4.5.1VHDL                                     | 53<br>53<br>55<br>55             |

|          | 4.4<br>4.5                                    | Initial tests with the firmwareCreation of a protocol to communicate between Matlab and the C++ programreceiving the ADC dataReview and amendment of the code C + + and VHDL to support simultaneoussampling of the 8 ADCs4.5.1 VHDL4.5.2 C++                           | 53<br>53<br>55<br>55<br>61       |

|          | 4.4                                           | Initial tests with the firmwareCreation of a protocol to communicate between Matlab and the C++ programreceiving the ADC dataReview and amendment of the code C + + and VHDL to support simultaneoussampling of the 8 ADCs4.5.1 VHDL4.5.2 C++ENOB of the ADCs           | 53<br>53<br>55<br>55<br>61<br>63 |

|          | <ul><li>4.4</li><li>4.5</li><li>4.6</li></ul> | Initial tests with the firmwareCreation of a protocol to communicate between Matlab and the C++ programreceiving the ADC dataReview and amendment of the code C + + and VHDL to support simultaneoussampling of the 8 ADCs4.5.1 VHDL4.5.2 C++ENOB of the ADCs4.6.1 ENOB | 53<br>53<br>55<br>55             |

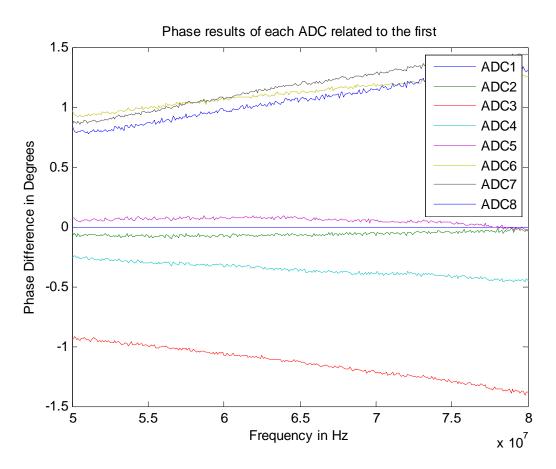

|          | 4.4<br>4.5                                    | Initial tests with the firmware                                                                                                                                                                                                                                         | 53<br>53<br>55<br>61<br>63<br>63 |

|          | <ul><li>4.4</li><li>4.5</li><li>4.6</li></ul> | Initial tests with the firmwareCreation of a protocol to communicate between Matlab and the C++ programreceiving the ADC dataReview and amendment of the code C + + and VHDL to support simultaneoussampling of the 8 ADCs4.5.1 VHDL4.5.2 C++ENOB of the ADCs4.6.1 ENOB | 53<br>53<br>55<br>55<br>61<br>63 |

|     | 4.9                                    | 4.8.1<br>4.8.2<br>Recons<br>4.9.1<br>4.9.2<br>4.9.3 | Material used                                                                                                                                                                                                                                                                        | 71<br>72<br>73<br>73<br>74<br>75                                                   |

|-----|----------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

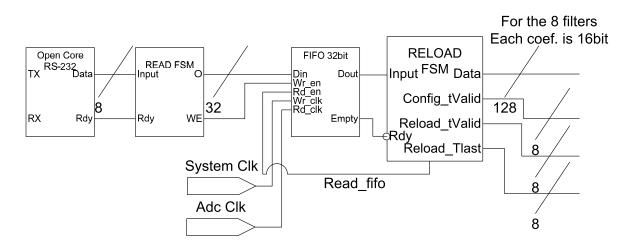

|     | <b>Rea</b><br>5.1<br>5.2               | Impler                                              | Implementation of the digital Syntheses Filter Bank on FPGA         Inentation of FIR filters         Inentation of reconfigurable FIR filters via Serial Port         Studying the reloadable coefficients on the FIR Compiler         Serial Protocol         Implemented Hardware | <b>77</b><br>77<br>78<br>78<br>79<br>79                                            |

| V   | Co                                     | onclus                                              | ions and Future work                                                                                                                                                                                                                                                                 | 81                                                                                 |

| 6   | Con                                    | clusio                                              | ns and Future work                                                                                                                                                                                                                                                                   | 82                                                                                 |

| VI  | A                                      | nnexe                                               | S                                                                                                                                                                                                                                                                                    | 83                                                                                 |

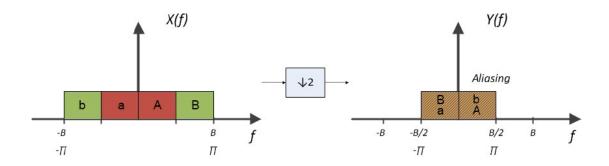

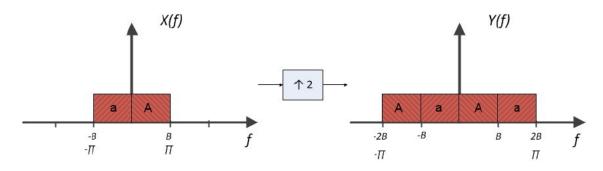

|     | <b>Ann</b><br>7.1<br>7.2<br>7.3<br>7.4 | Decim<br>Interpe<br>Equali                          | ng                                                                                                                                                                                                                                                                                   | <ul> <li>84</li> <li>84</li> <li>85</li> <li>86</li> <li>87</li> <li>89</li> </ul> |

| Bił | oliog                                  | raphy                                               |                                                                                                                                                                                                                                                                                      | 94                                                                                 |

| Bib | oliog                                  | raphy                                               |                                                                                                                                                                                                                                                                                      | 95                                                                                 |

# Nomenclature

| ADC or A/D     | Analog-to-Digital Converter           |

|----------------|---------------------------------------|

| ASIC           | Application Specic Integrated Circuit |

| DAC or D/A     | Digital-to-Analog Converter           |

| dB             | Decibel                               |

| DDR            | Double data rate                      |

| DSP            | Digital Signal Processing             |

| ENOB           | Effective Number Of Bits              |

| $\mathbf{FFT}$ | fast Fourier transform                |

| FIFO           | First In, First Out                   |

| FIR            | Finite impulse response               |

| FMC            | FPGA Mezzanine Card                   |

| FPGA           | Field-Programmable Gate Array         |

| FSM            | Finite-State Machine                  |

| GPIB           | General Purpose Interface Bus         |

| GPS            | Global Positioning System             |

| HFB            | Hybrid Filter Bank                    |

| Hz             | Hertz                                 |

| IIR            | Infinite impulse response             |

| LUT            | Lookup table                          |

| MAC            | Media Access Control                  |

| MATLAB         | MATrix LABoratory                     |

| PC             | Personal Computer                     |

| PLL            | Phase lock loop                       |

| PNA   | general-Purpose Network Analysis                   |

|-------|----------------------------------------------------|

| RF    | Radio Frequency                                    |

| SDR   | Software Defined Radio                             |

| SINAD | ${\it Signal-to-Noise-and-Distortion}$             |

| SMA   | SubMiniature version A                             |

| SNR   | Signal-to-Noise Ratio                              |

| SPI   | Serial Peripheral Interface Bus                    |

| SPS   | Samples Per Second                                 |

| txt   | Text file                                          |

| UART  | $Universal \ a synchronous \ receiver/transmitter$ |

| USB   | Universal Serial Bus                               |

| VHDL  | VHSIC Hardware Description Language                |

| VNA   | Vector network analyzer                            |

Part I Introduction

### Chapter 1

### Radio - State of the art

### 1.1 The radio technology

The radio technology is all the technology used for wireless communication based on transmission and reception of an electromagnetic signal, which may be broadcasted, for example the transmission of television signals and GPS, or point-to-point such as WiFi or Bluetooth.

In recent years there has been a rapid spread and evolution of this technology caused by a continuous demand for higher data transfer rates, reliability, service quality, autonomy and mobility of the equipment. With the evolution of photolithography it has been possible to develop radio equipment with low dimensions and reasonable autonomy.

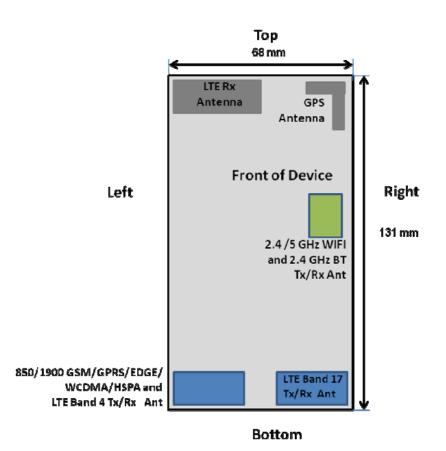

However, due to the great diversity of communication standards and protocols that operate on different radio bands caused the integration in silicon to be complex, and often an individual integrated circuit is used, independently, for each desired communication standard. So, instead of a device having only a universal radio system, it's common to have a large number of frontends, which compromises the autonomy, reliability and cost of the device.

The incorporation of a large number of radio front-ends raises serious problems to the manufacturers. The most complex being the interference between the radios within the device or with the exterior. To minimize this interference, it's common to build analog filters that are constructed so that the radio signal fulfils a given spectral mask. The development of these filters is however complex and expensive, especially if it is dimensioned for high frequencies of operation.

Figure 1.1: A common smartphone today with five different antennas and respective radios (Galaxy 2 LTE)[1]

Another problem is the non-linearity of various electronic components that are used in the radio. These components affect the original signal, and create once again the need to increase the complexity of the radio in order to offset all of these non-linearities.

Thus, the evolution of wireless communications technology will necessarily increase in the digital domain of the radio, as has been taking place in other areas of mobile technology. This evolution will allow to overcome problems such as the quality factor of the analog filters and the creation of phase or heat noise by electronic components used in the analog domain.

### 1.2 Software Defined Radio

The Software-Defined Radio was first introduced by Joseph Mitola as a concept of the future of the radio [2].

To Mitola, a radio would be able to modulate and demodulate any signal entirely in software, regardless of the standard, operating frequency or bandwidth of the signal. The transmitter had, in this vision, the ability to create any waveform, and translates it to any frequency to be later converted to the analog domain, by an DAC, and then amplified and sent. On the other hand the receiver should collect a certain bandwidth of the spectrum, amplify it and convert it to the digital domain, with an ADC. After that conversion the process of detection and demodulation of the signal would be carried by software. If we assume that the resources needed to implement the Software-Defined Radio are able to work at a satisfactory bandwidth, then we can create a multi-band operation mobile radio with lower production cost, ability of adapting to new techologies and performance optimization[3]. Besides this, an SDR provides an universal front-end, i.e. the same front-end can be used for various standards and can operate in different frequency bands or with different protocols. Moreover, unlike traditional approaches, this radio enables simultaneous reception of several channels. Being another benefit of this type of radio the ability to add any new functionality with a simple software update.

Despite the enormous potential that this concept has, in reality there are some technological problems that affect this implementation:

- The antennas need to have a high bandwidth and low losses;

- The amplifiers must have wide linear dynamic range of operation and low power consumption;

- The A/D and D/A must have a high sample rate, high resolution and dynamic range, high bandwidth, low cost and low power consumption;

- The digital processing units (DSP) must be capable of operating at high speeds to process the high bandwidth signals in real time.

There are already in the market devices that are named as "Software-Defined Radios", such as the USRP[4] and WARP [5]. These systems are primarily directed to research and enable bandwidths of about 100MHz. In its receiver architecture there is a demodulator that translates the signal to an intermediate frequency and then the resulting signal is sampled using two ADCs with a sampling frequency of about 160MSamples per second and 16-bit resolution. The processing is performed with a combination of DSPs and a FPGA, thus providing the possibility of reprogramming and reconfigure the system.

### 1.3 Cognitive Radio

Traditional wireless networks work in a license-free spectrum, with is called the ISM bands, the ISM bands are parts of the radio spectrum used for personal, industrial, scientific and medical uses. As these bands became crowded with all the new uses, as for example WiFi and Bluetooth, the need for a new system is becoming increasingly important. The expected solution will be the Cognitive Radio.

Cognitive radio is a system based on a Dynamic spectrum access (DSA) from a secondary and unlicensed user. The DSA works by opportunistically accessing a licensed spectrum band owned by the so called "primary users", this access, nevertheless, is subject to some regulations. The usage of this method would be expected to alleviate the current spectrum usage.

Cognitive Radios work by sensing the licensed bands and detecting the occupation of those. If one of those spectrum bands are temporary free then secondary users will occupy it.

However the practical implementation of such devices is surrounded by several challenges both in software and hardware. First, there's a need of synchronization, when two communicating devices decide to change band, they must synchronize with each other to resume the communication. Therefore, there is a need to create protocols to allow a share of information about the available frequencies list in each location of the devices, bandwidth and type of modulation that is going to be used.

In the Hardware there's necessary to sense the entire viable spectrum and detect witch bands are being already used. If the band is not being currently used, the CR should be able to change the frequency of the transmission to allocate it into the available band. It should also detect if any of the primary users want to start to use their rightful band and then stop the transmission.

### **1.4 Analog to Digital Converters**

The A/D converter is a key component of a Software-Defined Radio and also one of the key elements that hider to implement this type of architecture.

One of the desirable properties of an ADC is the possibility to sample a large frequency spectrum. However, for large bandwidths of operation, in the order of GHz, with the present technology we start to have a low ENOB. The decreasing dynamic range for these bandwidths would create quantization errors that will limit the reception in this type of radio.

Thus the conversion between the analog domain and digital is technological limited by the ADC. It would be desirable that they had:

- A high number of quantization bits in order to guarantee a high dynamic range;

- A wide dynamic range so that signals with high power will not cause other information with lower values to be lost;

- A large sampling frequency to cover a large bandwidth;

- Reduced price and power consumption.

It's not expected that these needs are met in the coming years, so need to find alternatives. Currently the best ADC in the commercial market is the ADC12D1800 [6] from Texas Instruments with 3.6GSPS and 12bit with an ENOB of 9.4bits and a SNR of 58.5dB, and typically consumes 4.4W.

### 1.5 Author publications

As the result of the work done by the author to this thesis the following publication in a conference was approved and it will be published in:

D. Malafaia, J. Magalhães, J. Vieira "Real Time Front-end for Cognitive Radio Inspired by the Human Cochlea" RWW, Texas, 2013

# Part II

# **Bio-Inspired front-end**

### Chapter 2

### Cochlear radio

### 2.1 Human Auditory System

Nature have found a way to create a sampling system that can sample a large bandwidth without high power signals effecting low power ones thus maintaining the dynamic range of the system[7].

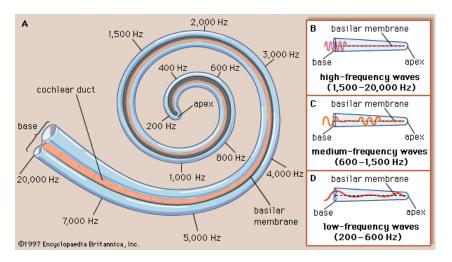

Figure 2.1: Analysis of sound frequency in the cochlea[8]

This was achieved through evolution of the auditory system of mammals. Humans can cope with a dynamic range of 120dB and several octaves of bandwidth.

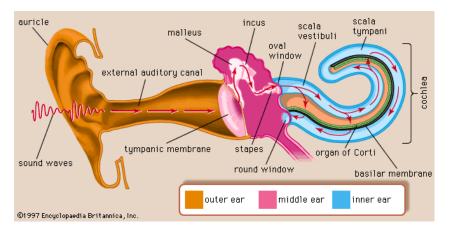

Figure 2.2: Human hearing mechanism[9]

As we can see at figure 2.2 it works as follows: the sound enters in the ear auricle and is guided by the external auditory canal to the tympanic membrane. Struck by the soundwaves, the tympanic membrane oscillates and make the ossicular chain (malleus, incus and stapes bones) reproduce and amplifies the oscillation into the inner ear and later enter in a curled tube located at the inner ear the cochlea. This is important because it provides the impedance matching between the outer ear and the inner ear. The cochlea then contains several membranous sections, which are filled with watery fluids. The ossicular chain vibrate the fluid, thus making nerve terminations, hair cells, in the basiliar membrane to sense these mechanical vibrations and convert them into electrical pulses. The hair cells convert the signal with a low sampling frequency and a low equivalent number of bits, so this is where the cochlea shows its fundamental importance by dividing the input signal in bands so that a single hair cell will have only a small band to convert, achieving then the incredible performance of the human hearing.

Later the electrical pulses are then sent via the cochlear nerve and travel then trough the nervous system reaching the primary auditory cortex in the brain where they are processed[10].

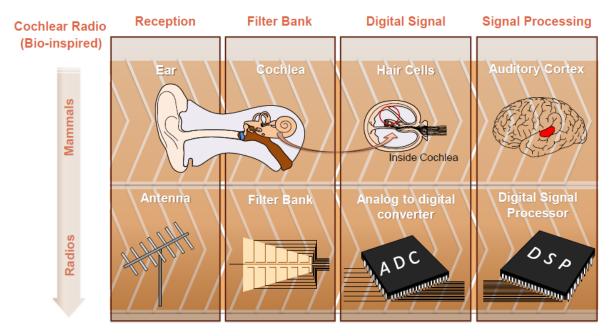

Figure 2.3: Analogy between the auditory system and RF[11]

Creating an analogy to RF, as show in figure 2.3 we can say that the ear auricle works as an antenna, the external auditory canal as a waveguide, the cochlea as an filter bank, the nerve terminations as mid-end ADCs, the nervous system as a data-bus and the primary auditory cortex is then a DSP.

### 2.2 Proposal for an SDR front-end based on hybrid filter banks

### 2.2.1 Front-End proposal

Using the mammals auditory system as a guideline we can create an alternative for the radio front-ends used nowadays and create a radio for Cognitive Radio that could achieve the requirements for the ideal Software Defined Radio by ensuring a high-bandwidth operation while maintain a high dynamic-range. The proposal is the following:

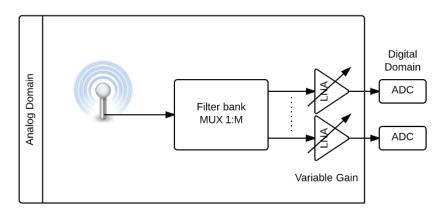

Figure 2.4: Front end proposal

The RF signal coming from the antenna is divided into M contiguous frequency bands, through a bank of analog high-frequency filters. These bands are passed to an intermediate frequency and are then converted to the digital domain with an ADC for each channel. As the spectrum of the input signal is divided into M signals with a fraction M of the bandwidth, then the sampling rate of the ADC becomes M times lower. Thus it's possible to obtain an even better negotiation with the conversion resolution, which can be increased by  $\sqrt{M}$  bits compared to conventional receivers.

This approach has the following advantages:

- The smaller bandwidth of the M divided signals enables the use of an M time lower sampling frequency for each ADC;

- The need for a lower sampling rate of the ADC relaxes the requirements, allowing a better engagement with the resolution of the conversion, making it possible to improve the it in  $\sqrt{M}$ ;

- A higher resolution conversion will lower quantization noise improving the SNR of the system;

- The fact that the bandwidth of the input signal for each ADC is lower will result in less power consumption;

- The reduced bandwidth of each channel also enables to relax important factors of the amplifier such as the non-linearity;

- Since we are converting small parts of the spectrum in each ADC we will have less problems with jamming signals, as we can see in figure 2.5.

Figure 2.5: Blocking effect reduction using a Hybrid Filter Bank compared with just one ADC[11]

This method is also know by the name Hybrid Filter Bank, because we use analog filters to divide the signal and sample it and then the signal is reconstructed with digital filters, making it a analog/digital hybrid.

#### 2.2.2 Hybrid Filter Banks

The hybrid filter banks are then one solution to avoid the limitations of the current A/D converters. These allow an improvement on the resolution of the conversion and its dynamic range. However, this approach creates a new problem, the need to ensure perfect reconstruction of the input signal. That is, it's intended that the signal is divided into several bands in analog filter banks and then can be reconstructed in the digital domain without any loss or distortion of information.

So, to archive a perfect reconstruction is necessary to very accurately know the characteristics of the analog filters that we are using in order to be able to generate the digital filters such that the transfer function of all the hybrid filter bank is only a delay. However, in practice the perfect reconstruction is impossible due to the nonideality of the elements in the analog filters so the practical objective is to obtain very approximate models of the reality in order to create a filter bank with almost perfect reconstruction.

### 2.3 Digital Signal Processing

The DSP unit is one of the most important components of any Software Defined Radio and especially to a cochlear radio because this component will be responsible for the reconstruction and processing of the signal received. The processor will receive the ADC data and reconstruct it to approximate the original signal and then use it for any function needed by the user. Another feature of any cognitive-defined radio is the reconfiguration, to allow the transfer of new software and to implement any standard in the receiver or any other new functions.

The processor can be a DSP, dedicated ASIC or an FPGA. A DSP can consume a lot of power and works typically with a serial processing. An ASIC is a very fast hardware that implements any function even parallel ones, and enables a cheap and low power solution for any radio. A FPGA can offer the same performance as an ASIC but usually consumes more power and is expensive, but is reconfigurable.

### 2.4 Reconfigurable Hardware

### 2.4.1 FPGA

Through the times many tools have been used to create programmable electronic logic SPLDs, PROMs and others.

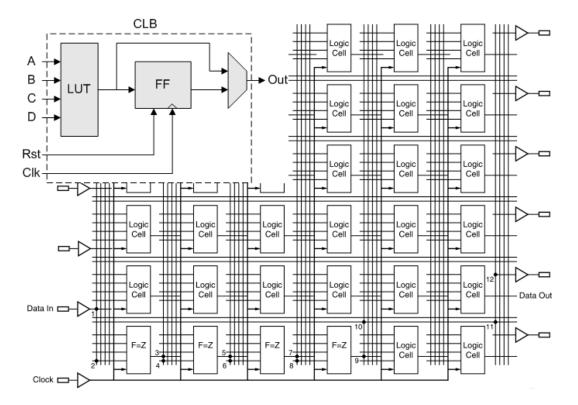

One of the most recent tools for testing, prototype implementation and even as a final product is the FPGA (field programmable gate array). These circuits contain an array of a large amount of logic blocks that can be programmed to interconnect as desired by the user. Each of that block is usually constituted by LUTs, multiplexers, flip-flops (FF) and some other additional logic, and can perform simple tasks, from a simple NOT gate to a synchronous sequential state machine.

In the FPGA that was used in this thesis, a Virtex6[12], these blocks are called CLBs (configurable logic block), they are grouped in slices and they can be a common ordinary slice, as showed in figure 2.6, or a DSP slice, the DSP slice have another kinds of logic, a more specific logic for DSP operations.

Figure 2.6: A slice is a array of Logic Cells, on the upper left we can see the common constitution of a logic cell in a FPGA[13]

In order to make the connections between CLBs flexible those are made with programmable interconnect fabric, leading to small frequencies of operation created by the large capacities from the multiple possible paths. But as we have access to a lot of available logic, we can create complex parallel processing than can allow a higher throughput than for example a pipeline processor.

#### 2.4.2 VHDL

To take all the possibilities from a FPGA we require a way to "program" it to do any operations needed by the user, as in a processor a user does not program in machine code neither in a FPGA we connect directly each block, but a compiler is used for that. A circuit system is written by the user using hardware description languages (HDL), where the circuit is described as well as the inputs and outputs. HDLs were originally created for simulation and they are still used for such but it started to be used to synthesis real hardware as well. It is important to note that not every circuit designed as a behavioural simulation may work as a real circuit and the code can have instructions that may be implementable but not behave correctly in reality.

With this method of programming we allow parallelism by creating a large amount of independent process running at the same time, this is the true advantage of a FPGA over a hard-wired processor.

The industry mainly uses two types of HDLs, VHDL and Verilog. For this thesis VHDL was used to program the FPGA but some blocks not created by the author, are written in

Verilog. As we can interconnect very easily Verilog blocks to VHDL blocks this does not cause any trouble.

### 2.5 FML605 board based in Virtex6 XILINX FPGA

#### 2.5.1 Integrated synthesis environment

The VHDL code needs to be translated to configuration data and then loaded into the FPGA. For this purpose we used the XILINX ISE 12.4/13.3[14] that will translate and synthesis the VHDL code into a bit-stream ready to transfer to the FPGA board memory, and then the XILINX IMPACT to load it on the FPGA.

When we write VHDL code in the ISE, it synthesis that code, generating the hardware and connections that implement the behaviour of the system created. Syntax errors are then detected at this point and must be corrected before moving anywhere further.

In addiction to the code written in VHDL, the user creates a constraint file. This constraint file has all timing requirements needed in the project and in/out connections of a VHDL port to a pin of the FPGA circuit package. The timing requirements permit to ensure that a certain signal or clock have a certain delay or can run at a certain frequency without any problems and with a certain tolerance.

The constraint file is used in the Implementation phase of the code, this step generates a netlist, from the previous generated hardware, that is mapped into the FPGA, allocating the resources in specific locations to permit the best routing and also providing the interconnections to that allocation. This creates a FPGA configuration file and a report of the used resources as for an estimation of the power consumption.

This configuration file is then programmed intro the FPGA and after conclusion the system it's ready to use.

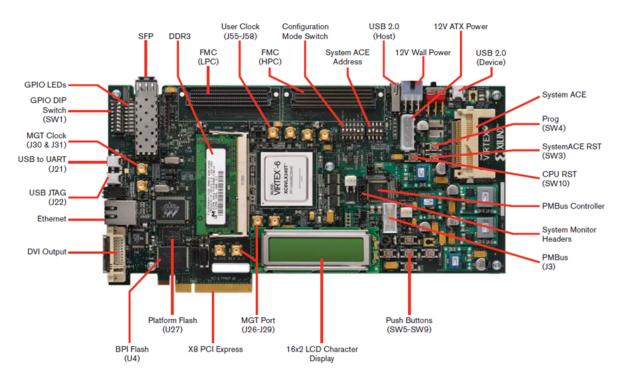

#### 2.5.2 ML605 board

For this thesis a ML605[15] evaluation board was used. This board contains a Virtex6 XC6VLX240T-1FFG1156 FPGA, and each slice of this FPGA is constituted by four sixinput LUTs, multiplexers, four FlipFlop/Latches and four FlipFlops. The most important characteristics of this FPGA are the follow:

| Logic cells | Slices | Distributed | DSP48E1  | Block RAM blocks |       |          | $\operatorname{Ethernet}$ |

|-------------|--------|-------------|----------|------------------|-------|----------|---------------------------|

| Logic cells | Silces | RAM (Kb)    | DSF 40E1 | 18 Kb            | 36 Kb | Max (Kb) | MACs                      |

| 241.152     | 37.680 | 3.650       | 768      | 32               | 16    | 14.976   | 4                         |

| Table 2.1: | Virtex6 | XC6VI | LX240T | FPGA | key | characteristic | cs [16] |

|------------|---------|-------|--------|------|-----|----------------|---------|

|------------|---------|-------|--------|------|-----|----------------|---------|

The evaluation board that we use have the following characteristics [17]:

- FPGA Virtex6 XC6VLX240T-1FFG1156;

- Configuration through USB2.0 or Flash memory;

- Power supplied through transformer;

- DDR3 (512MB) and Flash memories (34MB+16MB+8Mb);

- 200MHz differential oscillator and 16MHz socket clock;

- SMA sockets for external clock or user GPIO;

- LCD display, LEDs, Push-buttons and Switches;

- Communication through RS232, Ethernet, USB2.0, GTX and PCI Express.

Figure 2.7: ML605 Dev. Board[18]

### 2.6 4DSP FMC108 8-ADC 250MSamples board

To perform the signal acquisition and convention to digital we used an ADC board from 4DSP[19]. 4DSP is a Nevada, USA based corporation that develop and manufacture commercial off the shelf data-conversion boards (ADCs and DACs) and respective FPGA Intellectual Property. Is also member of Xilinx Alliance Program, so the majority of the products are developed directly for Xilinx evaluation boards.

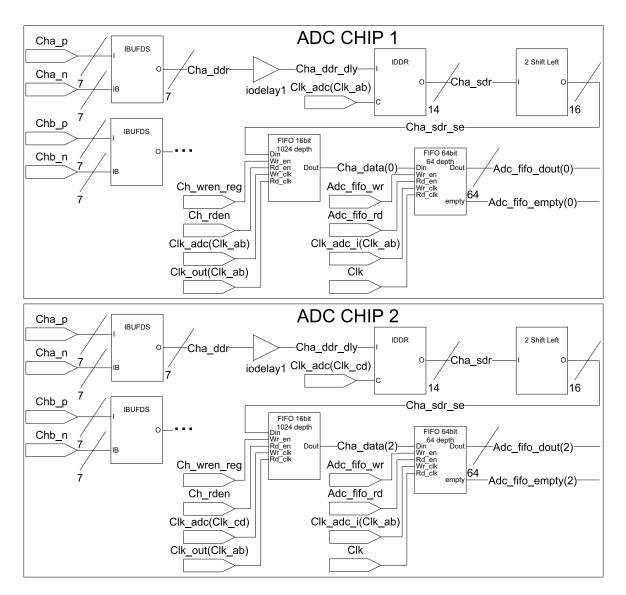

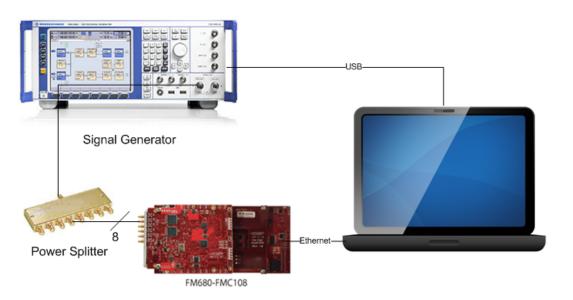

The specific board used is this thesis is a FMC108, a 4DSP board with 4ADCs, each of which has two channels, as each channel is being used individually it enables that 8 analog signals to be sampled at the same time. It also offers a connection to an external clock and another one for an external trigger.

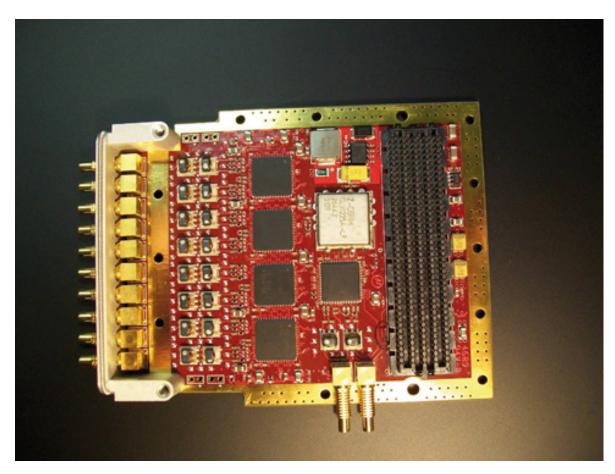

Figure 2.8: FMC108 board[20]

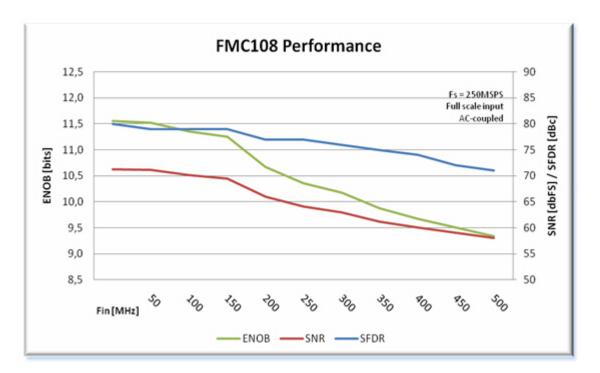

Each ADC channel has a resolution of 14-bit and a maximum sampling rate of 250Msps. The ADC clocks can be clocked by the internal clock source that offers some level of selectivity freedom of the clock frequency, but it can also be clocked externally by any frequency from 3 to 250MHz.

The ADCs used on the board are the TI's ADS62P49[21] dual channel 14-bit 250Msps ADCs with a DDR LVDS output. That also allows a programmable gain up to 6dB individually for each channel. The frequency of the analog input signals in this board must be between 3MHz to 650MHz as there is a AC coupling to get a better SNR from the ADCs, the input voltage can go as high as 2Vp-p (10dBm), and the input is tuned at 500hm impedance.

A clock tree is used that offers some flexibility and high performance. A AD9510[22] PPL and clock distribution IC are the base of the clock tree and a VCO is connected to one of the clock inputs (the other clock input can be used by an external clock). An external reference 100MHz crystal is then connected to the VCO.

There's also on the board two ADT7411[23] devices which monitors the temperature of the ADCs and the clock input frequency for each ADC, each of these devices controls two ADC chips.

The input channels, clock and trigger are connected by a SSMC connectors in the front panel, these connectors are not a standard so SSMC to SMA cables were used to connect to other laboratory equipment. As the temperatures of the board can reach  $85^{\circ}$ C during use and to avoid damage a external fan was annexed to the FMC108 and is powered by the ML605, that had one extra fan power supply that was not at use. This alteration allows the FMC108 to run at no more than  $50^{\circ}$ C.

Figure 2.9: The external fan bolted to the FMC108

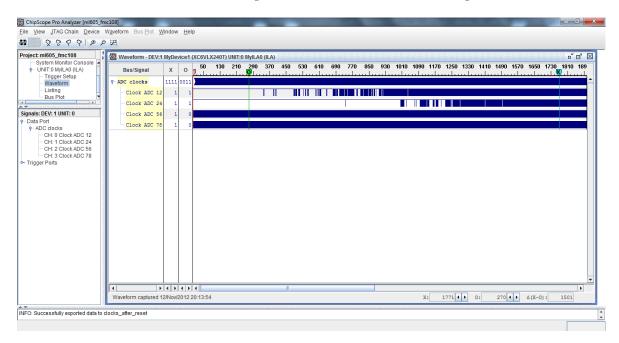

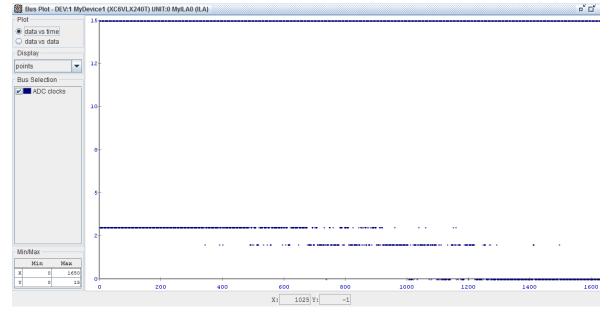

The board connects via FMC to the FPGA evaluation board. 4DSP provides with the board the respective firmware based in their high-level "Stellar architecture" written in VHDL that allows to sample each channel at a time.

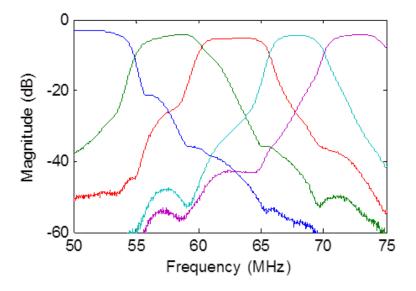

### 2.7 The Cochlea analog filter bank

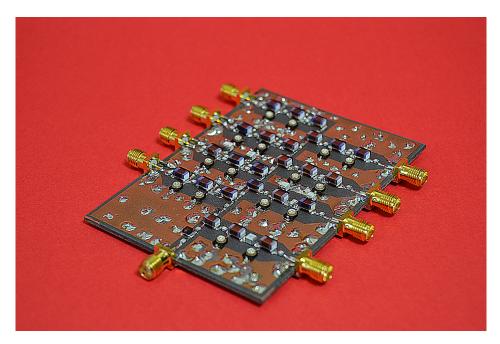

For this thesis a custom made filter bank was used, this filter bank was designed/built by José Pedro Magalhães[24]. It works by coupled filters, using discrete capacitors and coils into a RT/d5880 substrate with a  $\varepsilon_r = 2.2$  and 1.58mm thick.

This filter bank have 8 channels adapted to  $50\Omega$  impedance, and projected to each filter to have a bandwidth of approximately 5MHz and be a filter of 3 order. So this will allow to the filter bank to be used as a multiplexer between 50 and 100MHz.

Figure 2.10: The RF multiplexer with 8 channels for frequencies between 50 and 100MHz

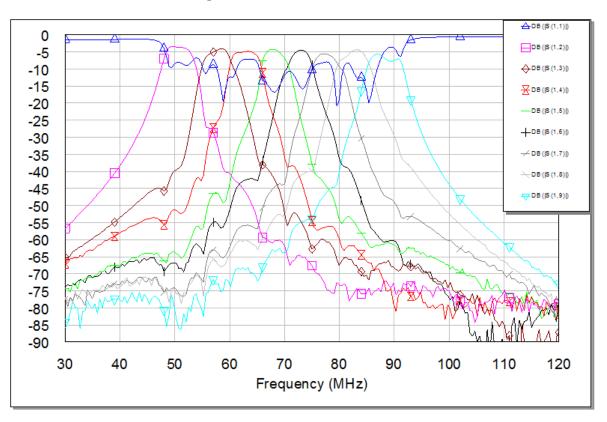

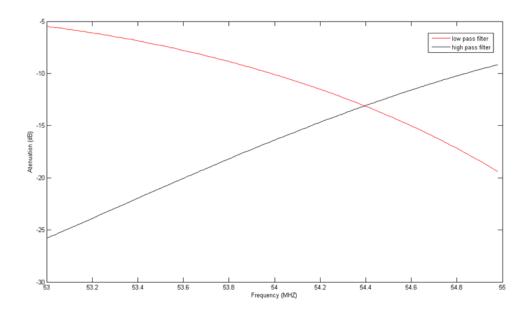

This filter have the following transmission coefficients:

Figure 2.11: Transmission coefficients of the filter bank used

### 2.8 The behaviour of a reconstruction filter bank with subsampling

All the simulation process for this thesis was done using MATLAB[25] that is an IDE with its own high-level programming language.

For simplicity, we will study the case where M = 2 or when the hybrid filter bank has only 2 channels.

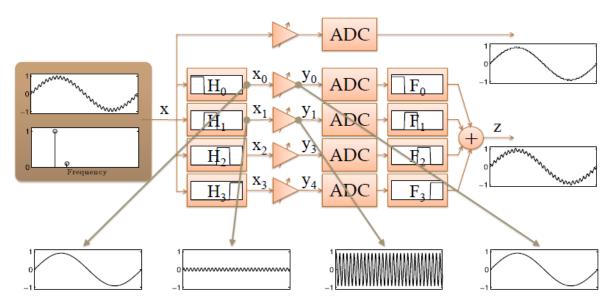

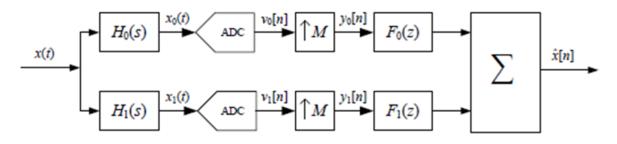

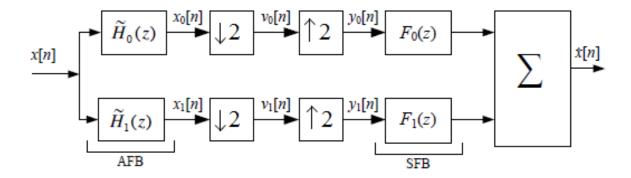

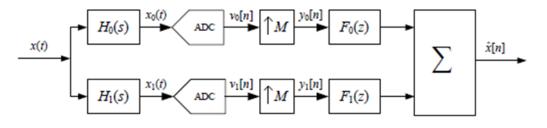

Figure 2.12: Hybrid Filter Bank

In this case the analog signal is filtered by the analysis filter bank in two frequency bands which are then passed to the digital domain by a sub-sampling ADC. The signal is then interpolated by a factor equal to the number of bands and then filtered by the synthesis filter bank. After this, the 2 signals are then summed giving rise to the reconstructed signal.

The previous system is equivalent to the following all digital filter bank:

Figure 2.13: HFB digital equivalent

Let's now see the output equation of the entire system, after passing through the decimation we get the signals:

$$\begin{cases} V_0(z) = \frac{1}{2T_s} [X(z^{\frac{1}{2}}) \tilde{H}_0(z^{\frac{1}{2}}) + X(-z^{\frac{1}{2}}) \tilde{H}_0(-z^{\frac{1}{2}})] \\ V_1(z) = \frac{1}{2T_s} [X(z^{\frac{1}{2}}) \tilde{H}_1(z^{\frac{1}{2}}) + X(-z^{\frac{1}{2}}) \tilde{H}_1(-z^{\frac{1}{2}})] \end{cases}$$

(2.1)

so, the reconstructed signal will then be:

$$\hat{X}(z) = V_0(z^2)F_0(z) + V_1(z^2)F_1(z)$$

(2.2)

Replacing $V_1$  and  $V_2$  we have:

$$\hat{X}(z) = \frac{1}{2T_s} [\tilde{H}_0(z)F_0(z) + \tilde{H}_1(z)F_1(z)]X(z) + \frac{1}{2T_s} [\tilde{H}_0(-z)F_0(z) + \tilde{H}_1(-z)F_1(z)]X(-z) \quad (2.3)$$

define from now on  $T_0$  and  $T_1$  as:

$$T_0(z) = \frac{1}{2T_s} [\tilde{H}_0(z)F_0(z) + \tilde{H}_1(z)F_1(z)]$$

(2.4)

$$T_1(z) = \frac{1}{2T_s} [\tilde{H}_0(-z)F_0(z) + \tilde{H}_1(-z)F_1(z)]$$

(2.5)

Where  $T_0$  is the distortion, which allows to achieve perfect reconstruction if only it is a delay or a constant. And  $T_1$  is called aliasing and must be 0 in order to have a linear frequency response, this is caused by the decimation of the signal.

The discrete time Fourier transform of the output signal is then:

$$\hat{X}(e^{jw}) = X(e^{jw})T_0(e^{jw}) + X(e^{j(w-\pi)})T_1(e^{jw})$$

(2.6)

in matrix form it's:

$$\begin{bmatrix} e^{-jw_q d} \\ 0 \end{bmatrix} = \frac{1}{2T_s} \begin{bmatrix} \widetilde{H}_0(e^{jw_q}) & \widetilde{H}_1(e^{jw_q}) \\ \widetilde{H}_0(e^{j(w_q - \pi)}) & \widetilde{H}_1(e^{j(w_q - \pi)}) \end{bmatrix} \begin{bmatrix} F_0(e^{jw_q}) \\ F_1(e^{jw_q}) \end{bmatrix}$$

(2.7)

As we want to know the synthesis filters we then have,

$$F(e^{jw_q}) = 2T_s H^{-1}(e^{jw_q})T(e^{jw_q})$$

(2.8)

In witch  $w_q$  is the arbitrary set of frequencies with  $q = [0 \dots Q-1]$ .

Assuming that we want the synthesis filters to be FIR filters which have the advantage of being always stable, although it loses part of the impulse response of the filter compared to the IIR filter implementation. So in order to obtain the response of synthesis filters in the time domain we have to solve,

$$\begin{cases} F_1 = W^H f_1 \\ F_2 = W^H f_2 \end{cases}$$

(2.9)

In witch  $(.)^H$  is the conjugate transpose and  $W_q^H = [W^0 W^{-q} ... W^{-q(L-1)}]$  with  $W = e^{j\frac{2\pi}{Q}}$  and L the number of coefficients of the filters. Generally, we use a Q greater than or equal to L resulting in an indeterminate system where we can find a minimum  $L_2$  solution.

In order to f we have:

$$\begin{cases} f_1 = W^+ F_1 \\ f_2 = W^+ F_2 \end{cases}$$

(2.10)

in witch  $W^+$  is the pseudo-inverse of the Fourier transformation matrix W, in other words  $W^+$  is the product of the inverse matrix W with the identity matrix [26].

### 2.9 Interchannel phase delay effect on HFBs

# 2.9.1 Effects of phase mismatches between the measured and the real system

When projecting a Hybrid Filter Bank we need to design the Synthesis Filter Bank, which is part of the digital system, in function of the response of the analog counterpart system, the Analysis Filter Bank. During the designing process we assume that the analog system is invariant in time and, thus, the resulting relationships between the analog and digital parts are always true. However, if little deviations occur in the analog part of a HFB, the Digital domain system previously designed may not be suitable to offer the initial reconstruction figures. Such deviations may occur due to detrition on the connectors, use of cables with different transmission properties or different lengths, misplaced connectors, etc. In theory, the digital system could be updated and optimized in order to guarantee that the initial reconstruction conditions are rediscovered. However, such an adaptive system is complex to design owing to the increase of the physical equipment and to the highly complex digital procedures required for that purpose. Other solution is to predict the aforementioned deviations and check if the reconstruction deterioration is acceptable or inadmissible. Thus, we want to characterize the performance of an HFB, when the analog part is deliberately subjected to interchannel phase mismatches.

Next equations relates, on an analog transmission line, the phase delay  $(\theta)$  with the length of the line (l) and the frequency at use  $(f_o)$ .

$$l = \frac{\theta}{f_o} \frac{v_p}{360} \tag{2.11}$$

$$\implies \theta = l \frac{360 f_o}{v_p} \tag{2.12}$$

where  $v_p$  is the velocity of propagation in a substrate with a given dielectric constant  $\epsilon_r$ and magnetic constant  $\mu_r$ :

$$v_p = \frac{C}{\sqrt{\epsilon_r \mu_r}} \tag{2.13}$$

Now, for example, at  $f_o = 100MHz$ , a phase delay of 1 degree ( $\theta = 1^o$ ) is equivalent to the inclusion of a line with l = 5.6mm. In a practical case, the mismatches in the length of the cables or in the connectors are unlikely to exceed that value, unless for human negligence as a misplaced connector or the use of male-male/female-female type connectors. In any case, we should check if our system is sensitive to phase errors of one degree or two degrees.

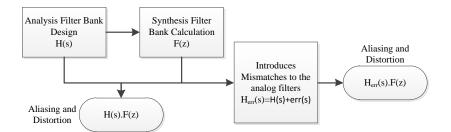

Before proceeding to the simulations, maybe it is convenient to explain how the overall procedure was done.

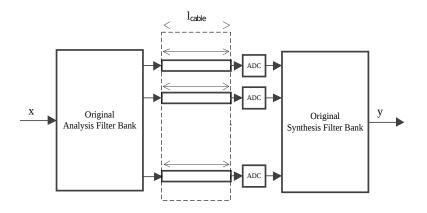

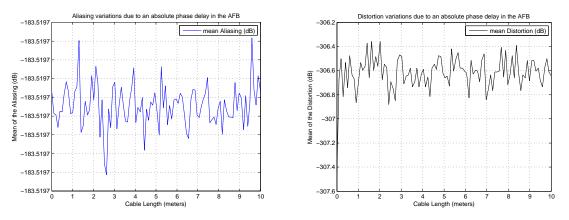

Figure 2.14: Main procedure to test

Figure 2.14 shows a diagram of the procedure, and it can be seen that a HFB is originally designed and, thereafter, some phase errors are placed on the analog part and the aliasing and distortion is recalculated. We know that the output of a Hybrid Filter bank may be given by

$$\hat{Y}(e^{j\omega}) = \sum_{p=-\infty}^{\infty} \tilde{X}\left(e^{j\left(\omega - \frac{2\pi}{M}p\right)}T_p\left(e^{j\omega}\right)\right)$$

(2.14)

where

$$T_p(e^{j\omega}) = \frac{1}{MT_s} \sum_{m=0}^{M-1} \tilde{H_m}\left(e^{j\left(\omega\frac{2\pi}{M}p\right)}\right) F_m\left(e^{j\omega}\right)$$

represents both the aliasing and distortion over the reconstructed signal and, thus, is the value we want to measure for the different conditions that the analog filters will be subjected to.

At last, the phase errors are placed right down on the H matrix that characterizes the analog part of the system and the one that is used to calculate aliasing and distortion. Equation (2.15) shows how the phase errors are placed into each filter that constitutes the H matrix, where  $\theta_m$  is the phase delay error to add to the original filter response  $H_m$ .

$$\ddot{H}_m(s) = \|H_m(s)\| e^{j\{ \angle H_m(s) + \theta_m(s)\}}, \ m = 0, \ \dots, \ M - 1$$

(2.15)

If we assume that the phase error  $\theta_m(s)$  is linear with frequency, i.e., has a constant group delay, then we may modulate  $\theta_m(s)$  with the inclusion of a line section, with a non-negligible length l, at the end of a given analog channel. Thus, to add the phase error  $\theta_m(s)$  to the original filter response, we just have to calculate equation (2.12) for the range of frequencies in consideration and for a given length l. Notice that we assume that all lines are ideal, i.e., are correctly matched and are lossless.

#### 2.9.2 The HFBs used for this test

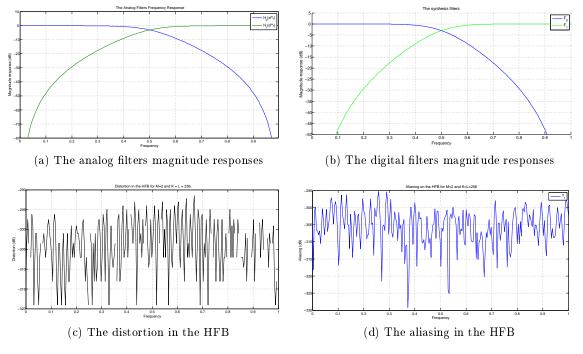

To test the interchannel phase delay effects, two hybrid filter banks will be created. In the first case, a simple M = 2 case is constructed, where the analog filters were designed through a butterworth technique.

Figure 2.15: The original hybrid filter bank for M=2

Figure 2.15 shows the analysis and synthesis filters responses, as well as the aliasing and distortion results, where it can be seen that reconstruction is possible with -300dB errors and beyond.

Figure 2.16: The original hybrid filter bank for M=2

The M = 4 case, also with butterworth filters, is presented in figure 2.16 where it shows that reconstruction error figures placed around -180dB which is also good.

#### 2.9.3 Absolute Phase Delay

In this part, we want to examine the behavior of the previously designed filter banks, when equal length lines are employed before the A/D converters and without a digital counterpart update.

Figure 2.17: The system to be tested

Figure 2.17 shows a diagram of the system to be tested and it can be seen that the procedure is equivalent to the insertion of individual lines, with the same length  $l_{cable}$ , at the end of each channel filter. In theory, if ideal transmission lines are assumed, then the extra lines is will only delay all channels in phase in a equal manner and, therefore, won't impair the initial reconstruction figures, only causing an extra delay to the reconstructed signal. Thus, all lines could be replaced by a singular line, with the same length, placed at the input port.

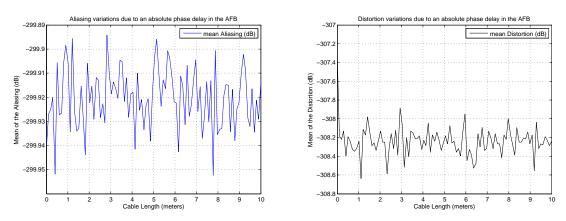

(a) Mean aliasing for M = 2 and for a wide range of (b) Mean distortion for M = 2 and for a wide range of cable length l cable length l

(c) Mean aliasing for M = 4 and for a wide range of (d) Mean distortion for M = 4 and for a wide range of cable length l cable length l

Figure 2.18: The aliasing and distortion mean errors for a sweep in  $\theta$  value from 0° to 180°

Figure 2.18 shows the simulation results where it is plotted the mean of distortion and aliasing, for each  $l_{cable}$  considered and for both M = 2 or M = 4 cases, and considering that the cables are lossless. From the results, it can be seen that equal length lossless lines do not affect the reconstruction levels, as the interchannel relationships remain unalterable. The only effect of such lines is the increase of the delay to the reconstructed signal y. In short, equal lines at the end of each channel do not affect the HFBs performance.

#### 2.9.4 Relative Phase Delay

#### 2.9.4.1 Test 1

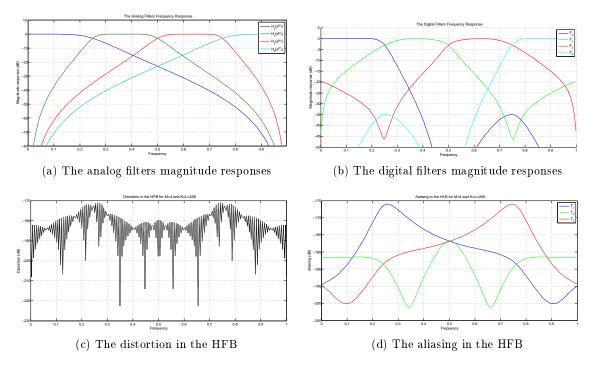

In this part, we'll examine the behavior of the filter banks designed in Section 2.9.2 when an individual line with length l is placed at the end of one channel. Lets start by assuming that the HFB is designed to operate from 50MHz to 75Mhz. Therefor, the schematic from figure 2.19 is employed. In short, with this simulation, we are assuming that one of the channels suffers from variation in its phase response which is not covered by the digital part of the system. By knowing this, we want to measure the associated reconstruction error.

Figure 2.19: System schematic to employ - only one channel has it's phase delayed

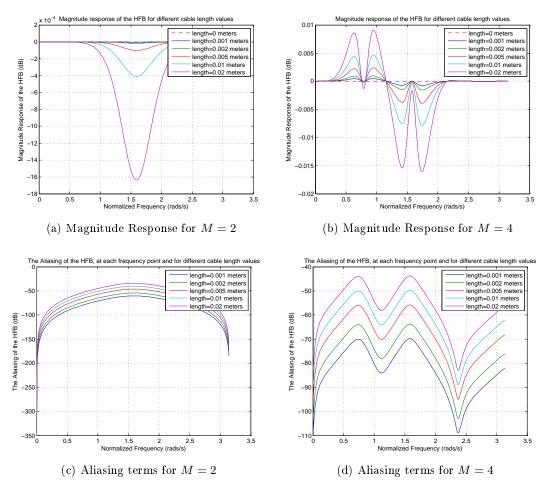

Figure 2.20 (a) and (b) shows the overall system magnitude responses, either for M = 2and M = 4, when a cable with length l is placed in the second channel. It can be seen that for l = 0 meters, the magnitude response of the HFB is perfect because it creates zero distortion for all the considered bandwidth. However, as l increases, it can be seen that distortions start to appear at some frequencies. Those frequencies are, in fact, the cross frequencies between the delayed filter and it's adjacent ones, whereas the digital part is unable to produce a convenient reconstruction own to the interchannel relationships that have changed.

Figure 2.20: The magnitude response of the HFB and the Aliasing terms for a variety of l

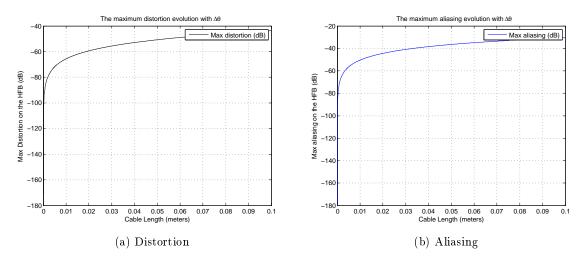

The same effect will occur in terms of aliasing, figure 2.20 (c) and (d). Therefore, we can see that a slight channel delay will disturb the HFB from correctly reconstructing an input signal, thus causing degradation of reconstruction figures. To conclude this case of study, figure 2.21 shows the **maximum values** of aliasing and distortion for each cable length value l, on a M = 4 system, and the aforementioned conclusions can be observed once again.

Figure 2.21: Maximum value of distortion and aliasing for different  $\Delta \theta$  values

Notice that the error starts to saturate at some point. This is because the main focus of error is only at frequencies nearby the crosspoints between adjacent filters, while in the other frequencies, the signal is still correctly reconstructed.

#### 2.9.4.2 Test 2

Lets now test another configuration. Again, lets assume that the HFB is designed to operate from 50MHz to 75Mhz.

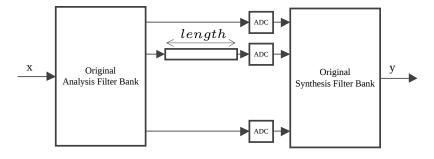

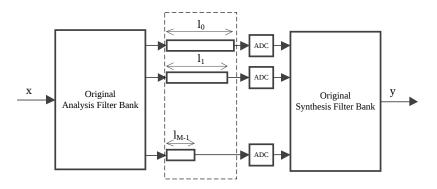

Figure 2.22: Test procedure - All different lengths

Also, assume that the schematic from figure 2.22 is applied, i.e., lets consider that we use M cables, with different lengths  $l_m$  between each other, and that the length of each cable is given by:

$$l_m = l_{m-1} + \Delta l, \ m = 1..M - 1 \tag{2.16}$$

where  $l_m$  is the length of the cable in channel m and  $\Delta l$  is the length difference between adjacent channels. Assume also that all cables are ideal and lossless.

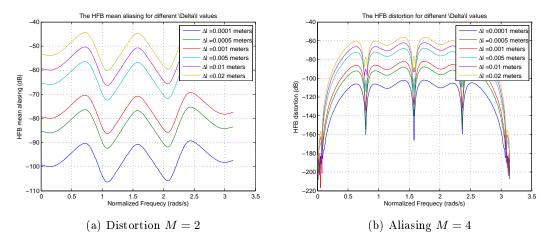

Figure 2.23: The distortion and aliasing in the HFB for different values of  $l_m$ .

Having this, the following results from figure 2.23 were obtained, whereas the distortion and aliasing were calculated for different values of  $\Delta l$ . It can be seen that for small differences as  $\Delta l = 0.1mm$ , no major concerns have to be taken as the reconstruction errors are placed under -90dB which is still very good. On other hand, for  $\Delta l$  above 1cm, the error of reconstruction might be higher than -50dB, and therefore jeopardizing the advantages of the Hybrid Filter Bank.

#### 2.9.5 Conclusions of the effects of phase mismatches

It may be helpful to describe the measurement errors in terms of degrees rather then meters. We saw that an measurement error of 1cm in the 50MHz-75MHz range is enough to degrade the system performance. However, in a system operating from 1.4GHz to 1.7GHz, for example, the same 1cm would caused a completely different error. Thus, to generalize beyond the frequency usage, we need to establish the measurement error in terms of degrees of interchannel delay. With that measurement, we may point a maximum interchannel delay, in degrees, that will apply to every HFB system, for any frequency. For that purpose, consider the following equation, which is an extension of eq.2.11:

$$\Delta \theta = |\theta_2 - \theta_1| = \frac{360f}{v_p} (l_2 - l_1) = \frac{360f}{v_p} \Delta l$$

(2.17)

where  $\Delta\theta$  represents the interchannel delay between two adjacent channels, whose present  $l_2$  and  $l_1$  as their respective measurement errors in meters. Now with  $\Delta\theta$  it is possible to have an generic measurement for the interchannel phase delay error, i.e., it is guaranteed that an error of  $\Delta\theta = 1^o$  has the same effect either at low frequencies or at high frequencies. However, the measurement error  $\Delta l$  will be different. Table 1 shows the measurement error  $\Delta l$  needed to obtain an interchannel delay of one degree ( $\Delta\theta = 1^o$ ) either in the Cochlea case or in the Star Junction case.

|                                | High Frequency Multiplexer | Cochlea Multiplexer |

|--------------------------------|----------------------------|---------------------|

| Operating frequency            | 1.3GHz - 1.7GHz            | 50MHz - 100MHz      |

| $\epsilon_r$                   | 9.8                        | 2.2                 |

| $\Delta l_{@\Delta\theta=1^o}$ | $\approx 0.2mm$            | > 1cm               |

Table 2.2: The measurent error  $\Delta l$  needed to achieve  $\Delta \theta = 1$

It the cochlea case, when  $l_1 = 0$  (meaning no measurement errors in the channel 1), a one degree of interchannel phase delay ( $\Delta \theta = 1^{\circ}$ ) is obtained if channel 2 has a measurement error over 1*cm* of length (which is almost the length of a male-male/female-female connector). As seen from figures 2.20 and 2.23, a 1*cm* line will cause the reconstruction error to rise up from -300dB to -40dB in the M = 2 and from -180dB to -50dB in the M = 4 case. In practice, such error measurement seems quite unreasonable, unless female-female or male-male connectors are used and not included into the digital system.

On the other hand, if we consider the Star-Junction Multiplexer case, it can be seen that the prone to error is much higher. For example, considering that  $l_1 = 0$  (no errors in the measurement of channel 1), a 1 degree of interchannel phase delay will occur if the channel 2 is measured with 0.2mm of error. We know, from the cochlea case, that a  $\Delta \theta = 1^{\circ}$  error means the rising of aliasing and distortion up to approximately -50dB. Thus, the prone of error in the 50-100MHz analog filter bank case may be inappropriate to produce real-time measurements and reconstructions as it is very easy to commit measurement errors that will highly degrade the system performance.

On the other hand, in relation to the Cochlea multiplexer, special care as to be taken in order to guarantee measurement errors inferior to 1cm. If the use of male-male or femalefemale connectors is unavoidable, then those connectors responses must also be measured and taken into account when measuring the overall analog system performance.

# Part III

# Accurate Measurements in RF

## Chapter 3

# Accurate Analog Filter Bank Measurements

### 3.1 Matlab code development for interaction with a GPIB Oscilloscope and Signal Generator

The majority of the measurement equipment used in RF has a GPIB (IEEE-488)[27] interface, which is a short-range protocol created on the late 1960s by Hewlett-Packard for use in laboratory equipment and it became the standard. It uses a parallel bus with individual control lines.

All the equipment that we used had a GPIB connector to interact with them. For use with our personal computer we used a GPIB adapter to Ethernet or to USB. There are 2 ways to start the serial connection from Matlab, the VISA[28] and the MATLAB Toolkit for R&S[29], in both toolkits we then define the IP from the equipment and associate it in Matlab, the equipments use the Agilent protocols[30] that also need to be installed on the computer. A basic command to know if everything is connected is to query for a '\*IDN?' GPIB command, if everything is working the equipment should respond with its name. After confirming this we are ready to send any command and receive any response.

## 3.2 Code development to interact with the oscilloscope and the signal generator to create a frequency sweep and analyzing the resulting data in a sampled transfer function

The first step to create a frequency sweep and measuring the results is to connect Matlab to the SMU200A generator and to the DPO72004B oscilloscope and query them for a '\*IDN?' to see if everything is working as expected. After this we turn off the RF of the generator to change the configurations. We choose then the output power, and the initial frequency.

From the oscilloscope we choose to acquire in sample mode and at real time. We then choose the sampling rate (in our case we used 250MHz), and the record length that is the amount of samples that we are going to acquire. Now this is a tricky selection because only some frequencies are selectable from the range of the oscilloscope, so after the selection a query should be made to know if the sample rate was successfully changed to what we had previously defined. Then, for each of 4 channels of the oscilloscope used, we do the following: turn the

channel on, choose DC coupling,  $50\Omega$  termination, 0 position and offset, and the specific scale in volts. Now the scale is very important because different scales can have different behaviour, so every channel should have the same scale, this scale can also be changed in the middle of the measurements but as we are going to see later this will add additional errors to the measurement.

After this initial setup of the oscilloscope we should choose the AUTO trigger, this allow for the trigger to be a software trigger sent by the PC user. Then we define the waveform data transfer definitions: "DAT:ENCdg SRIBinary" to define the output data format as an integer and to transfer first the least significant byte, then specify the number of bytes per data point using, in our case we choose 2 bytes so the command is "WFMOutpre:BYT\_Nr 2", the we specify the number of points of the waveform that we want to transfer using "DATA:START 1" and "DATA:STOP 'x" where 'x' is the number of samples that we want to sample.

With everything ready we activate the output of the generator and now it's time to start the sweep.

We run this process 'n' times where n is the number of frequencies of the sweep:

1 - We define the 'n' frequency of the generator;

2 - Wait at least 2ms for the generator to stabilize the output;

3 - We start sampling with the oscilloscope with 'ACQUIRE:STATE RUN' that will sample a single sequence, each sequence contains 25000 samples;

4 - Then for each of the 4 channels we do the following: select the data source to the channel then we run the "CURV?" command and the waveform of that channel is transferred;

5 - We then use that values and run a FFT with 25000 points and save the maximal point and its frequency for each channel and save it. Running the FFT with 25000 points at the sampling frequency of 250MHz allows a frequency resolution of 1 Hz.

We now have the transfer function of the frequency interval selected for each channel.

### 3.3 Characterization of the Oscilloscope

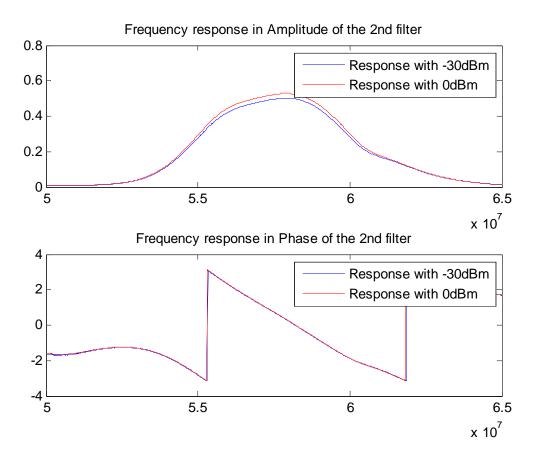

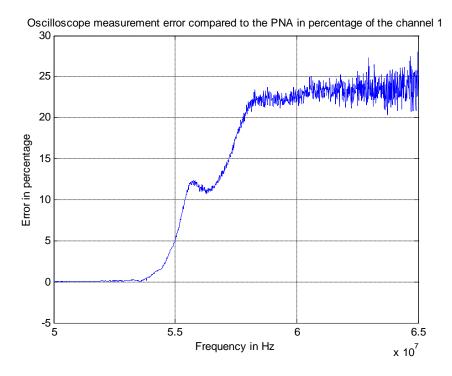

We now want to legitimate with a laboratory experiment that is possible to measure S parameters of a filter bank with a signal generator and an ADC (in this experiment we will use a oscilloscope).

With this lab experience we want to obtain the S parameters with a Network Analyser of a filter bank with 2 channels in a particular range of frequency. This measurement is made using all the system apparatus including the filter bank, a directional coupler and the cables used to connect the components. After the measurement of the S parameters with the Network Analyser the frequency response of the filter bank will be measured using a signal generator and an oscilloscope. This experiment will be made using as input, in the filter bank, a sinusoid with a determined frequency and observing the output of the filter bank, this way we will be able to measure the variation of amplitude and phase that the system provokes in the signal. This procedure will be repeated for every frequency that was analyzed in the Network Analyzer.

As we are working with low frequencies (50-100MHz) and with  $50\Omega$  components, we are expecting that the reflections of the circuit are negligible (S11, S12 and S22), if that is true then we shall have similar results from the two sources of measurement.

So this experiment is divided in two. The first one is the measurement with the Network Analyser and the second one is the measurement of the response in frequency with the oscilloscope

#### 3.3.1 Used material

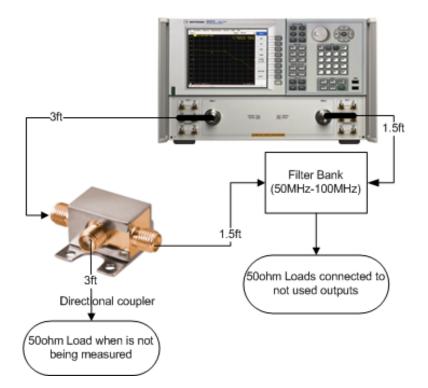

In the first part with measurement of the S parameters with the Network Analyser the material used is:

- Filter bank with 8 channels (50MHz-100MHz)

- ZX30-9-4-S+ (Directional coupler)[31]

- Agilent E8361C (Network Analyser)[32]

- VNA calibration kit

- $6 \ge 50 \Omega$  male SMA Loads and  $2 \ge$  female

- 2x CBL-1.5FT-SMSM+ (Coaxial cable of  $50\Omega$  with 1.5ft length)[33]

- 2x CBL-3FT-SMSM+ (Coaxial cable of  $50\Omega$  with 3ft length)[34]

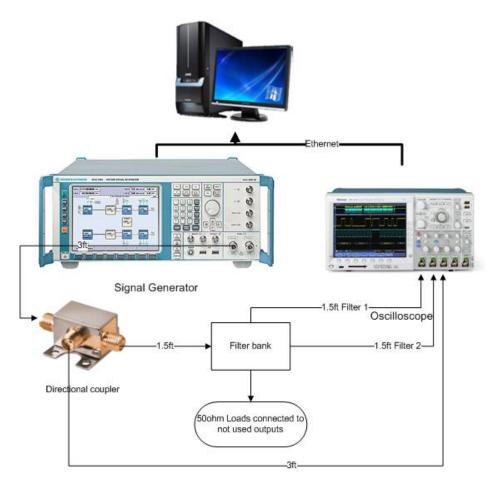

The second experiment will be the measurement of the frequency response with the oscilloscope and the material used is:

- SMU200A Signal Generator[35]

- Oscilloscope DPO72004B (20GHz) with Ethernet communication[36]

- PC with Matlab to interact between the generator and the oscilloscope

- Filter bank with 8 channels (50MHz-100MHz)

- ZX30-9-4-S+ (Directional coupler)

- $6 \mathrm{x} \ 50 \Omega$  Load male SMA

- 3x CBL-1.5FT-SMSM+ (Coaxial cable of  $50\Omega$  with 1.5ft length)

- 2x CBL-3FT-SMSM+ (Coaxial cable of  $50\Omega$  with 3ft length)

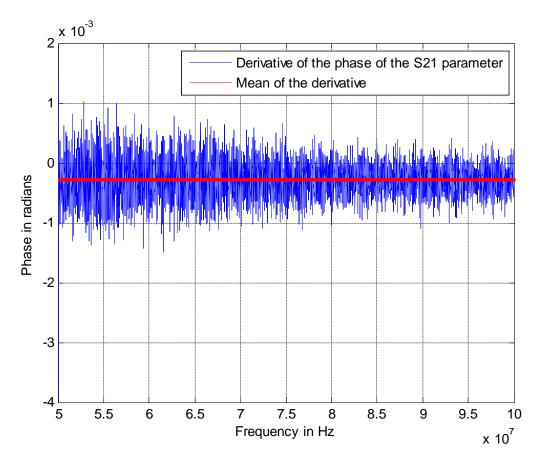

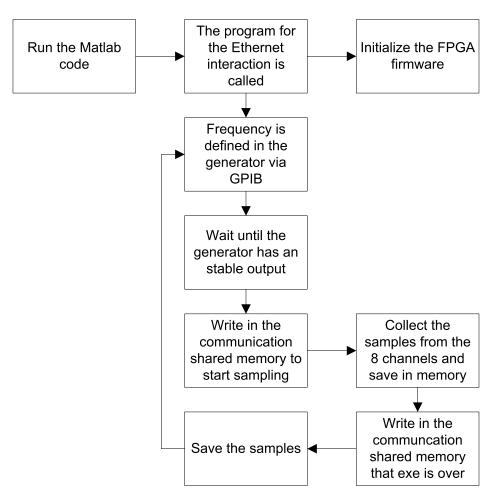

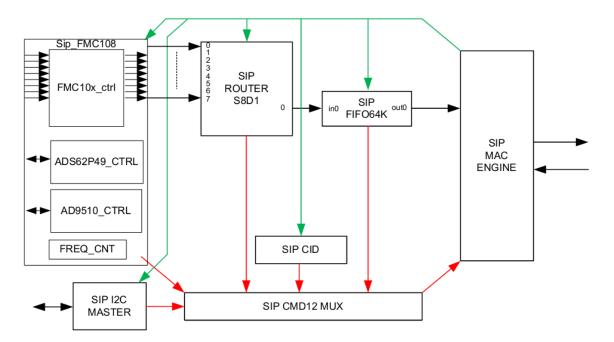

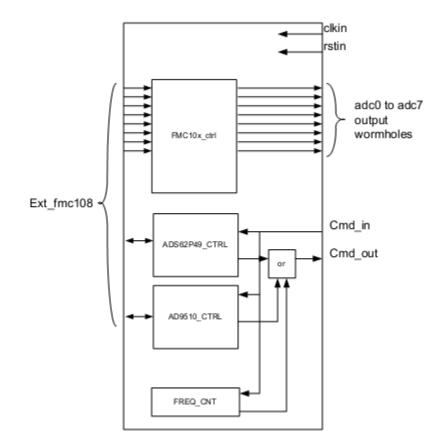

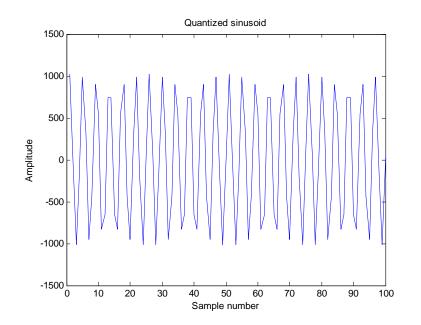

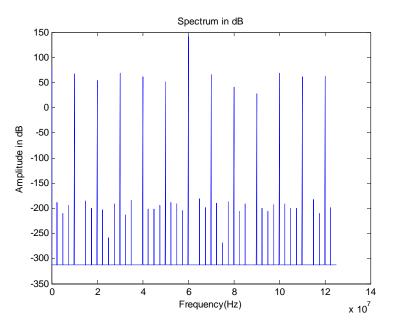

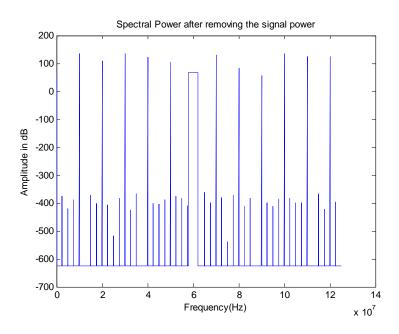

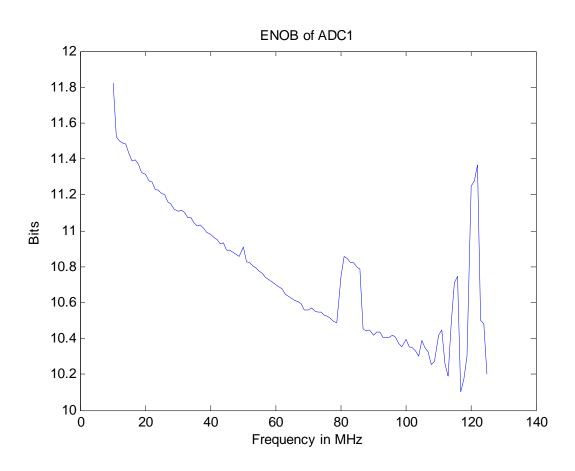

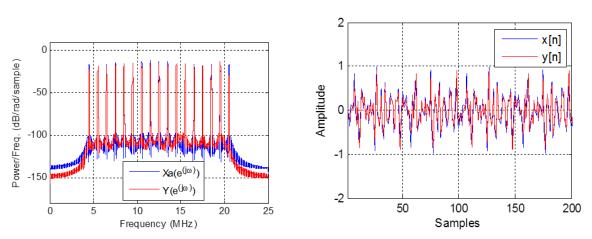

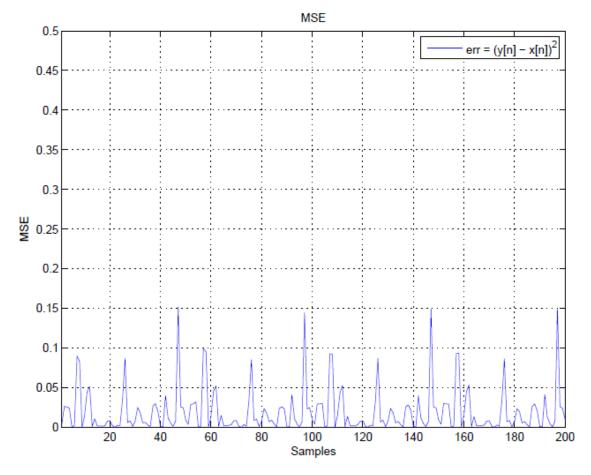

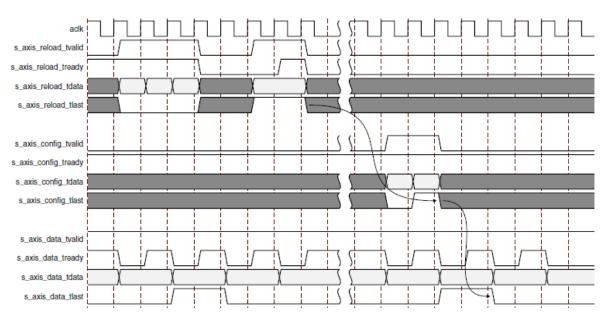

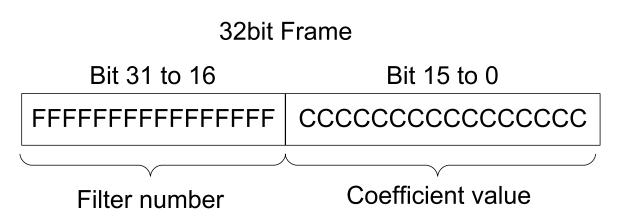

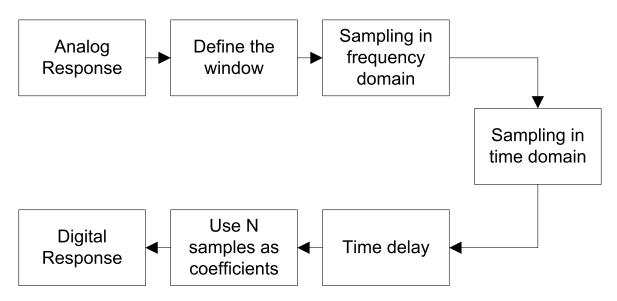

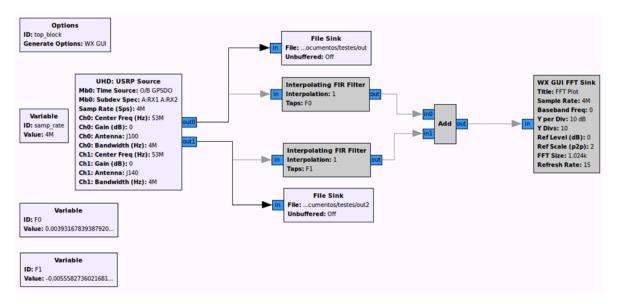

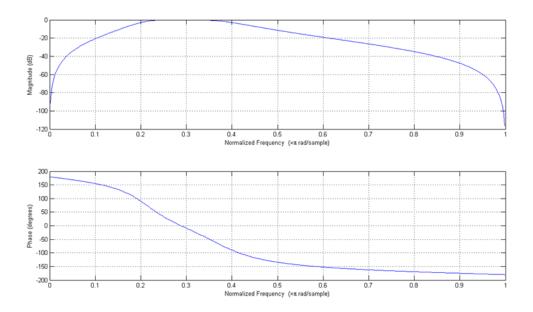

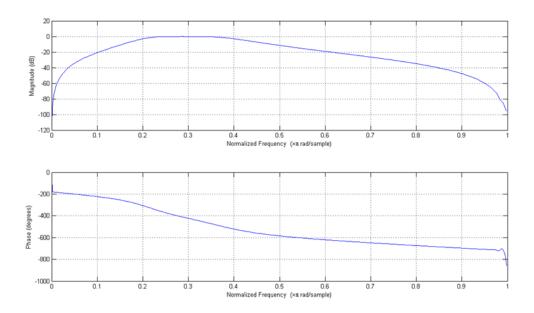

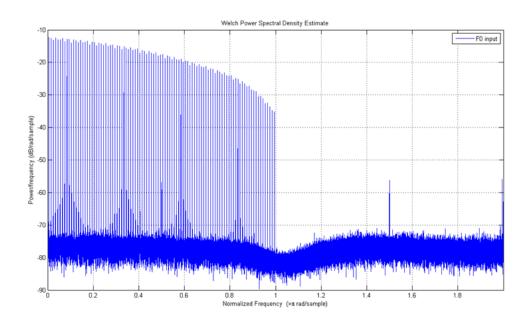

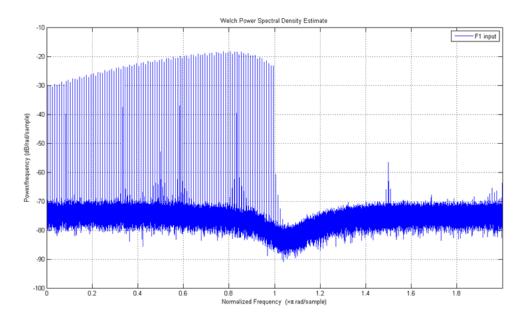

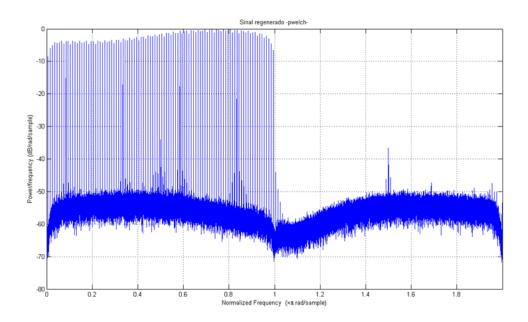

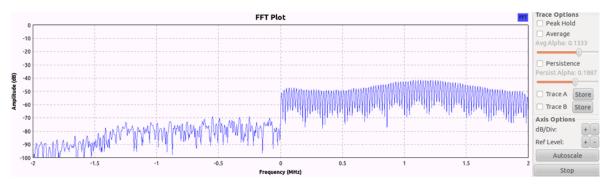

#### 3.3.2 Experimental assembly