# Valter Filipe Miranda Castelão da Silva

Gestão Flexível de Largura de Banda e Redundância em Barramentos de Campo

Flexible Redundancy and Bandwidth Management in Fieldbuses

# Valter Filipe Miranda Castelão da Silva

# Gestão Flexível de Largura de Banda e Redundância em Barramentos de Campo

# Flexible Management of Bandwidth and Redundancy in Fieldbuses

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Doutor em Engenharia Electrotécnica, realizada sob a orientação científica do Doutor José Alberto Gouveia Fonseca, Professor Associado do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro e do Doutor Joaquim José de Castro Ferreira, Professor Adjunto da Escola Superior de Tecnologia e Gestão de Águeda da Universidade de Aveiro.

Dissertation submitted to the University of Aveiro in the fulfilment of the requirements for the degree of Doutor em Engenharia Electrotécnica, under the supervision of José Alberto Gouveiva Fonseca, Professor Associado at the Departamento de Electrónica, Telecomunicações e Informática of the University of Aveiro and co-supervision of Joaquim José de Castro Ferreira, Professor Adjunto at Escola Superior de Tecnologia e Gestão de Águeda of the University of Aveiro.

Apoio financeiro da FCT e do FSE no âmbito do III Quadro Comunitário de Apoio.

Apoio da Escola Superior de Tecnologia e Gestão de Águeda da Universidade de Aveiro e do IEETA de Aveiro.

# o júri

#### Presidente

#### Prof. Doutor José Joaquim Costa Cruz Pinto

Professor catedrático do Departamento de Química da Universidade de Aveiro

#### Prof. Doutor Christian Fraboul

Professeur des Universités de l'Institut National Polytechnique de Toulouse, França

#### Prof. Doutor Adriano da Silva Carvalho

Professor associado da Faculdade de Engenharia da Universidade do Porto

## Prof. Doutor Eduardo Manuel de Médicis Tovar

Professor coordenador do Instituto Superior de Engenharia do Instituto Politécnico do Porto

# Prof. Doutor João Pedro Estima de Oliveira

Professor associado da Escola Superior de Tecnologia e Gestão de Águeda da Universidade de Aveiro

# Prof. Doutor Pedro Nicolau Faria da Fonseca

Professor auxiliar do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro

# Prof. Doutor José Alberto Gouveia Fonseca

Professor associado do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro

# Prof. Doutor Joaquim José de Castro Ferreira

Professor adjunto da Escola Superior de Tecnologia e Gestão de Águeda da Universidade de Aveiro

# agradecimentos

O longo e árduo trabalho que culmina com a escrita (e defesa) desta tese chegou (finalmente) ao fim!

Neste longo percurso tive a ajuda directa ou indirecta de muitas pessoas, as quais têm o meu sincero agradecimento. Tenho a plena noção de que sem elas este trabalho não teria sucesso.

Neste pequeno texto vou-lhes fazer uma homenagem em poucas palavras que, significam uma profunda gratidão. Assim, e sem que a ordem reflicta qualquer ordenação, o meu muito obrigado:

A José Alberto Fonseca, amigo e (também) orientador científico deste trabalho, pela amizade demonstrada, pela sua orientação perspicaz e pelas horas de discussão sobre "tudo o resto" marginal ao trabalho! A sua ajuda passa muito os limites de um orientador.

A Joaquim Ferreira, amigo e (também) co-orientador científico, pela dedicação, "puxões de orelhas", correcção exemplar desta tese e por todos os momentos de boa disposição que proporciona no laboratório 319!

A Paulo Bartolomeu, pela preciosa ajuda nos testes ao FTT e no aperfeiçoamento do DMS. Também pela amizade e discussões até "altas horas" após os jantares que terminavam tarde (ou cedo, dependendo do ponto de vista).

A Paulo Pedreiras, pelo grande amigo e pessoa que é, pela sua sempre (boa) disposição para "dois dedos de conversa" sobre "tudo e sobre nada".

A Luís Almeida, pelas discussões sobre o andamento do trabalho e pelos empurrões nos momentos mais aborrecidos.

A Ricardo Marau pela amizade demonstrada ao longo destes anos e pelo Verão de 2009 passado frente-a-frente no laboratório 319!

A Mário Calha pelo trabalho que desenvolvemos juntos que em muito ajudou para este trabalho.

A Rui Santos, Alexandre Vieira, Vasco Santos, Arnaldo Oliveira, Frederico Santos, Fernando Dias, Ana Antunes e Zé Vieira pela amizade demonstrada.

A Manuel Barranco, Isidro Calvo e Francisco Carreiro pelos tempos que animaram o laboratório 319!

A Margarida Urbano pela amizade, pelas importantes ajudas na ESTGA e pela discussão de certos temas.

À ESTGA, na pessoa do seu Director, Estima de Oliveira e aos restantes colegas, em especial aos colegas de gabinete. Sem eles este trabalho não teria sido possível.

A todos os meus amigos e amigas por ter dito tantas vezes "não posso, tenho uma tese para fazer", Em particular ao Filipe Oliveira, António Tavares, Rui Soares, Carlos Neves e Marisa Matos.

A Manuela Quintaneiro e Margarida Lima pelas palavras encorajadoras nos momentos difíceis.

A todos os meus professores que me deram competências para chegar a este ponto da minha formação.

A Maria de Lurdes, pelo apoio incondicional, revisão do texto e tempo que não lhe dediquei.

Ao meu irmão, Telmo Silva, pela revisão da tese, pelas ajudas no trabalho e no resto, e por me aturar a má disposição!

Aos meus pais e avós por me aturarem as "taras e manias" e por tudo aquilo que hoje sou.

A toda a restante família (impossível de nomear!) por tudo o que representam e fazem por mim no dia-a-dia.

À Fundação para a Ciência e Tecnologia e ao Fundo Social Europeu pelo apoio financeiro tão importante para a minha dispensa de serviço docente. Adicionalmente a todos os que tornaram possível esse apoio e dispensa.

Apesar das palavras serem poucas comparadas com o que representam, expresso a todos os meus sinceros agradecimentos.

Muito obrigado!

## palavras-chave

Redundância, confiança de funcionamento, Comunicações tempo-real, sistemas distribuídos, barramentos de campo, CAN-Controller Area Network.

#### resumo

Os sistemas distribuídos embarcados (*Distributed Embedded Systems* – DES) têm sido usados ao longo dos últimos anos em muitos domínios de aplicação, da robótica, ao controlo de processos industriais passando pela aviónica e pelas aplicações veiculares, esperando-se que esta tendência continue nos próximos anos.

A confiança no funcionamento é uma propriedade importante nestes domínios de aplicação, visto que os serviços têm de ser executados em tempo útil e de forma previsível, caso contrário, podem ocorrer danos económicos ou a vida de seres humanos poderá ser posta em causa.

Na fase de projecto destes sistemas é impossível prever todos os cenários de falhas devido ao não determinismo do ambiente envolvente, sendo necessária a inclusão de mecanismos de tolerância a falhas.

Adicionalmente, algumas destas aplicações requerem muita largura de banda, que também poderá ser usada para a evolução dos sistemas, adicionando-lhes novas funcionalidades.

A flexibilidade de um sistema é uma propriedade importante, pois permite a sua adaptação às condições e requisitos envolventes, contribuindo também para a simplicidade de manutenção e reparação. Adicionalmente, nos sistemas embarcados, a flexibilidade também é importante por potenciar uma melhor utilização dos, muitas vezes escassos, recursos existentes.

Uma forma evidente de aumentar a largura de banda e a tolerância a falhas dos sistemas embarcados distribuídos é a replicação dos barramentos do sistema. Algumas soluções existentes, quer comerciais quer académicas, propõem a replicação dos barramentos para aumento da largura de banda ou para aumento da tolerância a falhas. No entanto e quase invariavelmente, o propósito é apenas um, sendo raras as soluções que disponibilizam uma maior largura de banda e um aumento da tolerância a falhas. Um destes raros exemplos é o FlexRay, com a limitação de apenas ser permitido o uso de dois barramentos.

Esta tese apresentada e discute uma proposta para usar a replicação de barramentos de uma forma flexível com o objectivo duplo de aumentar a largura de banda e a tolerância a falhas. A flexibilidade dos protocolos propostos também permite a gestão dinâmica da topologia da rede, sendo o número de barramentos apenas limitado pelo hardware/software. As propostas desta tese foram validadas recorrendo ao barramento de campo CAN – Controller Area Network, escolhido devido à sua grande implantação no mercado. Mais especificamente, as soluções propostas foram implementadas e validadas usando um paradigma que combina flexibilidade com comunicações event-triggered e time-triggered: o FTT – Flexible Time-Triggered. No entanto, uma generalização para CAN nativo é também apresentada e discutida.

A inclusão de mecanismos de replicação do barramento impõe a alteração dos antigos protocolos de replicação e substituição do nó mestre, bem como a definição de novos protocolos para esta finalidade. Este trabalho tira partido da arquitectura centralizada e da replicação do nó mestre para suportar de forma eficiente e flexível a replicação de barramentos. Em caso de ocorrência de uma falta num barramento (ou barramentos) que poderia provocar uma falha no sistema, os protocolos e componentes propostos nesta tese fazem com que o sistema reaja, mudando para um modo de funcionamento degradado. As mensagens que estavam a ser transmitidas nos barramentos onde ocorreu a falta são reencaminhadas para os outros barramentos.

A replicação do nó mestre baseia-se numa estratégia líder-seguidores (*leader-followers*), onde o líder (*leader*) controla todo o sistema enquanto os seguidores (*followers*) servem como nós de reserva. Se um erro ocorrer no nó líder, um dos nós seguidores passará a controlar o sistema de uma forma transparente e mantendo as mesmas funcionalidades.

As propostas desta tese foram também generalizadas para CAN nativo, tendo sido para tal propostos dois componentes adicionais. É, desta forma possível ter as mesmas capacidades de tolerância a falhas ao nível dos barramentos juntamente com a gestão dinâmica da topologia de rede.

Todas as propostas desta tese foram implementadas e avaliadas. Uma implementação inicial, apenas com um barramento foi avaliada recorrendo a uma aplicação real, uma equipa de futebol robótico onde o protocolo FTT-CAN foi usado no controlo de movimento e da odometria.

A avaliação do sistema com múltiplos barramentos foi feita numa plataforma de teste em laboratório. Para tal foi desenvolvido um sistema de injecção de faltas que permite impor faltas nos barramentos e nos nós mestre, e um sistema de medida de atrasos destinado a medir o tempo de resposta após a ocorrência de uma falta.

# keywords

Redundancy, dependability, real-time communications, distributed systems, fieldbuses, CAN-Controller Area Network.

#### abstract

Distributed embedded systems (DES) have been widely used in the last few decades in several application domains, from robotics, industrial process control, avionics and automotive. In fact, it is expectable that this trend will continue in the next years.

In some of these application fields the dependability requirements are very important since the fail to provide services in a timely and predictable manner may cause important economic losses or even put humans in risk. In the design phase it is impossible to predict all the possible scenarios of faults, due to the non deterministic behaviour of the surrounding environment. In that way, the fault tolerance mechanisms must be included in the distributed embedded system to prevent failures occurrence.

Also, many application domains require a high available bandwidth to perform the desired functions, or to turn possible the scaling with the addition of new features.

The flexibility of a system also plays an important role, since it improves the capability to adapt to the surrounding world, and to the simplicity of the repair and maintenance. The flexibility improves the efficiency of all the system by providing a way to efficiently manage the available resources. This is very important in embedded systems due to the limited resources often available. A natural way to improve the bandwidth and the fault tolerance in distributed systems is to use replicated buses. Commercial and academic solutions propose the use of replicated fieldbuses for a single purpose only, either to improve the fault tolerance or to improve the available bandwidth, being the first the most common. One illustrative exception is FlexRay where the bus replica can be used to improve the bandwidth of the overall system, besides enabling redundant communications. However, only one bus replica can be used. In this thesis, a flexible bus replication scheme to improve both the dependability and the throughput of fieldbuses is presented and studied. It can be applied to any number of replicated buses, provided the required hardware support is available. The flexible use of the replicated buses can achieve an also flexible management of the network topology.

This claim has been validated using the Controller Area Network (CAN) fieldbus, which has been chosen because it is widely spread in millions of systems. In fact, the proposed solution uses a paradigm that combines flexibility, time and event triggered communication, that is the Flexible Time-Triggered over CAN network (FTT-CAN). However, a generalization to native CAN is also presented and studied.

The inclusion of bus replication in FTT-CAN imposes not only new mechanisms but also changes of the mechanisms associated with the master replication, which has been already studied in previous research work. In this work, these mechanisms were combined and take advantage of the centralized architecture and of the redundant masters to support an efficient and flexible bus replication.

When considering the system operation, if a fault in the bus (or buses) occurs, and the consequent error leads to a system failure, the system reacts, switching to a degraded mode, where the message flows that were transmitted in the faulty bus (or buses) change to the non-faulty ones.

The central node replication uses a leader-follower strategy, where the leader controls the system while the followers serve as backups. If an error occurs in the leader, a backup will take the system control maintaining the system with the same functionalities.

The system has been generalized for native CAN, using two additional components that provide the same fault tolerance capabilities at the bus level, and also enable the dynamic management of the network topology.

All the referred proposals were implemented and assessed in the scope of this

All the referred proposals were implemented and assessed in the scope of this work. The single bus version of FTT-CAN was assessed using a real application, a robotic soccer team, which has obtained excellent results in international competitions. There, the FTT-CAN based embedded system has been applied in the low level control, where, mainly it is responsible for the motion control and odometry.

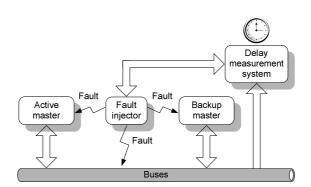

For the case of the multiple buses system, the assessment was performed in a laboratory test bed. For this, a fault injector was developed in order to impose faults in the buses and in the central nodes. To measure the time reaction of the system, a special hardware has been developed: a delay measurement system. It is able to measure delays between two important time marks for posterior offline analysis of the obtained values.

# Contents

| 1        | Inti | roduction 1                                                         |  |  |  |  |  |

|----------|------|---------------------------------------------------------------------|--|--|--|--|--|

|          | 1.1  | The problem                                                         |  |  |  |  |  |

|          | 1.2  | 2 The thesis                                                        |  |  |  |  |  |

|          | 1.3  | 3 Contributions                                                     |  |  |  |  |  |

|          |      | 1.3.1 A proposed solution to use multiple buses in a flexible way   |  |  |  |  |  |

|          |      | 1.3.2 Mechanisms to provide fault detection among multiple masters  |  |  |  |  |  |

|          |      | 1.3.3 A generalization of the proposed solutions for native CAN     |  |  |  |  |  |

|          |      | 1.3.4 A fault injector system for bus based communication systems 4 |  |  |  |  |  |

|          |      | 1.3.5 A delay measurement system                                    |  |  |  |  |  |

|          |      | 1.3.6 An implementation of the FTT-CAN middleware                   |  |  |  |  |  |

|          | 1.4  | Publications                                                        |  |  |  |  |  |

|          | 1.5  | Organization of the dissertation                                    |  |  |  |  |  |

| _        | ъ    |                                                                     |  |  |  |  |  |

| <b>2</b> |      | s media redundancy: a survey                                        |  |  |  |  |  |

|          | 2.1  | Introduction                                                        |  |  |  |  |  |

|          | 2.2  | Fault tolerant communication: a brief introduction                  |  |  |  |  |  |

|          |      | 2.2.1 Introduction                                                  |  |  |  |  |  |

|          |      | 2.2.2 Dependability                                                 |  |  |  |  |  |

|          |      | 2.2.3 Fault, error and failure                                      |  |  |  |  |  |

|          |      | 2.2.4 Fieldbuses and dependability                                  |  |  |  |  |  |

|          |      | 2.2.5 Redundancy and fault tolerance                                |  |  |  |  |  |

|          |      | 2.2.6 Replica consistency                                           |  |  |  |  |  |

|          | 2.3  | Buses for industrial automation                                     |  |  |  |  |  |

|          |      | 2.3.1 Introduction                                                  |  |  |  |  |  |

|          |      | 2.3.2 WorldFIP                                                      |  |  |  |  |  |

|          |      | 2.3.3 PROFIBUS                                                      |  |  |  |  |  |

|          |      | 2.3.4 P-NET                                                         |  |  |  |  |  |

|          | 2.4  | Buses for embedded applications                                     |  |  |  |  |  |

|          |      | 2.4.1 Introduction                                                  |  |  |  |  |  |

|          |      | 2.4.2 TTP                                                           |  |  |  |  |  |

|          |      | 2.4.3 FlexRay                                                       |  |  |  |  |  |

|          |      | 2.4.4 MIL-STD-1553B                                                 |  |  |  |  |  |

|          | 2.5  | Ethernet based solutions                                            |  |  |  |  |  |

|          | 2.6  | Controller Area Network (CAN)                                       |  |  |  |  |  |

|          |      | 2.6.1 Introduction                                                  |  |  |  |  |  |

|          |      | 2.6.2 CAN Basics                                                    |  |  |  |  |  |

|          |      | Physical layer                                                      |  |  |  |  |  |

|          |      | Data link layer                                                     |  |  |  |  |  |

|          |      | CAN fault tolerance                                                 |  |  |  |  |  |

|   |               | 2.6.3 CAN protocols with media redundancy                      | 36  |

|---|---------------|----------------------------------------------------------------|-----|

|   |               | TTCAN                                                          | 36  |

|   |               | FlexCAN                                                        | 38  |

|   |               | RedCAN                                                         | 39  |

|   |               | Columbus Egg Idea                                              | 40  |

|   |               | CANdor                                                         | 41  |

|   |               | Fault-Active Mechanism                                         | 42  |

|   |               | CANopen                                                        | 43  |

|   |               | MilCAN                                                         | 45  |

|   |               | DeviceNet                                                      | 45  |

|   |               | 2.6.4 CAN star topologies                                      | 46  |

|   | 2.7           | Brief comparison                                               | 48  |

|   | 2.8           | Conclusions                                                    | 51  |

| 3 | Αp            | oposal for bus media redundancy in FTT-CAN                     | 53  |

| _ | 3.1           | Introduction                                                   | 53  |

|   | 3.2           | The FTT-CAN protocol                                           | 54  |

|   | 0.2           | 3.2.1 FTT master replication                                   | 56  |

|   |               | 3.2.2 FTT features summary                                     | 57  |

|   | 3.3           | Limitations of the FTT-CAN                                     | 57  |

|   | 0.0           | 3.3.1 The priority inversion and jitter problem                | 57  |

|   |               | 3.3.2 Network redundancy support                               | 59  |

|   |               | 3.3.3 Available bandwidth                                      | 59  |

|   | 3.4           | FTT-CAN with multiple buses                                    | 64  |

|   | J.T           | 3.4.1 Introduction                                             | 64  |

|   |               | 3.4.2 Multiple buses architecture                              | 65  |

|   |               | 3.4.3 The trigger message                                      | 65  |

|   |               | Bandwidth allocation for synchronous and asynchronous messages | 69  |

|   |               |                                                                | 71  |

|   |               | Strategy and trigger flags example                             | 72  |

|   | 2 =           | 3.4.4 Master replication                                       | 73  |

|   | 3.5           | -                                                              |     |

|   |               |                                                                | 73  |

|   |               | 3.5.2 Fault model and assumptions                              | 74  |

|   |               | 3.5.3 Detectable faults                                        | 74  |

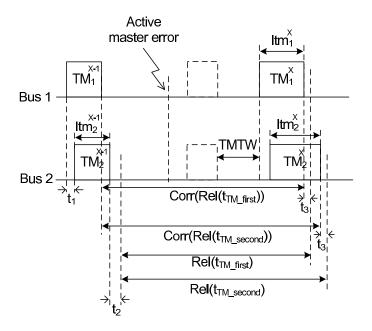

|   |               | 3.5.4 Master errors: replacement and analysis                  | 75  |

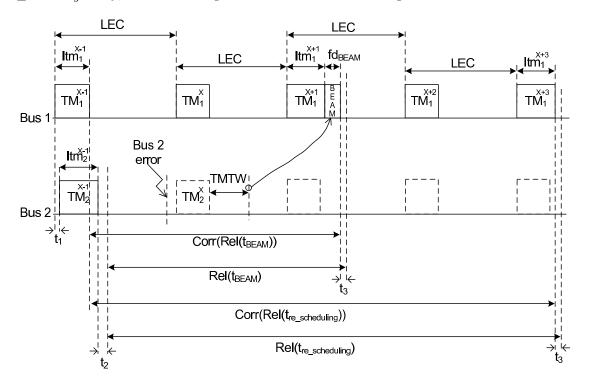

|   |               | 3.5.5 Bus errors: replacement and analysis                     | 79  |

|   |               | Reconfiguring the buses                                        | 81  |

|   |               | Bus error detection in two or more buses and practical issues  | 83  |

|   | 3.6           | Final remarks                                                  | 86  |

|   | 3.7           | Conclusions                                                    | 87  |

| 4 | $\mathbf{FT}$ | -CAN Implementation                                            | 89  |

|   | 4.1           | Introduction                                                   | 89  |

|   | 4.2           | Data structures and API                                        | 89  |

|   |               | 4.2.1 The synchronous requirement database                     | 93  |

|   |               | 4.2.2 The trigger message                                      | 97  |

|   |               | 4.2.3 Application programming interface                        | 99  |

|   | 4.3           | The master implementation                                      | 100 |

|   |               | 4.3.1 Single bus master                                        | 101 |

|   |               | 4.3.2 Multiple buses master                                    | 105 |

|   | 4.4            | The slave implementation                                  |

|---|----------------|-----------------------------------------------------------|

|   | 4.5            | Evaluation of the computational overhead                  |

|   |                | 4.5.1 Experimental results                                |

|   | 4.6            | Conclusions                                               |

|   |                |                                                           |

| 5 | $\mathbf{Exp}$ | perimental evaluation 115                                 |

|   | 5.1            | Introduction                                              |

|   | 5.2            | Single bus mechanisms' assessment                         |

|   |                | 5.2.1 Experimental platform: the CAMBADA soccer robot 116 |

|   |                | 5.2.2 Communication requirements                          |

|   |                | 5.2.3 Communications architecture                         |

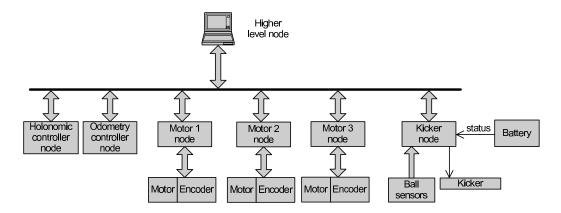

|   |                | 5.2.4 Synchronizing data flows                            |

|   |                | 5.2.5 Experimental validation                             |

|   | 5.3            | Multiple buses experimental platform and results          |

|   |                | 5.3.1 Experiment's rationale                              |

|   |                | 5.3.2 Fault injector and delay measurement system 129     |

|   |                | Fault injector                                            |

|   |                | The delay measurement system (DMS)                        |

|   |                | Using the DMS in related work                             |

|   |                | Joining time measurement and fault injection              |

|   |                | 5.3.3 Experimental setup and results                      |

|   |                | Bus error test results                                    |

|   |                | Active master error test results                          |

|   |                | 5.3.4 Practical issues                                    |

|   |                | Comparing expected and practical delays                   |

|   | 5.4            |                                                           |

|   | 5.4 $5.5$      | Results summary                                           |

|   | 5.5            | Conclusions                                               |

| 6 | Usi            | ng multiple buses in native CAN - A generalization 153    |

| Ū | 6.1            | Introduction                                              |

|   | 6.2            | Comparing bus and stars architecture in terms of wiring   |

|   | 6.2            | Providing automatic bus redundancy in legacy CAN          |

|   | 6.4            | Fault hypothesis                                          |

|   | 6.5            | v a                                                       |

|   |                |                                                           |

|   | 6.6            | 1 00                                                      |

|   | c 7            |                                                           |

|   | 6.7            | Operational scenarios                                     |

|   | 6.8            | Implementation                                            |

|   | 6.9            | Conclusions                                               |

| 7 | Cor            | aclusions and future work 167                             |

| ' |                | Thesis validation                                         |

|   | $7.1 \\ 7.2$   | Future research                                           |

|   | 1.4            |                                                           |

|   |                | 7.2.1 The asynchronous messaging system                   |

|   |                | 7.2.2 Slave nodes                                         |

|   |                | 7.2.3 Dependability evaluation                            |

|   |                | 7.2.4 Generalization to other protocols                   |

|   |                | 7.2.5 Wireless and heterogeneous networks 170             |

# List of Figures

| 2.1  | The dependability tree (from [ALR01])                             | 11 |

|------|-------------------------------------------------------------------|----|

| 2.2  | Network topologies                                                | 16 |

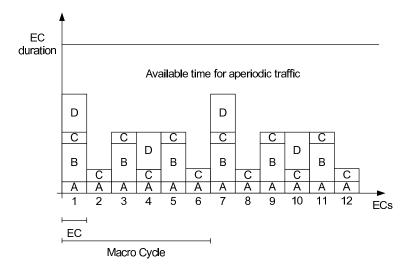

| 2.3  | Macro cycle example (from [AC98])                                 | 19 |

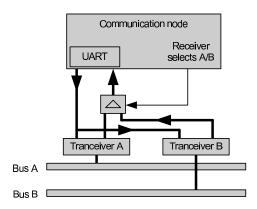

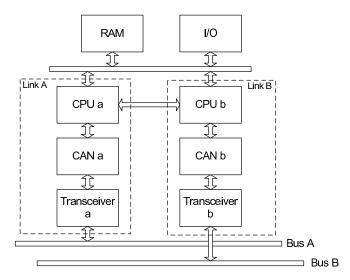

| 2.4  | PROFIBUS node architecture with redundant bus(from [LS95])        | 21 |

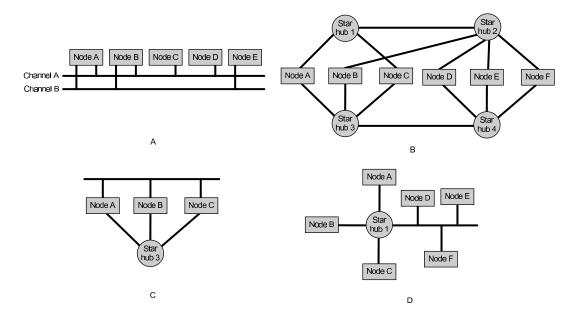

| 2.5  | FlexRay network topologies                                        | 25 |

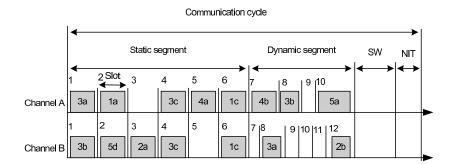

| 2.6  | FlexRay communication cycle (from [MT06])                         | 26 |

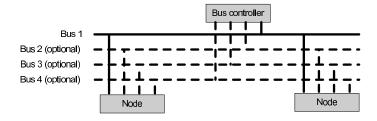

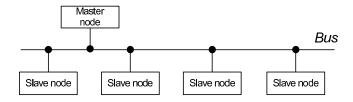

| 2.7  | MIL-STD-1553B system architecture                                 | 27 |

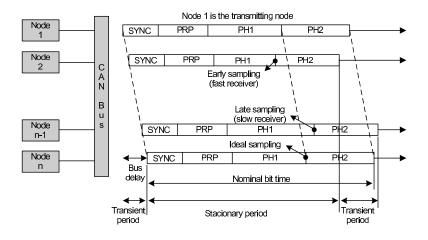

| 2.8  | CAN bit timing (from [RVA99])                                     | 30 |

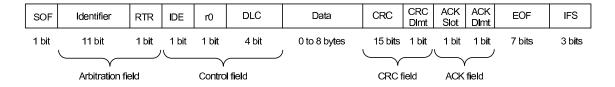

| 2.9  | CAN 2.0A frame format                                             | 32 |

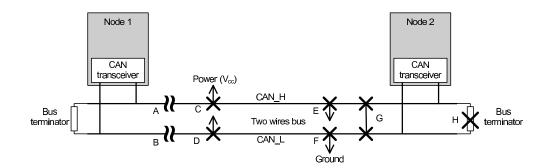

| 2.10 | Failures in CAN ISO 11898-2 (from [RVA99])                        | 34 |

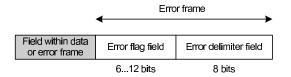

|      | Error frame                                                       | 35 |

|      | CAN error states                                                  | 36 |

|      | TTCAN network example (from $[MFH^+02]$ )                         | 37 |

|      | Fault tolerant TTCAN network example (from [MFH <sup>+</sup> 02]) | 37 |

|      | FlexCAN node and OSI layers (from [PF04])                         | 38 |

|      | FlexCAN architecture (from [PF04])                                | 39 |

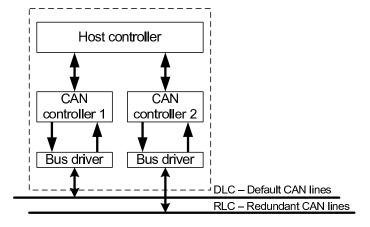

|      | RedCAN module (from [SOJT04])                                     | 39 |

|      | Columbus Egg Idea physical layer (from [RVA99])                   | 40 |

|      | CANdor node (from [FNP+98])                                       | 41 |

|      | Fault tolerant communication node (from [HKD97])                  | 42 |

|      | CANopen redundant communication                                   | 44 |

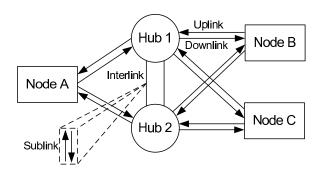

|      | ReCANCentrate architecture (from [BPA09])                         | 47 |

|      | ( [ 17                                                            |    |

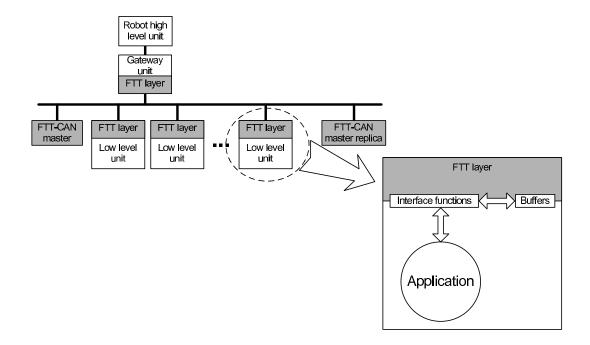

| 3.1  | FTT-CAN architecture                                              | 54 |

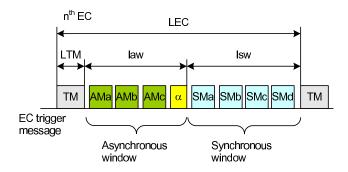

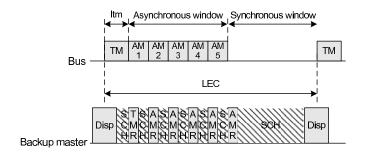

| 3.2  | The elementary cycle in FTT-CAN                                   | 55 |

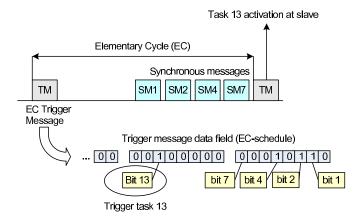

| 3.3  | Master-multislave access control and EC schedule coding scheme    | 55 |

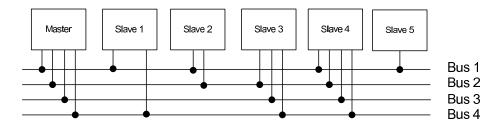

| 3.4  | FTT-CAN with multiple buses architecture                          | 65 |

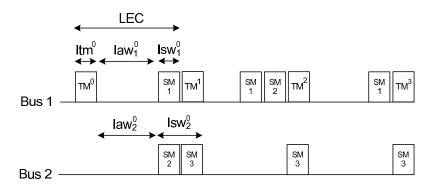

| 3.5  | Scenario (a)                                                      | 67 |

| 3.6  | Scenario (b)                                                      | 68 |

| 3.7  | Scenario (c)                                                      | 68 |

| 3.8  | Example of trigger message with multiple buses                    | 72 |

| 3.9  | System architecture for multiple masters                          | 73 |

| 3.10 | Master replacement state diagram                                  | 76 |

|      | Master replacement protocol                                       | 77 |

| 3.12 | Bus error detection mechanism                                     | 79 |

| 3.13 | Bus error asynchronous message (BEAM)                             | 81 |

| 3.14 | Bus changing time flow                                            | 83 |

|      | Multiple errors detection                                         | 84 |

| 3 16 | Delay in transmission of the trigger messages in different buses  | 85 |

| 4.1  | FTT stack                                                              | 2  |

|------|------------------------------------------------------------------------|----|

| 4.2  | SRT line for multiple buses                                            | 6  |

| 4.3  | Synchronous requirement table architecture                             | 7  |

| 4.4  | Trigger message structure                                              | 8  |

| 4.5  | Development board for PIC18F258                                        | 1  |

| 4.6  | Development board for dsPIC30F6012A                                    | 2  |

| 4.7  | Master firmware overview                                               | 3  |

| 4.8  | Timer occurrences in masters                                           | 4  |

| 4.9  | Master firmware with multiple buses                                    | 6  |

| 4.10 | Slave firmware overview                                                |    |

| 4.11 | Backup master computational overhead                                   |    |

|      |                                                                        |    |

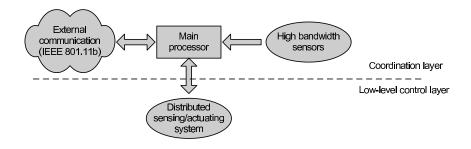

| 5.1  | The biomorphic architecture of the CAMBADA robots                      | 7  |

| 5.2  | Functional robot modules                                               | 7  |

| 5.3  | FTT-CAN low-level control system                                       | 2  |

| 5.4  | Timeline for motion information flow                                   | 3  |

| 5.5  | Master replacement delay                                               | 5  |

| 5.6  | Assessment setup global view                                           | 6  |

| 5.7  | Bus error timeline                                                     | 8  |

| 5.8  | Master error timeline                                                  | 9  |

| 5.9  | Multiplexer structure                                                  | 9  |

| 5.10 | CAN bus multiplexers                                                   | 1  |

| 5.11 | Fault injector internal modules                                        | 2  |

|      | DMS internal structure                                                 | 3  |

|      | xDMS internal modules                                                  | 4  |

|      | Measurement architecture                                               | 5  |

|      | Developed system                                                       | 6  |

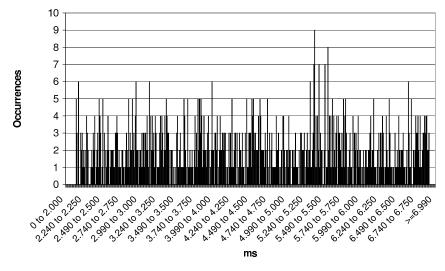

|      | Maximum of $t_{phase}$                                                 | 7  |

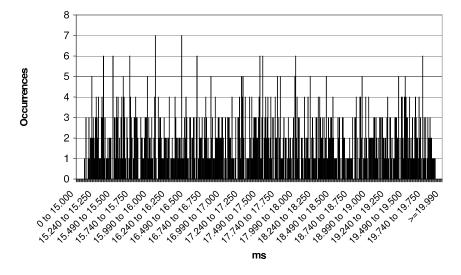

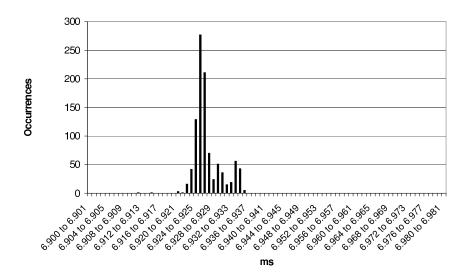

|      | Fault-injection instant histogram                                      | 8  |

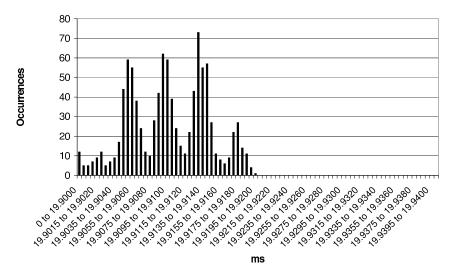

|      | $t_{BEAM}$ histogram (absolute delay)                                  | 0  |

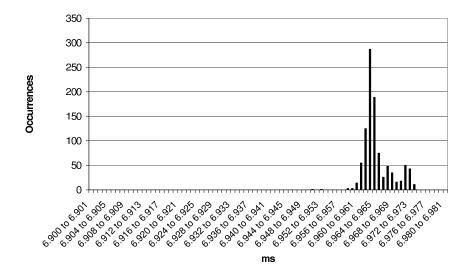

|      | $Rel(t_{BEAM})$ histogram (relative delay)                             | 1  |

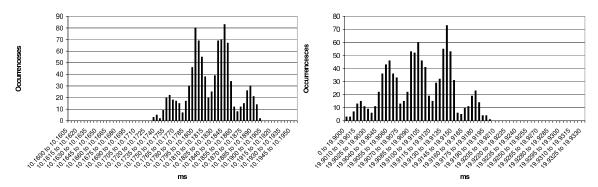

|      | $t_{re\ scheduling}$ histogram (absolute delay)                        | 1  |

|      | $Rel(t_{re\_scheduling})$ histogram (relative delay)                   | 2  |

|      | $Rel(t_{BEAM})$ and $Rel(t_{re\_scheduling})$ injecting a dominant bit | 2  |

| 5.23 | $t_{TM}$ first histogram (absolute delay)                              | .3 |

|      | $Rel(t_{TM \ first})$ histogram (relative delay)                       | .3 |

|      | $Rel(t_{TM} _{second})$ histogram (relative delay)                     |    |

|      | Practical analysis for bus error timeline                              | 5  |

|      | Practical analysis for master error timeline                           |    |

| 6.1  | Star topology best scenario                                            | .1 |

| 6.2  | Bus topology best scenario                                             |    |

| 6.3  | Replicated network with heterogeneous nodes                            |    |

|      | •                                                                      |    |

| 6.4  | Proposed architecture                                                  |    |

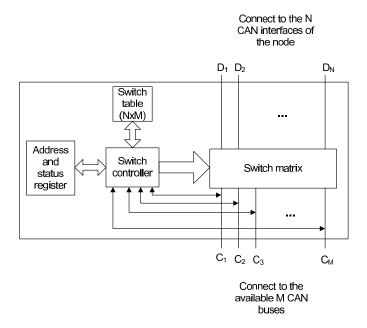

| 6.5  | Network switch unit architecture                                       |    |

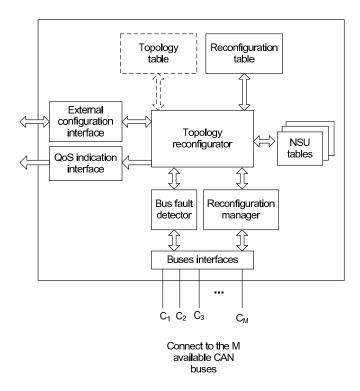

| 6.6  | Topology management unit architecture                                  |    |

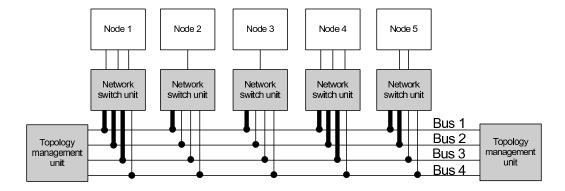

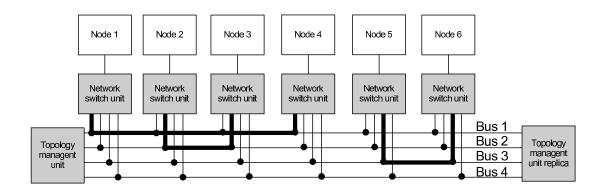

| 6.7  | Architecture example                                                   |    |

| 6.8  | Operational scenario example                                           |    |

| 6.9  | Operational scenario: star                                             |    |

| 0.10 | 5WILCH CONFIDNEL (ILLOH 1910AL)                                        |    |

# List of Tables

| 2.1  | Type of redundancy                                              |

|------|-----------------------------------------------------------------|

| 2.2  | Bus arbitrator table example                                    |

| 2.3  | Industrial automation protocols comparison                      |

| 2.4  | Embedded applications protocols comparison                      |

| 2.5  | CAN based protocols comparison                                  |

| 2.6  | CAN star topologies comparison                                  |

| 2.7  | Ethernet based protocols comparison                             |

| 3.1  | CAN overhead                                                    |

| 3.2  | Trigger message overhead for $5ms$ of elementary cycle 63       |

| 3.3  | Trigger message overhead for $20ms$ of elementary cycle 65      |

| 4.1  | Message and task parameters mapping                             |

| 4.2  | Trigger message parameters mapping                              |

| 5.1  | Low-level control layer communication requirements              |

| 5.2  | Low-level control layer message set and activity tasks          |

| 5.3  | Timeliness of information flow                                  |

| 5.4  | CAN high and CAN low lines voltages                             |

| 5.5  | Multiplexer functions                                           |

| 5.6  | xDMS parameters for bus faults                                  |

| 5.7  | xDMS parameters for master faults                               |

| 5.8  | Observed, corrected and theoretical delays for bus error        |

| 5.9  | Observed, corrected and theoretical delays for bus master error |

| 5.10 | Results summary                                                 |

| 6.1  | Cable length comparison                                         |

| 6.2  | NSU table example                                               |

| 6.3  | NSU table example after faulty bus                              |

# Chapter 1

# Introduction

# 1.1 The problem

In the last few decades Distributed Embedded Systems (DES) have been widely used in several application fields, ranging from industrial machinery to avionics, automotive systems and robotics. Most of these applications have strict timeliness requirements. Also, the requirements of these systems that can only be met with deterministic networks, and rely on distributed coordination that require synchronization protocols. Besides in many cases, they require mechanisms for online reconfiguration and fault tolerance. These mechanisms impose an overhead in terms of network bandwidth and computational performance of the nodes.

Fieldbuses are usually adopted for the network infrastructure. One of the most popular fieldbuses is CAN - Controller Area Network [BOS91]. CAN protocol was initially targeted to automotive control systems, as a single digital bus to replace traditional point-to-point cables that were growing in complexity, weight and cost with the introduction of new electrical and electronic systems. The widespread and successful use of CAN in the automotive industry, the low cost associated with high volume production of controllers and its inherent technical merit, have driven to CAN adoption in other application domains. Despite its success story, CAN application designers would be happier if CAN could be made faster, cover longer distances, be more deterministic and more dependable. Some current distributed control applications require higher bandwidth [SFNM05] and the dependability of native CAN is not adequate for some applications, e.g., wheel-chairs robots [BHHP01], autonomous robots for urban transportation vehicles [BNMS05], urban transportation systems [MZP+02, WTSW03], x-by-wire system for automotive [Tea98] and home automation systems [BFS+07, FBS+08].

The shortcomings of CAN call for new solutions, either based on CAN extensions/improvements or on the adoption of another fieldbus protocol. It can be said that CAN technology is now mature and engineers are well trained in designing and maintaining CAN based DES, with relative low time to market. So a potential migration to other fieldbus technology is challenging and it could take several years.

In this scenario, and not only to replace CAN, new fieldbuses were proposed, notably FlexRay [Fle02] and TTP/C [KG94] (TTP stands for Time-Triggered Protocol). In parallel with the advent of new fieldbus protocols, extensions/improvements of CAN have been proposed over the years, such as: Time-Triggered CAN (TTCAN) [HMFH00, ISO01], Flexible Time-Triggered over CAN (FTT-CAN) [APF02] or FlexCAN [PF04]. Notice, however, that none of these solutions solve the problems of native CAN, just minimize them. Indeed some solutions address fault tolerance issues, while others increase the available bandwidth.

In this context, it would be desirable to increase the available bandwidth of CAN and to improve its fault tolerance capabilities while maintaining the backward compatibility with legacy systems. A possible solution to this problem is using multiple buses to provide additional bandwidth, which is proportional to the number of used buses. This extra bandwidth can be used either to provide bus media redundancy only, transmitting different data in different buses, or to provide data redundancy, transmitting the same data in different buses. A third alternative would be combining these two approaches in a flexible way, *i.e.*, the network could provide a mix of bus media redundancy and data redundancy. This is a flexible approach in the sense that the bus media redundancy and the data redundancy trade-off can be assigned online according to the application requirements in terms of bandwidth and dependability.

Besides the described features, a multiple buses architecture can also be used to tolerate bus failures, so that the network can be switched to degraded modes using less buses than originally.

This thesis proposes components and protocols to take advantage of multiple CAN buses, and to achieve bus fault tolerance and efficient bandwidth usage. Notice that FTT-CAN is used as a proof of concept, since the proposal can be generalized to other fieldbus protocol, including native CAN.

# 1.2 The thesis

The thesis supported by the present dissertation argues that:

The use of a flexible bus replication scheme could improve both the dependability and the throughput of a network. Furthermore, it is possible to adapt online the network topology to evolving operational scenarios.

# 1.3 Contributions

The main contributions presented in this dissertation are:

- A proposed solution to use multiple buses in a flexible way;

- Mechanisms to provide fault detection among multiple masters;

1.3 Contributions 3

- A generalization of the proposed solutions for native CAN;

- A fault injector system for bus based communication systems;

- A delay measurement system (DMS);

- An implementation of the FTT-CAN middleware.

Despite the system architecture, protocols and components, are targeted to the FTT-CAN protocol [APF02] and native CAN, most of the contributions could equally generalized to other fieldbuses.

Next, the contributions are summarized.

# 1.3.1 A proposed solution to use multiple buses in a flexible way

The previous versions of FTT-CAN support only one bus making it a single point of failure. One way to avoid this problem is by replicating the bus.

This thesis presents a proposal to replicate the bus to provide flexible bus media redundancy and data redundancy.

The proposal takes advantage of the bus media redundancy to increase the dependability while providing additional bandwidth. In this way, whenever a bus would fail, the affected traffic could be switched to other bus and the network would start operating in a degraded mode. The maximum number of buses the system can accommodate is only limited by the hardware, such as the number of CAN interfaces or by the performance limits of the microcontrollers used.

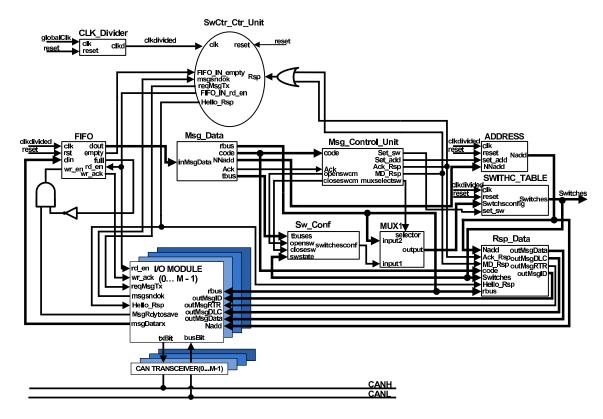

The management of buses and messages is made by the FTT-CAN central node, the master, that is also replicated. The proposal was implemented and validated using a fault injection system combined with a delay measurement system.

# 1.3.2 Mechanisms to provide fault detection among multiple masters

The previous FTT-CAN architecture included a protocol to handle master replication [MFA<sup>+</sup>02]. However, with the introduction of bus media redundancy, the master replication protocol needs to be updated in order to accommodate the management of multiple buses. This thesis proposes a new master replacement protocol, based on the single bus version [FPAF02], where the active master node is responsible to detect and to react to permanent bus faults. This protocol relies on the masters location, at both ends of the buses, to have a global view of the network and to avoid bus partitions.

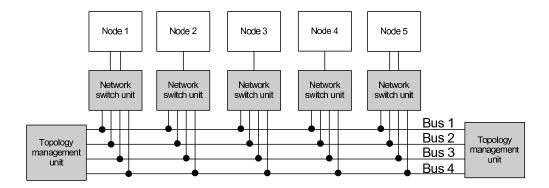

## 1.3.3 A generalization of the proposed solutions for native CAN

The proposed multiple buses and multiple master system is targeted to FTT-CAN, however, it can be generalized to any fieldbuses. A proposal to generalize the bus media redun-

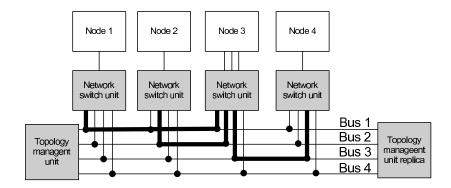

dancy to native CAN is presented in this work. The generalization of the concept requires two new components, a Topology Management Unit (TMU) and a Network Switch Unit (NSU), that were designed and partially implemented. The network topology management has a global view of the network and controls all the network switch units. The network topology management is replicated and follows the same strategy as the master replication node in the FTT-CAN bus replication presented before. This is, the network topology management units are located at the end of the CAN bus and exchange messages with the other located in the other end.

# 1.3.4 A fault injector system for bus based communication systems

A hardware of a fault injector was developed to assess the multiple buses and multiple masters system. This fault injector imposes faults in the CAN bus (or buses) or in the FTT-CAN master node. The fault injector is capable of injecting different kinds of faults at pre-defined instants.

The fault injector has been designed for the FTT-CAN, but it can be used in native CAN without any adaptation. Moreover, it can be easily adapted to any other fieldbus protocol.

# 1.3.5 A delay measurement system

The fault injector works in close cooperation with a delay measurement system that recognizes the instant of the fault injection and the relevant timing instants of the FTT-CAN, to measure the time elapsed between these different instants. The collected data, a histogram, is stored internally in the Delay Measurement System (DMS) and it can be uploaded to a personal computer.

The DMS is generic, thus it can be used in other contexts, where the events to recognize are not related to FTT-CAN. For example, it has been used in an Ethernet based system [BSF07].

# 1.3.6 An implementation of the FTT-CAN middleware

A new, designed from scratch, FTT-CAN implementation was made. This implementation became the FTT-CAN reference implementation, used in real world applications.

The FTT-CAN implementation includes the single bus nodes with all the defined features. For the case of the multiple buses, only the master node was implemented. Slave nodes with multiple buses were not implemented because they are out of scope of this thesis.

# 1.4 Publications

The presented contributions have been published in a book chapter, journals and conference proceedings. They are listed below:

1.4 Publications 5

# Book chapter

Luís Almeida, Paulo Pedreiras, Joaquim Ferreira, Mário Calha, José Fonseca, Ricardo Marau, Valter Silva, and Ernesto Martins. Handbook of Real-Time and Embedded Systems, chapter 19, pages 19–1 to 19–22. CRC Press, 2007;

# Journal papers

- Ricardo Moraes, Francisco Carreiro, Paulo Bartolomeu, Valter Silva, José Fonseca, and Francisco Vasques. Enforcing the timing behavior of real-time stations in legacy bus-based industrial Ethernet networks. *Computer Standards & Interfaces*, In Press, Corrected Proof, 2010;

- Ricardo Marau, Valter Silva, Joaquim Ferreira, Luís Almeida, and José Fonseca. Assessment of FTT-CAN master replication mechanisms for safety-critical applications. Transactions Journal of Passenger Cars-Electronic and Electrical Systems, pages 447—455, March 2007♣. Also presented at SAE 2006 World Congress (see paper ♠);

### Conference papers

- Valter Silva, Paulo Bartolomeu, Joaquim Ferreira, and José Fonseca. Assessment of multi-bus fault-tolerant communications. In proceedings of the 7<sup>th</sup> IEEE International Conference on Industrial Informatics (INDIN), pages 72 –78, Cardiff, Wales, UK, June 2009;

- José Fonseca, Paulo Bartolomeu, Valter Silva, Vasco Santos, Carlos Abreu, Alexandre Mota, Margarida Cunha, and Arminda Lopes. Using CAN to retrofit houses for quadriplegic people. In 12<sup>th</sup> International CAN Conference, Barcelona, Spain, March 2008;

- Valter Silva, José Fonseca, and Joaquim Ferreira. Adapting the FTT-CAN Master for Multiple-bus Operation. In proceedings of the 5<sup>th</sup> IEEE International Conference on Industrial Informatics (INDIN), Vienna, Austria, July 2007;

- Paulo Bartolomeu, José Fonseca, Vasco Santos, Alexandre Mota, Valter Silva, and Margarida Sizenando. Automating Home Appliances For Elderly and Impaired People: The B-Live Approach. In Software Development for Enhancing Accessibility and Fighting Info-exclusion, Vila Real, Portugal, November 2007;

- Valter Silva, Joaquim Ferreira, and José Fonseca. Flexible Bus Media Redundancy. In proceedings of the 4<sup>th</sup> International Workshop on Dependable Embedded Systems (in conjunction with the 26<sup>th</sup> Symposium on Reliable Distributed Systems), Beijing, China, October 2007;

- Valter Silva, Joaquim Ferreira, and José Fonseca. Master Replication and Bus Error Detection in FTT-CAN with Multiple Buses. In proceedings of the 12<sup>th</sup> IEEE Conference on Emerging Technologies and Factory Automation (ETFA), Patras, Greece, 2007;

- Paulo Bartolomeu, Valter Silva, and José Fonseca. Delay measurement system for realtime serial data streams. In proceedings of 12<sup>th</sup> IEEE Conference Emerging Technologies and Factory Automation (ETFA), pages 516-523, Patras, Greece, September 2007;

- José Fonseca, Paulo Bartolomeu, Valter Silva, and Francisco Carreiro. On the practical issues of implementing the VTPE-hBEB protocol in small processing power controllers.

In proceedings of the 12<sup>th</sup> IEEE Conference on Emerging Technologies and Factory Automation (ETFA), pages 949 956, Patras, Greece, September 2007;

- Ricardo Marau, Valter Silva, Joaquim Ferreira, Luís Almeida, and José Fonseca.

Assessment of FTT-CAN master replication mechanisms for safety-critical applications.

In proceedings of the 2006 SAE congress & exhibition, number 06AE-278, 2006. published at Transactions Journal of Passenger Cars-Electronic and Electrical Systems (see paper .);

- Valter Silva, Joaquim Ferreira, and José Fonseca. Dynamic Topology Management in CAN. In proceeding of the 11<sup>th</sup> IEEE Conference on Emerging Technologies and Factory Automation (ETFA), pages 1222 1229, Prague, Czech Republic, September 2006;

- Valter Silva, José Fonseca, and Joaquim Ferreira. Using FTT-CAN to the Flexible Control of Bus Redundancy and Bandwidth Usage. In proceedings of the 11<sup>th</sup> International CAN Conference (iCC), pages 5.9 – 5.15, Stockholm, Sweden, September 2006;

- Valter Silva and José Fonseca. Using FTT-CAN to Combine Redundancy with Increased Bandwidth. In proceedings of the 6<sup>th</sup> IEEE International Workshop on Factory Communication Systems (WFCS), pages 54–62, Torino, Italy, June 2006;

- Mário Calha, José Fonseca, Valter Silva, and Ricardo Marau. Kernel design for FTT-CAN systems. In proceedings of the 6<sup>th</sup> IEEE International Workshop on Factory Communication Systems (WFCS), pages 151 – 156, Torino, Italy, June 2006;

- Fernando Ataide, Carlos Pereira, and Valter Silva. A New Approach for Time-Triggered Phase in the FTT-CAN Protocol: A Case Study in an Automotive System. In Workshop on Models and Analysis Methods for Automotive Systems, 27<sup>th</sup> IEEE Real-Time Systems Symposium, Brasil, December 2006;

- Valter Silva, José Fonseca, Urbano Nunes, and Rodrigo Maia. Communications Requirements for Autonomous Mobile Robots: Analysis and Examples. In Elsevier, editor, proceeding of FeT 2005, pages 91 – 98, Mexico, November 2005;

- Mário Calha, Valter Silva, and José Fonseca. Real-Time Procedures in Distributed Systems. In proceedings from IFAC International Conference on Fieldbus Systems and their Applications (FeT), pages 24 – 31, Mexico, November 2005;

- Valter Silva, Ricardo Marau, Luís Almeida, Joaquim Ferreira, Mário Calha, Paulo Pedreiras, and José Fonseca. Implementing a distributed sensing and actuation system: The CAMBADA robots case study. In proceedings of the 10<sup>th</sup> IEEE Conference on Emerging Technologies and Factory Automation (ETFA), volume 2, pages 781–788, Catania, Italy, September 2005;

- Luís Almeida, Frederico Santos, Tullio Facchinetti, Paulo Pedreiras, Valter Silva, and Luís Lopes. Coordinating distributed autonomous agents with a real-time database: The CAMBADA project. In proceedings of the 19<sup>th</sup> International Symposium on Computer and Information Sciences (ISCIS), 2004;

- Francisco Carreiro, José Fonseca, Valter Silva, and Francisco Vasques. The virtual token-passing Ethernet implementation and experimental results. In *proceedings of the* 3<sup>rd</sup> International Workshop on Real-Time Networks, pages 57 60, Catania, Italy, June 2004.

# 1.5 Organization of the dissertation

In order to support the thesis previously stated, this dissertation is organized as follows:

- Chapter 2 Presents background information concerning dependability, and more specifically redundancy in fieldbuses. This chapter presents a survey of the protocols which support redundant buses or nodes. In particular, the CAN protocol is analyzed, with special attention to its dependability features. This chapter also presents a comparative study regarding the use of redundancy.

- Chapter 3 This chapter begins with the presentation of the FTT-CAN protocol in its single bus, multiple master version, highlighting the limitations in terms of dependability and bandwidth. The FTT-CAN protocol with bus media redundancy is then presented and discussed. This chapter also presents the necessary adaptations of the master node so it could handle multiple buses. Special attention is given to the master replication protocol for the multiple buses case.

- Chapter 4 This chapter describes the implementation of FTT-CAN protocol with special emphasis on the application programming interface available for FTT-CAN applications and presents the relevant data structures. The single bus implementation is a particular instance of the multiple buses one. Despite the slave implementation is only made for the single bus version, it is also discussed in this chapter.

- Chapter 5 The implementation presented in the previous chapter is verified and validated in this chapter. This chapter describes test platforms which are different for the single and multiple buses implementation. The additional hardware needed to perform the verification and validation, the fault injector and delay measurement system, is also described. The chapter is concluded with the experimental results and their discussion.

- Chapter 6 This chapter presents a generalization of the proposed solutions to legacy CAN networks. Two new components are introduced: the network switch unit and the topology management unit. A preliminary implementation of the network switch unit is presented.

- **Chapter 7** Sets the conclusion of the dissertation and points out several directions for future work.

# Chapter 2

# Bus media redundancy: a survey

# 2.1 Introduction

This chapter presents a survey of the state of the art concerning media redundancy techniques used in communications for safety critical applications. The chapter is divided into five main sections: a brief introduction of fault tolerant communications (section 2.2), buses for industrial automation (section 2.3), buses for embedded applications (section 2.4), Ethernet based solutions (section 2.5) and Controller Area Network (section 2.6).

The first section presents relevant definitions and concepts on the dependability, redundancy and fault tolerance techniques applied to communications.

The second section considers the fieldbuses for interconnecting industrial automation devices, such as the ones used in factory automation, process control and similar applications, e.g., WorldFIP, PROFIBUS and P-NET.

The third section considers fieldbuses that operate embedded in machines, in a general sense. Typical applications include avionics, automotive and robotics. Examples of such fieldbuses are TTP and FlexRay.

The fourth section addresses the protocols based on Ethernet (section 2.5), that are sometimes derived from the mentioned before.

Controller Area Network could obviously be included in one of the previous sections (buses for automation and/or buses for embedded applications), considering either its upper layer protocols such as DeviceNet and CANopen or the native CAN protocol itself. However, since the work presented in this thesis uses CAN, it was decided to describe CAN and its higher layer protocols in a specific section. The CAN section presents the fundamentals of CAN, with a special emphasis on the physical medium and introduces the redundancy techniques used in CAN based communications. Some adaptations of CAN like star topologies are also analyzed.

When considering the communication solutions analyzed in this chapter, it was decided to include a general overview of each and to devote a special attention to the physical layer redundancy. This was required to enable comparisons with the main results of the work presented in this dissertation.

# 2.2 Fault tolerant communication: a brief introduction

## 2.2.1 Introduction

When talking about fault tolerant communication it becomes necessary to introduce a set of definitions and a set of principles. The main works that include definitions concerning fault tolerant systems are [Lap92], [Lap95] and [ALR01]. There, dependability is defined using a set of attributes and means that must be met by the system to resist the threats it is subject to. Fault tolerance is one of the means to achieve dependability.

The definition of a fault tolerant system needs first the definition of a dependable system to be understandable. Both definitions will be presented in this section.

The dependability of a distributed system can be affected by the implicit use of the network. One reason for this is that the use of the communication network needs more electronic components and includes a novel resource, the physical medium. Also, the use of a communication network implies that this network can suffer from external interferences, such as electromagnetic interferences. The availability of the medium is then another concern.

One way to improve the system fault tolerance is to provide components replication, either software or hardware based. In this section the discussion on the replication issues is focused in the network. The component replicas must be synchronized to guarantee a correct operation of the system. Replica consistency is also briefly discussed further in this section.

# 2.2.2 Dependability

As stated in [ALR01], dependability of a computer system is "The ability to deliver service that can justifiably be trusted. The **service** delivered by a system is its behaviour as it is perceived by its user(s); a **user** is another system (physical, human) that interacts with the former at the **service interface**. The **function** of a system is what the system is intended for, and is described by the system specification"

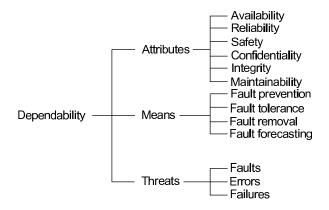

The concept of dependability can be explained with support of three elements: the **threats** to, the **attributes** of, and the **means** by which dependability is attained as shown is figure 2.1.

As it can be seen in figure 2.1, dependability is a complex concept. Mainly, there are six attributes: availability, reliability, safety, confidentiality, integrity and maintainability. More specifically:

- Availability is the capacity of the system to be ready to offer a correct service;

- Reliability is the attribute of the system to offer the continuity of a correct service;

Figure 2.1: The dependability tree (from [ALR01])

- Safety is the attribute of guaranteeing the absence of catastrophic consequences to the user(s) and the environment;

- Confidentiality is the attribute for the absence of unauthorized disclosure of information;

- Integrity is the attribute for the absence of improper system state change;

- Maintainability is the ability to undergo repairs and modifications.

In Portuguese we use the word "segurança" with a broader meaning than in English. In English "segurança" can be mapped either in safety and in security. Security is the absence of unauthorized access to, or handling of, system state [ALR01]. Security is also defined in [ALR04] by "the concurrent existence of a) availability for authorized users only, b) confidentiality, and c) integrity", where integrity means the attribute for the absence of unauthorized system state change.

Although security is currently an important issue to attain dependability considering the increasing openness of embedded systems (remote access is currently used), and, as explained before, it deals with several of the six attributes referred previously, it is out of the scope of this work and thus it will not be discussed further in this dissertation.

To develop a dependable system, different means are to be used. They can be grouped in four categories: fault prevention, fault tolerance, fault removal and fault forecasting [ALR04]. More specifically:

- Fault prevention is the means to prevent the occurrence or introduction of faults;

- Fault tolerance is the means to avoid service failure in the presence of faults. Fault tolerance can be accomplished using replication of system components or using specific components to prevent a specific fault (example of such component is a bus guardian);

- Fault removal is the means to reduce the number or severity of the faults;

Fault forecasting is the means to predict the number, severity and consequence of the faults in the future.

In the scope of our work, and in what concerns dependability, two types of systems are of concern:

- Fail-safe systems: When there are failures in the system, it responds in a way that will cause no harm, or a minimum of harm to the other systems and humans;

- Fail-operational: When there are failures in the system, it responds in a way that will keep the minimum working performance to perform the task continuation.

The concept of fault cannot be dissociated from the concept of error and failure. In the next section these three concepts are explained and discussed.

# 2.2.3 Fault, error and failure

The concepts of fault (sometimes called defect), error and failure can be found ambiguous in the literature concerning the meaning of fault and failure [Gär99]. These three terms can sometimes be interpreted as the same or can be easily confused. In [Cri91] we can read: "what one person calls a failure, a second person calls a fault, and a third person might call an error". This statement demonstrates very well the misconceptions that exist in persons about these three terms used in the fault tolerance scientific community.

Laprie et al. [Lap92] and Avižienis [ALR01], define fault, error and failure as threats for dependability. A system failure occurs when the delivered service deviates from the correct service for the system, this is, a failure occurs when the system changes from a correct service delivery to an incorrect service delivery.

Error is what causes the failure [VR01]. This is, an error that reaches the service interface will cause a failure. An activation of a fault results on an error, that reaching the service interface will provoke a failure.

Fault is an abnormal condition that causes a reduction or a loss of the capability of a functional unit to perform a required function.

Even in Portuguese there has been a discussion about the terminology of these three definition. For more information and details about this topic, refer to [VL89] and [Ver96].

## 2.2.4 Fieldbuses and dependability

The use of fieldbuses combined with the use of sensors and actuators enables the reduction and simplification of the wiring when compared with a centralized topology. Thus, it leads to a system with a lower cost and contributes to the dissemination of the solution. The increasing use of fieldbuses makes the network interfaces and transceivers cheaper and then it is possible to connect more data points in the field. Also, the use of a fieldbus compared

with the use of a centralized topology enables the distribution of the tasks among all the nodes of the network. On the other hand, centralized topologies have a central point of failure. This point of failure is the central node that carries out functions such as the control of the network and control algorithms.

However, fieldbuses introduced new possible failures in components, namely the network and the network interfaces. According to [CCTB03], the error rate of an electrical bus is very low. It can be read in [CCTB03]: "By its passive electrical nature, a bus has a very low failure rate". However, there are some faults that can occur and propagate to errors and system failures. The type of errors that can occur in the physical layer are:

- 1. A continuous transmission to the network due to an internal failure of any node or due to infinite repetitions of the transmissions attemps (babbling idiot behaviour);

- 2. The non-reception of information by one or by several nodes in the network. This can be caused by:

- disruption of transmission on the medium causing illegible frames;

- external aggression such as: cuts, impedance mismatch, loss of line termination, electromagnetic interference.

To make the communication system safe in relation to these faults it is necessary to choose a transmission support adequate to the system and environmental conditions. The dependability of fieldbus systems also depends on the redundancy of the physical layer. There has been some research work analyzing the dependability of fieldbuses such as [KP91], [PC01] and [LY05].

In [KP91] the bus and ring communication topologies for the Delta-4 distributed fault tolerant architecture [Bar93] are evaluated. In this paper, the conclusion is, for the specific case of Delta-4, that the single bus and the single ring topology are equivalent in terms of dependability. In [KP91], for a failure rate of the bus less than  $4 \times 10^{-3}/h$ , duplication of the medium is more interesting in the case of the bus than in the case of the ring.

In [PC01] the dependability of fieldbus systems in the presence of permanent failures in the bus is analyzed. This analysis includes the study of a redundant mode and also of a degraded mode. Comparing a single bus with a dual bus architecture, the authors conclude that the most important factor is a coverage factor (the coverage factor is modelled as a probability of automatic recovery from a node fault<sup>1</sup>). The coverage factor considers the existence of two types of failures: a failure that does not lead to fieldbus failure, due to a system recovery and a failure that leads to a fieldbus failure. The authors also conclude that just in case of a node coverage factor greater than 0.9 the bus duplication leads to an

<sup>&</sup>lt;sup>1</sup>Node element fault, not a system failure.

appreciable increase on dependability. This is because the failure rate of the bus is low, the dependability is mainly conditioned by the nodes failure rate and by the coverage factor.

In [LY05] the authors compare a single CAN bus architecture with a dual CAN bus architecture in terms of reliability and stability for a small aircraft. The authors conclude that, "from the simulations and implementations, the dual bus architecture enhances the fault tolerance of the system and satisfies, reliability and stability" [LY05].

In [LY05], Lin and Yen refer stability as an important parameter, not yet referred in this dissertation. Some disciplines, such as control theory, define stability as property which specifies that, for a given parameter with bounded inputs, the parameter is bounded [Sta85]. However, Stankovic defines a more specific notion for stability, please refer to [Sta85] for more details. Applying this definition to embedded distributed systems seems to be reasonable with the necessary adaptations.

# 2.2.5 Redundancy and fault tolerance

In presence of a failure, one way to promote fault tolerance is to use redundant components [Sch90]. The replication of the components can be done in a hardware level or in the application software level. In this dissertation, the redundancy studied is in the hardware, more specifically in the network.

Redundancy is "The use of more elements than necessary to maintain the performance of a system in the event of failure of one or more of the elements" [LHB03]. According to [LHB03] there are four types of redundancy: diverse, homogeneous, active and passive [LHB03].

- Diverse redundancy is the use of more than one element of different types to provide redundancy. An example of such redundancy is the use of mechanical and electrical brakes in cars:

- Homogeneous redundancy is the use of more than one element of a single type. One example of such is the use of two wires in a CAN bus, enabling differential operation in the absence of failures and single-ended if one of the wires is, by example, cut;

- Active redundancy is the use of more than one element at all times. Active redundancy

distributes the load across all the elements and allows an element failure, repair and

substitution with minimal interference in the system performance;

- Passive redundancy is the application of the redundant element only when the active element fails. Example of such redundancy is the use of a spare tire in a car.

In our opinion the first two types of redundancy (diverse and homogeneous) refer to the redundant elements themselves and the last two (active and passive) to the operation of the redundant elements. This is, we are defining two dimensions of redundancy: on the elements (diverse or homogeneous) and regarding type of operation (active or passive).

In the previous paragraphs, the redundancy is seen in a general point of view. However the same definitions can be applied and used in the fieldbuses domain. One example of diverse redundancy is the use of more than one fieldbus type to send the same information.

Concerning the type of operation, other authors [DSS98, WPS $^+00$ ] define more types besides the two referred before: semi-active and semi-passive.  $D\acute{e}fago\ et\ al.$  [DSS98] stated that a system uses semi-passive redundancy, when there is a primary server and backups. Concerning databases, in semi-passive replication, the selection of the server that processes the request from the client is based on a rotating coordinator paradigm. The same authors [DSS98], define semi-active redundancy for databases. In semi-active replication, all the servers process the request and the primary master applies the changes in all backups. Applying these definitions (semi-passive replication and semi-active replication) to bus redundancy seams to be inadequate, however it can be applied to node redundancy.

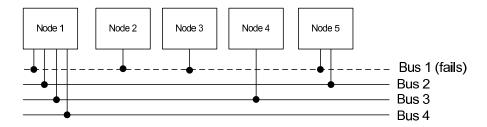

Regarding fieldbuses, a passive redundancy is considered when the additional buses are in standby and one of them is activated in the case of a failure in the primary bus. Conversely, when using active redundancy, all the available buses are used to send redundant data.

Each type of redundancy is more adequate for each type of system. In that way, if the cause of the failure cannot be anticipated, the most suitable redundancy type is diverse redundancy. On the other hand, if the probable cause of failure can be anticipated, the most suitable redundancy is the homogeneous redundancy. Active redundancy is used in critical systems that must maintain continuous operation in a case of a system element failure. Passive redundancy is used in elements of a system that are noncritical or in systems where performance interruption is tolerable. In table 2.1 this is systematize.

| System/failure                     | Redundancy  |

|------------------------------------|-------------|

| Failure can be antecipated         | Homogeneous |

| Failure cannot be antecipated      | Diverse     |

| System must maitain operation      | Active      |

| Performance interruption tolerable | Passive     |

Table 2.1: Type of redundancy

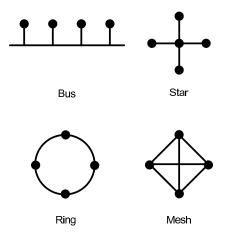

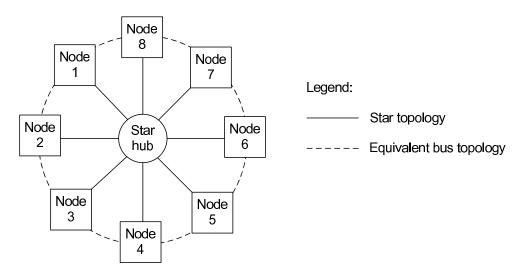

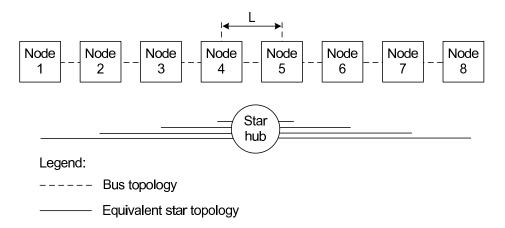

As it can be seen in figure 2.2, for the network there are mainly four topologies (or hybrid solutions among them) that can be used: star, mesh, ring and bus.

Star topology implies that there is a central point that controls all the system network. This central node can be replicated and, also, the links to the nodes can be replicated. Moreover, all the processing must be done by the central point, which must be a system with an appreciable processing power. This can be costly due to the need to replicate this element.

In case of a mesh network topology, all nodes connect to all others. In this network topology, if a link is broken, the communication can be done by other links.

The ring topology connects all the nodes forming a ring (the communication network forms a circular architecture). This kind of topology provides some redundancy, because if

Figure 2.2: Network topologies

a partition is made in the network, the system can work in a degraded mode since all nodes still have a communication path with the others. The degraded mode is achieved because no electrical termination is done in the cut wires. In the case of the partition, the network topology becomes a bus topology without termination.

In the bus topology all the nodes are connected to the same physical wires. Conversely to star topology, where a faulty node can be isolated, in bus topology a node fault can affect all the system. In case of a partition, the bus will be divided into two buses. For the bus topology, the redundancy of the bus can contribute to the system availability and reliability. However it will not contribute to the system safety because it does not avoid catastrophic consequence to persons and environment [CCTB03].

In the case of redundancy, all replicas must be consistent. This topic will be discussed further.

# 2.2.6 Replica consistency

The issue of replication is of interest in several domains, in particular in databases and in distributed systems. One of the main issues is achieving consistency among replicas which is fundamental to guarantee a correct operation of the system when one of the replicas replaces the unit that failed [PSL80, PLS82]. In the database area, examples of discussion of techniques to guarantee consistency can be found in [Bir92], [PB95] and [Mar03]. However, definitions and solutions are conceptually similar for databases and distributed systems [WPS+00].

The replication of a system component brings new problems in what concerns the synchronization of all the replicas. The component replicas must be synchronized in value and in time domains [HWV03]. The literature defines two main consistency criteria for the distributed systems [WPS<sup>+</sup>00]: linearisability and sequential consistency.

Linearisability is based in real-time dependencies while sequential consistency is only based on the order of the sequential operations performed in individual processes. Thus, linearisability is a stronger criteria than sequential consistency. A detailed comparison between them can be found in [AW94] and [GS96].

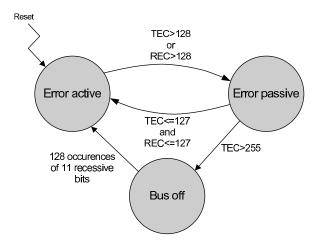

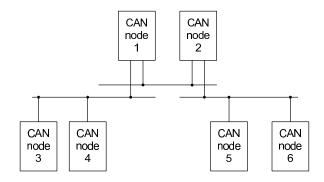

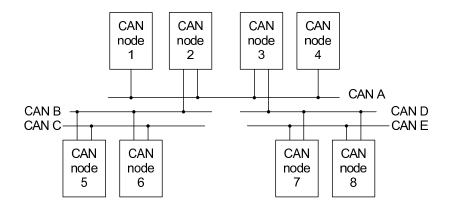

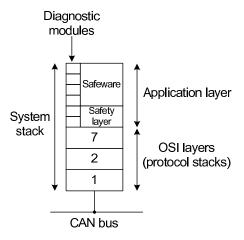

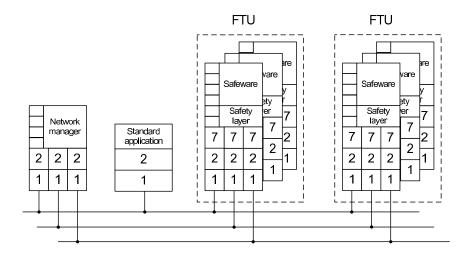

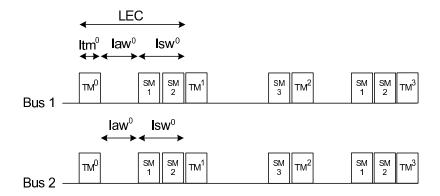

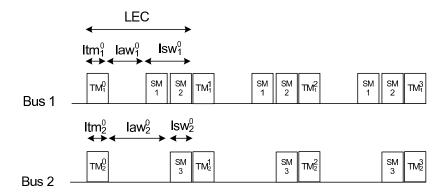

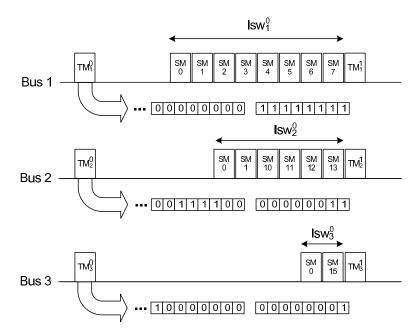

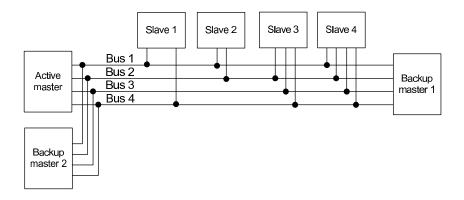

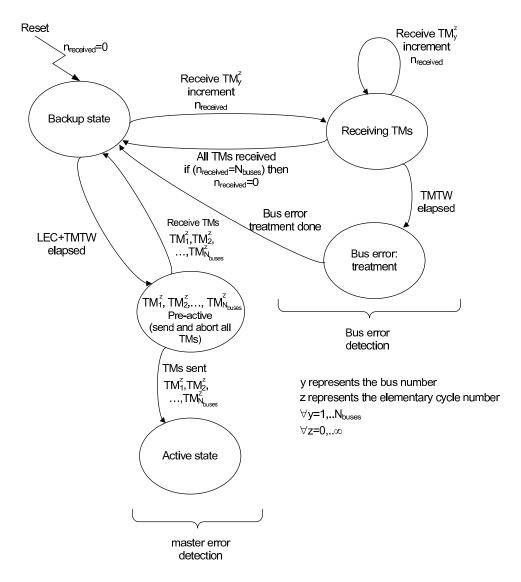

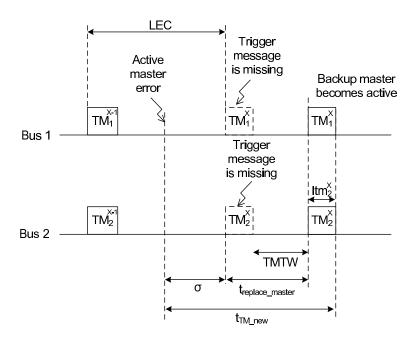

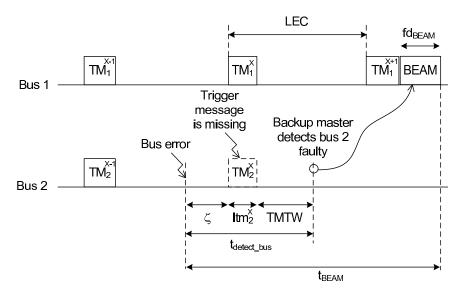

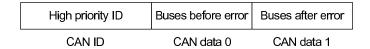

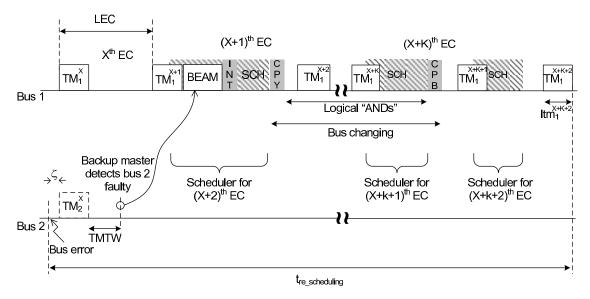

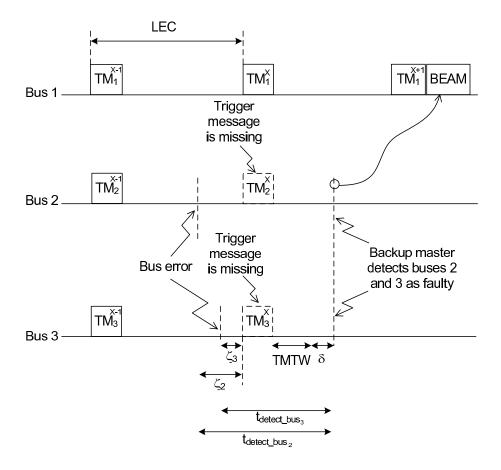

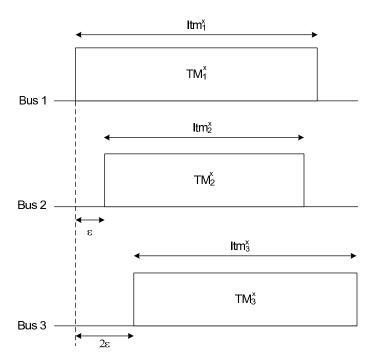

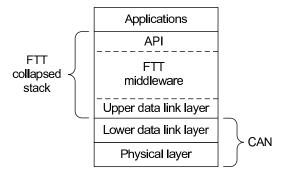

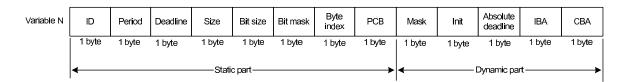

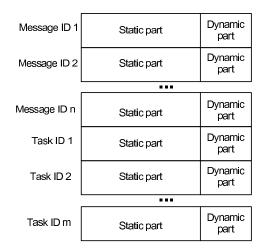

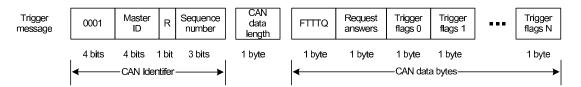

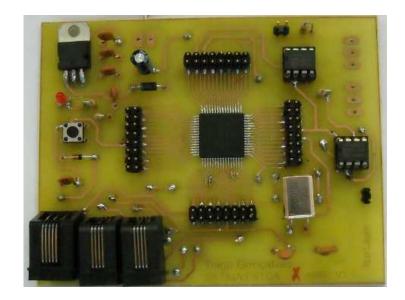

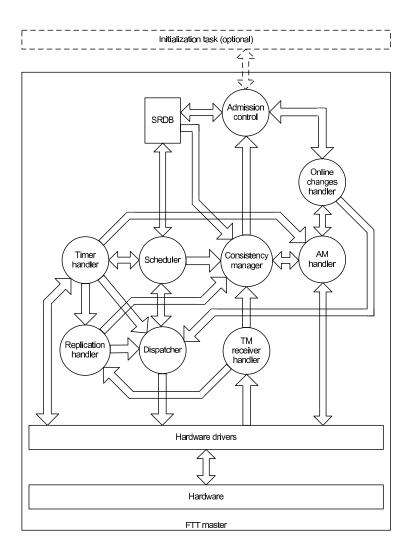

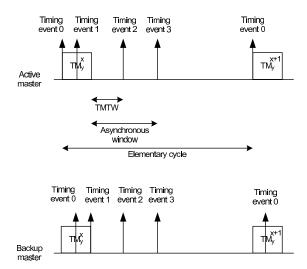

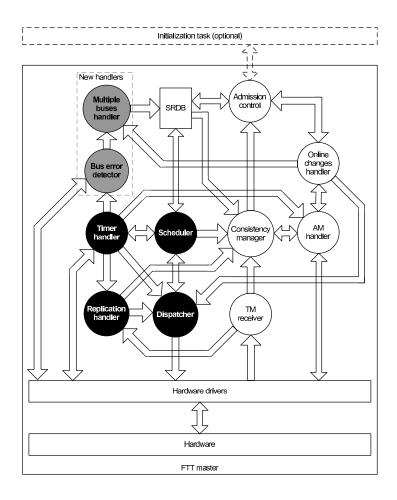

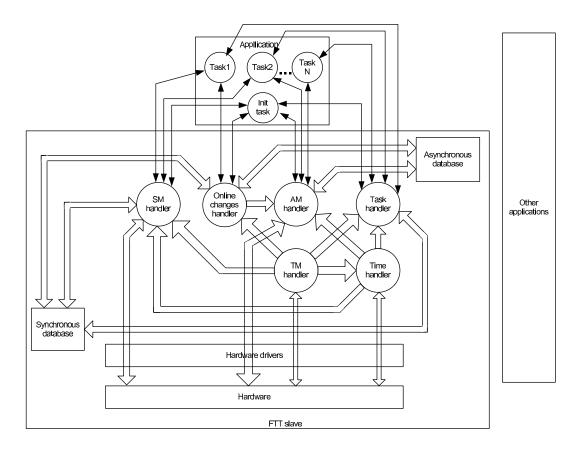

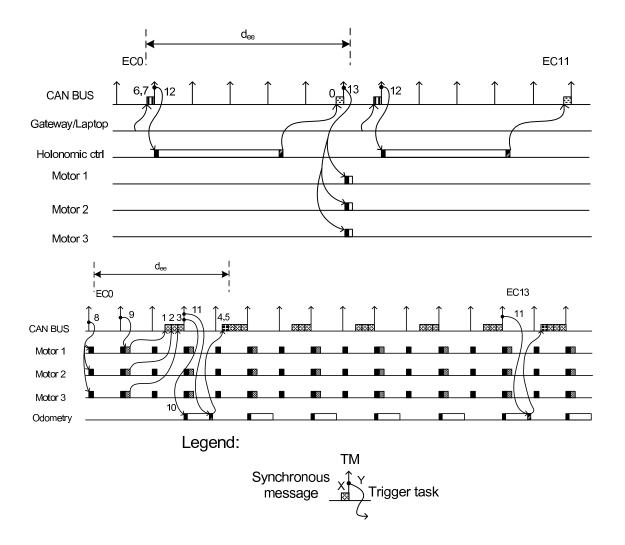

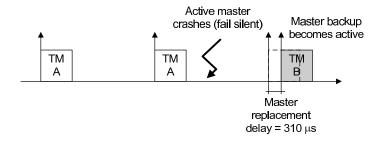

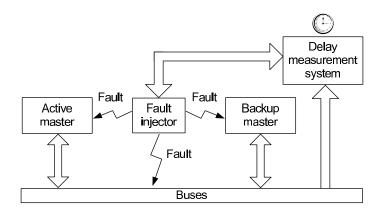

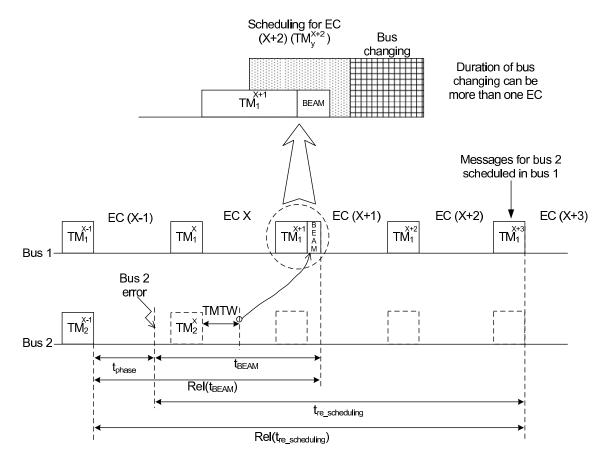

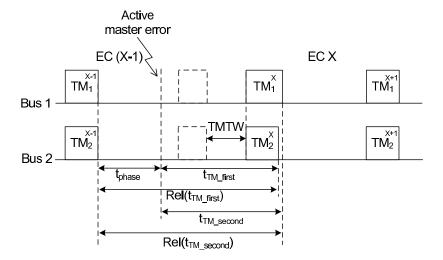

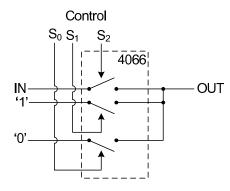

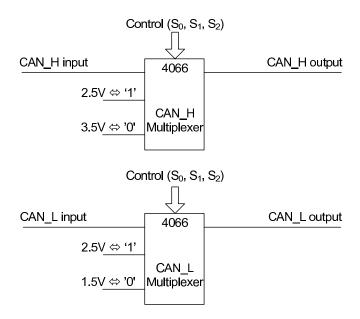

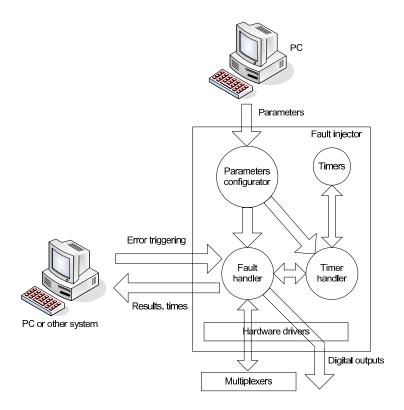

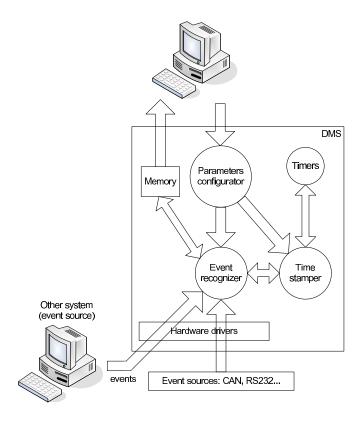

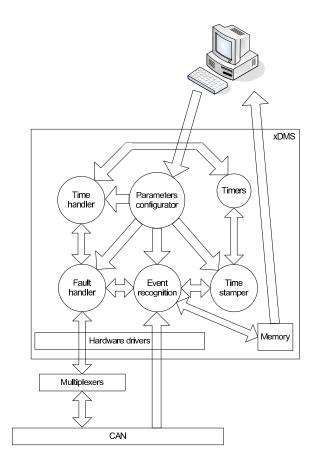

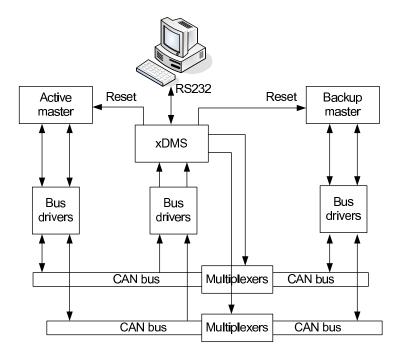

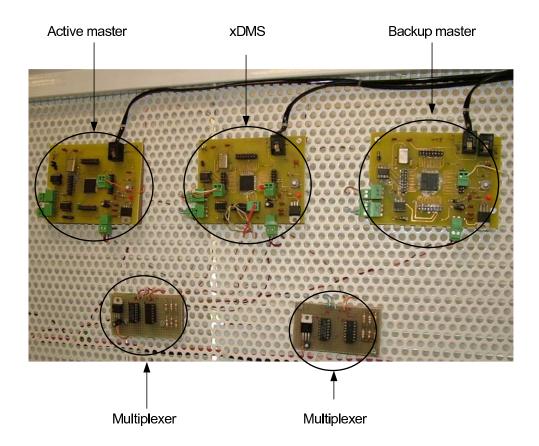

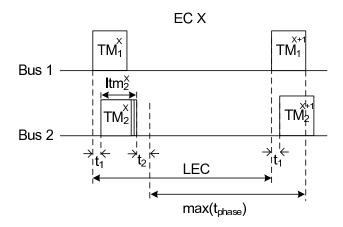

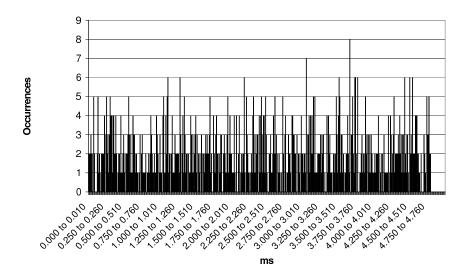

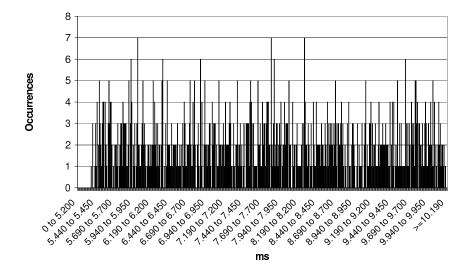

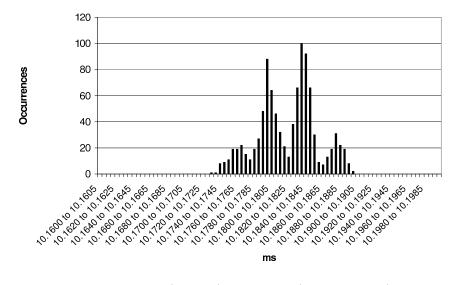

As expected, a full synchronization in every instant is hard to achieve. However, a semi-synchronous approach can be made, where the distributed replicas are not synchronized all the time. There are instants where the replicas are not synchronized. But, after a bounded time interval, all the replicas should maintain a coherent view of the system parameters or data [FNTTJ04].