### BRUNO FIGUEIREDO PIMENTEL

# Síntese de aceleradores baseados em FPGAs implementando algoritmos recursivos

Synthesis of FPGA-based accelerators implementing recursive algorithms

### BRUNO FIGUEIREDO PIMENTEL

# Síntese de aceleradores baseados em FPGAs implementando algoritmos recursivos

Synthesis of FPGA-based accelerators implementing recursive algorithms

dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Doutorado em Engenharia Informática, realizada sob a orientação científica do Dr. Valeri Skliarov, Professor Catedrático do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro, e co-orientação da Dr.ª Iouliia Skliarova, Professora Auxiliar do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro

Apoio financeiro da FCT e do FSE no âmbito do III Quadro Comunitário de Apoio.

### o júri

presidente

Prof. Dr. Paulo Jorge de Melo Matias Faria de Vila Real professor catedrático da Universidade de Aveiro

Prof. Dr. António Manuel de Brito Ferrari Almeida professor catedrático da Universidade de Aveiro

Prof. Dr. Valeri Skliarov professor catedrático da Universidade de Aveiro (orientador)

Prof. Dr. Horácio Cláudio de Campos Neto professor associado do Instituto Superior Técnico da Universidade Técnica de Lisboa

Prof. Dr. Henrique Manuel Dinis Santos professor associado da Universidade do Minho

Prof.<sup>a</sup> Dr.<sup>a</sup> Iouliia Skliarova professora auxiliar da Universidade de Aveiro (co-orientadora)

### agradecimentos

Chegado ao fim desta importante etapa, quero expressar o meu agradecimento:

Ao Prof. Dr. Valeri Skliarov e à Prof.<sup>a</sup> Dr.<sup>a</sup> Iouliia Skliarova, pela sábia orientação, pelo dedicado contributo para este trabalho e pela querida amizade que deles recebi ao longo deste período;

Ao Prof. Dr. António de Brito Ferrari e ao Prof. Dr. António Rui Borges, pelas palavras amigas e de grande motivação que me foram dirigindo durante este trabalho:

Ao Prof. Dr. Rui Tomaz Valadas e ao Prof. Dr. Luís Seabra Lopes, pela simpatia demonstrada, nomeadamente com a escrita das cartas de referência;

À Prof.<sup>a</sup> Dr.<sup>a</sup> Ana Maria Tomé e ao Prof. Dr. Rui Manuel Escadas, pelo interesse demonstrado pelo andamento deste trabalho e pelas palavras amigas que me dirigiram em várias ocasiões;

À Fundação para a Ciência e a Tecnologia por todo o apoio financeiro no âmbito da Bolsa de Doutoramento que me concedeu;

Aos membros de diferentes órgãos da Universidade de Aveiro e ao Instituto de Engenharia Electrotécnica e Telemática de Aveiro pelas boas condições que me proporcionaram;

Ao meu pai, pelos importantes conselhos orientadores que me deu desde muito cedo;

À minha família, em particular à minha mãe, ao meu irmão César, à Ana, ao Alexandre e à Helena, por todo um confortante suporte familiar que me deram;

Ao meu amigo Aneesh Chauhan e ao meu irmão César, pelo companheirismo e pelas inúmeras e produtivas trocas de ideias;

Ao meu colega e amigo Manuel Almeida, pela saudável cooperação e companheirismo que tornaram confortável o laboratório que partilhámos.

### palavras-chave

FPGA, algoritmos recursivos, computação reconfigurável, desenvolvimento de sistemas computacionais

#### resumo

O desenvolvimento de sistemas computacionais é um processo complexo, com múltiplas etapas, que requer uma análise profunda do problema, levando em consideração as limitações e os requisitos aplicáveis. Tal tarefa envolve a exploração de técnicas alternativas e de algoritmos computacionais para optimizar o sistema e satisfazer os requisitos estabelecidos. Neste contexto, uma das mais importantes etapas é a análise e implementação de algoritmos computacionais.

Enormes avanços tecnológicos no âmbito das FPGAs (*Field-Programmable Gate Arrays*) tornaram possível o desenvolvimento de sistemas de engenharia extremamente complexos. Contudo, o número de transístores disponíveis por *chip* está a crescer mais rapidamente do que a capacidade que temos para desenvolver sistemas que tirem proveito desse crescimento. Esta limitação já bem conhecida, antes de se revelar com FPGAs, já se verificava com ASICs (*Application-Specific Integrated Circuits*) e tem vindo a aumentar continuamente.

O desenvolvimento de sistemas com base em FPGAs de alta capacidade envolve uma grande variedade de ferramentas, incluindo métodos para a implementação eficiente de algoritmos computacionais. Esta tese pretende proporcionar uma contribuição nesta área, tirando partido da reutilização, do aumento do nível de abstracção e de especificações algorítmicas mais automatizadas e claras. Mais especificamente, é apresentado um estudo que foi levado a cabo no sentido de obter critérios relativos à implementação em hardware de algoritmos recursivos versus iterativos. Depois de serem apresentadas algumas das estratégias para implementar recursividade em hardware mais significativas, descreve-se, em pormenor, um conjunto de algoritmos para resolver problemas de pesquisa combinatória (considerados enquanto exemplos de aplicação). Versões recursivas e iterativas destes algoritmos foram implementados e testados em FPGA. Com base nos resultados obtidos, é feita uma cuidada análise comparativa. Novas ferramentas e técnicas de investigação que foram desenvolvidas no âmbito desta tese são também discutidas e demonstradas.

### keywords

FPGA, recursive algorithms, reconfigurable computing, design of computational systems

#### abstract

Design of computational systems is a complex multistage process which requires a deep analysis of the problem, taking into account relevant limitations and constraints as well as software/hardware co-design. Such task involves exploring competitive techniques and computational algorithms, enabling the system to be optimized while satisfying given requirements. In this context, one of the most important stages is analysis and implementation of computational algorithms.

Tremendous progress in the scope of FPGA (Field-Programmable Gate Array) technology has made it possible to design very complicated engineering systems. However, the number of available transistors grows faster than the ability to meaningfully design with them. This situation is a well known design productivity gap, which was inherited by FPGA from ASIC (Application-Specific Integrated Circuit) and which is increasing continuously.

Developing engineering systems on the basis of high capacity FPGAs involves a wide variety of design tools, including methods for efficient implementation of computational algorithms. The thesis is intended to provide a contribution in this area by aiming at reuse, high level abstraction, automation, and clearness of algorithmic specifications. More specifically, it presents research studies which have been carried out in order to obtain criteria regarding implementation of recursive vs. iterative algorithms in hardware. After describing some of the most relevant strategies for implementing recursion in hardware, a selection of algorithms for solving combinatorial search problems (considered as application examples) are also described in detail. Iterative and recursive versions of these algorithms have been implemented and tested in FPGA. Taking into consideration the results obtained, a careful comparative analysis is given.

New research-oriented tools and techniques for hardware design which have been developed in the scope of this thesis are also discussed and demonstrated.

# **Index of Contents**

| 1. | Introduction                                             | 1    |

|----|----------------------------------------------------------|------|

|    | 1.1. Motivation                                          | 2    |

|    | 1.2. Design prototyping                                  | 13   |

|    | 1.3. Main objectives                                     | 15   |

|    | 1.4. Thesis structure                                    | 16   |

| 2. | BACKGROUND AND STATE OF THE ART                          | 19   |

|    | 2.1. Background                                          | 19   |

|    | 2.1.1. Recursion                                         | 19   |

|    | 2.1.2. Combinatorial problems                            | 20   |

|    | 2.1.3. Backtracking search algorithms                    | 21   |

|    | 2.2. State of the art                                    | 24   |

|    | 2.2.1. Comparison of recursive and iterative algorithms  | 24   |

|    | 2.2.2. Strategies for implementing recursion in hardware | 25   |

|    | 2.2.2.1. Maruyama, Takagi, and Hoshino                   |      |

|    | 2.2.2. Sklyarov                                          |      |

|    | 2.2.2.3. Ferizis and El Gindy                            |      |

|    | 2.2.2.4. Ninos and Dollas                                | . 29 |

|    | 2.3. Conclusion                                          | 31   |

| 3. | . DESIGN SPACE EXPLORATION                                          | 33         |

|----|---------------------------------------------------------------------|------------|

|    | 3.1. Introduction                                                   | 33         |

|    | 3.2. Backtracking search algorithms                                 | 34         |

|    | 3.2.1. Generic approach to backtracking search algorithms           | . 34       |

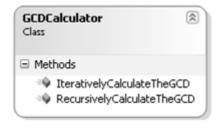

|    | 3.2.2. The set covering problem                                     | . 36       |

|    | 3.2.3. The Boolean satisfiability problem                           | . 41       |

|    | 3.2.4. The graph coloring problem                                   | . 47       |

|    | 3.2.5. The knapsack problem                                         | . 53       |

|    | 3.3. Other selected algorithms                                      | 55         |

|    | 3.3.1. Sorting                                                      |            |

|    | 3.3.2. The greatest common divisor                                  | . 58       |

|    | 3.4. Conclusion                                                     | 58         |

|    |                                                                     |            |

| 4. | SOFTWARE/HARDWARE TOOLS FOR PROTOTYPING AND                         | <b>C</b> 4 |

|    | EXPERIMENTS                                                         | 61         |

|    | 4.1. Prototyping system                                             | 61         |

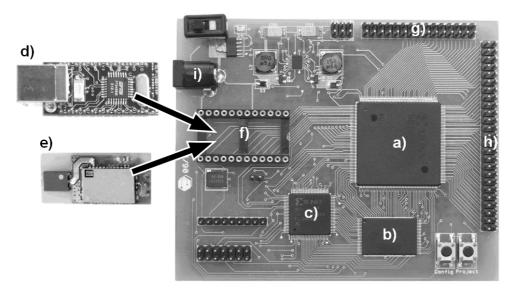

|    | 4.1.1. The DETIUA-S3 FPGA-based prototyping board                   | . 62       |

|    | 4.1.2. The PBM system software for DETIUA-S3                        | . 64       |

|    | 4.1.3. Remote interaction                                           | . 66       |

|    | 4.1.4. Hardware/software co-simulation                              | . 67       |

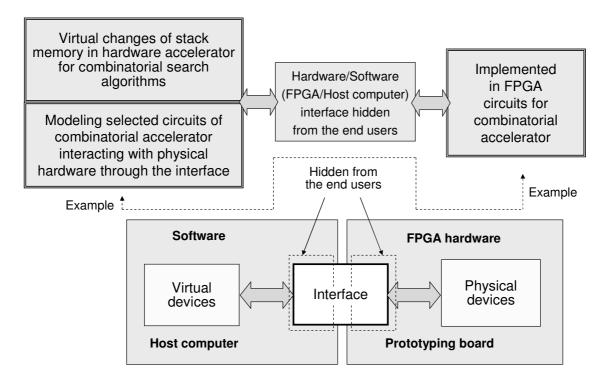

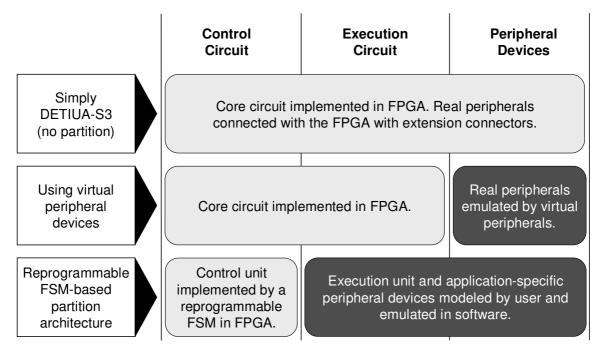

|    | 4.1.4.1. Interaction with virtual peripheral devices                | . 70       |

|    | 4.1.4.2. Reprogrammable FSM-based architecture                      | . 74       |

|    |                                                                     |            |

|    | 4.2. Advantages and applicability of the designed prototyping tools |            |

|    |                                                                     | 79         |

| 5. ALGORITHM MODELING AND IMPLEMENTATION                                  | 85  |

|---------------------------------------------------------------------------|-----|

| 5.1. Modeling in software                                                 | 86  |

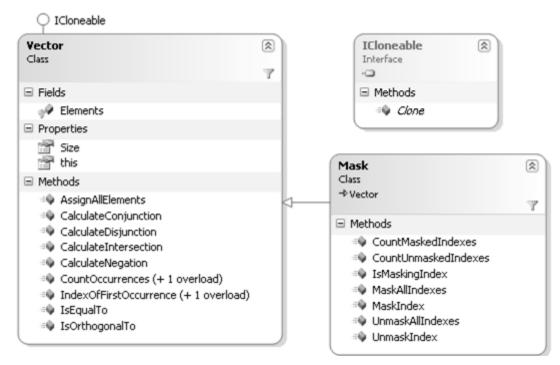

| 5.1.1. Data structures                                                    | 86  |

| 5.1.1.1. Common classes                                                   | 86  |

| 5.1.1.2. Classes for set covering algorithms                              | 90  |

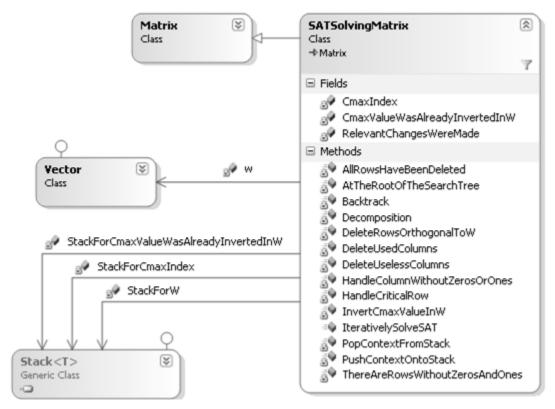

| 5.1.1.3. Classes for SAT solving algorithms                               | 90  |

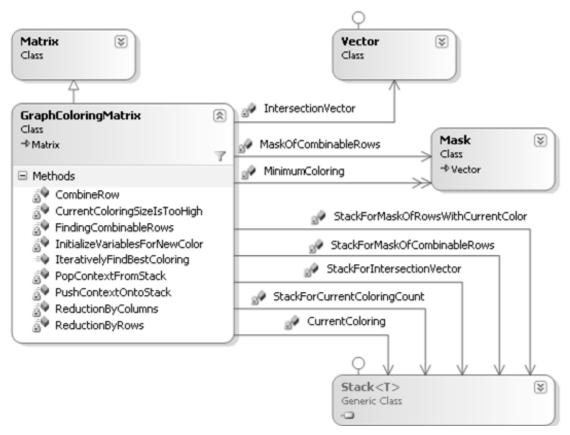

| 5.1.1.4. Classes for graph coloring algorithms                            | 91  |

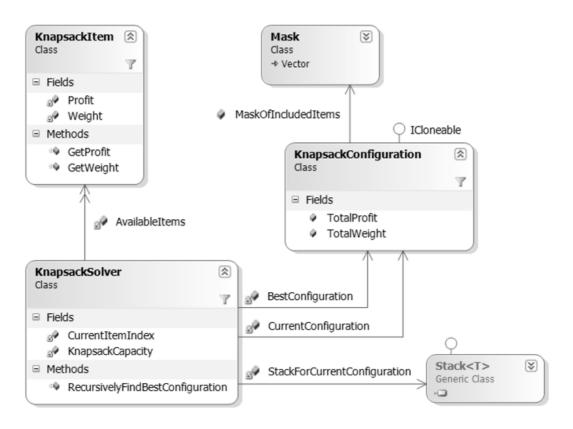

| 5.1.1.5. Classes for solving the knapsack problem                         | 93  |

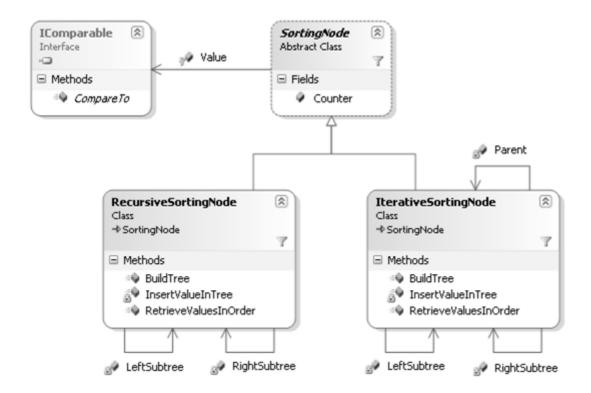

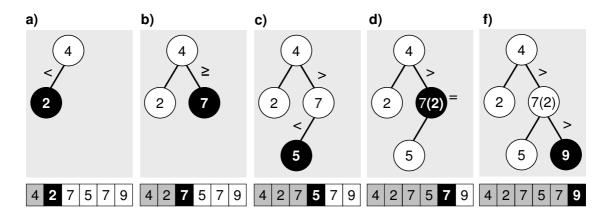

| 5.1.1.6. Classes for tree-based sorting algorithms                        | 94  |

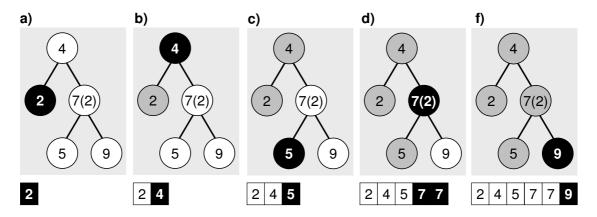

| 5.1.1.7. Classes for calculating the greatest common divisor              | 96  |

| 5.1.2. Algorithmic flows                                                  | 97  |

| 5.1.2.1. The set covering algorithm                                       | 97  |

| 5.1.2.2. The SAT solving algorithm                                        | 99  |

| 5.1.2.3. The graph coloring algorithm                                     | 102 |

| 5.1.2.4. The algorithm for solving the knapsack problem                   | 104 |

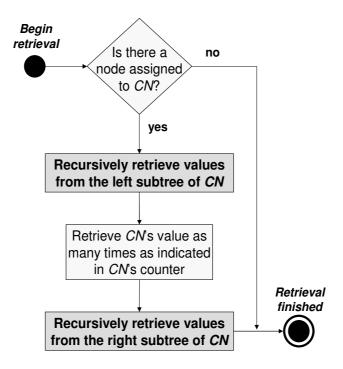

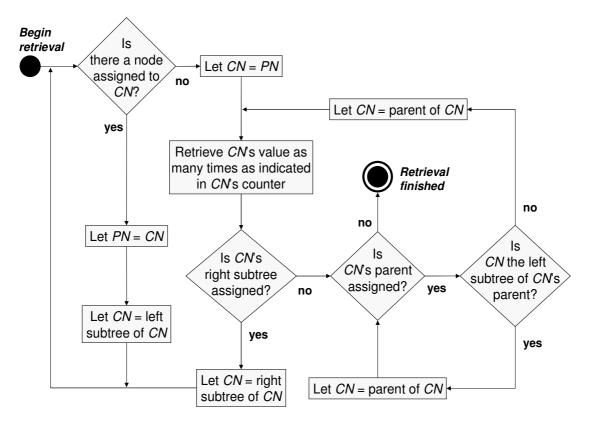

| 5.1.2.5. The tree-based sorting algorithm                                 | 105 |

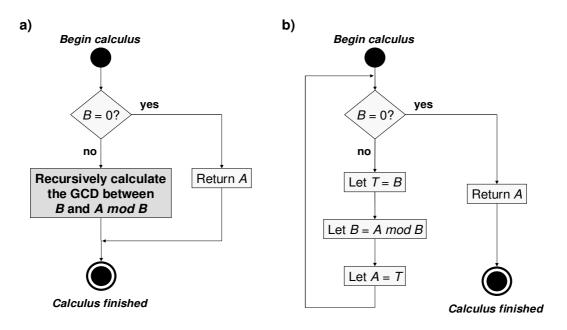

| 5.1.2.6. The algorithm for calculating the GCD                            | 109 |

| 5.2. Implementation in hardware                                           | 109 |

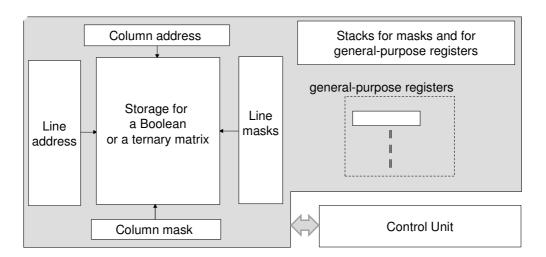

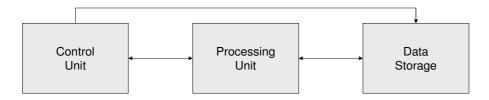

| 5.2.1. Data storage                                                       | 110 |

| 5.2.1.1. Binary vectors and ternary vectors                               | 110 |

| 5.2.1.2. Binary matrices and ternary matrices                             | 111 |

| 5.2.1.3. Supplementary problem-oriented data structures                   | 112 |

| 5.2.2. Control unit                                                       | 114 |

| 5.2.3. Processing unit                                                    | 118 |

| 5.2.3.1. Similarities amongst matrix-based backtracking search algorithms |     |

| 5.2.3.2. Stacks                                                           | 120 |

| 5.2.3.3. Architecture for the processing unit                             | 121 |

| 5.2.4. Proposed architecture for a generic matrix-oriented solver         | 122 |

| 5.3. Validation and implementation of the hardware accelerators           | 125 |

|                                                                           | 407 |

| 6. | EXPERIMENTS, RESULTS, AND ANALYSIS                                                       | 131 |

|----|------------------------------------------------------------------------------------------|-----|

|    | 6.1. Experiments and comparison of iterative and recursive implementations in hardware   | 132 |

|    | 6.1.1. Experiment results                                                                | 134 |

|    | 6.1.2. Result analysis                                                                   | 135 |

|    | 6.1.2.1. Experiments based on hardware description specifications                        | 135 |

|    | 6.1.2.2. Experiments based on system-level specifications                                | 139 |

|    | 6.1.2.3. Summary and further discussion                                                  | 142 |

|    | 6.2. Validation and analysis of the architecture for generic matrix-oriented solvers     | 143 |

|    | 6.3. Assessment of the developed prototyping tools and summary of potential applications | 147 |

|    | 6.4. Conclusion                                                                          | 148 |

|    |                                                                                          |     |

| 7. | CONCLUSION                                                                               | 153 |

|    | 7.1. Contributions                                                                       | 153 |

|    | 7.2. Future work                                                                         | 158 |

| Re | FERENCES                                                                                 | 159 |

# **Index of Figures**

| Figure 1.1 – SOC reconfigurability from 2007 to 2022                                                 |

|------------------------------------------------------------------------------------------------------|

| Figure 1.2 – FPGA usage in industry                                                                  |

| Figure 1.3 - Typical FPGA design flow                                                                |

| Figure 1.4 - Comparison of specification methods (from [Sklyarov07b])                                |

| Figure 2.1 - Recursive definitions for procedures (a) and data types (b)20                           |

| Figure 2.2 – Traversed part of the search tree for solving the four queens problem23                 |

| Figure 2.3 - Queen placements represented by the 4-tuples in Figure 2.223                            |

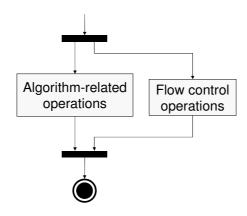

| Figure 2.4 - Parallel execution of algorithm-related and flow control operations27                   |

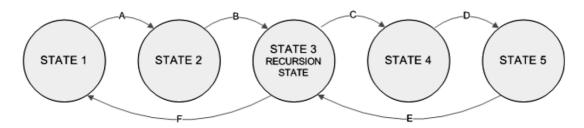

| Figure 2.5 – An originally recursive state diagram after recursion simplification (from [Ninos08])30 |

| Figure 3.1 - Pseudocode for calculating the factorial iteratively (a) and recursively (b)34          |

| Figure 3.2 - Basic structure for backtracking search algorithms34                                    |

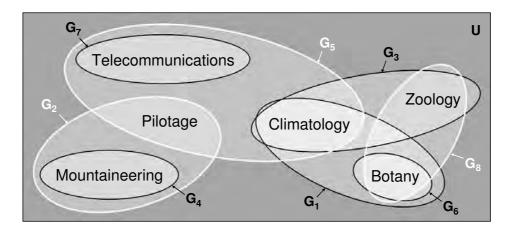

| Figure 3.3 - Practical example diagram for the set covering problem36                                |

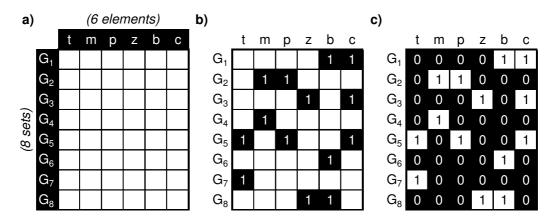

| Figure 3.4 - Converting a set covering problem instance to a binary matrix37                         |

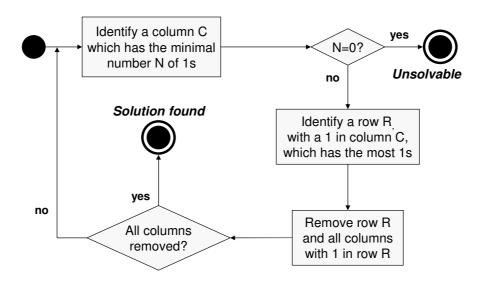

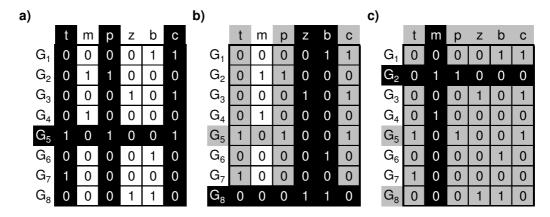

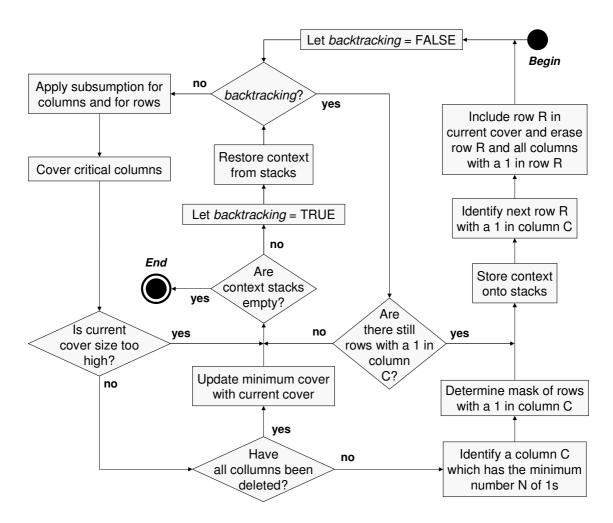

| Figure 3.5 - Iterative approximate algorithm to solve the matrix covering problem38                  |

| Figure 3.6 - Solving a set covering problem instance                                                 |

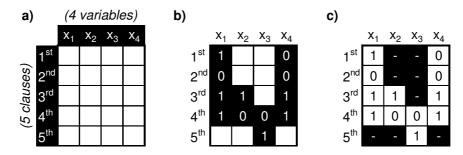

| Figure 3.7  | - Converting a Boolean formula to a ternary matrix                                          | 42 |

|-------------|---------------------------------------------------------------------------------------------|----|

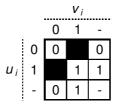

| Figure 3.8  | - Determining the i <sup>th</sup> element of the intersection of ternary vectors u and v    | 43 |

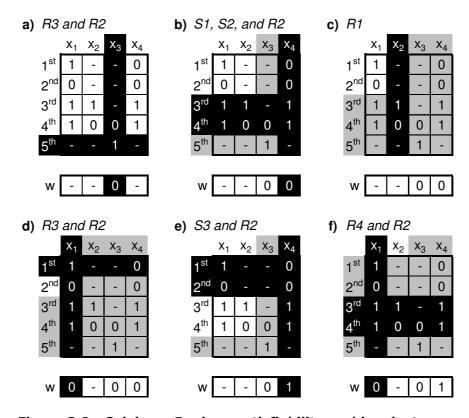

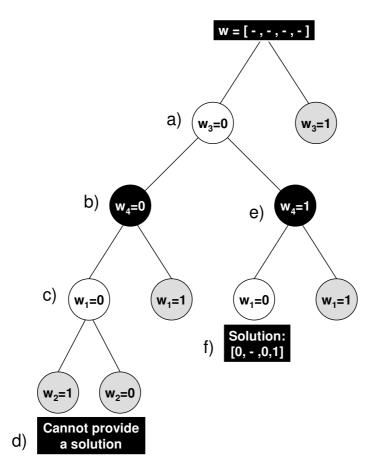

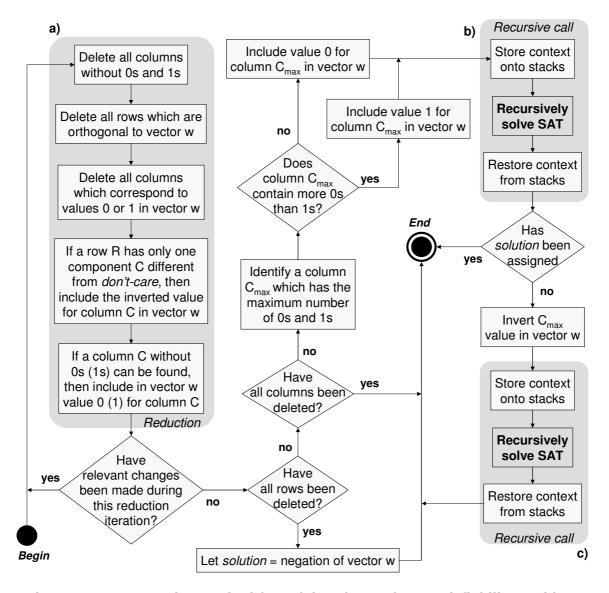

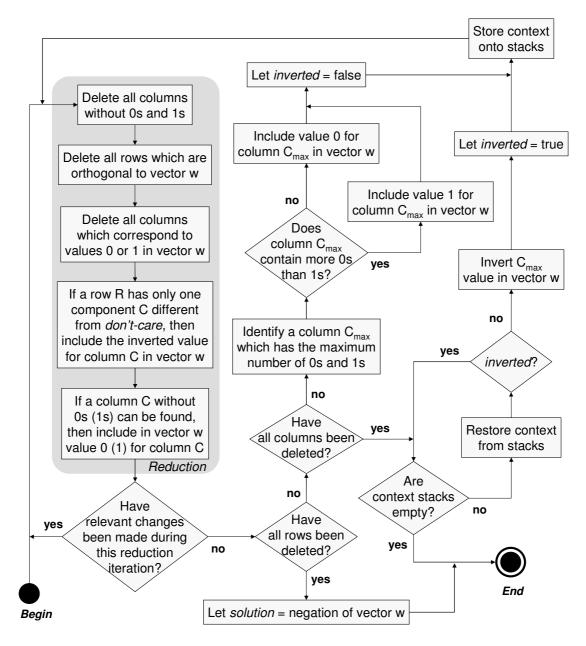

| Figure 3.9  | - Solving a Boolean satisfiability problem instance                                         | 45 |

| Figure 3.10 | – Search tree for the SAT problem example                                                   | 46 |

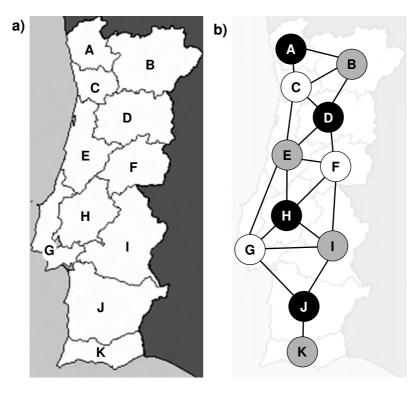

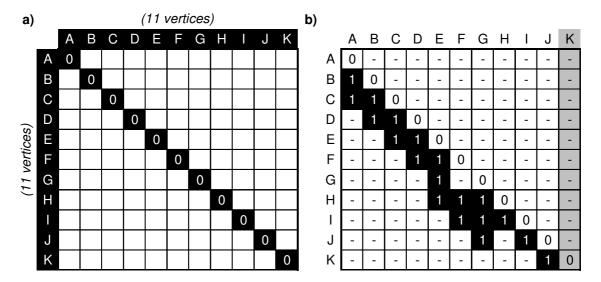

| Figure 3.11 | - Portugal's historical province map (a) and the corresponding province adjacency graph (b) | 48 |

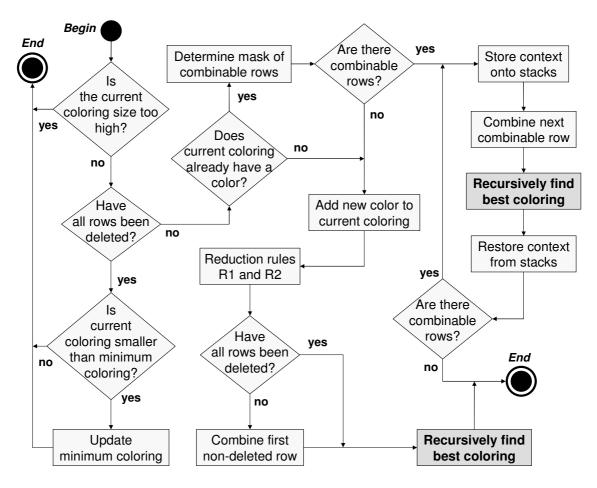

| Figure 3.12 | 2 - Converting a graph coloring problem instance to a ternary matrix                        | 49 |

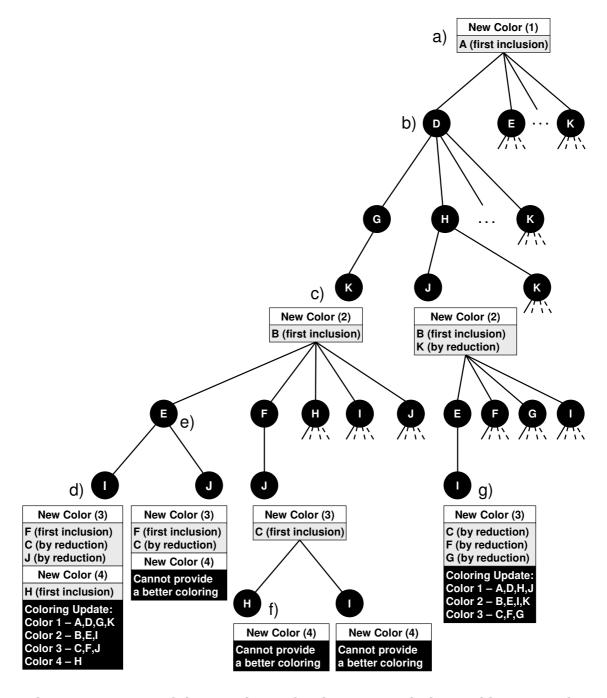

| Figure 3.13 | Part of the search tree for the vertex coloring problem     example                         | 51 |

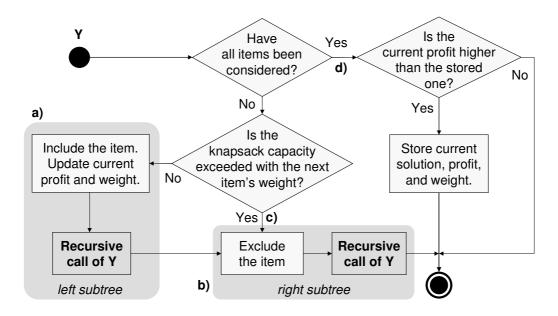

| Figure 3.14 | - Recursive exact algorithm to solve the knapsack problem                                   | 54 |

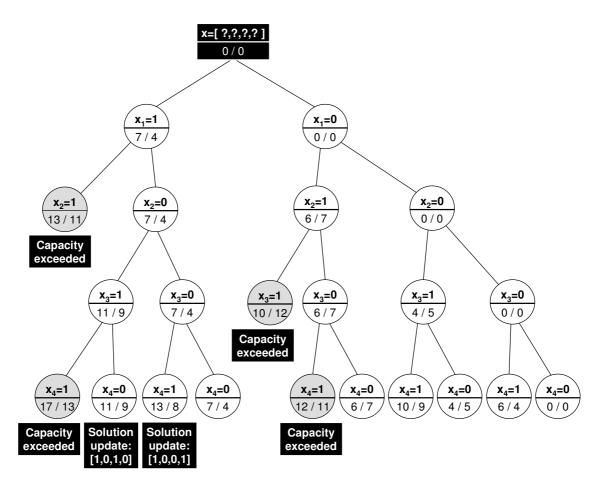

| Figure 3.15 | 5 - Search tree for the knapsack problem example                                            | 55 |

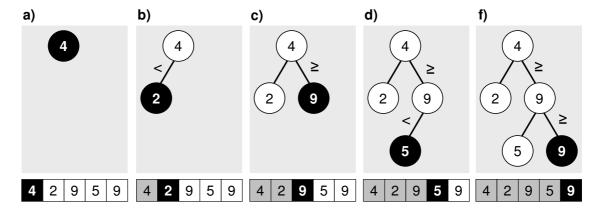

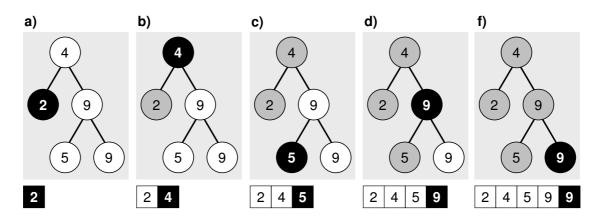

| Figure 3.16 | 5 - Constructing an ordered binary tree                                                     | 57 |

| Figure 3.17 | ' - Retrieving ordered binary tree nodes                                                    | 57 |

| Figure 3.18 | B - Pseudocode for calculating the GCD of two integers iteratively (a) and recursively (b)  | 58 |

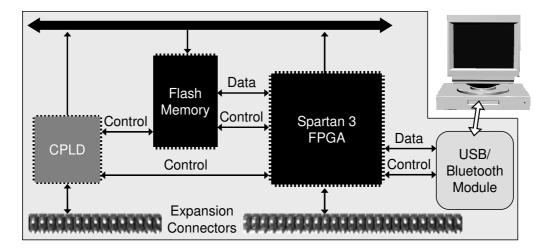

| Figure 4.1  | - The DETIUA-S3 board with interface module alternatives                                    | 62 |

| Figure 4.2  | - The DETIUA-S3 board basic architecture                                                    | 63 |

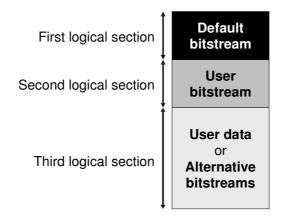

| Figure 4.3  | - Logical division of the flash memory in DETIUA-S3                                         | 64 |

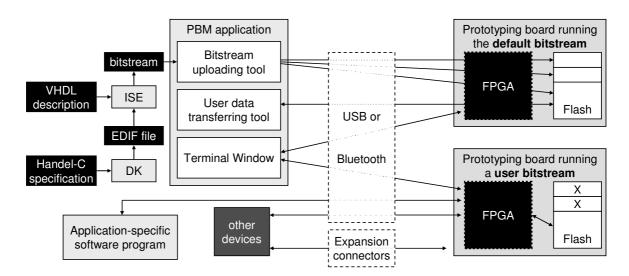

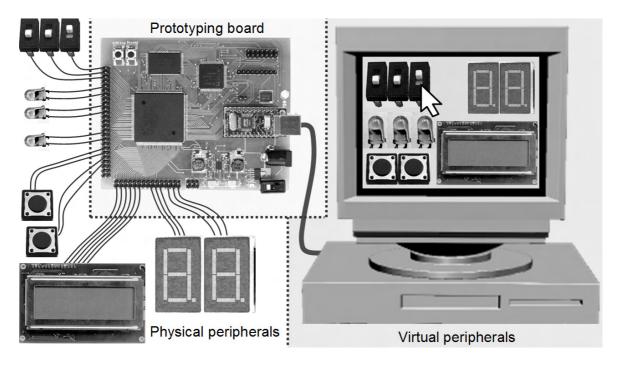

| Figure 4.4  | - Examples of DETIUA-S3 and PBM prototyping capabilities                                    | 65 |

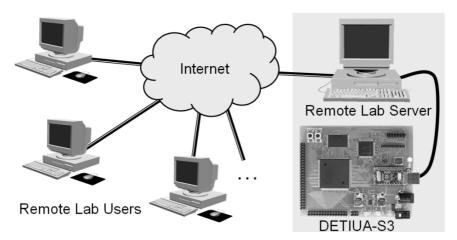

| Figure 4.5  | - Remote access to DETIUA-S3                                                                | 67 |

| Figure 4.6  | – Demonstrating virtual and physical peripheral devices                                     | 69 |

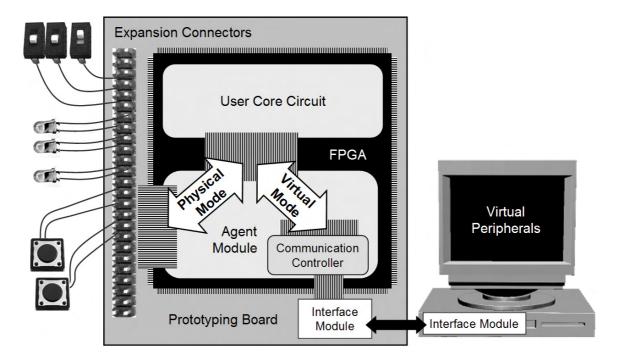

| Figure 4.7  | - Signal routing with the agent module                                                      | 71 |

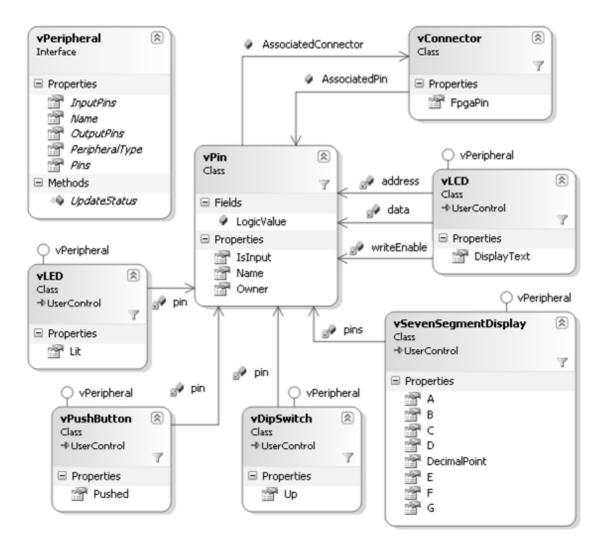

| Figure 4.8  | - Partial class diagram used in the software for running virtual peripheral devices         | 72 |

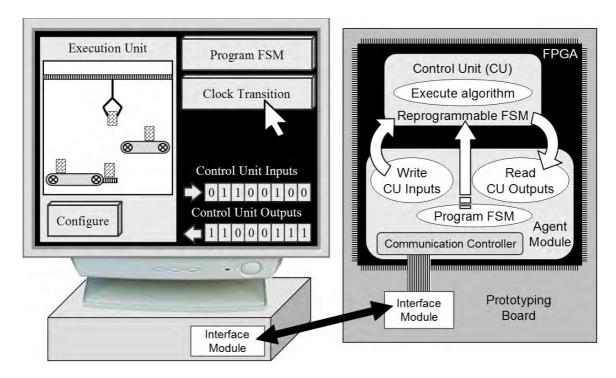

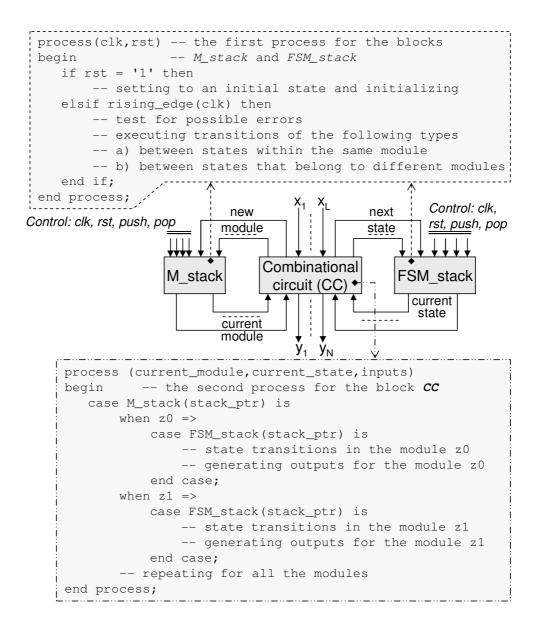

| Figure 4.9  | - Using the proposed reprogrammable FSM-based model                                         | 74 |

| Figure 4.10  | - An example of a hardware template                                         | . 75 |

|--------------|-----------------------------------------------------------------------------|------|

| Figure 4.11  | - Incremental circuit design with the proposed technique                    | .77  |

| Figure 4.12  | - Assembly line scenario                                                    | .78  |

| Figure 4.13  | - Feasible FSM for controlling the assembly line component                  | . 79 |

| Figure 4.14  | - Overview of the virtual visual environment                                | .80  |

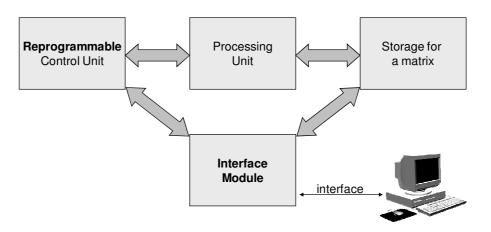

| Figure 4.15  | - Structure of a combinatorial accelerator                                  | .82  |

| Figure 4.16  | - Using different hardware/software co-simulation frameworks                | .84  |

| Figure 5.1 - | Class members of <i>Vector</i> and <i>Mask</i>                              | .87  |

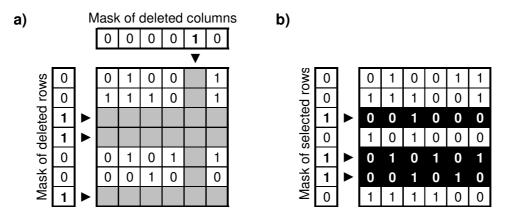

| Figure 5.2 - | Using deletion (a) and selection (b) masks                                  | .88  |

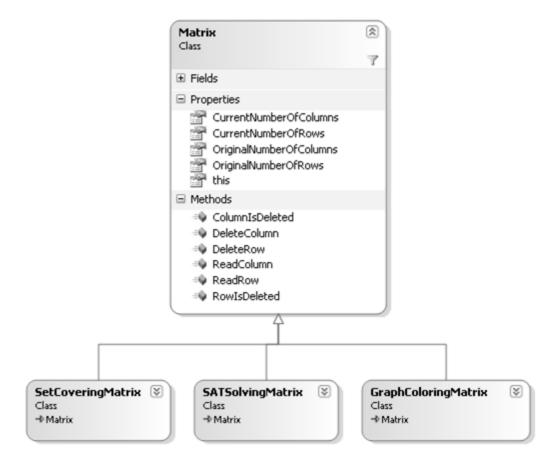

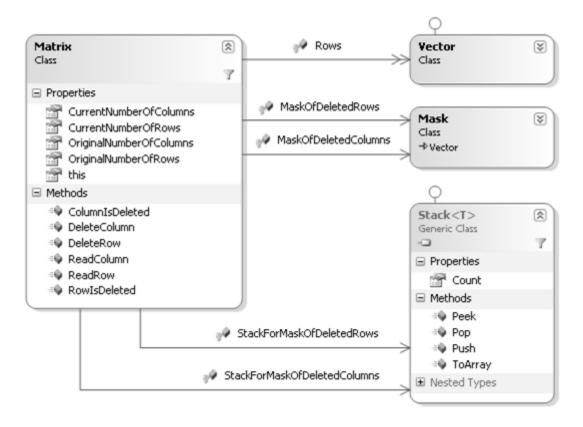

| Figure 5.3 - | Properties, methods, and derived classes of <i>Matrix</i>                   | .88  |

| Figure 5.4 - | Class members of <i>Matrix</i>                                              | .89  |

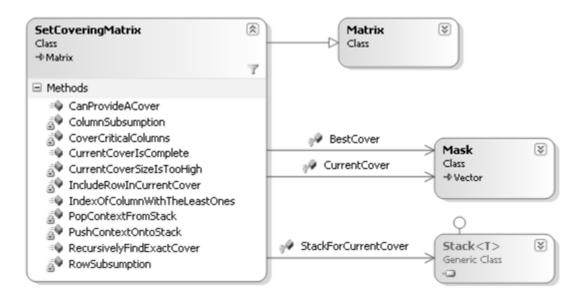

| Figure 5.5 - | Class members of SetCoveringMatrix                                          | .90  |

| Figure 5.6 - | Class members of SATSolvingMatrix                                           | .91  |

| Figure 5.7 - | Class members of GraphColoringMatrix                                        | .92  |

| Figure 5.8 - | Class diagram for knapsack-solving algorithms                               | .93  |

| Figure 5.9 - | Class diagram for iterative and the recursive tree-based sorting            | .94  |

| Figure 5.10  | - Constructing a sorting tree with occurrence accumulation                  | .95  |

| Figure 5.11  | - Retrieving the values of a sorting tree with occurrence accumulation      | . 95 |

| Figure 5.12  | - The <i>GCDCalculator</i> class                                            | .96  |

| Figure 5.13  | - Recursive method for finding an exact cover                               | .97  |

| Figure 5.14  | - Iterative method for finding an exact cover                               | .98  |

| Figure 5.15  | <ul> <li>Recursive method for solving the Boolean satisfiability</li> </ul> | 100  |

| _             | <ul> <li>Iterative method for solving the Boolean satisfiability</li> <li>problem</li> </ul> | 101 |

|---------------|----------------------------------------------------------------------------------------------|-----|

| Figure 5.17 - | - Recursive method for finding an exact vertex coloring                                      | 103 |

| Figure 5.18 - | - Iterative method for finding an exact vertex coloring                                      | 104 |

| _             | - Recursive method for finding the most profitable knapsack configuration                    | 105 |

| Figure 5.20 - | - Recursive method for inserting a value in a sorted tree                                    | 106 |

| Figure 5.21 - | - Iterative method for inserting a value in a sorted tree                                    | 107 |

| Figure 5.22 - | - Recursive method for retrieving tree values                                                | 108 |

| Figure 5.23 - | - Iterative method for retrieving tree values                                                | 108 |

| _             | - Recursive (a) and iterative (b) algorithms for calculating the GCD of two integers A and B | 109 |

| Figure 5.25 - | - General architecture of hardware solvers                                                   | 110 |

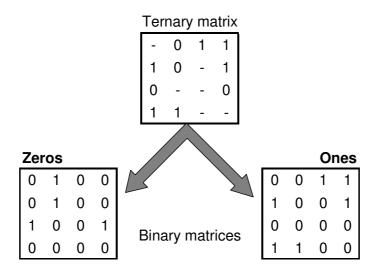

| Figure 5.26 - | - Coding of a 4x4 ternary matrix by two binary matrices                                      | 111 |

| Figure 5.27 - | - Representation of a 4x4 binary matrix in two memory blocks                                 | 111 |

| Figure 5.28 - | - Memory block with sorting tree nodes' data                                                 | 113 |

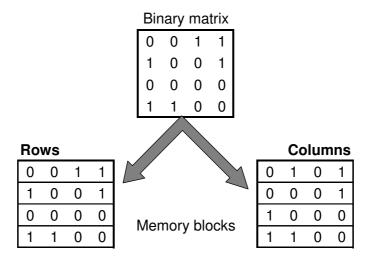

| •             | - Simplified hardware data structures for solving the knapsack problem                       | 113 |

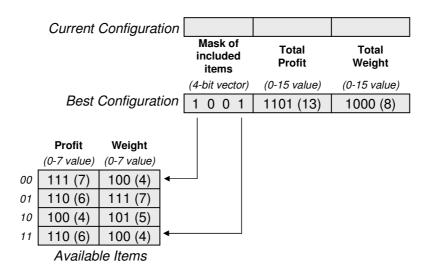

| Figure 5.30 - | - Design template for an FSM and VHDL description                                            | 115 |

| Figure 5.31 - | – Design template for an FSM described in Handel-C                                           | 116 |

| Figure 5.32 - | - Design template for an HFSM and VHDL description                                           | 117 |

| Figure 5.33 - | – Design template for an HFSM described in Handel-C                                          | 118 |

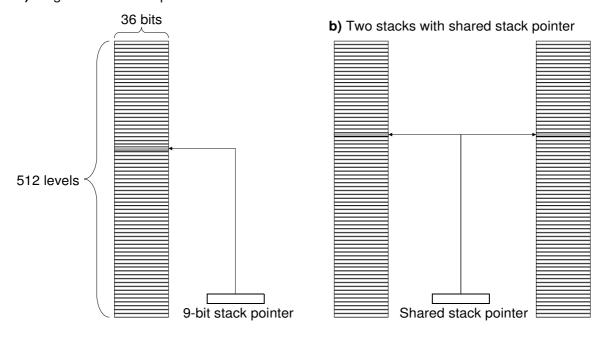

| Figure 5.34 - | - Stacks with dedicated (a) and shared (b) stack pointers                                    | 120 |

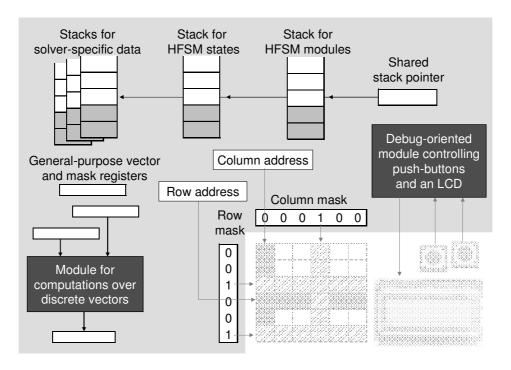

| Figure 5.35 - | - Overview of the processing unit                                                            | 121 |

| Figure 5.36 - | - Proposal for a generic solver architecture                                                 | 123 |

| Figure 5.37  | - Hardware model of a reprogrammable HFSM (from [Sklyarov06c])                            | 124 |

|--------------|-------------------------------------------------------------------------------------------|-----|

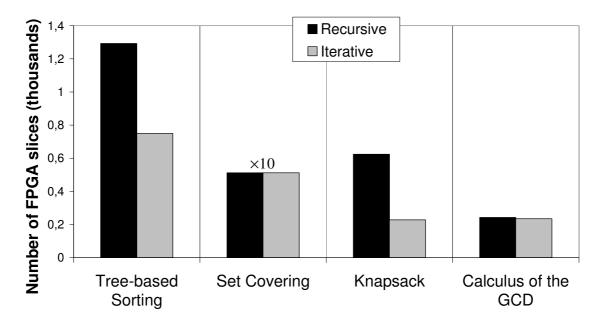

| Figure 6.1 - | Number of FPGA slices occupied by VHDL-based implementations                              | 136 |

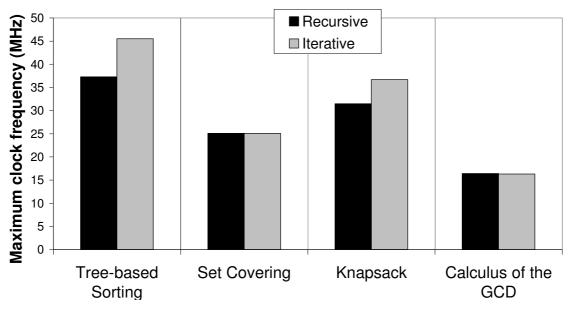

| Figure 6.2 - | Maximum clock frequency allowed on the VHDL-based implementations                         | 137 |

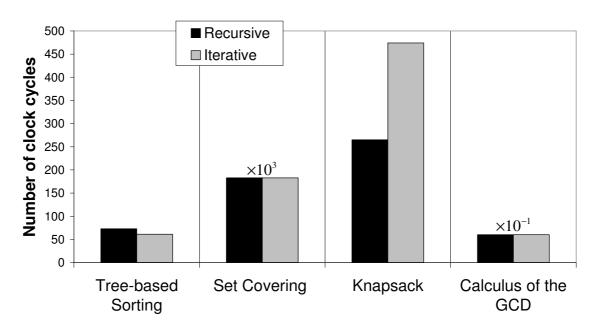

| Figure 6.3 - | Number of clock cycles used for solving the problem on the VHDL-based implementations     | 137 |

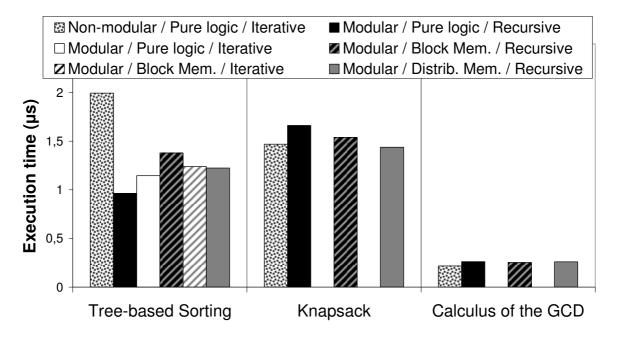

| Figure 6.4 - | Time required by the VHDL-based implementations for solving the problem                   | 138 |

| Figure 6.5 - | Number of FPGA slices occupied by Handel-C-based implementations                          | 139 |

| Figure 6.6 - | Maximum clock frequency allowed on the Handel-C-based implementations                     | 140 |

| Figure 6.7 - | Number of clock cycles used for solving the problem on the Handel-C-based implementations | 141 |

|              | Time required by the Handel-C-based implementations for                                   | 1/1 |

# **Index of Tables**

| Table 1.1 – Details of Xilinx Virtex-6 and Spartan-6 FPGA families                           | 6  |

|----------------------------------------------------------------------------------------------|----|

| Table 4.1 - Sensor and actuator roles in the assembly line scenario                          | 78 |

| Table 5.1 - Representing binary and ternary vectors                                          | 10 |

| Table 5.2 - Number of embedded memory blocks in function of matrix and matrix access types   | 12 |

| Table 5.3 - Languages and CAD tools chosen for design at different abstraction levels        | 26 |

| Table 6.1 – Algorithms implemented in hardware for comparison 1                              | 32 |

| Table 6.2 - Prototyping tools used for algorithm implementation and comparison1              | 33 |

| Table 6.3 - VHDL-based experiment results1                                                   | 34 |

| Table 6.4 - Handel-C-based experiment results1                                               | 35 |

| Table 6.5 - Summary of general criteria achieved with this experiment set 1                  | 42 |

| Table 6.6 - Data structure usage in different matrix-based backtracking search algorithms1   | 44 |

| Table 6.7 - Functional block usage in different matrix-based backtracking search algorithms1 | 46 |

| Table 6.8 - Average execution time in function of task and interface used 1                  | 47 |

# **Glossary of Abbreviations**

ASIC Application-Specific Integrated Circuit

BV Binary Vector

CAD Computer-Aided Design

CLB Configurable Logic Block

CNF Conjunctive Normal Form

CPLD Complex Programmable Logic Device

DABM Dual Access Binary Matrix

DATM Dual Access Ternary Matrix

DSP Digital Signal Processor

EDIF Electronic Design Interchange Format

FPGA Field-Programmable Gate Array

FSM Finite State Machine

GCD Greatest Common Divisor

GPPL General-Purpose Programming Language

HDL Hardware Description Language

HFSM Hierarchical Finite State Machine

HT Hardware Template

IP Intellectual Property

ITRS International Technology Roadmap for Semiconductors

LCD Liquid Crystal Display

LED Light-Emitting Diode

PBM Prototyping Board Manager

PC Personal Computer

RAM Random Access Memory

RHFSM Recursive Hierarchical Finite State Machine

RTL Register Transfer Level

SABM Single Access Binary Matrix

SAT Boolean Satisfiability

SATM Single Access Ternary Matrix

SLSL System-Level Specification Language

SOC System-On-Chip

TCP Transmission Control Protocol

TV Ternary Vector

UML Unified Modeling Language

USB Universal Serial Bus

VEW Virtual Execution Workbench

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLSI Very Large-Scale Integration

**GLOSSARY OF ABBREVIATIONS**

## 1. Introduction

### 1.1. Motivation

Design of computational systems is a complex multistage process which requires a deep analysis of the problem, taking into account relevant limitations and constraints as well as software/hardware co-design strategies. These factors are essential to achieve the required functionality while optimizing the most important system's characteristics (e.g. maximizing the performance or minimizing the needed hardware resources).

The system requirements are the constraints whose satisfaction is to be guaranteed. Typical constraints concern maximum respond time to different requests, maximum power consumption, etc. So long as the requirements are met, the computational system can be optimized in terms of complementary goals, such as minimizing the hardware resources, providing clearness of specifications, simplifying system maintenance, design reuse, opportunities for further updates and improvements, etc. Trade-offs between such system characteristics often take place, and determining the most appropriate choices involves exploring competitive techniques and computational algorithms, which is a process that can be seen as design space exploration. Analysis and implementation of computational algorithms is therefore a very important step to guarantee that the system functions in strong conformity with the given requirements and to achieve a good compromise between mutually-dependable system characteristics.

Algorithmic structure plays a very important role in the development of computational systems and it has direct relationship with important issues, such as: how well the algorithms are organized; how the algorithms are implemented; how clearly the algorithms are described; how different parts of the algorithms can be reused; how easily the algorithms can be modified and improved if required; etc. In case these features are carefully taken into account, it becomes possible to optimize algorithms,

to simplify their implementation, to shorten their development lead time, and to increase their effectiveness.

The thesis is dedicated to the problem of optimizing computational algorithms, and it explores and compares two known alternative ways to implement them, namely recursive and iterative. Additionally, important algorithmic features such as modularity, reusability, clearness, and verifiability are carefully studied.

### 1.1.1. General approach to hardware/software co-design

Hardware/software co-design of a computational system requires an answer to the following general question: Which parts of that system should be implemented in hardware and which parts of it should be implemented in software? In order to answer this question, it is necessary to consider multiple sub-questions, namely: What exactly is software and what exactly is hardware? For instance, software can be considered for general-purpose computers, for application-specific computers, for application-specific microcontrollers, for built-in 'hard/soft' cores such as the FPGA (Field-Programmable Gate Array) Power PC processor [EETimes02] which is built-in to FPGA or the Micro Blaze soft core [Xilinx], etc. Nevertheless, all these types of software have a number of common features, such as sequential processing of machine instructions, and implementation of fundamental concepts like procedure calls, interrupts, etc. Hardware can also be 'hard', like ASICs (Application-Specific Integrated Circuits), and 'soft', like FPGAs. Comparing with software, hardware is significantly more heterogeneous, and it is either difficult or even impossible to indicate a number of common features like for software. The main objective of this thesis is to explore hardware implementation of different algorithms. Due to complexity, not all of them can be realized entirely in hardware, urging software/hardware co-design to be employed. Exploring this topic also constitutes an objective of this thesis.

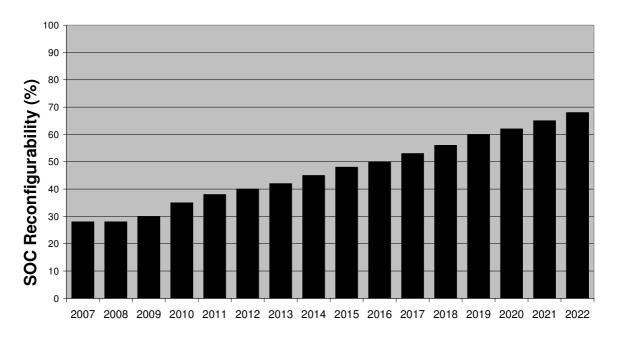

Special attention should be paid to reconfigurable computing. Indeed, the market for FPGAs and other programmable logic devices is expected to grow from \$3.2 billion in 2005 to \$6.7 billion in 2010, according to Gartner Dataquest [EETimes06a]. Figure 1.1 demonstrates the increasing reconfigurability (see percentage in vertical axis) of SOCs (Systems-On-Chip) from 2007 to 2022 [Roadmap07].

Figure 1.1 – SOC reconfigurability from 2007 to 2022

Such increase of SOC reconfigurability is expected because "the growing system complexity will make it impossible to ship designs without errors in the future. Hence, it is essential to be able to fix errors after fabrication" [Roadmap07]. These circumstances lead to extensive on-going research in digital circuit test and diagnosis [Ubar07, Jutman07], as well as in fault detection and fault tolerance strategies [Raik07, Ubar08]. Moreover, the increase of SOC reconfigurability is also due to the fact that "reconfigurability increases reuse, since existing devices can be reprogrammed to fulfill new tasks" [Roadmap07].

Since a forecast of importance of reconfigurable systems in general, and FPGAs in particular, is very promising for the future, this technology is assumed for implementation of computational algorithms in hardware within this work. Particularities of FPGA-based systems are considered in detail in the next subsection.

### 1.1.2. FPGA-based digital systems and reconfigurable computing

Tremendous progress in the scope of FPGA technology has made it possible to evolve configurable microchips from simple gate arrays that appeared on the market in the mid-1980s, to multi-platform FPGAs containing more than 10 million system gates and targeted to the design of very complicated engineering systems. Today, the way to evolve high performance computing from a general-purpose computer, proposed more than 50 years ago [Estrin60], has finally been implemented in reality. As mentioned in

the previous subsection, the market for FPGAs and other programmable logic devices is expected to grow from \$3.2 billion in 2005 to \$6.7 billion in 2010 [EETimes06a].

Developing engineering systems on the basis of high capacity FPGAs involves a large variety of design tools, including methods for efficient implementation of computational algorithms. The thesis is intended to provide significant contribution in this area.

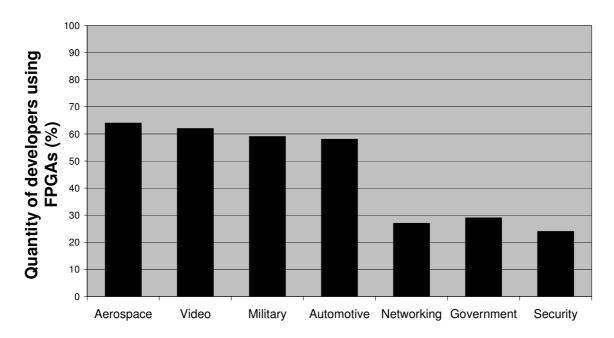

An analysis presented in [D&R06] clearly demonstrates that the largest FPGA consumers will be in engineering, with numerous applications in the scope of electronic system design, from glue logic to high-complexity application-specific (ASIC-type) devices. Pioneering products such as Xilinx's Virtex or Altera's Stratix FPGA families will find their main applications in the development of high-volume products. Figure 1.2 demonstrates how FPGAs have been employed in different industries [Turley05]. Furthermore, Light Reading Inc.'s *Components Insider* conducted a worldwide survey in which 91 industry professionals participated, including equipment-manufacturing engineers, product developers and managers from more than 50 major equipment makers, and "90 percent of survey respondents said their company now uses FPGAs" [EETimes06c].

Figure 1.2 - FPGA usage in industry

In particular, FPGAs have been intensively used in the areas of mobile computing [Sridharanand05, Jung07] and multimedia. For example, Xylon company combines

Xilinx FPGAs of Spartan-3 family with the logicBRICKS IP (Intellectual Property) cores library [Kovacec05], allowing to quickly customize system designs running on generic FPGA development platforms into specialized multimedia products. Xilinx multimedia solutions provide the programmable hardware platforms, design tools, intellectual property, and reference designs which are needed to develop real-time video and image processing systems for a wide diversity of applications, such as video broadcasting and video conferencing, surveillance cameras, medical imaging, home gateway and digital TV [Newswire05].

The Xilinx Virtex-4 programmable technology enables the developers to rapidly implement state-of-the-art DSP (Digital Signal Processor) systems with high performance. Using FPGA-based reconfigurable processors for computation-intensive multimedia functions was considered in [Panainte04], reporting significant reduction in the number of clock cycles. Announced in 2006, Xilinx Virtex-5 FPGAs are a programmable alternative to custom ASIC technology and offer the best solution for addressing the needs of designers in the scope of high-performance logic, DSP, and embedded systems with unprecedented logic, hard/soft microprocessor, and connectivity capabilities [Xilinx06]. Virtex-5 microchips are built upon advanced 65nm triple-oxide technology with speed on average 30 percent higher and with capacity increased 65 percent over previous generation 90nm FPGAs.

The enormous potential of reconfigurable devices that recently appeared on the market for the design of complex systems can be seen from the example of the XC5VLX330 FPGA (Virtex-5 family) [Xilinx06]. This chip contains 25,920 configurable logic blocks (CLBs), 192 DSP slices, 10,368 Kb of block RAM (including 18 Kb and 36 Kb blocks), and 6 devices for advanced clock management. The plenary talk by Mike Butts in FPL'03 (the International Conference on Field-Programmable Logic and Applications, 2003), entitled 'Molecular Electronics: All chips will be reconfigurable', reports that future project densities are likely to be upwards of 100 billion devices per square centimeter and argues that cheap molecular-scale reconfigurable logic, memory, and interconnect are likely to become the predominant digital technology a decade hence. The advances and promising applications of reconfigurable systems given above clearly demonstrate future prospects of FPGA technology and its challenging capabilities for both industrial needs [Salcic06, Aimé07, Du07, Zhuang07] and research activity.

Announced in 2008, Xilinx Virtex-6 and Spartan-6 FPGAs can be seen as one more example demonstrating rapid progress in the scope of reconfigurable computing. Table 1.1 presents some of the characteristics of these two recent FPGA families [Xilinx09].

Table 1.1 - Details of Xilinx Virtex-6 and Spartan-6 FPGA families

| Feature              | Virtex-6         | Spartan-6       |

|----------------------|------------------|-----------------|

| Logic Cells          | 74,500 – 759,000 | 3,400 – 147,000 |

| Distributed RAM (Kb) | 1,045 – 8,280    | 32 – 1,358      |

| Block RAM (Kb)       | 5,616 – 38,304   | 144 – 4,824     |

| DSP Slices           | 288 – 2,016      | 4 – 182         |

Developing digital systems on the basis of high capacity FPGAs requires the extensive use of computer-aided design (CAD) tools. In fact, the electronic design automation business has profoundly influenced the integrated circuit business and vice versa, *e.g.* in the scope of design methodology, verification, libraries, and intellectual property [MacMillen00]. Traditionally, FPGA-targeted CAD systems support schematic and hardware description language-based design flows involving model-specific tools (such as those for synthesizing finite state machines (FSMs) from graphical specifications) and IP core generators based on parameterization or templates. Recently, commercial CAD tools which allow digital circuits to be synthesized from system-level specification languages (such as Handel-C and SystemC) as well as high-level programming languages (such as C) have appeared on the market. The domain of reconfigurable systems design turns out to be very dynamic and many-sided.

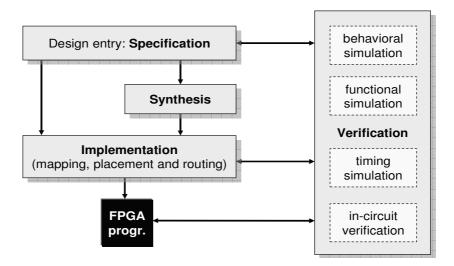

Designers of FPGA-based systems must wade through several layers of design before programming the actual device. The typical FPGA flow includes five major phases illustrated in Figure 1.3: design entry; synthesis; mapping, placement and routing; FPGA programming; and verification. The latter may occur at different levels, such as behavioral simulation, functional simulation, static timing analysis, post-layout timing simulation and, finally, in-circuit verification. If we focus our attention on the design entry, four different specification methods can be envisioned: schematic entry, hardware description languages, system-level specification languages (SLSLs) and, finally, general-purpose programming languages (GPPLs) [Sklyarov07b].

Figure 1.3 - Typical FPGA design flow

The schematic-based approach is nowadays not very appropriate for specifying the functionality of modern systems because, instead of thinking in terms of algorithms and data structures, it forces the designer to deal directly with the hardware components and their interconnections. Contrariwise, the hardware description languages (HDLs), such as VHDL and Verilog, are widely used for design specification since they typically include means for describing structure and functionality at a number of levels, from the most abstract algorithmic level, down to the gate level.

Recently, commercial tools for synthesizing digital circuits from system-level specification languages, such as Handel-C and SystemC, have appeared on the market. In this area, C and C++, with application-specific class libraries and with the addition of inherent parallelism, are emerging as the dominant languages in which system descriptions are provided. This fact allows the designer to work at a very high level of abstraction, virtually without worrying about how the underlying computations are executed. Consequently, even computer engineers with a limited knowledge of the targeted FPGA architecture are capable of rapidly producing functional, algorithmically-optimized designs.

An even higher level of abstraction is achieved with general-purpose programming languages, such as C or Java. During the last years, commercial tools (e.g. Catapult Synthesis from Mentor Graphics and CoDeveloper from Impulse) started appearing on the market, allowing the respective high-level descriptions to be automatically converted to HDL descriptions, which are then used for synthesis. In this case, the code portions that can be executed in parallel are automatically identified by the design tools. In addition to the design specification methods mentioned, there are

other available tools, such as vendor libraries, graphical finite state machine editors, parameterizable IP cores, and so on.

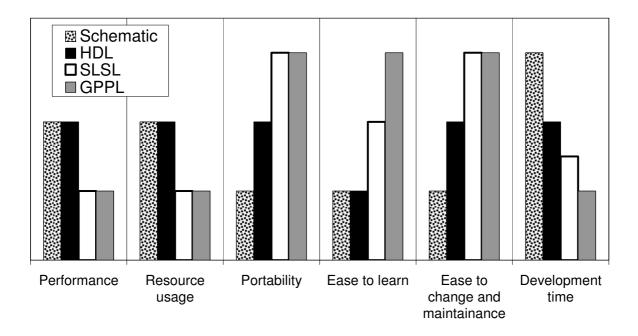

In the graph of Figure 1.4 [Sklyarov07b], different design specification methods are assessed according to performance, FPGA resource usage, portability, ease to learn, ease to change and maintenance, and development time (for the first five groups of vertical bars: the higher, the better; for the last group: the lower, the better).

Figure 1.4 - Comparison of specification methods (from [Sklyarov07b])

From the graph, we can see that the schematic-based approach leads to circuits with very good performance and efficient resource usage. However, when we consider portability and ease to learn, change and maintenance, and the associated development time, schematic entry is an obvious outsider. As mentioned in an Electrical Engineering Times survey, "the days of designing FPGA with schematics are gone" [EETimes06b].

Hardware description languages are currently the golden mean of the design entry methods [Sklyarov07b]. They allow creating high-performance circuits that are optimized from the resource usage point of view, the associated development time is not too long, and design changes are not so difficult. The only weak point is that it's not very easy to learn HDLs.

System-level and high-level languages possess the highest portability and the highest level of abstraction. Of course, the higher level of abstraction leads to some

performance degradation and not very efficient resource usage. On the other hand, SLSLs and GPPLs have important advantages such as ease to learn, ease of change and maintenance, and a very short development time. We can therefore expect that, as the tools responsible for generating hardware from high-level source code advance, the SLSLs and GPPLs may become the predominant hardware description methodology, in the same way as general-purpose high-level programming languages have already supplanted microprocessor assembly languages [Skliarova06a]. Due to such advantages, system-level specification languages and the relevant synthesis tools are considered within this work to be basic instruments for comparing alternative recursive and iterative implementations of computational algorithms.

According to Moore's law [Moore65], chip complexity grows exponentially with time. But more important is that the number of available transistors grows faster than the ability to meaningfully design with them. This situation is a well known design productivity gap, which was inherited by FPGA from ASIC and which is increasing continuously. Therefore, the design productivity will be the real challenge for future systems. It is believed that platform FPGAs could alleviate this problem since they offer the flexibility, time-to-market, and the bandwidth requirements to rapidly bring electronic systems to market. With such highly programmable platforms that include one or more programmable processors and/or reconfigurable logic, derivative designs may be created without fabricating a new system-on-chip (SOC) [Roadmap05]. Platform customization for a particular SOC derivative then becomes a constrained form of design space exploration: the basic communications architecture and platform processor choices are fixed, and the design team is restricted to choosing certain customization parameters and optional IPs from a library [Roadmap05].

In order to increase the design productivity, three important strategic directions must be followed. First of all, design reuse must be encouraged. Reusable, high-level functional blocks (such as IP blocks) offer great potential for productivity gains because design effort for the reused logic is only a portion of the effort needed for newly designed logic. According to International Technology Roadmap for Semiconductors (ITRS), reuse rate for system-level design will increase from 35% in 2007, to 58% in 2022 [Roadmap07].

The second strategic line concerns design abstraction levels, which must be raised. Higher levels of abstraction allow many forms of verification to be performed much earlier in the design process, reducing time-to-market and lowering cost by

discovering problems earlier [Roadmap05]. As previously mentioned, tools which allow for hardware design at a very high level of abstraction are currently emerging.

And last, the third strategic direction is to increase the level of automation and clearness of algorithmic specification, which will inevitably allow the number of design iterations to be reduced. In case of platform-based design, further improvements in automated software/hardware partitioning tools are strongly required.

It is now clear that reconfigurability will certainly be the key aspect of future systems, since it will be required for fault tolerance, *e.g.* for molecular-scale systems, and for development of adaptive and self-correcting or self-repairing circuits. In addition, reconfigurability increases reuse, since existing devices can be reprogrammed to fulfill new tasks. According to what ITRS estimates (see Figure 1.1), more and more SOC functionality will become reconfigurable [Roadmap07].

Another important aspect of SOC design is the exploration of efficient methods for implementation of computational algorithms which allow for clearness of specification, reuse and effectiveness of future implementation. Contributing to this topic is the primary target of the thesis. The following section discusses widely used ways of implementing computational algorithms.

### 1.1.3. Recursive implementation of computational algorithms

It is known that recursion is an extremely powerful problem-solving technique [Carrano95] that permits a problem to be decomposed into smaller sub-problems that are of exactly the same form as the original problem.

Many examples that demonstrate advantages of recursion are presented in [Kernighan88, Carrano95, Maruyama99, Sklyarov04]. However this technique is not always appropriate, particularly when a clear efficient iterative solution exists [Carrano95, Sklyarov04]. This fact is primarily due to the large amount of states that are accumulated during deep recursive calls. Besides, in most high-level programming languages, a function call incurs a bookkeeping overhead. Recursive functions magnify this overhead because a single initial call to the function might generate a large number of recursive invocations of the function.

The paper [Sklyarov04] provides significant contribution to solve this problem and proves that recursion can be implemented in hardware more efficiently than in

software. This achievement resulted from combining any activation of a recursive subsequence of operations with the execution of the operations that are required by the respective algorithm. The same combination takes place when any recursive subsequence is being terminated, *i.e.* when control has to be returned to the point after the last recursive call, and the following operation of the executing algorithm has to be activated.

The number of states that are required for the execution of recursion in hardware can be made smaller than in software, but it is still greater than for iterative solutions. However, codes for such states are accumulated on stacks that are typically implemented on built-in memory blocks, which are very regular and relatively cheap. The results obtained for some known methods for implementing recursive calls in hardware, such as a technique based on multi-thread and speculative execution [Maruyama99], have shown that hardware circuits can be faster than software programs running on general-purpose computers, with respect to this matter. Moreover, it is known that a recursive algorithm can be implemented in hardware with the aid of a hierarchical finite state machine (HFSM) [Sklyarov84, Sklyarov99] and this strategy is explored in this thesis.

Note that recursive algorithms have a wide scope of practical applications (see, for example, [Sklyarov04, Carrano95, Maruyama99]). However, they are most often employed for various kinds of binary search and this is a notable exception, even when implemented in software [Carrano95], because the recursive solutions are quite efficient in this area. There are many examples of recursive binary search and we will briefly discuss just a few of them.

Let us consider a binary tree whose nodes contain four fields, which are: a pointer to the left child node, a pointer to the right child node, a counter, and a value (let us say an integer or a pointer to a string). The nodes are maintained so that, at any considered node, the left sub-tree contains only values that are smaller than the one at the considered node, and the right sub-tree contains only values that are bigger than that. The counter indicates the number of occurrences of the value associated with the respective node. It is known that such a tree can be constructed and used for sorting various types of data [Kernighan88]. In order to build such a tree for a given set of values, we have to find the appropriate place for each incoming node in the current tree. In order to sort the data, we can apply a special technique [Kernighan88] using forward and backtracking propagation steps that are exactly the

same for each node. Thus a recursive procedure is very efficient. Sorting of this type was considered in [Sklyarov04] as a working example.

Other useful applications can be encountered in the area of lossless data compression [Sklyarov04]. Many techniques have been proposed in this context, such as Huffman coding, arithmetic coding, run-length coding, and Lempel-Ziv compression algorithms (see, for example, the Internet site [EFF], which collects many useful publications, methods, and software tools). They combine components for modeling (classified by statistical methods and dictionary methods [Nunez03]) and coding.

Recursive algorithms are quite efficient for such applications and we will show two examples taken from [Sklyarov04]. Huffman coding requires a sequential invocation of two procedures: data sorting, and incremental construction of a Huffman binary tree [Rosen00]. The latter contains information about Huffman codes with different lengths. We have already mentioned that recursive algorithms can be efficiently employed for data sorting. However, they can also be used for constructing a Huffman tree. Moreover, these two procedures can be combined in a single recursive procedure. Dictionary methods often require a content-addressable memory, which is resource-consuming [Nunez03]. On the other hand, searching in dictionaries can be performed using recursive methods that are employed for software applications [Carrano95]. Thus the considered technique can be helpful. This is especially important today because many data compression algorithms need to be implemented in hardware, in general, and in reconfigurable hardware (such as FPGA), in particular [Nunez03]. One potential example of applying recursive algorithms for Huffman coding was examined in [Sklyarov04].

Another important application area that can be addressed is in the scope of combinatorial optimization [Sklyarov04, Skliarova04a, Skliarova08]. Combinatorial search algorithms that are widely used in this area have two distinctive features. Firstly, as a rule they require a huge number of different feasible solutions to be considered. Secondly, these feasible solutions can be ordered and examined with the aid of a search tree that provides an efficient way for handling intermediate solutions. The search tree is constructed during the search process and it is traversed starting from the root. Typically, this is an N-ary tree [Rosen00] with N≥2. Note that a recursive search can also be efficiently applied to N-ary trees and this has been demonstrated in [Sklyarov03b] on an example of discovering a minimal column cover of a binary matrix. A similar approach can be used for solving many other combinatorial problems, such as Boolean satisfiability, graph coloring, etc. Two

examples from this scope which can make use of recursive calls (namely the knapsack and the knight's tour problems) were discussed in [Maruyama99].

Let us note that many combinatorial algorithms deal with a huge amount of data which have to be transferred between a host computer and a hardware accelerator [Skliarova04b]. In many circumstances, due to the complexity, the problem cannot be completely solved in hardware, and combined hardware/software solutions are therefore employed. This is a typical way of hardware/software co-design and it involves multiple time consuming data transfers. Thus recursion can be employed [Sklyarov04] on the one hand for the data compression/decompression operations mentioned above (enabling the amount of data and consequently the data transfer time to be significantly reduced), and on the other hand for the combinatorial algorithms themselves, allowing more efficient solutions for tree search problems to be provided (see, for instance, some assessments in [Maruyama99, Sklyarov03b]).

As already mentioned, FPGA-based systems are going to be used for implementation and evaluation of the considered computational algorithms. Thus, it is necessary to analyze the basic distinctive features of FPGA-based systems and to take advantage of them. The relevant features of such systems are the following:

- Can be seen as 'soft' ASICs;

- Introduce a new computing paradigm;

- Eliminate the necessity for the von Neumann architecture although such architecture can be used if required;

- Enable the designers to implement algorithms directly in silicon;

- Make parallelism a key feature;

- Permit any required interface with external devices to be established.

## 1.2. Design prototyping

There are a number of available prototyping boards that support various experiments with FPGA-based circuits [Xilinx, Celoxica, Trenz]. These boards permit to implement digital systems in FPGAs and to provide for an interaction of these systems with both onboard microchips and external devices (such as static RAM and micro controllers), which might be connected through expansion headers. The use of such boards

significantly simplifies the design of new FPGA-based systems and allows the development lead time to be shortened.

Prototyping boards are widely employed in engineering practice, in research activity, and in education. When choosing an FPGA-based prototyping board, it is necessary to find a compromise between the required hardware/software resources and the price; but with the large number of available boards, it becomes difficult to make the best choice for a particular application. Taking into account that the majority of prototyping boards include many typical components (memories, LCDs, standard interfaces, etc.), it is very difficult to find a board that contains only elements that are required and nothing else, which only occupies the space and increases the cost. Moreover, it is necessary to develop software targeted to the desired experiments, taking into account numerous particularities of the developed algorithms. However, it is either difficult or even impossible to satisfy all the requirements mentioned above due to unavailability of detailed technical documentation and hardware support projects implemented by relevant manufacturers. As a rule, such materials are not supplied.

Thus, an extendable set of hardware/software tools have been proposed. Hardware tools have been developed in [Almeida06, Almeida08], and software tools have been designed and explored within the scope of this research. It is important that any particular problem can be solved using only the subset of hardware/software components that are required (from the considered extendable set), excluding all the other available components. In case the desired components are not available, they can easily be constructed and integrated/attached.

In general, the suggested tools have to provide prioritized support for the following distinctive functionality:

- Configuration of the core FPGA using wired (USB) and wireless (Bluetooth)

interfaces, the latter making the prototyping system ideal for remote

applications;

- Dynamic onboard reconfiguration and remote wireless reconfiguration and/or interaction;

- Implementation and comparison of recursive and iterative algorithms in hardware and software/hardware partitioning;

- Versatile, efficient, user-friendly workflows (by integration with other CAD tools)

for system design on the basis of hardware description languages (VHDL in

particular), system-level specification languages (Handel-C in particular), templates, design libraries and IP cores.

### 1.3. Main objectives

The three main objectives of this research are the following:

- 1. Implementation of recursive algorithms in reconfigurable hardware and comparison of recursive and iterative implementations. Analysis of the design space where recursive/iterative algorithms are more advantageous taking into account the design objectives and target requirements;

- **2.** Exploration of a reuse technique, in hardware design, on the basis of parameterizable, reprogrammable architecture and generic IP modules;

- **3.** Development of software tools for hardware/software co-design and co-simulation of FPGA-based reconfigurable prototyping systems.

In order to pursue the first main objective, it is necessary to address the following tasks:

- Answering the question: How to implement recursion in hardware? Note that known hardware and system-level specification languages do not provide support for implementing recursion;

- Exploring hardware architectures enabling recursive algorithms to be implemented in hardware;

- Designing system components, such as IP modules, which support the development of hardware from recursive specifications;

- Considering particular design examples allowing to compare alternative recursive and iterative algorithms;

- Experiments and comparisons of recursive and iterative algorithms. Determining design space for recursive and iterative algorithms.

To satisfy the second objective it is necessary to address the following tasks:

• Explore the relationship between recursion and modularity in hardware design (indeed, recursion assumes modularity);

- Explore and compare different opportunities for the design of reusable modules;

- Provide a set of experiments and recommendations;

- Analyze a relationship between modularity and dynamic reconfigurability.

To attain the third objective, it is necessary to carry out the following set of tasks:

- Analyze potential ways to explore such type of software/hardware co-design and co-simulation, which enable designers to easily explore digital systems with either more software and less hardware or vice versa;

- Suggest an FPGA-based prototyping system suitable for such purposes;

- Develop software oriented to the comparison and implementation of alternative FPGA-based accelerators;

- Provide a set of experiments based on the developed methods and tools.

### 1.4. Thesis structure

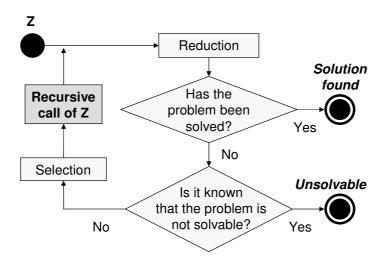

This thesis is organized in seven chapters. Chapter 2 starts with describing background concepts which are essential for understanding the remainder of the thesis (namely recursion, combinatorial problems, and backtracking search algorithms) and then presents the state of the art relevant to the thesis area, addressing known results on the comparison of recursive and iterative algorithms, and strategies for implementing recursion in hardware. The last section of chapter 2 summarizes the main aspects of the background and strategies considered.

Chapter 3 analyzes computationally intensive problems which are taken mainly from the scope of combinatorial search. The latter is relevant because both targeted techniques, *i.e.* recursive and iterative, can rationally be applied. For each of six selected problems, the following is provided: problem description, application domains, an algorithm for solving it, and a detailed illustration in which the given algorithm is applied to solve the problem on the basis of a practical example. Four particular problems are solved with the aid of backtracking search algorithms, namely: set covering, Boolean satisfiability, graph coloring, and knapsack. Two supplementary problems (tree-based data sorting and discovering of a greatest common divisor) are also studied. A generic approach to backtracking search algorithms is described and discussed.

Chapter 4 describes the developed prototyping system and software tools that enable experiments with hardware accelerators and comparisons of alternative recursive and iterative algorithms to be carried out easier and more efficiently. The system is based on the DETIUA-S3 prototyping board, featuring wired and wireless interfaces with a host computer, and on software tools proposed and implemented in the scope of this thesis. These software tools provide user-friendly interface with the board (including wireless interaction) and high-level support for many different experiments which are required for the hardware accelerators considered. Virtual peripheral devices, modules for software/hardware co-simulation, and procedures for extracting intermediate results for analysis are examples of the software tools developed. A more advanced technique assumes the application of the developed tools through the Internet in such a way that allows different users to configure and to interact with the remotely accessed prototyping board. Although this work was not initially planned, many tools have been developed, implemented and tested, permitting to conclude that the proposed system can efficiently be used for remote interactions.

Chapter 5 provides details of reconfigurable hardware implementation of iterative and recursive algorithms for the selected problems. Every algorithm was first modeled in software in order to simplify the design process, and the respective object-oriented classes and activity diagrams are presented. After modeling, some of the algorithms were described in a system-level specification language (Handel-C) and a hardware description language (VHDL). The respective specifications were finally synthesized and implemented in commercially available FPGAs and carefully analyzed.

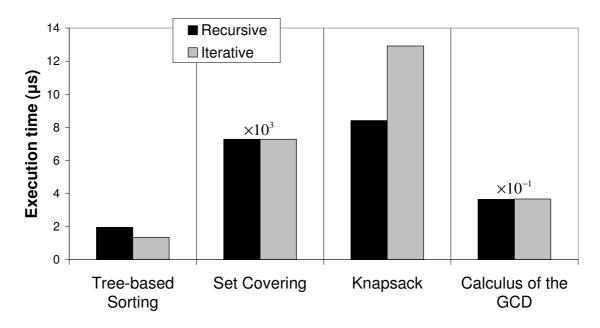

Chapter 6 presents the details and results of the various sets of experiments which were carried out, followed by careful analyses. The first set of experiments addresses the comparison of iterative and recursive implementations in hardware. Results are not only shown in tables with the relevant numerical results but put into perspective by means of graphical charts, allowing for an easier analysis. Relevant remarks beyond the observation of the results are made in order to complement the comparison. The second subsection of this chapter describes the validation and analysis of the architecture for generic matrix-oriented solvers, providing an overview of the key data structure and functional block usage amongst different matrix-based backtracking search algorithms. The third section provides an assessment of the prototyping tools which were developed in the scope of this thesis and a summary of relevant potential applications.

| Chapter 7 summarizes the author's contribution, | lists | the  | most   | important | results | and |

|-------------------------------------------------|-------|------|--------|-----------|---------|-----|

| suggests future work in the considered area.    | 11303 | tiic | 111030 | important | resures | ana |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

|                                                 |       |      |        |           |         |     |

# 2. Background and State of the Art

This chapter is composed of the following three sections: background (section 2.1) which describes recursion, combinatorial problems, and backtracking search algorithms; state of the art relevant to the thesis area (section 2.2), presenting known results in comparison of recursive and iterative algorithms as well as strategies for implementing recursion in hardware; and finally a conclusion (section 2.3).

# 2.1. Background

#### 2.1.1. Recursion

Something is said to be *recursive* if it partially consists or is defined in terms of itself [Wirth86]. Recursion can be applied and observed in many fields and, in problem solving, it is known to be an extremely powerful technique [Carrano95] which permits to decompose a problem into smaller sub-problems that are of the same form as the original problem [Sklyarov04].

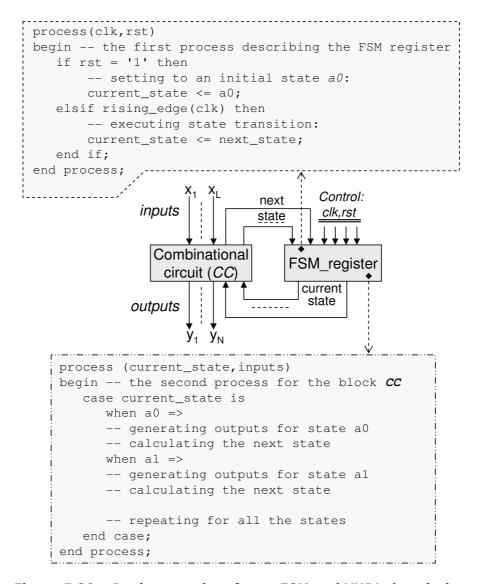

Within the context of algorithm implementation, recursion is mainly used in the definition of procedures (see Figure 2.1-a) and structured data types (Figure 2.1-b). The thesis focuses on the procedure-oriented kind of recursion but, in fact, recursive algorithms are particularly appropriate when the data to be processed and the problem to be solved are defined in recursive terms [Wirth86].

a)

b)

Figure 2.1 - Recursive definitions for procedures (a) and data types (b)

Recursion can be *direct* and *indirect*. A procedure that includes an explicit invocation of itself is said to be *directly recursive* (see Figure 2.1-a). On the other hand, an *indirectly recursive* procedure is one that invokes some other procedure which directly or indirectly invokes the first one. For example, most recursive algorithms developed for solving combinatorial problems are directly recursive. Nonetheless, both kinds of recursion present essentially the same implementation challenges. It should also be noted that, although recursion is often very useful, it has been proven that any recursive algorithm can be re-expressed non-recursively [Kruse87].

In order to illustrate the applicability and advantages of recursive algorithms when they are implemented in hardware for solving computationally intensive problems, we will explore combinatorial search problems as an example. The subsequent two sections present general characteristics of such problems and a technique widely used to solve them.

#### 2.1.2. Combinatorial problems

Combinatorics is a branch of mathematics with increasing importance which can be described as the study of how discrete sets of objects can be arranged, counted, and constructed, according to specified constraints [Cameron94, Erickson96].

Combinatorial search problems are divided in four types, depending on the kind of solution that is required [Kreher99, Skliarova04a]:

- Decision problems, in which a question is to be answered 'yes' or 'no';

- Search problems, in which a question is to be answered 'yes' or 'no' and, in case the answer is 'yes', an n-tuple  $[x_1,...,x_n]$  that verifies the given constraints is to be provided;

- Enumeration problems, in which the number of different n-tuples  $[x_1,...,x_n]$  that verify the given constraints is to be found;

- Optimization problems, in which an n-tuple  $[x_1,...,x_n] \in \{0,1\}^n$  which maximizes the value of a specified profit-evaluating function (or minimizes the value of a specified cost-evaluating function) is to be provided.

A significant characteristic of combinatorial problems is their vast applicability, which is also the reason for their increasing importance. Algorithms for solving such problems are therefore getting a lot of attention today [Zakrevskij08]. Applications of combinatorial problems can be found in Boolean expression simplification [Breuer70]; resource allocation [Rubin73, Walker74, Gleeson94, Rodin90, Bodin91, Henig90]; mathematical logic, artificial intelligence, VLSI engineering, and computing theory [Gu97]; automated reasoning, computer-aided design, computer-aided manufacturing, machine vision, database, robotics, integrated circuit design automation, computer architecture design, embedded systems, and computer network design [Gu97, Goossens97, Subramonian04]; microprogramming for applicationspecific embedded microprocessors and resource distribution [Culberson, Wu93]; cutting stock systems [Gilmore61, Hahn68, Madsen79, Seth87]; cryptography [Merkle78, Chor88, Jan93], broadband communications [Ross89, Gavious94], etc. More detailed application examples of particular combinatorial problems will be considered in chapter 3, when describing the problems which will be used in the scope of this thesis.

# 2.1.3. Backtracking search algorithms

Most algorithms for solving combinatorial problems have a top-down approach based on search trees [Zhang89]. Search trees are typically implemented by means of a backtracking mechanism [Golomb65, Floyd67, Bitner75, Cohen79, Skliarova04a]. In this context, the search consists of a multi-stage decision process in which some choice is made at each stage [Helsgaun95]. At every stage, a solvability test which

takes the earlier choices into account is also performed and, under certain circumstances, such test can determine that some of those choices cannot lead to a solution. If this is the case, the algorithm restores the context belonging to the previous stage, *i.e.* it *backtracks*, in order to make an alternative choice. If all alternative choices based on that context have already been tried, the algorithm backtracks again. The process continues until the whole search tree is traversed or, in case the given problem is not an optimization problem, when a satisfactory solution is found. In either case, algorithms which follow this general strategy are called *backtracking search algorithms*.

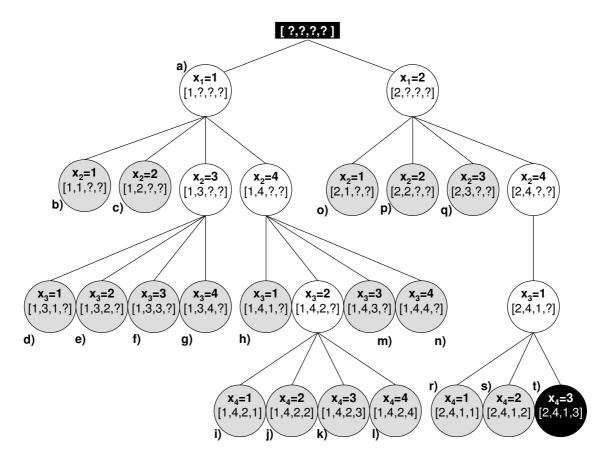

The eight queens problem [Ball60] is a classic combinatorial problem that is very appropriate for illustrating backtracking search algorithms. Let us consider a simplified version which consists of finding a way to place 4 queens in a 4 by 4 chessboard in such a way that no queen is able to attack another. In this problem, there is no distinction between white and black queens. Thus, in order to achieve a solution, no pair of queens can be placed in the same row, column, or diagonal.

In order to solve this problem, Bitner and Reingold chose the following strategy [Bitner75]: Because exactly one queen must be placed in each column, a solution can be represented as a tuple  $[x_1, x_2, x_3, x_4]$  in which  $x_i$  represents the row of the queen placed in the i<sup>th</sup> column. They do not consider all possible combinations of queen placements; only those with one queen in each column. This way, all combinations with more than a queen per column (which are obviously not solutions) are excluded from the beginning.

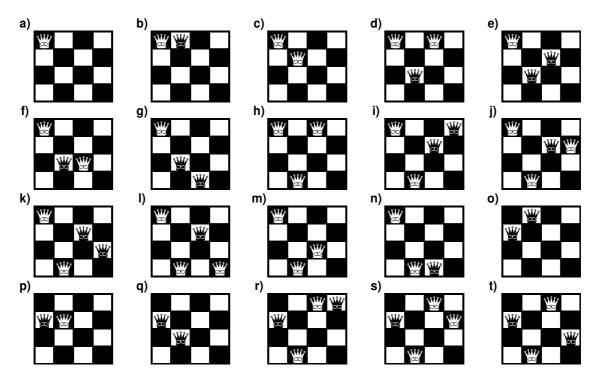

Using this strategy, one can conceive a search process with 4 stages in which the value of  $x_i$  is chosen at stage i. Each choice is made amongst 4 possible values: 1 to 4 (which identify the 4 rows). As a result, a quaternary search tree with a depth of 4 levels is obtained. Figure 2.2 depicts the part of that search tree which is actually traversed by a backtracking search algorithm that would follow this approach. At the root of the search tree, the 4-tuple variable which will provide the solution is completely unassigned. At each level, one of its elements is assigned and hence the variable becomes completely assigned when a leaf is reached. White circles correspond to legal partial queen placements which are therefore explored further. On the other hand, grey circles illustrate partial or complete queen placements which are illegal and therefore trigger a backtrack movement. The black circle is the leaf of the search tree in which a solution is found (see Figure 2.2-t).

Figure 2.2 – Traversed part of the search tree for solving the four queens problem

Figure 2.3 - Queen placements represented by the 4-tuples in Figure 2.2

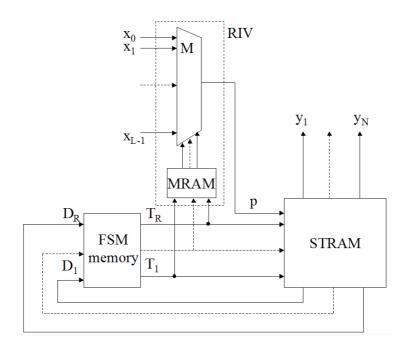

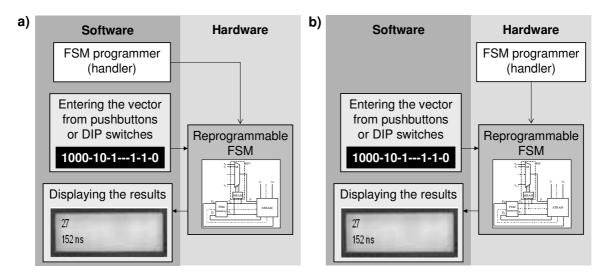

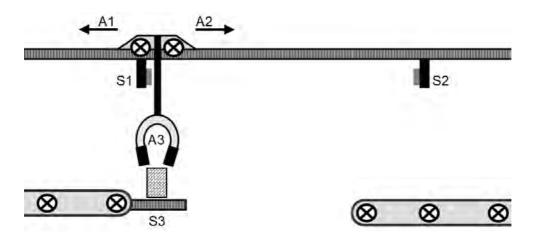

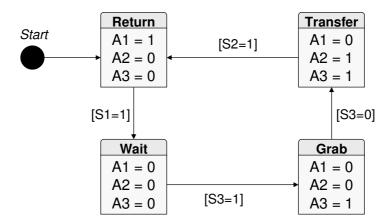

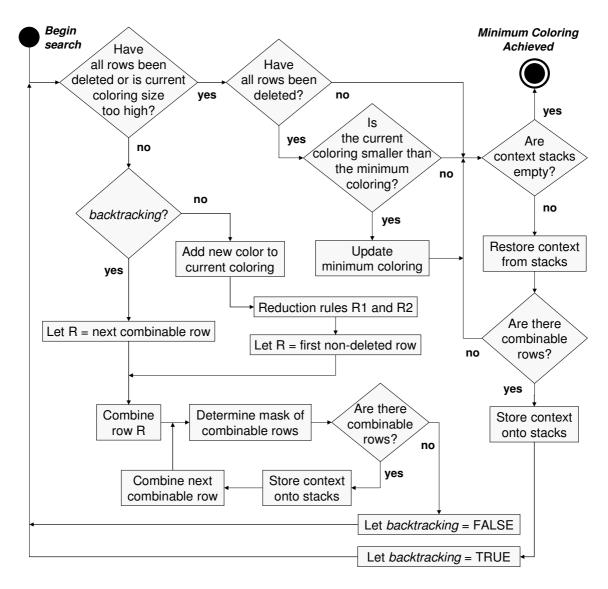

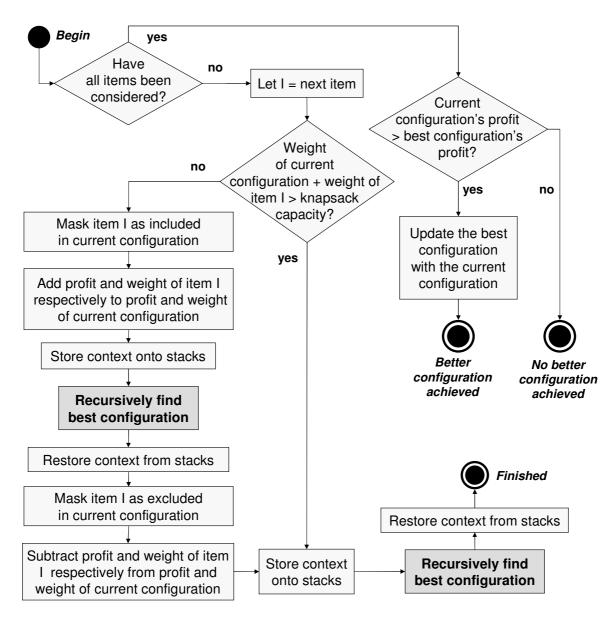

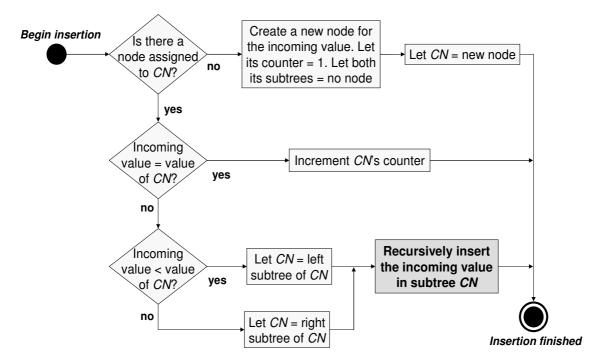

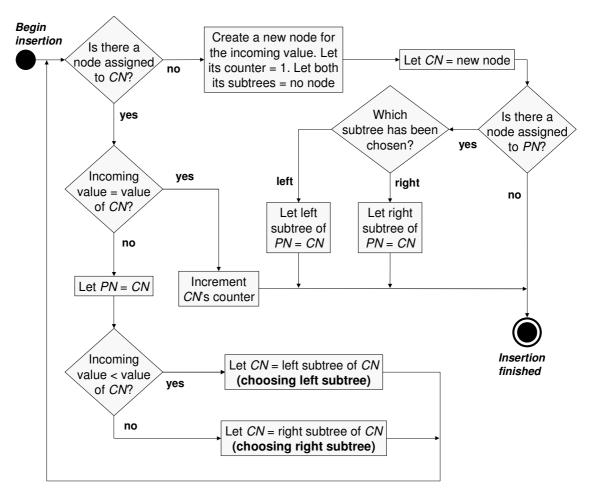

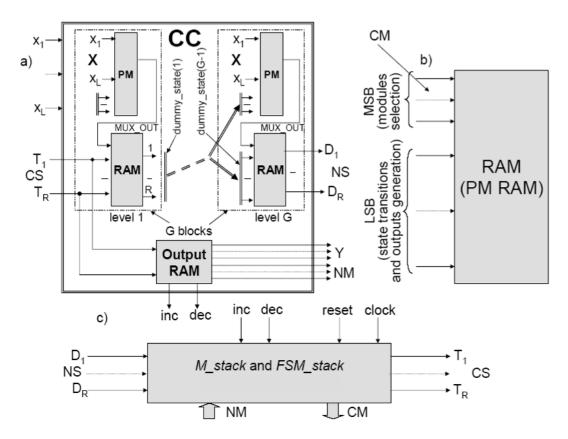

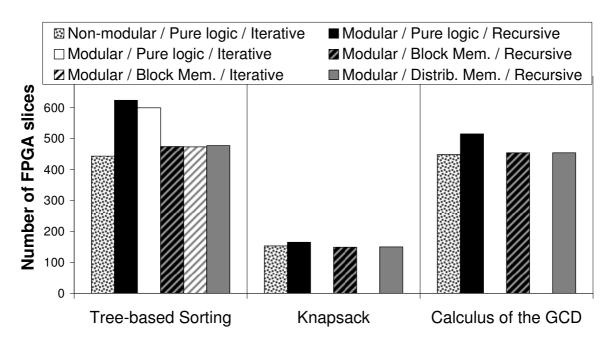

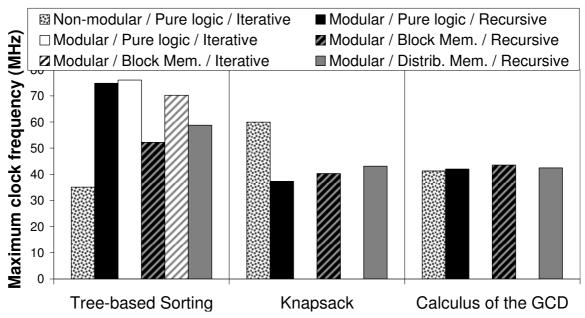

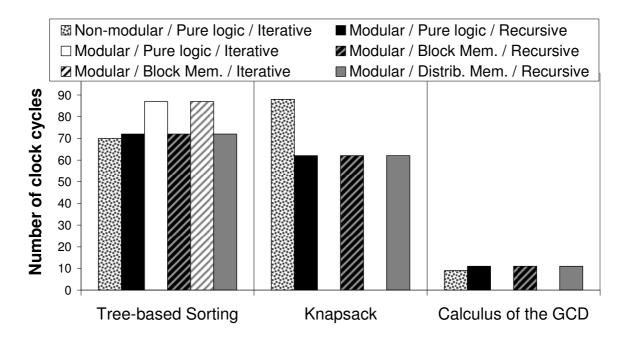

In order to better understand the traversed search tree and the reason for which some of its nodes correspond to illegal placements, the queen placements that are represented by the 4-tuples in Figure 2.2-a to Figure 2.2-t are depicted in Figure 2.3-a to Figure 2.3-t, respectively.