### Francisco Borges Carreiro

Usando o Protocolo Ethernet em Sistemas de Comunicação Tempo-Real Embutidos

**Using the Ethernet Protocol for Real-Time Communications in Embedded Systems**

### Francisco Borges Carreiro

## Usando o Protocolo Ethernet em Sistemas de Comunicação Tempo-Real Embutidos

# Using the Ethernet Protocol for Real-Time Communications in Embedded Systems

Tese apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Doutor em Engenharia Electrotécnica, realizada sob a orientação científica do Dr. José Alberto Gouveia Fonseca, Professor Associado do Departamento de Electrónica, Telecomunicações e Informática (DETI) da Universidade de Aveiro e do Dr. Francisco Manuel Madureira e Castro Vasques de Carvalho, Professor Associado da Faculdade de Engenharia da Universidade do Porto.

Apoio financeiro da Unidade de Investigação IEETA da Universidade de Aveiro

### O júri / The Jury

Presidente / President

### Vogais / Examiners committee

### Prof. Dr. Jorge Carvalho Arroteia

Professor Catedrático do Departamento de Ciências da Educação da Universidade de Aveiro.

### Prof. Dr. Carlos Eduardo Pereira

Professor Associado do Departamento de Engenharia Eléctrica da Universidade Federal do Rio Grande do Sul - UFRGS, Brasil.

Prof. Dr. Francisco Manuel Madureira e Castro Vasques de Carvalho Professor Associado do Departamento de Engenharia Mecânica da Faculdade de Engenharia da Universidade do Porto (Co-orientador).

### Prof. Dr. José Alberto Gouveia Fonseca

Professor Associado do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro (Orientador).

### Prof. Paulo José Lopes Machado Portugal

Professor Auxiliar do Departamento de Engenharia Electrotécnica e de Computadores da Faculdade de Engenharia da Universidade do Porto.

### Prof. Dr. Luís Miguel Pinho de Almeida

Professor Auxiliar do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro.

### Prof. Dr. Paulo Bacelar dos Reis Pedreiras

Professor Auxiliar do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro.

### agradecimentos

A realização de uma tese de doutoramento conta com a colaboração directa e indirecta de diversas pessoas. Bem sei que corro o risco de não dar conta de expressar nominalmente o meu 'muitíssimo obrigado' a todos aqueles que colaboraram. Contudo devido ao seu especial envolvimento, gostaria de particularizar os seguintes agradecimentos.

A José Alberto Fonseca, Professor da Universidade de Aveiro e meu orientador, a quem quero expressar meu profundo reconhecimento pelo empenho, amizade, disponibilidade, estímulo, sugestões, e apoio incondicional nos momentos mais difíceis.

A Francisco Vasques, Professor da Universidade do Porto e meu co-orientador, pela disponibilidade e inestimáveis contribuições que em muito ajudaram a valorizar o meu trabalho.

A Luis Almeida e Paulo Pedreiras pelas sugestões e clarificações em diversos assuntos discutidos ao longo deste trabalho.

A Joaquim Ferreira pela amizade e discussões científicas. A Valter Silva pelas sugestões, discussões científicas e principalmente em programação dos microcontroladores e por sua amizade.

Aos colegas Ricardo Marau, Filipe, Vasco, Maxmauro, Manuel Barranco, Iria, Arnaldo, Whatney e muitos outros que tive contacto no DETI durante o desenvolvimento deste trabalho.

E por últimos mas não os últimos quero agradecer a minha esposa e filhos. A Neldeci pelo suporte incansável de esposa e aos filhos Francisco Filho e Elioena que me conferem o orgulho de ser pai.

### palavras-chave

Tempo-real, ethernet, barramentos de campo, passagem de testemunho virtual, VTPE

#### resumo

Os Sistemas Computacionais de Controlo Distribuído (SCCD) estão muito disseminados em aplicações que vão desde o controlo de processos e manufactura a automóveis, aviões e robôs. Muitas aplicações são de natureza tempo-real, ou seja, impõem fortes restrições às propriedades subjacentes aos sistemas de controlo, gerando a necessidade de fornecer um comportamento temporal previsível durante períodos alargados de tempo. Em particular, dependendo da aplicação, uma falha em garantir as restrições pode causar importantes perdas económicas ou mesmo pôr vidas humanas em risco.

Actualmente, a quantidade e funcionalidade dos modernos SCCD têm crescido firmemente. Esta evolução é motivada por uma nova classe de aplicações que requer maior demanda de recursos tais como aplicações de multimedia (por exemplo visão), bem como pela tendência em usar grande número de processadres simples e interconectados, em vez de poucos e poderosos processadores, encapsulando cada funcionalidade num único processador. Consequentemente, a quantidade de informação que deve ser trocada entre os nós da rede também cresceu drasticamente nos últimos anos e está agora atingindo os limites que podem ser obtidos por tradicionais barramentos de campo, como por exempo CAN, WorldFIP, PROFIBUS.

Outras alternativas são pois requeridas para suportar a necessidade de largura de banda e a manutenção de exigências dos sistemas de comunicação tempo-real: previsibilidade, pontualidade, atraso e variação de período limitados.

Uma das linhas de trabalho tem apostado na Ethernet, tirando vantagem dos baixos custos dos circuitos, da elevada largura de banda, da fácil integração com a Internet, e da simplicidade em promover expansões e compatibilidade com redes usadas na estrutura administrativa das empresas industriais. Porém, o mecanismo padronizado de acesso ao meio da Ethernet (CSMA/CD) é destrutivo e não determinístico, o que impede seu uso directo ao nível de campo ou pelo menos em aplicações de comunicação tempo-real. Apesar disso, muitas abordagens diferentes têm sido propostas e usadas para obter comportamento tempo-real em Ethernet.

As abordagens actuais para dotar de comportamento tempo-real Ethernet partilhada apresentam desvantagens tais como: exigência de hardware especializado, fornecimento de garantias temporais estatísticas, ineficiência na utilização da largura de banda ou na reposta tempo-real. São ainda por vezes inflexíveis com respeito às propriedades de tráfego bem como com as políticas de escalonamento. Podem exigir processadores com elevado poder de cálculo. Finalmente não permitem que estações tempo-real possam coexistir com estações Ethernet standard no mesmo segmento. Uma proposta recente, o algoritmo hBEB, permite a coexistência de estações tempo-real e standard no mesmo segmento. Contudo, apenas uma estação tempo-real pode estar activa, o que é inaceitável para aplicações de automação e controlo.

Esta tese discute uma nova solução para promover tempo-real em Ethernet partilhada, baseando-se na passagem implícita de testemunho de forma similar à usada pelo protocolo P-NET. Esta técnica é um mecanismo de acesso ao meio físico pouco exigente em termos de processamento, sendo portanto adequada para implementar uma rede de dispositivos baseados em processadores de baixo poder de cálculo e controladores Ethernet standard.

Esta tese apresenta ainda uma proposta de implementação do VTPE em IP core para superar algumas dificuldades derivadas de funcionalidades que não são suportadas por controladores standard, nomeadamente a arbitragem do meio físico durante a transmissão de uma trama. Esta nova proposta pode aumentar muito a eficiência do VTPE no uso da largura de banda.

O VTPE, assim como P-NET ou protocolos similares, permite a uma estação apenas comunicar uma vez por cada circulação do testemunho. Esta imposição pode causar bloqueios de comunicação por períodos inaceitáveis em aplicações com tráfego isócrono, por exemplo multimedia. Uma solução proposta permite que uma estação possa aceder ao meio físico mais de uma vez por cada circulação do token. Os resultados experimentais a as análises desenvolvidas mostram que o bloqueio pode ser drasticamente reduzido.

Por último esta tese discute uma variante do protocolo VTPE, o VTPE/h-BEB, que permite que mais de uma estação hBEB possa coexistir com diversas estações Ethernet standard num mesmo segmento partilhado. Um demonstrador para prova de conceito bem como uma aplicação foram também implementados.

### keywords

Real-time, ethernet, fieldbus, virtual token passing, VTPE

#### abstract

Distributed Computer-Control Systems (DCCS) are widely disseminated in applications ranging from automation and control to automotive, avionics and robotics. Many of these applications are real-time, posing stringent constraints to the properties of underlying control systems, which arise from the need to provide predictable behaviour during extended time periods. Depending on the particular type of application, a failure to meet these constraints can cause important economic losses or can even put human life in risk.

Currently the number and functionality of modern DCCSs have been increasing steadily. This evolution has been motivated for a new class of applications of more resource demanding applications, such as multimedia (e.g. machine vision), as well as by the trend to use large numbers of simple interconnected processors, instead of a few powerful ones, encapsulating each functionality in one single processor. Consequently, the amount of information that must be exchanged among the network nodes has also increased dramatically and is now reaching the limits achievable by traditional fieldbuses.

Therefore, other alternatives are required to support higher bandwidth demands while keeping the main requirements of a real-time communication system: predictability, timeliness, bounded delays and jitter.

Efforts have been made with Ethernet to take advantage of the low cost of the silicon, high bandwidth, easy integration with the Internet, easy expansion and compatibility with the networks used at higher layers in the factory structure. However its standardized media access control (CSMA/CD) is destructive and not deterministic, impairing its direct use at field level at least for real-time communication.

Despite this, many solutions have been proposed to achieve real-time behavior in Ethernet. However they present several disadvantages: requiring specialized hardware, providing statistical timeliness guarantees only, being bandwidth or response-time inefficient, being inflexible concerning traffic properties and/or scheduling policy, or finally not allowing real-time stations to coexist with standard Ethernet stations in the same segment. A recent proposal, the hBEB algorithm, allows the coexistence of real-time and standard Ethernet stations in the same shared segment. However hBEB limits at most one real-time station per segment which is unacceptable for applications in industrial automation and process control.

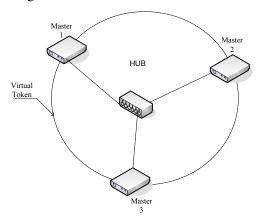

This thesis discusses a new real-time shared Ethernet solution based on the virtual token passing technique similarly to the one used by the P-NET protocol. This technique is a medium access control mechanism that requires small processing power, being suitable to implement devices based on processors with small processing power. The solution is called Virtual Token Passing Ethernet or VTPE. This proposal discusses the modifications required in the Ethernet frame format, the temporal analysis to guarantee real-time communication and the implementation of two demonstrators based on microcontrollers and standard Ethernet controllers.

This thesis also presents a proposal to implement VTPE in an IP Core to overcome some difficulties derived from limitations of standard Ethernet controllers, namely to allow medium access control during a frame transmission. This proposal can increase the bandwidth efficiency of VTPE.

VTPE, as well as P-NET or any other protocol based on circular token rotation technique, only allows a station to communicate once for each token round. This design imposition can cause unacceptable communication blocking in applications with isochronous traffic such as multimedia. An improvement in the VTPE proposal enables a station to access the medium more than once per token round. The experimental results as well as the temporal analysis show that the blocking can be drastically reduced. This improvement can also be used in the P-NET protocol.

Finally this thesis proposes a variant of VTPE, named VTPE/hBEB, to be implemented in Ethernet controllers that are able to support the hBEB algorithm. The VTPE/hBEB allows more than one hBEB station to coexist with several standard Ethernet stations in the same shared Ethernet segment. A demonstrator for the VTPE/hBEB validation, as well as an application, are also presented and discussed.

### apoios

Este trabalho foi apoiado pelas seguintes instituições:

Unidade de Investigação IEETA da Universidade de Aveiro, que me apoiou financeiramente com uma bolsa de investigação científica, bem como, para participação em várias conferências internacionais para apresentação de resultados parciais obtidos no âmbito desta tese.

Centro Federal de Educação Tecnológica do Maranhão CEFET-MA (Brasil), que me dispensou de serviço docente durante quatro anos.

## Index

| Index                                                                 | 1  |

|-----------------------------------------------------------------------|----|

| List of Figures                                                       | 4  |

| List of Tables                                                        | 6  |

| Chapter 1                                                             | 9  |

| Introduction                                                          | 9  |

| 1.1 The problem                                                       | 9  |

| 1.2 The thesis                                                        | 11 |

| 1.3 Contributions                                                     | 11 |

| 1.3.1 The VTPE protocol                                               | 12 |

| 1.3.2 The VTPE-hBEB                                                   | 12 |

| 1.4 Organization of the dissertation                                  | 12 |

| Chapter 2                                                             | 15 |

| Achieving real-time communication on ethernet                         | 15 |

| 2.1 Introduction                                                      | 15 |

| 2.2 Overview on the ethernet protocol                                 | 16 |

| 2.2.1 Ethernet roots                                                  | 16 |

| 2.2.2 The CSMA/CD protocol and the BEB collision resolution algorithm | 18 |

| 2.2.3 Analytical study of the BEB algorithm                           | 20 |

| 2.3 Achieving real-time communication on ethernet                     | 21 |

| 2.4 Modified CSMA protocols                                           | 22 |

| 2.4.1 hBEB algorithm                                                  | 23 |

| 2.4.2 EQuB                                                            | 25 |

| 2.4.3 Windows protocol                                                | 28 |

| 2.4.4 CSMA/DCR                                                        | 29 |

| 2.4.5 Virtual time CCMA                                               | 22 |

| 2.5 Token passing technique                       | 33 |

|---------------------------------------------------|----|

| 2.5.1 RETHER                                      | 34 |

| 2.5.2 RT-EP: Real-Time Ethernet Protocol          | 35 |

| 2.5.3 Other                                       | 37 |

| 2.6 Virtual token passing                         | 37 |

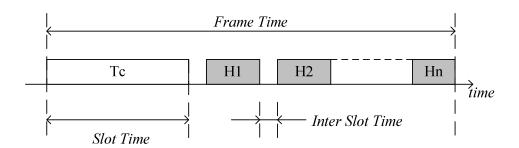

| 2.7 Time division multiple access – TDMA          | 41 |

| 2.7.1 The MARS bus                                | 41 |

| 2.7.2 Variable bandwidth allocation scheme        | 42 |

| 2.8 Master/slave techniques                       | 43 |

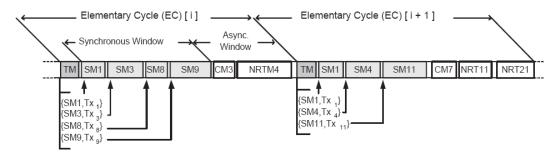

| 2.8.1 FTT-Ethernet protocol                       | 44 |

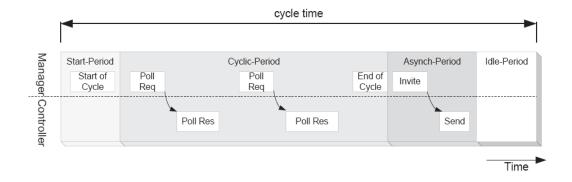

| 2.8.2 ETHERNET Powerlink                          | 45 |

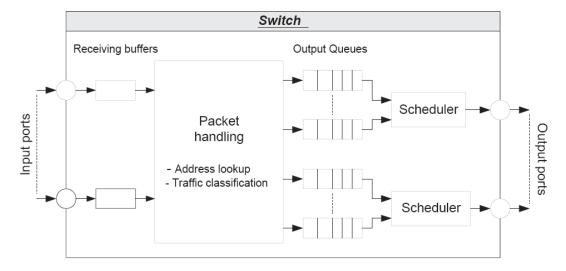

| 2.9 Switched ethernet                             | 47 |

| 2.9.1 EDF scheduled switch                        | 49 |

| 2.9.2 EtheReal                                    | 51 |

| 2.10 Recent advances                              | 53 |

| 2.11 Conclusion                                   | 55 |

| Chapter 3                                         | 57 |

| Virtual Token Passing Ethernet –VTPE              | 57 |

| 3.1 Introduction                                  | 57 |

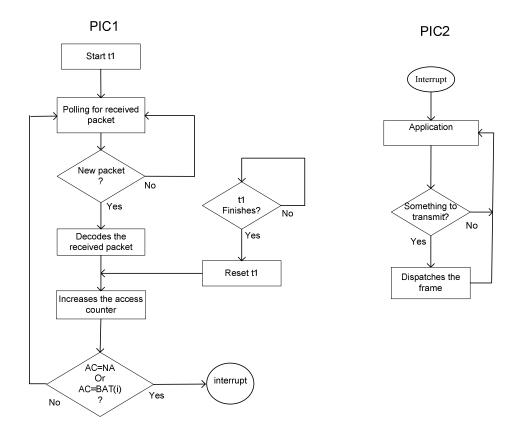

| 3.2 The classic virtual token-passing approach    | 58 |

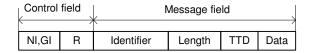

| 3.2.1 The VTPE format frame                       | 61 |

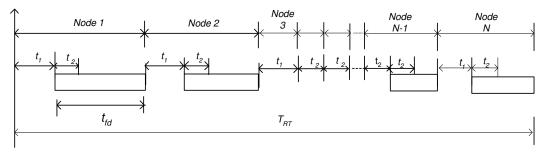

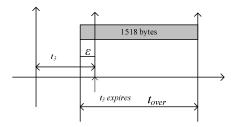

| 3.2.2 The VTPE parameters $t_1$ and $t_2$         | 63 |

| 3.2.3 VTPE real-time worst-case computation       | 64 |

| 3.2.4 Some experimental results                   | 66 |

| 3.3. Adapting VTPE to support isochronous traffic | 67 |

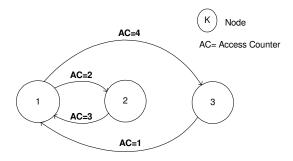

| 3.3.1 The bandwidth allocation scheme             | 68 |

| 3.3.2 Timing analysis                             | 70 |

| 3.3.3 Example                                     | 73 |

| 3.3.4 Adapting the classic VTPE frame             | 75 |

| 3.4. Conclusions                                  | 75 |

| Chapter 4                                         | 77 |

| The VTPE-hBEB Protocol                            | 77 |

| 4.1 Introduction                                                      | 77                 |

|-----------------------------------------------------------------------|--------------------|

| 4.2 The VTPE-hBEB protocol                                            | 79                 |

| 4.2.1 VTPE-hBEB topology                                              | 79                 |

| 4.2.2 VTPE-hBEB protocol                                              | 79                 |

| 4.2.3 Timing analysis                                                 | 81                 |

| 4.2.4 Adapting the VTPE-hBEB proposal                                 | 84                 |

| 4.3 Conclusions                                                       | 88                 |

| napter 5                                                              | 89                 |

| TPE and VTPE-hBEB Implementations                                     | 89                 |

| 5.1 Introduction                                                      | 89                 |

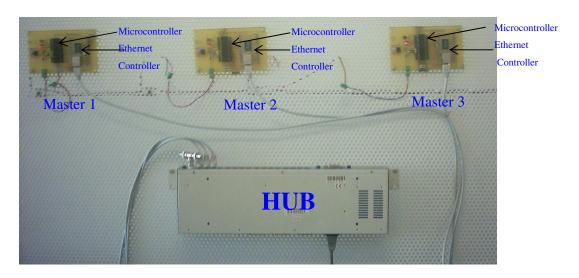

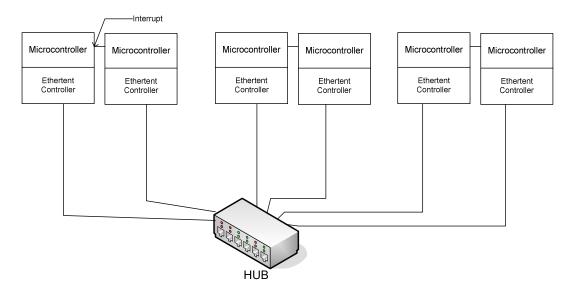

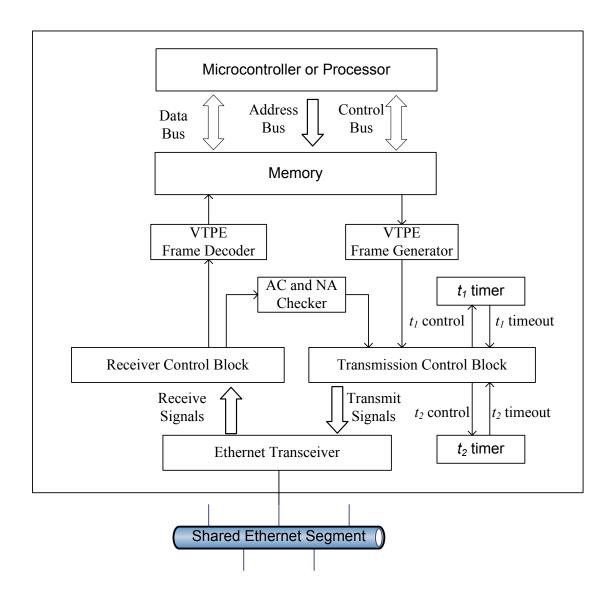

| 5.2 Implementation based on single ethernet controller                | 90                 |

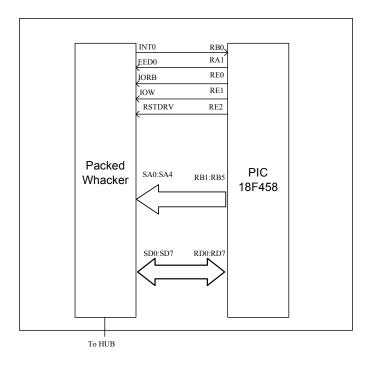

| 5.2.1 System architecture based on single ethernet controller         | 90                 |

| 5.2.2 Hardware of master based on single controller                   | 91                 |

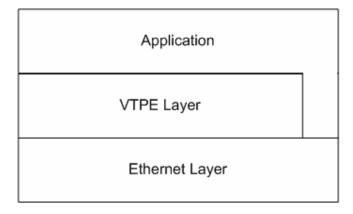

| 5.2.3 The VTPE stack architecture                                     | 93                 |

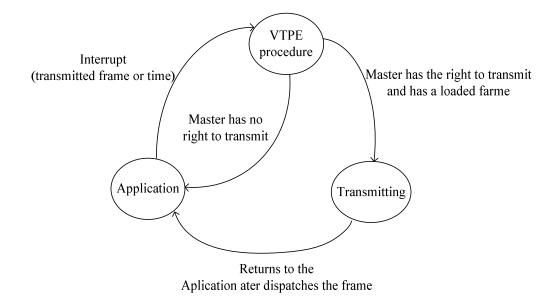

| 5.2.4 Using VTPE with application program                             | 97                 |

| 5.3 Implementation based on a dual ethernet controller architecture   | 98                 |

| 5.3.1 The dual ethernet controller architecture                       | 98                 |

| 5.3.2 Hardware of master based on dual ethernet controller architectu | re100              |

| 5.3.3 VTPE or VTPE-hBEB software for the dual ethernet controllers    | s architecture 102 |

| 5.3.4 Using VTPE with an application program                          | 107                |

| 5.4 Implementation based on an IP core                                | 108                |

| 5.5 Conclusions                                                       | 110                |

| napter 6                                                              | 113                |

| ming Behavior and Validation of VTPE and VTPE-hBEB                    | 113                |

| 6.1 Introduction                                                      | 113                |

| 6.2 Timing behavior of VTPE in the implementation based on single co  | ntroller114        |

| 6.3 Timing behavior of VTPE in the implementation based on the        | e dual controller  |

| architecture                                                          | 116                |

| 6.4 Demonstration system for validation of VTPE-hBEB                  | 121                |

| 6.4.1 The Evaluation setup                                            | 124                |

| 6.5 Timing analysis                                                   | 128                |

| 6.6 Results                                                           | 132                |

| 6.6.1 Unloaded network                                                                            | 133             |

|---------------------------------------------------------------------------------------------------|-----------------|

| 6.6.2 Full loaded ethernet                                                                        | 135             |

| 6.7 Conclusions                                                                                   | 139             |

| Chapter 7                                                                                         | 141             |

| Conclusions and Future Works                                                                      | 141             |

| 7.1 Thesis validation                                                                             | 142             |

| 7.2 Future work                                                                                   | 144             |

| Bibliography                                                                                      | 147             |

| List of Figures                                                                                   |                 |

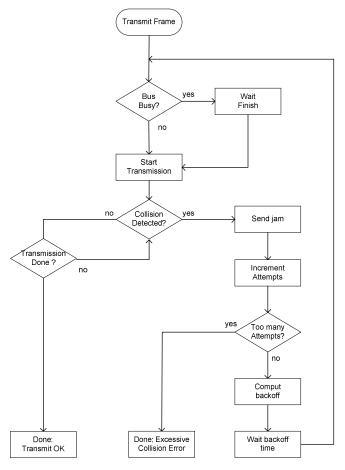

| Figure 2.1: CSMA/CD protocol with BEB algorithm.                                                  | 18              |

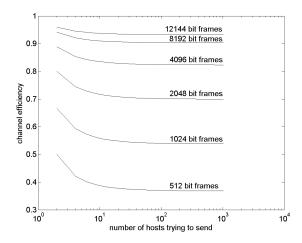

| Figure 2.2: Chanel Efficiency                                                                     | 21              |

| Figure 2.3: Control Flow Summary – hBEB.                                                          | 23              |

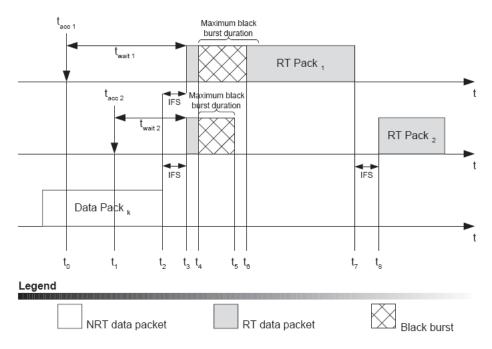

| Figure 2.4: Black burst contention resolution mechanism.                                          | 27              |

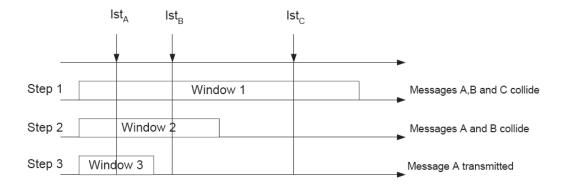

| Figure 2.5: Resolving collisions with the Windows protocol.                                       | 29              |

| Figure 2.6: Example of tree search with CSMA/DCR.                                                 | 31              |

| Figure 2.7: Example of Virtual-Time CSMA operation using MLF                                      | 32              |

| Figure 2.8: Sample network configuration for RETHER.                                              | 35              |

| Figure 2.9: Concepts of message cycle, token holding time (H), slave's tu                         | ırnaround time, |

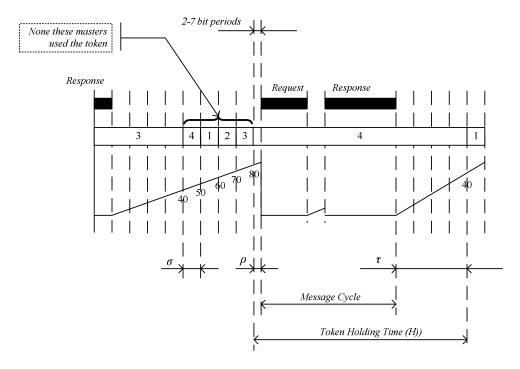

| master's reaction time $(\rho)$ , idle token time $(\sigma)$ and token passing time $(\tau)$ in F | -NET39          |

| Figure 2.10: Byte structure in a P-NET frame.                                                     | 40              |

| Figure 2.11: Frame of P-NET.                                                                      | 40              |

| Figure 2.12: The structure of a TDMA frame.                                                       | 42              |

| Figure 2.13: FTT-Ethernet traffic structure.                                                      | 44              |

| Figure 2.14: Powerlink cycle structure.                                                           | 46              |

| Figure 2.15: Switch internal architecture.                                                        | 48              |

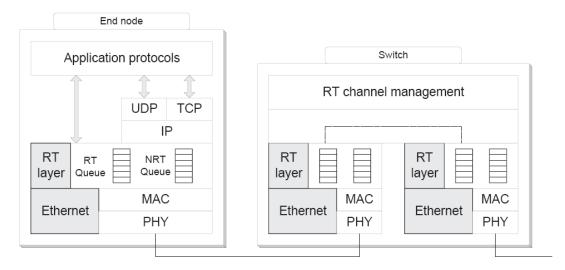

| Figure 2.16: System architecture.                                                                 | 50              |

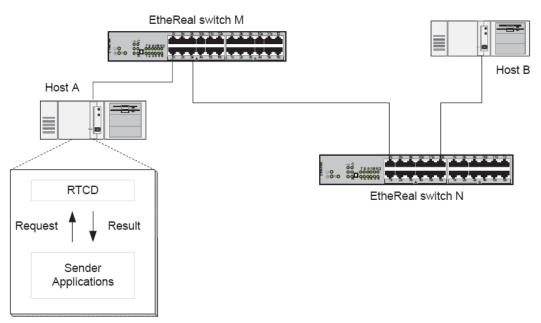

| Figure 2.17: Connection set-up procedure in the EtheReal architecture                             | 52              |

| Figure 3.1: The Virtual Token-passing in a VTPE system.                                           | 58              |

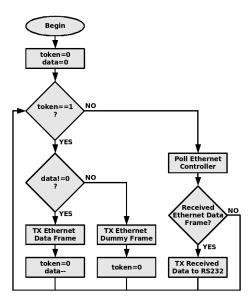

| Figure 3.2: VTPE flowchart.                                                                       | 60              |

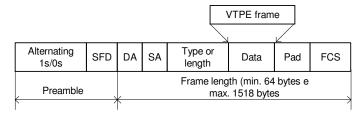

| Figure 3.3: Virtual Token-Passing Ethernet MAC frame.                                    | 61  |

|------------------------------------------------------------------------------------------|-----|

| Figure 3.4: VTPE frame format.                                                           | 62  |

| Figure 3.5: VTPE real-time behavior                                                      | 64  |

| Figure 3.6: State machine of the bandwidth allocation scheme.                            | 69  |

| Figure 3.7: New VTPE frame.                                                              | 75  |

|                                                                                          |     |

| Figure 4.1: Heterogeneous Ethernet environment.                                          | 77  |

| Figure 4.2: VTPE-hBEB Topology.                                                          | 79  |

| Figure 4.3: Control Flow Summary – VTPE-hBEB.                                            | 80  |

| Figure 4.4: Collision scenario solved by the hBEB collision resolution algorithm         | 82  |

| Figure 4.5: VTPE-hBEB token holding time.                                                | 84  |

| Figure 4.6: VTPE flowchart for a dual Ethernet controller implementation                 | 86  |

| Figure 5.1: VTPE system architecture                                                     | 90  |

| Figure 5.2: Experimental setup                                                           |     |

| Figure 5. 3: Hardware of a VTPE master                                                   |     |

| Figure 5. 4:VTPE master software architecture                                            |     |

| Figure 5. 5: Path of application to the VTPE                                             | 96  |

| Figure 5.6: Dual Ethernet controller architecture.                                       | 99  |

| Figure 5. 7:Experimental setup for dual Ethernet controller architecture                 | 100 |

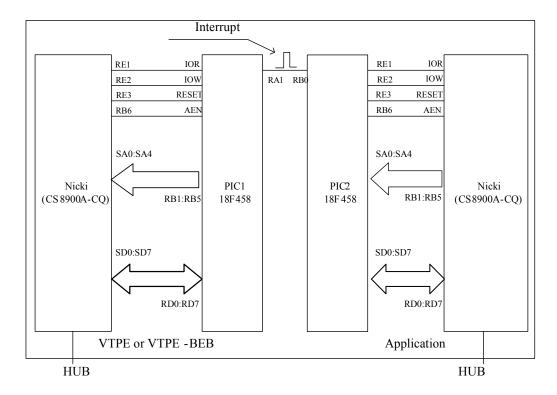

| Figure 5. 8: Hardware of master based on dual Ethernet controllers                       | 101 |

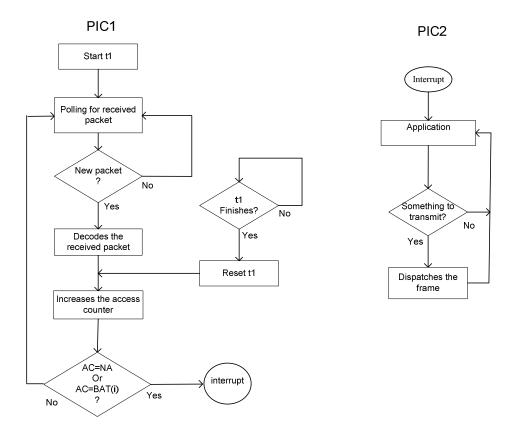

| Figure 5. 9:VTPE or VTPE-hBEB based on dual Ethernet controller architecture             | 103 |

| Figure 5. 10: VTPE or VTPE-hBEB for dual Ethernet controller architecture                | 103 |

| Figure 5. 11: Software for the second part of the dual Ethernet Controller architecture. | 107 |

| Figure 5. 12:VTPE IP core block diagram                                                  |     |

|                                                                                          |     |

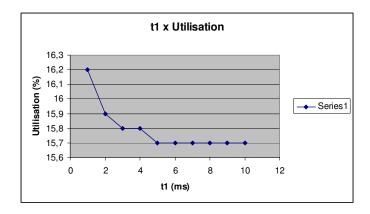

| Figure 6. 1: $t_1$ ( $\mu$ s) x bus utilisation (%)                                      | 116 |

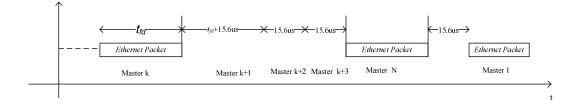

| Figure 6. 2: VTPE transmission scenario in the dual Ethernet controller architecture     | 119 |

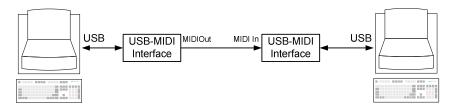

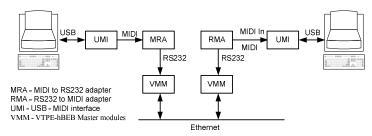

| Figure 6. 3: Testing a dedicated MIDI link.                                              | 121 |

| Figure 6. 4: MIDI to RS232 level logic adaptation.                                       | 122 |

| Figure 6. 5: MIDI to VTPE-hBEB link                                                      | 122 |

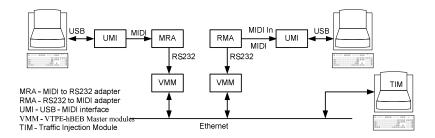

| Figure 6.6: MIDI to VTPE-hBEB link with Ethernet traffic injection.                      | 123 |

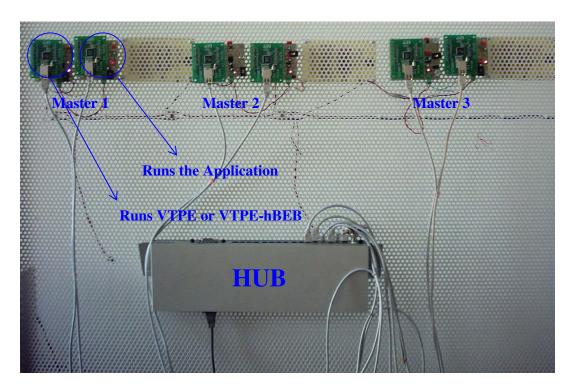

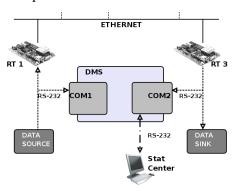

| Figure 6. 7: Evaluation test-bed                                                                  |

|---------------------------------------------------------------------------------------------------|

| Figure 6. 8: Application sub-node flowchart                                                       |

| Figure 6. 9: Application sub-node ISRs flowchart                                                  |

| Figure 6. 10: Delay Measurement System                                                            |

| Figure 6. 11: Ethereal capture – unloaded network                                                 |

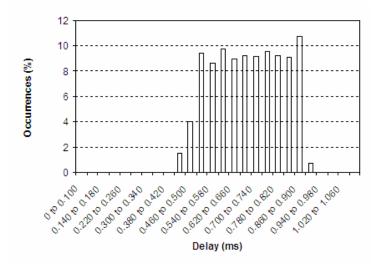

| Figure 6.12: Delay histogram - unloaded network                                                   |

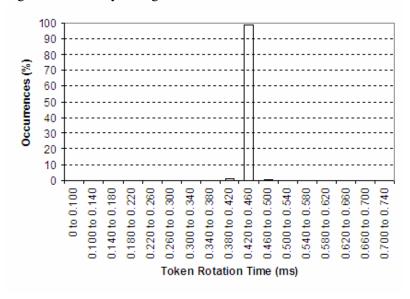

| Figure 6.13: TRT histogram - unloaded network                                                     |

| Figure 6.14: Ethereal capture – fully loaded network                                              |

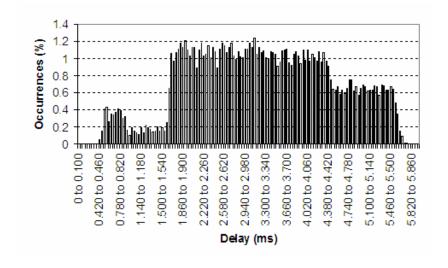

| Figure 6.15: Delay histogram – fully loaded network                                               |

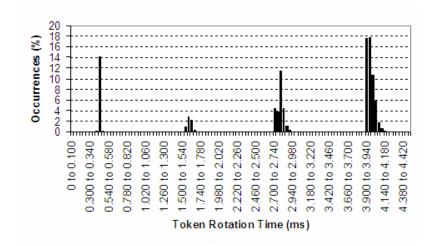

| Figure 6. 16: TRT histogram – fully loaded network                                                |

| Figure 6. 17: Worst case TRT time line                                                            |

|                                                                                                   |

| List of Tables                                                                                    |

| Table 2.1: Tree search example (contending sequence)                                              |

| Table 3.1: Tasks on received frame                                                                |

| Table 3.2: VTPE experimental results                                                              |

| Table 3.3: Bandwidth allocation table for the example of Figure 3.670                             |

| Table 3.4: Bandwidth allocation table for an example with 5 nodes                                 |

| Table 3.5:Real-time analysis results for the example of Table 3.4                                 |

| Table 4.1: Maximum delay to start transferring a message in the hBEB algorithm82                  |

| Table 5. 1:Set of functions for RTL8019AS initialisation                                          |

| Table 5. 2:VTPE Layer                                                                             |

| Table 5. 3: Set of functions for CS8900A-CQ initialisation                                        |

| Table 5. 4: Set of functions for the VTPE or VTPE-hBEB Layer                                      |

| Table 6.1: $t_1$ and bus utilisation in the implementation based on a single Ethernet controller. |

| Table 6. 2: Arbitration time on the dual Ethernet controller architecture                         |

| 1 and 0. 2. Individual time on the dual Emerification of dictine tune                             |

| Table 6. 3: Unloaded network – summary.   | .135 |

|-------------------------------------------|------|

| Table 6.4: Fully loaded network – summary | .138 |

### Chapter 1

### Introduction

### 1.1 The problem

Distributed Computer-Control Systems (DCCS) are widely disseminated, appearing in applications ranging from automated process and manufacturing control to automotive, avionics and robotics. Many of these applications have real-time nature, i.e., pose stringent constraints to the properties of the underlying control systems, which arise from the need to provide predictable behaviour during extended time periods. Depending on the particular type of application, failure to meet these constraints can cause important economic losses or can even put human life in risk [1].

Nowadays, the quantity and functionality of microprocessor-based nodes in modern DCCS have been increasing steadily [2]. This evolution has been motivated by new classes of more resource demanding applications, such as multimedia applications (e.g. machine vision), as well as by the trend to use large numbers of simple interconnected processors, instead of few powerful ones [3], encapsulating each functionality in one single processor [3]. Consequently, the amount of information that must be exchanged among the network nodes has also increased dramatically over the last years and it is now reaching the limits that are achievable using traditional fieldbuses [4], e.g. CAN, WorldFIP, PROFIBUS.

Therefore, other alternatives are required to support higher bandwidth demands while keeping the main requirements of a real-time communication system: predictability, timeliness, bounded delays and jitter.

Well-known networks, such as FDDI and ATM, have been extensively analysed for both hard and soft real-time communication systems [4]. However, due to high complexity, high cost, lack of flexibility and interconnection capacity, they have not gained general acceptance for the use at the field level [4].

Similar efforts have been done with Ethernet, trying to take advantage of the availability of cheap silicon, easy integration with Internet, clear path for future expandability, and compatibility with networks used at higher layers in the factory structure [5]. However, its standardized non-deterministic arbitration mechanism (CSMA/CD) prevents its direct use at field level, at least for hard real-time communications. Despite of this, there are many different approaches for achieving real-time behaviour on Ethernet.

The techniques that have been used to achieve deterministic message transmission on Ethernet are the well-known medium access control techniques for shared broadcast networks such as Modified CSMA protocols, Time Division Multiple Access – TDMA, Token-passing, Master/slave technique, and Switched Ethernet.

Since roughly one decade ago that the interest on using Ethernet switches has been growing as a means to improve global throughput, traffic isolation and to reduce the impact of the non-deterministic features of the original CSMA/CD arbitration mechanism. However a common misconception is that the use of switches, due to the elimination of collisions, is enough to enforce real-time behaviour in Ethernet networks, but this is not true in the general case.

Despite of the recent proposals consisting in using switched Ethernet to replace fieldbuses in control and factory automation, the interest on shared Ethernet is not over, yet, either for applications requiring frequent multicasting, in which case the benefits of using switches are substantially reduced, as well as for applications requiring precise control of transmission timing, such as high speed servoing (Almeida and Pedreiras [6]).

Solving the collision problem however is only part of a useful shared Ethernet solution to field level application. There are many other important requirement that a real-time Ethernet solution must have, or at least, that it is desirable to have. For example some of those are the introduction of operational flexibility, like to add and to remove nodes, to have an online bandwidth allocation scheme, to have an efficient support of multicast messages, and to be fault tolerant.

Nowadays there are many approaches to achieve real-time on shared Ethernet, but it is interesting to notice that such approaches either require specialized hardware, or just provide statistical timeliness guarantees, or are bandwidth or response-time inefficient, or are inflexible concerning the properties of the network traffic as well as the traffic scheduling policy, or finally, they are costly in terms of processing power and memory requirements. Also, recent proposals such as hBEB [9] limit the number of real-time nodes to just a single transmission station which is unacceptable for automation applications. Thus they are not well suited for use in small sensors, actuators and controllers with communications capability. So there is a need to find Ethernet deterministic solutions, so that it becomes possible to take profit of its higher data-communication capacity to interconnect sensors, controllers and actuators at the field level.

This thesis discourses about a new real-time Ethernet solution based on the virtual token-passing in order to override the destructive and non-deterministic CSMA/CD medium access arbitration mechanism of Ethernet. Virtual token-passing technique is a real-time bus arbitration mechanism especially suitable for shared networks which use small processing power processors in most of the nodes.

### 1.2 The thesis

This thesis presents a proposal and the development of the Virtual Tokenpassing Ethernet (VTPE), a new real-time implementation to support real-time traffic on shared Ethernet, and the VTPE-hBEB protocol, an improvement of VTPE to support real-time communication in unconstrained shared Ethernet, i.e., an environment comprised of an unlimited number of Ethernet standard stations and real-time stations (hBEB).

EQuB and hBEB, according our best knowledge are the unique solutions that provide traffic separation, allowing real-time devices to coexist with standard Ethernet devices in the same network segment.

### 1.3 Contributions

Two general contributions of this thesis are summarized in the following subsections. The first one is the proposal and development of the VTPE protocol, and the second one is the VTPE-hBEB protocol a variant of VTPE, to support real-time communication in unconstraint shared Ethernet.

### 1.3.1 The VTPE protocol

The VTPE [7] is a real-time Ethernet approach based on implicit token rotation (virtual token passing) like the one used in the P-NET fieldbus protocol [8]. The virtual token-passing approach is a simple and efficient technique suitable for shared bus networks, especially when small processing power processors are used as CPUs.

The following goals have been established to develop VTPE:

- Support on the same bus of slow and cheap devices based in microcontrollers, as well as more demanding devices integrating powerful processors;

- Low processing overhead in order to be implemented in microcontrollers with low processing power;

- Hardware based in COTs components;

- Online bandwidth allocation scheme

- Support for hBEB protocol to work as multi-node (VTPE-hBEB protocol);

- Efficient support of multicast messages;

### 1.3.2 The VTPE-hBEB

The VTPE-hBEB protocol, as the name indicates, is an implementation of VTPE over hBEB protocol. hBEB is a real-time shared Ethernet protocol proposed in [9] which main advantage is to support real-time traffic separation on a shared Ethernet bus. However hBEB has a disadvantage: it is single-node, i.e., it just allows one node with real-time privileges. hBEB lacks a mechanism to support multi-node implementation and the VTPE is indicated as the principal bus arbitration mechanism to solve this problem. So the VTPE-hBEB is other important contribution of this thesis.

### 1.4 Organization of the dissertation

In order to support the thesis previously stated this dissertation is organized in the following chapters.

**Chapter 2** - Presents a background on the Ethernet protocol and discusses the main Ethernet approaches proposed for real-time communication on shared Ethernet networks throughout Ethernet evolution. Chapter 2 also presents some discussions and approaches for real-time communication on switched Ethernet considering its current popularity. However it is focused on shared Ethernet that is the context of this thesis.

**Chapter 3** – Presents the Virtual Token-Passing Ethernet protocol - VTPE. In the Chapter 3 are presented the VTPE classic approach similar to the P-NET protocol and an adaptation of VTPE in order to support isochronous traffic.

**Chapter 4** - Presents the VTPE-hBEB protocol. VTPE-hBEB is an improvement of VTPE aimed for real-time communication on shared Ethernet. VTPE-hBEB allows the coexistence of real-time devices as well as standards Ethernet devices in the same network segment.

**Chapter 5** - Presents the implementations of VTPE and VTPE-hBEB protocol. Implementation aspects as well as software and hardware are presented and discussed.

**Chapter 6** - Presents the experimental results obtained for both implementations.

**Chapter 7** - This chapter presents the conclusions and future works. As future works are proposed the implementation of VTPE and its variants on IP cores and a new version of VTPE for power line communication.

### Chapter 2

### Achieving real-time communication on ethernet

### 2.1 Introduction

Ethernet is the most frequently used wired local area network technology today. The Main factors that favour the use of the Ethernet protocol are [6]:

- It is cheap, due to mass production;

- Integration with Internet is easy (TCP/IP stacks over Ethernet are widely available, allowing the use of application layer protocols such as FTP, HTTP and so on);

- Steady increases on the transmission speed have happened in the past, and are expected to occur in the near future;

- Due to its inherent compatibility with the communication protocols used at higher levels, the information exchange with the plant level becomes easier;

- The bandwidth made available by existing fieldbuses is insufficient to support some recent developments, like the use of multimedia (e.g. machine vision) at the field level;

- Availability of technicians familiar with this protocol;

- Wide availability of test equipment from different sources;

- Mature technology, well specified and with equipment available from many sources, without incompatibility issues.

However Ethernet does not fulfil some fundamental requirements that are expected from a communication protocol operating at the field level. In particular, the destructive and non-deterministic arbitration mechanism has been regarded as the main obstacle faced by Ethernet concerning this applications domain. The answer to this concern is the use of

switched Ethernet, which allows bypassing the native CSMA/CD arbitration mechanism. In these cases, provided that a single network interface card (NIC) is connected to each port, and the operation is full duplex, no collisions occur. However, just avoiding collisions does not make Ethernet deterministic: for example, if a burst of messages destined to a single port arrive at the switch in a given time interval, they must be serialized and transmitted one after the other. If the arriving rate is greater that the transmission rate, buffers will be exhausted and messages will be lost. Therefore, even with switched Ethernet, some kind of higher-level coordination is required. Moreover, bounded transmission delay is not the only requirement of a fieldbus, some other important factors commonly referred to in the literature are: temporal consistency indication, precedence constraints, efficient handling of periodic and sporadic traffic. Clearly, Ethernet, even with switches, does not provide answers to all these demands [6].

This chapter presents and discusses the state of the art of the main real-time protocols based on Ethernet, proposed during Ethernet evolution. It is focused on shared Ethernet. However, a brief overview on switched Ethernet is also presented, considering its current popularity.

The remaining of this chapter is as follows: Section 2.2 presents an overview on the Ethernet protocol. Section 2.3 presents the main medium access control techniques for shared broadcast networks that are commonly used to guarantee real-time communication. Section 2.4 to section 2.8 discusses each one of the medium access control techniques and the main shared Ethernet real-time approaches based on these techniques. Section 2.9 presents some discussions and techniques related to switched Ethernet and section 2.10 presents the recent advances in the Ethernet issues. Finally section 2.11 presents the conclusions.

### 2.2 Overview on the ethernet protocol

#### 2.2.1 Ethernet roots

Ethernet was born about 30 years ago, invented by Bob Metcalfe at the Xerox's Palo Alto Research Center. Its initial purpose was to connect two products developed by Xerox: a personal computer and a brand new laser printer. Since then, this protocol has evolved in many ways. For instance, concerning the transmission speed, it has grown from the

original 2.94Mbps to 10Mbps [10] [11] [12] [13] [14] then to 100Mbps [15] and more recently to 1Gbps [16] and 10Gbps [17]. Concerning physical medium and network topology, Ethernet also has evolved: it started by a bus topology based firstly on thick coaxial cable [11] and afterwards on thin coaxial cable [12]. In the mid 80's a more structured and fault-tolerant approach, based on a star topology, was standardized [13], running however only at 1Mbps. In the beginning of the 90's an improvement of this latter technology was standardized [14], running at 10Mbps over category 5 unshielded twisted pair cable.

Along this way, two fundamental properties have been kept unchanged:

- Single collision domain, that is, frames are broadcast on the physical medium and all the network interface cards (NIC) connected to it receive them;

- The arbitration mechanism, which is called Carrier Sense Multiple Access with Collision detection (CSMA/CD).

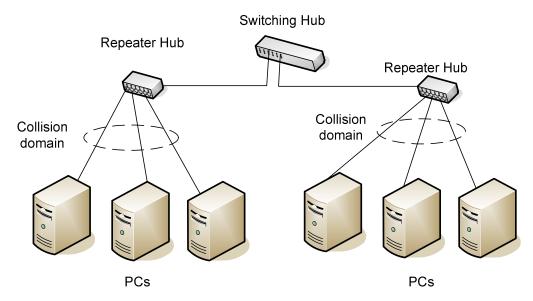

The use of a single broadcast domain and the CSMA/CD arbitration mechanism has created a bottleneck when facing highly loaded networks: above a certain threshold, when the submitted load increases the throughput of the bus decreases, a phenomenon referred to as thrashing. In the beginning of the 90's, the use of switches in place of hubs has been proposed as an effective way to deal with thrashing. A switch creates a single collision domain for each of its ports. If a single node is connected to each port, collisions never actually occur unless they are created on purpose, e.g. for flow control. Switches also keep track of the addresses of the NICs connected at each port by inspecting the source address in the incoming messages. This allows forwarding incoming messages directly to the respective outgoing ports according to the respective destination address, a mechanism generally known as forwarding. When a match between a destination address and a port cannot be established, the switch forwards the respective message to all ports, a process commonly referred to as flooding. The former mechanism, forwarding, allows a higher degree of traffic isolation so that each NIC receives the traffic addressed to it, only. Moreover, since each forwarding action uses a single output port, several of these actions can be carried out in parallel, resulting in multiple simultaneous transmission paths across the switch and, consequently, in a significant increase in the global throughput.

### 2.2.2 The CSMA/CD protocol and the BEB collision resolution algorithm

The CSMA/CD (Carrier Sense Multiple Access with Collision Detection) protocol is the protocol implemented at the MAC layer of Ethernet.

Basically the CSMA/CD protocol works as shown in Figure 2.1. When a station wants to transmit it listens the transmission medium. If the transmission medium is busy, the station waits until it goes idle, otherwise it transmits immediately. If two or more stations begin simultaneously to transmit, the transmitted frames will collide. Upon the collision detection, all the transmitting stations will terminate their own transmission and send a jamming sequence. When the transmission is aborted due to a collision, it will be repeatedly retried after a randomly evaluated delay (backoff time), until it is either successfully transmitted, or definitely aborted (after a maximum number of 16 attempts).

Figure 2.1: CSMA/CD protocol with BEB algorithm.

The backoff delay is evaluated by locally executing the Binary Exponential Backoff (BEB) algorithm, which operates as follows: after the end of the jamming sequence, the time is

divided into discrete slots, whose length is equal to the slot time<sup>1</sup>. The backoff time is given by  $t_{backoff} = r \times T$ , where r is a random integer in the range  $0 \le r \le 2^k - 1$ , k is the smaller of n or 10 (n is the number of retransmission attempts) and T is the slot time in seconds. This means that the station will wait between 0 and  $2^k - 1$  slot times. After 10 attempts, the waiting interval is fixed at 1023 slot times, and finally, after 16 attempts, the transmission is discarded.

The CSMA/CD protocol seems to have a random queue service discipline, i.e., the message to be transferred after a successful transmission seems to be randomly chosen among the N hosts with ready messages. However, Christensen [18] demonstrated that the BEB algorithm imposes a last come first serve policy, as a station with the more recently queued packet, will have a higher probability for the acquisition of the medium.

Another particularity of the CSMA/CD protocol is the Packet Starvation Effect. Wheten et al. [19] demonstrated that, in heavily loaded networks, an older packet will have a smaller probability to be transferred than a newer one. For example: consider that 2 stations have packets ready to be transmitted (station1 and station2), which will be transmitted at approximately the same time; a collision will occur and then both stations will backoff during a randomly selected delay between 0 and 2<sup>n</sup>-1 slot times, where n is the number of previous collisions. In the first collision resolution interval, if station1 waits 0 slot times and station2 waits 1 slot time, station1 will transmit its packet while station2 will wait. Supposing that station1 has other packets to be transferred, then, in the following collision, the backoff time of station1 will be 0 or 1, and the backoff time of the station2 will be 0, 1, 2 or 3. Therefore, station1 will have a higher transmission probability. Such Packet Starvation Effect will occur whenever a station has a sequence of packets to be consecutively transferred, if the network interface adapter is able to effectively contend for the network access at the end of every transmitted frame. Otherwise, another station will acquire the transmission medium.

٠

$<sup>^{1}</sup>$  For Ethernet and Fast Ethernet (10/100 Mbps) networks, one slot time is the time required for transmitting the minimum frame size (512 bits), that is, respectively, 51.2 and 5.12  $\mu$ sec. For Gigabit Ethernet (1Gbps), one slot time corresponds to the transmission time of 4096 bits.

### 2.2.3 Analytical study of the BEB algorithm

In order to analyse the BEB Algorithm many performance analyses have been proposed. One of the first Ethernet performance analyses was presented by Metcalfe and Boggs in [20], where the authors draw up a set of formulas to execute the exact analysis in heavily loaded Ethernet networks. In that analysis, a constant retransmission probability on each slot has been assumed, and the successful retransmission probability (on the next slot) has been considered to be equal to a constant: p. Therefore, for the case of K active hosts (hosts with packets ready to be transmitted), the probability that only one host will transmit in the beginning of a slot (thus avoiding a collision), according to [20] is:

$$A = K \times p \times (1-p)^{K-1} \tag{2.1}$$

Such probability A is maximized when p=1/K. (equal probability of successful retransmission). Such assumption is an interesting approximation for the real backoff function, as it has been shown in multiple simulation studies by Lam and Kleinrock [21], and by Almes and Lazowska [22]. Thus,

$$A = (1 - \frac{1}{K})^{K - 1} \tag{2.2}$$

The probability that a host will wait during just 1 slot is A(1-A), while the probability that the contention interval will be exactly n slots is:

$$P_n = A \times (1 - A)^{n-1}$$

n >=1 (2.3)

The estimated number of stations trying to transmit is truncated to 1023. Truncating imposes an upper bound to the time interval (backoff delay) that any station must wait before trying to transmit again. Therefore, it results on an upper bound of 1024 potential slots for transmission. Such upper bound imposes a maximum number of 1024 stations that can be supported by a half duplex Ethernet system (Spurgeon [23]).

The average number of contention slots is given by Metcalfe and Boggs [20]:

$$Z = \sum_{n=0}^{\infty} n \times A \times (1 - A)^n = \frac{1 - A}{A}$$

(2.4)

Considering P as the packet length (expressed in bits) and C as the network data rate (expressed in bps), the ratio P/C represents the transmission time of an average packet (expressed in seconds). Therefore, the channel efficiency E (time during which packets are being effectively transmitted) can be evaluated as the ratio between the transmission time and the transmission plus contention intervals:

$$E = \frac{P/C}{P/C + (Z \times T)} \tag{2.5}$$

where Z×T represents the average acquisition time before effectively transmitting (T is the slot time in seconds). Figure 2.2 illustrates the "channel efficiency" in heavily loaded networks, assuming a 10Mbps Ethernet network (C=10 Mbps; T=51.2ms).

Figure 2.2: Chanel Efficiency.

According to Boggs et al. [24], one of the most widely accepted Ethernet myths is that it saturates at an offered load of 37%. Such assertion is well founded when dealing with short sized frames and a significant number of hosts. However, for longer frames, the channel efficiency is significantly improved. Schoch and Hupp [25] presented measurements results indicating that for 4096 bit frames and small number of hosts, the channel utilization approaches 97%; however, for small packets and larger number of hosts the utilization approaches 1/e, that is, approaches the 37% bound. These results are consistent with the Metcalfe and Boggs analysis [20], as it can be observed in the channel efficiency results represented in Figure 2.2.

### 2.3 Achieving real-time communication on ethernet

In the quest for real-time communication over Ethernet several approaches have been developed and used. Many of them override the Ethernet CSMA/CD medium access control by setting an upper transmission control layer that eliminates, or at least reduces, the occurrence of collisions at the medium access. Other approaches propose the

modification of the CSMA/CD medium access control layer so that collisions either occur seldom or when they do, the collision resolution is deterministic and takes a bounded worst-case time.

Moreover, some approaches support such deterministic reasoning on the network access delay while other ones allow a probabilistic characterization, only.

The solutions to make shared Ethernet real time are mainly based on the usual medium access control techniques for shared broadcast networks. For the sake of clarity, they are classified and presented as follows in the remainder of this chapter:

- Modified CSMA protocols;

- Token-passing;

- Virtual token passing;

- Time Division Multiple Access TDMA;

- Master/slave techniques;

Switched Ethernet doesn't enable the use of a shared Ethernet bus because the switch creates a single collision domain. In spite of this large difference, Switched Ethernet is also discussed, considering its current popularity.

### 2.4 Modified CSMA protocols

In this category the CSMA mechanism is adequately modified in order to improve the temporal behaviour of the network (e.g. [26] [27] [28]). The result is still a fully distributed arbitration protocol of the CSMA family (Carrier Sense, Multiple Access) that determines when to transmit based on local information and on the current state of the bus, only.

There are two most common options, either sorting out collisions in a more deterministic way than the Ethernet original BEB mechanism (truncated Binary Exponential Backoff) or reducing the probability of collisions. This section presents five modified CSMA/CD protocols, the first four, i.e., hBEB algorithm, EQuB, Windows protocol and the CSMA/DCR follow the first option. The last one, that is, the Virtual Time CSMA follows the second option by implementing a type of CSMA/CA (Collision Avoidance) that delays message transmissions according to a temporal parameter.

### 2.4.1 hBEB algorithm

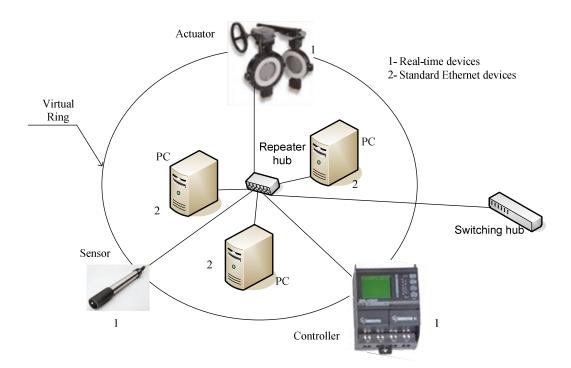

Moraes and Vasques [9] proposed the "high priority Binary Exponential Backoff (hBEB)" collision resolution algorithm. The main advantage of hBEB is allowing Ethernet standard devices to coexist with one hBEB modified station. As a consequence, it becomes possible the implementation of traffic separation policies, which are the foundation for the support of real-time communication, in heterogeneous Ethernet environments.

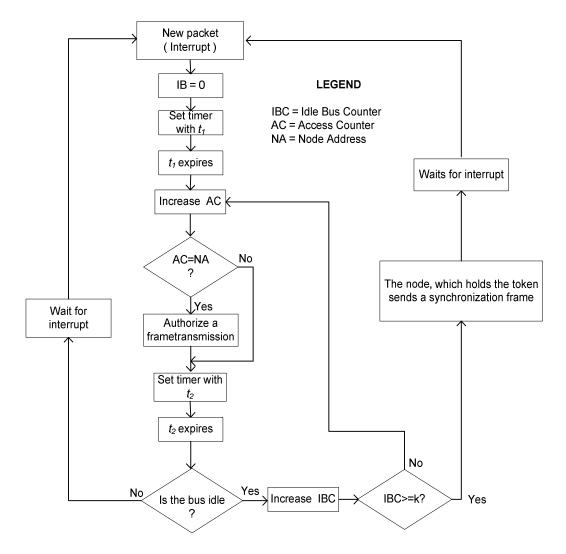

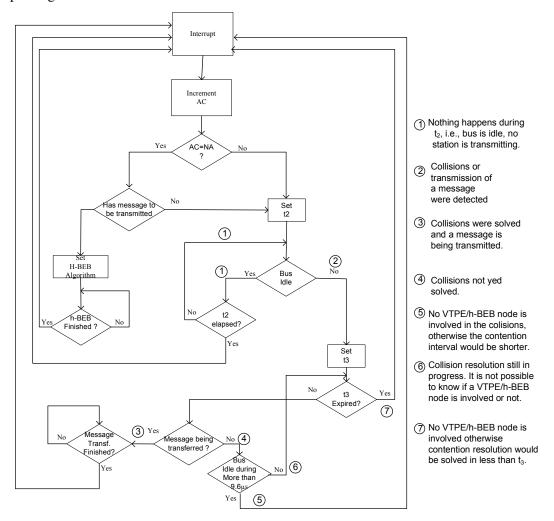

A station implementing the hBEB algorithm has the same operating behavior of BEB algorithm, except for the backoff delay, which is set to 0. In such case, an hBEB station starts immediately to transmit after the end of the jamming sequence. This behavior guarantees the highest transmitting probability to the hBEB station, in a shared Ethernet segment with multiple BEB stations. The hBEB station will always try to transmit its frame in the first available slot after the jamming sequence, while all the other stations implementing the BEB algorithm will wait between 0 and 2<sup>n</sup>-1 slot times, where n is the number of collision resolution rounds. Figure 2.3 summarize the dynamic behavior of the CSMA/CD protocol with the hBEB collision resolution algorithms.

Figure 2.3: Control Flow Summary – hBEB.

The hBEB collision resolution algorithm is therefore able to impose real-time traffic separation, as the traffic generated by the hBEB station will always be transferred before the traffic generated by the other stations. Therefore, this algorithm is adequate to support real-time communications in shared Ethernet segments, as long as all the real-time traffic in the network is generate by the hBEB station. According to Moraes and Vasques this behavior is highly adequate for real-time video/voice transferring applications in

legacy shared Ethernet networks. By simply plugging a notebook computer with the modified hardware to the shared Ethernet segment, it becomes possible to transfer traffic at a higher priority than the traffic generated by all the other stations.

In [9] Moraes and Vasques show that the probability that the hBEB station sends a message in the  $n^{th}$  collision round (after an initial collision) is given by:

$$P(n,N) = \sum_{i=0}^{N} (-1)^{i} {N \choose j} \times 2^{-jn}$$

(2.6)

where the coefficients of the Pascal Triangle are given by:

$$\binom{N}{j} = \frac{N!}{j!(N-j)!} \tag{2.7}$$

n is the number of collision resolution rounds, and N is the number of BEB stations in the network (N+1 is the total number of stations).

A comparative analysis of BEB and hBEB algorithms has been performed and presented in [29]. This analysis considers a shared Ethernet environment where 64 standard Ethernet stations are interconnected with a special station implementing either the hBEB (enhanced Ethernet mode) or the BEB (traditional Ethernet mode) collision resolution algorithms. Probabilistic analytical results obtained from Equation (2.3) were compared with those obtained from Equation (2.6). The results show that approximately 95% of the messages from the hBEB station are transferred before 8 collision rounds. On the other hand, the probability to transfer a message, in the same heavily loaded network scenario, using the BEB algorithm (traditional mode) is smaller than 2%, whatever the considered collision round.

For more realistic network load scenarios a simulation analysis has been done. A simulation model was implemented using the Network Simulator tool [30], considering a 10 Mbps Ethernet network, where each station has a Poisson traffic source with a fixed packet length of 250 bytes. For each simulated load value,  $75x10^4$  packets are successfully transmitted. The performance measures included: throughput, average packet delay and standard deviation of the average packet delay. It has be shown in [31] that the hBEB collision resolution algorithm guarantees, whatever the network load, an average access delay significantly smaller for the hBEB station, when compared with the access delay for the BEB stations. More significantly, almost constant values for both the average access delay and the related standard deviation have been observed for the traffic transferred by

the hBEB station. This is a very important result, as it forecasts a predictable communication delay when supporting real-time communications.

The authors of hBEB showed by simulation analysis that the hBEB traffic must be tightly controlled, as it has a high interference level over the non-real-time traffic [32], otherwise, if the load generated by the hBEB station is not closely controlled, the standard Ethernet stations may experience extended access delays.

A probabilistic timing analysis of hBEB was presented in [33] for two cases. Firstly, the analytical study for a heavily loaded network scenario shows that the maximum access delay for 95% of the messages is smaller than 1,86ms. Secondly, for more realistic load scenarios (intermediate load cases), the simulation analysis shows that the maximum access delay for 98% of the messages is always smaller than 1ms. More importantly, it shows a nearly constant message transfer jitter, which is one order of magnitude smaller than the maximum access delay for 98% of the messages. Also it is shown that concerning the probability of a message frame being discarded by the hBEB algorithm, for the heavily loaded network scenario, such probability is always smaller than 2x10<sup>-3</sup> and for more realistic load scenarios, the simulation analysis never detected any discarded frame. According to Moraes and Vasques these are important results, as they forecast a predictable communication delay when supporting real-time communications with the hBEB collision resolution algorithm. These results are also consistent with the claim that the hBEB algorithm is adequate to support most part of the soft real-time applications.

The main drawback of the hBEB algorithm is that it allows at most one hBEB station per shared Ethernet segment. However, this mechanism has been extended by the use of a virtual token passing procedure in [34], allowing multiple hBEB (real-time) stations to coexist with multiple standard Ethernet stations in the same network segment, and still imposing a higher priority for the transfer of privileged traffic. This new version of hBEB is named Virtual Token Passing over hBEB or VTPE-hBEB for short and is presented in Chapter 4.

### 2.4.2 EQuB

Sobrinho and Krishnakumar [35] propose the EQuB protocol, which allows achieving predictable behaviour on shared Ethernet networks. EQuB consists on an overlay mechanism to the native CSMA/CD while providing privileged access to the former over

the latter, with a FCFS (First-Come-First-Served) access discipline between contending real-time sources.

The collision resolution mechanism for real-time sources (EQuB hosts) requires the disabling of the native exponential backoff mechanism of Ethernet and the transmission of jamming sequences with pre-defined durations. Both features are configured in the network interface card of the respective hosts. The underlying real-time traffic model assumes that, during long intervals of time called sessions, real-time hosts generate continuously periodic streams of data to be transmitted over the network.

Collisions involving non-real-time hosts, only, are sorted out by the native CSMA/CD mechanism of Ethernet. However, when real-time hosts participate in a collision, they start transmitting a jamming signal, as specified in the Ethernet MAC protocol, but with duration different from the specified 32 bit times. These crafted jamming signals are called black bursts and their maximum duration is set proportionally to the time a given host has been waiting to transmit a given message, i.e. the duration of the collision resolution process. During the transmission of a black burst, the bus state is continuously monitored. If, at some moment, a real-time host contending for the bus detects that no other nodes are sending black bursts, it infers that itself is the host having the oldest ready message (highest priority according to FCFS), subsequently aborts the transmission of its own black burst and immediately after it transmits the data message. If a real-time host transmits its black burst completely and still feels the bus jammed it infers that other hosts having longer black bursts, and consequently having a longer waiting times, are also disputing the bus. In these circumstances the host relinquishes the bus access, waiting for it to become idle for the duration of an IFS. At this time the black burst duration is recomputed, to reflect the increased waiting time.

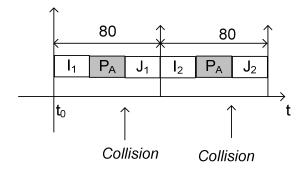

Figure 2.4 illustrates the mechanism explained before. Two hosts have one real-time message each, 1 and 2, scheduled for transmission at instants  $t_0$  and  $t_1$ , respectively, while a third data message is being transmitted (Figure 2.4). Since both hosts feel the bus busy, they wait for the end of the message transmission and for the IFS, which occurs at instant  $t_3$ . According to EQuB, both nodes attempt to transmit their message at time  $t_3$  but feel a collision and start the transmission of black bursts ( $t_4$ ). Since message 2 has a shorter waiting time than message 1, its black burst is completely transmitted, terminating at instant  $t_5$ , and the respective host backs-off, waiting for the bus to become idle again,

before retrying the message transmission. Simultaneously, the winning host, having the oldest message, feels that the bus is not being jammed anymore and thus initiates the transmission of its data message immediately after, at instant t<sub>6</sub>.

Figure 2.4: Black burst contention resolution mechanism.

It is important to realize that non real-time data messages always loose the arbitration against any real-time messages because real-time hosts transmit their messages right after the jamming signal without further delay, while the non-real-time messages follow the standard Ethernet back-off process (BEB). On the other hand, among real-time messages, the ones with longer waiting time lead to longer black bursts and thus are transmitted before other real-time messages with shorter waiting times, which results in the FCFS serialization as referred before.

An advantage of EQuB is allowing real-time and non-real-time traffic to coexist on the same Ethernet segment. Moreover, the EQuB protocol also takes advantage of the underlying periodic model of the real-time traffic and schedules the next transmission in each host based on the transmission instant of the current instance. Thus, in some circumstances, particularly when the message periods in all real-time hosts are equal or harmonic, the future instances of the respective messages will not collide again, leading to a high efficiency in bus utilization and to a round-robin service of real-time hosts. However the implementation of EQuB requires special hardware because, according to our best knowledge, there are no Ethernet controllers able to disable the backoff algorithm and to perform timing control of the jamming sequence.

## 2.4.3 Windows protocol

The Windows protocol has been proposed both for CSMA/CD and token ring networks [36]. Concerning the CSMA/CD implementation, the operation is as follows. The nodes on a network agree on a common time interval (referred to as window). All nodes synchronize upon a successful transmission, restarting the respective window. The bus state is used to assess the number of nodes with messages to be transmitted within the window:

- If the bus remains idle, there are no messages to be transmitted in the window;

- If only one message is in the window, it will be transmitted;

- If two or more messages are within the window, a collision occurs.

Depending on the bus state, several actions can be performed:

- If the bus remains idle, the window duration is increased in all nodes;

- In the case of a collision, the time window is shortened in all nodes;

- In case of a successful transmission, the window is restarted and its duration is kept as it is.

In the first two cases, the window duration is changed but the window is not restarted. Moreover, the window duration varies between a maximum (initial) and minimum values. Whenever there is a sufficiently long idle period in the bus, the window will return to its original maximum length. If a new node enters dynamically in the system, it may have instantaneous window duration different from the remaining nodes. This may cause some perturbation during an initial period, with more collisions than expected. However, as soon as an idle period occurs, all windows will converge to the initial length. A probabilistic retry mechanism may also be necessary when the windows are shrunk to their minimum and collisions still occur (e.g. when two messages have the same transmission time).

Legend:

lst,: latest sending time of message x

Figure 2.5: Resolving collisions with the Windows protocol.

Figure 2.5 shows an example of the operation of the windows protocol used to implement MLF message scheduling. The top axis represents the latest send times (lst) of messages A, B and C. The *lst* of a message is the latest time instant by which the message transmission must start so that the respective deadline is met. The first window (Step 1) includes the *lst* of the three messages, thus leading to a collision. The intervenient nodes feel the collision and the window is shrunk (Step 2). However, the *lst* of messages A and B are still inside the window, causing another collision. In response to this event the window size is shrunk again (Step 3). In this case only message A has its lst within the window, leading to a successful transmission.

This method exhibits properties that are very similar to those of the previous method (virtual time protocol). However, it is somewhat more efficient due to its adaptive behaviour. In general, it also aims at soft real-time systems and uses a fully distributed symmetrical approach with relatively low computational overhead. Notice that all message parameters are relative and that there is no global time base again. Moreover, the protocol efficiency is substantially influenced by the magnitude of variations in the window duration, either when increasing or decreasing it.

### **2.4.4 CSMA/DCR**

In [27], LeLann and Rivierre present the CSMA/DCR protocol, where DCR stands for Deterministic Collision Resolution. This protocol implements a fully deterministic network access scheme that consists on a binary tree search of colliding messages, i.e. there is a

hierarchy of priorities in the retry that allows calculating the maximum network delay a message can suffer.

During normal operation, the CSMA/DCR follows the standard IEEE 802.3 protocol (Random Access mode). However, whenever a collision is detected the protocol switches to the Epoch mode. In this mode, lower priority message sources voluntarily cease contending for the bus, and higher priority ones try again. This process in repeated until a successful transmission occurs. After all frames involved in the collision are transmitted, the protocol switches back to random access mode.

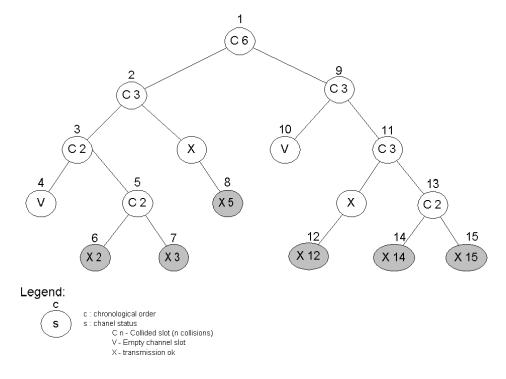

Figure 2.6 together with Table 2.1 depict the CSMA/DCR operation in a situation where 6 messages collide. Considering that lower indexes correspond to higher priorities, after the initial collision the right branch of the tree (messages 12, 14 and 15) cease contending for the bus. Since there are still three messages on the left branch, a new collision appears, between messages 2, 3 and 5. Thus, the left sub-branch is selected again, leaving message 5 out. In the following slot, messages 2 and 3 will collide again. The sub-branch selected after this collision has no active message sources, and thus in the following time slot the bus will be idle (step 4). This causes a move to the right sub-branch, where messages 3 and 5 reside, resulting in a new collision. Finally, in step 6 the branch containing only the message with index 5 is selected, resulting in a successful transmission. The algorithm continues this way until all messages are successfully transmitted.

Figure 2.6: Example of tree search with CSMA/DCR.

| Searcher Order | 1  | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|----------------|----|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

| Channel Status | С  | С | С | V | С | X | X | X | C  | V  | С  | X  | C  | X  | X  |

|                | 2  | 2 | 2 |   | 2 | 2 | 3 | 5 | 12 |    | 12 | 12 | 14 | 14 | 15 |

|                | 3  | 3 | 3 |   | 3 |   |   |   | 14 |    | 14 |    | 15 |    |    |

| Source Index   | 5  | 5 |   |   |   |   |   |   | 15 |    | 15 |    |    |    |    |

| Source mack    | 12 |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                | 14 |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                | 15 |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

Table 2.1: Tree search example (contending sequence).

Despite assuring a bounded access time to the transmission medium, this approach exhibits two main drawbacks:

- In some cases (e.g. [27]) the firmware must be modified, therefore the economy of scale obtained when using standard Ethernet hardware is lost;

- The worst-case transmission time, which is the main factor considered when designing real-time systems, can be orders of magnitude greater than the average transmission time. This forces any kind of analysis to be very

pessimistic, and therefore leads to low bandwidth utilization, at least concerning real-time traffic.

#### 2.4.5 Virtual time CSMA

The Virtual Time CSMA protocol has been presented in [39] and [40]. It allows implementing different scheduling policies (e.g. minimum-laxity first), and bases its decisions on the assessment of the communication channel status, only. When the bus becomes idle and a node has a message to transmit, it waits for a given amount of time, related to the scheduling policy implemented. For example, if MLF (minimum laxity first) scheduling is used, the waiting time is derived directly from the laxity using a proportional constant. When this amount of time expires, and if the bus is still idle, the node tries to transmit the message. If the scheduler outcome results in more than one message having permission to be transmitted at the same time (e.g. when two messages have the same laxity in MLF) then a collision occur. In this case the protocol can either recalculate the waiting time using the same rule or use a probabilistic approach according to which the messages involved in a collision are retransmitted with probability p (p-persistent). This last option is important to sort out situations in which the scheduler cannot differentiate messages, e.g. messages with the same laxity would always collide.

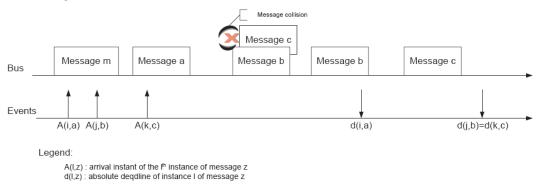

Figure 2.7 shows the operation of the Virtual-Time CSMA protocol, with MLF scheduling.

Figure 2.7: Example of Virtual-Time CSMA operation using MLF.

As it is shown in Figure 2.7 during the transmission of message m, messages a and b become ready and since the laxity of message a (i.e. deadline minus message transmission time) is shorter than the laxity of message b, message a is transmitted first.

However during the transmission of message a, message c arrives and the messages b and c have the same deadline and the same laxity. Therefore, an attempt will be made to transmit them at the same time, causing a collision. Then the algorithm uses the probabilistic approach, with message b having a lower waiting time than message c, and thus being transmitted next. Finally, message c is transmitted on the bus. Since the only global information is the channel status, there is no way to know that there is only a single message pending. For this reason, after the transmission of message b the waiting time corresponding to message c is computed, and only after the expiration of this interval message c is finally transmitted.

Beyond the advantage of using standard Ethernet hardware, this approach also has the advantage of not requiring any other global information but the channel status, which is readily available at all Network Interface Cards (NICs). Thus, a fully distributed and symmetric implementation is possible, which, in this case, also incurs in relatively low computational overhead. Nevertheless, this approach presents some important drawbacks:

- 1- Performance highly dependent on the proportional constant value used to relate the waiting time with the scheduling policy in use, leading to:

- Collisions if it is too short;

- Large amount of idle time if it is too long;

- 2- Proportional constant depends on the properties of the message set; therefore on-line changes to that set can lead to poor performance;

- 3- The waiting times are computed locally using relative parameters, only. There is no global time base and thus, relative phasing is hard to implement;

- 4- Due to possible collisions, worst-case transmission time is much higher than average transmission time and only probabilistic timeliness guarantees can be given (soft real-time systems).

# 2.5 Token passing technique

Token passing is other well-know medium access control technique suited for shared broadcast bus or ring networks. The token is a special kind of network frame to regulate network access of the individual nodes. The token flows from node to node and each node may transmit a message only when it has acquired the token. In the simplest and more common way, the token rotates in a circular fashion, which tends to divide the bandwidth

equally among all nodes in high traffic load conditions. For asymmetrical bandwidth distribution some protocols allow the token to visit the same node more than once in each token round as proposed by Cheng et al in [41]. In both cases, a basic condition for real-time operation is that the time spent by the token at each node must be bounded. This can be achieved by using a timed-token protocol [42] as in the well-known cases of FDDI, IEEE 802.4 Token Bus and PROFIBUS (this one still belonging to the same class but exhibiting a few differences).

The token passing technique is frequently used to override the native Ethernet CSMA/CD arbitration mechanism. This subsection presents three approaches using the token passing technique.

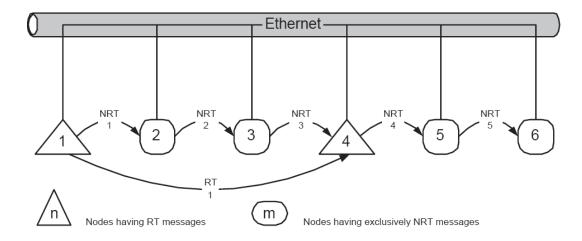

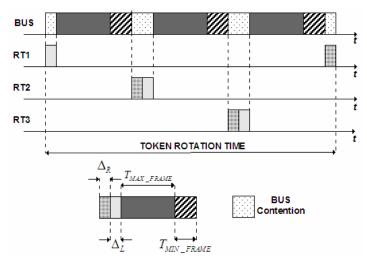

### **2.5.1 RETHER**